# 20 V, 6 A, Synchronous Step-Down DC-to-DC Regulator

## **Data Sheet**

## FEATURES

Input voltage: 4.5 V to 20 V Integrated MOSFET: 44 mΩ/11 mΩ Reference voltage: 0.6 V ± 1% Continuous output current: 6 A Programmable switching frequency: 200 kHz to 1.4 MHz Synchronizes to external clock: 200 kHz to 1.4 MHz 180° out of phase clock synchronization Precision enable and power good External compensation Internal soft start with external adjustable option Startup into a precharged output Supported by ADIsimPower design tool

#### **APPLICATIONS**

Communications infrastructure Networking and servers Industrial and instrumentation Healthcare and medical Intermediate power rail conversion DC-to-dc point-of-load applications

#### **GENERAL DESCRIPTION**

The ADP2386 is a synchronous step-down, dc-to-dc regulator with an integrated 44 m $\Omega$ , high-side power MOSFET and an 11 m $\Omega$ , synchronous rectifier MOSFET to provide a high efficiency solution in a compact 4 mm × 4 mm LFCSP package. This device uses a peak current mode, constant frequency pulse-width modulation (PWM) control scheme for excellent stability and transient response. The switching frequency of the ADP2386 can be programmed from 200 kHz to 1.4 MHz. To minimize system noise, the synchronization function allows the switching frequency to be synchronized to an external clock.

The ADP2386 requires minimal external components and operates from an input voltage of 4.5 V to 20 V. The output voltage can be adjusted from 0.6 V to 90% of the input voltage and delivers up to 6 A of continuous current. Each IC draws less than 110  $\mu$ A current from the input source when it is disabled.

This regulator targets high performance applications that require high efficiency and design flexibility. External compensation and an adjustable soft start function provide design flexibility. The powergood output and precision enable input provide simple and reliable power sequencing.

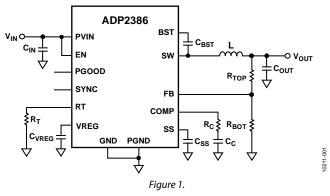

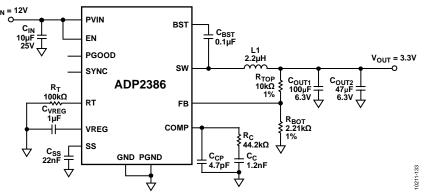

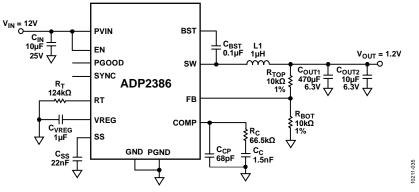

## **TYPICAL APPLICATIONS CIRCUIT**

**ADP2386**

Other key features include undervoltage lockout (UVLO), overvoltage protection (OVP), overcurrent protection (OCP), short-circuit protection (SCP), and thermal shutdown (TSD).

The ADP2386 operates over the  $-40^{\circ}$ C to  $+125^{\circ}$ C junction temperature range and is available in a 24-lead, 4 mm × 4 mm LFCSP package.

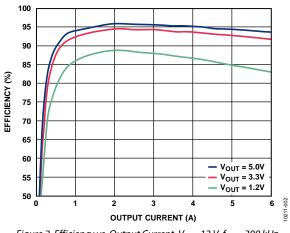

Figure 2. Efficiency vs. Output Current,  $V_{IN} = 12 V$ ,  $f_{SW} = 300 kHz$

Rev. C Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2012–2015 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# TABLE OF CONTENTS

| Features                                          |

|---------------------------------------------------|

| Applications1                                     |

| Typical Applications Circuit1                     |

| General Description                               |

| Revision History                                  |

| Specifications                                    |

| Absolute Maximum Ratings                          |

| Thermal Resistance                                |

| ESD Caution                                       |

| Pin Configuration and Function Descriptions       |

| Typical Performance Characteristics7              |

| Functional Block Diagram11                        |

| Theory of Operation12                             |

| Control Scheme                                    |

| Precision Enable/Shutdown12                       |

| Internal Regulator (VREG)12                       |

| Bootstrap Circuitry12                             |

| Oscillator                                        |

| Synchronization12                                 |

| Soft Start                                        |

| Power Good13                                      |

| Peak Current-Limit and Short-Circuit Protection13 |

| Overvoltage Protection (OVP)14                    |

| Undervoltage Lockout (UVLO)14                     |

| Thermal Shutdown14                                |

## **REVISION HISTORY**

| 10/15—Rev. B to Rev. C                |      |

|---------------------------------------|------|

| Changes to Inductor Selection Section | . 16 |

#### 7/14—Rev. A to Rev. B

| Changes to Table 2 and Table 3             | 5  |

|--------------------------------------------|----|

| Changes to Inductor Selection Section      | 15 |

| Changes to Figure 33                       | 19 |

| Changes to Compensation Components Section | 20 |

| Updated Outline Dimensions                 |    |

#### 4/13—Rev. 0 to Rev. A

| Changes to Figure 4 and Figure 7 | 7  |

|----------------------------------|----|

| Updated Outline Dimensions       | 23 |

| Changes to Ordering Guide        | 23 |

## 11/12—Revision 0: Initial Version

| Applications Information                    |

|---------------------------------------------|

| Input Capacitor Selection15                 |

| Output Voltage Setting15                    |

| Voltage Conversion Limitations15            |

| Inductor Selection 15                       |

| Output Capacitor Selection16                |

| Programming the Input Voltage UVLO 17       |

| Compensation Design17                       |

| ADIsimPower Design Tool18                   |

| Design Example 19                           |

| Output Voltage Setting (Design Example)19   |

| Frequency Setting 19                        |

| Inductor Selection (Design Example) 19      |

| Output Capacitor Selection (Design Example) |

| Compensation Components                     |

| Soft Start Time Program20                   |

| Input Capacitor Selection (Design Example)  |

| Recommended External Components 21          |

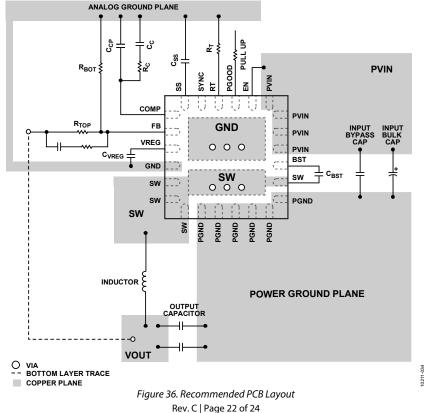

| Circuit Board Layout Recommendations 22     |

| Typical Applications Circuits               |

| Outline Dimensions                          |

| Ordering Guide                              |

# **SPECIFICATIONS**

$V_{PVIN} = 12 V$ ,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$  for minimum/maximum specifications, and  $T_A = 25^{\circ}C$  for typical specifications, unless otherwise noted.

| Parameter                                    | Symbol                | Test Conditions/Comments                | Min   | Тур  | Max   | Unit         |

|----------------------------------------------|-----------------------|-----------------------------------------|-------|------|-------|--------------|

| PVIN                                         |                       |                                         |       |      |       |              |

| PVIN Voltage Range                           | VPVIN                 |                                         | 4.5   |      | 20    | V            |

| Quiescent Current                            | lq                    | No switching                            | 2.4   | 2.9  | 3.6   | mA           |

| Shutdown Current                             | ISHDN                 | EN = GND                                | 50    | 80   | 110   | μA           |

| PVIN Undervoltage Lockout Threshold          | UVLO                  | PVIN rising                             |       | 4.3  | 4.4   | V            |

| -                                            |                       | PVIN falling                            | 3.6   | 3.8  |       | V            |

| FB                                           |                       |                                         |       |      |       |              |

| FB Regulation Voltage                        | V <sub>FB</sub>       | –40°C < T」 < 85°C                       | 0.594 | 0.6  | 0.606 | V            |

| 5                                            |                       | –40°C < T」 < 125°C                      | 0.591 | 0.6  | 0.609 | v            |

| FB Bias Current                              | I <sub>FB</sub>       |                                         |       | 0.01 | 0.1   | μA           |

| ERROR AMPLIFIER (EA)                         |                       |                                         |       |      |       |              |

| Transconductance                             | <b>g</b> <sub>m</sub> |                                         | 380   | 480  | 580   | μS           |

| EA Source Current                            | ISOURCE               |                                         | 45    | 60   | 75    | μΑ           |

| EA Sink Current                              | I <sub>SINK</sub>     |                                         | 45    | 60   | 75    | μΑ           |

| INTERNAL REGULATOR (VREG)                    |                       |                                         |       |      |       |              |

| VREG Voltage                                 | VVREG                 | $V_{PVIN} = 12 V$ , $I_{VREG} = 50 mA$  | 7.6   | 8    | 8.4   | v            |

| Dropout Voltage                              |                       | $V_{PVIN} = 12 V$ , $I_{VREG} = 50 mA$  |       | 340  |       | mV           |

| Regulator Current Limit                      |                       | , , , , , , , , , , , , , , , , , , , , | 62    | 100  | 137   | mA           |

| SW                                           |                       |                                         |       |      |       |              |

| High-Side On Resistance <sup>1</sup>         |                       | $V_{BST} - V_{SW} = 5 V$                |       | 44   | 70    | mΩ           |

| Low-Side On Resistance <sup>1</sup>          |                       | $V_{VREG} = 8 V$                        |       | 11   | 18    | mΩ           |

| High-Side Peak Current Limit                 |                       |                                         | 7.2   | 9.6  | 11.5  | A            |

| Low-Side Negative Current-Limit <sup>2</sup> |                       |                                         |       | 2.5  |       | А            |

| SW Minimum On Time                           | t <sub>MIN ON</sub>   |                                         |       | 125  | 165   | ns           |

| SW Minimum Off Time                          | t <sub>MIN_OFF</sub>  |                                         |       | 200  | 260   | ns           |

| BST                                          |                       |                                         |       |      |       |              |

| Bootstrap Voltage                            | VBOOT                 |                                         | 4.6   | 5    | 5.4   | v            |

| OSCILLATOR (RT PIN)                          |                       |                                         |       | -    |       |              |

| Switching Frequency                          | fsw                   | $R_T = 100 \text{ k}\Omega$             | 540   | 600  | 660   | kHz          |

| Switching Frequency Range                    | fsw                   |                                         | 200   |      | 1400  | kHz          |

| SYNC                                         |                       |                                         |       |      |       |              |

| Synchronization Range                        |                       |                                         | 200   |      | 1400  | kHz          |

| SYNC Minimum Pulse Width                     |                       |                                         | 100   |      |       | ns           |

| SYNC Positive Pulse Maximum Duty Cycle       | Dmax_sync             |                                         |       |      | 50    | %            |

| SYNC Input High Voltage                      |                       |                                         | 1.3   |      |       | V            |

| SYNC Input Low Voltage                       |                       |                                         |       |      | 0.4   | v            |

| SS                                           |                       |                                         |       |      |       | †.           |

| Internal Soft Start                          |                       |                                         |       | 1600 |       | Clock cycles |

| SS Pin Pull-Up Current                       | Ι.                    |                                         | 2.3   | 3.2  | 3.9   | μΑ           |

| Parameter                     | Symbol | Test Conditions/Comments           | Min  | Тур  | Max  | Unit         |

|-------------------------------|--------|------------------------------------|------|------|------|--------------|

| PGOOD                         |        |                                    |      |      |      |              |

| Power-Good Range              |        |                                    |      |      |      |              |

| FB Rising Threshold           |        | PGOOD from low to high             |      | 95   |      | %            |

| FB Rising Hysteresis          |        | PGOOD from high to low             |      | 5    |      | %            |

| FB Falling Threshold          |        | PGOOD from low to high             |      | 105  |      | %            |

| FB Falling Hysteresis         |        | PGOOD from high to low             |      | 11.7 |      | %            |

| Power-Good Deglitch Time      |        | PGOOD from low to high             |      | 1024 |      | Clock cycles |

|                               |        | PGOOD from high to low             |      | 16   |      | Clock cycles |

| Power-Good Leakage Current    |        | $V_{PGOOD} = 5 V$                  |      | 0.01 | 0.1  | μΑ           |

| Power-Good Output Low Voltage |        | $I_{PGOOD} = 1 \text{ mA}$         |      | 125  | 190  | mV           |

| EN                            |        |                                    |      |      |      |              |

| EN Rising Threshold           |        |                                    |      | 1.17 | 1.25 | V            |

| EN Falling Threshold          |        |                                    | 0.97 | 1.07 |      | V            |

| EN Source Current             |        | EN voltage below falling threshold |      | 5    |      | μΑ           |

|                               |        | EN voltage above rising threshold  |      | 1    |      | μΑ           |

| THERMAL SHUTDOWN              |        |                                    |      |      |      |              |

| Thermal Shutdown Threshold    |        |                                    |      | 150  |      | °C           |

| Thermal Shutdown Hysteresis   |        |                                    |      | 25   |      | °C           |

<sup>1</sup> Pin-to-pin measurement. <sup>2</sup> Guaranteed by design.

# **ABSOLUTE MAXIMUM RATINGS**

#### Table 2.

| Parameter                            | Rating                |

|--------------------------------------|-----------------------|

| PVIN, SW, EN, PGOOD                  | –0.3 V to +22 V       |

| SW 10 ns Transient                   | –2.5 V to +22 V       |

| SW 100 ns Transient                  | –1 V to +22 V         |

| BST                                  | V <sub>sw</sub> + 6 V |

| FB, SS, COMP, SYNC, RT               | –0.3 V to +6 V        |

| VREG                                 | –0.3 V to +12 V       |

| PGND to GND                          | –0.3 V to +0.3 V      |

| Operating Junction Temperature Range | -40°C to +125°C       |

| Storage Temperature Range            | –65°C to +150°C       |

| Soldering Conditions                 | JEDEC J-STD-020       |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a 4-layer, JEDEC standard circuit board for surface-mount packages.

#### Table 3. Thermal Resistance

| Package Type     | θ」   | οιο           | Unit |

|------------------|------|---------------|------|

| 24-Lead LFCSP_WQ | 42.6 | 6.8 (EP, SW)  | °C/W |

|                  |      | 2.3 (EP, GND) |      |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

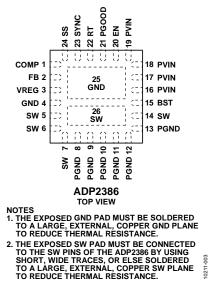

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 3. Pin Configuration

#### **Table 4. Pin Function Descriptions**

| Pin No.              | Mnemonic | Description                                                                                                                                                                                                              |

|----------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                    | COMP     | Error Amplifier Output. Connect an RC network from COMP to GND.                                                                                                                                                          |

| 2                    | FB       | Feedback Voltage Sense Input. Connect to a resistor divider from the output voltage, Vout.                                                                                                                               |

| 3                    | VREG     | Output of the Internal 8 V Regulator. The control circuits are powered from this voltage. Place a 1 μF, X7R or X5R ceramic capacitor between this pin and GND.                                                           |

| 4                    | GND      | Analog Ground. Return of internal control circuit.                                                                                                                                                                       |

| 5, 6, 7, 14          | SW       | Switch Node Output. Connect to the output inductor.                                                                                                                                                                      |

| 8, 9, 10, 11, 12, 13 | PGND     | Power Ground. Return of low-side power MOSFET.                                                                                                                                                                           |

| 15                   | BST      | Supply Rail for the High-Side Gate Drive. Place a 0.1 $\mu$ F, X7R or X5R capacitor between SW and BST.                                                                                                                  |

| 16, 17, 18, 19       | PVIN     | Power Input. Connect to the input power source and connect a bypass capacitor between this pin and PGND.                                                                                                                 |

| 20                   | EN       | Precision Enable Pin. An external resistor divider can be used to set the turn-on threshold. To enable the part automatically, connect the EN pin to the PVIN pin.                                                       |

| 21                   | PGOOD    | Power-Good Output (Open Drain). A pull-up resistor of 10 k $\Omega$ to 100 k $\Omega$ is recommended.                                                                                                                    |

| 22                   | RT       | Frequency Setting. Connect a resistor between RT and GND to program the switching frequency from 200 kHz to 1.4 MHz.                                                                                                     |

| 23                   | SYNC     | Synchronization Input. Connect this pin to an external clock to synchronize the switching frequency within a range from 200 kHz to 1.4 MHz. See the Oscillator section and Synchronization section for more information. |

| 24                   | SS       | Soft Start Control. Connect a capacitor from SS to GND to program the soft start time. If this pin is open, the regulator uses the internal soft start time.                                                             |

| 25                   | EP, GND  | The exposed GND pad must be soldered to a large, external, copper GND plane to reduce thermal resistance.                                                                                                                |

| 26                   | EP, SW   | The exposed SW pad must be connected to the SW pins of the ADP2386 by using short, wide traces, or else soldered to a large, external, copper SW plane to reduce thermal resistance.                                     |

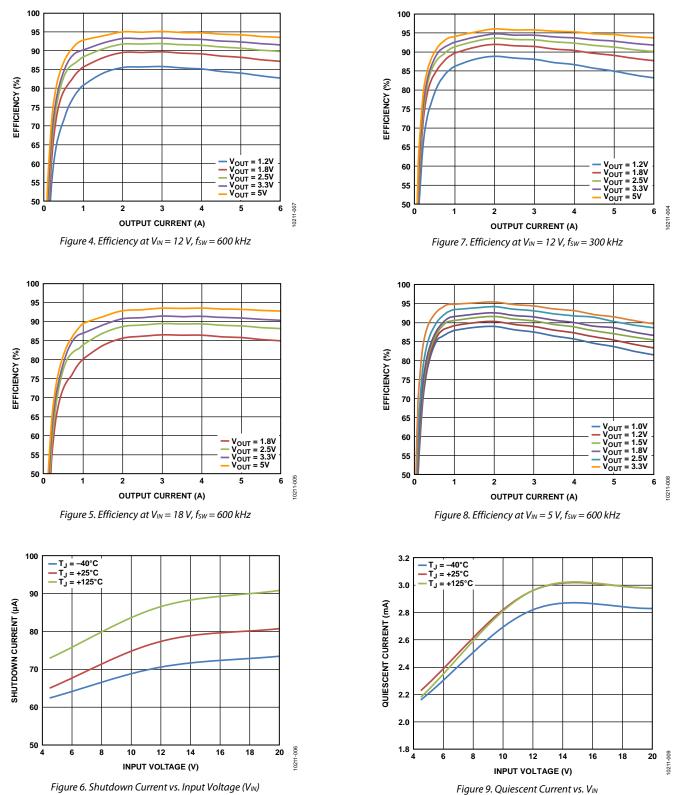

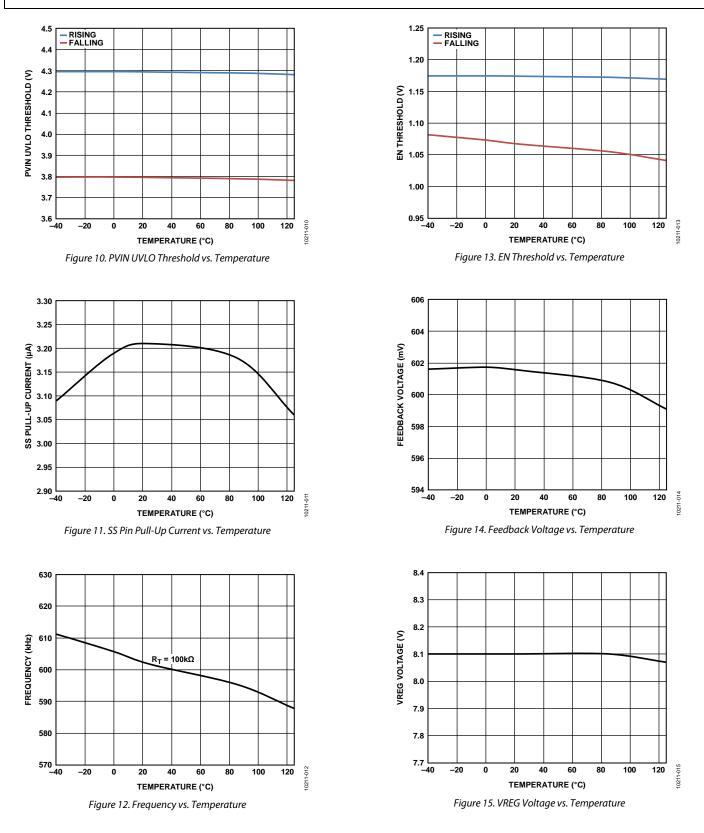

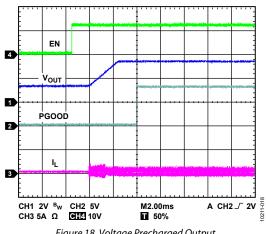

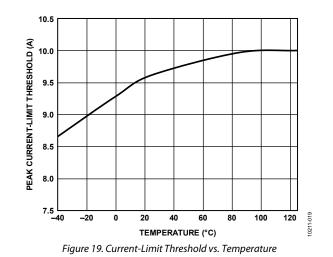

# **TYPICAL PERFORMANCE CHARACTERISTICS**

$T_{\rm A}=25^{\circ}\text{C}, V_{\rm IN}=12 \text{ V}, V_{\rm OUT}=3.3 \text{ V}, L=2.2 \text{ }\mu\text{H}, C_{\rm OUT}=100 \text{ }\mu\text{F}+47 \text{ }\mu\text{F}, f_{\rm SW}=600 \text{ }k\text{Hz}, unless otherwise noted.}$

# **Data Sheet**

65 HIGH-SIDE R<sub>DSON</sub> 55 MOSFET RESISTOR (mD) 45 35 25 15 5 └─ -40 10211-016 -20 0 20 40 60 80 100 120 TEMPERATURE (°C) Figure 16. MOSFET R<sub>DSON</sub> vs. Temperature

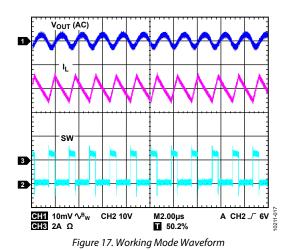

Figure 18. Voltage Precharged Output

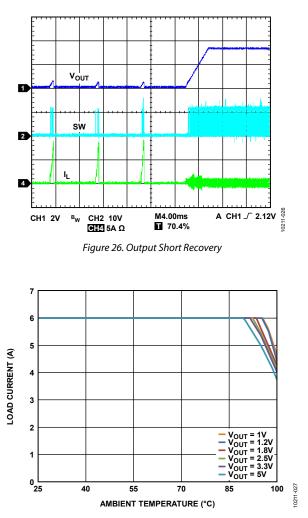

Figure 23. Output Short Entry

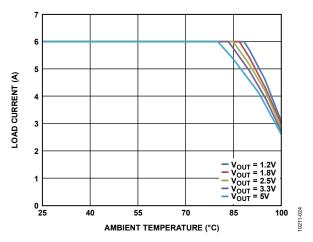

Figure 24. Load Current vs. Ambient Temperature at  $V_{\rm IN}$  = 12 V,  $f_{\rm SW}$  = 600 kHz

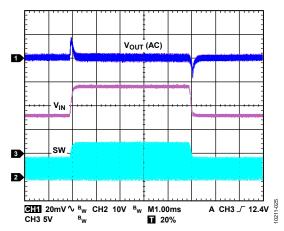

Figure 25. Line Transient Response,  $V_{IN}$  from 8 V to 14 V,  $I_{OUT} = 6 A$

Figure 27. Load Current vs. Ambient Temperature at  $V_{\rm IN}$  = 12 V,  $f_{\rm SW}$  = 300 kHz

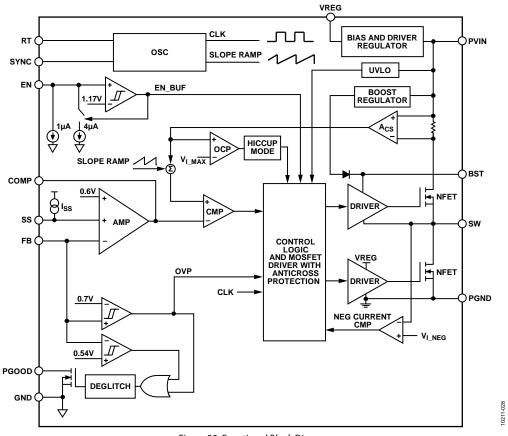

# FUNCTIONAL BLOCK DIAGRAM

Figure 28. Functional Block Diagram

# THEORY OF OPERATION

The ADP2386 is a synchronous step-down, dc-to-dc regulator that uses a current-mode architecture with an integrated highside power switch and a low-side synchronous rectifier. The regulator targets high performance applications that require high efficiency and design flexibility.

The ADP2386 operates from an input voltage that ranges from 4.5 V to 20 V and regulates the output voltage from 0.6 V to 90% of the input voltage. Additional features that maximize design flexibility include the following: programmable switching frequency, programmable soft start, external compensation, precision enable, and a power-good output.

## **CONTROL SCHEME**

The ADP2386 uses a fixed frequency, peak current-mode PWM control architecture. At the start of each oscillator cycle, the highside N-MOSFET is turned on, putting a positive voltage across the inductor. When the inductor current crosses the peak inductor current threshold, the high-side N-MOSFET is turned off and the low-side N-MOSFET is turned on. This puts a negative voltage across the inductor, causing the inductor current to decrease. The low-side N-MOSFET stays on for the rest of the cycle (see Figure 17).

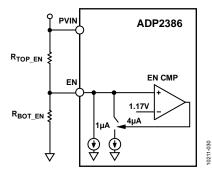

## **PRECISION ENABLE/SHUTDOWN**

The EN input pin has a precision analog threshold of 1.17 V (typical) with 100 mV of hysteresis. When the enable voltage exceeds 1.17 V, the regulator turns on; when it falls to less than 1.07 V (typical), the regulator turns off. To force the regulator to automatically start when input power is applied, connect EN to PVIN.

The precision EN pin has an internal pull-down current source (5  $\mu A)$  that provides a default turn-off when the EN pin is open.

When the EN pin voltage exceeds 1.17 V (typical), the ADP2386 is enabled and the internal pull-down current source at the EN pin decreases to 1  $\mu$ A, which allows users to program the PVIN UVLO and hysteresis.

## **INTERNAL REGULATOR (VREG)**

The on-board regulator provides a stable supply for the internal circuits. It is recommended that a 1  $\mu$ F ceramic capacitor be placed between the VREG and GND pins. The internal regulator includes a current-limit circuit to protect the output if the maximum external load current is exceeded.

## **BOOTSTRAP CIRCUITRY**

The ADP2386 includes a regulator to provide the gate drive voltage for the high-side N-MOSFET. It uses differential sensing to generate a 5 V bootstrap voltage between the BST and SW pins.

It is recommended that a 0.1  $\mu\text{F},$  X7R or X5R ceramic capacitor be placed between the BST pin and the SW pin.

## OSCILLATOR

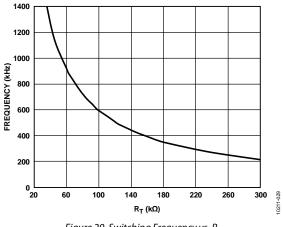

The ADP2386 switching frequency is controlled by the RT pin. A resistor from RT to GND can program the switching frequency according to the following equation:

$$f_{SW}$$

(kHz) =  $\frac{69,120}{R_r(k\Omega) + 15}$

A 100 k $\Omega$  resistor sets the frequency to 600 kHz, and a 42.2 k $\Omega$  resistor sets the frequency to 1.2 MHz. Figure 29 shows the typical relationship between  $f_{SW}$  and  $R_{T}$ .

#### Figure 29. Switching Frequency vs. $R_{T}$

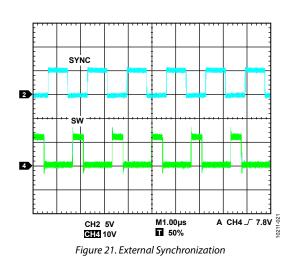

## SYNCHRONIZATION

To synchronize the ADP2386, connect an external clock to the SYNC pin. The external clock frequency can be in the range of 200 kHz to 1.4 MHz. During synchronization, the regulator operates in continuous conduction mode (CCM), and the rising edge of the switching waveform runs 180° out of phase to the rising edge of the external clock.

When the ADP2386 operates in synchronization mode, a resistor must be connected from the RT pin to GND to program the internal oscillator to run at 90% to 110% of the external synchronization clock.

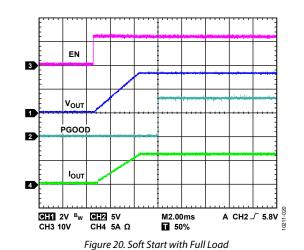

## SOFT START

The ADP2386 has integrated soft start circuitry to limit the output voltage rising time and reduce inrush current at startup. The internal soft start time is calculated using the following equation:

$$t_{SS_{INT}} = \frac{1600}{f_{SW} \text{ (kHz)}} \text{ (ms)}$$

A slower soft start time can be programmed by using the SS pin. When a capacitor is connected between the SS pin and GND, an internal current charges the capacitor to establish the soft start ramp. The soft start time is calculated using the following equation:

$$t_{SS\_EXT} = \frac{0.6 \, \text{V} \times C_{SS}}{I_{SS\_UP}}$$

where:

$C_{SS}$  is the soft start capacitance.

$\mathit{I}_{\mathit{SS\_UP}}$  is the soft start pull-up current (3.2  $\mu A$ ).

The internal error amplifier includes three positive inputs: the internal reference voltage, the internal digital soft start voltage, and the SS pin voltage. The error amplifier regulates the FB voltage to the lowest of the three voltages.

If the output voltage is charged prior to turn-on, the ADP2386 prevents reverse inductor current that would discharge the output capacitor. This function remains active until the soft start voltage exceeds the voltage on the FB pin.

## **POWER GOOD**

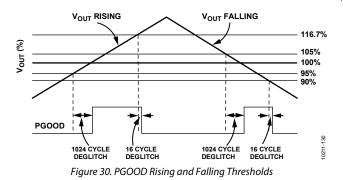

The power-good pin (PGOOD) is an active high, open-drain output that requires an external resistor to pull it up to a voltage. A logic high on the PGOOD pin indicates that the voltage on the FB pin (and, therefore, the output voltage) is within regulation.

The power-good circuitry monitors the output voltage on the FB pin and compares it to the rising and falling thresholds that are specified in Table 1. If the rising output voltage exceeds the target value, the PGOOD pin is held low. The PGOOD pin continues to be held low until the falling output voltage returns to the target value.

If the output voltage falls below the target output voltage, the PGOOD pin is held low. The PGOOD pin continues to be held low until the rising output voltage returns to the target value.

The power-good rising and falling thresholds are shown in Figure 30. There is a 1024-cycle waiting period (deglitch) before the PGOOD pin is pulled from low to high, and there is a 16-cycle waiting period (deglitch) before the PGOOD pin is pulled from high to low.

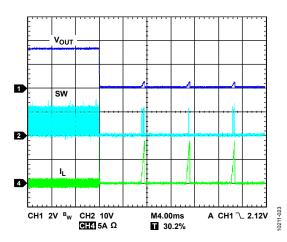

# PEAK CURRENT-LIMIT AND SHORT-CIRCUIT PROTECTION

The ADP2386 has a peak current-limit protection circuit to prevent current runaway. During the initial soft start, the ADP2386 uses frequency foldback to prevent output current runaway. The switching frequency is reduced according to the voltage on the FB pin, which allows more time for the inductor to discharge. The correlation between the switching frequency and the FB pin voltage is shown in Table 5.

#### Table 5. FB Pin Voltage and Switching Frequency

| FB Pin Voltage              | Switching Frequency |

|-----------------------------|---------------------|

| $V_{FB} \geq 0.4 \ V$       | fsw                 |

| $0.4~V > V_{FB} \geq 0.2~V$ | fsw/2               |

| $V_{FB} < 0.2 \text{ V}$    | fsw/4               |

For protection against heavy loads, the ADP2386 uses a hiccup mode for overcurrent protection. When the inductor peak current reaches the current-limit value, the high-side MOSFET turns off and the low-side MOSFET turns on until the next cycle. The overcurrent counter increments during this process. If the overcurrent counter reaches 10, or the FB pin voltage falls to 0.4 V after the soft start, the regulator enters hiccup mode. The high-side and low-side MOSFETs are both turned off. The regulator remains in hiccup mode for 4096 clock cycles and then attempts to restart. If the current-limit fault has cleared, the regulator resumes normal operation. Otherwise, it reenters hiccup mode.

The ADP2386 also provides a sink current limit to prevent the low-side MOSFET from sinking a lot of current from the load. When the voltage across the low-side MOSFET exceeds the sink current-limit threshold, which is typically 2.5 A, the low-side MOSFET turns off immediately for the rest of the cycle. Both highside and low-side MOSFETs turn off until the next clock cycle.

In some cases, the input voltage ( $V_{PVIN}$ ) ramp rate is too slow or the output capacitor is too large for the output to reach regulation during the soft start process, which causes the regulator to enter the hiccup mode. To avoid such occurrences, use a resistor divider at the EN pin to program the input voltage UVLO, or use a longer soft start time.

## **OVERVOLTAGE PROTECTION (OVP)**

The ADP2386 includes an overvoltage protection feature to protect the regulator against an output short to a higher voltage supply or when a strong load disconnect transient occurs. If the feedback voltage increases to 0.7 V, the internal high-side and low-side MOSFETs are turned off until the voltage at the FB pin decreases to 0.63 V. At that time, the ADP2386 resumes normal operation.

#### **UNDERVOLTAGE LOCKOUT (UVLO)**

Undervoltage lockout circuitry is integrated in the ADP2386 to prevent the occurrence of power-on glitches. If the V<sub>PVIN</sub> voltage falls to less than 3.8 V typical, the part shuts down, and both the power switch and synchronous rectifier turn off. When the V<sub>PVIN</sub> voltage rises to greater than 4.3 V typical, the soft start period is initiated, and the part is enabled.

## THERMAL SHUTDOWN

If the ADP2386 junction temperatures rises to greater than 150°C, the internal thermal shutdown circuit turns off the regulator for self-protection. Extreme junction temperatures can be the result of high current operation, poor circuit board thermal design, and/or high ambient temperature. A 25°C hysteresis is included in the thermal shut-down circuit so that, if an overtemperature event occurs, the ADP2386 does not return to normal operation until the on-chip temperature falls to less than 125°C. Upon recovery, a soft start is initiated before normal operation begins.

## APPLICATIONS INFORMATION INPUT CAPACITOR SELECTION

The input capacitor reduces the input voltage ripple caused by the switch current on PVIN. Place the input capacitor as close as possible to the PVIN pin. A ceramic capacitor in the 10  $\mu$ F to 47  $\mu$ F range is recommended. The loop that is composed of this input capacitor, the high-side N-MOSFET, and the low-side N-MOSFET must be kept as small as possible.

The voltage rating of the input capacitor must be greater than the maximum input voltage. Ensure that the rms current rating of the input capacitor is larger than the value calculated from the following equation:

$$I_{C_{IN}_{RMS}} = I_{OUT} \times \sqrt{D \times (1-D)}$$

## **OUTPUT VOLTAGE SETTING**

The output voltage of the ADP2386 is set by an external resistive divider. The resistor values are calculated using

$$V_{OUT} = 0.6 \times \left(1 + \frac{R_{TOP}}{R_{BOT}}\right)$$

To limit the output voltage accuracy degradation due to the FB bias current (0.1  $\mu A$  maximum) to less than 0.5% (maximum), ensure that  $R_{BOT} < 30~k\Omega.$

Table 6 lists the recommended resistor divider values for the various output voltages.

| V <sub>оит</sub> (V) | $R_{TOP} \pm 1\%$ (kΩ) | R <sub>BOT</sub> ± 1% (kΩ) |  |  |  |  |  |

|----------------------|------------------------|----------------------------|--|--|--|--|--|

| 1.0                  | 10                     | 15                         |  |  |  |  |  |

| 1.2                  | 10                     | 10                         |  |  |  |  |  |

| 1.5                  | 15                     | 10                         |  |  |  |  |  |

| 1.8                  | 20                     | 10                         |  |  |  |  |  |

| 2.5                  | 47.5                   | 15                         |  |  |  |  |  |

| 3.3                  | 10                     | 2.21                       |  |  |  |  |  |

| 5.0                  | 22                     | 3                          |  |  |  |  |  |

#### **VOLTAGE CONVERSION LIMITATIONS**

The minimum output voltage for a given input voltage and switching frequency is constrained by the minimum on time. The minimum on time of the ADP2386 is typically 125 ns. The minimum output voltage for a given input voltage and switching frequency can be calculated using the following:

$$V_{OUT\_MIN} = V_{IN} \times t_{MIN\_ON} \times f_{SW} - (R_{DSON\_HS} - R_{DSON\_LS}) \times I_{OUT\_MIN} \times t_{MIN\_ON} \times f_{SW} - (R_{DSON\_LS} + R_L) \times I_{OUT\_MIN}$$

(1)

where:

$V_{OUT\_MIN}$  is the minimum output voltage.  $V_{IN}$  is the input voltage.  $t_{MIN\_ON}$  is the minimum on time.  $f_{SW}$  is the switching frequency.  $R_{DSON\_HS}$  is the high-side MOSFET on resistance.  $R_{DSON\_LS}$  is the low-side MOSFET on resistance.  $I_{OUT\_MIN}$  is the minimum output current.  $R_L$  is the series resistance of the output inductor.

The maximum output voltage for a given input voltage and switching frequency is constrained by the minimum off time and the maximum duty cycle. The minimum off time is typically 200 ns, and the maximum duty cycle of the ADP2386 is typically 90%.

The maximum output voltage, limited by the minimum off time at a given input voltage and switching frequency, can be calculated using the following equation:

$V_{OUT\_MAX} = V_{IN} \times (1 - t_{MIN\_OFF} \times f_{SW}) - (R_{DSON\_HS} - R_{DSON\_LS}) \times I_{OUT\_MAX} \times (1 - t_{MIN\_OFF} \times f_{SW}) - (R_{DSON\_LS} + R_L) \times I_{OUT\_MAX}$ (2)

where:

$V_{OUT\_MAX}$  is the maximum output voltage.  $V_{IN}$  is the input voltage.  $t_{MIN\_OFF}$  is the minimum off time.  $f_{SW}$  is the switching frequency.  $R_{DSON\_HS}$  is the high-side MOSFET on resistance.  $R_{DSON\_LS}$  is the low-side MOSFET on resistance.  $I_{OUT\_MAX}$  is the maximum output current.

$R_L$  is the series resistance of the output inductor.

The maximum output voltage, limited by the maximum duty cycle at a given input voltage, can be calculated using the following equation:

$$V_{OUT\_MAX} = D_{MAX} \times V_{IN} \tag{3}$$

where  $D_{\mbox{\tiny MAX}}$  is the maximum duty cycle;  $V_{\mbox{\tiny IN}}$  is the input voltage.

As shown in Equation 1 to Equation 3, reducing the switching frequency alleviates the minimum on time and minimum off time limitation.

## **INDUCTOR SELECTION**

The inductor value is determined by the operating frequency, input voltage, output voltage, and inductor ripple current. Using a small inductor value leads to a faster transient response; however, it degrades efficiency, due to a larger inductor ripple current. Using a large inductor value leads to smaller ripple current and better efficiency, but it results in a slower transient response.

As a guideline, the inductor ripple current,  $\Delta I_L$ , is typically set to one-third of the maximum load current. The inductor value is calculated using the following equation:

$$L = \frac{(V_{IN} - V_{OUT}) \times D}{\Delta I_L \times f_{SW}}$$

where:

$V_{IN}$  is the input voltage.  $V_{OUT}$  is the output voltage. D is the duty cycle (D = V\_{OUT}/V\_{IN}).  $\Delta I_L$  is the inductor current ripple.  $f_{SW}$  is the switching frequency.

The ADP2386 uses adaptive slope compensation in the current loop to prevent subharmonic oscillations when the duty cycle is larger than 50%. The internal slope compensation limits the minimum inductor value.

For a duty cycle that is larger than 50%, the minimum inductor value is determined using the following equation:

$$L (Minimum) = \frac{V_{OUT} \times (1-D)}{4 \times f_{SW}}$$

The peak inductor current is calculated by

$$I_{PEAK} = I_{OUT} + \frac{\Delta I_L}{2}$$

The saturation current of the inductor must be larger than the peak inductor current. For ferrite core inductors with a quick saturation characteristic, the saturation current rating of the inductor must be higher than the current-limit threshold of the switch. This prevents the inductor from reaching saturation.

The rms current of the inductor is calculated as follows:

$$I_{RMS} = \sqrt{I_{OUT}^2 + \frac{\Delta I_L^2}{12}}$$

Shielded ferrite core materials are recommended for low core loss and low EMI. Table 7 lists some recommended inductors.

## **OUTPUT CAPACITOR SELECTION**

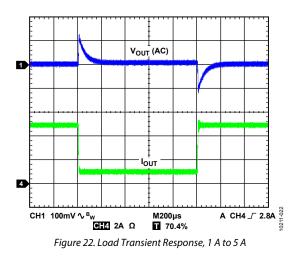

The output capacitor selection affects the output ripple voltage load step transient and the loop stability of the regulator.

For example, during a load step transient where the load is suddenly increased, the output capacitor supplies the load until the control loop can ramp up the inductor current. The delay caused by the control loop causes output undershoot. To calculate the output capacitance that is required to satisfy the voltage droop requirement use the following equation:

| $C_{OUT_UV} =$ | $K_{UV} \times \Delta I_{STEP}^2 \times L$          |    |  |  |  |  |

|----------------|-----------------------------------------------------|----|--|--|--|--|

|                | $2 \times (V_{IN} - V_{OUT}) \times \Delta V_{OUT}$ | UV |  |  |  |  |

where:

$K_{UV}$  is a factor, with a typical setting of  $K_{UV} = 2$ .

$\Delta I_{STEP}$  is the load step.

$\Delta V_{\textit{OUT\_UV}}$  is the allowable undershoot on the output voltage.

Another example occurs when a load is suddenly removed from the output, and the energy stored in the inductor rushes into the output capacitor, causing the output to overshoot.

To calculate the output capacitance that is required to meet the overshoot requirement use the following equation:

$$C_{OUT\_OV} = \frac{K_{OV} \times \Delta I_{STEP}^{2} \times L}{(V_{OUT} + \Delta V_{OUT\_OV})^{2} - V_{OUT}^{2}}$$

where:

$\Delta V_{OUT_OV}$  is the allowable overshoot on the output voltage. *K*<sub>OV</sub> is a factor, with a typical setting of *K*<sub>OV</sub> = 2.

The output ripple is determined by the ESR and the value of the capacitance. Use the following equations to select a capacitor that can meet the output ripple requirements:

$$C_{OUT\_RIPPLE} = \frac{\Delta I_L}{8 \times f_{SW} \times \Delta V_{OUT\_RIPPLE}}$$

$$R_{ESR} = \frac{\Delta V_{OUT\_RIPPLE}}{\Delta I_L}$$

where:

$\Delta I_L$  is the inductor current ripple.

$\Delta V_{OUT\_RIPPLE}$  is the allowable output ripple voltage.

$R_{ESR}$  is the equivalent series resistance of the output capacitor in ohms ( $\Omega$ ).

Select the largest output capacitance given by  $C_{OUT\_UV}$ ,  $C_{OUT\_OV}$ , and  $C_{OUT\_RIPPLE}$  to meet both load transient and output ripple performance.

| Vendor           | Part No.           | Value (µH) | I <sub>SAT</sub> (A) | I <sub>RMS</sub> (A) | DCR (mΩ) |  |

|------------------|--------------------|------------|----------------------|----------------------|----------|--|

| Toko             | FDVE0630-R47M      | 0.47       | 15.6                 | 14.1                 | 3.7      |  |

|                  | FDVE0630-R75M      | 0.75       | 10.9                 | 10.7                 | 6.2      |  |

|                  | FDVE0630-1R0M      | 1.0        | 9.5                  | 9.5                  | 8.5      |  |

|                  | FDVE1040-1R5M      | 1.5        | 13.7                 | 14.6                 | 4.6      |  |

|                  | FDVE1040-2R2M      | 2.2        | 11.4                 | 11.6                 | 6.8      |  |

|                  | FDVE1040-3R3M      | 3.3        | 9.8                  | 9.0                  | 10.1     |  |

|                  | FDVE1040-4R7M      | 4.7        | 8.2                  | 8.0                  | 13.8     |  |

| Vishay           | IHLP3232DZ-R47M-11 | 0.47       | 14                   | 25                   | 2.38     |  |

|                  | IHLP3232DZ-R68M-11 | 0.68       | 14.5                 | 22.2                 | 3.22     |  |

|                  | IHLP3232DZ-1R0M-11 | 1.0        | 12                   | 18.2                 | 4.63     |  |

|                  | IHLP4040DZ-1R5M-01 | 1.5        | 27.5                 | 15                   | 5.8      |  |

|                  | IHLP4040DZ-2R2M-01 | 2.2        | 25.6                 | 12                   | 9        |  |

|                  | IHLP4040DZ-3R3M-01 | 3.3        | 18.6                 | 10                   | 14.4     |  |

|                  | IHLP4040DZ-4R7M-01 | 4.7        | 17                   | 9.5                  | 16.5     |  |

| Wurth Elektronik | 744 325 120        | 1.2        | 25                   | 20                   | 1.8      |  |

|                  | 744 325 180        | 1.8        | 18                   | 16                   | 3.5      |  |

|                  | 744 325 240        | 2.4        | 17                   | 14                   | 4.75     |  |

|                  | 744 325 330        | 3.3        | 15                   | 12                   | 5.9      |  |

|                  | 744 325 420        | 4.2        | 14                   | 11                   | 7.1      |  |

The selected output capacitor voltage rating must be greater than the output voltage. The rms current rating of the output capacitor must be larger than the value that is calculated by

$$I_{C_{OUT}-RMS} = \frac{\Delta I_L}{\sqrt{12}}$$

#### **PROGRAMMING THE INPUT VOLTAGE UVLO**

The ADP2386 has a precision enable input that can be used to program the UVLO threshold of the input voltage (see Figure 31).

Figure 31. Programming the Input Voltage UVLO

Use the following equations to calculate  $R_{\text{TOP}\_\text{EN}}$  and  $R_{\text{BOT}\_\text{EN}}$ :

$$R_{TOP\_EN} = \frac{1.07 \text{ V} \times V_{IN\_RISING} - 1.17 \text{ V} \times V_{IN\_FALLING}}{1.07 \text{ V} \times 5\mu\text{A} - 1.17 \text{ V} \times 1\mu\text{A}}$$

$$R_{BOT\_EN} = \frac{1.17 \text{ V} \times R_{TOP\_EN}}{V_{IN\_RISING} - R_{TOP\_EN} \times 5\mu\text{A} - 1.17 \text{ V}}$$

where:

$V_{IN\_RISING}$  is the V<sub>IN</sub> rising threshold.  $V_{IN\_FALLING}$  is the V<sub>IN</sub> falling threshold.

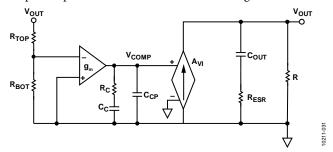

#### **COMPENSATION DESIGN**

For peak current-mode control, the power stage can be simplified as a voltage controlled current source supplying current to the output capacitor and load resistor. It is composed of one domain pole and a zero that is contributed by the output capacitor ESR. The control-to-output transfer function is based on the following:

$$G_{VD}(s) = \frac{V_{OUT}(s)}{V_{COMP}(s)} = A_{VI} \times R \times \frac{\left(1 + \frac{s}{2 \times \pi \times f_Z}\right)}{\left(1 + \frac{s}{2 \times \pi \times f_P}\right)}$$

$$f_Z = \frac{1}{2 \times \pi \times R_{ESR} \times C_{OUT}}$$

$$f_P = \frac{1}{2 \times \pi \times (R + R_{ESR}) \times C_{OUT}}$$

where:

$A_{VI} = 8.7 \text{ A/V.}$

*R* is the load resistance.

$C_{OUT}$  is the output capacitance.

$R_{ESR}$  is the equivalent series resistance of the output capacitor.

The ADP2386 uses a transconductance amplifier for the error amplifier and to compensate the system. Figure 32 shows the simplified, peak current-mode control, small signal circuit.

Figure 32. Simplified Peak Current Mode Control, Small Signal Circuit

The compensation components,  $R_C$  and  $C_C$ , contribute a zero, and  $R_C$  and the optional  $C_{CP}$  contribute an optional pole.

The closed-loop transfer equation is as follows:

$$T_{V}(s) = \frac{R_{BOT}}{R_{BOT} + R_{TOP}} \times \frac{-g_{m}}{C_{C} + C_{CP}} \times \frac{1 + R_{C} \times C_{C} \times s}{s \times (1 + \frac{R_{C} \times C_{C} \times C_{CP}}{C_{C} + C_{CP}} \times s)} \times G_{VD}(s)$$

The following design guideline shows how to select the  $R_c$ ,  $C_c$ , and  $C_{CP}$  compensation components for ceramic output capacitor applications:

- 1. Determine the cross frequency,  $f_{\rm C}$  . Generally,  $f_{\rm C}$  is between  $f_{\rm SW}/12$  and  $f_{\rm SW}/6.$

- 2. Calculate R<sub>c</sub>, using the following equation:

$$R_{C} = \frac{2 \times \pi \times V_{OUT} \times C_{OUT} \times f_{C}}{0.6 \,\mathrm{V} \times g_{m} \times A_{VI}}$$

3. Place the compensation zero at the domain pole, f<sub>P</sub>; then determine C<sub>C</sub> by using the following equation:

$$C_C = \frac{(R + R_{ESR}) \times C_{OUT}}{R_C}$$

4.  $C_{CP}$  is optional. It can be used to cancel the zero caused by the ESR of the output capacitor.

$$C_{CP} = \frac{R_{ESR} \times C_{OUT}}{R_C}$$

## **ADIsimPOWER DESIGN TOOL**

The ADP2386 is supported by the ADIsimPower<sup>™</sup> design tool set. ADIsimPower is a collection of tools that produce complete power designs that are optimized for a specific design goal. The tools enable the user to generate a full schematic and bill of materials and calculate performance in minutes. ADIsimPower can optimize designs for cost, area, efficiency, and part count, while taking into consideration the operating conditions and limitations of the IC and all real external components. For more information about theADIsimPower design tools, refer to www.analog.com/ADIsimPower. The tool set is available from this website, and users can request an unpopulated board.

# **DESIGN EXAMPLE**

Figure 33. Schematic for Design Example Please change

This section describes the procedures for selecting the external components, based on the example specifications that are listed in Table 8. See Figure 33 for the schematic of this design example.

#### Table 8. Step-Down DC-to-DC Regulator Requirements

| <b>1</b>              | 0 1                                                |

|-----------------------|----------------------------------------------------|

| Parameter             | Specification                                      |

| Input Voltage         | $V_{IN} = 12.0 V \pm 10\%$                         |

| Output Voltage        | V <sub>OUT</sub> = 3.3 V<br>I <sub>OUT</sub> = 6 A |

| Output Current        | I <sub>OUT</sub> = 6 A                             |

| Output Voltage Ripple | $\Delta V_{OUT_{RIPPLE}} = 33 \text{ mV}$          |

| Load Transient        | ±5%, 1 A to 5 A, 2 A/μs                            |

| Switching Frequency   | $f_{sw} = 600 \text{ kHz}$                         |

## **OUTPUT VOLTAGE SETTING (DESIGN EXAMPLE)**

Choose a 10 k $\Omega$  resistor as the top feedback resistor (R<sub>TOP</sub>), and calculate the bottom feedback resistor (R<sub>BOT</sub>) by using the following equation:

$$R_{BOT} = R_{TOP} \times \left(\frac{0.6}{V_{OUT} - 0.6}\right)$$

To set the output voltage to 3.3 V, the resistors values are as follows:  $R_{TOP} = 10 \text{ k}\Omega$ , and  $R_{BOT} = 2.21 \text{ k}\Omega$ .

#### **FREQUENCY SETTING**

To set the switching frequency to 600 kHz, connect a 100 k $\Omega$  resistor from the RT pin to GND.

#### **INDUCTOR SELECTION (DESIGN EXAMPLE)**

The peak-to-peak inductor ripple current,  $\Delta I_L$ , is set to 30% of the maximum output current. Use the following equation to estimate the inductor value:

$$L = \frac{(V_{IN} - V_{OUT}) \times D}{\Delta I_L \times f_{SW}}$$

where:  $V_{IN} = 12$  V.  $V_{OUT} = 3.3$  V. D = 0.275.  $\Delta I_L = 1.8$  A.  $f_{SW} = 600$  kHz. This calculation results in L = 2.215  $\mu$ H. Choose the standard inductor value of 2.2  $\mu$ H.

The peak-to-peak inductor ripple current can be calculated by using the following equation:

$$\Delta I_L = \frac{(V_{IN} - V_{OUT}) \times D}{L \times f_{SW}}$$

This calculation results in  $\Delta I_L = 1.81$  A.

Use the following equation to calculate the peak inductor current:

$$I_{PEAK} = I_{OUT} + \frac{\Delta I_L}{2}$$

This calculation results in  $I_{PEAK} = 6.905$  A.

Use the following equation to calculate the rms current flowing through the inductor:

$$I_{RMS} = \sqrt{I_{OUT}^2 + \frac{\Delta I_L^2}{12}}$$

This calculation results in  $I_{RMS} = 6.023$  A.

Based on the calculated current value, select an inductor with a minimum rms current rating of 6.03 A and a minimum saturation current rating of 6.91 A.

However, to protect the inductor from reaching its saturation point under the current-limit condition, the inductor should be rated for at least a 9.6 A saturation current for reliable operation.

Based on the requirements described previously, select a 2.2  $\mu H$  inductor, such as the FDVE1040-2R2M from Toko, which has a 6.8 m $\Omega$  DCR and a 11.4 A saturation current.

## OUTPUT CAPACITOR SELECTION (DESIGN EXAMPLE)

The output capacitor is required to meet both the output voltage ripple and load transient response requirements.

To meet the output voltage ripple requirement, use the following equation to calculate the ESR and capacitance value of the output capacitor:

$$C_{OUT\_RIPPLE} = \frac{\Delta I_L}{8 \times f_{SW} \times \Delta V_{OUT\_RIPPLE}}$$

$$R_{ESR} = \frac{\Delta V_{OUT\_RIPPLE}}{\Delta I_L}$$

This calculation results in Cout\_RIPPLE = 11.4  $\mu$ F, and Resr = 18 m $\Omega$ .

To meet the  $\pm 5\%$  overshoot and undershoot transient requirements, use the following equations to calculate the capacitance:

$$C_{OUT\_OV} = \frac{K_{OV} \times \Delta I_{STEP}^{2} \times L}{(V_{OUT} + \Delta V_{OUT\_OV})^{2} - V_{OUT}^{2}}$$

$$C_{OUT\_UV} = \frac{K_{UV} \times \Delta I_{STEP}^{2} \times L}{2 \times (V_{IN} - V_{OUT}) \times \Delta V_{OUT\_UV}}$$

where:

$K_{OV} = K_{UV} = 2$  are the coefficients for estimation purposes.  $\Delta I_{STEP} = 4$  A is the load transient step.  $\Delta V_{OUT\_OV} = 5\%$  V<sub>OUT</sub> is the overshoot voltage.  $\Delta V_{OUT\_UV} = 5\%$  V<sub>OUT</sub> is the undershoot voltage.

This calculation results in  $C_{OUT_OV} = 63.1 \,\mu\text{F}$ , and  $C_{OUT_UV} = 24.5 \,\mu\text{F}$ .

According to the calculation, the output capacitance must be greater than 63  $\mu$ F, and the ESR of the output capacitor must be smaller than 18 m $\Omega$ . It is recommended that one 100  $\mu$ F/X5R/6.3 V ceramic capacitor and one 47  $\mu$ F/X5R/6.3 V ceramic capacitor be used, such as the GRM32ER60J107ME20 and GRM32ER60J476ME20 from Murata, with an ESR of 2 m $\Omega$ .

#### **COMPENSATION COMPONENTS**

For better load transient and stability performance, set the cross frequency,  $f_c$ , to  $f_{sw}/10$ . In this case,  $f_{sw}$  is running at 600 kHz; therefore, the  $f_c$  is set to 60 kHz.

The 100  $\mu F$  and 47  $\mu F$  ceramic output capacitors have a derated value of 62  $\mu F$  and 32  $\mu F.$

$$R_{C} = \frac{2 \times \pi \times 3.3 \text{ V} \times 94 \,\mu\text{F} \times 60 \,\text{kHz}}{0.6 \,\text{V} \times 480 \,\mu\text{S} \times 8.7 \,\text{A/V}} = 46.7 \,\text{k}\Omega$$

$$C_{C} = \frac{(0.55 \,\Omega + 0.002 \,\Omega) \times 94 \,\mu\text{F}}{46.7 \,\text{k}\Omega} = 1111 \,\text{pF}$$

$$C_{CP} = \frac{0.002 \ \Omega \times 94 \ \mu F}{46.7 \ k\Omega} = 4.0 \ pF$$

Choose standard components, as follows:  $R_{\rm C}$  = 44.2 kΩ,  $C_{\rm C}$  = 1200 pF, and  $C_{\rm CP}$  = 4.7 pF.

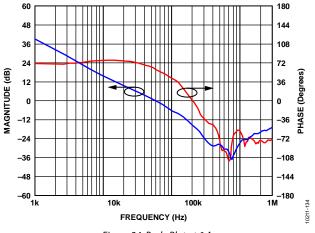

Figure 34 shows the bode plot at 6 A. The cross frequency is 58 kHz, and the phase margin is 61°.

Figure 34. Bode Plot at 6 A

#### SOFT START TIME PROGRAM

The soft start feature allows the output voltage to ramp up in a controlled manner, eliminating output voltage overshoot during soft start and limiting the inrush current. Set the soft start time to 4 ms.

$$C_{SS} = \frac{t_{SS\_EXT} \times I_{SS\_UP}}{0.6} = \frac{4 \text{ ms} \times 3.2 \mu \text{A}}{0.6 \text{ V}} = 21.3 \text{ nF}$$

Choose a standard component value, as follows:  $C_{SS} = 22 \text{ nF}$ .

#### INPUT CAPACITOR SELECTION (DESIGN EXAMPLE)

Place a minimum 10  $\mu F$  ceramic capacitor near the PVIN pin. In this application, it is recommended that one 10  $\mu F$ , X5R, 25 V ceramic capacitor be used.

## **RECOMMENDED EXTERNAL COMPONENTS**

Table 9. Recommended External Components for Typical Applications with 6 A Output Current

| fsw (kHz) | V <sub>IN</sub> (V) | Vout (V) | L (µH) | <b>C</b> <sub>OUT</sub> (μ <b>F</b> ) <sup>1</sup> | <b>R</b> <sub>TOP</sub> ( <b>k</b> Ω) | <b>R</b> <sub>BOT</sub> ( <b>k</b> Ω) | R <sub>c</sub> (kΩ) | C <sub>c</sub> (pF) | C <sub>CP</sub> (pF) |

|-----------|---------------------|----------|--------|----------------------------------------------------|---------------------------------------|---------------------------------------|---------------------|---------------------|----------------------|

| 300       | 12                  | 1        | 1.5    | 680 + 2 × 100                                      | 10                                    | 15                                    | 57.6                | 2200                | 150                  |

|           | 12                  | 1.2      | 2.2    | 680 + 2 × 100                                      | 10                                    | 10                                    | 68.1                | 2200                | 120                  |

|           | 12                  | 1.5      | 2.2    | 680                                                | 15                                    | 10                                    | 73.2                | 2200                | 100                  |

|           | 12                  | 1.8      | 3.3    | 680                                                | 20                                    | 10                                    | 88.7                | 2200                | 82                   |

|           | 12                  | 2.5      | 3.3    | 470                                                | 47.5                                  | 15                                    | 84.5                | 2200                | 47                   |

|           | 12                  | 3.3      | 4.7    | 3 × 100                                            | 10                                    | 2.21                                  | 44.2                | 2200                | 8.2                  |

|           | 12                  | 5        | 4.7    | 100 + 47                                           | 22                                    | 3                                     | 33                  | 2200                | 4.7                  |

|           | 5                   | 1        | 1.5    | $680 + 2 \times 100$                               | 10                                    | 15                                    | 57.6                | 2200                | 150                  |

|           | 5                   | 1.2      | 1.5    | 680                                                | 10                                    | 10                                    | 57.6                | 2200                | 120                  |

|           | 5                   | 1.5      | 2.2    | 680                                                | 15                                    | 10                                    | 73.2                | 2200                | 100                  |

|           | 5                   | 1.8      | 2.2    | 470                                                | 20                                    | 10                                    | 61.9                | 2200                | 82                   |

|           | 5                   | 2.5      | 2.2    | 3 × 100                                            | 47.5                                  | 15                                    | 33                  | 2200                | 10                   |

|           | 5                   | 3.3      | 2.2    | 3 × 100                                            | 10                                    | 2.21                                  | 44.2                | 2200                | 8.2                  |

| 600       | 12                  | 1.5      | 1      | 3 × 100                                            | 15                                    | 10                                    | 39                  | 1200                | 10                   |

|           | 12                  | 1.8      | 1.5    | 3 × 100                                            | 20                                    | 10                                    | 47                  | 1200                | 8.2                  |

|           | 12                  | 2.5      | 2.2    | 2×100                                              | 47.5                                  | 15                                    | 44.2                | 1200                | 4.7                  |

|           | 12                  | 3.3      | 2.2    | 100 + 47                                           | 10                                    | 2.21                                  | 44.2                | 1200                | 4.7                  |

|           | 12                  | 5        | 3.3    | 100                                                | 22                                    | 3                                     | 44.2                | 1200                | 2.2                  |

|           | 5                   | 1        | 1      | 680                                                | 10                                    | 15                                    | 97.6                | 1200                | 68                   |

|           | 5                   | 1.2      | 1      | 470                                                | 10                                    | 10                                    | 82                  | 1200                | 47                   |

|           | 5                   | 1.5      | 1      | 3 × 100                                            | 15                                    | 10                                    | 39                  | 1200                | 10                   |

|           | 5                   | 1.8      | 1      | 2 × 100                                            | 20                                    | 10                                    | 33                  | 1200                | 8.2                  |

|           | 5                   | 2.5      | 1      | 100                                                | 47.5                                  | 15                                    | 22                  | 1200                | 4.7                  |

|           | 5                   | 3.3      | 1      | 100 + 47                                           | 10                                    | 2.21                                  | 44.2                | 1200                | 4.7                  |

| 1000      | 12                  | 2.5      | 1      | 100                                                | 47.5                                  | 15                                    | 37.4                | 680                 | 3.3                  |

|           | 12                  | 3.3      | 1.5    | 100                                                | 10                                    | 2.21                                  | 47                  | 680                 | 2.2                  |

|           | 12                  | 5        | 1.5    | 100                                                | 22                                    | 3                                     | 73.2                | 680                 | 2.2                  |

|           | 5                   | 1        | 0.47   | 3 × 100                                            | 10                                    | 15                                    | 44.2                | 680                 | 8.2                  |

|           | 5                   | 1.2      | 0.47   | 2 × 100                                            | 10                                    | 10                                    | 34.8                | 680                 | 6.8                  |

|           | 5                   | 1.5      | 0.68   | 100 + 47                                           | 15                                    | 10                                    | 33                  | 680                 | 4.7                  |

|           | 5                   | 1.8      | 0.68   | 100 + 47                                           | 20                                    | 10                                    | 39                  | 680                 | 4.7                  |

|           | 5                   | 2.5      | 0.68   | 100                                                | 47.5                                  | 15                                    | 37.4                | 680                 | 3.3                  |

|           | 5                   | 3.3      | 0.68   | 100                                                | 10                                    | 2.21                                  | 47                  | 680                 | 2.2                  |

<sup>1</sup> 680 μF: 4 V, Sanyo 4TPF680M; 470 μF: 6.3 V, Sanyo 6TPF470M; 100 μF: 6.3 V, X5R, Murata GRM32ER60J107ME20; 47 μF: 6.3 V, X5R, Murata GRM32ER60J476ME20.

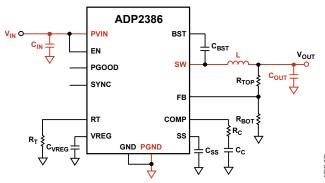

# **CIRCUIT BOARD LAYOUT RECOMMENDATIONS**

Good printed circuit board (PCB) layout is essential for obtaining the best performance from the ADP2386. Poor PCB layout can degrade the output regulation, as well as the electromagnetic interference (EMI) and electromagnetic compatibility (EMC) performance. Figure 36 shows an example of a good PCB layout for the ADP2386. For optimum layout, refer to the following guidelines:

- Use separate analog ground planes and power ground planes. Connect the ground reference of sensitive analog circuitry, such as output voltage divider components, to analog ground. In addition, connect the ground reference of power components, such as input and output capacitors, to power ground. Connect both ground planes to the exposed GND pad of the ADP2386.

- Place the input capacitor, inductor, and output capacitor as close as possible to the IC, and use short traces.

- Ensure that the high current loop traces are as short and as wide as possible. Make the high current path from the input capacitor through the inductor, the output capacitor, and the power ground plane back to the input capacitor as short as possible. To accomplish this, ensure that the input and output capacitors share a common power ground plane.

In addition, ensure that the high current path from the power ground plane through the inductor and output capacitor back to the power ground plane is as short as possible by tying the PGND pins of the ADP2386 to the PGND plane as close as possible to the input and output capacitors.

- Connect the exposed GND pad of the ADP2386 to a large, external copper ground plane to maximize its power dissipation capability and minimize junction temperature. In addition, connect the exposed SW pad to the SW pins of the ADP2386, using short, wide traces; or connect the exposed SW pad to a large copper plane of the switching node for high current flow.

- Place the feedback resistor divider network as close as possible to the FB pin to prevent noise pickup. Minimize the length of the trace that connects the top of the feedback resistor divider to the output while keeping the trace away from the high current traces and the switching node to avoid noise pickup. To further reduce noise pickup, place an analog ground plane on either side of the FB trace and ensure that the trace is as short as possible to reduce the parasitic capacitance pickup.

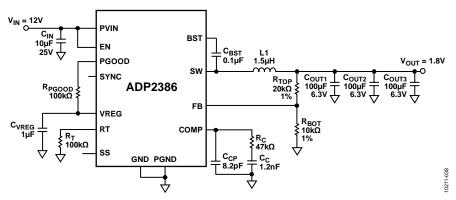

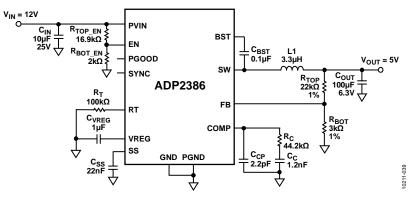

# **TYPICAL APPLICATIONS CIRCUITS**

Figure 37. Typical Applications Circuit,  $V_{IN} = 12 V$ ,  $V_{OUT} = 1.2 V$ ,  $I_{OUT} = 6 A$ ,  $f_{SW} = 500 \text{ kHz}$

Figure 38. Typical Applications Circuit Using Internal Soft Start, V<sub>IN</sub> = 12 V, V<sub>OUT</sub> = 1.8 V, I<sub>OUT</sub> = 6 A, f<sub>SW</sub> = 600 kHz

Figure 39. Programming Input Voltage UVLO Rising Threshold at 11 V, Falling Threshold at 10 V, VIN = 12 V, VOUT = 5 V, IOUT = 6 A, f<sub>SW</sub> = 600 kHz

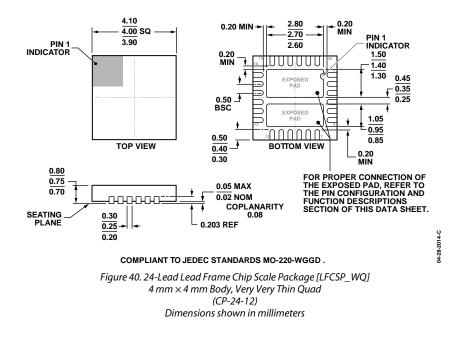

# **OUTLINE DIMENSIONS**

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                                                | Package Option |

|--------------------|-------------------|--------------------------------------------------------------------|----------------|

| ADP2386ACPZN-R7    | -40°C to +125°C   | 24-Lead Lead Frame Chip Scale Package [LFCSP_WQ], 7" Tape and Reel | CP-24-12       |

| ADP2386-EVALZ      |                   | Evaluation Board                                                   |                |

| ADP2386BB-EVALZ    |                   | Inverting Buck-Boost Evaluation Board                              |                |

<sup>1</sup> Z = RoHS Compliant Part.

©2012-2015 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D10211-0-10/15(C)

www.analog.com

Rev. C | Page 24 of 24

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Voltage Regulators category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below :

FAN53610AUC33X FAN53611AUC123X FAN48610BUC33X FAN48610BUC45X FAN48617UC50X R3 430464BB KE177614 FAN53611AUC12X MAX809TTR NCV891234MW50R2G NCP81103MNTXG NCP81203PMNTXG NCP81208MNTXG NCP81109GMNTXG SCY1751FCCT1G NCP81109JMNTXG AP3409ADNTR-G1 NCP81241MNTXG LTM8064IY LT8315EFE#TRPBF LTM4664EY#PBF LTM4668AIY#PBF NCV1077CSTBT3G XCL207A123CR-G MPM54304GMN-0002 MPM54304GMN-0004 MPM54304GMN-0003 AP62300Z6-7 MP8757GL-P MIC23356YFT-TR LD8116CGL HG2269M/TR OB2269 XD3526 U6215A U6215B U6620S LTC3412IFE LT1425IS MAX25203BATJA/VY+ MAX77874CEWM+ XC9236D08CER-G MP3416GJ-P MP5461GC-Z MPQ4415AGQB-Z MPQ4590GS-Z MAX38640BENT18+T MAX77511AEWB+ MAX20406AFOD/VY+