# Low Noise Micro PMU, 3 A Buck Regulator with 3 A LDO

Data Sheet ADP5003

#### **FEATURES**

Low noise, dc power supply system

High efficiency buck for first stage conversion

High PSRR, low noise LDO regulator to remove switching

Adaptive LDO regulator headroom control option for optimal efficiency and PSRR across full load range

3 A, low noise, buck regulator

Wide input voltage range: 4.2 V to 15 V

Programmable output voltage range: 0.6 V to 5.0 V

0.3 MHz to 2.5 MHz internal oscillator

0.3 MHz to 2.5 MHz SYNC frequency range

3 A, low noise, NFET LDO regulator (active filter)

Wide input voltage range: 0.65 V to 5 V

Programmable output voltage range: 0.6 V to 3.3 V

Differential point of load remote sensing

3 µV rms output noise (independent of output voltage)

PSRR > 50 dB (to 100 kHz) with 400 mV headroom at 3 A

Ultrafast transient response

Power-good output

Precision enable inputs for both the buck regulator and LDO  $-40^{\circ}$ C to  $+125^{\circ}$ C operating junction temperature range 32-lead, 5 mm  $\times$  5 mm, LFCSP

#### **APPLICATIONS**

Low noise power for high speed analog-to-digital converter (ADC) and digital-to-analog converter (DAC) designs Powering RF transceivers and clocking ICs

#### **GENERAL DESCRIPTION**

The ADP5003 integrates a high voltage buck regulator and an ultralow noise low dropout (LDO) regulator in a small, 5 mm  $\times$  5 mm, 32-lead LFCSP package to provide highly efficient and quiet regulated supplies.

The buck regulator is optimized to operate at high output currents up to 3 A. The LDO is capable of a maximum output current of 3 A and operates efficiently with low headroom voltage while maintaining high power supply rejection.

The ADP5003 can operate in one of two modes. Adaptive mode allows the LDO to operate with an optimized headroom by adjusting the buck output voltage internally in response to the LDO load current. Alternatively, the ADP5003 can operate in independent mode, where both regulators operate separately from each other, and where the output voltages are

#### Rev. A Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

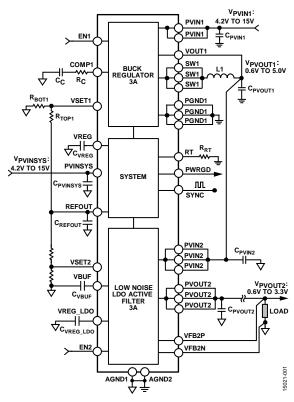

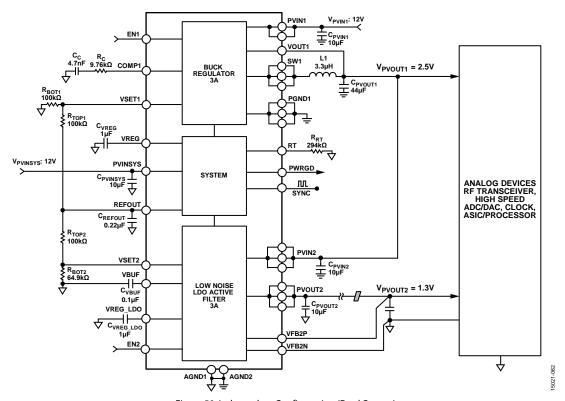

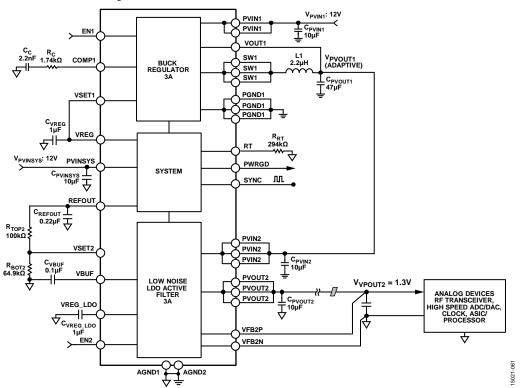

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

programmed using resistor dividers.

The LDO regulator output can be accurately controlled at the point of load (POL) using remote sensing that compensates for the printed circuit board (PCB) trace impedance while delivering high output currents.

Each regulator is activated via a dedicated precision enable input. The buck switching frequency can be synchronized to an external signal, or programmed with an external resistor.

Safety features in the ADP5003 include thermal shutdown (TSD), input undervoltage lockout (UVLO) and independent current limits for each regulator. The ADP5003 is rated for a  $-40^{\circ}$ C to  $+125^{\circ}$ C operating junction temperature range.

## **TABLE OF CONTENTS**

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| Functional Block Diagram                    | 1  |

| General Description                         | 1  |

| Revision History                            | 3  |

| Specifications                              | 4  |

| Buck Regulator Specifications               | 5  |

| LDO Specifications                          | 6  |

| Adaptive Headroom Controller Specifications | 6  |

| Absolute Maximum Ratings                    | 7  |

| Thermal Resistance                          | 7  |

| ESD Caution                                 | 7  |

| Pin Configuration and Function Descriptions | 8  |

| Typical Performance Characteristics         | 9  |

| Theory of Operation                         | 15 |

| Power Management Unit                       | 15 |

| Buck Regulator                              | 15 |

| LDO Regulator                               | 17 |

| Power-Good                                  | 18 |

| Output Voltage of the Buck Regulator        | 18 |

| Output Voltage of the LDO Regulator         | 18 |

| Voltage Conversion Limitations              | 18 |

| Component Selection                         | 19 |

| Compensation Components Design              | 21 |

| Junction Temperature                        | 21 |

|                                             |    |

| Setting the Switching Frequency for the Buck Regulator 22                                      |

|------------------------------------------------------------------------------------------------|

| Setting the Output Voltage for the Buck Regulator                                              |

| Selecting the Inductor for the Buck Regulator                                                  |

| Selecting the Output Capacitor for the Buck Regulator 22                                       |

| Designing the Compensation Network for the Buck Regulator                                      |

| 23                                                                                             |

| Selecting the Input Capacitor for the Buck Regulator                                           |

| Adaptive Headroom Control Design Example24                                                     |

| Setting the Switching Frequency for the Buck Regulator Using Adaptive Headroom Control24       |

| Setting the Output Voltage for the LDO Regulator Using Adaptive Headroom Control24             |

| Selecting the Inductor for the Buck Regulator Using Adaptive<br>Headroom Control24             |

| Selecting the Output Capacitors for the Buck Regulator Using Adaptive Headroom Control24       |

| Designing the Compensation Network for the Buck<br>Regulator Using Adaptive Headroom Control25 |

| Selecting the Input Capacitor for the Buck Regulator Using Adaptive Headroom Control25         |

| Recommended External Components for the Buck Regulator                                         |

|                                                                                                |

| Buck Configurations                                                                            |

| Independent28                                                                                  |

| Adaptive Headroom29                                                                            |

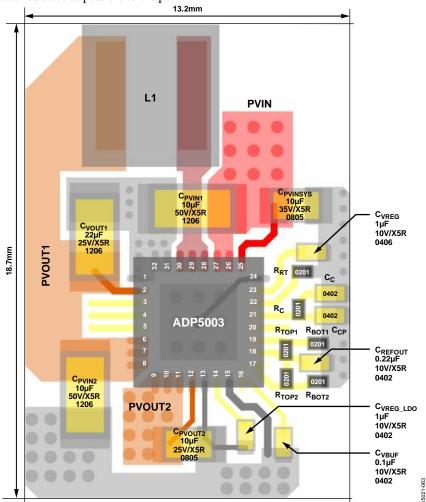

| Layout Considerations                                                                          |

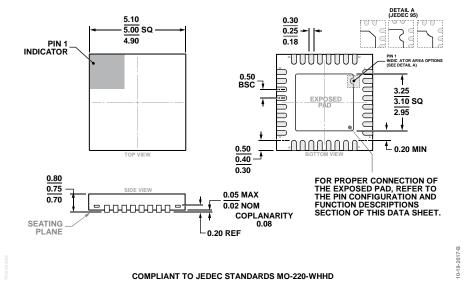

| Outline Dimensions                                                                             |

| Ordering Guide                                                                                 |

#### **REVISION HISTORY**

| 3/2019—Rev. 0 to Rev. A                                   |

|-----------------------------------------------------------|

| Changes to Applications Section, General Description, and |

| Figure 1                                                  |

| Changes to Table 14                                       |

| Changes to Table 25                                       |

| Changes to Table 36                                       |

| Changes to Table 57                                       |

| Changes to Table 78                                       |

| Updated Typical Performance Characteristics Section;      |

| Renumbered Sequentially9                                  |

| Changes to Adaptive Headroom Control Section, Active Pull |

| Down Section, and Power-Good Section15                    |

| Changes to Oscillator Frequency Control Section16         |

| Add Figure 38 and Figure 3916                             |

| Changes to Current-Limit and Short-Circuit Protection     |

| Section and Current Limit Section17                       |

| Changes to Output Voltage of the Buck Regulator Section,  |

| Figure 44, Output Voltage of the LDO Regulator Section,   |

| Figure 45, and Voltage Conversion Limitations Section18   |

| Changes to Input Capacitor Section, Inductor Section, and |

| Table 9                                                   |

|                                                           |

| Changes to Compensation Components Design Section,            |

|---------------------------------------------------------------|

| Figure 46 and Junction Temperature Section21                  |

| Changes to Table 10, Setting the Switching Frequency for the  |

| Buck Regulator Section, Setting the Output Voltage for the    |

| Buck Regulator Section, Selecting the Inductor for the Buck   |

| Regulator Section, and Selecting the Output Capacitor for the |

| Buck Regulator Section                                        |

| Deleted Figure 44; Renumbered Sequentially22                  |

| Changes Figure 4723                                           |

| Changes to Table 11, Setting the Output Voltage for the LDO   |

| Regulator Using Adaptive Headroom Control Section, and        |

| Selecting the Inductor for the Buck Regulator Using Adaptive  |

| Headroom Control Section                                      |

| Changes Figure 4825                                           |

| Changes to Recommended External Components for the Buck       |

| Regulator Section and Table 12 Title26                        |

| Changes to Figure 49 Caption and Figure 5028                  |

| Changes to Adaptive Headroom Section and Figure 5229          |

| Changes to Layout Considerations Section and Figure 5330      |

| Updated Outline Dimensions                                    |

11/2017—Revision 0: Initial Version

## **SPECIFICATIONS**

$V_{PVIN1} = V_{PVINSYS} = 4.2 \text{ V}$  to 15 V,  $V_{PVIN2} = 0.65 \text{ V}$  to 5 V,  $T_J = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  for minimum/maximum specifications, and  $T_A = 25^{\circ}\text{C}$  for typical specifications, unless otherwise noted.

Table 1.

| Parameter                           | Symbol                                    | Min   | Тур  | Max   | Unit | Test Conditions/Comments                               |

|-------------------------------------|-------------------------------------------|-------|------|-------|------|--------------------------------------------------------|

| INPUT VOLTAGE RANGE                 | V <sub>PVIN1</sub> , V <sub>PVINSYS</sub> | 4.2   |      | 15    | ٧    |                                                        |

|                                     | V <sub>PVIN2</sub>                        | 0.65  |      | 5     | ٧    |                                                        |

| THERMAL SHUTDOWN                    |                                           |       |      |       |      |                                                        |

| Threshold                           | T <sub>SD</sub>                           |       | 155  |       | °C   | T <sub>J</sub> rising                                  |

| Hysteresis                          | T <sub>SD-HYS</sub>                       |       | 15   |       | °C   |                                                        |

| SYNC INPUT                          |                                           |       |      |       |      |                                                        |

| Input Logic                         |                                           |       |      |       |      |                                                        |

| High                                | V <sub>IH</sub>                           | 1.1   |      |       | ٧    |                                                        |

| Low                                 | V <sub>IL</sub>                           |       |      | 0.4   | ٧    |                                                        |

| Input Leakage Current               | V <sub>I-LEAKAGE</sub>                    |       |      | 1     | μΑ   |                                                        |

| ADAPTIVE MODE INPUT (VSET1)         |                                           |       |      |       |      |                                                        |

| Input Rising Threshold              | V <sub>ADPR</sub>                         |       | 2.5  |       | ٧    |                                                        |

| Input Hysteresis                    | V <sub>ADPH</sub>                         |       | 16   |       | mV   |                                                        |

| PRECISION ENABLING                  |                                           |       |      |       |      |                                                        |

| High Level Threshold                | V <sub>TH_H</sub>                         | 1.125 | 1.15 | 1.175 | ٧    |                                                        |

| Low Level Threshold                 | $V_{TH\_L}$                               | 1.025 | 1.05 | 1.075 | ٧    |                                                        |

| Shutdown Mode                       | $V_{TH\_S}$                               |       |      | 0.4   | ٧    |                                                        |

| EN1, EN2 Pull-Down Resistance       | R <sub>ENPD</sub>                         |       | 1.5  |       | МΩ   |                                                        |

| INPUT CURRENT                       |                                           |       |      |       |      |                                                        |

| Both Channels Enabled               | I <sub>STBY-NOSW</sub>                    |       | 0.5  | 1     | mΑ   | No load, not switching                                 |

| Both Channels Disabled              | I <sub>SHUTDOWN</sub>                     |       | 5    | 10    | μΑ   | $T_{J} = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |

| REFOUT CHARACTERISTICS              |                                           |       |      |       |      |                                                        |

| Output Voltage                      | V <sub>REFOUT</sub>                       |       | 2.0  |       | ٧    |                                                        |

| Accuracy                            |                                           | -0.5  |      | +0.5  | %    |                                                        |

| VREG AND VREG_LDO CHARACTERISTICS   |                                           |       |      |       |      |                                                        |

| Output Voltage                      | V <sub>REG</sub> , V <sub>REG_LDO</sub>   |       | 5    |       | ٧    |                                                        |

| Accuracy                            |                                           | -2    |      | +2    | %    |                                                        |

| Current Limit <sup>1</sup>          |                                           | 10    |      |       | mΑ   |                                                        |

| POWER-GOOD PIN (PWRGD)              |                                           |       |      |       |      |                                                        |

| Power Good Threshold                | PWRGD <sub>F</sub>                        | 80    | 85   | 90    | %    | Applies to VOUT1 and VFB2P to VFB2N                    |

| Hysteresis                          | PWRGD <sub>FH</sub>                       |       | 2.5  |       | %    |                                                        |

| Output Voltage Level                | V <sub>OL</sub>                           |       | 25   | 50    | mV   | PWRGD pin sink current = 1 mA                          |

| Deglitch Time                       | <b>t</b> PWRGDD                           |       | 60   |       | μs   |                                                        |

| PVINSYS UNDERVOLTAGE LOCKOUT (UVLO) |                                           |       |      |       |      |                                                        |

| Input Voltage                       |                                           |       |      |       |      |                                                        |

| Rising                              | UVLOPVINSYSRISE                           |       |      | 4.2   | ٧    |                                                        |

| Falling                             | UVLOPVINSYSFALL                           | 3.9   |      |       | ٧    |                                                        |

$<sup>^{1}</sup>$  Do not use VREG and VREG\_LDO to supply the external loads. This current limit protects against a pin short to ground.

#### **BUCK REGULATOR SPECIFICATIONS**

$V_{PVINI} = V_{PVINSYS} = 4.2 \text{ V}$  to 15 V,  $V_{PVIN2} = 0.65 \text{ V}$  to 5 V,  $T_J = -40^{\circ}\text{C}$  to +125°C for minimum/maximum specifications, and  $T_A = 25^{\circ}\text{C}$  for typical specifications, unless otherwise noted.

Table 2.

| Parameter                                      | Symbol                                            | Min  | Тур   | Max  | Unit | Test Conditions/Comments                                                                                 |

|------------------------------------------------|---------------------------------------------------|------|-------|------|------|----------------------------------------------------------------------------------------------------------|

| OUTPUT CHARACTERISTICS                         | ·                                                 |      |       |      |      |                                                                                                          |

| Programmable Output Voltage Range <sup>1</sup> | V <sub>PVOUT1</sub>                               | 0.6  |       | 5.0  | ٧    |                                                                                                          |

| Buck Regulator Gain                            | Ависк                                             |      | 2.5   |      |      | V <sub>PVOUT1</sub> /V <sub>VSET1</sub>                                                                  |

| Error Amplifier Transconductance               | g <sub>m1</sub>                                   | 509  | 600   | 661  | μS   |                                                                                                          |

| Buck Output Voltage Accuracy <sup>2</sup>      |                                                   | -1   |       | +1   | %    | VOUT1 load current (I <sub>LOAD1</sub> ) = 10 mA                                                         |

| Regulation                                     |                                                   |      |       |      |      |                                                                                                          |

| Line                                           | $(\Delta V_{PVOUT1}/V_{PVOUT1})/\Delta V_{PVIN1}$ |      | 0.004 |      | %/V  | $I_{LOAD1} = 10 \text{ mA}$                                                                              |

| Load                                           | $(\Delta V_{PVOUT1}/V_{PVOUT1})/\Delta I_{LOAD1}$ |      | 0.04  |      | %/A  | $0 \text{ mA} \le I_{LOAD1} \le 3 \text{ A}, V_{PVIN1} = 12 \text{ V}$                                   |

| Total Output Voltage Accuracy                  |                                                   |      | ±1.5  |      | %    | $4.2 \text{ V} \le \text{V}_{PVIN1} \le 15 \text{ V}, 1 \text{ mA} \le \text{I}_{LOAD1} \le 3 \text{ A}$ |

| OPERATING SUPPLY CURRENT                       | l <sub>IN</sub>                                   |      | 3.8   |      | mA   | I <sub>LOAD1</sub> = 0 mA, LDO disabled, buck switching                                                  |

| SW1 CHARACTERISTICS                            |                                                   |      |       |      |      |                                                                                                          |

| SW1 On Resistance                              | R <sub>PFET</sub>                                 |      | 130   | 200  | mΩ   | $V_{PVIN1} = 15 \text{ V (PVIN1 to SW1)}$                                                                |

|                                                | R <sub>NFET</sub>                                 |      | 60    | 100  | mΩ   | $V_{PVIN1} = 15 \text{ V (SW1 to PGND1)}$                                                                |

| Current Limit Threshold                        | Інміт1                                            | 3.5  |       |      | А    | Negative channel field effect<br>transistor (NFET) switch valley<br>current limit                        |

|                                                |                                                   |      |       | -1   | Α    | Negative current limit                                                                                   |

| Slew Rate                                      | SLEW <sub>SW1</sub>                               |      | 1.6   |      | V/ns | V <sub>PVIN1</sub> = 15 V, I <sub>LOAD1</sub> = 1 A                                                      |

| Minimum On Time <sup>3</sup>                   | t <sub>MIN_ON</sub>                               |      | 35    |      | ns   |                                                                                                          |

| Minimum Off Time                               | t <sub>MIN_OFF</sub>                              |      | 100   | 128  | ns   |                                                                                                          |

| BUCK REGULATOR ACTIVE PULL DOWN                | R <sub>PDWN-B</sub>                               |      | 90    |      | Ω    | Channel disabled                                                                                         |

| BUCK REGULATOR SOFT START (SS)                 | t <sub>SSBUCK</sub>                               |      | 2     |      | ms   |                                                                                                          |

| HICCUPTIME                                     | thiccup                                           |      | 33    |      | ms   |                                                                                                          |

| VSETx ADJUSTABLE INPUT BIAS CURRENT            | I <sub>VSET1</sub> , I <sub>VSET2</sub>           |      | 10    | 150  | nA   |                                                                                                          |

| OSCILLATOR                                     |                                                   |      |       |      |      |                                                                                                          |

| Internal Switching Frequency 1                 | f <sub>SW1</sub>                                  | 2.25 | 2.5   | 2.75 | MHz  | $R_{RT} \le 71.2 \text{ k}\Omega$                                                                        |

| Internal Switching Frequency 2                 | f <sub>SW2</sub>                                  | 0.26 | 0.3   | 0.34 | MHz  | $R_{RT} = 600 \text{ k}\Omega$                                                                           |

| SYNC                                           |                                                   |      | _     |      |      |                                                                                                          |

| Frequency Range                                | f <sub>SYNC</sub>                                 | 0.3  |       | 2.5  | MHz  |                                                                                                          |

| Minimum Pulse Width                            |                                                   |      |       |      |      |                                                                                                          |

| Positive                                       |                                                   | 20   |       |      | ns   |                                                                                                          |

| Negative                                       |                                                   | 10   |       |      | ns   |                                                                                                          |

$<sup>^{1}</sup>$  The switching frequency, minimum on time, and minimum off time may limit the output voltage range.

<sup>&</sup>lt;sup>2</sup> The buck output voltage accuracy is relative to the nominal output voltage and accounts for reference voltage, gain, and offset error.

<sup>&</sup>lt;sup>3</sup> The minimum on time indicates the minimum high-side turn on time to ensure fixed frequency switching.

#### **LDO SPECIFICATIONS**

$V_{PVIN1} = V_{PVINSYS} = 4.2 \text{ V}$  to 15 V,  $V_{PVIN2} = 0.65 \text{ V}$  to 5 V, LDO headroom voltage ( $V_{HR}$ ) = 300 mV,  $T_J = -40^{\circ}\text{C}$  to +125°C for minimum/maximum specifications, and  $T_A = 25^{\circ}\text{C}$  for typical specifications, unless otherwise noted.

Table 3.

| Parameter                                      | Symbol                                      | Min | Тур   | Max | Unit   | Test Conditions/Comments                                                                         |

|------------------------------------------------|---------------------------------------------|-----|-------|-----|--------|--------------------------------------------------------------------------------------------------|

| OUTPUT CHARACTERISTICS                         |                                             |     |       |     |        |                                                                                                  |

| Programmable Output Voltage Range <sup>1</sup> | V <sub>LDO</sub>                            | 0.6 |       | 3.3 | V      | V <sub>VFB2P-VFB2N</sub>                                                                         |

| LDO Gain                                       | A <sub>LDO</sub>                            |     | 1.65  |     |        | V <sub>LDO</sub> /V <sub>VSET2</sub>                                                             |

| Output Voltage Accuracy <sup>2</sup>           |                                             | -1  |       | +1  | %      | VOUT2 load current (I <sub>LOAD2</sub> ) = 150 mA                                                |

| Regulation                                     |                                             |     |       |     |        |                                                                                                  |

| Line                                           | $(\Delta V_{LDO}/V_{LDO})/\Delta V_{PVIN2}$ |     | 0.007 |     | %/V    | $(V_{PVOUT2} + V_{HR}) \le V_{PVIN2} \le 6 V$ , $I_{LOAD2} = 100 \text{ mA}$                     |

| Load                                           | $(\Delta V_{LDO}/V_{LDO})/\Delta I_{LOAD2}$ |     | 0.08  |     | %/A    | 10 mA ≤ I <sub>LOAD2</sub> ≤ 3 A                                                                 |

| Total Output Voltage Accuracy                  |                                             |     | ±1.5  |     | %      | $(V_{PVOUT2} + V_{HR}) \le V_{PVIN2} \le 6 V$ ,<br>$10 \text{ mA} \le I_{LOAD2} \le 3 \text{ A}$ |

| OPERATING SUPPLY CURRENT                       | I <sub>GND</sub>                            |     | 1.8   | 2.5 | mA     | $I_{LOAD2} = 0 \mu A$                                                                            |

|                                                |                                             |     | 2.3   |     | mA     | $I_{LOAD2} = 3 A$                                                                                |

| MINIMUM VOLTAGE REQUIREMENTS                   |                                             |     |       |     |        | $I_{LOAD2} = 3 A$                                                                                |

| PVINSYS to PVOUT2 <sup>3</sup>                 | V <sub>PVINSYS-PVOUT2</sub>                 |     | 1.5   |     | ٧      |                                                                                                  |

| VREG_LDO to PVOUT2⁴                            | Vvreg_ldo-pvout2                            |     | 1.35  |     | V      | Required to drive NFET                                                                           |

| Dropout <sup>5</sup>                           | V <sub>DROPOUT</sub>                        |     | 100   |     | mV     |                                                                                                  |

| CURRENT-LIMIT THRESHOLD <sup>6</sup>           | I <sub>LIMIT2</sub>                         | 3.1 |       | 4.5 | Α      |                                                                                                  |

| LDO SOFT START (SS) TIME                       | t <sub>SSLDO</sub>                          |     | 400   |     | μs     |                                                                                                  |

| LDO ACTIVE PULL-DOWN                           | R <sub>PDWNLDO</sub>                        |     | 300   |     | Ω      | Channel disabled                                                                                 |

| OUTPUT NOISE                                   | N <sub>PVOUT2</sub>                         |     | 3     |     | μV rms | 10 Hz to 100 kHz, ILOAD2 = 1 A                                                                   |

| LDO POWER SUPPLY REJECTION RATIO               | PSRR <sub>LDO</sub>                         |     |       |     |        | $V_{PVIN2} = V_{PVOUT2} + 0.3 V$ , $I_{LOAD2} = 1A$                                              |

| $V_{PVOUT2} = 1.3 V$                           |                                             |     | 87    |     | dB     | 1 kHz                                                                                            |

|                                                |                                             |     | 82    |     | dB     | 10 kHz                                                                                           |

|                                                |                                             |     | 61    |     | dB     | 100 kHz                                                                                          |

|                                                |                                             |     | 38    |     | dB     | 1000 kHz                                                                                         |

| $V_{PVOUT2} = 3.3 V$                           |                                             |     | 89    |     | dB     | 1 kHz                                                                                            |

|                                                |                                             |     | 83    |     | dB     | 10 kHz                                                                                           |

|                                                |                                             |     | 61    |     | dB     | 100 kHz                                                                                          |

|                                                |                                             |     | 37    |     | dB     | 1000 kHz                                                                                         |

$<sup>^{\</sup>rm 1}$  Limited by minimum PVINSYS to PVOUT2 and VREG\_LDO to PVOUT2 voltage.

#### **ADAPTIVE HEADROOM CONTROLLER SPECIFICATIONS**

$V_{PVINI} = V_{PVINSYS} = 4.2 \text{ V}$  to 15 V,  $V_{PVIN2} = 0.65 \text{ V}$  to 5 V,  $T_J = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  for minimum/maximum specifications, and  $T_A = 25^{\circ}\text{C}$  for typical specifications, unless otherwise noted.

Table 4.

| Parameter                         | Symbol          | Min | Тур | Max | Unit | Test Conditions/Comments   |

|-----------------------------------|-----------------|-----|-----|-----|------|----------------------------|

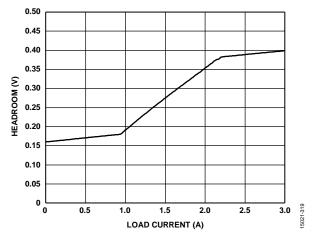

| HEADROOM VOLTAGE (PVIN2 – PVOUT2) | V <sub>HR</sub> |     | 160 |     | mV   | I <sub>LOAD2</sub> = 1 mA  |

|                                   |                 |     | 280 |     | mV   | I <sub>LOAD2</sub> = 1.5 A |

|                                   |                 |     | 400 |     | mV   | $I_{LOAD2} = 3 A$          |

<sup>&</sup>lt;sup>2</sup> The LDO output voltage accuracy is relative to the nominal output voltage and accounts for reference voltage, gain, and offset error.

<sup>&</sup>lt;sup>3</sup> PVINSYS must be higher than PVOUT2 by at least V<sub>PVINSYS-PVOUT2</sub> to keep the LDO regulating.

<sup>&</sup>lt;sup>4</sup> PVOUT2 must be lower than VREG\_LDO by at least V<sub>VREG\_LDO-PVOUT2</sub> to keep the LDO regulating.

<sup>&</sup>lt;sup>5</sup> The dropout voltage is the input to output voltage differential when the input voltage is set to the nominal output voltage.

<sup>&</sup>lt;sup>6</sup> The current-limit threshold is the current at which the output voltage drops to 90% of the specified typical value. For example, the current limit for a 1.0 V output voltage is the current that causes the output voltage to drop to 90% of 1.0 V or 0.9 V.

### **ABSOLUTE MAXIMUM RATINGS**

Table 5.

| Parameter Rat                          | ing                       |

|----------------------------------------|---------------------------|

| PVIN1/PVINSYS to AGND1/AGND2 -0.3      | 3 V to +16 V              |

| PVIN2 to AGND1/AGND2 -0.3              | 3 V to +6.0 V             |

| AGND1 to AGND2 -0.3                    | 3 V to +0.3 V             |

| PGND1 to AGND1/AGND2 -0.3              | 3 V to +0.3 V             |

| PVOUT2 to AGND1/AGND2 -0.3             | 3 V to the lower of       |

| (PVI                                   | IN2 + 0.3 V) or +6.0 V    |

| VFB2N to AGND1/AGND2/PGND1 -0.3        | 3 V to +0.3 V             |

| VOUT1, VFB2P, EN1, EN2, SYNC, RT, -0.3 | 3 V to the lower of (VREG |

| REFOUT, VBUF, VSET1, VSET2, + 0.       | .3 V) or +6.0 V           |

| COMP1 to AGND1/AGND2                   |                           |

| SW1 to PGND1 -0.3                      | 3 V to (PVIN1 + 0.3 V)    |

| VREG, VREG_LDO to -0.3                 | 3 V to the lower of       |

| AGND1/AGND2/PGND1/VFB2N (PVI           | INSYS + 0.3 V) or +6.0 V  |

| VREG to VREG_LDO -0.3                  | 3 V to +0.3 V             |

| Storage Temperature Range –65          | 5°C to +150°C             |

| Operating Junction Temperature -40     | 0°C to +125°C             |

| Range                                  |                           |

| Soldering Conditions JED               | EC J-STD-020              |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to PCB design and operating environment. Careful attention to PCB thermal design is required.

**Table 6. Thermal Resistance**

| Package Type | $\theta_{JA}^{1}$ | $\theta_{JC}^{1}$ | Unit |

|--------------|-------------------|-------------------|------|

| CP-32-7      | 46.91             | 20.95             | °C/W |

$<sup>^1</sup>$   $\theta_{JA}$  and  $\theta_{JC}$  are based on a 4-layer PCB (two signal and two power planes) with nine thermal vias connecting the exposed pad to the ground plane as recommended in the Layout Considerations section.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

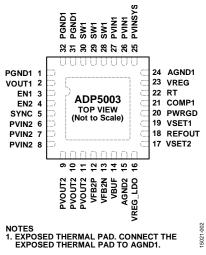

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 7. Pin Function Descriptions**

| Pin No.   | Mnemonic | Description                                                                                                                                                                       |

|-----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 31, 32 | PGND1    | Buck Regulator Dedicated Power Ground.                                                                                                                                            |

| 2         | VOUT1    | Buck Regulator Feedback Input. Connect a short sense trace to the buck output capacitor.                                                                                          |

| 3         | EN1      | Buck Regulator Precision Enable Pin. Drive the EN1 pin high to turn on the buck regulator, and drive the EN1 pin low to turn off the buck regulator.                              |

| 4         | EN2      | LDO Precision Enable Pin. Drive the EN2 pin high to turn on the LDO regulator, and drive the EN2 pin low to turn off the LDO regulator.                                           |

| 5         | SYNC     | Synchronization Input. To synchronize the switching frequency of the device to an external clock, connect this pin to an external clock with a frequency from 300 kHz to 2.5 MHz. |

| 6 to 8    | PVIN2    | LDO Regulator Power Input. Connect a 10 µF ceramic capacitor between this pin and AGND2.                                                                                          |

| 9 to 11   | PVOUT2   | LDO Regulator Power Output. Connect a 10 µF ceramic capacitor between this pin and AGND2.                                                                                         |

| 12        | VFB2P    | LDO Regulator Positive Sense Feedback Input. Connect a sense trace to the LDO output at the load. Route this pin alongside the VFB2N pin on the PCB.                              |

| 13        | VFB2N    | LDO Regulator Ground Sense Feedback Input. Connect a sense trace to ground at the load. Route this pin alongside the VFB2P pin on the PCB.                                        |

| 14        | VBUF     | Output of the LDO Reference Buffer. Connect a 0.1 µF ceramic capacitor between this pin and VFB2N.                                                                                |

| 15        | AGND2    | LDO Dedicated Analog Ground.                                                                                                                                                      |

| 16        | VREG_LDO | Internal Regulator Output for the LDO. Connect a 1 µF ceramic decoupling capacitor between this pin and AGND2. Do not use this pin to power external devices.                     |

| 17        | VSET2    | LDO Regulator Output Voltage Configuration Input.                                                                                                                                 |

| 18        | REFOUT   | Internal Reference Output Required for Driving the External Resistor Dividers for VSET1 and VSET2. Connect a 0.22 µF ceramic capacitor between this pin and AGND2.                |

| 19        | VSET1    | Buck Regulator Output Voltage Configuration Input. Connect this pin to VREG to enable adaptive headroom control.                                                                  |

| 20        | PWRGD    | Power-Good Digital Output (Open-Drain NFET Pull-Down Driver).                                                                                                                     |

| 21        | COMP1    | Buck Regulator External Compensation Pin.                                                                                                                                         |

| 22        | RT       | Resistor Adjustable Frequency Programming Input.                                                                                                                                  |

| 23        | VREG     | Internal Regulator Output. Connect a 1 $\mu$ F ceramic decoupling capacitor between this pin and AGND1. Do not use this pin to power external devices.                            |

| 24        | AGND1    | Analog Ground.                                                                                                                                                                    |

| 25        | PVINSYS  | System Power Supply for the ADP5003. Connect a 10 µF ceramic capacitor between this pin and AGND1.                                                                                |

| 26, 27    | PVIN1    | Buck Regulator Power Input. Connect a 10 μF ceramic capacitor between this pin and PGND1.                                                                                         |

| 28 to 30  | SW1      | Buck Regulator Switching Output.                                                                                                                                                  |

|           | EPAD     | Exposed Thermal Pad. Connect the exposed thermal pad to AGND1.                                                                                                                    |

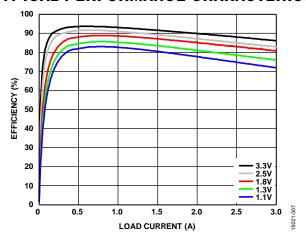

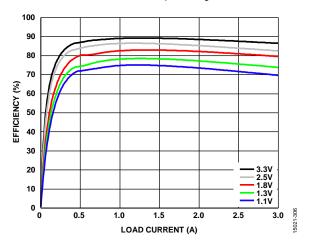

### TYPICAL PERFORMANCE CHARACTERISTICS

Figure 3. Buck Efficiency vs. Load Current,  $V_{PVIN1} = 5 V$ ,  $f_{SW} = 600 \text{ kHz}$  at Various Buck Output Voltages

Figure 4. Buck Efficiency vs. Load Current,  $V_{PVIN1} = 12 V$ ,  $f_{SW} = 600 \text{ kHz}$  at Various Buck Output Voltages

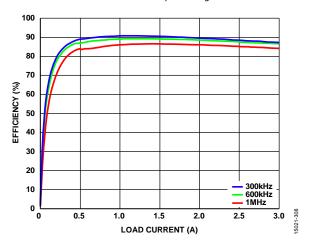

Figure 5. Buck Efficiency vs. Load Current,  $V_{PVIN1} = 12 V$ ,  $V_{PVOUT1} = 3.3 V$  at Various Buck Switching Frequencies

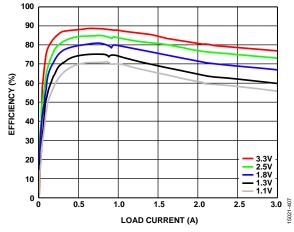

Figure 6. Adaptive Mode Efficiency vs. Load Current,  $V_{PVINI} = 5 V$ ,  $f_{SW} = 600 \text{ kHz}$  at Various LDO Output Voltages

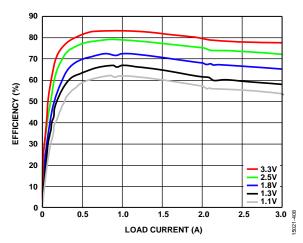

Figure 7. Adaptive Mode Efficiency vs. Load Current,  $V_{PVINI} = 12 V$ ,  $f_{SW} = 600 \text{ kHz}$  at Various LDO Output Voltages

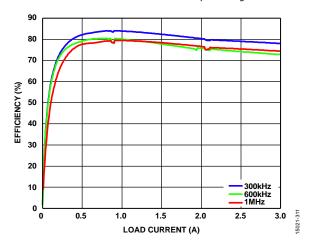

Figure 8. Adaptive Mode Efficiency vs. Load Current,  $V_{PVINI} = 12 V$ ,  $V_{PVOUT2} = 3.3 V$  at Various Buck Switching Frequencies

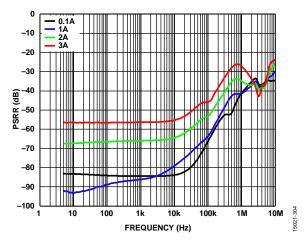

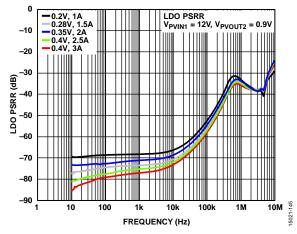

Figure 9. LDO PSRR vs. Frequency,  $V_{HR} = 0.3 V$ ,  $V_{PVOUT2} = 1.3 V$  at Various LDO Load Currents

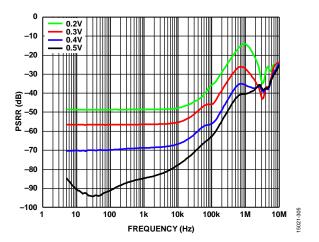

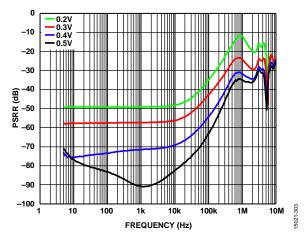

Figure 10. LDO PSRR vs. Frequency,  $V_{PVOUT2} = 1.3 V$ ,  $I_{LOAD2} = 1 A$  at Various LDO Headroom Voltages

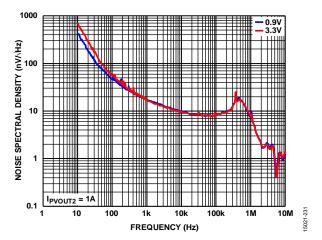

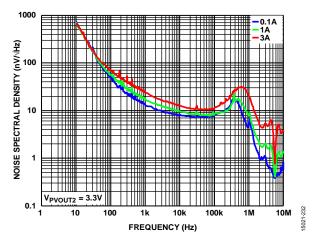

Figure 11. LDO Noise Spectral Density vs. Frequency at Various LDO Output Voltages

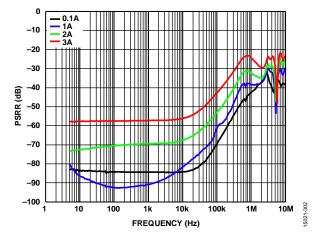

Figure 12. LDO PSRR vs. Frequency,  $V_{HR} = 0.3 \text{ V}$ ,  $V_{PVOUT2} = 3.3 \text{ V}$  at Various LDO Load Currents

Figure 13. LDO PSRR vs. Frequency,  $V_{PVOUT2} = 3.3 V$ ,  $I_{LOAD2} = 1 A$  at Various LDO Headroom Voltages

Figure 14. LDO Noise Spectral Density vs. Frequency,  $V_{PVOUT2} = 3.3 \text{ V}$  at Various LDO Load Currents

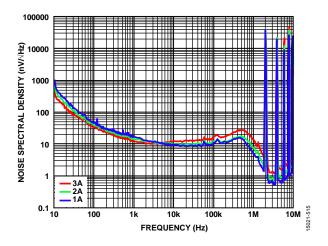

Figure 15. Adaptive Mode Noise Spectral Density vs. Frequency at various Load Currents,  $V_{PVOUT1} = V_{PVIN2} = 3.7 \text{ V}$ ,  $V_{PVOUT2} = 3.3 \text{ V}$ ,  $f_{SW} = 2 \text{ MHz}$ ,  $L = 1.5 \mu\text{H}$ ,  $R_C = 23.7 \text{ k}\Omega$ ,  $C_C = 1 \text{ nF}$ ,  $C_{CP} = 10 \text{ pF}$ ,  $C_{PVOUT1} = 22 \mu\text{F}$

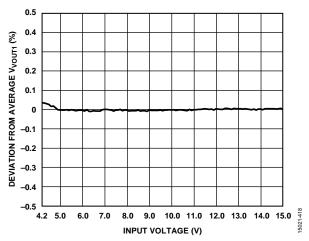

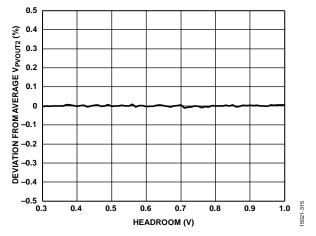

Figure 16. Buck Line Regulation,  $V_{PVOUT1} = 3.3 \text{ V}$ ,  $I_{LOAD1} = 1 \text{ A}$ ,  $f_{SW} = 600 \text{ kHz}$

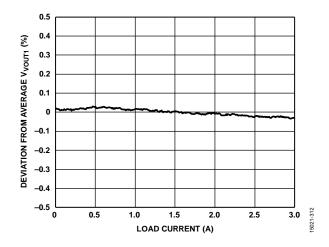

Figure 17. LDO Line Regulation,  $V_{PVOUT2} = 3.3 \text{ V}$ ,  $I_{LOAD2} = 1 \text{ A}$

Figure 18. Buck Load Regulation,  $V_{PVIN1} = 12 \text{ V}$ ,  $V_{PVOUT1} = 3.3 \text{ V}$ ,  $f_{SW} = 600 \text{ kHz}$

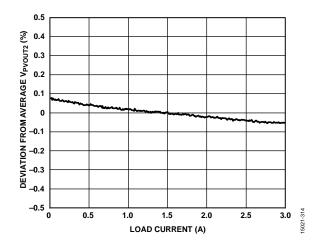

Figure 19. LDO Load Regulation,  $V_{PVOUT2} = 3.3 \text{ V}$ ,  $V_{HR} = 0.3 \text{ V}$

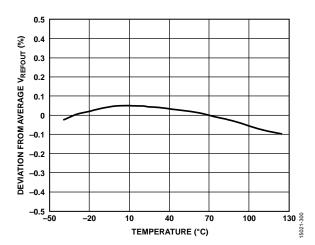

Figure 20. REFOUT Voltage (V<sub>REFOUT</sub>) vs. Temperature

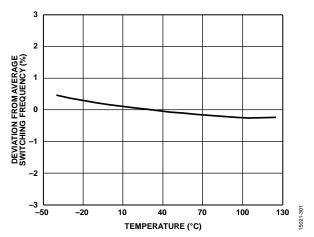

Figure 21. Switching Frequency vs. Temperature

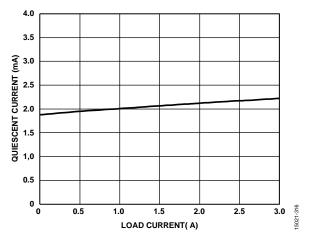

Figure 22. LDO Quiescent Current vs. Load Current

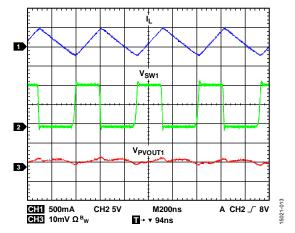

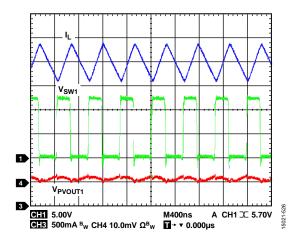

Figure 23 SW1 Waveform,  $V_{PVOUT1} = 5$  V,  $I_{LOAD1} = 100$  mA,  $f_{SW} = 2$  MHz, L = 2.2  $\mu$ H,  $R_C = 2.7$  k $\Omega$ ,  $C_C = 22$  nF,  $C_{CP} = 22$  pF,  $C_{PVOUT1} = 22$   $\mu$ F

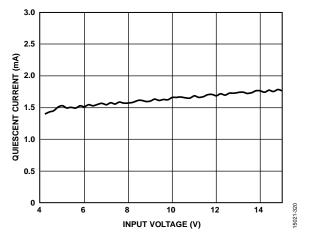

Figure 24. Buck Quiescent Current vs. Input Voltage

Figure 25. Adaptive Mode Headroom vs. Load Current

Figure 26. SW1 Waveform,  $V_{PVOUT1} = 5 V$ ,  $I_{LOAD1} = 3 A$ ,  $f_{SW} = 2 MHz$ ,  $L = 2.2 \mu H$ ,  $R_C = 2.7 \, k\Omega$ ,  $C_C = 22 \, nF$ ,  $C_{CP} = 22 \, pF$ ,  $C_{PVOUT1} = 22 \, \mu F$

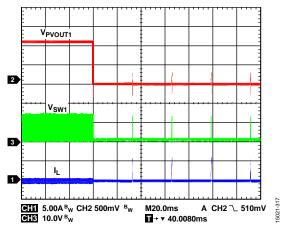

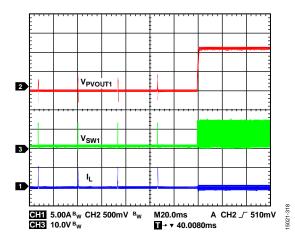

Figure 27. Entering Hiccup Mode  $(V_{SW1}$  is the Voltage of the SW1 Pin, and  $I_L$  is Inductor Current)

Figure 28. Buck Startup,  $V_{PVOUT1} = 3.3V$ ,  $I_{LOAD1} = 3 A$  ( $V_{EN1}$  is the EN1 voltage.)

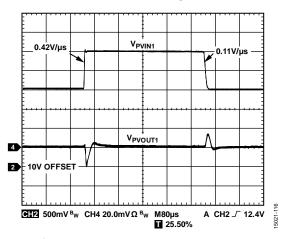

Figure 29. Buck Line Transient,  $V_{PVIN1}=12~V$  to 13 V,  $V_{PVOUT1}=1.2~V$ ,  $I_{LOAD1}=1A$ ,  $f_{SW}=0.6~MHz$ ,  $L=2.2~\mu H$ ,  $R_C=3.48~k\Omega$ ,  $C_C=2~nF$ ,  $C_{CP}=22~pF$ ,  $C_{PVOUT1}=44~\mu F$

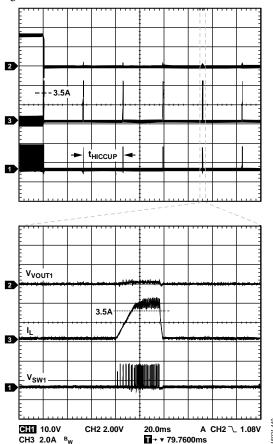

Figure 30. Exiting Hiccup Mode

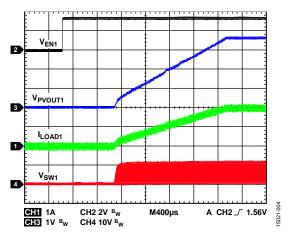

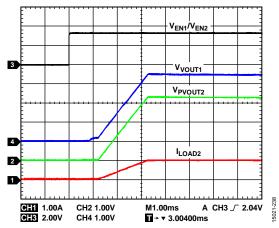

Figure 31. Adaptive Mode Startup,  $V_{PVOUT2} = 3.3 V$ ,  $I_{LOAD2} = 1 A$  ( $V_{EN2}$  is the EN2 voltage.)

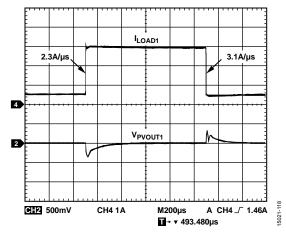

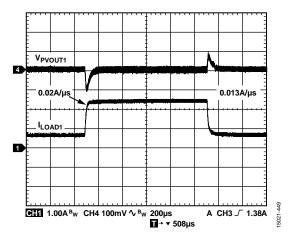

Figure 32. Buck Load Transient,  $V_{PVIN1} = 12 V$ ,  $V_{PVOUT1} = 1.2 V$ ,  $I_{LOAD1} = 0.5 A$  to 3 A,  $f_{SW} = 0.6 MHz$ ,  $L = 2.2 \mu H$ ,  $R_C = 3.48 k\Omega$ ,  $C_C = 2 nF$ ,  $C_{CP} = 22 pF$ ,  $C_{PVOUT1} = 44 \mu F$

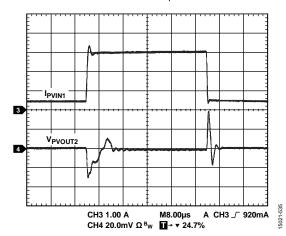

Figure 33. LDO Line Transient,  $V_{PVIN2} = 3.6 \text{ V}$  to 4.1 V,  $V_{PVOUT2} = 3.3 \text{ V}$ ,  $I_{LOAD2} = 1 \text{ A}$

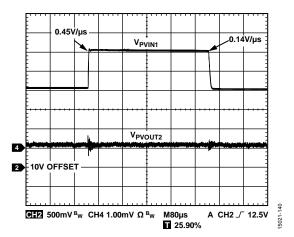

Figure 34. Adaptive Mode Line Transient,  $V_{PVIN1} = 11 \text{ V to } 13 \text{ V}$ ,  $V_{PVOUT2} = 3.3 \text{ V}$ ,  $I_{LOAD2} = 1 \text{ A}$ ,  $f_{SW} = 1.5 \text{ MHz}$ ,  $L = 2.2 \text{ }\mu\text{H}$ ,  $R_C = 3.48 \text{ }k\Omega$ ,  $C_C = 22 \text{ }n\text{F}$ ,  $C_{CP} = 22 \text{ }p\text{F}$ ,  $C_{PVOUT1} = 64 \text{ }\mu\text{F}$

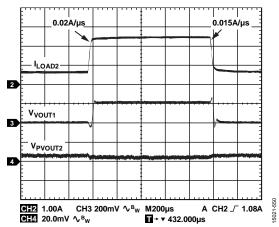

Figure 35. Adaptive Mode Load Transient,  $V_{PVIN1} = 12 \, V$ ,  $V_{PVOUT2} = 3.3 \, V$ ,  $I_{LOAD2} = 0.5 \, A$  to 3 A,  $f_{SW} = 1.5 \, MHz$ ,  $L = 2.2 \, \mu H$ ,  $R_C = 3.48 \, k\Omega$ ,  $C_C = 22 \, nF$ ,  $C_{CP} = 22 \, pF$ ,  $C_{PVOUT1} = 64 \, \mu F$

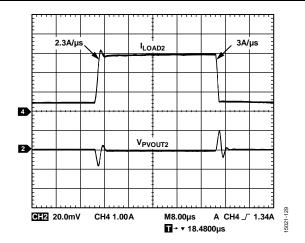

Figure 36. LDO Load Transient,  $V_{PVIN2} = 3.6 \text{ V}$ ,  $V_{PVOUT2} = 3.3 \text{ V}$ ,  $I_{LOAD2} = 0.5 \text{ A to } 3 \text{ A}$

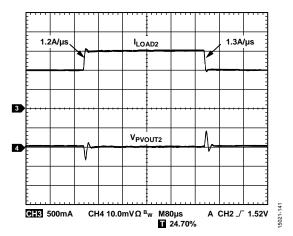

Figure 37. Adaptive Mode Load Transient,  $V_{PVIN1} = 12 V$ ,  $V_{PVOUT2} = 3.3 V$ ,  $I_{LOAD2} = 1 A$  to 1.5 A,  $f_{SW} = 1.5$  MHz,  $L = 2.2 \mu H$ ,  $R_C = 3.48 \text{ k}\Omega$ ,  $C_C = 22 \text{ nF}$ ,  $C_{CP} = 22 \text{ pF}$ ,  $C_{PVOUT1} = 64 \mu F$

# THEORY OF OPERATION POWER MANAGEMENT UNIT

The ADP5003 is a micropower management unit combining a step-down (buck) dc-to-dc converter and an ultralow noise low dropout linear (LDO)regulator. The high switching frequency and 5 mm  $\times$  5 mm, 32-lead LFCSP package allow a compact power management solution.

#### **Adaptive Headroom Control**

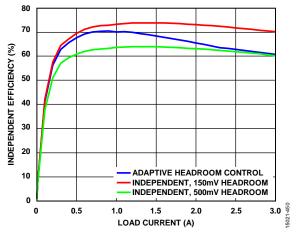

The ADP5003 features a scheme to control the LDO headroom voltage to ensure optimal operating efficiency while maintaining a consistent power supply rejection ratio (PSRR) across the full range of the LDO load current.

The scheme works by varying the headroom voltage across the LDO NFET with respect to the LDO load current. Lower and upper limits prevent the headroom from approaching zero volts at light loads and from increasing more than necessary at high loads.

#### Precision Enable/Shutdown

The ADP5003 has individual enable pins (EN1 and EN2) to control the regulators.

The precision enable function allows a precise turn on point for the regulators to allow the possibility of external sequencing. A voltage level higher than  $V_{\text{TH\_H}}$  applied to the EN1 or EN2 pin activates a regulator, whereas a level below  $V_{\text{TH\_L}}$  turns off a regulator. The buck is controlled by EN1, and the LDO is controlled by the EN2 pin. When both EN1 and EN2 fall below  $V_{\text{TH\_S}}$ , the ADP5003 enters shutdown mode.

#### **Undervoltage Lockout (UVLO)**

To protect against the input voltage being too low, UVLO circuitry is integrated into the system. If the input voltage on PVINSYS drops to less than the UVLO<sub>PVINSYSFALL</sub> threshold, all channels shut down.

The device is enabled again when the voltage on PVINSYS rises to more than the  $UVLO_{PVINSYSRISE}$  threshold, provided the enable pins remain active.

#### Thermal Shutdown (TSD)

In the event that the junction temperature rises above  $T_{\text{SD}}$ , the thermal shutdown circuit turns off both regulators. Extreme junction temperatures can be the result of high current operation, poor circuit board design, or a high ambient temperature. A hysteresis value of  $T_{\text{SD-HYS}}$  is included so that when thermal shutdown occurs, the regulators do not return to operation until the on-chip temperature drops below  $T_{\text{SD}} - T_{\text{SD-HYS}}$ . When emerging from thermal shutdown, both regulators restart with soft start control.

#### **Active Pull Down**

Both regulators have active pull-down resistors discharging the respective output capacitors when the regulators are disabled. The pull-down resistors are connected between VOUT1 to AGND1 and PVOUT2 to AGND2. Active pull-down resistors are disabled when the regulators are turned on.

When the enable pins are asserted low, or a TSD or UVLO event occurs, the active pull-down resistors enable to quickly discharge the output capacitors. The pull-down resistors remain engaged until the enable pins are asserted high, the fault event is no longer present, or the VREG supply voltage falls to less than the voltage required (approximately 1 V) to guarantee that the pull-down resistor remains enabled.

#### Soft Start (SS)

Both regulators have an internal soft start function that ramps the output voltage in a controlled manner on startup, thereby limiting the inrush current. The soft start function reduces the risk of noise spikes and voltage drops on the upstream supplies.

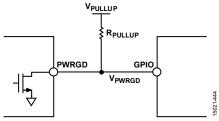

#### Power-Good

The ADP5003 has a dedicated power-good, open-drain, output (PWRGD). PWRGD indicates whether one or more regulators are outside the voltage limits specified by the power-good lower limit (PWRGD<sub>F</sub>) and the power-good upper limit (PWRGD<sub>F</sub> + PWRGD<sub>FH</sub>). When either one or both of the regulator outputs are outside the power-good limits, the PWRGD output pulls low. PWRGD will continue to pull low, provided the VREG supply voltage remains above approximately 1 V.

When in adaptive mode, PWRGD only monitors the LDO output, and when in standalone mode, PWRGD only monitors the regulator/regulators that are enabled.

#### **BUCK REGULATOR**

#### **Control Scheme**

The buck regulator operates with a fixed frequency, emulated peak current mode, pulse-width modulation (PWM) control architecture, where the duty cycle of the integrated switches is adjusted and regulates the output voltage. At the start of each oscillator cycle, the positive channel field effect transistor (PFET) switch is turned on, sending a positive voltage across the inductor. Current in the inductor increases until the emulated current sense signal crosses the peak inductor current threshold, which turns off the PFET switch and turns on the NFET synchronous rectifier. Turning on the NFET synchronous rectifier creates a negative voltage across the inductor, which causes the inductor current to decrease. The synchronous rectifier stays on for the remainder of the cycle. By adjusting the peak inductor current threshold, the buck regulator can regulate the output voltage.

The emulated inductor current scheme senses the current in the inductor during the off phase of the cycle, when the NFET is conducting, and uses this inductor current to generate the emulated current sense signal during the on time of the cycle. This scheme allows the low duty cycles necessary for high input voltage,  $V_{\rm IN}$ , to output voltage,  $V_{\rm OUT}$ , conversion ratios.

#### **Oscillator Frequency Control**

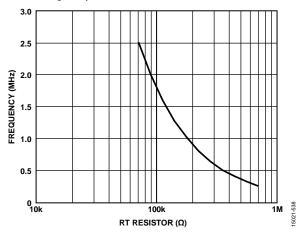

The ADP5003 buck regulator oscillator frequency is controlled by using the RT pin or the SYNC pin. To define the buck regulator internal switching frequency, connect the RT pin via a resistor to AGND1. Figure 38 shows the relationship of the buck oscillator frequency and the RT resistor value.

Figure 38. Buck Oscillator Frequency vs. RT Resistor (RRT)

To determine the oscillator frequency (f<sub>SW</sub>), use the following equation:

$$f_{SW} = (1.78 \times 10^{11})/R_{RT} \tag{1}$$

An upper limit prevents out of range frequencies when the RT pin is shorted to ground or connected with a resistor value less than 70 k $\Omega$ .

#### **External Oscillator Synchronization**

The SYNC pin is dedicated for oscillator synchronization and allows the ADP5003 to lock to an external clock.

When an applied external clock signal is present at the SYNC pin, the buck regulator operates in sync with this signal.

When alternating between external clocks and the internal oscillator, the presence of an external frequency causes a multiplexer to switch between the internal oscillator and the external SYNC frequency. The output of this multiplexer acts as the frequency reference to an internal phase-locked loop (PLL), which ensures that changing between the two modes of operation results in a smooth transition between the different frequencies.

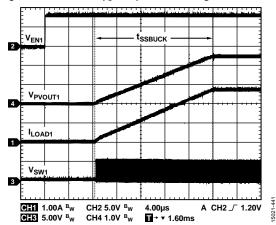

#### **Buck Startup**

The buck regulator turns on with a controlled soft start ramp to limit inrush current. The reference of the buck is ramped during t<sub>SSBUCK</sub>, which is typically 2 ms (see Figure 39).

Figure 39. Buck Startup

#### **Current-Limit and Short-Circuit Protection**

The buck regulator includes current-limit protection circuitry to limit the amount of forward current through the field effect transistor (FET) switches. When the valley inductor current exceeds the overcurrent limit threshold for a number of clock cycles during an overload or short-circuit condition, the regulator enters hiccup mode. The regulator stops switching and then restarts with a new soft start cycle after the hiccup time, thiccup, and repeats until the over-current condition is removed. If the buck regulator output voltage falls below 50% of the nominal output voltage, the regulator immediately enters hiccup mode. When the valley inductor current falls below the negative current-limit threshold, the NFET turns off and the PFET remains off allowing the inductor current to be discharged via the PFET body diode. The PFET turns on again with the next clock edge after the inductor current no longer exceeds the negative current-limit threshold.

Figure 40. Short-Circuit Response (Current Limit and Hiccup Mode)

#### **LDO REGULATOR**

The ADP5003 contains a single low noise, low dropout (LDO) linear regulator that uses an NFET pass device to provide high PSRR with low headroom voltage and an output current up to 3 A.

The LDO regulator can operate with an input voltage of 0.65 V to 5 V while providing excellent line and load transient response using 10  $\mu F$  ceramic input and output capacitors.

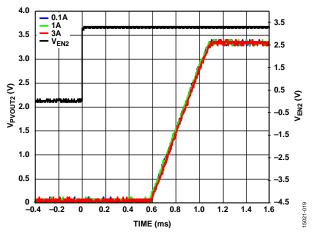

#### **LDO Startup**

The LDO regulator turns on with a controlled soft start ramp to limit inrush current. This soft start ramp is dictated by  $t_{\text{SSLDO}}$ , which is typically 400  $\mu s$ .

Figure 41. LDO Startup

#### **Current Limit**

The LDO operates in current limit when the output load exceeds I<sub>LIMIT2</sub>. When in current limit operation, the output voltage reduces to maintain a constant output current.

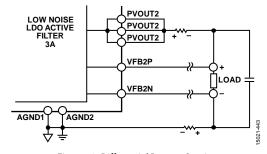

#### **Differential Remote Sensing**

The LDO can sense at the point of load by using VFB2P and VFB2N as shown in Figure 42. Differential remote sensing compensates for both the source drop and the return drop to provide a more precise supply scheme at the point of load.

Figure 42. Differential Remote Sensing

#### **POWER-GOOD**

An external pull-up resistor is necessary to drive the PWRGD output high (see Figure 43). Through the value of the pull-up resistor is not critical, it is recommended to use a 10 k $\Omega$  to 300 k $\Omega$  resistor. The resistor must be pulled to a voltage level no greater than 5.5 V.

Figure 43. Power-Good Setup

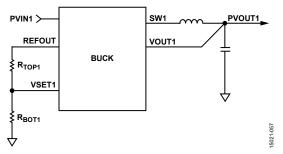

#### **OUTPUT VOLTAGE OF THE BUCK REGULATOR**

The output voltage on the buck regulator is adjustable through an external resistor divider. When using adaptive mode, the ADP5003 controls the buck output voltage.

The adjustable output voltage configuration is shown in Figure 44.

Figure 44. Buck Regulator Adjustable Output Voltage

To calculate the buck output voltage, use the following equation:

$$V_{PVOUT\,1} = V_{REFOUT}\,A_{BUCK} \left( \frac{R_{BOT\,1}}{R_{TOP\,1} + R_{BOT\,1}} \right) \tag{2}$$

where:

$V_{REFOUT}$  is the REFOUT output voltage.

$A_{BUCK}$  is the buck regulator gain.

$R_{BOT1}$  is the bottom divider resistor.

$R_{TOP1}$  is the top divider resistor.

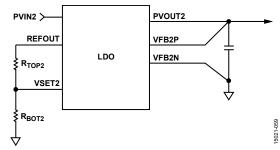

#### **OUTPUT VOLTAGE OF THE LDO REGULATOR**

The output voltage on the LDO regulator is adjustable through an external resistor divider. The LDO adjustable output voltage configuration is shown in Figure 45.

Figure 45. LDO Adjustable Output Voltage Configuration

To calculate the LDO output voltage, use the following equation:

$$V_{PVOUT\,2} = V_{REFOUT} A_{LDO} \left( \frac{R_{BOT\,2}}{R_{TOP\,2} + R_{BOT\,2}} \right)$$

(3)

where:

$A_{LDO}$  is the LDO gain.

$R_{BOT2}$  is the bottom divider resistor.

$R_{TOP2}$  is the top divider resistor.

#### **VOLTAGE CONVERSION LIMITATIONS**

For a given input voltage and switching frequency, an upper and lower limitation on the output voltage exists due to the minimum on time and minimum off time. The minimum on time limits the minimum output voltage for a given input voltage and switching frequency.

If the minimum on time is exceeded, the ADP5003 may not switch at a fixed frequency because the device can switch at an effective zero on time, resulting in unpredictable switching frequencies and unwanted noise.

To calculate the minimum output voltage for a given input voltage and fixed switching frequency, use the following equation:

$$V_{OUT\_MIN} = V_{PVIN1} \times t_{MIN\_ON} \times f_{SW} - (R_{PFET} - R_{NFET}) \times I_{OUT\_MIN} \times t_{MIN\_ON} \times f_{SW} - (R_{NFET} + R_L) \times I_{OUT\_MIN}$$

(4)

where:

$V_{OUT\_MIN}$  is the minimum output voltage.

$V_{PVIN1}$  is the input voltage.

$t_{MIN\_ON}$  is the minimum on time.

$f_{SW}$  is the switching frequency.

$R_{PFET}$  is the high-side PFET on resistance.

$R_{NFET}$  is the low-side NFET on resistance.

$I_{OUT\_MIN}$  is the minimum output current.

$R_L$  is the resistance of the output inductor.

The minimum off time limits the maximum duty cycle which in turn limits the maximum output voltage for a given input voltage and switching frequency. Calculate the maximum output voltage for a given input voltage and switching frequency by using the following equation:

$$V_{OUT\_MAX} = V_{PVIN1} \times (1 - t_{MIN\_OFF} \times f_{SW}) - (R_{PFET} - R_{NFET}) \times I_{OUT\_MAX} \times (1 - t_{MIN\_OFF} \times f_{SW}) - (R_{NFET} + R_L) \times I_{OUT\_MAX}$$

(5)

where:

$V_{OUT\_MAX}$  is the maximum output voltage.

$I_{OUT\_MAX}$  is the maximum output current.

$t_{MIN\_OFF}$  is the minimum off time.

As shown in Equation 4 and Equation 5, reducing the switching frequency eases the minimum on time and minimum off time limitations.

#### COMPONENT SELECTION

#### **Output Capacitors**

Higher output capacitor values reduce the output voltage ripple and improve the load transient response.

Ceramic capacitors are manufactured with a variety of dielectrics, each with a different behavior over temperature and applied voltage. Capacitors must have a dielectric adequate to ensure the minimum capacitance over the necessary temperature range and dc bias conditions. X5R or X7R dielectrics with a voltage rating of 25 V are recommended for best performance. Y5V and Z5U dielectrics are not recommended for use with any dc-to-dc converter because of their poor temperature and dc bias characteristics.

Use the following equation to calculate the worst case capacitance, accounting for capacitor variation over temperature, component tolerance, and voltage:

$$C_{EFFECTIVE} = C_{NOMINAL} \times (1 - TEMPCO) \times (1 - DCBIASCO) \times (1 - Tolerance)$$

(6)

where:

$C_{EFFECTIVE}$  is the effective capacitance at the operating voltage.  $C_{NOMINAL}$  is the nominal data sheet capacitance.

TEMPCO is the worst case capacitor temperature coefficient. DCBIASCO is the dc bias derating at the output voltage. Tolerance is the worst case component tolerance.

To guarantee the performance of the device, it is imperative to evaluate the dc bias effects, temperature, and tolerances on the behavior of the capacitors for each application.

Capacitors with lower effective series resistance (ESR) and effective series inductance (ESL) are preferred to minimize output voltage ripple.

Use the following equation to calculate the minimum capacitance needed for a specific output voltage ripple:

$$C_{OUT\_MIN} \cong \frac{\Delta I_L}{8 \times f_{SW} \times (V_{RIPPLE} - \Delta I_L \times R_{ESR})}$$

(7)

where:

$\Delta I_L$  is the current ripple.

*f*<sub>SW</sub> is the switching frequency.

$V_{RIPPLE}$  is the allowed peak-to-peak voltage ripple.

$R_{ESR}$  is the effective series resistance of the capacitor.

The minimum capacitance needed for stability considering temperature and dc bias effects is 22  $\mu F$ .

The minimum capacitance recommended for the LDO is 10  $\mu\text{F}.$

**Table 8. Recommended Output Capacitors**

| Vendor | Part No.          | Value (μF) | Туре | Voltage Rating (V) | Case |

|--------|-------------------|------------|------|--------------------|------|

| Wurth  | 885 012 207 026   | 10         | X7R  | 10                 | 0805 |

|        | 885 012 209 006   | 22         | X7R  | 10                 | 1210 |

|        | 885 012 109 012   | 47         | X5R  | 25                 | 1210 |

|        | 885 012 109 004   | 100        | X5R  | 6.3                | 1210 |

| Murata | GRM21BR71A106KE51 | 10         | X7R  | 10                 | 0805 |

|        | GRM32ER71C226KEA8 | 22         | X7R  | 16                 | 1210 |

|        | GRM32ER71A476KE15 | 47         | X7R  | 10                 | 1210 |

#### **Input Capacitor**

The input current to the buck converter steps from zero to a positive value that is dependent on inductor value, switching frequency, and load current (typically between 1 A and 4 A) and then drops quickly to zero again every switching cycle. Because these current pulses occur at relatively high frequencies (0.3 MHz to 2.5 MHz), the input bypass capacitor provides most of the high frequency current while the input power source supplies only the average current. Higher value input capacitors reduce the input voltage ripple and improve transient response.

To minimize supply noise, it is recommended to place a low ESR capacitor as close as possible to the relevant supply pin.

#### Inductor

The high switching frequency of the ADP5003 buck allows the selection of small chip inductors. A small inductor leads to larger inductor current ripple that provides improved transient response but degrades efficiency. The sizing of the inductor is a trade-off between efficiency and transient response. As a guideline, the inductor peak-to-peak current ripple is typically set to 1/3 of the maximum load current for optimal transient response and efficiency.

To calculate the inductor value, L, use the following equation:

$$L = ((V_{PVIN1} - V_{PVOUT1}) \times D)/(\Delta I_L \times f_{SW})$$

(8)

where:

$V_{PVIN1}$  is the input voltage.

$V_{PVOUT1}$  is the output voltage.

*D* is the duty cycle ( $D = V_{VOUT1}/V_{PVIN1}$ ).

$\Delta I_L$  is the inductor ripple current.

*f*<sub>SW</sub> is the switching frequency.

The minimum dc current rating of the inductor must be greater than the inductor peak current. Use the following equation to calculate the inductor peak current:

$$I_{PEAK} = I_{LOAD1} + (\Delta I_L/2) \tag{9}$$

where:

$I_{LOAD1}$  is the output current.

$\Delta I_L$  is the inductor ripple current.

Inductor conduction losses are minimized by using larger sized inductors that have smaller dc resistance; this in turn improves efficiency at the cost of solution size. Due to the high switching frequency of the ADP5003, shielded ferrite core material is recommended for its low core losses and low electromagnetic interference (EMI).

**Table 9. Recommended Inductors**

| Vendor    | Part No.       | Value (μH) | Saturation Current, I <sub>SAT</sub> (A) | RMS Current, I <sub>RMS</sub> (A) | DC Resistance (mΩ) | Size (mm) |

|-----------|----------------|------------|------------------------------------------|-----------------------------------|--------------------|-----------|

| Coilcraft | XAL4020-102    | 1          | 8.7                                      | 6.7                               | 13.25              | 4×4       |

|           | XAL4020-122    | 1.2        | 7.9                                      | 6.6                               | 17.75              | 4×4       |

|           | XAL4020-152    | 1.5        | 7.1                                      | 5.2                               | 21.45              | 4 × 4     |

|           | XAL4020-222    | 2.2        | 5.6                                      | 4                                 | 35.2               | 4×4       |

|           | XAL5030-102    | 1          | 14                                       | 8.7                               | 8.5                | 5 × 5     |

|           | XAL5030-122    | 1.2        | 12.5                                     | 7.9                               | 11.4               | 5 × 5     |

|           | XAL5030-222    | 2.2        | 9.2                                      | 7.2                               | 13.2               | 5 × 5     |

|           | XAL5030-332    | 3.3        | 8.7                                      | 5.9                               | 21.2               | 5 × 5     |

|           | XAL5050-562    | 5.6        | 6.3                                      | 5.3                               | 23.45              | 5 × 5     |

|           | XAL5050-682    | 6.8        | 6                                        | 4.7                               | 26.75              | 5 × 5     |

|           | XEL6030-102    | 1          | 18                                       | 12                                | 6.32               | 6×6       |

|           | XEL6030-152    | 1.5        | 15                                       | 10                                | 9.57               | 6×6       |

|           | XEL6030-222    | 2.2        | 13                                       | 7                                 | 12.7               | 6×6       |

|           | XEL6030-332    | 3.3        | 10.5                                     | 6                                 | 19.92              | 6×6       |

|           | XEL6060-472    | 4.7        | 11.4                                     | 9                                 | 13.65              | 6×6       |

|           | XAL6060-562    | 5.6        | 9.9                                      | 7.5                               | 14.46              | 6×6       |

|           | XEL6060-682    | 6.8        | 7.9                                      | 7.3                               | 20.82              | 6×6       |

|           | XEL6060-822    | 8.2        | 7.6                                      | 7                                 | 22.71              | 6×6       |

|           | XAL6060-103    | 10         | 7.6                                      | 5                                 | 27                 | 6×6       |

| Wurth     | 744 383 570 10 | 1          | 9.6                                      | 7.4                               | 11.6               | 4 × 4     |

|           | 744 383 570 12 | 1.2        | 8.8                                      | 7                                 | 13.4               | 4 × 4     |

|           | 744 383 570 15 | 1.5        | 8.5                                      | 6.2                               | 17.1               | 4×4       |

|           | 744 383 570 18 | 1.8        | 8                                        | 5.8                               | 18                 | 4×4       |

|           | 744 383 570 22 | 2.2        | 7                                        | 5.2                               | 22                 | 4 × 4     |

#### **COMPENSATION COMPONENTS DESIGN**

For the peak current mode control architecture, the power stage can be simplified as a voltage controlled current source that supplies current to the output capacitor and load resistor. The simplified loop is composed of one dominant pole and a zero contributed by the output capacitor ESR.

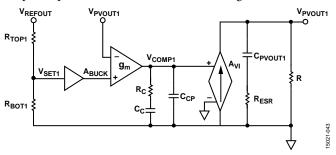

The ADP5003 uses a transconductance amplifier as the error amplifier to compensate the system. Figure 46 shows the simplified peak current mode control, small signal circuit.

Figure 46. Simplified Peak Current Mode Control, Small Signal Circuit

The compensation components,  $R_C$  and  $C_C$ , contribute a zero, and the optional  $C_{CP}$  and  $R_C$  contribute an optional pole.

The following procedure shows how to select the compensation components ( $R_C$ ,  $C_C$ , and  $C_{CP}$ ) for ceramic output capacitor applications:

- 1. Determine the cross frequency ( $f_c$ ). Generally,  $f_c$  is between  $f_{SW}/12$  and  $f_{SW}/6$ .

- 2. Use the following equation to calculate  $R_C$ :

$$R_C = \frac{2 \times \pi \times C_{PVOUT1} \times A_{BUCK}}{g_m \times A_{VI}}$$

(10)

where:

$C_{PVOUT1}$  is the output capacitance.

$A_{VI} = 7 \text{ A/V}.$

3. Place the compensation zero at the domain pole  $(f_P)$ . Determine  $C_C$  as follows:

$$C_C = ((R + R_{ESR}) \times C_{PVOUT1})/R_C$$

(11)

where:

$R_{ESR}$  is the equivalent series resistance of the output capacitor.

4.  $C_{CP}$  is optional. It can cancel the zero caused by the ESR of the output capacitor. Determine  $C_{CP}$  as follows:

$$C_{CP} = (R_{ESR} \times C_{PVOUT1})/R_C \tag{12}$$

#### **JUNCTION TEMPERATURE**

In cases where the ambient temperature  $(T_A)$  is known, the thermal resistance parameter  $(\theta_{JA})$  can estimate the junction temperature rise  $(T_J)$ .  $T_J$  is calculated with  $T_A$  and the power dissipation  $(P_D)$  using the following formula:

$$T_{J} = T_{A} + (P_{D} \times \theta_{JA}) \tag{13}$$

The typical  $\theta_{JA}$  value for the 32-lead, 5 mm  $\times$  5 mm LFCSP is 46.91°C/W. An important factor to consider is that  $\theta_{JA}$  is based on a 4-layer, 4 inches  $\times$  3 inches, 2.5 ounces copper PCB, as per the JEDEC standard, and applications may use different sizes and layers. It is important to maximize the copper used to remove the heat from the device. Copper exposed to air dissipates heat better than copper used in the inner layers. Connect the exposed pad to the ground plane with several vias.

If the case temperature can be measured, the junction temperature is calculated by

$$T_I = T_C + (P_D \times \theta_{IC}) \tag{14}$$

where:

$T_C$  is the case temperature.

$\theta_{JC}$  is the junction to case thermal resistance provided in Table 6.

To achieve reliable operation of the buck converter and LDO regulator, the estimated die junction temperature of the ADP5003 must be less than 125°C. Reliability and mean time between failures (MTBF) is highly affected by increasing the junction temperature. Additional information about product reliability can be found in the Analog Devices, Inc., *Reliability Handbook* at www.analog.com/reliability\_handbook.

The total power dissipation in the ADP5003 simplifies to

$$P_D = P_{DBUCK} + P_{DLDO} \tag{15}$$

where:

$P_{DBUCK} = (V_{PVIN1} \times I_{PVIN1}) - (V_{PVOUT1} \times I_{LOAD1}).$   $P_{DLDO} = ((V_{PVIN2} - V_{PVOUT2}) \times I_{LOAD2}) + (V_{PVIN2} \times I_{GND}).$

### **BUCK REGULATOR DESIGN EXAMPLE**

This section provides an example of the step by step design procedures and the external components required for the buck regulator. Table 10 lists the design requirements for this example.

Table 10. Example Design Requirements for the Buck Regulator

| Parameter      | Specification                             |

|----------------|-------------------------------------------|

| Input Voltage  | V <sub>PVIN1</sub> = 12 V                 |

| Output Voltage | $V_{PVOUT1} = 2.5 V$                      |

| Output Current | $I_{LOAD1} = 3 A$                         |

| Output Ripple  | $\Delta V_{OUT1\_RIPPLE} = 25 \text{ mV}$ |

| Load Transient | ±5% at 20% to 80% load transient          |

## SETTING THE SWITCHING FREQUENCY FOR THE BUCK REGULATOR

The first step is to determine the switching frequency for the ADP5003 design. In general, higher switching frequencies produce a smaller solution size due to the lower component values required, whereas lower switching frequencies result in higher conversion efficiency due to lower switching losses.

The switching frequency of the ADP5003 can be set from 0.3 MHz to 2.5 MHz by connecting a resistor from the RT pin to ground. The selected resistor allows the user to make decisions based on the trade-off between efficiency and solution size. (For more information, see the Oscillator Frequency Control section.) However, the highest supported switching frequency must be assessed by checking the voltage conversion limitations enforced by the minimum on time and the minimum off time (see the Voltage Conversion Limitations section).

In this design example, a switching frequency of 600 kHz is used to achieve an ideal combination of small solution size and high conversion efficiency. To set the switching frequency to 600 kHz, use Equation 1 to calculate the resistor value,  $R_{\text{RT}}.$  This gives a standard resistor value of  $R_{\text{T}}=294~\text{k}\Omega.$

## SETTING THE OUTPUT VOLTAGE FOR THE BUCK REGULATOR

Select a value for the top resistor ( $R_{TOP1}$ ) and then calculate the bottom feedback ( $R_{BOT1}$ ) resistor by using the following equation:

$$R_{BOTI} = (R_{TOPI} \times V_{PVOUTI})/((V_{REFOUT} \times A_{BUCK}) - V_{PVOUTI}) \quad (16)$$

where

$V_{PVOUT1}$  is the buck output voltage.

$V_{REFOUT}$  is 2 V.

$A_{BUCK}$  is the buck regulator gain.

To set the output voltage to 2.5 V,  $R_{TOP1}$  is set to 100 k $\Omega$ , giving an  $R_{BOT1}$  value of 100 k $\Omega$ .

## SELECTING THE INDUCTOR FOR THE BUCK REGULATOR

The peak-to-peak inductor ripple current,  $\Delta I_L$ , is set to 35% of the maximum output current. Use Equation 8 to estimate the value of the inductor:

$$L = ((V_{PVIN1} - V_{PVOUT1}) \times D)/(\Delta I_L \times f_{SW})$$

where:

$V_{PVIN1} = 12 \text{ V}.$

$V_{PVOUT1} = 2.5 \text{ V}.$

*D* is the duty cycle ( $D = V_{PVOUT1}/V_{PVIN1}$ ).

$\Delta I_L = 35\% \times 3 \text{ A} = 1.05 \text{ A}.$

$f_{SW} = 600 \text{ kHz}.$

The resulting value for L is 3.14  $\mu$ H. The selected standard inductor value is 3.3  $\mu$ H; therefore,  $\Delta I_L$  is 1 A.

To calculate the peak inductor current (IPEAK), use Equation 9:

$$I_{PEAK} = I_{LOAD1} + (\Delta I_L/2)$$

The calculated peak current for the inductor is 3.5 A.

# SELECTING THE OUTPUT CAPACITOR FOR THE BUCK REGULATOR

The output capacitor must meet the output voltage ripple, load transient requirements and stability requirements. To meet the output voltage ripple requirement, use Equation 7 to calculate the capacitance:

$$C_{OUT\_MIN} \cong \frac{\Delta I_L}{8 \times f_{SW} \times (V_{RIPPLF} - \Delta I_L \times R_{FSR})}$$

The calculated capacitance,  $C_{OUT\ MIN}$ , is 8.7 µF.

To meet the  $\pm 5\%$  overshoot and undershoot requirements, use the following equations to calculate the capacitance:

$$C_{OUT\_UV} = \frac{K_{UV} \times \Delta I_{STEP}^2 \times L}{2 \times (V_{PVIN1} - V_{PVOUT1}) \times \Delta V_{OUT} \ _{UV}}$$

(17)