### **Data Sheet**

### FEATURES

Ultrawideband frequency range: 100 MHz to 30 GHz Nonreflective 50 Ω design Low insertion loss: 2.6 dB at 20 GHz to 30 GHz High isolation: 43 dB at 20 GHz to 30 GHz High input linearity P1dB: 28 dBm typical IP3: 50 dBm typical High power handling 24 dBm through path 24 dBm terminated path No low frequency spurious 0.1 dB settling time (50% V<sub>CTL</sub> to 0.1 dB of final RF output): 37 ns 24-terminal LGA package

### APPLICATIONS

**Test instrumentation**

Microwave radios and very small aperture terminals (VSATs) Military radios, radars, and electronic counter measures (ECMs) Broadband telecommunications systems

### **GENERAL DESCRIPTION**

The ADRF5044 is a general-purpose, single-pole, four-throw (SP4T) switch manufactured using a silicon process. It comes in a 24-terminal land grid array (LGA) package and provides high isolation and low insertion loss from 100 MHz to 30 GHz.

# 100 MHz to 30 GHz, Silicon, SP4T Switch

# **ADRF5044**

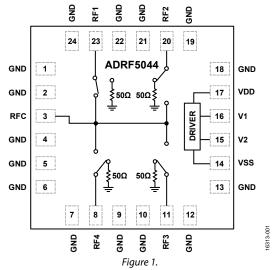

### FUNCTIONAL BLOCK DIAGRAM

This broadband switch requires dual-supply voltages, +3.3 V and -3.3 V, and provides complementary metal-oxide semiconductor (CMOS)/low voltage transistor-transistor logic (LVTTL) logic-compatible control.

Rev. A

#### Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# TABLE OF CONTENTS

| Features                                    |

|---------------------------------------------|

| Applications 1                              |

| Functional Block Diagram 1                  |

| General Description 1                       |

| Revision History                            |

| Specifications                              |

| Absolute Maximum Ratings 5                  |

| Thermal Resistance 5                        |

| Power Derating Curves 5                     |

| ESD Caution 5                               |

| Pin Configuration and Function Descriptions |

| Interface Schematics                        |

### **REVISION HISTORY**

| 3/2020- | -Rev. | 0 | to | Rev. | A |

|---------|-------|---|----|------|---|

|         |       |   |    |      |   |

| Changes to Digital Control Inputs Parameter, Table 2 5 | , |

|--------------------------------------------------------|---|

| Added Endnote 1, Table 2; Renumbered Sequentially 5    |   |

| Changes to Theory of Operation Section                 | ) |

### 12/2017—Revision 0: Initial Version

| Typical Performance Characteristics                                | 7    |

|--------------------------------------------------------------------|------|

| Insertion Loss, Return Loss, and Isolation                         | 7    |

| Input 0.1 dB, 1 dB Power Compression, and Third-Order<br>Intercept |      |

| Theory of Operation                                                | . 10 |

| Applications Information                                           | . 11 |

| Evaluation Board                                                   | . 11 |

| Probe Matrix Board                                                 | . 13 |

| Outline Dimensions                                                 | . 14 |

| Ordering Guide                                                     | . 14 |

# **SPECIFICATIONS**

$V_{\text{DD}} = 3.3 \text{ V}, V_{\text{SS}} = -3.3 \text{ V}, \text{V1} = 0 \text{ V or } 3.3 \text{ V}, \text{V2} = 0 \text{ V or } 3.3 \text{ V}, \text{and } T_{\text{CASE}} = 25^{\circ}\text{C}, 50 \Omega \text{ system, unless otherwise noted.}$

### Table 1.

| Parameter                                     | Symbol                              | Test Conditions/Comments                                                   | Min   | Тур | Max             | Unit |

|-----------------------------------------------|-------------------------------------|----------------------------------------------------------------------------|-------|-----|-----------------|------|

| FREQUENCY RANGE                               |                                     |                                                                            | 100   |     | 30,000          | MHz  |

| INSERTION LOSS                                |                                     |                                                                            |       |     |                 |      |

| Between RFC and RF1 to RF4 (On) (Worst Case)  |                                     | 100 MHz to 10 GHz                                                          |       | 1.7 |                 | dB   |

|                                               |                                     | 10 GHz to 20 GHz                                                           |       | 2.1 |                 | dB   |

|                                               |                                     | 20 GHz to 30 GHz                                                           |       | 2.6 |                 | dB   |

| ISOLATION                                     |                                     |                                                                            |       |     |                 |      |

| Between RFC and RF1 to RF4 (Off) (Worst Case) | 1                                   | 100 MHz to 10 GHz                                                          |       | 55  |                 | dB   |

|                                               |                                     | 10 GHz to 20 GHz                                                           |       | 52  |                 | dB   |

|                                               |                                     | 20 GHz to 30 GHz                                                           |       | 43  |                 | dB   |

| RETURN LOSS                                   |                                     |                                                                            |       |     |                 |      |

| RFC and RF1 to RF4 (On)                       |                                     | 100 MHz to 10 GHz                                                          |       | 16  |                 | dB   |

|                                               |                                     | 10 GHz to 20 GHz                                                           |       | 22  |                 | dB   |

|                                               |                                     | 20 GHz to 30 GHz                                                           |       | 22  |                 | dB   |

| RF1 to RF4 (Off)                              |                                     | 100 MHz to 10 GHz                                                          |       | 24  |                 | dB   |

|                                               |                                     | 10 GHz to 20 GHz                                                           |       | 24  |                 | dB   |

|                                               |                                     | 20 GHz to 30 GHz                                                           |       | 16  |                 | dB   |

| SWITCHING TIME                                |                                     |                                                                            |       |     |                 |      |

| Rise and Fall                                 | trise, t <sub>FALL</sub>            | 10% to 90% of radio frequency (RF) output                                  |       | 4   |                 | ns   |

| On and Off                                    | t <sub>on</sub> , t <sub>off</sub>  | 50% V <sub>CTL</sub> to 90% of RF output                                   |       | 19  |                 | ns   |

| Settling                                      |                                     |                                                                            |       |     |                 |      |

| 0.1 dB                                        |                                     | 50% V <sub>CTL</sub> to 0.1 dB of final RF output                          |       | 37  |                 | ns   |

| 0.05 dB                                       |                                     | 50% V <sub>CTL</sub> to 0.05 dB of final RF output                         |       | 50  |                 | ns   |

| INPUT LINEARITY                               |                                     | · · ·                                                                      |       |     |                 |      |

| Power Compression                             |                                     |                                                                            |       |     |                 |      |

| 0.1 dB                                        | P0.1dB                              |                                                                            |       | 26  |                 | dBm  |

| 1 dB                                          | P1dB                                |                                                                            |       | 28  |                 | dBm  |

| Third-Order Intercept                         | IP3                                 | Two-tone input power = 14 dBm each tone,<br>$\Delta f = 1 \text{ MHz}$     |       | 50  |                 | dBm  |

| SUPPLY CURRENT                                |                                     | VDD, VSS pins                                                              |       |     |                 |      |

| Positive                                      | IDD                                 | Typical at $V_{CTL} = 0$ V or 3.3 V, maximum at $V_{CTL} = 0.8$ V or 1.4 V |       | 12  | 20              | μΑ   |

| Negative                                      | I <sub>ss</sub>                     | Typical at $V_{CTL} = 0$ V or 3.3 V, maximum at $V_{CTL} = 0.8$ V or 1.4 V |       | 110 | 130             | μΑ   |

| DIGITAL CONTROL INPUTS                        |                                     | V1, V2 pins                                                                |       |     |                 | 1    |

| Voltage                                       |                                     |                                                                            |       |     |                 |      |

| Low                                           | VINL                                |                                                                            | 0     |     | 0.8             | v    |

| High                                          | VINH                                |                                                                            | 1.2   |     | 3.3             | V    |

| Current                                       |                                     |                                                                            |       |     |                 |      |

| Low and High                                  | I <sub>INL</sub> , I <sub>INH</sub> |                                                                            |       | <1  |                 | μA   |

| RECOMMENDED OPERATING CONDITONS               | ,                                   |                                                                            |       |     |                 |      |

| Supply Voltage                                |                                     |                                                                            |       |     |                 |      |

| Positive                                      | V <sub>DD</sub>                     |                                                                            | 3.15  |     | 3.45            | v    |

| Negative                                      | Vss                                 |                                                                            | -3.45 |     | -3.15           | v    |

| Digital Control Voltage                       | V <sub>CTL</sub>                    |                                                                            | 0     |     | V <sub>DD</sub> | v    |

**Data Sheet**

| Parameter        | Symbol            | Test Conditions/Comments                                        | Min | Тур | Max | Unit |

|------------------|-------------------|-----------------------------------------------------------------|-----|-----|-----|------|

| RFx Input Power  | PIN               | $T_{CASE} = 85^{\circ}C$                                        |     |     |     |      |

| Through Path     |                   | RF signal is applied to RFC or through connected RF1/RF2        |     |     | 24  | dBm  |

| Terminated Path  |                   | RF signal is applied to terminated<br>RF1/RF2                   |     |     | 24  | dBm  |

| Hot Switching    |                   | RF signal is present at RFC while switching between RF1 and RF2 |     |     | 21  | dBm  |

| Case Temperature | T <sub>CASE</sub> | -                                                               | -40 |     | +85 | °C   |

# **ABSOLUTE MAXIMUM RATINGS**

For recommended operating conditions, see Table 1.

#### Table 2.

| Parameter                                                                          | Rating                                                                    |

|------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Supply Voltage                                                                     |                                                                           |

| Positive                                                                           | –0.3 V to +3.6 V                                                          |

| Negative                                                                           | -3.6 V to +0.3 V                                                          |

| Digital Control Inputs <sup>1</sup>                                                | -0.3 V to V <sub>DD</sub> + 0.3 V<br>or 3.3 mA, whichever<br>occurs first |

| RFx Input Power <sup>2</sup> (f = 400 MHz to 30 GHz,<br>$T_{CASE} = 85^{\circ}$ C) |                                                                           |

| Through Path                                                                       | 25 dBm                                                                    |

| Terminated Path                                                                    | 25 dBm                                                                    |

| Hot Switching                                                                      | 22 dBm                                                                    |

| Temperature                                                                        |                                                                           |

| Junction, T                                                                        | 135°C                                                                     |

| Storage Range                                                                      | –65°C to +150°C                                                           |

| Reflow (Moisture Sensitivity Level 3<br>(MSL3) Rating)                             | 260°C                                                                     |

| Electrostatic Discharge (ESD) Sensitivity                                          |                                                                           |

| Human Body Model (HBM)                                                             |                                                                           |

| RFC and RF1 to RF4 Pins                                                            | 375 V                                                                     |

| Other Pins                                                                         | 2000 V                                                                    |

<sup>1</sup> Overvoltages at digital control inputs are clamped by internal diodes.

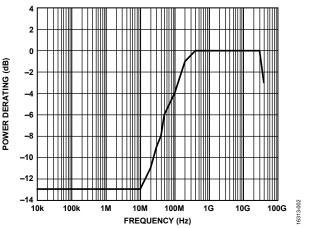

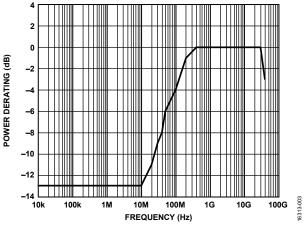

Current must be limited to the maximum rating given. <sup>2</sup> For power derating less than 400 MHz, see Figure 2 and Figure 3.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

Only one absolute maximum rating can be applied at any one time.

### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{\rm JC}$  is the junction to case bottom (channel to package bottom) thermal resistance.

#### Table 3. Thermal Resistance

| Package Type    | οισ | Unit |

|-----------------|-----|------|

| CC-24-4         |     |      |

| Through Path    | 400 | °C/W |

| Terminated Path | 160 | °C/W |

### **POWER DERATING CURVES**

Figure 2. Power Derating for Through Path and Hot Switching vs. Frequency,  $T_{CASE} = 85 \,^\circ \text{C}$

Figure 3. Power Derating for Terminated Path vs. Frequency,  $T_{CASE} = 85^{\circ}C$

### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

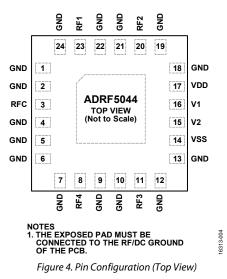

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

### Table 4. Pin Function Descriptions

| Din No.                                            | 1        |                                                                                                                                                                                                    |

|----------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.                                            | Mnemonic | Description                                                                                                                                                                                        |

| 1, 2, 4 to 7, 9, 10, 12,<br>13, 18, 19, 21, 22, 24 | GND      | Ground. These pins must be connected to the RF/dc ground of the PCB.                                                                                                                               |

| 3                                                  | RFC      | RF Common Port. This pin is dc-coupled and matched to $50 \Omega$ . A dc blocking capacitor is required if the RF line potential is not equal to 0 V dc. See Figure 5 for the interface schematic. |

| 8                                                  | RF4      | RF4 Port. This pin is dc-coupled and matched to 50 $\Omega$ . A dc blocking capacitor is required if the RF line potential is not equal to 0 V dc. See Figure 5 for the interface schematic.       |

| 11                                                 | RF3      | RF3 Port. This pin is dc-coupled and matched to 50 $\Omega$ . A dc blocking capacitor is required if the RF line potential is not equal to 0 V dc. See Figure 5 for the interface schematic.       |

| 14                                                 | VSS      | Negative Supply Voltage.                                                                                                                                                                           |

| 15                                                 | V2       | Control Input 2. See Table 5 for the control voltage truth table.                                                                                                                                  |

| 16                                                 | V1       | Control Input 1. See Table 5 for the control voltage truth table.                                                                                                                                  |

| 17                                                 | VDD      | Positive Supply Voltage.                                                                                                                                                                           |

| 20                                                 | RF2      | RF2 Port. This pin is dc-coupled and matched to 50 $\Omega$ . A dc blocking capacitor is required if the RF line potential is not equal to 0 V dc. See Figure 5 for the interface schematic.       |

| 23                                                 | RF1      | RF1 Port. This pin is dc-coupled and matched to 50 $\Omega$ . A dc blocking capacitor is required if the RF line potential is not equal to 0 V dc. See Figure 5 for the interface schematic.       |

|                                                    | EPAD     | Exposed Pad. The exposed pad must be connected to the RF/dc ground of the PCB.                                                                                                                     |

### **INTERFACE SCHEMATICS**

Figure 5. RFx Pins (RFC and RF1 to RF4) Interface Schematic

16313-005

Figure 6. Digital Pins (V1 and V2) Interface Schematic

# **TYPICAL PERFORMANCE CHARACTERISTICS**

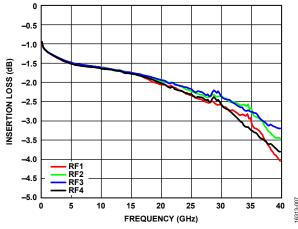

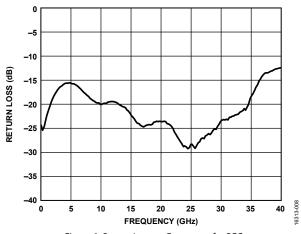

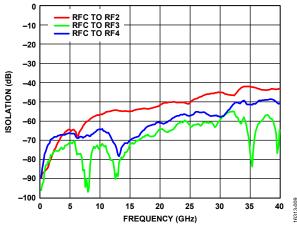

### INSERTION LOSS, RETURN LOSS, AND ISOLATION

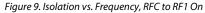

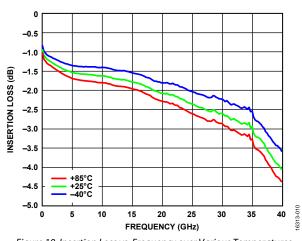

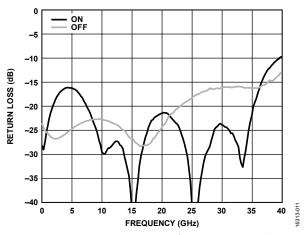

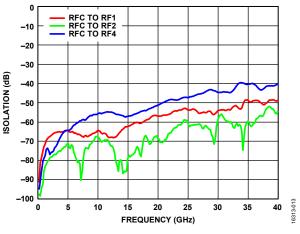

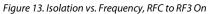

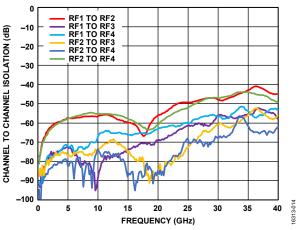

Insertion loss and return loss measured on the probe matrix board using ground signal ground (GSG) probes close to the RFx pins; isolation measured on the evaluation board because signal coupling between the probes limits the isolation performance of the ADRF5044 on the probe matrix board.

Figure 7. Insertion Loss vs. Frequency for RF1, RF2, RF3, and RF4

Figure 8. Return Loss vs. Frequency for RFC

Figure 10. Insertion Loss vs. Frequency over Various Temperatures Between RFC and RF1

Figure 11. Return Loss vs. Frequency for RF1, RF2, RF3, and RF4

Figure 12. Isolation vs. Frequency, RFC to RF2 On

Figure 14. Channel to Channel Isolation vs. Frequency, RFC to RF1 On

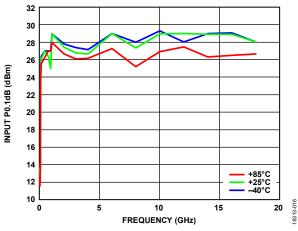

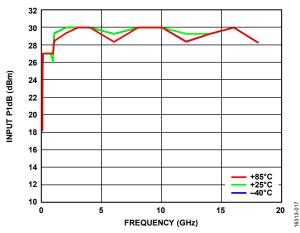

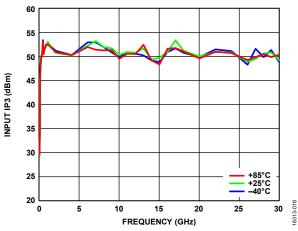

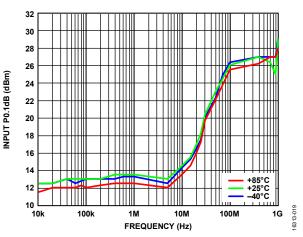

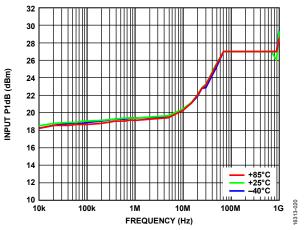

### INPUT 0.1 dB, 1 dB POWER COMPRESSION, AND THIRD-ORDER INTERCEPT

All large signal performance parameters were measured on the evaluation board.

Figure 16. Input 0.1 dB Power Compression (P0.1dB) vs. Frequency over Various Temperatures

Figure 17. Input 1 dB Power Compression (P1dB) vs. Frequency over Various Temperatures

Figure 18. Input IP3 vs. Frequency over Various Temperatures

Figure 19. Input 0.1 dB Power Compression (P0.1dB) vs. Frequency over Various Temperatures (Low Frequency Detail)

Figure 20. Input 1 dB Power Compression (P1dB) vs. Frequency over Various Temperatures (Low Frequency Detail)

Figure 21. Input IP3 vs. Frequency over Various Temperatures (Low Frequency Detail)

# **THEORY OF OPERATION**

The ADRF5044 requires a positive supply voltage applied to the VDD pin and a negative supply voltage applied to the VSS pin. Bypassing capacitors are recommended on the supply lines to minimize RF coupling.

The ADRF5044 incorporates a driver to perform logic functions internally and to provide the user with the advantage of a simplified control interface. The driver features two digital control input pins (V1 and V2) that control the state of the RF paths. Depending on the logic level applied to the V1 and V2 pins, one RF path is in an insertion loss state, while the other three paths are in an isolation state (see Table 5). The insertion loss path conducts the RF signal equally well in both directions between the RF throw port and the RF common port, and the isolation paths provides high loss between the RF throw ports terminated to internal 50  $\Omega$  resistors and the insertion loss path.

The ideal power-up sequence for the ADRF5044 is as follows:

- 1. Connect GND.

- 2. Power up VDD and VSS. Powering up VSS after VDD avoids current transients on VDD during ramp-up.

- 3. Apply digital control inputs, V1 and V2. Applying the digital control inputs before the VDD supply may inadvertently forward bias and damage the internal ESD protection structures. In this case, use a series 1 k $\Omega$  resistor to limit the current flowing in to the control pin. If the control pins are not driven to a valid logic state (for example, if the controller output is in a high impedance state) after VDD is powered up, it is recommended to use pull-up and pull-down resistors.

- 4. Apply an RF input signal. The design is bidirectional. The RF input signal can be applied to the RFC port, while the RF throw ports are outputs, or vice versa. The RF ports are dc-coupled to 0 V, and no dc blocking is required at the RF ports when the RF line potential is equal to 0 V.

The ideal power-down sequence is the reverse order of the power-up sequence.

| Digital Control Input |      | RF Paths            |                     |                     |                     |

|-----------------------|------|---------------------|---------------------|---------------------|---------------------|

| V1                    | V2   | RF1 to RFC          | RF2 to RFC          | RF3 to RFC          | RF4 to RFC          |

| Low                   | Low  | Insertion loss (on) | Isolation (off)     | Isolation (off)     | Isolation (off)     |

| High                  | Low  | Isolation (off)     | Insertion loss (on) | Isolation (off)     | Isolation (off)     |

| Low                   | High | Isolation (off)     | Isolation (off)     | Insertion loss (on) | Isolation (off)     |

| High                  | High | Isolation (off)     | Isolation (off)     | Isolation (off)     | Insertion loss (on) |

### Table 5. Control Voltage Truth Table

### APPLICATIONS INFORMATION evaluation board

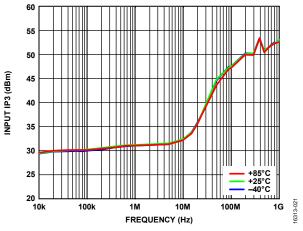

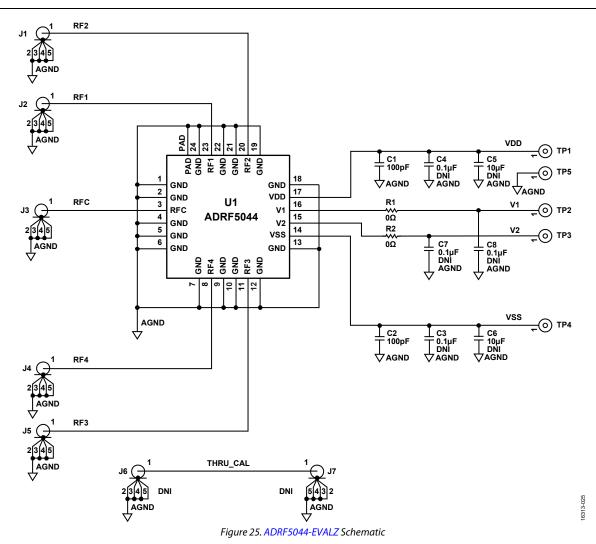

Figure 22 shows the top view of the ADRF5044-EVALZ, and Figure 23 shows the cross sectional view of the ADRF5044-EVALZ.

The ADRF5044-EVALZ is a 4-layer evaluation board. Each copper layer is 0.7 mil (0.5 oz) and separated by dielectric materials. All RF and dc traces are routed on the top copper layer, and the inner and bottom layers are grounded planes that provide a solid ground for the RF transmission lines. The top dielectric material is 8 mil Rogers RO4003, offering optimal high frequency performance. The middle and bottom dielectric materials provide mechanical strength. The overall board thickness is 62 mil, which allows 2.4 mm RF launchers to be connected at the board edges.

The RF transmission lines were designed using a coplanar waveguide (CPWG) model, with a trace width of 14 mil and a ground clearance of 5 mil, to have a characteristic impedance of 50  $\Omega$ . For optimal RF and thermal grounding, as many plated through vias as possible are arranged around the transmission lines and under the exposed pad of the package.

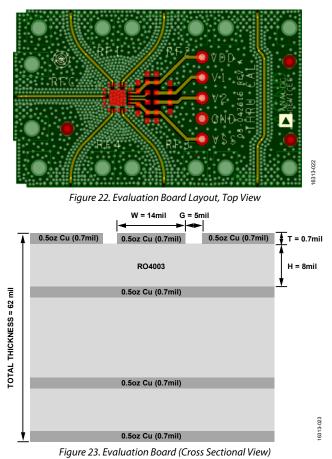

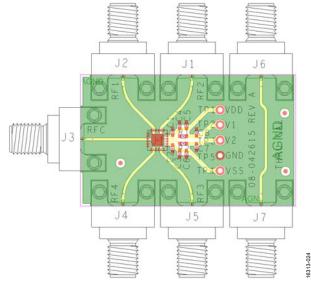

Figure 24 shows the actual ADRF5044 evaluation board with component placement. Two power supply ports are connected to the VDD and VSS test points (TP1 and TP4), control voltages are connected to the V1 and V2 test points (TP2 and TP3), and the ground reference is connected to the GND test point (TP5).

Figure 24. Evaluation Board Component Placement

On the control traces, V1 and V2, a 0  $\Omega$  resistor connects the test points to the pins on the ADRF5044. On the supply traces, VDD and VSS, a 100 pF bypass capacitor filters the high frequency noise. Additionally, unpopulated components positions are available for applying extra bypass capacitors.

The RF input and output ports (RFC, RF1, RF2, RF3, and RF4) are connected through 50  $\Omega$  transmission lines to the 2.4 mm RF launchers (J1 to J5). These high frequency RF launchers are by contact and not soldered onto the board. A thru calibration line connects the unpopulated J6 and J7 launchers; this transmission line is used to estimate the loss of the PCB over the environmental conditions being evaluated.

The schematic of the ADRF5044-EVALZ is shown in Figure 25.

### Table 6. Evaluation Board Components

| Component      | Default Value  | Description                                                   |

|----------------|----------------|---------------------------------------------------------------|

| C1, C2         | 100 pF         | Capacitors, C0402 package                                     |

| C5, C6         | 10 μF          | Capacitors C3216 package, do not install (DNI)                |

| C3, C4, C7, C8 | 0.1 μF         | Capacitors, C0402 package, DNI                                |

| J1 to J7       | Not applicable | 2.4 mm end launch connector (Southwest Microwave: 1492-04A-5) |

| R1, R2         | 0 Ω            | Resistors, 0402 package                                       |

| TP1 to TP5     | Not applicable | Through-hole mount test point                                 |

| U1             | ADRF5044       | ADRF5044 digital attenuator, Analog Devices, Inc.             |

| РСВ            | 08-042615-01   | Evaluation PCB, Analog Devices                                |

### **PROBE MATRIX BOARD**

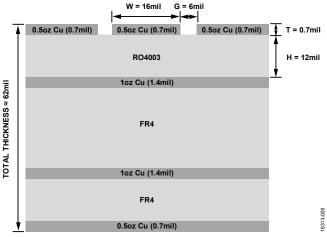

The probe matrix board is a 4-layer board that uses a 12 mil Rogers RO4003 as the top dielectric material. The external copper layer is 0.7 mil, and the internal copper layers are 1.4 mil. The RF transmission lines were designed using a CPWG model, with a 16 mil width and a ground spacing of 6 mil, to have a characteristic impedance of 50  $\Omega$ .

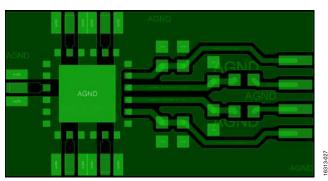

Figure 26 shows the cross sectional view of the probe matrix board, and Figure 27 shows the top view of the probe matrix board. Measurements were made using 535  $\mu$ m GSG probes at close proximity to the RFx pins. Unlike the ADRF5044-EVALZ, probing reduces reflections caused by mismatch arising from connectors, cables, and board layout, resulting in a more accurate measurement of the performance of the ADRF5044.

Figure 26. Probe Matrix Board (Cross Sectional View)

Figure 27. Probe Board Layout (Top View)

RF traces for a through reflect line (TRL) calibration are designed on the board itself. A nonzero line length compensates for board loss at calibration. The actual board duplicates the same layout in matrix form to assemble multiple devices at once. Insertion loss and input and output return losses were measured on this probe matrix board. Isolation performance measured on the probe matrix board is limited due to signal coupling between the RF probes that are in close proximity. Therefore, RF port to port isolation was measured on the ADRF5044-EVALZ.

# **ADRF5044**

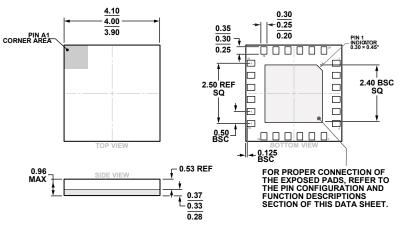

# **OUTLINE DIMENSIONS**

Figure 28. 24-Terminal Land Grid Array [LGA] (CC-24-4) Dimensions shown in millimeters

### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description               | Package Option |

|--------------------|-------------------|-----------------------------------|----------------|

| ADRF5044BCCZN      | -40°C to +85°C    | 24-Terminal Land Grid Array [LGA] | CC-24-4        |

| ADRF5044BCCZN-R7   | -40°C to +85°C    | 24-Terminal Land Grid Array [LGA] | CC-24-4        |

| ADRF5044-EVALZ     |                   | Evaluation Board                  |                |

<sup>1</sup> Z = RoHS Compliant Part.

©2017–2020 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D16313-3/20(A)

www.analog.com

Rev. A | Page 14 of 14

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for RF Development Tools category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below :

MAAM-011117 MAAP-015036-DIEEV2 EV1HMC1113LP5 EV1HMC6146BLC5A EV1HMC637ALP5 EVAL-ADG919EBZ ADL5363-EVALZ LMV228SDEVAL SKYA21001-EVB SMP1331-085-EVB EV1HMC618ALP3 EVAL01-HMC1041LC4 MAAL-011111-000SMB MAAM-009633-001SMB MASW-000936-001SMB 107712-HMC369LP3 107780-HMC322ALP4 SP000416870 EV1HMC470ALP3 EV1HMC520ALC4 EV1HMC244AG16 MAX2614EVKIT# 124694-HMC742ALP5 SC20ASATEA-8GB-STD MAX2837EVKIT+ MAX2612EVKIT# MAX2692EVKIT# EV1HMC629ALP4E SKY12343-364LF-EVB 108703-HMC452QS16G EV1HMC863ALC4 EV1HMC427ALP3E 119197-HMC658LP2 EV1HMC647ALP6 ADL5725-EVALZ 106815-HMC441LM1 EV1HMC1018ALP4 UXN14M9PE MAX2016EVKIT EV1HMC939ALP4 MAX2410EVKIT MAX2204EVKIT+ EV1HMC8073LP3D SIMSA868-DKL SIMSA868C-DKL SKY65806-636EK1 SKY68020-11EK1 SKY67159-396EK1 SKY66181-11-EK1 SKY65804-696EK1