# Low Frequency to 3 GHz, Dual VGA with **Output Common-Mode and DC Offset Control**

**ADRF6521 Data Sheet**

#### **FEATURES**

**Dual, matched VGAs**

Maximum voltage gain: 18 dB

Gain control attenuation range: 21 dB typical for  $T_A = 25^{\circ}C$

±1 dB gain flatness bandwidth: 2.5 GHz typical

IMD2 and IMD3 (1.5 V p-p output level)

-56.8 dBc typical and -75 dBc typical, respectively, at VGN =

1.5 V, 980 MHz and 1000 MHz tones

HD2 and HD3 (1.5 V p-p output level)

-75 dBc typical and -73.7 dBc typical, respectively, at VGN =

1.5 V, fundamental at 500 MHz

-55.9 dBc typical and -57.5 dBc typical, respectively, at

VGN = 1.5 V, fundamental at 1 GHz

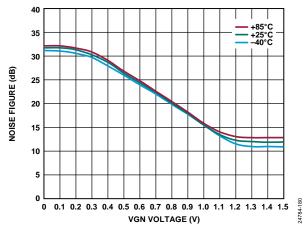

#### **Noise figure**

10.5 dB typical at maximum gain and at 500 MHz

14.8 dB at maximum gain and at 2 GHz

Noise figure decreases dB for dB with gain backoff

100 Ω differential input impedance

≤16 \(\Omega\) differential output impedance

**Programmable**

Output DC offset nominal range: ±400 mV

Output common-mode control:  $> \pm 200$  mV for VOCM =  $\pm 0.2$  V

Single- or dual-supply operation with power-down feature

Single supply: VPOS = 5 V, VNEG = 0 V (nominal)

Dual supply: VPOS = 3 V, VNEG = -2 V (nominal)

#### **APPLICATIONS**

Point-to-point and point-to-multipoint radios **Baseband IQ receivers Diversity receivers ADC drivers** Instrumentation Medical

#### **GENERAL DESCRIPTION**

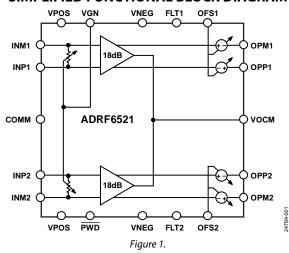

The ADRF6521 is a dual, fully differential, low noise and low distortion variable gain amplifier (VGA). The high spuriousfree dynamic range over the gain range makes the ADRF6521 ideal for communication systems with dense constellations, multiple carriers, and nearby interferers.

The VGA has a 21 dB attenuation range with a typical voltage gain of 18 dB. The differential input impedance is 100  $\Omega$ , while the differential output impedance is 16  $\Omega$ . The  $\pm 1$  dB gain flatness bandwidth is 2.5 GHz. The output buffers are capable of swinging 1.5 V p-p into 100  $\Omega$  loads at >55 dBc for second-order and third-order intermodulation distortion (IMD2 and IMD3), and

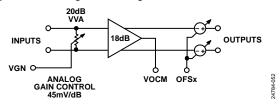

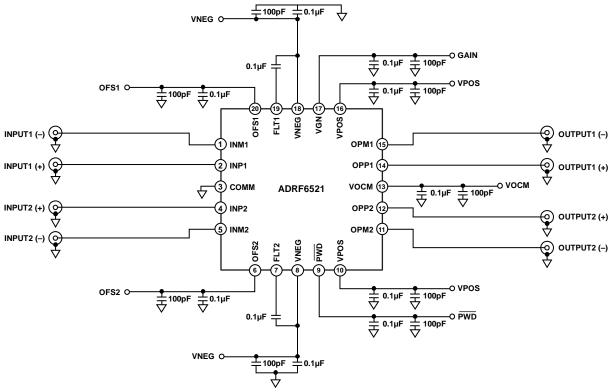

#### SIMPLIFIED FUNCTIONAL BLOCK DIAGRAM

for second and third harmonic distortion (HD2 and HD3) from low frequency to 1 GHz. Variable output dc offset control is accomplished with the OFS1 and OFS2 pins, and the output common-mode can be controlled with the VOCM pin.

The ADRF6521 flexibly operates from a single +5 V supply or from a range of dual supplies and consumes a total supply current of 200 mA. When fully disabled, it consumes 25 mA typical. The ADRF6521 is fabricated in an advanced silicongermanium BiCMOS process and is available in a 20-lead, exposed pad, 3 mm × 3 mm LFCSP. Performance is specified over the -40°C to +85°C temperature range.

## **TABLE OF CONTENTS**

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| Simplified Functional Block Diagram         | 1  |

| General Description                         | 1  |

| Revision History                            | 2  |

| Specifications                              | 3  |

| Absolute Maximum Ratings                    | 7  |

| Thermal Resistance                          | 7  |

| Electrostatic Discharge (ESD) Ratings       | 7  |

| ESD Caution                                 | 7  |

| Pin Configuration and Function Descriptions | 8  |

| Typical Performance Characteristics         | 9  |

| Single-Supply Operation                     | 9  |

| Dual-Supply Operation                       | 19 |

| Theory of Operation                         | 29 |

| Input VVAs                                  | 29 |

| Amplifiers                                  | 29 |

| Output Common-Mode Voltage                  | 29 |

| 29 |

|----|

| 30 |

| 30 |

| 31 |

| 31 |

| 31 |

| 31 |

| 31 |

| 32 |

| 32 |

| 32 |

| 32 |

| 32 |

| 32 |

| 33 |

| 33 |

|    |

### **REVISION HISTORY**

11/2020—Revision 0: Initial Version

## **SPECIFICATIONS**

For single-supply operation, VPOS = 5 V, VNEG = 0 V nominal, and VOCM = 2.5 V, and for dual-supply operation, VPOS = 3 V, VNEG = -2 V nominal, and VOCM = 0 V, unless otherwise noted.  $T_A$  = 25°C and load impedance ( $Z_{LOAD}$ ) = 186  $\Omega$ , unless otherwise noted. Voltages on VOCM, OFS1, and OFS2 are with respect to COMM (analog ground).

Table 1.

| Parameter                        | Test Conditions/Comments                                  | Min Typ                                    | Max  | Unit  |

|----------------------------------|-----------------------------------------------------------|--------------------------------------------|------|-------|

| FREQUENCY RESPONSE               | Single-supply operation                                   |                                            |      |       |

| ±1 dB Gain Flatness Bandwidth    | Channel 1 or 2, maximum gain                              | 2.5                                        |      | GHz   |

| –3 dB Bandwidth                  | Maximum gain                                              | 3.25                                       |      | GHz   |

| Pass-Band Flatness               | Defined as difference between value at 100 kHz and 1 GHz  | 0.5                                        |      | dB    |

| Gain Matching                    | Channel A and Channel B at same gain                      |                                            |      |       |

|                                  | Less than 1 GHz                                           | ±0.2                                       |      | dB    |

|                                  | Less than 3 GHz                                           | ±0.4                                       |      | dB    |

| Group Delay                      |                                                           |                                            |      |       |

| Variation                        | From 500 MHz to 1 GHz                                     | 0.1                                        |      | ns    |

| Matching                         | Frequency = 1 GHz                                         | ±25                                        |      | ps    |

|                                  | Frequency = 3 GHz                                         | ±40                                        |      | ps    |

| INPUT STAGE                      | INP1, INM1, INP2, INM2                                    |                                            |      |       |

| Maximum Input Swing              | At minimum gain, VGN = 0 V                                | 8                                          |      | V p-p |

| Differential Input Impedance     | •                                                         | 100                                        |      | Ω     |

| Input Common-Mode                | (VPOS + VNEG)/2, ac coupling recommended                  |                                            |      |       |

| •                                | VOCM undriven, single-supply operation                    | 2.5                                        |      | V     |

|                                  | VOCM undriven, dual-supply operation                      | 0.5                                        |      | V     |

| GAIN CONTROL                     | VGN (ground referenced)                                   |                                            |      |       |

| Voltage Range 1, 2               | Minimum                                                   | 0                                          |      | V     |

|                                  | Maximum                                                   | 1.5                                        |      | v     |

| Voltage Gain                     | VGN = 1.5 V, maximum gain                                 | 18                                         |      | dB    |

|                                  | VGN = 0 V, minimum gain                                   | -3                                         |      | dB    |

| Attenuation Range                | T <sub>A</sub> = 25°C                                     | 21                                         |      | dB    |

|                                  | -40°C ≤ T <sub>A</sub> ≤ +85°C                            | >20                                        |      | dB    |

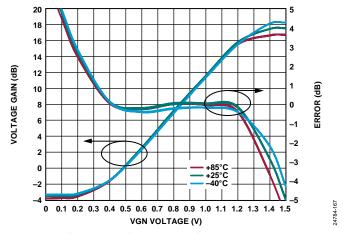

| Gain Slope                       |                                                           | 45                                         |      | mV/dB |

| Gain Error                       | VGN voltage (V <sub>VGN</sub> ) range = 500 mV to 1000 mV | 0.2                                        |      | dB    |

| VGA Step Response Time           | Through full attenuator range                             |                                            |      |       |

| Rise Time                        | From 10% to 90% of output                                 | 240                                        |      | ns    |

| Fall Time                        | From 90% to 10% of output                                 | 250                                        |      | ns    |

| COMMON-MODE CONTROL <sup>3</sup> | VOCM (VPOS and VNEG supply referenced)                    |                                            |      |       |

| Default Value                    | VOCM floating (nominal)                                   | (V <sub>VPOS</sub> + V <sub>VNE</sub>      | s)/2 | V     |

| Voltage Range <sup>1</sup>       | Minimum                                                   | (V <sub>VPOS</sub> + V <sub>VNEO</sub>     | •    | V     |

|                                  | Maximum                                                   | (V <sub>VPOS</sub> + V <sub>VNEO</sub> + 1 | 5)/2 | V     |

| Output Common Mode <sup>4</sup>  | $(V_{OPP1} + V_{OPM1})/2$ or $(V_{OPP2} + V_{OPM2})/2$    |                                            |      |       |

| ·                                | VOCM = 0 V                                                | 0                                          |      | V     |

|                                  | VOCM = 0.2 V                                              | 200                                        |      | mV    |

|                                  | VOCM = -0.2 V                                             | -200                                       |      | mV    |

|                                  | VOCM = ±0.3 V, functional maximum                         | ±300                                       |      | mV    |

| DC OFFSET CONTROL                | OFS1 and OFS2 (ground referenced)                         |                                            |      |       |

| Voltage Range <sup>1, 2</sup>    | Minimum                                                   | 0                                          |      | V     |

| 5 5 .                            | Maximum                                                   | 1.5                                        |      | V     |

| Parameter                                | Test Conditions/Comments                                                         | Min Typ      | Max Uni |

|------------------------------------------|----------------------------------------------------------------------------------|--------------|---------|

| Output DC Offset                         | $(V_{OPP1} - V_{OPM1})$ or $(V_{OPP2} - V_{OPM2})$                               |              |         |

|                                          | OFS1 and OFS2 = 0.75 V (nominal)                                                 | <20          | mV      |

|                                          | OFS1 and OFS2 = 1.2 V                                                            | 400          | mV      |

|                                          | OFS1 and OFS2 = 0.3 V                                                            | -400         | mV      |

|                                          | OFS1 and OFS2 = 0 V                                                              | -600         | mV      |

|                                          | OFS1 and OFS2 = 1.5 V                                                            | 600          | mV      |

| DC Offset Channel to Channel<br>Mismatch | OFS1 and OFS2 = 0.75 V                                                           | 6.2          | mV      |

| OUTPUT STAGE                             | OPP1, OPM1, OPP2, and OPM2                                                       |              |         |

| Maximum Output Swing                     | At maximum gain, load resistance ( $R_{LOAD}$ ) = 186 $\Omega$                   | 5.64         | Vp      |

|                                          | IMD2, IMD3, HD2, and HD3 are $>$ 55 dBc at a 100 $\Omega$ interface <sup>5</sup> | 1.5          | Vp      |

| Output 1 dB Compression Point (OP1dB)    | Frequency = 1 GHz, gain = 18 dB, $R_{LOAD}$ = 186 $\Omega$                       | >6           | dB\     |

|                                          | At 100 Ω interface <sup>5</sup>                                                  | > 0.6        | dB\     |

| Differential Output Impedance            |                                                                                  | ≤16          | Ω       |

| NOISE AND DISTORTION                     |                                                                                  |              |         |

| Single-Supply Operation                  |                                                                                  |              |         |

| Output Noise Density                     | Input impedance $(Z_{IN}) = 100 \Omega$ at $100 \Omega$ interface <sup>5</sup>   |              |         |

|                                          | VGN = 1.5 V at 500 MHz                                                           | -159.9       | dB\     |

|                                          | VGN = 0.75 V at 500 MHz                                                          | -161         | dB\     |

|                                          | VGN = 0 V at 500 MHz                                                             | -161.5       | dB\     |

|                                          | VGN = 1.5 V at 2 GHz                                                             | -155         | dB\     |

|                                          | VGN = 0.75 V at 2 GHz                                                            | -157         | dB\     |

|                                          | VGN = 0 V at 2 GHz                                                               | -157.4       | dB\     |

| Noise Figure                             |                                                                                  |              |         |

| _                                        | VGN = 1.5 V at 500 MHz                                                           | 12.3         | dB      |

|                                          | VGN = 0.75 V at 500 MHz                                                          | 21.5         | dB      |

|                                          | VGN = 0 V at 500 MHz                                                             | 31.5         | dB      |

|                                          | VGN = 1.5 V at 2 GHz                                                             | 16.3         | dB      |

|                                          | VGN = 0.75 V at 2 GHz                                                            | 24.5         | dB      |

|                                          | VGN = 0 V at 2 GHz                                                               | 34.3         | dB      |

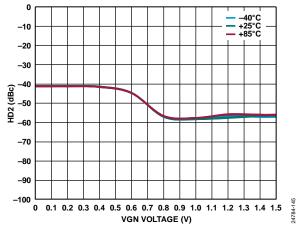

| Second Harmonic Distortion, HD2          | 1.5 V p-p output level                                                           |              |         |

| ,                                        | VGN = 1.5 V, fundamental at 500 MHz                                              | <b>–75</b>   | dBo     |

|                                          | VGN = 0.75 V, fundamental at 500 MHz                                             | <b>–76</b>   | dBo     |

|                                          | VGN = 0 V, fundamental at 500 MHz                                                | _77          | dBo     |

|                                          | VGN = 1.5 V, fundamental at 1 GHz                                                | -55.9        | dBo     |

|                                          | VGN = 0.75 V, fundamental at 1 GHz                                               | -54          | dBo     |

|                                          | VGN = 0 V, fundamental at 1 GHz                                                  | -41          | dBo     |

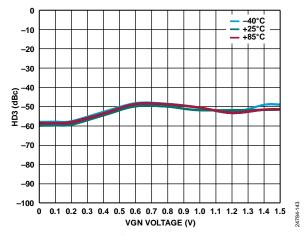

| Third Harmonic Distortion, HD3           | 1.5 V p-p output level                                                           |              | abo     |

| Tillia Harmonic Distortion, 1103         | VGN = 1.5 V, fundamental at 500 MHz                                              | -73.7        | dBo     |

|                                          | VGN = 0.75 V, fundamental at 500 MHz                                             | -72          | dBo     |

|                                          | VGN = 0 V, fundamental at 500 MHz                                                | -72.6        | dBo     |

|                                          | VGN = 1.5 V, fundamental at 1 GHz                                                | -57.5        | dBo     |

|                                          | VGN = 0.75 V, fundamental at 1 GHz                                               | -57.5<br>-68 | dBo     |

|                                          |                                                                                  |              |         |

| IMD2                                     | VGN = 0 V, fundamental at 1 GHz<br>1.5 V p-p output level                        | -62          | dBo     |

|                                          | VGN = 1.5 V, 480 MHz and 500 MHz tones                                           | -74          | dBo     |

|                                          | VGN = 1.5 V, 480 MHz and 500 MHz tones                                           | -/4<br>-62   | dBo     |

|                                          |                                                                                  | -62<br>-53   |         |

|                                          | VGN = 0 V, 480 MHz and 500 MHz tones                                             |              | dBo     |

|                                          | VGN = 1.5 V, 980 MHz and 1000 MHz tones                                          | -56.8        | dBo     |

|                                          | VGN = 0.75 V, 980 MHz and 1000 MHz tones                                         | -54<br>45    | dBo     |

|                                          | VGN = 0 V, 980 MHz and 1000 MHz tones                                            | -45          | dBo     |

| Parameter                                    | Test Conditions/Comments                                     | Min Typ    | Max Un   |

|----------------------------------------------|--------------------------------------------------------------|------------|----------|

| IMD3                                         | 1.5 V p-p output level                                       |            |          |

|                                              | VGN = 1.5 V, 480 MHz and 500 MHz tones                       | -74        | dBo      |

|                                              | VGN = 0.75 V, 480 MHz and 500 MHz tones                      | <b>–77</b> | dBo      |

|                                              | VGN = 0 V, 480 MHz and 500 MHz tones                         | -73        | dBo      |

|                                              | VGN = 1.5 V, 980 MHz and 1000 MHz tones                      | -75        | dBo      |

|                                              | VGN = 0.75 V, 980 MHz and 1000 MHz tones                     | -82        | dBo      |

|                                              | VGN = 0 V, 980 MHz and 1000 MHz tones                        | -76        | dBo      |

| Input Second-Order Intercept<br>Point (IIP2) |                                                              |            |          |

|                                              | VGN = 1.5 V, 480 MHz and 500 MHz tones                       | 44.9       | dB\      |

|                                              | VGN = 0.75 V, 480 MHz and 500 MHz tones                      | 44.5       | dB\      |

|                                              | VGN = 0 V, 480 MHz and 500 MHz tones                         | 45         | dB\      |

|                                              | VGN = 1.5 V, 980 MHz and 1000 MHz tones                      | 27.5       | dB\      |

|                                              | VGN = 0.75 V, 980 MHz and 1000 MHz tones                     | 36.3       | dB\      |

|                                              | VGN = 0 V, 980 MHz and 1000 MHz tones                        | 36.7       | dB\      |

| Input Third-Order Intercept Point (IIP3)     |                                                              |            |          |

|                                              | VGN = 1.5 V, 480 MHz and 500 MHz tones                       | 7.9        | dB\      |

|                                              | VGN = 0.75 V, 480 MHz and 500 MHz tones                      | 20.1       | dB\      |

|                                              | VGN = 0 V, 480 MHz and 500 MHz tones                         | 28.5       | dB\      |

|                                              | VGN = 1.5 V, 980 MHz and 1000 MHz tones                      | 8.2        | dB\      |

|                                              | VGN = 0.75 V, 980 MHz and 1000 MHz tones                     | 23.3       | dB\      |

|                                              | VGN = 0 V, 980 MHz and 1000 MHz tones                        | 29.7       | dB\      |

| Dual-Supply Operation                        |                                                              |            |          |

| Output Noise Density                         | $Z_{IN} = 100 \Omega$ at $100 \Omega$ interface <sup>5</sup> |            |          |

| output Hoise Bensity                         | VGN = 1.5 V at 500 MHz                                       | -161.7     | dB\      |

|                                              | VGN = 0.75 V at 500 MHz                                      | -162.2     | dB\      |

|                                              | VGN = 0 V at 500 MHz                                         | -162.1     | dB\      |

|                                              | VGN = 1.5 V at 2 GHz                                         | -158.2     | dB\      |

|                                              | VGN = 0.75 V at 2 GHz                                        | -158.4     | dB\      |

|                                              | VGN = 0.73 V at 2 GHz                                        | -158.7     | dB\      |

| Noise Figure                                 | VGIV = 0 V at 2 GI I2                                        | -136.7     | l db     |

| Noise rigule                                 | VGN = 1.5 V at 500 MHz                                       | 10.5       | dB       |

|                                              | VGN = 0.75 V at 500 MHz                                      | 20         | dB       |

|                                              | VGN = 0.73 V at 300 MHz                                      | 31.3       | dB       |

|                                              | VGN = 1.5 V at 2 GHz                                         |            |          |

|                                              |                                                              | 14.8       | dB<br>dB |

|                                              | VGN = 0.75 V at 2 GHz                                        | 24.5       |          |

| LIDO                                         | VGN = 0 V at 2 GHz                                           | 34.4       | dB       |

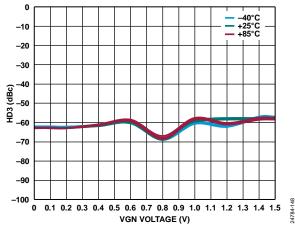

| HD2                                          | 1.5 V p-p output level                                       |            | lo.      |

|                                              | VGN = 1.5 V, fundamental at 500 MHz                          | -79        | dBo      |

|                                              | VGN = 0.75 V, fundamental at 500 MHz                         | -93<br>-70 | dBo      |

|                                              | VGN = 0 V, fundamental at 500 MHz                            | -79<br>50  | dBo      |

|                                              | VGN = 1.5 V, fundamental at 1 GHz                            | -59<br>53  | dBo      |

|                                              | VGN = 0.75 V, fundamental at 1 GHz                           | -53        | dBo      |

| UDO                                          | VGN = 0 V, fundamental at 1 GHz                              | -40.5      | dBo      |

| HD3                                          | 1.5 V p-p output level                                       |            |          |

|                                              | VGN = 1.5 V, fundamental at 500 MHz                          | -72<br>    | dBo      |

|                                              | VGN = 0.75 V, fundamental at 500 MHz                         | <b>–75</b> | dBo      |

|                                              | VGN = 0 V, fundamental at 500 MHz                            | -72        | dBo      |

|                                              | VGN = 1.5 V, fundamental at 1 GHz                            | -57        | dBo      |

|                                              | VGN = 0.75 V, fundamental at 1 GHz                           | -70        | dBo      |

|                                              | VGN = 0 V, fundamental at 1 GHz                              | -62.5      | dBo      |

| Parameter             | Test Conditions/Comments                   | Min Typ                  | Max Uni |

|-----------------------|--------------------------------------------|--------------------------|---------|

| IMD2                  | 1.5 V p-p output level                     |                          |         |

|                       | VGN = 1.5 V, 480 MHz and 500 MHz tones     | -74                      | dBo     |

|                       | VGN = 0.75 V, 480 MHz and 500 MHz tones    | -60.9                    | dBo     |

|                       | VGN = 0 V, 480 MHz and 500 MHz tones       | -53                      | dBo     |

|                       | VGN = 1.5 V, 980 MHz and 1000 MHz tones    | -58                      | dBo     |

|                       | VGN = 0.75 V, 980 MHz and 1000 MHz tones   | <b>–</b> 55              | dBo     |

|                       | VGN = 0 V, 980 MHz and 1000 MHz tones      | -46                      | dBo     |

| IMD3                  | 1.5 V p-p output level                     |                          |         |

|                       | VGN = 1.5 V, 480 MHz and 500 MHz tones     | -80                      | dBo     |

|                       | VGN = 0.75 V, 480 MHz and 500 MHz tones    | -86                      | dBo     |

|                       | VGN = 0 V, 480 MHz and 500 MHz tones       | -73.5                    | dBo     |

|                       | VGN = 1.5 V, 980 MHz and 1000 MHz tones    | -71.6                    | dBo     |

|                       | VGN = 0.75 V, 980 MHz and 1000 MHz tones   | -87                      | dBo     |

|                       | VGN = 0 V, 980 MHz and 1000 MHz tones      | -76                      | dBo     |

| IIP2                  |                                            |                          |         |

|                       | VGN = 1.5 V, 480 MHz and 500 MHz tones     | 44.9                     | dBV     |

|                       | VGN = 0.75 V, 480 MHz and 500 MHz tones    | 43.4                     | dBV     |

|                       | VGN = 0 V, 480 MHz and 500 MHz tones       | 45                       | dBV     |

|                       | VGN = 1.5 V, 980 MHz and 1000 MHz tones    | 28.7                     | dBV     |

|                       | VGN = 0.75 V, 980 MHz and 1000 MHz tones   | 37.3                     | dBV     |

|                       | VGN = 0 V, 980 MHz and 1000 MHz tones      | 37.7                     | dBV     |

| IIP3                  |                                            |                          |         |

|                       | VGN = 1.5 V, 480 MHz and 500 MHz tones     | 10.9                     | dBV     |

|                       | VGN = 0.75 V, 480 MHz and 500 MHz tones    | 25.5                     | dBV     |

|                       | VGN = 0 V, 480 MHz and 500 MHz tones       | 28.7                     | dBV     |

|                       | VGN = 1.5 V, 980 MHz and 1000 MHz tones    | 6.5                      | dBV     |

|                       | VGN = 0.75 V, 980 MHz and 1000 MHz tones   | 25.8                     | dBV     |

|                       | VGN = 0 V, 980 MHz and 1000 MHz tones      | 29.7                     | dBV     |

| POWER AND ENABLE      | VPOS, VNEG, COMM, and PWD                  |                          |         |

| Supply Voltage Range  | VPOS > COMM ≥ VNEG                         |                          |         |

| VPOS – VNEG           | Minimum                                    | 4                        | V       |

|                       | Maximum                                    | 5                        | V       |

| VPOS                  | Minimum                                    | 2.5                      | V       |

|                       | Maximum                                    | 5                        | V       |

| VNEG                  | Minimum                                    | -2.5                     | V       |

|                       | Maximum                                    | 0                        | V       |

| Total Supply Current  | PWD high voltage                           | 200                      | mA      |

| Disable Current       | PWD = VNEG                                 | 25                       | mA      |

| PWD Voltage Range     | Minimum                                    | VNEG                     | V       |

| voltage narige        | Maximum                                    | VNEG + 3.3               | V       |

| Enable Threshold      | IVIAAIITIUITI                              | VNEG + 3.3<br>VNEG + 2.7 | V       |

| Disable Threshold     |                                            | VNEG + 0.3               | V       |

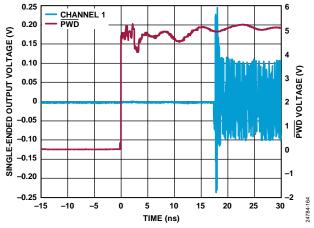

| Enable Response Time  | Delay following PWD low to high transition |                          |         |

|                       |                                            | <20                      | ns      |

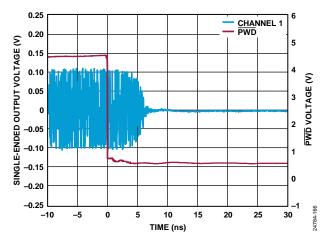

| Disable Response Time | Delay following PWD high to low transition | <8                       | ns      |

<sup>&</sup>lt;sup>1</sup>Voltages beyond this range, but below the absolute maximum ratings, may cause latch-up problems. <sup>2</sup>The voltage range is the functional range of the pin.

$<sup>^3</sup>$   $\ensuremath{V_{VPOS}}$  is the VPOS voltage, and  $\ensuremath{V_{VNEG}}$  is the VNEG voltage.

$<sup>^{4}</sup>$ V<sub>OPP1</sub> is the OPP1 voltage, V<sub>OPM1</sub> is the OPM1 voltage, V<sub>OPP2</sub> is the OPP2 voltage, and V<sub>OPM2</sub> is the OPM2 voltage.  $^{5}$ Voltage levels at the interface are between the 43  $\Omega$  back termination resistors and 100  $\Omega$  differential load. This interface is -5.4 dB lower in voltage level than the output of the ADRF6521.  $^6$ X dBV =  $20 \times log10$ (x V rms/1 V rms). 0 dBV is equivalent to 1 V rms.

## **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| 14010 21                     |                 |

|------------------------------|-----------------|

| Parameter                    | Rating          |

| Supply Voltages: VPOS – VNEG | 5.25 V          |

| PWD                          | VNEG + 3.3 V    |

| INP1, INM1, INP2, and INM2   | VPOS + 0.5 V    |

| OPP1, OPM1, OPP2, and OPM2   | VPOS + 0.5 V    |

| OFS1, OFS2                   | VPOS + 0.5 V    |

| VOCM                         | VPOS + 0.5 V    |

| VGN                          | VPOS + 0.5 V    |

| Internal Power Dissipation   | 1.53 W          |

| Temperature                  |                 |

| Maximum Junction             | 125°C           |

| Operating Range              | -40°C to +85°C  |

| Storage Range                | −65°C to +150°C |

| Lead (Soldering 60 sec)      | 300°C           |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

**Table 3. Thermal Resistance**

| Package Type | $\theta_{JA}^{1}$ | $\theta_{JC}^2$ | Unit |

|--------------|-------------------|-----------------|------|

| CP-20-19     | 62.25             | 52.8            | °C/W |

<sup>&</sup>lt;sup>1</sup> Based on simulation with JEDEC Standard JESD-51, using a 2S2P board.

#### **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

Field induced charged device model (FICDM) per ANSI/ESDA/JEDEC JS-002.

#### **ESD Ratings for ADRF6521**

Table 4. ADRF6521, 20-Lead LFCSP

| ESD Model Withstand Threshold (V) |       | Class |

|-----------------------------------|-------|-------|

| НВМ                               | ±1000 | 1B    |

| FICDM                             | ±1250 | 4     |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> Based on simulation with JEDEC Standard JESD-51, using a 1S0P board.

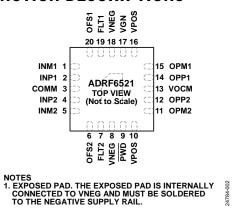

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 5. Pin Function Descriptions**

| Pin No. | Mnemonic   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2    | INM1, INP1 | Channel 1 Differential Inputs, $100 \Omega$ Differential Input Impedance. (VPOS + VNEG)/2 nominal common mode.                                                                                                                                                                                                                                                                                                                                                                     |

| 3       | COMM       | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4, 5    | INP2, INM2 | Channel 2 Differential Inputs, $100 \Omega$ Differential Input Impedance. (VPOS + VNEG)/2 nominal common mode.                                                                                                                                                                                                                                                                                                                                                                     |

| 6       | OFS2       | Channel 2 Output DC Offset Control. Nominal control range from 0.3 V to 1.2 V relative to analog ground. A 0.75 V on OFSx produces a 0 V output offset voltage. OFS2 is not self biased. OFS2 must be driven. Left unconnected, OFS2 is pulled to ground via an on-chip 5 k $\Omega$ resistor, which forces the output dc offset to be $-700$ mV. Voltages greater than 1.5 V but less than the absolute maximum ratings may cause latch-up.                                       |

| 7       | FLT2       | Channel 2 Filter Pin. Connect FLT2 to the negative supply via a 1 µF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8, 18   | VNEG       | Analog Negative Supply Voltage. For single-supply operation, set VNEG to 0 V nominal, and for dual-supply operation, set VNEG to $-2$ V nominal. Keep (VPOS $-$ VNEG) $\le 5$ V, VNEG $\le$ COMM $\le$ VPOS, and $-2.5$ V $\le$ VNEG $\le 0$ V to keep the voltage at the allowable pin voltage related to the voltage on the VPOS pin. Pins are electrically connected on chip and to the exposed pad. Connect both VNEG pins and the exposed pad to the negative supply voltage. |

| 9       | PWD        | Chip Power Down. Pull to VNEG supply to disable both channels. Leave unconnected to enable. Keep V <sub>PWD</sub> ≤                                                                                                                                                                                                                                                                                                                                                                |

|         |            | (VNEG + 3.3 V).                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10, 16  | VPOS       | Analog Positive Supply Voltage. For single-supply operation, set VPOS to 5 V nominal, and for dual-supply operation, set VPOS to 3 V nominal. Keep (VPOS – VNEG) $\leq$ 5 V, VNEG $\leq$ COMM $\leq$ VPOS, and VPOS $\geq$ 2.3 V to keep the voltage at the allowable pin voltage related to the voltage on the VNEG pin. Pins are electrically connected on chip. Connect both VPOS pins to the positive supply voltage.                                                          |

| 11, 12  | OPM2, OPP2 | Channel 2 Differential Outputs. These outputs have a 16 $\Omega$ differential output impedance.                                                                                                                                                                                                                                                                                                                                                                                    |

| 13      | VOCM       | Output Common-Mode Voltage Control. The nominal control range is $(VPOS + VNEG)/2 - 200 \text{ mV}$ to $(VPOS + VNEG)/2 + 200 \text{ mV}$ . A 0 V on VOCM is a 0 V output common-mode voltage. Self biased to $(VPOS + VNEG)/2$ . Voltages greater than $(V_{VPOS} + V_{VNEG})/2 \pm 1 \text{ V}$ but less than the absolute maximum ratings may cause latch-up.                                                                                                                   |

| 14, 15  | OPP1, OPM1 | Channel 2 Differential Outputs. These outputs have a 16 $\Omega$ differential output impedance.                                                                                                                                                                                                                                                                                                                                                                                    |

| 17      | VGN        | VGA Analog Gain Control. The VGN pins operate from 0 V to 1.5 V with 45 mV/dB gain scaling. Voltages greater than 1.5 V but less than the absolute maximum ratings may cause latch-up.                                                                                                                                                                                                                                                                                             |

| 19      | FLT1       | Channel 1 Filter Pin. Connect FLT1 to a negative supply via a 1 µF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 20      | OFS1       | Channel 1 Output DC Offset Control. Nominal control range from 0.3 V to 1.2 V relative to analog ground. A 0.75 V on OFSx produces a 0 V output offset voltage. OFS1 is not self biased. OFS1 must be driven. Left unconnected, OFS1 is pulled to ground via an on-chip 5 k $\Omega$ resistor, which forces the output dc offset to be $-700$ mV.                                                                                                                                  |

| EP      |            | Exposed Pad. The exposed pad is internally connected to VNEG and must be soldered to the negative supply rail.                                                                                                                                                                                                                                                                                                                                                                     |

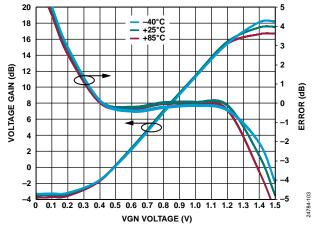

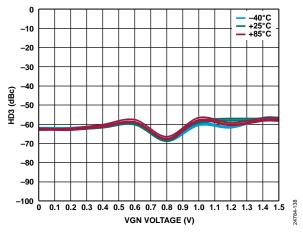

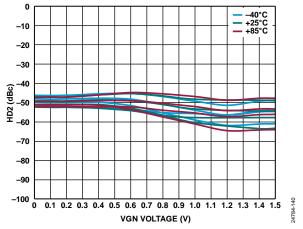

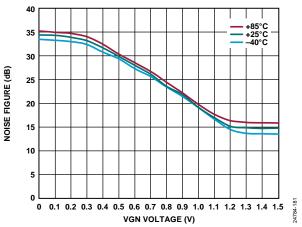

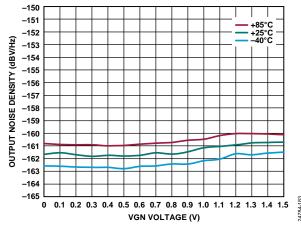

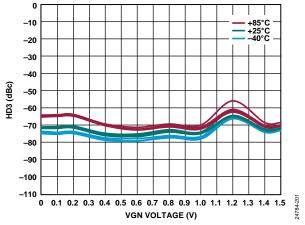

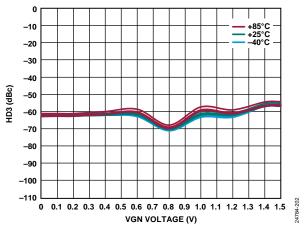

# TYPICAL PERFORMANCE CHARACTERISTICS SINGLE-SUPPLY OPERATION

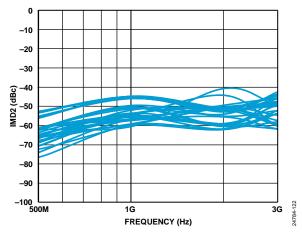

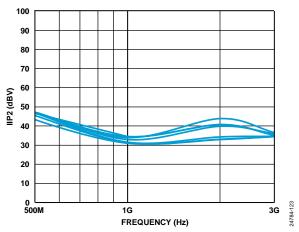

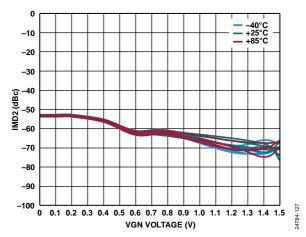

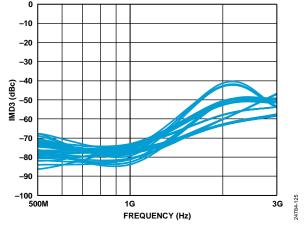

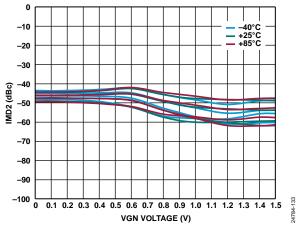

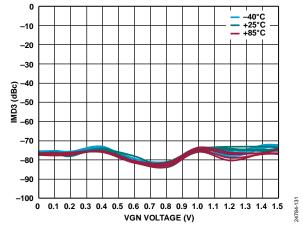

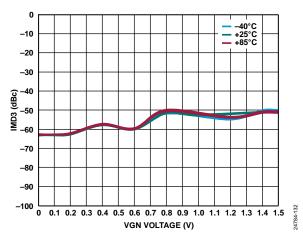

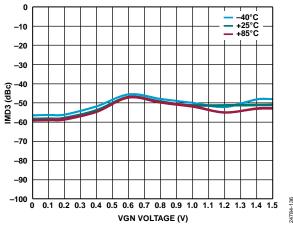

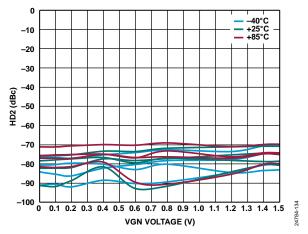

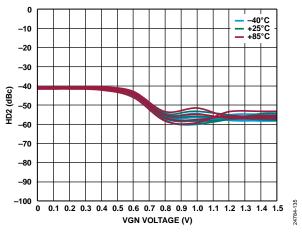

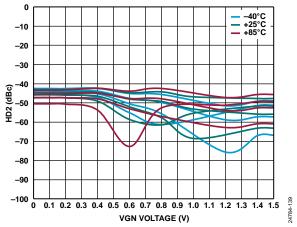

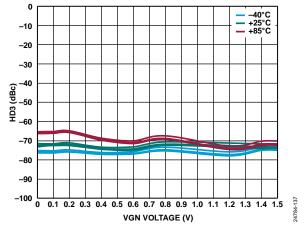

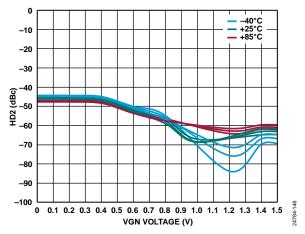

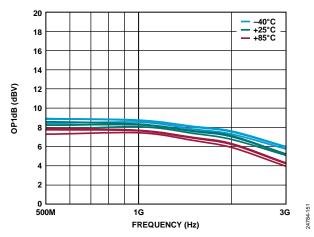

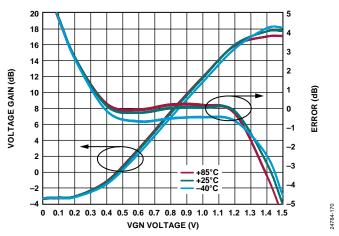

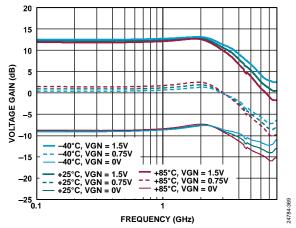

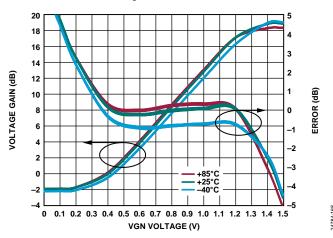

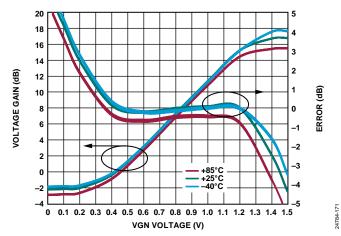

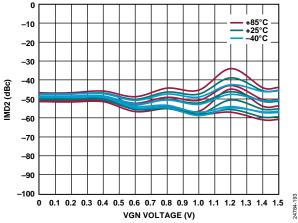

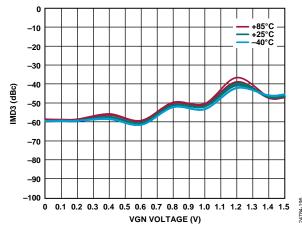

VPOS = 5 V, VNEG = 0 V,  $T_A$  = 25°C,  $Z_{LOAD}$  = 186 Ω, VGN = 1.5 V, VOCM = 2.5 V, OFS1 = OFS2 = 0.75 V, output level = 1.5 V p-p, and 43 Ω back termination resistors de-embedded, unless otherwise noted. Noise figure measured with 100 Ω differential input termination. Worst case IMD2 and IMD3 tone reported.  $V_{OFSx}$  sweeps = 0 V, 0.4 V, 0.75 V, or 1.2 V. VOCM sweeps = 2.4 V, 2.5 V, or 2.6 V.

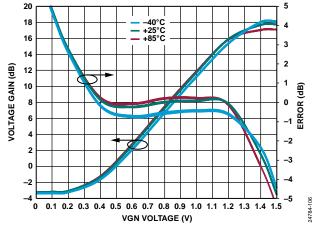

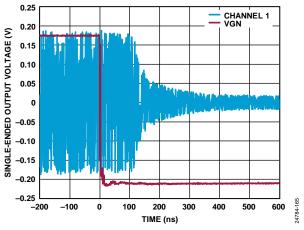

Figure 3. Voltage Gain and Error vs. VGN Voltage over Temperature at 500 MHz

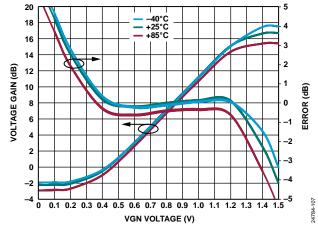

Figure 4. Voltage Gain and Error vs. VGN Voltage over Temperature at 2 GHz

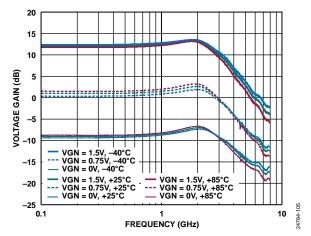

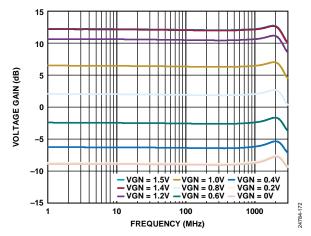

Figure 5. Voltage Gain vs. Frequency over Temperature and VGN, 43  $\Omega$  Back Terminations not De-Embedded

Figure 6. Voltage Gain and Error vs. VGN Voltage over Temperature at 1 GHz

Figure 7. Voltage Gain and Error vs. VGN Voltage over Temperature at 3 GHz

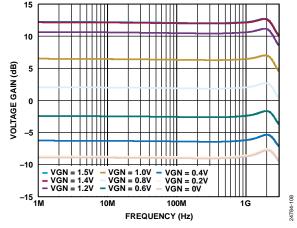

Figure 8. Voltage Gain vs. Frequency over 200 mV VGN Steps, 43  $\Omega$  Back Terminations not De-Embedded

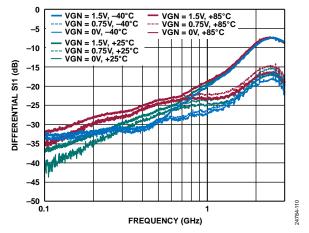

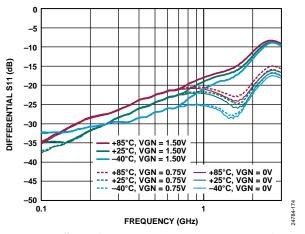

Figure 9. Differential Input Return Loss (S11) vs. Frequency over Temperature and VGN

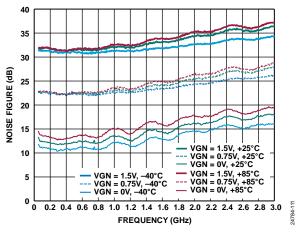

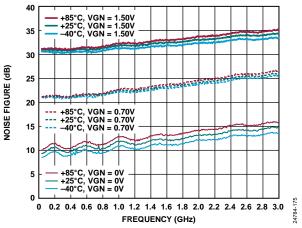

Figure 10. Noise Figure vs. Frequency over Temperature and VGN

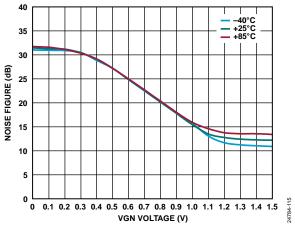

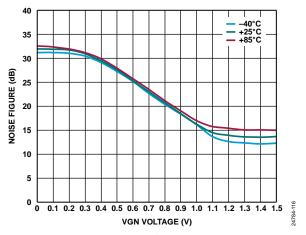

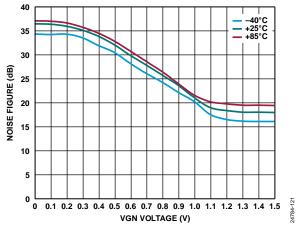

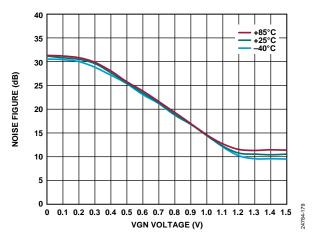

Figure 11. Noise Figure vs. VGN Voltage over Temperature at 500 MHz

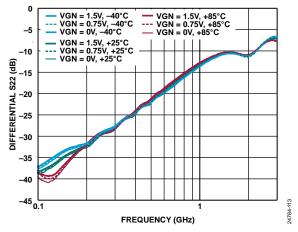

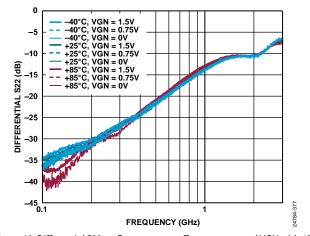

Figure 12. Differential Output Return Loss (S22) vs. Frequency over Temperature and VGN

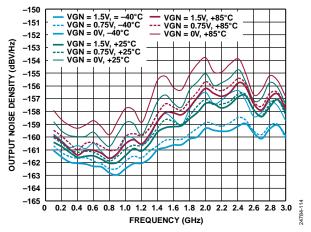

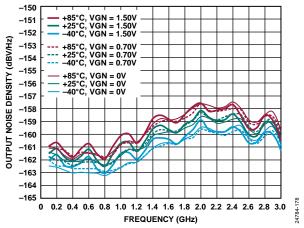

Figure 13. Output Noise Density vs. Frequency over Temperature and VGN

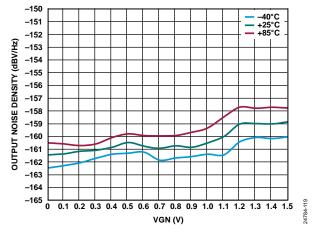

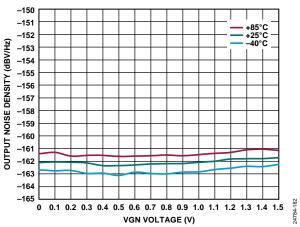

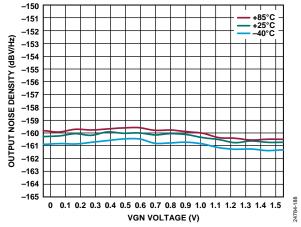

Figure 14. Output Noise Density vs. VGN over Temperature at 500 MHz

Figure 15. Noise Figure vs. VGN Voltage over Temperature, at 1 GHz

Figure 16. Noise Figure vs. VGN Voltage over Temperature, at 2 GHz

Figure 17. Noise Figure vs. VGN Voltage over Temperature at 3 GHz

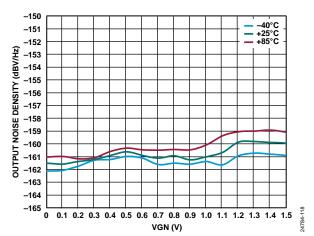

Figure 18. Output Noise Density vs. VGN over Temperature at 1 GHz

Figure 19. Output Noise Density vs. VGN over Temperature at 2 GHz

Figure 20. Output Noise Density vs. VGN over Temperature at 3 GHz

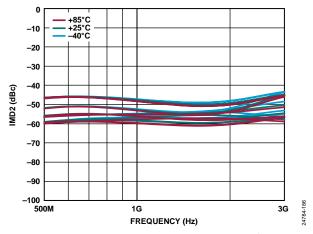

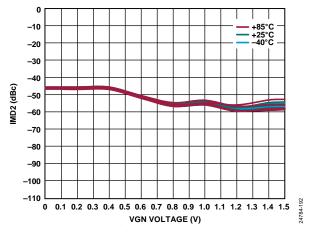

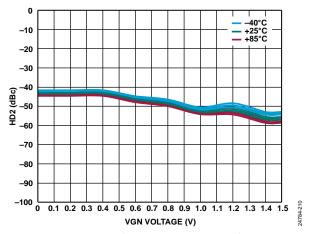

Figure 21. IMD2 vs. Frequency over VGN and OFSx

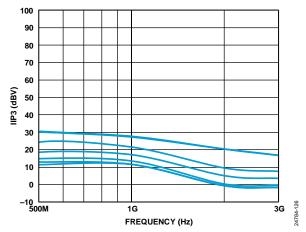

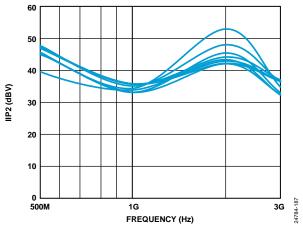

Figure 22. IIP2 vs. Frequency over VGN

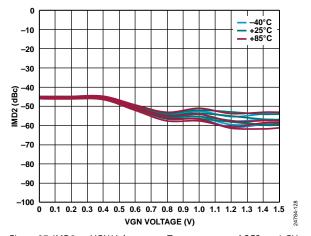

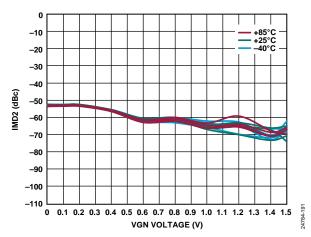

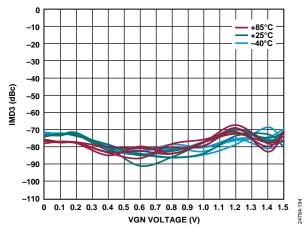

Figure 23. IMD2 vs. VGN Voltage over Temperature and OFSx at 500 MHz

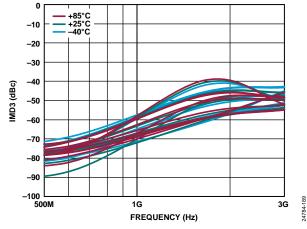

Figure 24. IMD3 vs. Frequency over VGN and OFSx

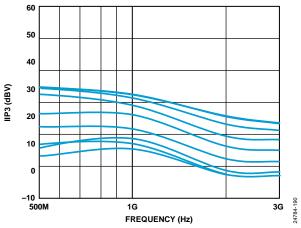

Figure 25. IIP3 vs. Frequency over VGN

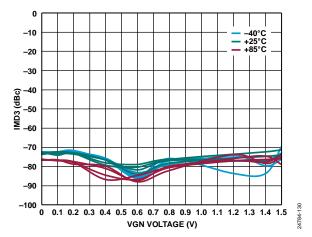

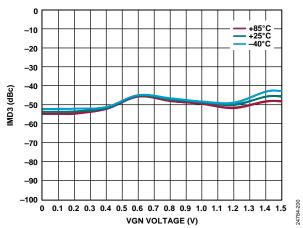

Figure 26. IMD3 vs. VGN Voltage over Temperature and OFSx at 500 MHz

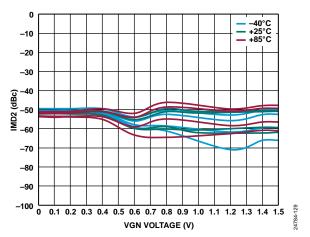

Figure 27. IMD2 vs. VGN Voltage over Temperature and OFSx at 1 GHz

Figure 28. IMD2 vs. VGN Voltage, over Temperature and OFSx at 2 GHz

Figure 29. IMD2 vs. VGN Voltage over Temperature and OFSx at 3 GHz

Figure 30. IMD3 vs. VGN Voltage over Temperature and OFSx at 1 GHz

Figure 31. IMD3 vs. VGN Voltage over Temperature and OFSx at 2 GHz

Figure 32. IMD3 vs. VGN Voltage over Temperature and OFSx at 3 GHz

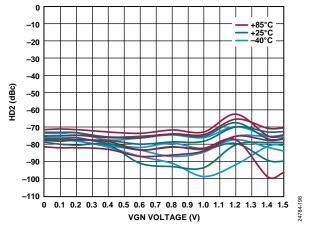

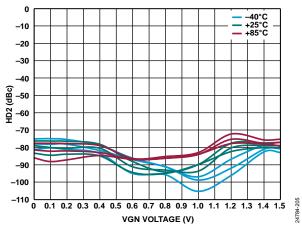

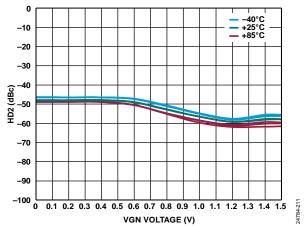

Figure 33. HD2 vs. VGN Voltage over Temperature and OFSx at 500 MHz

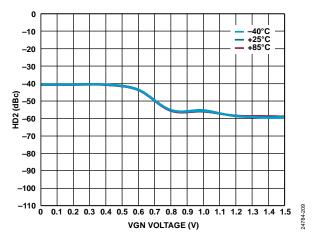

Figure 34. HD2 vs. VGN Voltage over Temperature and OFSx at 1 GHz

Figure 35. HD2 vs. VGN Voltage over Temperature and OFSx at 2 GHz

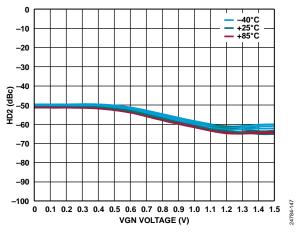

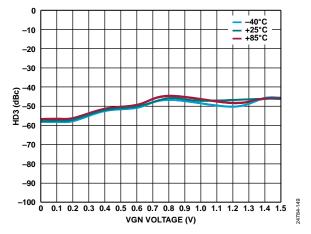

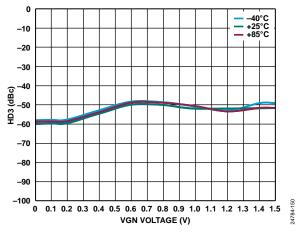

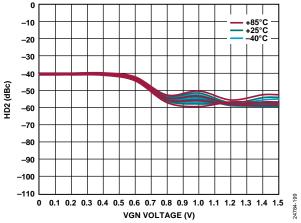

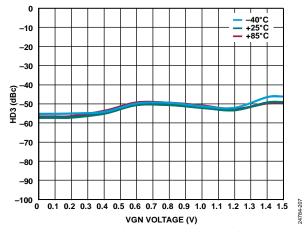

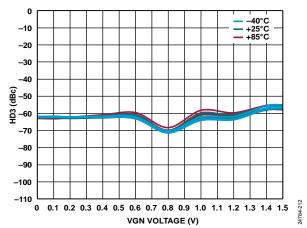

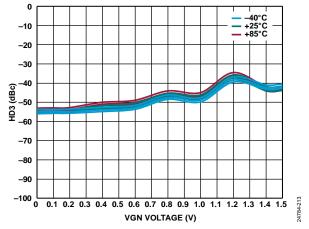

Figure 36. HD3 vs. VGN Voltage over Temperature and OFSx at 500 MHz

Figure 37. HD3 vs. VGN Voltage over Temperature and VOCM at 1 GHz

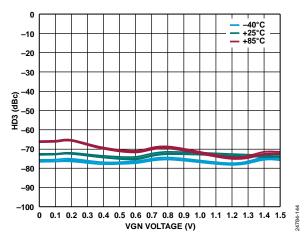

Figure 38. HD3 vs. VGN Voltage over Temperature and OFSx at 2 GHz

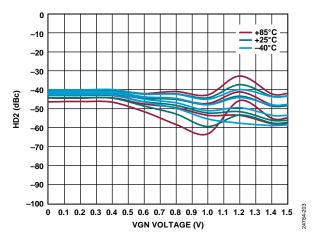

Figure 39. HD2 vs. VGN Voltage over Temperature and OFSx at 3 GHz

Figure 40. HD2 vs. VGN Voltage over Temperature and VOCM at 500 MHz

Figure 41. HD2 vs. VGN Voltage over Temperature and VOCM at 1 GHz

Figure 42. HD3 vs. VGN Voltage over Temperature and OFSx at 3 GHz

Figure 43. HD3 vs. VGN Voltage over Temperature and VOCM at 500 MHz

Figure 44. HD3 vs. VGN Voltage over Temperature and VOCM at 1 GHz

Figure 45. HD2 vs. VGN Voltage over Temperature and VOCM at 2 GHz

Figure 46. HD2 vs. VGN Voltage over Temperature and VOCM at 3 GHz

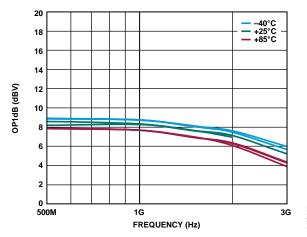

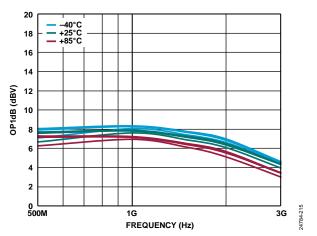

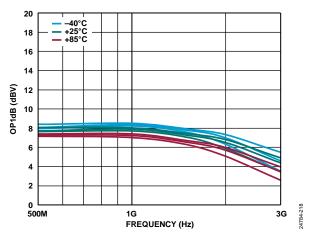

Figure 47. OP1dB vs. Frequency over Temperature and OFSx

Figure 48. HD3 vs. VGN Voltage over Temperature and VOCM at 2 GHz

Figure 49. HD3 vs. VGN Voltage over Temperature and VOCM at 3 GHz

Figure 50. OP1dB vs. Frequency over Temperature and VOCM

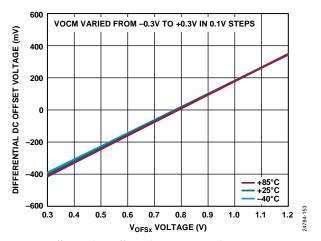

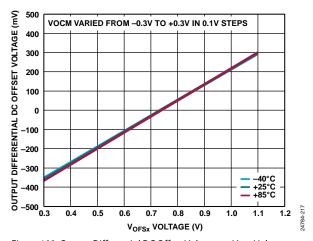

Figure 51. Differential DC Offset Voltage vs. V<sub>OFSx</sub> Voltage over Temperature and VOCM

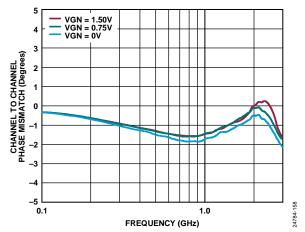

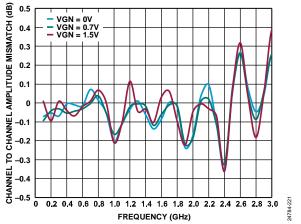

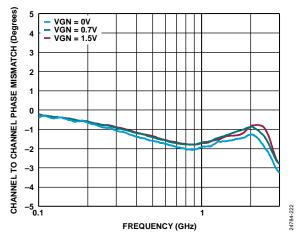

Figure 52. Channel to Channel Phase Mismatch vs. Frequency over VGN

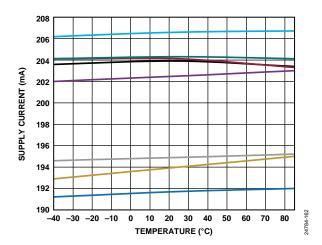

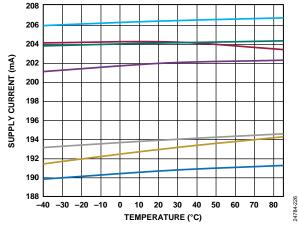

Figure 53. Supply Current vs. Temperature for Multiple Devices

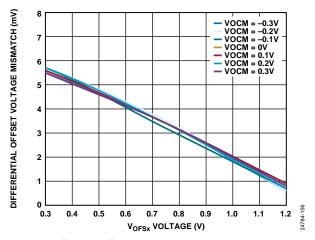

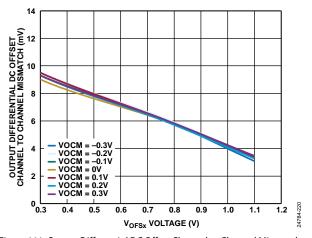

Figure 54. Differential Offset Voltage Mismatch (Channel to Channel) vs.  $V_{OFSx}$  Voltage over VOCM

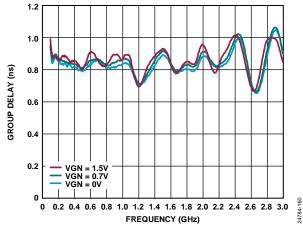

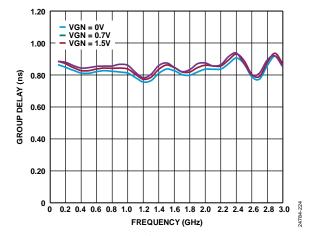

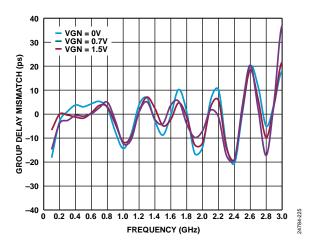

Figure 55. Group Delay vs. Frequency over VGN

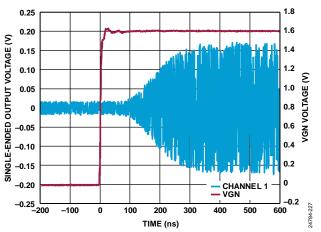

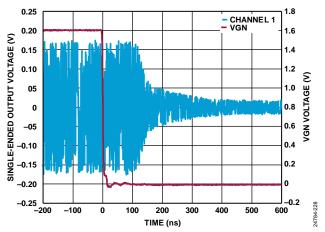

Figure 56. VGA Step Response Rise Time, Minimum to Maximum Gain

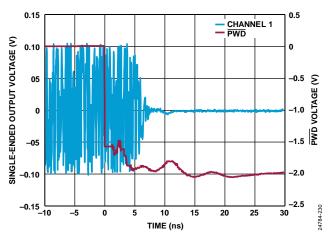

Figure 57. VGA Step Response Fall Time, Maximum to Minimum Gain

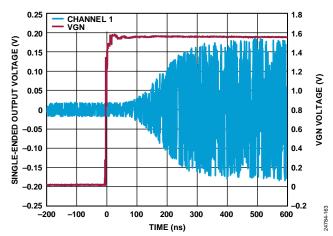

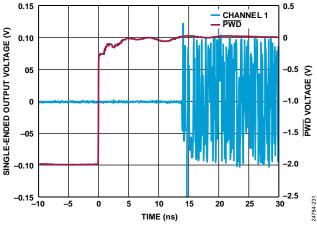

Figure 58. Disable Response Time

Figure 59. Enable Response Time

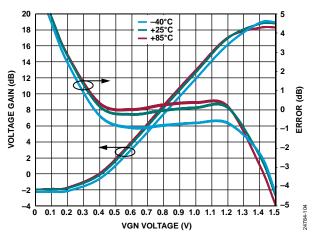

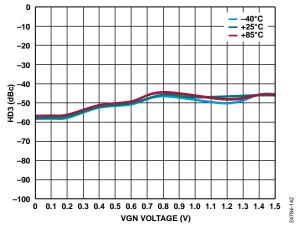

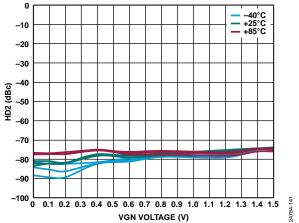

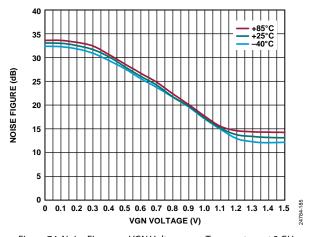

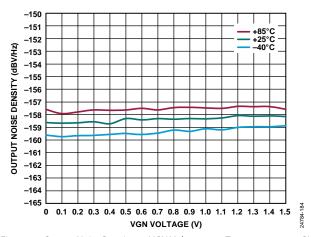

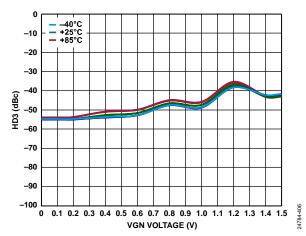

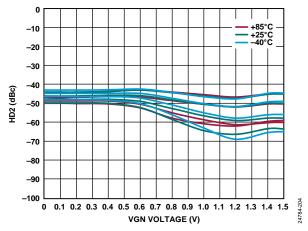

#### **DUAL-SUPPLY OPERATION**

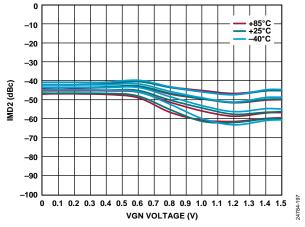

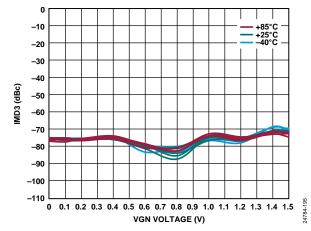

VPOS = 3 V and VNEG = -2 V,  $T_A$  = 25°C,  $Z_{LOAD}$  = 186  $\Omega$ , VGN = 1.5 V, VOCM = 0 V, OFS1 = OFS2 = 0.75 V, output level = 1.5 V p-p, and 43  $\Omega$  back termination de-embedded, unless otherwise noted. Noise figure measured with 100  $\Omega$  differential input termination. Worst case IMD2 and IMD3 tone reported.  $V_{OFSx}$  sweeps = 0 V, 0.4 V, 0.75 V, or 1.2 V. VOCM sweeps = -0.1 V, 0 V, or +0.1 V.

Figure 60. Voltage Gain and Error vs. VGN Voltage over Temperature at 500 MHz

Figure 61. Voltage Gain and Error vs. VGN Voltage over Temperature at 2 GHz

Figure 62. Voltage Gain vs. Frequency, over Temperature and VGN, 43  $\Omega$  Back Terminations not De-Embedded

Figure 63. Voltage Gain and Error vs. VGN Voltage over Temperature at 1 GHz

Figure 64. Voltage Gain and Error vs. VGN Voltage over Temperature at 3 GHz

Figure 65. Voltage Gain vs. Frequency over 200 mV VGN Steps, 43  $\Omega$  Back Terminations not De-Embedded

Figure 66. Differential S11 vs. Frequency over Temperature and VGN

Figure 67. Noise Figure vs. Frequency over Temperature and VGN

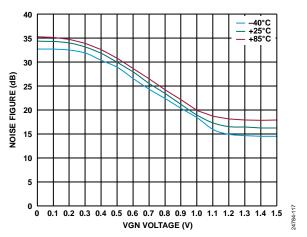

Figure 68. Noise Figure vs. VGN Voltage over Temperature at 500 MHz

Figure 69. Differential S22 vs. Frequency over Temperature and VGN with 43  $\Omega$  Back Terminations

Figure 70. Output Noise Density vs. Frequency over Temperature and VGN

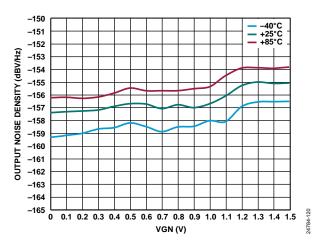

Figure 71. Output Noise Density vs. VGN Voltage over Temperature at 500 MHz

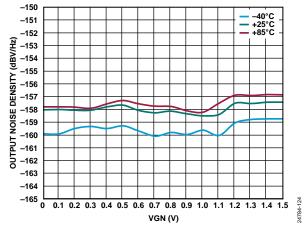

Figure 72. Noise Figure vs. VGN Voltage over Temperature at 1 GHz

Figure 73. Noise Figure vs. VGN Voltage over Temperature at 2 GHz

Figure 74. Noise Figure vs. VGN Voltage over Temperature at 3 GHz

Figure 75. Output Noise Density vs. VGN Voltage over Temperature at 1 GHz

Figure 76. Output Noise Density vs. VGN Voltage over Temperature at 2 GHz

Figure 77. Output Noise Density vs. VGN Voltage over Temperature at 3 GHz

Figure 78. IMD2 vs. Frequency over Temperature and VGN

Figure 79. IIP2 vs. Frequency over VGN in 200 mV Steps

Figure 80. IMD2 vs. VGN Voltage over Temperature and OFSx at 500 MHz

Figure 81. IMD3 vs. Frequency over Temperature and VGN

Figure 82. IIP3 vs. Frequency over VGN in 200 mV Steps

Figure 83. IMD3 vs. VGN Voltage over Temperature and OFSx at 500 MHz

Figure 84. IMD2 vs. VGN Voltage over Temperature and OFSx at 1 GHz

Figure 85. IMD2 vs. VGN Voltage over Temperature and OFSx at 2 GHz

Figure 86. IMD2 vs. VGN Voltage over Temperature and OFSx at 3 GHz

Figure 87. IMD3 vs. VGN Voltage over Temperature and OFSx at 1 GHz

Figure 88. IMD3 vs. VGN Voltage over Temperature and OFSx at 2 GHz

Figure 89. IMD3 vs. VGN Voltage over Temperature and OFSx at 3 GHz

Figure 90. HD2 vs. VGN Voltage over Temperature and OFSx at 500 MHz

Figure 91. HD2 vs. VGN Voltage over Temperature and OFSx at 1 GHz

Figure 92. HD2 vs. VGN Voltage over Temperature and OFSx at 2 GHz

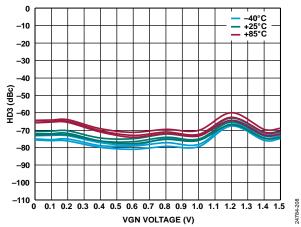

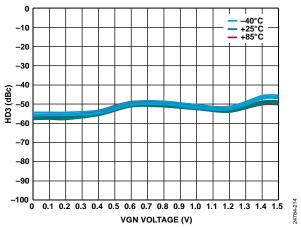

Figure 93. HD3 vs. VGN Voltage over Temperature and OFSx at 500 MHz

Figure 94. HD3 vs. VGN Voltage over Temperature and OFSx at 1 GHz

Figure 95. HD3 vs. VGN Voltage over Temperature and OFSx at 2 GHz

Figure 96. HD2 vs. VGN Voltage over Temperature and OFSx at 3 GHz

Figure 97. HD2 vs. VGN Voltage over Temperature and VOCM at 500 MHz

Figure 98. HD2 vs. VGN Voltage over Temperature and VOCM at 1 GHz

Figure 99. HD3 vs. VGN Voltage over Temperature and OFSx at 3 GHz

Figure 100. HD3 vs. VGN Voltage over Temperature and VOCM at 500 MHz

Figure 101. HD3 vs. VGN Voltage over Temperature and VOCM at 1 GHz

Figure 102. HD2 vs. VGN Voltage over Temperature and VOCM at 2 GHz

`Figure 103. HD2 vs. VGN Voltage over Temperature and VOCM at 3 GHz

Figure 104. OP1dB vs. Frequency over Temperature and OFSx at Maximum

Gain

Figure 105. HD3 vs. VGN Voltage over Temperature and VOCM at 2 GHz

Figure 106. HD3 vs. VGN Voltage over Temperature and VOCM at 3 GHz

Figure 107. OP1dB vs. Frequency over Temperature and VOCM at Maximum Gain

Figure 108. Output Differential DC Offset Voltage vs. V<sub>OFSx</sub> Voltage over Temperature and VOCM

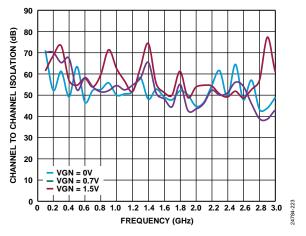

Figure 109. Channel to Channel Amplitude Mismatch vs. Frequency over VGN

Figure 110. Channel to Channel Phase Mismatch vs. Frequency over VGN

Figure 111. Output Differential DC Offset Channel to Channel Mismatch vs.  $V_{OFSx}$  Voltage over VOCM

Figure 112. Group Delay vs. Frequency over VGN

Figure 113. Group Delay Mismatch (Channel to Channel) vs. Frequency over

Figure 114. Channel to Channel Isolation vs. Frequency over VGN

Figure 115. VGA Step Response Time, Minimum to Maximum Gain

Figure 116. Enable Response Time

Figure 117. Supply Current vs. Temperature over Multiple Devices

Figure 118. VGA Step Response Time, Maximum to Minimum Gain

Figure 119. Disable Response Time

### THEORY OF OPERATION

The ADRF6521 is a highly linear, dual channel VGA with a -3 dB frequency response of 3.25 GHz. The ADRF6521 consists of a matched pair of VGAs, each consisting of a voltage variable attenuator (VVA) designed to have 21 dB of attenuation range at room temperature ( $T_A = 25^{\circ}$ C), followed by an 18 dB amplifier, producing a gain range from +18 dB to -3 dB.

The output stage has the ability to change its common-mode voltage and have a purposeful dc offset voltage. The output common-mode voltage range and output dc offset voltage range are adjustable up to  $\pm 200$  mV and  $\pm 400$  mV, respectively, while still maintaining the high linearity outlined in Table 1. Larger ranges are possible, but linearity degrades. Figure 120 shows the simplified block diagram of a single channel.

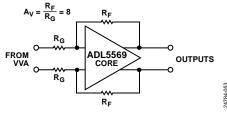

Figure 120. Simplified Functional Block Diagram for a Single Channel

The entire differential signal chain is dc-coupled. However it is recommended to ac-couple the input signal paths. The gain setting control for the two channels is a shared pin (VGN), ensuring close matching of their magnitude and phase responses. The ADRF6521 is fully disabled by pulling  $\overline{PWD}$  to the VNEG supply.

#### **INPUT VVAs**

The input VVAs are designed to have high linearity and excellent log conformance. The VVAs have a differential input impedance of 100  $\Omega$  and an attenuation range of 21 dB, which decreases slightly over temperature. If the input must be dc-coupled, the output common mode of the previous stage must match the voltage on the VOCM pin. The topology of an input VGA, for example, the VVA located at the input of the device, is such that the noise figure degrades dB for dB as attenuation increases. The VVA maintains its high linearity across its full range of attenuation.

#### **AMPLIFIERS**

The ADRF6521 amplifiers use the same core as the ADL5569. The amplifiers have a low output impedance (<20  $\Omega$ ), and the R<sub>F</sub> to R<sub>G</sub> on-chip resistor ratio is approximately 8×, which creates the 18 dB of differential voltage gain. The amplifiers are designed to drive subsequent amplifier stages and are capable of high linearity with 1.5 V p-p two-tone signals into 100  $\Omega$  differential loads.

Figure 121. 18 dB Amplifier for a Single Channel

#### **OUTPUT COMMON-MODE VOLTAGE**

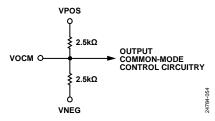

The output common-mode voltage is set internally to (VPOS + VNEG)/2, with an on-chip resister divider (see Figure 122). This voltage can be adjusted  $\pm 200$  mV via the VOCM pin and the ADRF6521 still maintains IMD2, IMD3, HD2, and HD3 of -55 dBc or better. There is a 1 to 1 mapping between the control voltage applied to VOCM and the output common-mode voltage.

Figure 122. VOCM Simplified Circuit

#### **OUTPUT DC OFFSET CIRCUIT**

The output dc offset on each channel of the ADRF6521 can be independently nulled out to account for the small inherent dc offsets of the VVA and amplifier. For applications such as predistortion, the output dc offset voltage of each channel can intentionally be increased up to  $\pm 400~\text{mV}$  in addition to the  $\pm 200~\text{mV}$  output common-mode range, while still maintaining high linearity. Adjusting the output common-mode and the output dc offset voltage more than a combined 400 mV from the nominal voltage on any output pin causes the linearity to degrade, possibly to IMDx and/or HDx levels worse than -55~dBc.

The output dc offset voltage is defined as follows:

$$V_{OFS\_DC} = V_{OPPx} - V_{OPMx}$$

where  $V_{\text{OPPx}}$  and  $V_{\text{OPMx}}$  are the dc voltages on the OPP1 and OPM1 or the OPP2 and OPM2 output pins.

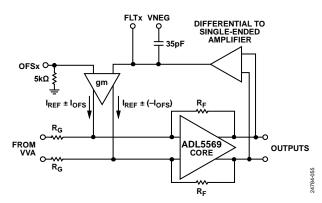

The output dc offset voltage is controlled via the OFS1 pin and OFS2 pin, shown in Figure 120 and Figure 124 as a generic OFSx pin. The output dc offset voltage is fundamentally caused by injecting a differential current into the input of the amplifier. The differential current consists of the following:

- A reference current (I<sub>REF</sub>), which is added to both the positive and negative legs of the differential path

- A bipolar offset current (I<sub>OFS</sub>), which is added on one leg of the differential path and subtracted from the other leg

The reference current is a static current, but the bipolar offset current is controlled via the respective OFSx pins. Both currents are injected between the 18 dB amplifier and VVA. Because the offset current is bipolar, the output dc offset voltage goes up to  $+400~\rm mV$  or down to  $-400~\rm mV$ . The nominal closed form equation between the control voltage on the FLTx pins and the output dc offset voltage is

$$V_{DC\ OFFSET\ DIFF} = 0.89 \times V_{OFSx} - 0.668 \text{ V}$$

#### DC Offset Loop High-Pass Corner

The ADRF6521 has dc offset loops that null any signal below their low-pass frequency corner, which is set by a combination of the internal 35 pF capacitor plus any external capacitor decoupled to VNEG from OFSx.

Although the dc offset loops have a low-pass response, the signal paths show a high-pass response because the loops null any low frequency signal below their low-pass corner. The following equation shows the relationship between the high-pass corner observed on the signal paths and the value of the external capacitor decoupled to VNEG, which is called  $C_{\rm OFS}$ :

$$f_{HP}$$

(Hz) =  $60/(C_{OFS} (\mu F) + 35 \times 10^{-6})$

With  $C_{OFS} = 1 \mu F$ , the high-pass corner in Hz is calculated as:

$$f_{HP}$$

(Hz) =  $60/(1 + 35 \times 10^{-6}) = 60$  Hz

The feedback loop shown in Figure 124 creates the output dc offset voltage. The differential to single-ended amplifier samples the differential output, converts the signal into single-ended mode, and averages the signal with a capacitor connected to VNEG. This averaged version of the output is compared to the dc voltage applied to the OFSx pin(s) with the transconductance amplifier (gm). The output differential current of the gm stage is injected between the  $R_{\rm F}$  and  $R_{\rm G}$  resistors of the 18 dB amplifier. The feedback loop forces the differential current of the gm amplifier to increase or decrease until the averaged voltage from the differential to single-ended amplifier is equal to the applied OFSx voltage. This differential current injected at the input of the amplifier creates an intentional dc offset voltage at the input, which is then amplified and seen on the output pins, OPPx and OPMx.

The output dc offset circuits are filtered on each channel via the FLT1 and FLT2 pins, for Channel 1 and Channel 2, respectively. Connect both pins to the negative supply via a 1  $\mu$ F capacitor. There is an on-chip capacitance of 35 pF on each FLTx node.

#### **GAIN CONTROL INTERFACE**

The ADRF6521 has a linear-in-dB gain control interface. The gain control slope is maintained at 22.2 dB/V over temperature, supply, and process as gain varies from 250 mV to 1200 mV.

The gain function is given by

$$Gain (dB) = 22.2 \times V_{VGN} - 8.5$$

where  $V_{\text{VGN}}$  is the voltage on the VGN gain pin in volts.

The gain control voltage range is from 0 V to 1.5 V, with respect to analog ground.

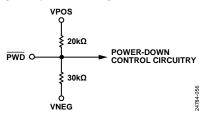

### **POWER-DOWN FUNCTION**

The power-down function is accomplished via the  $\overline{PWD}$  pin. By default, the device is enabled via the resistive divider shown in Figure 123. Assert the  $\overline{PWD}$  pin to the same potential as VNEG to reduce the current consumption to roughly 25 mA. Do not apply a voltage more than VNEG + 3.3 V on the  $\overline{PWD}$  pin. Higher voltages may cause damage to the device.

Figure 123. Simplified Power Down Interface

Figure 124. Output DC Offset Circuit for a Single Channel

# APPLICATIONS INFORMATION BASIC CONNECTIONS

Figure 125 shows the basic connections for a typical ADRF6521 application.

#### **SUPPLY DECOUPLING**

Decouple each supply pin, VPOS and VNEG, to ground with at least one low inductance, surface-mount ceramic capacitor of 0.1  $\mu$ F placed as close as possible to the ADRF6521 device.

#### **INPUT SIGNAL PATH**

Each signal path has an input VGA, accessed through the INP1, INM1, INP2, and INM2 pins, which sets a differential input impedance of 100  $\Omega$ .

The inputs can be dc-coupled or ac-coupled, but ac coupling is strongly recommended. There is no mechanism to change the common-mode voltage. Therefore, if the user wants to use dc coupling, the common-mode voltage of the previous stage must match the ADRF6521 input common-mode voltage of (VPOS + VNEG)/2 V.

#### **OUTPUT SIGNAL PATH**

The low impedance (20  $\Omega$ ) output buffers are designed to drive a 100  $\Omega$  impedance load. However, the buffers can drive larger resistive loads. The output pins (OPP1, OPM1, OPP2, and OPM2) sit at a nominal output common-mode voltage of (VPOS + VNEG)/2 V. The outputs can be dc-coupled or ac-coupled. However, dc coupling is required to take advantage of the output dc offset voltage functionality. To change the output common-mode voltage, the user must apply a dc voltage to the VOCM pin different than (VPOS + VNEG)/2 V. Left open, VOCM defaults to (VPOS + VNEG)/2 V. To change the output dc offset voltage, the user must apply a voltage to the OFS1 and OFS2 pins different than 0.75 V. Left open, these pins are pulled to ground via an on-chip 5 k $\Omega$  resistor, which creates an approximately –670 mV dc output offset.

Figure 125. Basic Connections

#### **ENABLE AND DISABLE FUNCTION**

To enable the ADRF6521, leave the  $\overline{PWD}$  pin open or pull this pin to VNEG + 3.0 V. Driving the  $\overline{PWD}$  pin to VNEG disables the device, reducing the current consumption to approximately 25 mA at room temperature.

#### **GAIN PIN (VGN) DECOUPLING**

The ADRF6521 has one analog gain control pin, VGN. The gain changes when an applied VGN voltage is between 0 V and 1.5 V. Maximum voltage on the VGN pin is equal to the voltage applied to VPOS. Use at least one low inductance, surface-mount ceramic capacitor with a value of 0.1  $\mu F$  and one 1000 pF in parallel to ground on the gain pin (VGN) to decouple to ground.

#### **OUTPUT IMPEDANCE MATCHING**

The ADRF6521 natively has a low differential output impedance of  $\leq$ 16  $\Omega$ . Depending on the PCB design of the user and the S22 requirements, matching the output impedance to 100  $\Omega$  differential may be desirable. To achieve a match looking towards the output pins, place a pair of 43  $\Omega$  series resistors as close as possible to the output pins (OPP1, OPM1, OPP2, and OPM2).

The installation of these 43  $\Omega$  resistors decreases the voltage level of the signal by roughly 6 dB, and thus decreases the maximum gain of the VGA to 12 dB. This loss of signal level is usually acceptable because of the high linearity of the ADRF6521. That is, the ADRF6521 can operate at twice the output signal level (with respect to no matching resistors), and still maintain -55 dBc IMD2 and IMD3 and HD2 and HD3 levels or better.

Note that when using series matching resistors, the output dc offset voltage is also reduced by the same amount as the RF signal level.

If a full 100  $\Omega$  match is not required and a greater than 12 dB gain value is more important, the user can decrease the series resistor value until an optimum trade-off between the gain and the output match is found.

#### SINGLE-SUPPLY OPERATION

The ADRF6521 can operate on a 5 V single supply. Connect VNEG to analog ground. The output common-mode voltage defaults to 2.5 V in this configuration. The nominal range of  $\pm 200$  mV still applies. A larger range is possible, however, linearity performance degrades.

#### **DUAL-SUPPLY OPERATION**

Apply a nominal supply voltage of +2.5 V to the VPOS supply pin, and -2.5 V to the VNEG supply pin. This setup yields a nominal output common-mode voltage of 0 V, and the output dc offset voltage moves above and below ground according to what voltage is applied to the OFSx pins.

When using a dual supply, ensure the following supply constraints:

- $4 \text{ V} \leq (\text{VPOS} \text{VNEG}) \leq 5 \text{ V}.$

- VNEG ≤ COMM ≤ VPOS

- VPOS  $\geq$  2.5 V

#### **AVOIDING LATCH-UP**

To avoid latch-up when the device is operational or when the device is powering up, do not apply a voltage greater than the following:

- 1.5 V (relative to ground) to the control pins (VGN, OFS1, and OFS2).

- $(V_{VPOS} + V_{VNEG})/2 \pm 1 \text{ V}$  to the control pin VOCM

If the RF input must be dc coupled, the common-mode voltage must be the same as the VOCM pin voltage, which must be limited to (VPOS + VNEG)/2  $\pm$  0.2 V. If while powered down and dc coupled a dc voltage with a magnitude greater than (VPOS + VNEG)/2  $\pm$  0.2 V is applied, this dc voltage must return within the common-mode limit before powering up the ADRF6521.

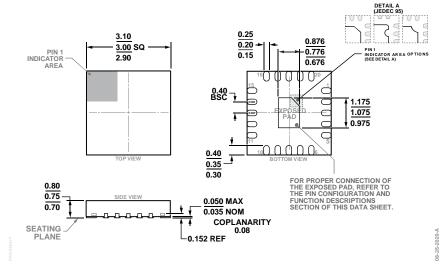

## **OUTLINE DIMENSIONS**

Figure 126. 20-Lead Lead Frame Chip Scale Package [LFCSP] 3 mm × 3 mm Body and 0.75 Package Height (CP-20-19) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                                            | Package Option |

|--------------------|-------------------|----------------------------------------------------------------|----------------|

| ADRF6521ACPZ       | −40°C to +85°C    | 20-Lead Lead Frame Chip Scale Package [LFCSP]                  | CP-20-19       |

| ADRF6521ACPZ-R7    | −40°C to +85°C    | 20-Lead Lead Frame Chip Scale Package [LFCSP], 7"Tape and Reel | CP-20-19       |

| ADRF6521-EVALZ     |                   | Evaluation Board                                               |                |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Parts.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for RF Amplifier category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below:

A82-1 BGA622H6820XTSA1 BGA 728L7 E6327 BGB719N7ESDE6327XTMA1 HMC397-SX HMC405 HMC561-SX HMC8120-SX HMC8121-SX HMC-ALH382-SX HMC-ALH476-SX SE2433T-R SMA3101-TL-E SMA39 A66-1 A66-3 A67-1 A81-2 LX5535LQ LX5540LL MAAM02350 HMC3653LP3BETR HMC549MS8GETR HMC-ALH435-SX SMA101 SMA32 SMA411 SMA531 SST12LP19E-QX6E WPM0510A HMC5929LS6TR HMC5879LS7TR HMC1087F10 HMC1086 HMC1016 SMA1212 MAX2689EWS+T MAAMSS0041TR MAAM37000-A1G LTC6430AIUF-15#PBF SMA70-2 SMA4011 A231 HMC-AUH232 LX5511LQ LX5511LQ-TR HMC7441-SX HMC-ALH310 XD1001-BD-000V A4011