# 700 MHz to 2700 MHz Rx Mixer with Integrated IF DGA, Fractional-N PLL, and VCO

### **Data Sheet**

# **ADRF6620**

### FEATURES

Integrated fractional-N phase-locked loop (PLL) RF input frequency range: 700 MHz to 2700 MHz Internal local oscillator (LO) frequency range: 350 MHz to 2850 MHz Input P1dB: 17 dBm Output IP3: 45 dBm Single-pole four-throw (SP4T) RF input switch Digital step attenuator (DSA) range: 0 dB to 15 dB Integrated RF tunable balun allowing single-ended 50 Ω input Multicore integrated voltage controlled oscillator (VCO) Digitally programmable variable gain amplifier (DGA) -3 dB bandwidth: >600 MHz

Balanced 150 Ω IF output impedance Programmable via 3-wire serial port interface (SPI) Single 5 V supply

#### **APPLICATIONS**

Wireless receivers Digital predistortion (DPD) receivers

#### **GENERAL DESCRIPTION**

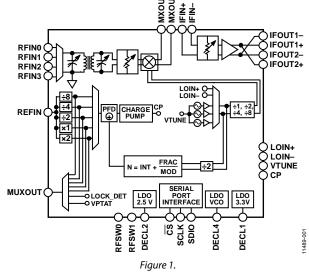

The ADRF6620 is a highly integrated active mixer and synthesizer that is ideally suited for wireless receiver subsystems. The feature rich device consists of a high linearity broadband active mixer; an integrated fractional-N PLL; low phase noise, multicore VCO; and IF DGA. In addition, the ADRF6620 integrates a 4:1 RF switch, an on-chip tunable RF balun, programmable RF attenuator, and low dropout (LDO) regulators. This highly integrated device fits within a small 7 mm × 7 mm footprint.

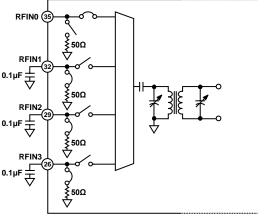

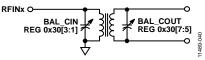

The high isolation 4:1 RF switch and on-chip tunable RF balun enable the ADRF6620 to support four single-ended 50  $\Omega$  terminated RF inputs. A programmable attenuator ensures optimal RF input drive to the high linearity mixer core. The integrated DSA has an attenuation range of 0 dB to 15 dB with a step size of 1 dB.

### FUNCTIONAL BLOCK DIAGRAM 등능

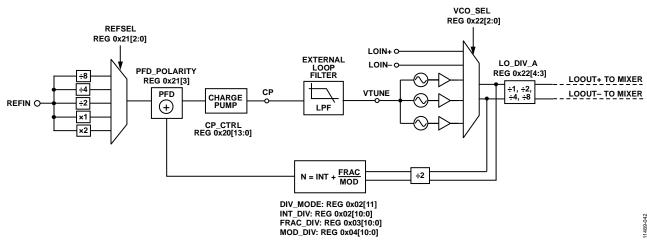

The ADRF6620 offers two alternatives for generating the differential LO input signal: externally, via a high frequency, low phase noise LO signal, or internally, via the on-chip fractional-N PLL synthesizer. The integrated synthesizer enables continuous LO coverage from 350 MHz to 2850 MHz. The PLL reference input can support a wide frequency range because the divide and multiply blocks can be used to increase or decrease the reference frequency to the desired value before it is passed to the phase frequency detector (PFD).

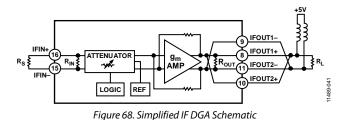

The integrated high linearity DGA provides an additional gain range from 3 dB to 15 dB in steps of 0.5 dB for maximum flexibility in driving an analog-to-digital converter (ADC).

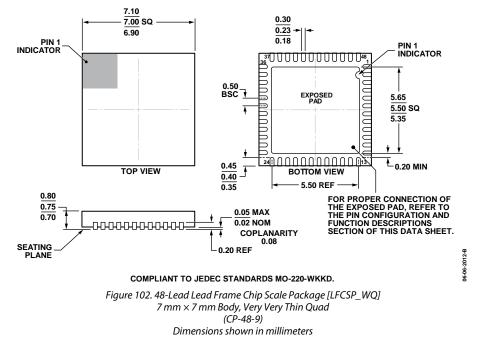

The ADRF6620 is fabricated using an advanced silicon-germanium BiCMOS process. It is available in a 48-lead, RoHS-compliant, 7 mm  $\times$  7 mm LFCSP package with an exposed pad. Performance is specified over the  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range.

Rev. 0

#### **Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2013 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# TABLE OF CONTENTS

| Features                                                                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Applications1                                                                                                                                                                                                                                                          |

| Functional Block Diagram1                                                                                                                                                                                                                                              |

| General Description                                                                                                                                                                                                                                                    |

| Revision History                                                                                                                                                                                                                                                       |

| Specifications                                                                                                                                                                                                                                                         |

| RF Input to IF DGA Output System Specifications                                                                                                                                                                                                                        |

| Synthesizer/PLL Specifications 4                                                                                                                                                                                                                                       |

| RF Input to Mixer Output Specifications6                                                                                                                                                                                                                               |

| IF DGA Specifications7                                                                                                                                                                                                                                                 |

| Digital Logic Specifications8                                                                                                                                                                                                                                          |

| Absolute Maximum Ratings                                                                                                                                                                                                                                               |

| Thermal Resistance                                                                                                                                                                                                                                                     |

| ESD Caution                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                        |

| Pin Configuration and Function Descriptions                                                                                                                                                                                                                            |

| Pin Configuration and Function Descriptions                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                        |

| Typical Performance Characteristics                                                                                                                                                                                                                                    |

| Typical Performance Characteristics11RF Input to DGA Output System Performance11Phase-Locked Loop (PLL)13RF Input to Mixer Output Performance17IF DGA20                                                                                                                |

| Typical Performance Characteristics11RF Input to DGA Output System Performance11Phase-Locked Loop (PLL)13RF Input to Mixer Output Performance17IF DGA20Spurious Performance22                                                                                          |

| Typical Performance Characteristics11RF Input to DGA Output System Performance11Phase-Locked Loop (PLL)13RF Input to Mixer Output Performance17IF DGA20Spurious Performance22Theory of Operation24                                                                     |

| Typical Performance Characteristics11RF Input to DGA Output System Performance11Phase-Locked Loop (PLL)13RF Input to Mixer Output Performance17IF DGA20Spurious Performance22Theory of Operation24RF Input Switches24                                                  |

| Typical Performance Characteristics11RF Input to DGA Output System Performance11Phase-Locked Loop (PLL)13RF Input to Mixer Output Performance17IF DGA20Spurious Performance22Theory of Operation24RF Input Switches24Tunable Balun25                                   |

| Typical Performance Characteristics11RF Input to DGA Output System Performance11Phase-Locked Loop (PLL)13RF Input to Mixer Output Performance17IF DGA20Spurious Performance22Theory of Operation24RF Input Switches24Tunable Balun25RF Digital Step Attenuator (DSA)25 |

### **REVISION HISTORY**

7/13—Revision 0: Initial Version

| Serial Port Interface (SPI)                     |

|-------------------------------------------------|

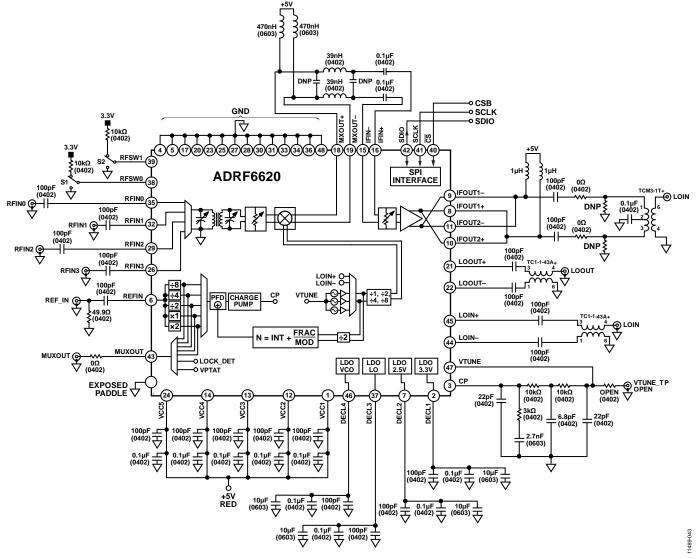

| Basic Connections                               |

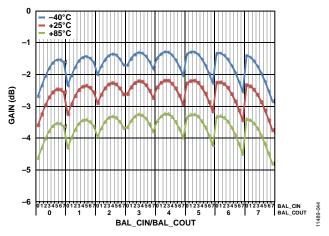

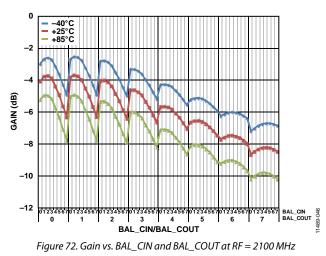

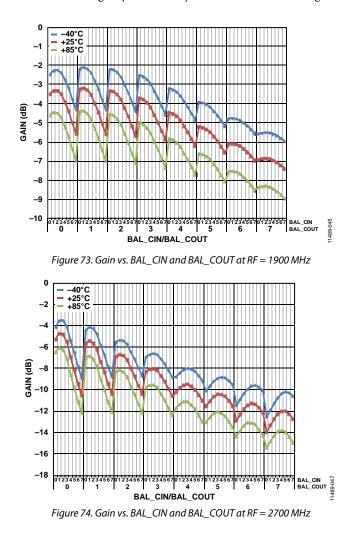

| RF Input Balun Insertion Loss Optimization      |

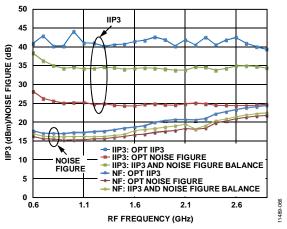

| IP3 and Noise Figure Optimization               |

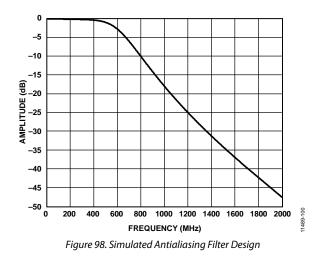

| Interstage Filtering Requirements               |

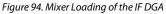

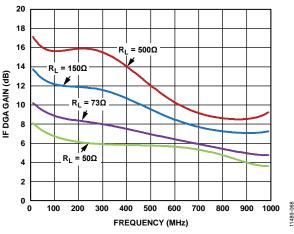

| IF DGA vs. Load                                 |

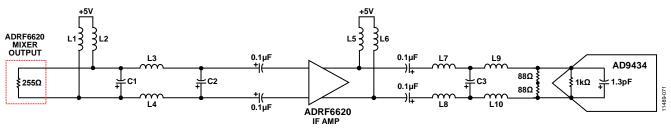

| ADC Interfacing                                 |

| Power Modes                                     |

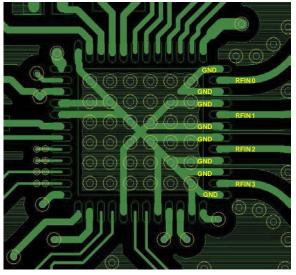

| Layout                                          |

| Register Map 41                                 |

| Register Address Descriptions                   |

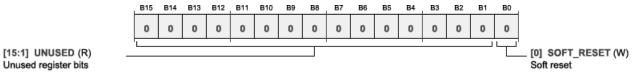

| Register 0x00, Reset: 0x00000, Name: SOFT_RESET |

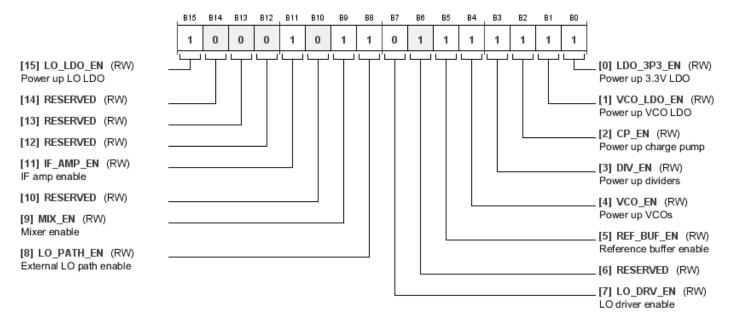

| Register 0x01, Reset: 0x8B7F, Name: Enables     |

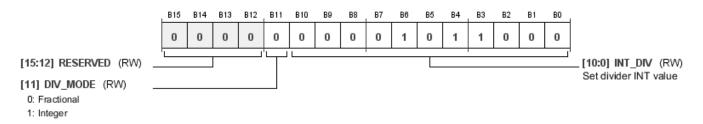

| Register 0x02, Reset: 0x0058, Name: INT_DIV     |

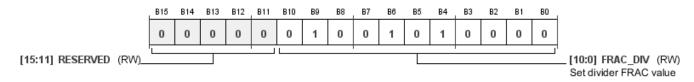

| Register 0x03, Reset: 0x0250, Name: FRAC_DIV    |

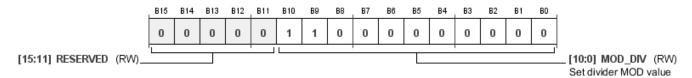

| Register 0x04, Reset: 0x0600, Name: MOD_DIV     |

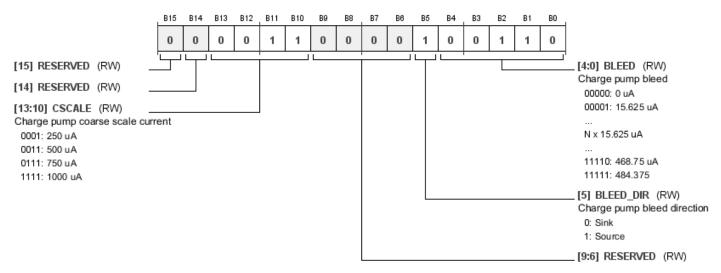

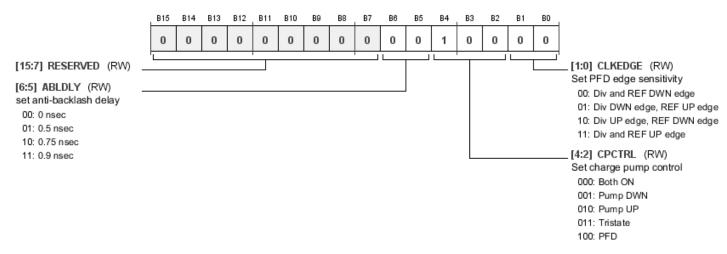

| Register 0x20, Reset: 0x0C26, Name: CP_CTL      |

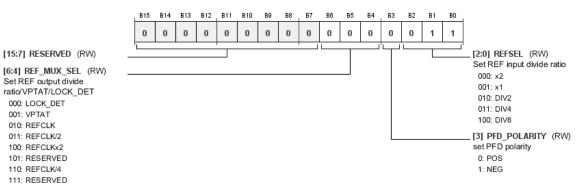

| Register 0x21, Reset: 0x0003, Name: PFD_CTL     |

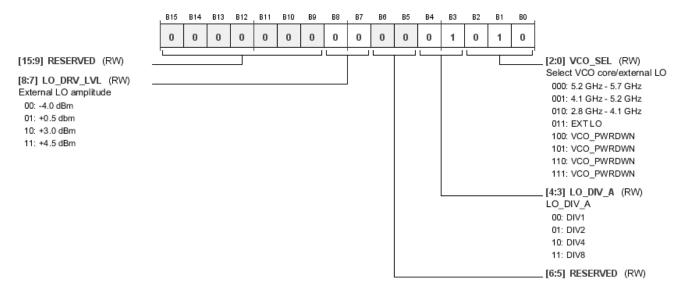

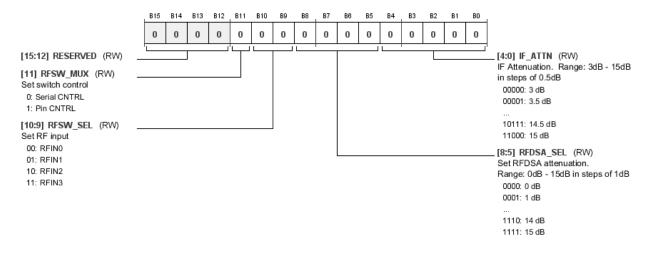

| Register 0x22, Reset: 0x000A, Name: FLO_CTL 46  |

| Register 0x23, Reset: 0x0000, Name: DGA_CTL 47  |

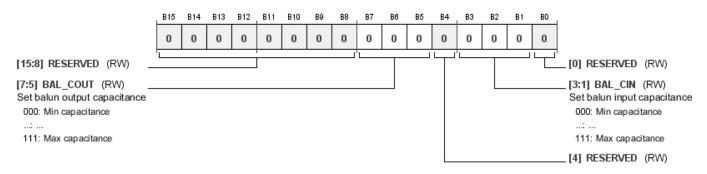

| Register 0x30, Reset: 0x00000, Name: BALUN_CTL  |

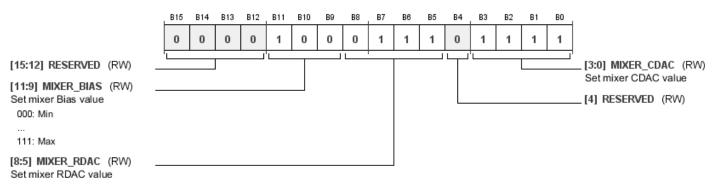

| Register 0x31, Reset: 0x08EF, Name: MIXER_CTL   |

| Register 0x40, Reset: 0x0010, Name: PFD_CTL2    |

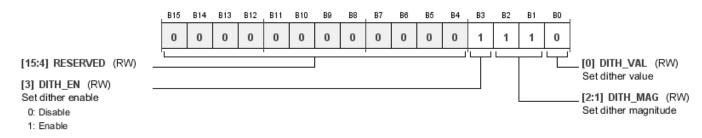

| Register 0x42, Reset: 0x000E, Name: DITH_CTL150 |

| Register 0x43, Reset: 0x0001, Name: DITH_CTL250 |

| Outline Dimensions                              |

| Ordering Guide 51                               |

|                                                 |

## **SPECIFICATIONS**

VCCx = 5 V,  $T_A = 25^{\circ}$ C, unless otherwise noted.

#### Table 1.

| Parameter                   | Test Conditions/Comments     | Min  | Тур | Max  | Unit |

|-----------------------------|------------------------------|------|-----|------|------|

| LO INPUT                    |                              |      |     |      |      |

| Internal LO Frequency Range |                              | 350  |     | 2850 | MHz  |

| External LO Frequency Range | $LO_DIV_A = 00$              | 350  |     | 3200 | MHz  |

| LO Input Level              |                              | -6   | 0   | +6   | dBm  |

| LO Input Impedance          |                              |      | 50  |      | Ω    |

| RF INPUT                    |                              |      |     |      |      |

| Input Frequency             |                              | 700  |     | 2700 | MHz  |

| Input Return Loss           |                              |      | 12  |      | dB   |

| Input Impedance             |                              |      | 50  |      | Ω    |

| RF DIGITAL STEP ATTENUATOR  |                              |      |     |      |      |

| Attenuation Range           | Step size = 1 dB             | 0    |     | 15   | dB   |

| POWER SUPPLY                |                              | 4.75 | 5.0 | 5.25 | V    |

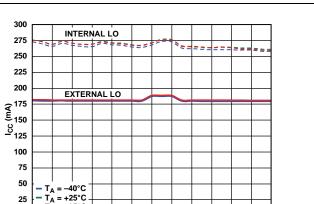

| Power Consumption           | LO output buffer disabled    |      |     |      |      |

|                             | External LO + IF DGA enabled |      | 1.3 |      | W    |

|                             | Internal LO + IF DGA enabled |      | 1.7 |      | W    |

|                             | Only IF DGA enabled          |      | 0.6 |      | W    |

| Power-Down Current          |                              |      | 6   |      | mA   |

### **RF INPUT TO IF DGA OUTPUT SYSTEM SPECIFICATIONS**

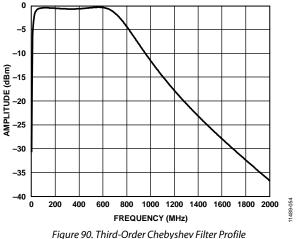

VCCx = 5 V,  $T_A = 25^{\circ}C$ , high-side LO injection,  $f_{IF} = 200 \text{ MHz}$ , internal LO frequency, IF DGA output load = 150  $\Omega$ , and 2 V p-p differential output with third-order low-pass filter, unless otherwise noted. For mixer settings for maximum linearity, see Table 16. All losses from input and output traces and baluns are de-embedded from results

| Parameter                                          | Test Conditions/Comments                        | Min | Тур  | Max | Unit |

|----------------------------------------------------|-------------------------------------------------|-----|------|-----|------|

| DYNAMIC PERFORMANCE AT $f_{RF} = 900 \text{ MHz}$  | $f_{IF} = 200 \text{ MHz}$                      |     |      |     |      |

| Voltage Conversion Gain                            |                                                 |     | 12   |     | dB   |

| Output P1dB                                        |                                                 |     | 18   |     | dBm  |

| Output IP3                                         | 1 V p-p each output tone, 1 MHz tone spacing    |     | 43   |     | dBm  |

| Output IP2                                         | 1 V p-p each output tone, 1 MHz tone spacing    |     | 78   |     | dBm  |

| Noise Figure                                       | Noise figure optimized 16                       |     | dB   |     |      |

| DYNAMIC PERFORMANCE AT $f_{RF} = 1900 \text{ MHz}$ | $f_{IF} = 200 \text{ MHz}$                      |     |      |     |      |

| Voltage Conversion Gain                            |                                                 |     | 11   |     | dB   |

| Output P1dB                                        |                                                 |     | 18   |     | dBm  |

| Output IP3                                         | 1 V p-p each output tone, 1 MHz tone spacing    |     | 45   |     | dBm  |

| Output IP2                                         | 1 V p-p each output tone, 1 MHz tone spacing 75 |     |      | dBm |      |

| Noise Figure                                       | Noise figure optimized                          |     | 18.5 |     | dB   |

| DYNAMIC PERFORMANCE AT $f_{RF} = 2100 \text{ MHz}$ | $f_{IF} = 200 \text{ MHz}$                      |     |      |     | dB   |

| Voltage Conversion Gain                            |                                                 |     | 10.5 |     | dBm  |

| Output P1dB                                        |                                                 |     | 18   |     | dBm  |

| Output IP3                                         | 1 V p-p each output tone, 1 MHz tone spacing    |     | 45   |     | dBm  |

| Output IP2                                         | 1 V p-p each output tone, 1 MHz tone spacing    |     | 66   |     | dBm  |

| Noise Figure                                       | Noise figure optimized                          |     | 19   |     | dB   |

| DYNAMIC PERFORMANCE AT $f_{RF} = 2700 \text{ MHz}$ | $f_{IF} = 200 \text{ MHz}$                      |     |      |     |      |

| Voltage Conversion Gain                            |                                                 |     | 9    |     | dB   |

| Output P1dB                                        |                                                 |     | 18   |     | dBm  |

| Output IP3                                         | 1 V p-p each output tone, 1 MHz tone spacing    |     | 44   |     | dBm  |

| Output IP2                                         | 1 V p-p each output tone, 1 MHz tone spacing    |     | 74   |     | dBm  |

| Noise Figure                                       | Noise figure optimized                          |     | 21   |     | dB   |

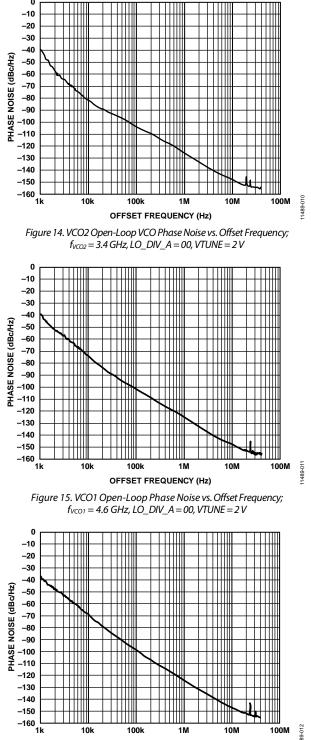

### SYNTHESIZER/PLL SPECIFICATIONS

VCCx = 5 V,  $T_A = 25^{\circ}C$ ,  $f_{REF} = 153.6 MHz$ ,  $f_{REF}$  power = 4 dBm,  $f_{PFD} = 38.4 MHz$ , and loop filter bandwidth = 120 kHz, unless otherwise noted.

| Table 3. Parameter                                         | Test Conditions/Comments                                         | Min  | Тур  | Max   | Unit       |

|------------------------------------------------------------|------------------------------------------------------------------|------|------|-------|------------|

| PLL REFERENCE                                              | Test Conditions/Comments                                         | NULL | тур  | IVIAA | Unit       |

| PLL Reference Frequency                                    |                                                                  | 12   |      | 464   | MHz        |

| PLL Reference Level                                        | For PLL lock condition                                           | -15  | +4   | +14   | dBm        |

| PFD FREQUENCY                                              |                                                                  | 24   | T4   | 58    | MHz        |

|                                                            |                                                                  |      |      |       |            |

|                                                            |                                                                  | 2800 |      | 5700  | MHz        |

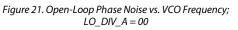

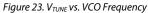

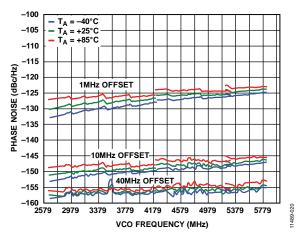

| OPEN-LOOP VCO PHASE NOISE                                  | $VTUNE = 2V, LO_DIV_A = 00$                                      |      | 20   |       | -10 - /11- |

| $f_{VCO2} = 3.4 \text{ GHz}$                               | 1 kHz offset                                                     |      | -39  |       | dBc/Hz     |

|                                                            | 10 kHz offset                                                    |      | -81  |       | dBc/Hz     |

|                                                            | 100 kHz offset                                                   |      | -103 |       | dBc/Hz     |

|                                                            | 800 kHz offset                                                   |      | -123 |       | dBc/Hz     |

|                                                            | 1 MHz offset                                                     |      | -125 |       | dBc/Hz     |

|                                                            | 6 MHz offset                                                     |      | -143 |       | dBc/Hz     |

|                                                            | 10 MHz offset                                                    |      | -147 |       | dBc/Hz     |

|                                                            | 40 MHz offset                                                    |      | -155 |       | dBc/Hz     |

|                                                            | VCO sensitivity (K <sub>v</sub> )                                |      | 88   |       | MHz/V      |

| $f_{VCO1} = 4.6 \text{ GHz}$                               | 1 kHz offset                                                     |      | -39  |       | dBc/Hz     |

|                                                            | 10 kHz offset                                                    |      | -74  |       | dBc/Hz     |

|                                                            | 100 kHz offset                                                   |      | -101 |       | dBc/Hz     |

|                                                            | 800 kHz offset                                                   |      | -123 |       | dBc/Hz     |

|                                                            | 1 MHz offset                                                     |      | -125 |       | dBc/Hz     |

|                                                            | 6 MHz offset                                                     |      | -143 |       | dBc/Hz     |

|                                                            | 10 MHz offset                                                    |      | -147 |       | dBc/Hz     |

|                                                            | 40 MHz offset                                                    |      | -156 |       | dBc/Hz     |

|                                                            | VCO sensitivity (K <sub>v</sub> )                                |      | 89   |       | MHz/V      |

| $f_{VC00} = 5.5 \text{ GHz}$                               | 1 kHz offset                                                     |      | -39  |       | dBc/Hz     |

|                                                            | 10 kHz offset                                                    |      | -69  |       | dBc/H      |

|                                                            | 100 kHz offset                                                   |      | -99  |       | dBc/H      |

|                                                            | 800 kHz offset                                                   |      | -121 |       | dBc/Hz     |

|                                                            | 1 MHz offset                                                     |      | -124 |       | dBc/Hz     |

|                                                            | 6 MHz offset                                                     |      | -142 |       | dBc/Hz     |

|                                                            | 10 MHz offset                                                    |      | -146 |       | dBc/Hz     |

|                                                            | 40 MHz offset                                                    |      | -155 |       | dBc/H      |

|                                                            | VCO sensitivity (K <sub>v</sub> )                                |      | 72   |       | MHz/V      |

| SYNTHESIZER SPECIFICATIONS                                 | Measured at LO output, LO_DIV_A = 01                             |      |      |       |            |

| $f_{LO} = 1.710 \text{ GHz}, f_{VCO2} = 3.420 \text{ GHz}$ | $f_{REF} = 153.6$ MHz, $f_{PFD} = 38.4$ MHz, 120 kHz loop filter |      |      |       |            |

| f <sub>PFD</sub> Spurs                                     | f <sub>PFD</sub> × 1                                             |      | -83  |       | dBc        |

|                                                            | f <sub>PFD</sub> × 2                                             |      | -89  |       | dBc        |

|                                                            | f <sub>PFD</sub> × 3                                             |      | -90  |       | dBc        |

|                                                            | $f_{PFD} \times 4$                                               |      | -93  |       | dBc        |

| Closed-Loop Phase Noise                                    | 1 kHz offset                                                     |      | -97  |       | dBc/Hz     |

| ·                                                          | 10 kHz offset                                                    |      | -110 |       | dBc/Hz     |

|                                                            | 100 kHz offset                                                   |      | -107 |       | dBc/Hz     |

|                                                            | 800 kHz offset                                                   |      | -128 |       | dBc/Hz     |

|                                                            | 1 MHz offset                                                     |      | -132 |       | dBc/Hz     |

|                                                            | 6 MHz offset                                                     |      | -144 |       | dBc/Hz     |

|                                                            | 10 MHz offset                                                    |      | -152 |       | dBc/Hz     |

|                                                            | 40 MHz offset                                                    |      | -158 |       | dBc/Hz     |

| Integrated Phase Noise                                     | 10 kHz to 40 MHz integration bandwidth                           |      | 0.21 |       | ° rms      |

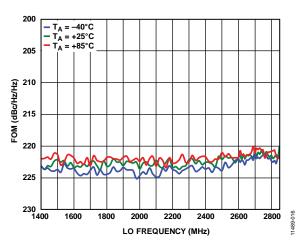

| Figure of Merit (FOM) <sup>1</sup>                         |                                                                  |      | -222 |       | dBc/Hz     |

| Parameter                                                  | Test Conditions/Comments               | Min | Тур  | Max | Unit  |

|------------------------------------------------------------|----------------------------------------|-----|------|-----|-------|

| $f_{LO} = 2.305 \text{ GHz}, f_{VCO1} = 4.610 \text{ GHz}$ |                                        |     |      |     |       |

| f <sub>PFD</sub> Spurs                                     | $f_{PFD} \times 1$                     |     | -84  |     | dBc   |

|                                                            | $f_{PFD} 	imes 2$                      |     | -87  |     | dBc   |

|                                                            | $f_{PFD} \times 3$                     |     | -91  |     | dBc   |

|                                                            | $f_{PFD} \times 4$                     |     | -92  |     | dBc   |

| Closed-Loop Phase Noise                                    | 1 kHz offset                           |     | -93  |     | dBc/H |

|                                                            | 10 kHz offset                          |     | 105  |     | dBc/H |

|                                                            | 100 kHz offset                         |     | -103 |     | dBc/H |

|                                                            | 800 kHz offset                         |     | -116 |     | dBc/H |

|                                                            | 1 MHz offset                           |     | -130 |     | dBc/H |

|                                                            | 6 MHz offset                           |     | -144 |     | dBc/H |

|                                                            | 10 MHz offset                          |     | -152 |     | dBc/H |

|                                                            | 40 MHz offset                          |     | -156 |     | dBc/H |

| Integrated Phase Noise                                     | 10 kHz to 40 MHz integration bandwidth |     | 0.3  |     | ° rms |

| Figure of Merit <sup>1</sup>                               |                                        |     | -222 |     | dBc/H |

| f <sub>LO</sub> = 2.75 GHz, f <sub>VCO2</sub> = 5.5 GHz    |                                        |     |      |     |       |

| f <sub>PFD</sub> Spurs                                     | $f_{PFD} 	imes 1$                      |     | -82  |     | dBc   |

|                                                            | $f_{PFD} \times 2$                     |     | -88  |     | dBc   |

|                                                            | $f_{PFD} \times 3$                     |     | -93  |     | dBc   |

|                                                            | $f_{PFD} 	imes 4$                      |     | -96  |     | dBc   |

| Closed-Loop Phase Noise                                    | 1 kHz offset                           |     | -93  |     | dBc/H |

|                                                            | 10 kHz offset                          |     | -101 |     | dBc/H |

|                                                            | 100 kHz offset                         |     | -99  |     | dBc/H |

|                                                            | 800 kHz offset                         |     | -122 |     | dBc/H |

|                                                            | 1 MHz offset                           |     | -128 |     | dBc/H |

|                                                            | 6 MHz offset                           |     | -144 |     | dBc/H |

|                                                            | 10 MHz offset                          |     | -151 |     | dBc/H |

|                                                            | 40 MHz offset                          |     | -154 |     | dBc/H |

| Integrated Phase Noise                                     | 10 kHz to 40 MHz integration bandwidth |     | 0.38 |     | ° rms |

|                                                            |                                        |     |      |     | 1     |

<sup>1</sup> Figure of merit (FOM) is computed as phase noise (dBc/Hz) – 10 log 10( $f_{PFD}$ ) – 20 log 10( $f_{LO}/f_{PFD}$ ). The FOM was measured across the full LO range, with  $f_{REF}$  = 160 MHz and  $f_{REF}$  power = 4 dBm (500 V/µs slew rate) with a 40 MHz  $f_{PFD}$ . The FOM was computed at 50 kHz offset.

# Data Sheet

Figure of Merit<sup>1</sup>

# ADRF6620

dBc/Hz

-222

### **RF INPUT TO MIXER OUTPUT SPECIFICATIONS**

VCCx = 5 V,  $T_A = 25^{\circ}C$ , high-side LO injection,  $f_{IF} = 200 \text{ MHz}$ , external LO frequency, and RF attenuation = 0 dB, unless otherwise noted. Mixer settings configured for maximum linearity (see Table 16). All losses from input and output traces and baluns are de-embedded from results.

| Parameter                                          | Test Conditions/Comments                   | Min Typ Max | Unit |  |

|----------------------------------------------------|--------------------------------------------|-------------|------|--|

| VOLTAGE GAIN                                       | Differential 255 $\Omega$ load             | -4          | dB   |  |

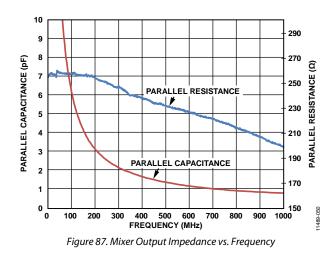

| MIXER OUTPUT IMPEDANCE                             | Differential (see Figure 87)               | 255         | Ω    |  |

| DYNAMIC PERFORMANCE AT f <sub>RF</sub> = 900 MHz   |                                            |             |      |  |

| Voltage Conversion Gain                            |                                            | -2          | dB   |  |

| Input P1dB                                         |                                            | 17          | dBm  |  |

| Input IP3                                          | –5 dBm each input tone, 1 MHz tone spacing | 40          | dBm  |  |

| Input IP2                                          | -5 dBm each input tone, 1 MHz tone spacing | 65          | dBm  |  |

| Noise Figure                                       |                                            | 15          | dB   |  |

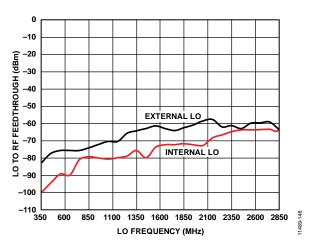

| LO to RF Leakage                                   |                                            | -70         | dBm  |  |

| RF to LO Leakage                                   |                                            | -60         | dBc  |  |

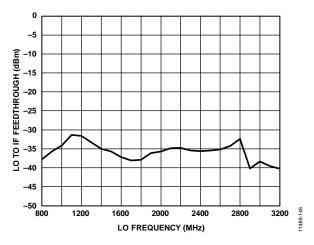

| LO to IF Leakage                                   |                                            | -32         | dBm  |  |

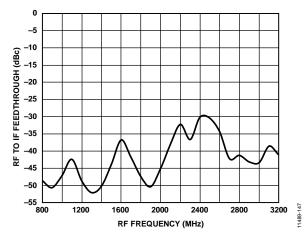

| RF to IF Leakage                                   | With respect to 0 dBm RF input power       | -45         | dBc  |  |

| Isolation <sup>1</sup>                             | Isolation between RFIN0 and RFIN3          | -52         | dBc  |  |

| DYNAMIC PERFORMANCE AT f <sub>RF</sub> =1900 MHz   |                                            |             |      |  |

| Voltage Conversion Gain                            |                                            | -3          | dB   |  |

| Input P1dB                                         |                                            | 17          | dBm  |  |

| Input IP3                                          | -5 dBm each input tone, 1 MHz tone spacing | 40          | dBm  |  |

| Input IP2                                          | –5 dBm each input tone, 1 MHz tone spacing | 62          | dBm  |  |

| Noise Figure                                       |                                            | 17          | dB   |  |

| LO to RF Leakage                                   |                                            | -60         | dBm  |  |

| RF to LO Leakage                                   |                                            | -50         | dBc  |  |

| LO to IF Leakage                                   |                                            | -35         | dBm  |  |

| RF to IF Leakage                                   | With respect to 0 dBm RF input power       | -43         | dBc  |  |

| Isolation <sup>1</sup>                             | Isolation between RFIN0 and RFIN3          | -47         | dBc  |  |

| DYNAMIC PERFORMANCE AT $f_{RF} = 2100 \text{ MHz}$ |                                            |             |      |  |

| Voltage Conversion Gain                            |                                            | -3.5        | dB   |  |

| Input P1dB                                         |                                            | 18          | dBm  |  |

| Input IP3                                          | –5 dBm each input tone, 1 MHz tone spacing | 40          | dBm  |  |

| Input IP2                                          | –5 dBm each input tone, 1 MHz tone spacing | 54.5        | dBm  |  |

| Noise Figure                                       |                                            | 18          | dB   |  |

| LO to RF Leakage                                   |                                            | -60         | dBm  |  |

| RF to LO Leakage                                   |                                            | -40         | dBc  |  |

| LO to IF Leakage                                   |                                            | -35         | dBm  |  |

| RF to IF Leakage                                   | With respect to 0 dBm RF input power       | -40         | dBc  |  |

| Isolation <sup>1</sup>                             | Isolation between RFIN0 and RFIN3          | -45         | dBc  |  |

| DYNAMIC PERFORMANCE AT $f_{RF} = 2700 \text{ MHz}$ |                                            |             |      |  |

| Voltage Conversion Gain                            |                                            | -4.7        | dB   |  |

| Input P1dB                                         |                                            | 19          | dBm  |  |

| Input IP3                                          | -5 dBm each input tone, 1 MHz tone spacing | 40          | dBm  |  |

| Input IP2                                          | -5 dBm each input tone, 1 MHz tone spacing | 56          | dBm  |  |

| Noise Figure                                       |                                            | 21          | dB   |  |

| LO to RF Leakage                                   |                                            | -60         | dBm  |  |

| RF to LO Leakage                                   |                                            | -45         | dBc  |  |

| LO to IF Leakage                                   |                                            | -40         | dBm  |  |

| RF to IF Leakage                                   | With respect to 0 dBm RF input power       | -42         | dBc  |  |

| Isolation <sup>1</sup>                             | Isolation between RFIN0 and RFIN3          | -41         | dBc  |  |

| Table 4. R | F Switch + | Balun + RI | F Attenuator | + Mixer |

|------------|------------|------------|--------------|---------|

|------------|------------|------------|--------------|---------|

<sup>1</sup> Isolation between RF inputs. An input signal was applied to RFIN0 while RFIN1 to RFIN3 were terminated with 50 Ω. The IF signal amplitude was measured at the mixer output. The internal switch was then configured for RFIN3, and the feedthrough was measured as a delta from the fundamental.

### **IF DGA SPECIFICATIONS**

VCCx = 5 V,  $T_A = 25^{\circ}C$ ,  $R_S = R_L = 150 \Omega$  differential,  $f_{IF} = 200 \text{ MHz}$ , 2 V p-p differential output, unless otherwise noted. All losses from input and output traces and baluns are de-embedded from results.

| Parameter                              | Test Conditions/Comments                     | Min | Тур   | Max | Unit |

|----------------------------------------|----------------------------------------------|-----|-------|-----|------|

| BANDWIDTH                              |                                              |     |       |     |      |

| –1 dB Bandwidth                        | $V_{OUT} = 2 V p - p$                        |     | 500   |     | MHz  |

| –3 dB Bandwidth                        | $V_{OUT} = 2 V p - p$                        |     | 700   |     | MHz  |

| SLEW RATE                              |                                              |     | 5.5   |     | V/ns |

| INPUT STAGE                            |                                              |     |       |     |      |

| Input P1dB                             | At minimum gain                              |     | 17    |     | dBm  |

| Input Impedance                        |                                              |     | 150   |     | Ω    |

| Common-Mode Input Voltage              |                                              |     | 1.5   |     | V    |

| Common-Mode Rejection Ratio (CMRR)     |                                              |     | 50    |     | dB   |

| GAIN                                   |                                              |     |       |     |      |

| Power/Voltage Gain, Step Size = 0.5 dB |                                              | 3   |       | 15  | dB   |

| Gain Flatness                          | $50 \text{ MHz} < f_C < 200 \text{ MHz}$     |     | 0.2   |     | dB   |

| Gain Conformance Error                 |                                              |     | ±0.1  |     | dB   |

| Gain Temperature Sensitivity           |                                              |     | 0.008 |     | dB/C |

| Gain Step Response                     |                                              |     | 15    |     | ns   |

| OUTPUT STAGE                           |                                              |     |       |     |      |

| Output P1dB                            |                                              |     | 18    |     | dBm  |

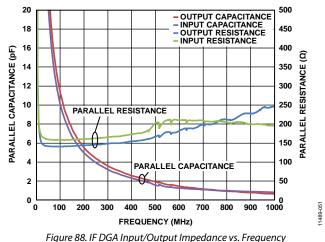

| Output Impedance                       | See Figure 88                                |     | 150   |     | Ω    |

| NOISE/HARMONIC PERFORMANCE at 200 MHz  |                                              |     |       |     |      |

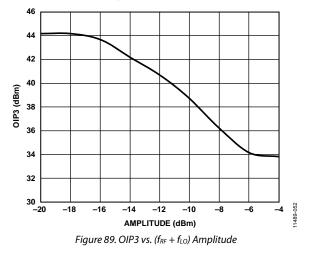

| Output IP3                             | 1 V p-p each output tone, 1 MHz tone spacing |     | 45    |     | dBm  |

| Output IP2                             | 1 V p-p each output tone, 1 MHz tone spacing |     | 63    |     | dBm  |

| HD2                                    | $V_{OUT} = 2 V p - p$                        |     | -87   |     | dBc  |

| HD3                                    | $V_{OUT} = 2 V p - p$                        |     | -84   |     | dBc  |

| Noise Figure                           |                                              |     | 10    |     | dB   |

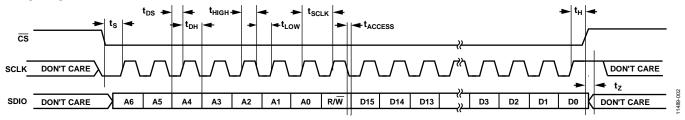

### DIGITAL LOGIC SPECIFICATIONS

| Table | 6. |

|-------|----|

|-------|----|

| Symbol              | Test Conditions/Comments                                                                | Min                                                                                                                                                                                   | Тур                                                                                                                                                                                                                                                                                | Мах                                                    | Unit                                                    |

|---------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|

|                     |                                                                                         |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                    |                                                        |                                                         |

| VIH                 |                                                                                         | 1.4                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                    |                                                        | V                                                       |

| VIL                 |                                                                                         |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                    | 0.70                                                   | V                                                       |

| V <sub>OH</sub>     | $I_{OH} = -100 \ \mu A$                                                                 | 2.3                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                    |                                                        | V                                                       |

| Vol                 | Ι <sub>ΟL</sub> = +100 μΑ                                                               | 0.2                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                    |                                                        | V                                                       |

| t <sub>SCLK</sub>   |                                                                                         | 38                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                    |                                                        | ns                                                      |

| t <sub>DS</sub>     |                                                                                         | 8                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                    |                                                        | ns                                                      |

| t <sub>DH</sub>     |                                                                                         | 8                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                    |                                                        | ns                                                      |

| ts                  |                                                                                         | 10                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                    |                                                        | ns                                                      |

| tн                  |                                                                                         | 10                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                    |                                                        | ns                                                      |

| t <sub>HIGH</sub>   |                                                                                         | 10                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                    |                                                        | ns                                                      |

| t <sub>LOW</sub>    |                                                                                         | 10                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                    |                                                        | ns                                                      |

| t <sub>ACCESS</sub> |                                                                                         |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                    | 231                                                    | ns                                                      |

| tz                  |                                                                                         |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                    | 5                                                      | ns                                                      |

|                     | VIH<br>VIL<br>Voh<br>Vol<br>tsclk<br>tds<br>tdh<br>ts<br>th<br>thigh<br>tlow<br>taccess | $ \begin{array}{c} V_{IH} \\ V_{IL} \\ V_{OH} \\ V_{OL} \\ I_{OL} = +100 \ \mu A \\ t_{SCLK} \\ t_{DS} \\ t_{DH} \\ t_{S} \\ t_{H} \\ t_{HiGH} \\ t_{LOW} \\ t_{ACCESS} \end{array} $ | $ \begin{array}{c c} V_{IH} \\ V_{IL} \\ V_{OH} \\ V_{OL} \\ I_{OL} = +100 \ \mu A \\ t_{SCLK} \\ t_{DS} \\ t_{DH} \\ t_{S} \\ t_{H} \\ t_{H} \\ t_{LOW} \\ t_{ACCESS} \end{array} \qquad \begin{array}{c} 1.4 \\ 2.3 \\ 0.2 \\ 38 \\ 8 \\ 10 \\ 10 \\ 10 \\ 10 \\ 10 \\ 10 \\ 10$ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $ |

Timing Diagram

Figure 2. Serial Port Interface Timing

# **ABSOLUTE MAXIMUM RATINGS**

#### Table 7.

| Parameter                    | Rating           |

|------------------------------|------------------|

| VCCx                         | –0.5 V to +5.5 V |

| RFSW0, RFSW1                 | –0.3 V to +3.6 V |

| RFIN0, RFIN1, RFIN2, RFIN3   | 20 dBm           |

| LOIN-, LOIN+                 | 16 dBm           |

| REFIN                        | –0.3 V to +3.6 V |

| IFIN–, IFIN+                 | –1.2 V to +3.6 V |

| CS, SCLK, SDIO               | –0.3 V to +3.6 V |

| VTUNE                        | –0.3 V to +3.6 V |

| Operating Temperature Range  | -40°C to +85°C   |

| Storage Temperature Range    | –65°C to +150°C  |

| Maximum Junction Temperature | 150°C            |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL RESISTANCE

#### Table 8. Thermal Resistance

| Package Type  | οις  | Unit |

|---------------|------|------|

| 48-Lead LFCSP | 1.62 | °C/W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

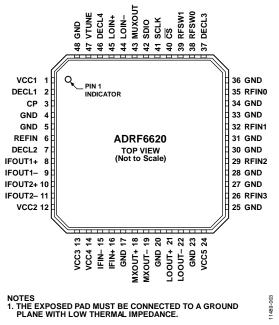

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 3. Pin Configuration

#### Table 9. Pin Function Descriptions<sup>1</sup>

| Din No.                                                 |                                       | Description                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.                                                 | Mnemonic                              | Description                                                                                                                                                                                                                                                                                           |

| 1, 12, 13, 14, 24                                       | VCC1, VCC2, VCC3,<br>VCC4, VCC5       | 5 V Power Supplies. Decouple all power supply pins to ground, using 100 pF and 0.1 μF capacitors. Place the decoupling capacitors near the pins.                                                                                                                                                      |

| 2, 7, 37, 46                                            | DECL1, DECL2,<br>DECL3, DECL4         | Decouple all DECLx pins to ground, using 100 pF, 0.1 $\mu$ F, and 10 $\mu$ F capacitors. Place the decoupling capacitors near the pins.                                                                                                                                                               |

| 3                                                       | СР                                    | Synthesizer Charge Pump Output. Connect this pin to the VTUNE pin through the loop filter.                                                                                                                                                                                                            |

| 4, 5, 17, 20, 23, 25, 27,<br>28, 30, 31, 33, 34, 36, 48 | GND                                   | Ground.                                                                                                                                                                                                                                                                                               |

| 6                                                       | REFIN                                 | Synthesizer Reference Frequency Input.                                                                                                                                                                                                                                                                |

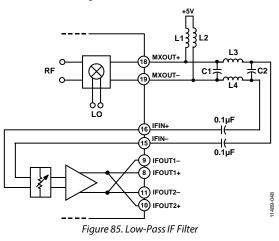

| 8 to 11                                                 | IFOUT1+, IFOUT1-,<br>IFOUT2+, IFOUT2- | IF DGA Outputs. Connect the positive pins such that IFOUT1+ and IFOUT2+ are tied together. Similarly, connect the negative pins such that IFOUT1- and IFOUT2- are tied together. Refer to the Layout section for a recommended layout that minimizes parasitic capacitance and optimizes performance. |

| 15, 16                                                  | IFIN–, IFIN+                          | Differential IF DGA Inputs. AC couple the mixer outputs to the IF DGA inputs.                                                                                                                                                                                                                         |

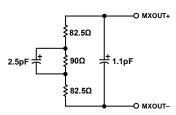

| 18, 19                                                  | MXOUT+, MXOUT-                        | Differential Mixer Outputs. AC couple the mixer outputs to the IF DGA inputs.                                                                                                                                                                                                                         |

| 21, 22                                                  | LOOUT+, LOOUT-                        | Differential LO Outputs. The differential output impedance is 50 $\Omega$ .                                                                                                                                                                                                                           |

| 26, 29, 32, 35                                          | RFIN3, RFIN2,<br>RFIN1, RFIN0         | RF Inputs. These single-ended RF inputs have a 50 $\Omega$ input impedance and must be ac-coupled.                                                                                                                                                                                                    |

| 38, 39                                                  | RFSW0, RFSW1                          | External Pin Control of RF Input Switches. For logic high, connect these pins to 2.5 V logic.                                                                                                                                                                                                         |

| 40                                                      | <u>cs</u>                             | SPI Chip Select, Active Low. 3.3 V tolerant logic levels.                                                                                                                                                                                                                                             |

| 41                                                      | SCLK                                  | SPI Clock. 3.3 V tolerant logic levels.                                                                                                                                                                                                                                                               |

| 42                                                      | SDIO                                  | SPI Data Input or Output. 3.3 V tolerant logic levels.                                                                                                                                                                                                                                                |

| 43                                                      | MUXOUT                                | Multiplexer Output. This output pin provides the PLL reference signal or the PLL lock detect signal.                                                                                                                                                                                                  |

| 44, 45                                                  | LOIN-, LOIN+                          | Differential Local Oscillator Inputs. The differential input impedance is 50 $\Omega$ .                                                                                                                                                                                                               |

| 47                                                      | VTUNE                                 | VCO Tuning Voltage. Connect this pin to the CP pin through the loop filter.                                                                                                                                                                                                                           |

| 49                                                      | EPAD                                  | Exposed Pad. The exposed pad must be connected to a ground plane with low thermal impedance.                                                                                                                                                                                                          |

<sup>1</sup> For more connection information about these pins, see Table 14.

# **TYPICAL PERFORMANCE CHARACTERISTICS**

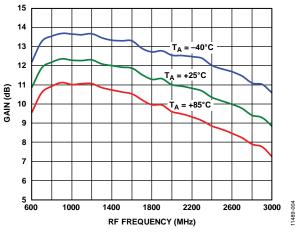

### **RF INPUT TO DGA OUTPUT SYSTEM PERFORMANCE**

VCCx = 5 V,  $T_A = 25^{\circ}C$ , RFDSA\_SEL = 00 (0 dB), RFSW\_SEL = 00 (RFIN0), BAL\_CIN and BAL\_COUT optimized for maximum gain; MIXER\_BIAS, MIXER\_RDAC, and MIXER\_CDAC optimized for highest linearity, DGA at maximum gain; third-order low-pass filter between the mixer output and IF DGA input; high-side LO, internal LO frequency, IF frequency = 200 MHz, unless otherwise noted. All losses from input and output traces and baluns are de-embedded from results.

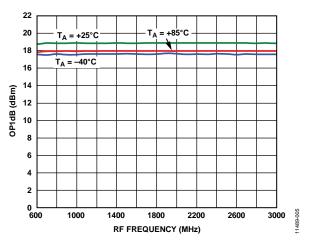

Figure 4. Gain vs. RF Frequency; IF Frequency = 200 MHz

Figure 5. OP1dB vs. RF Frequency

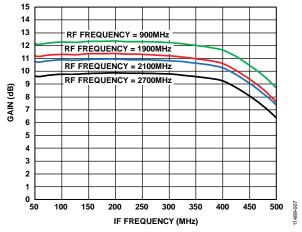

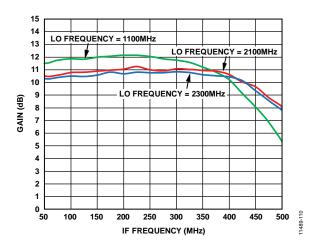

Figure 6. Gain vs. IF Frequency; LO Sweep with Fixed RF, IF Roll-Off

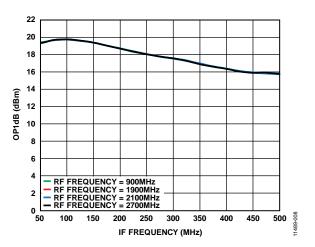

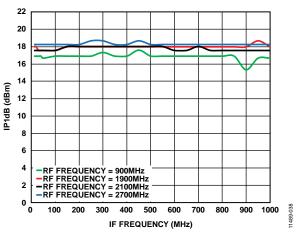

Figure 7. OP1dB vs. IF Frequency; LO Sweep with Fixed RF, IF Roll-Off

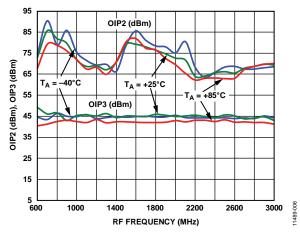

Figure 8. OIP2/OIP3 vs. RF Frequency; Measured on 1 V p-p on Each Tone at DGA Output

Figure 9. Gain vs. IF Frequency; RF Sweep with Fixed LO; IF and RF Roll-Off; Measured on 1 V p-p on Each Tone at DGA Output

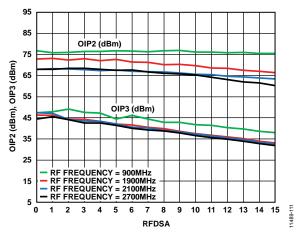

Figure 10. OIP2/OIP3 vs. RFDSA; Measured on 1 V p-p on Each Tone at DGA Output

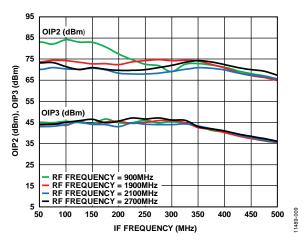

Figure 11. OIP2/OIP3 vs. IF Frequency; LO Sweep with Fixed RF, IF Roll-Off; Measured on 1 V p-p on Each Tone at DGA Output

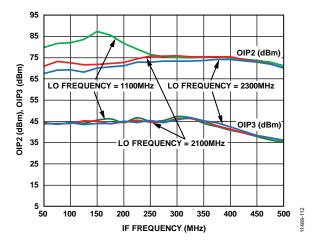

Figure 12. OIP2/OIP3 vs. IF Frequency; RF Sweep with Fixed LO; IF and RF Roll-Off; Measured on 1 V p-p on Each Tone at DGA Output

Rev. 0 | Page 12 of 52

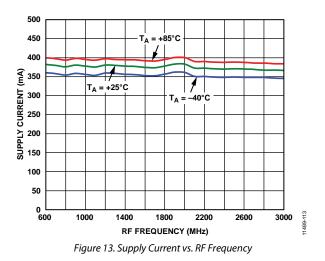

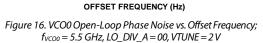

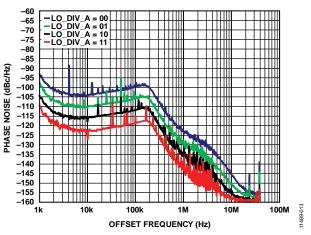

### PHASE-LOCKED LOOP (PLL)

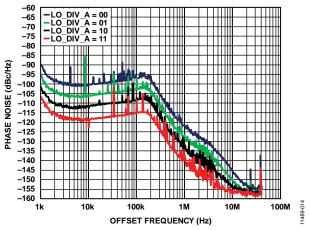

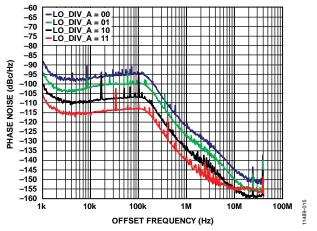

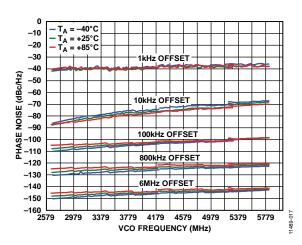

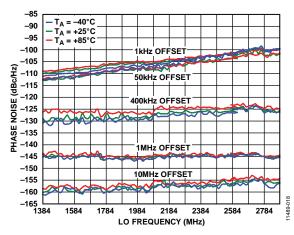

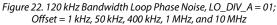

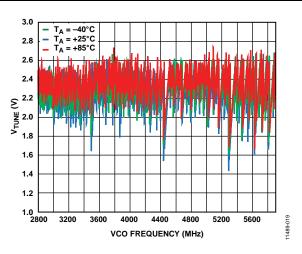

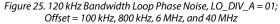

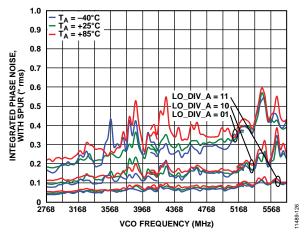

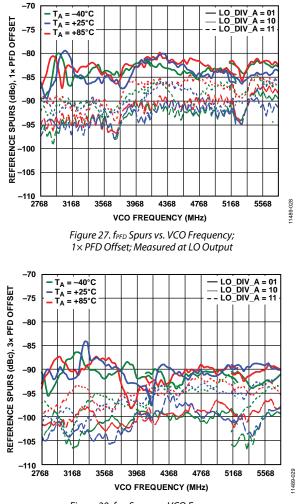

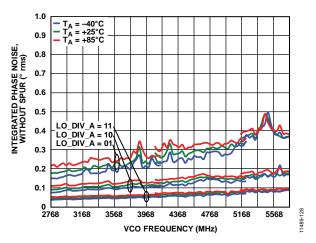

VCCx = 5 V,  $T_A = 25^{\circ}$ C, 120 kHz loop filter,  $f_{REF} = 153.6$  MHz, PLL reference amplitude = 4 dBm,  $f_{PFD} = 38.4$  MHz, measured at LO output, unless otherwise noted.

Figure 17. VCO2 Closed-Loop Phase Noise for Various LO\_DIV\_A Dividers vs. Offset Frequency;  $f_{VCO2} = 3.4 \text{ GHz}$

Figure 18. VCO1 Closed-Loop Phase Noise for Various LO\_DIV\_A Dividers vs. Offset Frequency;  $f_{VCO1} = 4.6 \text{ GHz}$

Figure 19. VCO0 Closed-Loop Phase Noise for Various LO\_DIV\_A Dividers vs. Offset Frequency;  $f_{VCO0} = 5.532$  GHz

Figure 20. PLL Figure of Merit (FOM) vs. LO Frequency

Figure 26. 10 kHz to 40 MHz Integrated Phase Noise vs. VCO Frequency; LO\_DIV\_A = 01, 10, and 11, Including Spurs, for Various LO Divider Ratios

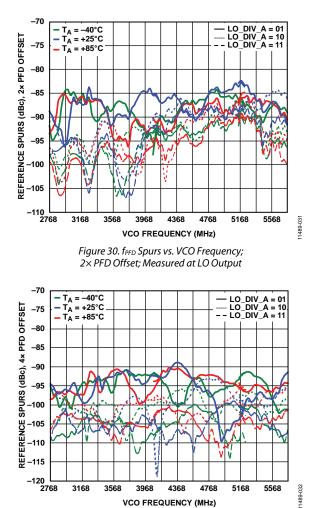

Figure 28. f<sub>PFD</sub> Spurs vs. VCO Frequency; 3× PFD Offset; Measured at LO Output

Figure 29. 10 kHz to 40 MHz Integrated Phase Noise vs. VCO Frequency; LO\_DIV\_A = 01, 10, and 11, Excluding Spurs, for Various LO Divider Ratios

Figure 31. f<sub>PFD</sub> Spurs vs. VCO Frequency; 4× PFD Offset; Measured at LO Output

VCO FREQUENCY (MHz)

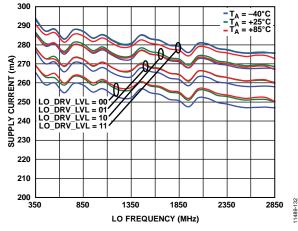

Figure 32. Supply Current vs. LO Frequency; LO\_DRV\_LVL = 00, 01, 10, and 11

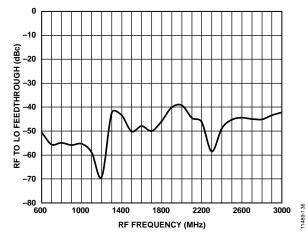

Figure 33. RF to LO Output Feedthrough, LO\_DRV\_LVL = 00

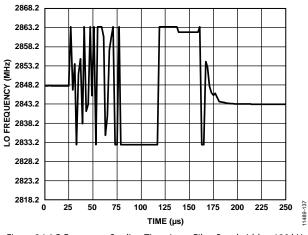

Figure 34. LO Frequency Settling Time, Loop Filter Bandwidth = 120 kHz

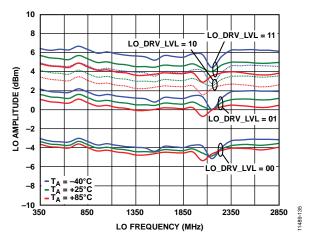

Figure 35. LO Amplitude vs. LO Frequency; LO\_DRV\_LVL = 00, 01, 10, and 11

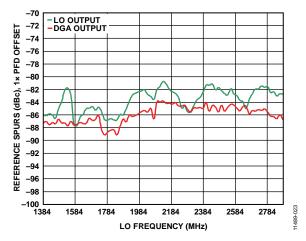

Figure 36.  $f_{PFD}$  Spurs, LO\_DIV\_A = 01, 1× PFD Offset; Measured on LO Output and DGA Output

## Data Sheet

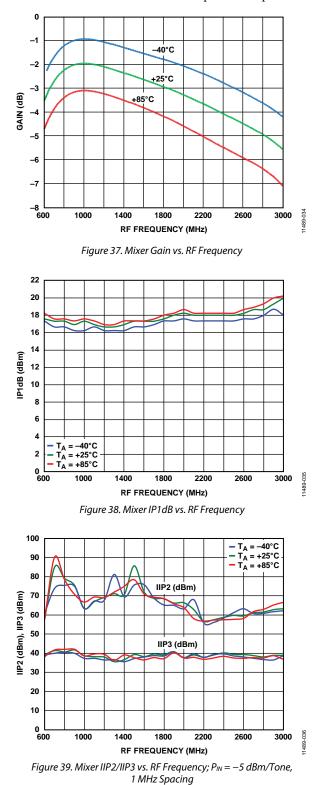

### **RF INPUT TO MIXER OUTPUT PERFORMANCE**

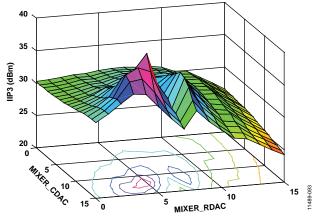

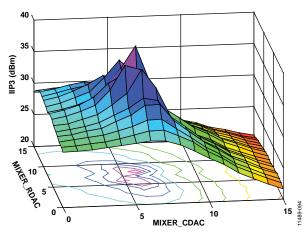

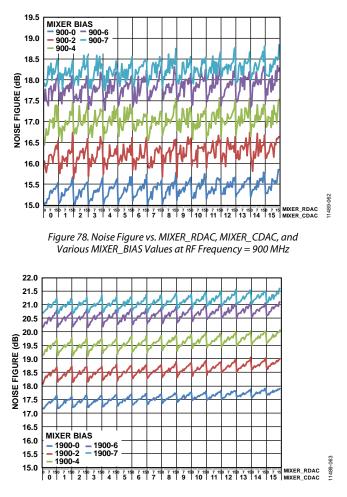

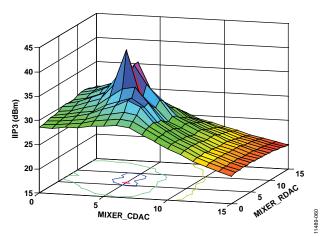

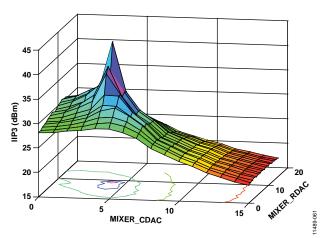

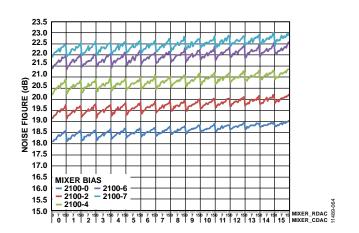

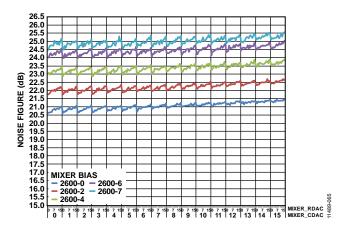

VCCx = 5 V,  $T_A = 25^{\circ}C$ ,  $R_L = 250 \Omega$ , external LO,  $P_{LO} = 0 \text{ dBm}$ , RFDSA\_SEL = 00 (0 dB), RFSW\_SEL = 00 (RFIN0), BAL\_CIN and BAL\_COUT optimized, MIXER\_BIAS, MIXER\_RDAC, and MIXER\_CDAC optimized for highest linearity, DGA and LO output disabled, unless otherwise noted. All losses from input and output traces and baluns are de-embedded from results.

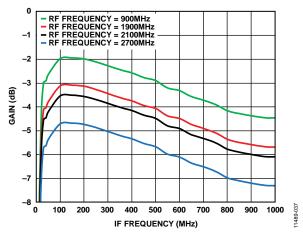

Figure 40. Mixer Gain vs. IF Frequency; LO Sweep with Fixed RF, IF Roll-Off

Figure 41. Mixer IP1dB vs. IF Frequency; LO Sweep with Fixed RF, IF Roll-Off

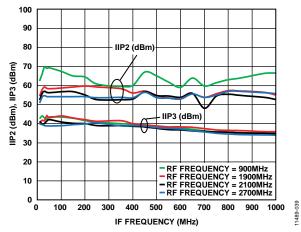

Figure 42. Mixer IIP2/IIP3 vs. IF Frequency; P<sub>IN</sub> = −5 dBm/Tone, 1 MHz Spacing, LO Sweep with Fixed RF, IF Roll-Off

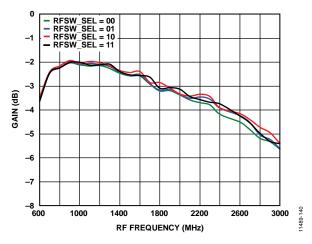

Figure 43. Mixer Gain vs. RF Frequency; RFSW\_SEL = 00, 01, 10, and 11

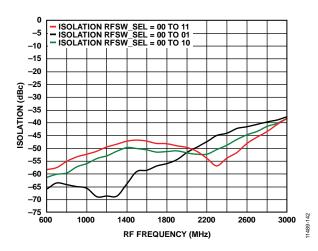

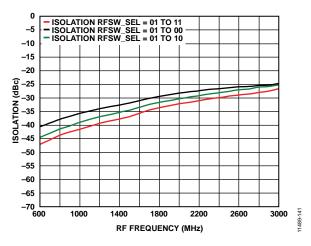

Figure 44. Mixer Input to Mixer Output Isolation vs. RF Frequency; RFSW\_SEL = 00 Driven

Figure 45. Mixer Input to Mixer Output Isolation vs. RF Frequency; RFSW\_SEL = 01 Driven

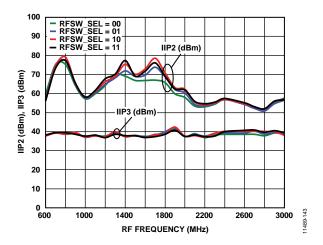

Figure 46. Mixer IIP2/IIP3 vs. RF Frequency; RFSW\_SEL = 00, 01, 10, and 11

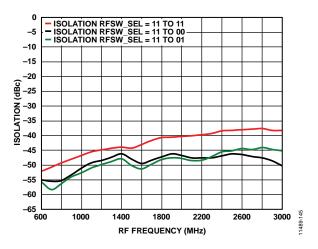

Figure 47. Mixer Input to Mixer Output Isolation vs. RF Frequency; RFSW\_SEL = 11 Driven

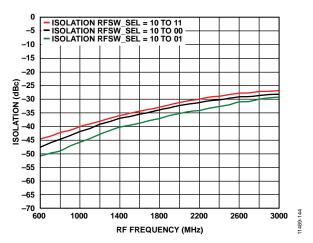

Figure 48. Mixer Input to Mixer Output Isolation vs. RF Frequency; RFSW\_SEL = 10 Driven

# Data Sheet

Figure 49. LO to IF Feedthrough at Mixer Output Without Filtering

Figure 50. RF to IF Feedthrough at Mixer Output Without Filtering; Mixer Input Power = 0 dBm

Figure 51. LO to RF Feedthrough;  $P_{LO} = 0 \, dBm$

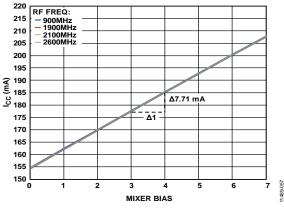

**RF FREQUENCY (MHz)** Figure 52. Icc vs. RF Frequency; DGA and LO Output Disabled

1800

2200

2600

T<sub>A</sub> = +85°C

1000

1400

0

600

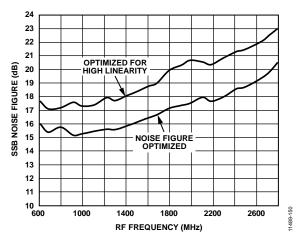

Figure 53. SSB Noise Figure vs. RF Frequency (see Table 16)

# **ADRF6620**

11489-149

3000

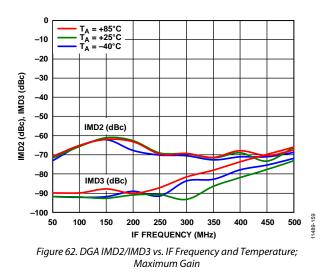

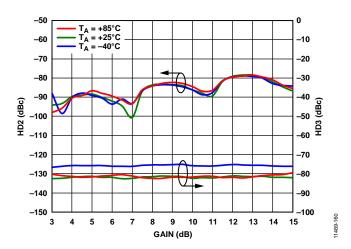

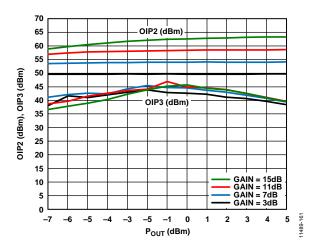

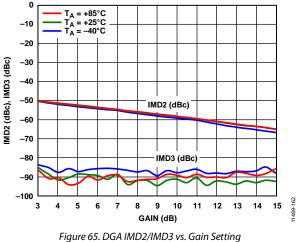

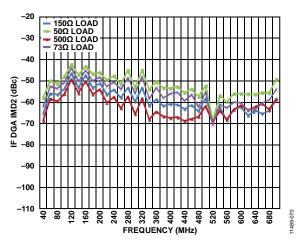

### IF DGA

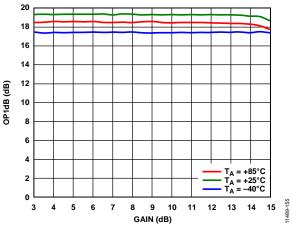

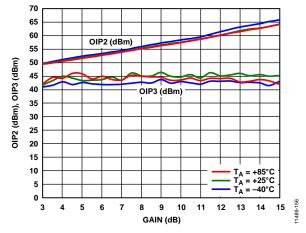

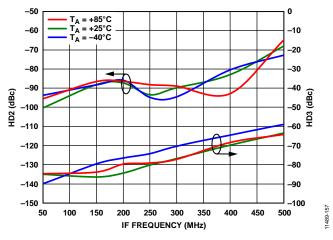

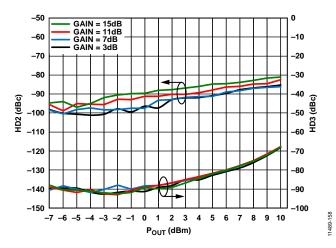

VCCx = 5 V,  $T_A = 25^{\circ}C$ ,  $R_S = R_L = 150 \Omega$ , IF = 200 MHz, 2 V p-p differential output, unless otherwise noted. All losses from input and output traces and baluns are de-embedded from results.

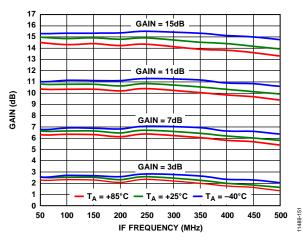

Figure 54. DGA Gain vs. IF Frequency and Temperature

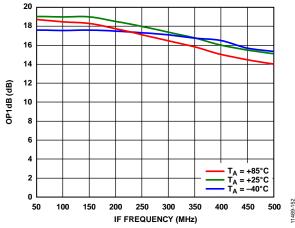

Figure 55. DGA OP1dB vs. Frequency and Temperature; Maximum Gain

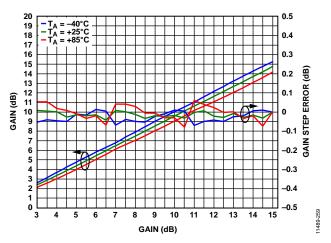

Figure 57. DGA Gain and Gain Step Error vs. Gain Setting and Temperature

Figure 58. DGA OP1dB vs. Gain Setting and Temperature

Figure 59. DGA OIP2/OIP3 vs. Gain Setting and Temperature

## **Data Sheet**

Figure 60. DGA HD2/HD3 vs. IF Frequency and Temperature; Maximum Gain

Figure 61. DGA HD2/HD3 vs. Output Power (POUT) and Gain Setting

Figure 63. DGA HD2/HD3 vs. Gain Setting and Temperature

Figure 64. DGA OIP2/OIP3 vs. Output Power (Pout) and Gain Setting

### **SPURIOUS PERFORMANCE**

$(N \times f_{RF}) - (M \times f_{LO})$  spur measurements were made using the standard evaluation board. Mixer spurious products were measured in decibels (dB) relative to the carrier (dBc) from the IF output power level. Data is shown for all spurious components greater than -115 dBc and frequencies of less than 3 GHz.

#### 915 MHz Performance

VCCx = 5 V,  $T_A = 25^{\circ}$ C, RF power = 0 dBm, internal LO,  $f_{RF} = 914$  MHz,  $f_{LO} = 1114$  MHz

|   |   | Μ    |      |       |       |       |       |       |

|---|---|------|------|-------|-------|-------|-------|-------|

|   |   | 0    | 1    | 2     | 3     | 4     | 5     | 6     |

|   | 0 |      | -34  | -35   |       |       |       |       |

|   | 1 | -43  | 0    | -52   | -16   |       |       |       |

|   | 2 | -72  | -60  | -72   | -67   | -74   |       |       |

| Ν | 3 | -102 | -73  | -103  | -78   | <-115 | -80   |       |

|   | 4 |      | -102 | <-115 | <-115 | <-115 | <-115 |       |

|   | 5 |      |      | <-115 | -105  | <-115 | <-115 | <-115 |

|   | 6 |      |      |       | <-115 | <-115 | <-115 | <-115 |

#### 1910 MHz Performance

VCCx = 5 V,  $T_A = 25^{\circ}$ C, RF power = 0 dBm, internal LO,  $f_{RF} = 1910$  MHz,  $f_{LO} = 2110$  MHz.

|   |   | M       |         |          |         |          |          |       |

|---|---|---------|---------|----------|---------|----------|----------|-------|

|   |   | 0       | 1       | 2        | 3       | 4        | 5        | 6     |

|   | 0 |         | -38.208 |          |         |          |          |       |

|   | 1 | -40.462 | -0.001  | -50.9    |         |          |          |       |

|   | 2 |         | -59.208 | -69.655  | -62.35  |          |          |       |

| Ν | 3 |         |         | -106.741 | -74.322 | -106.429 |          |       |

|   | 4 |         |         |          | <-115   | <-115    | <-115    |       |

|   | 5 |         |         |          | <-115   | <-115    | -110.954 |       |

|   | 6 |         |         |          |         |          | <-115    | <-115 |

### 2140 MHz Performance

VCCx = 5 V,  $T_A$  = 25°C, RF power = 0 dBm, internal LO,  $f_{RF}$  = 2140 MHz,  $f_{LO}$  = 2340 MHz.

|   |   |     | Μ   |       |       |       |       |       |  |

|---|---|-----|-----|-------|-------|-------|-------|-------|--|

|   |   | 0   | 1   | 2     | 3     | 4     | 5     | 6     |  |

|   | 0 |     | -40 |       |       |       |       |       |  |

|   | 1 | -36 | 0   | -45   |       |       |       |       |  |

|   | 2 |     | -58 | -67   | -59   |       |       |       |  |

| Ν | 3 |     |     | <-115 | -74   | <-115 |       |       |  |

|   | 4 |     |     |       | <-115 | <-115 | <-115 |       |  |

|   | 5 |     |     |       |       | <-115 | <-115 | <-115 |  |

|   | 6 |     |     |       |       |       | <-115 | <-115 |  |

### 2700 MHz Performance

VCCx = 5 V,  $T_A$  = 25°C, RF power = 0 dBm, internal LO,  $f_{RF}$  = 2700 MHz,  $f_{LO}$  = 2500 MHz.

|   |   | Μ       |         |        |         |       |       |       |

|---|---|---------|---------|--------|---------|-------|-------|-------|

|   |   | 0       | 1       | 2      | 3       | 4     | 5     | 6     |

|   | 0 |         | -38.613 |        |         |       |       |       |

|   | 1 | -40.126 | -0.001  | -43.84 |         |       |       |       |

|   | 2 |         | -58.299 | -67.06 | -62.116 |       |       |       |

| Ν | 3 |         |         |        | -73.603 | <-115 |       |       |

|   | 4 |         |         |        |         | <-115 | <-115 |       |

|   | 5 |         |         |        |         |       | <-115 | <-115 |

|   | 6 |         |         |        |         |       |       | <-115 |

# THEORY OF OPERATION

The ADRF6620 integrates the essential elements of a multichannel loopback receiver that is typically used in digital predistortion systems. The main features of the ADRF6620 include a single-pole four throw (SP4T) RF input switch with tunable balun, variable attenuation, a wideband active mixer, and digitally programmable variable gain amplifier (DGA). In addition, the ADRF6620 integrates a local oscillator (LO) generation block consisting of a synthesizer and a multicore voltage controlled oscillator (VCO) with an octave range and low phase noise. The synthesizer uses a fractional-N phase-locked loop (PLL) to enable continuous LO coverage from 350 MHz to 2850 MHz.

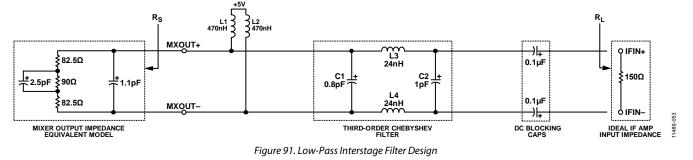

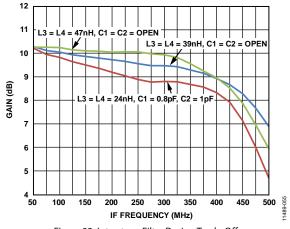

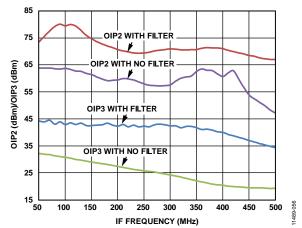

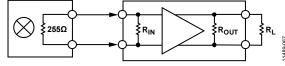

Putting all the building blocks of the ADRF6620 together, the signal path through the device starts at the RF input, where one of four single-ended RF inputs is selected by the input mux and converted to a differential signal via a tunable balun. The differential RF signal is attenuated to an optimal input level via the digital step attenuator with 15 dB of attenuation range in steps of 1 dB. The RF signal is then mixed via a Gilbert cell mixer with the LO signal down to an IF frequency. The 255  $\Omega$  terminated differential output of the mixer is brought off chip to a pair of inductors and passed through an IF filter. The output of the IF filter is ac-coupled off chip and fed to an on-chip digital attenuator and IF DGA. The output of the IF DGA is then passed to an off-chip analog-to-digital converter (ADC).

### **RF INPUT SWITCHES**

Table 10. RF Input Selection Table

The ADRF6620 integrates a SP4T switch where one of four RF inputs is selected. The desired RF input can be selected using either pin control or register writes via the SPI. Compared to the serial write approach, pin control allows faster control over the switch. When the RFSW0 pin (Pin 38) and the RFSW1 pin (Pin 39) are used, the RF switches can switch at speeds of up to

## **Data Sheet**

89

1489

100 ns. When serial port control is used, the switch time is 100 ns, plus the latency of the SPI programming.

The RFSW\_MUX bit (Register 0x23, Bit 11) selects whether the RF input switch is controlled via the external pins or the SPI port. By default at power-up, the device is configured for serial control. Writing to the RFSW\_SEL bits (Register 0x23, Bits[10:9]) allows selection of one of the four RF inputs. Alternatively, by setting the RFSW\_MUX bit high, the RFSW0 and RFSW1 pins can be used to select the RF input. Table 10 summarizes the different control options for the RF inputs.

To maintain good channel-to-channel isolation, ensure that unused RF inputs are properly terminated. The RFINx ports are internally terminated with 50  $\Omega$  resistors and have a dc bias level of 2.5 V. To avoid disrupting the dc level, the recommended termination is a dc blocking capacitor to GND. Figure 66 shows the recommended configuration when only RFIN0 is used, and the other RF input ports are properly terminated.

Figure 66. Terminating Unused RF Input Ports

| RFSW_MUX (Register Address 0x23[11]) | SPI Control, RFSW_SEL<br>(Register Address 0x23[10:9]) |                | Pin Control    |                |                 |

|--------------------------------------|--------------------------------------------------------|----------------|----------------|----------------|-----------------|

| Bit 11                               | Bit 10                                                 | Bit 9          | RFSW1, Pin 39  | RFSW0, Pin 38  | <b>RF Input</b> |

| 0                                    | 0                                                      | 0              | X <sup>1</sup> | X <sup>1</sup> | <b>RFIN0</b>    |

| 0                                    | 0                                                      | 1              | X <sup>1</sup> | X <sup>1</sup> | RFIN1           |

| 0                                    | 1                                                      | 0              | X <sup>1</sup> | X <sup>1</sup> | RFIN2           |

| 0                                    | 1                                                      | 1              | X <sup>1</sup> | X <sup>1</sup> | RFIN3           |

| 1                                    | X <sup>1</sup>                                         | X <sup>1</sup> | 0              | 0              | <b>RFINO</b>    |

| 1                                    | X <sup>1</sup>                                         | X <sup>1</sup> | 0              | 1              | RFIN1           |

| 1                                    | X <sup>1</sup>                                         | X <sup>1</sup> | 1              | 0              | RFIN2           |

| 1                                    | X <sup>1</sup>                                         | X <sup>1</sup> | 1              | 1              | RFIN3           |

$^{1}$  X = don't care.