# Voltage-to-Frequency and Frequency-to-Voltage Converter

ADVFC32

FEATURES

High Linearity

±0.01% Max at 10 kHz FS

±0.05% Max at 100 kHz FS

±0.2% Max at 500 kHz FS

Output TTL/CMOS-Compatible

V/F or F/V Conversion

6 Decade Dynamic Range

Voltage or Current Input

Reliable Monolithic Construction

MIL-STD-883-Compliant Versions Available

#### PRODUCT DESCRIPTION

The industry standard ADVFC32 is a low cost monolithic voltage-to-frequency (V/F) converter or frequency-to-voltage (F/V) converter with good linearity (0.01% max error at 10 kHz) and operating frequency up to 0.5 MHz. In the V/F configuration, positive or negative input voltages or currents can be converted to a proportional frequency using only a few external components. For F/V conversion, the same components are used with a simple biasing network to accommodate a wide range of input logic levels.

TTL or CMOS compatibility is achieved in the V/F operating mode using an open collector frequency output. The pull-up resistor can be connected to voltages up to 30 volts, or to 15 V or 5 V for conventional CMOS or TTL logic levels. This resistor should be chosen to limit current through the open collector output to 8 mA. A larger resistance can be used if driving a high impedance load.

Input offset drift is only 3 ppm of full scale per °C, and full-scale calibration drift is held to a maximum of 100 ppm/°C (ADVFC32BH) due to a low T.C. Zener diode.

The ADVFC32 is available in commercial, industrial, and extended temperature grades. The commercial grade is packaged in a 14-lead plastic DIP while the two wider temperature range parts are packaged in hermetically sealed 10-lead cans.

#### PRODUCT HIGHLIGHTS

1. The ADVFC32 uses a charge balancing circuit technique (see Functional Block Diagram) which is well suited to high accuracy voltage-to-frequency conversion. The full-scale operating frequency is determined by only one precision resistor and capacitor. The tolerance of other support components (including the integration capacitor) is not critical. Inexpensive ±20% resistors and capacitors can be used without affecting linearity or temperature drift.

#### REV. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

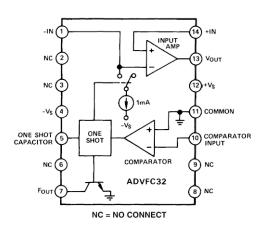

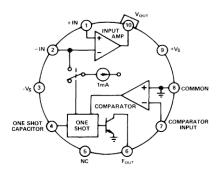

## PIN CONFIGURATION (TOP VIEW)

#### N-14 Package

H-10A Package

NC = NO CONNECT

- 2. The ADVFC32 is easily configured to satisfy a wide range of system requirements. Input voltage scaling is set by selecting the input resistor which sets the input current to 0.25 mA at the maximum input voltage.

- 3. The same components used for V/F conversion can also be used for F/V conversion by adding a simple logic biasing network and reconfiguring the ADVFC32.

- 4. The ADVFC32 is intended as a pin-for-pin replacement for VFC32 devices from other manufacturers.

- The ADVFC32 is available in versions compliant with MIL-STD-883. Refer to the Analog Devices Military Products Databook or current ADVFC32/883B data sheet for detailed specifications.

#

|                                                            |                  | FC32K                |                               |                       | FC32B                |                     |                 | VFC32S               |                     |                                         |

|------------------------------------------------------------|------------------|----------------------|-------------------------------|-----------------------|----------------------|---------------------|-----------------|----------------------|---------------------|-----------------------------------------|

| Model                                                      | Min              | Тур                  | Max                           | Min 7                 | ур                   | Max                 | Min             | Тур                  | Max                 | Unit                                    |

| DYNAMIC PERFORMANCE                                        |                  |                      |                               |                       |                      |                     |                 |                      |                     |                                         |

| Full-Scale Frequency Range                                 | 0                |                      | 500                           | 0                     |                      | 500                 | 0               |                      | 500                 | kHz                                     |

| Nonlinearity <sup>1</sup>                                  | 0.01             |                      | 1001                          | 0.01                  |                      |                     | 0.01            |                      | . 0 01              | 0/                                      |

| $f_{MAX} = 10 \text{ kHz}$                                 | -0.01            |                      | ±0.01                         | -0.01                 |                      | +0.01               | -0.01           |                      | +0.01               | %                                       |

| $f_{MAX} = 100 \text{ kHz}$                                | -0.05            | +0.05                | <b>+0.05</b><br><b>+</b> 0.20 | <b>-0.05</b><br>-0.20 | ±0.05                | +0.05               | -0.05           | ±0.05                | +0.05<br>+0.20      | %                                       |

| f <sub>MAX</sub> = 0.5 MHz<br>Full-Scale Calibration Error | -0.20            | ±0.05                | +0.20                         | -0.20                 | ±0.05                | +0.20               | -0.20           | ±0.05                | +0.20               | %0                                      |

| (Adjustable to Zero)                                       |                  | ±5                   |                               |                       | ±5                   |                     |                 | ±5                   |                     | %                                       |

| vs. Supply                                                 |                  | ± <i>y</i>           |                               |                       | ± <i>J</i>           |                     |                 | ± <i>J</i>           |                     | 70                                      |

| (Full-Scale Frequency = 100 kHz)                           | -0.015           |                      | +0.015                        | -0.015                |                      | +0.015              | -0.015          |                      | +0.015              | % of FSR?                               |

| vs. Temperature                                            |                  |                      |                               |                       |                      |                     |                 |                      |                     | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

| (Full-Scale Frequency = 10 kHz)                            |                  | ±75                  |                               | -100                  |                      | +100                | +150            |                      | +150                | ppm/°C                                  |

| DYNAMIC RESPONSE                                           |                  |                      |                               |                       |                      |                     |                 |                      |                     |                                         |

| Maximum Settling Time for Full Scale                       |                  |                      |                               |                       |                      |                     |                 |                      |                     |                                         |

| Step Input                                                 | 1 Pulse of New   | Frequency            | Plue 1 He                     | 1 Pulse of New        | Frequency            | Plue 1 He           | 1 Pulse of Ne   | w Frequency          | Plue 1 He           |                                         |

| Overload Recovery Time                                     | 1 Pulse of New   |                      |                               | 1 Pulse of New        |                      |                     | 1 Pulse of Ne   |                      |                     |                                         |

|                                                            | 1 1 disc of fiew | Trequency            | 11α51 μ5                      | T T tilse of New      | Trequency            | 11α3 1 μ3           | 1 1 disc of ive | w i requerie,        | 11α3 1 μ3           |                                         |

| ANALOG INPUT AMPLIFIER                                     |                  |                      |                               |                       |                      |                     |                 |                      |                     |                                         |

| (V/F Conversion)                                           |                  |                      | 0.05                          | 0                     |                      | 0.05                |                 |                      | 0.05                |                                         |

| Current Input Range                                        | 0                |                      | 0.25                          | 0                     |                      | 0.25                | 0               |                      | 0.25                | mA<br>V <sup>2</sup>                    |

| Voltage Input Range                                        | 0                |                      | -10<br>0.25                   | 0                     |                      | -10<br>0.25         | 0               |                      | -10<br>0.25         | mA                                      |

|                                                            |                  |                      | $\times R_{\rm IN}^{3}$       |                       |                      | $\times R_{IN}^{3}$ |                 |                      | $\times R_{IN}^{3}$ | IIIA                                    |

| Differential Impedance                                     | 300 kΩ  10 pF    | 2 MΩ  10             |                               | 300 kΩ  10 pF         | 2 MOII10             |                     | 300 kΩ  10 pF   | 2 MOII10             |                     |                                         |

| Common-Mode Impedance                                      | 300 MΩ  3 pF     | 750 MΩ               |                               | 300 MΩ  3 pF          |                      |                     | 300 MΩ  3 pF    |                      |                     |                                         |

| Input Bias Current                                         | Joo Williams bi  | 150 11111            | 5 P1                          | 300 Milian pr         | 130 11122            | 10 р1               | 500 11121  5 PI | 130 11111            | 10 p1               |                                         |

| Noninverting Input                                         |                  | 40                   | 250                           |                       | 40                   | 250                 |                 | 40                   | 250                 | nA                                      |

| Inverting Input                                            | -100             | ±8                   | +100                          | -100                  | ±8                   | +100                | -100            | ±8                   | +100                | nA                                      |

| Input Offset Voltage                                       |                  |                      |                               |                       |                      |                     |                 |                      |                     |                                         |

| (Trimmable to Zero) <sup>2, 3</sup>                        |                  |                      | 4                             |                       |                      | 4                   |                 |                      | 4                   | mV                                      |

| vs. Temperature ( $T_{MIN}$ to $T_{MAX}$ )                 |                  |                      | 30                            |                       |                      | 30                  |                 |                      | 30                  | μV/°C                                   |

| Safe Input Voltage                                         |                  | $\pm V_S$            |                               |                       | $\pm V_S$            |                     |                 | $\pm V_S$            |                     |                                         |

| COMPARATOR (F/V Conversion)                                |                  |                      |                               |                       |                      |                     |                 |                      |                     |                                         |

| Logic "0" Level                                            | -V <sub>S</sub>  |                      | -0.6                          | -V <sub>S</sub>       |                      | -0.6                | $-V_S$          |                      | -0.6                | V                                       |

| Logic "1" Level                                            | 1                |                      | +V <sub>s</sub>               | 1                     |                      | +V <sub>S</sub>     | 1               |                      | $+V_S$              | V                                       |

| Pulse Width Range <sup>4</sup>                             | 0.1              |                      | $0.15/f_{MAX}$                | 0.1                   |                      | $0.15/f_{MAX}$      | 0.1             |                      | $0.15/f_{MAX}$      | μs                                      |

| Input Impedance                                            | 50 kΩ  10 pF     | $250~\text{k}\Omega$ |                               | 50 kΩ∥10 pF           | $250~\text{k}\Omega$ |                     | 50 kΩ∥10 pF     | $250~\text{k}\Omega$ |                     |                                         |

| OPEN COLLECTOR OUTPUT                                      |                  |                      |                               |                       |                      |                     |                 |                      |                     |                                         |

| (V/F Conversion)                                           |                  |                      |                               |                       |                      |                     |                 |                      |                     |                                         |

| Output Voltage in Logic "0"                                |                  |                      |                               |                       |                      |                     |                 |                      |                     |                                         |

| I <sub>SINK</sub> = 8 mA                                   |                  |                      | 0.4                           |                       |                      | 0.4                 |                 |                      | 0.4                 | V                                       |

| Output Leakage Current in Logic "1"                        |                  |                      | 1                             |                       |                      | 1                   |                 |                      | 1                   | μA                                      |

| Voltage Range                                              | 0                |                      | 30                            | 0                     |                      | 30                  | 0               |                      | 30                  | V                                       |

| Fall Times (Load = 500 pF and                              |                  |                      |                               |                       |                      |                     |                 |                      |                     |                                         |

| $I_{SINK} = 5 \text{ mA}$                                  |                  |                      | 400                           |                       |                      | 400                 |                 |                      | 400                 | ns                                      |

| AMPLIFIER OUTPUT (F/V Conversion)                          |                  |                      |                               |                       |                      |                     |                 |                      |                     |                                         |

| Voltage Range (0 mA\leq I_0\leq 7 mA)                      | 0                |                      | 10                            | 0                     |                      | 10                  | 0               |                      | 10                  | v                                       |

| Source Current $(0 \le V_0 \le 7 \text{ V})$               | 10               |                      |                               | 10                    |                      |                     | 10              |                      |                     | mA                                      |

| Capacitive Load (Without Oscillation)                      |                  |                      | 100                           | 10                    |                      | 100                 | 10              |                      | 100                 | pF                                      |

| Closed Loop Output Impedance                               |                  |                      | 1                             |                       |                      | 1                   |                 |                      | 1                   | Ω                                       |

| POWER SUPPLY                                               |                  |                      |                               |                       |                      |                     |                 |                      |                     |                                         |

| Rated Voltage                                              |                  | ±15                  |                               |                       | ±15                  |                     |                 | ±15                  |                     | v                                       |

| Voltage Range                                              | ±9               | ±13                  | ±18                           | ±9                    | ±13                  | ±18                 | ±9              | 113                  | ±18                 | v                                       |

| Quiescent Current                                          | = /              | 6                    | 8                             |                       | 6                    | 8                   |                 | 6                    | 8                   | mA                                      |

|                                                            | <del> </del>     | -                    | -                             |                       |                      | -                   |                 | -                    | -                   |                                         |

| TEMPERATURE RANGE                                          |                  |                      | . 70                          | 25                    |                      | .05                 |                 |                      | . 105               | 00                                      |

| Specified Range                                            | 0                |                      | +70                           | -25<br>5.5            |                      | +85                 | -55<br>-5       |                      | +125                | °C                                      |

|                                                            | -25              |                      | +85<br>+85                    | -55<br>-55            |                      | +125                | -55             |                      | +125                | °C                                      |

| Operating Range                                            |                  |                      | +83                           | -65                   |                      | +150                | -65             |                      | +150                |                                         |

| Storage                                                    | -25              |                      |                               |                       |                      |                     |                 |                      |                     |                                         |

|                                                            | -25              |                      | .03                           |                       |                      |                     |                 |                      |                     |                                         |

| Storage                                                    |                  | FC32KN               |                               |                       |                      |                     |                 |                      |                     |                                         |

Specifications shown in **boldface** are tested on all production units at final electrical test. Results from those tests are used to calculate outgoing quality levels. All min and max specifications are guaranteed, although only those shown in boldface are tested on all production units.

Specifications subject to change without notice.

NOTES

Nonlinearity defined as deviation from a straight line from zero to full scale, expressed as a percentage of full scale.

See Figure 3.

See Figure 1.

4f<sub>MAX</sub> expressed in units of MHz.

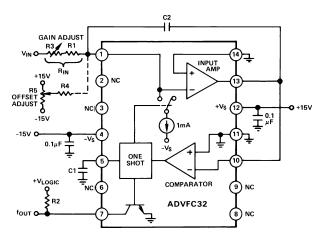

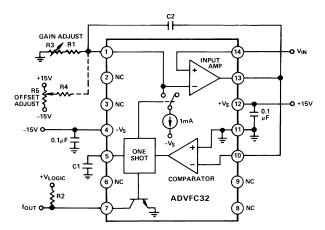

#### UNIPOLAR V/F, POSITIVE INPUT VOLTAGE

When operated as a V/F converter, the transformation from voltage to frequency is based on a comparison of input signal magnitude to the 1 mA internal current source.

A more complete understanding of the ADVFC32 requires a close examination of the internal circuitry of this part. Consider the operation of the ADVFC32 when connected as shown in Figure 1. At the start of a cycle, a current proportional to the

Figure 1. Connection Diagram for V/F Conversion, Positive Input Voltage

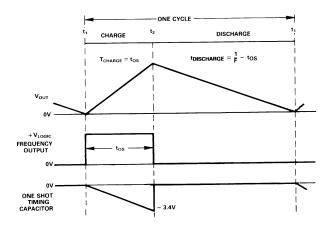

input voltage flows through R3 and R1 to charge integration capacitor C2. As charge builds up on C2, the output voltage of the input amplifier decreases. When the amplifier output voltage (Pin 13) crosses ground (see Figure 2 at time  $t_1$ ), the comparator triggers a one shot whose time period is determined by capacitor C1. Specifically, the one shot time period (in nanoseconds) is:

$$t_{OS} \cong (C_1 + 44 pF) \times 6.7 k\Omega$$

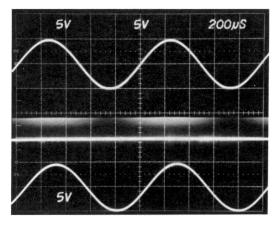

Figure 2. Voltage-to-Frequency Conversion Waveforms

During this period, a current of (1 mA –  $I_{IN}$ ) flows out of the integration capacitor. The total amount of charge depleted during one cycle is, therefore (1 mA –  $I_{IN}$ ) ×  $t_{OS}$ . This charge is

replaced during the remainder of the cycle to return the integrator to its original voltage. Since the charge taken out of C2 is equal to the charge that is put on C2 every cycle,

$$(1 mA - I_{IN}) \times t_{OS} = I_{IN} \times \left(\frac{1}{F_{OUT}} - t_{OS}\right)$$

or, rearranging terms,

$$F_{OUT} = \frac{I_{IN}}{1 \, mA \times t_{OS}}$$

The complete transfer equation can now be derived by substituting  $I_{\rm IN}$  =  $V_{\rm IN}/R_{\rm IN}$  and the equation relating C1 and  $t_{\rm OS}$ . The final equation describing ADVFC32 operation is:

$$\frac{V_{IN}/R_{IN}}{1\,mA\times\left(C_1+44\,pF\right)\times6.7\,k\Omega}$$

Components should be selected to optimize performance over the desired input voltage and output frequency range using the equations listed below:

$$\frac{3.7\times10^7\,pF/sec}{F_{OUT\,FS}}-44\,pF$$

$$C_2 = \frac{10^{-4} Farads / sec}{F_{OUT FS}} \left(1000 pF minimum\right)$$

$$R_{IN} = \frac{V_{IN\ FS}}{0.25\ mA}$$

$$R_2 \ge \frac{+V_{LOGIC}}{8 \, mA}$$

Both  $R_{\rm IN}$  and  $C_1$  should have very low temperature coefficients as changes in their values will result in a proportionate change in the V/F transfer function. Other component values and temperature coefficients are not critical.

Table I. Suggested Values for C<sub>1</sub>, R<sub>IN</sub> and C<sub>2</sub>

| V <sub>IN FS</sub> | F <sub>OUT FS</sub> | C <sub>1</sub> | R <sub>IN</sub> | C <sub>2</sub> |

|--------------------|---------------------|----------------|-----------------|----------------|

| 1 V                | 10 kHz              | 3650 pF        | 4.0 kΩ          | 0.01 μF        |

| 10 V               | 10 kHz              | 3650 pF        | 40 kΩ           | 0.01 μF        |

| 1 V                | 100 kHz             | 330 pF         | 4.0 kΩ          | 1000 pF        |

| 10 V               | 100 kHz             | 330 pF         | 40 kΩ           | 1000 pF        |

#### **ORDERING GUIDE**

| Part                | Gain Tempco | Temp Range  | Package               |

|---------------------|-------------|-------------|-----------------------|

| Number <sup>1</sup> | ppm/°C      | °C          | Option                |

| ADVFC32KN           | ±75 typ     | 0 to 70     | 14-Pin<br>Plastic DIP |

| ADVFC32BH           | ±100 max    | -25 to +85  | TO-100                |

| ADVFC32SH           | ±150 max    | -55 to +125 | TO-100                |

NOTE

<sup>1</sup>For details on grade and package offerings screened in accordance with MIL-STD-883, refer to the Analog Devices Military Products Databook or current ADVFC32/883B data sheet.

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADVFC32 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. B -3-

### ADVFC32

Input resistance  $R_{\rm IN}$  is composed of a fixed resistor (R1) and a variable resistor (R3) to allow for initial gain error compensation. To cover all possible situations, R3 should be 20% of  $R_{\rm IN}$ , and R1 should be 90% of  $R_{\rm IN}$ . This allows a  $\pm 10\%$  gain adjustment to compensate for the ADVFC32 full-scale error and the tolerance of C1.

If more accurate initial offset is required, the circuit of R4 and R5 can be added. R5 can have a value between  $10~\text{k}\Omega$  and  $100~\text{k}\Omega$ , and R4 should be approximately  $10~\text{M}\Omega$ . The amount of current required to trim zero offset will be relatively small, so the temperature coefficients of these resistors are not critical. If large offsets are added using this circuit, temperature drift of both of these resistors is much more important.

#### **BIPOLAR V/F**

By adding another resistor from Pin 1 (Pin 2 of TO-100 can) to a stable positive voltage, the ADVFC32 can be operated with a bipolar input voltage. For example, an 80 k $\Omega$  resistor to 10 V causes an additional current of 0.125 mA to flow into the integrator so that the net current flow to the integrator is positive even for negative input voltages. At negative full-scale input voltage, 0.125 mA will flow into the integrator from  $V_{\rm IN}$  cancelling out the 0.125 mA from the offset resistor, resulting in an output frequency of zero. At positive full scale, the sum of the two currents will be 0.25 mA and the output will be at its maximum frequency.

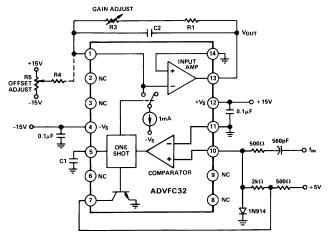

#### UNIPOLAR V/F, NEGATIVE INPUT VOLTAGE

Figure 3 shows the connection diagram for V/F conversion of negative input voltages. In this configuration full-scale output frequency occurs at negative full-scale input, and zero output frequency corresponds to zero input voltage.

Figure 3. Connection Diagram for V/F Conversion, Negative Input Voltage

A very high impedance signal source may be used since it only drive the noninverting integrator input. Typical input impedance at this terminal is 250  $M\Omega$  or higher. For V/F conversion of positive input signals the signal generator must be able to source 0.25 mA to properly drive the ADVFC32, but for negative V/F conversion the 0.25 mA integration current is drawn from ground through R1 and R3.

Circuit operation for negative input voltages is very similar to positive input unipolar conversion described in the previous section. For best operating results use component equations listed in that section.

#### F/V CONVERSION

Although the mathematics of F/V conversion can be very complex, the basic principle is easy to understand. Figure 4 shows the connection diagram for F/V conversion with TTL input logic levels. Each time the input signal crosses the comparator threshold going negative, the one shot is activated and switches 1 mA into the integrator input for a measured time period (determined by C1). As the frequency increases, the amount of charge injected into the integration capacitor increases proportionately. The voltage across the integration capacitor is stabilized when the leakage current through R1 and R3 equals the average current being switched into the integrator. The net result of these two effects is an average output voltage which is proportional to the input frequency. Optimum performance can be obtained by selecting components using the same guidelines and equations listed in the V/F conversion section.

Figure 4. Connection Diagram for F/V Conversion, TTL Input

#### **DECOUPLING**

Decoupling power supplies at the device is good practice in any system, but absolutely imperative in high resolution applications. For the ADVFC32, it is important to remember where the voltage transients and ground currents flow. For example, the current drawn through the output pull-down transistor originates from the logic supply, and is directed to ground through Pin 11 (Pin 8 of TO-100). Therefore, the logic supply should be decoupled near the ADVFC32 to provide a low impedance return path for switching transients. Also, if there is a separate digital ground it should be connected to the analog ground at the ADVFC32. This will prevent ground offsets that could be created by directing the full 8 mA output current into the analog ground, and subsequently back to the logic supply.

Although some circuits may operate satisfactorily with the power supplies decoupled at only one location on each board, this practice is not recommended for the ADVFC32. For best results, each supply should be decoupled with 0.1  $\mu$ F capacitor at the ADVFC32. In addition, a larger board level decoupling capacitor of 1  $\mu$ F to 10  $\mu$ F should be located relatively close to the ADVFC32 on each power supply.

#### COMPONENT TEMPERATURE COEFFICIENTS

The drift specifications of the ADVFC32 do not include temperature effects of any of the supporting resistors or capacitors. The drift of the input resistors R1 and R3 and the timing capacitor C1 directly affect the overall temperature stability. In the

-4- REV. B

application of Figure 2, a 10 ppm/°C input resistor used with a 100 ppm/°C capacitor may result in a maximum overall circuit gain drift of:

100 ppm/°C (ADVFC32BH) + 100 ppm/°C (C1) + 10 ppm/°C ( $R_{\rm IN}$ ) = 210 ppm/°C

Although  $R_{\rm IN}$  and C1 have the most pronounced effect on temperature stability, the offset circuit of resistors R4 and R5 may also have a slight effect on the offset temperature drift of the circuit. The offset will change with variations in the resistance of R4 and supply voltage changes. In most applications the offset adjustment is very small, and the offset drift attributable to this circuit will be negligible. In the bipolar mode, however, both the positive reference and the resistor used to offset the signal range will have a pronounced effect on offset drift. A high quality reference and resistor should be used to minimize offset drift errors.

Other circuit components do not directly influence temperature performance as long as their actual values are not so different from nominal value as to preclude operation. This includes integration capacitor C2. A change in the capacitance value of C2 results in a different rate of voltage change across C2, but this is compensated by an equal effect when C2 is discharged by the switched 1 mA current source so that no net effect occurs.

The temperature effects of the components described above are the same when the ADVFC32 is configured for negative or bipolar input ranges, or F/V conversion.

#### OTHER CIRCUIT CONSIDERATIONS

The input amplifier connected to Pins 1, 13, and 14 is not a standard operational amplifier. Although it operates like an op amp in most applications, two key differences should be noted. First, the bias current of the positive input is typically 40 nA while the bias current of the inverting input is ±8 nA. Therefore, any attempt to cancel input offset voltage due to bias currents by matching input resistors will create worse offsets. Second, the output of this amplifier will sink only 1 mA, even though it will source as much as 10 mA. When used in the F/V mode, the amplifier must be buffered if large sink currents are required.

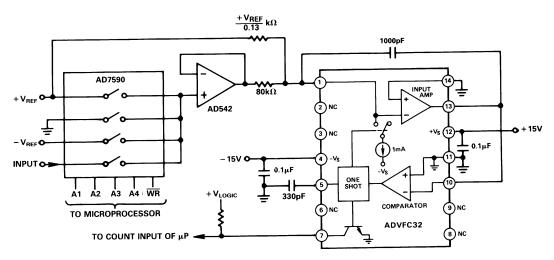

#### MICROPROCESSOR OPERATED A/D CONVERTER

With the addition of a few external components the ADVFC32 can be used as a  $\pm 10$  V A/D microprocessor front end. Although

the nonlinearity of the ADVFC32 is only 0.05% maximum (0.01% typ), the resolution is much higher, allowing it to be used in 16-bit measurement and control systems where a monotonic transfer function is essential. The resolution of the circuit shown in Figure 5 is dependent on the amount of time allowed to count the ADVFC32 frequency output. Using a full-scale frequency of 100 kHz, an 8-bit conversion can be made in about 10 ms, and a 2 second time period allows a 16-bit measurement, including offset and gain calibration cycles.

As shown in Figure 5, the input signal is selected via the AD7590 input multiplexer. Positive and negative references as well as a ground input are provided to calibrate the A/D. This is very important in systems subject to moderate or extreme temperature changes since the gain temperature coefficient of the ADVFC32 is as high as  $\pm 150$  ppm/°C. By using the calibration cycles, the A/D conversion will be as accurate as the references provided. The AD542 following the input multiplexer provides a high impedance input ( $10^{12}$  ohms) and buffers the switch resistance from the relatively low impedance ADVFC32 input.

If higher linearity is required, the ADVFC32 can be operated at 10 kHz, but this will require a proportionately longer conversion time. Conversely, the conversion time can be decreased at the expense of nonlinearity by increasing the maximum frequency to as high as 500 kHz.

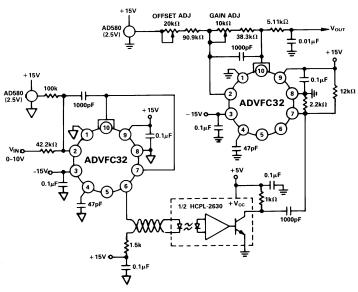

## HIGH NOISE IMMUNITY, HIGH CMRR ANALOG DATA LINK

In many applications, a signal must be sensed at a remote site and sent through a very noisy environment to a central location for further processing. In these cases, even a shielded cable may not protect the signal from noise pickup. The circuit of Figure 6 provides a solution in these cases. Due to the optocoupler and voltage-to-frequency conversion, this data link is extremely insensitive to noise and common-mode voltage interference. For even more protection, an optical fiber link substituted for the HCPL2630 will provide common-mode rejection of more than several hundred kilovolts and virtually total immunity to electrical noise. For most applications, however, the frequency modulated signal has sufficient noise immunity without using an optical fiber link, and the optocoupler provides common-mode isolation up to 3000 V dc.

Figure 5. High Resolution, Self-Calibrating, Microprocessor Operated A/D Converter

Figure 6. High Noise Immunity Data Link

The data link input voltage is changed in a frequency modulated signal by the first ADVFC32. A 42.2 k $\Omega$  input resistor and a 100 k $\Omega$  offset resistor set the scaling so that a 0 V input signal corresponds to 50 kHz, and a 10 V input results in the maximum output frequency of 500 kHz. A high frequency optocoupler is then used to transmit the signal across any common-mode voltage potentials to the receiving ADVFC32. The optocoupler is not necessary in systems where common-mode noise is either very small or a constant low level dc voltage. In systems where common-mode voltage may present a problem, the connection between the two locations should be through the optocoupler; no power or ground connections need to be made.

The output of the optocoupler drives an ADVFC32 hooked up in the F/V configuration. Since the reconstructed signal at Pin 10 has a considerable amount of carrier feedthrough, it is desirable to filter out any frequencies in the carrier range of 50 kHz to 500 kHz. The frequency response of the F/V converter is only 3 kHz due to the pole made by the integrator, so a second 3 kHz filter will not significantly limit the bandwidth. With the simple one pole filter shown in Figure 6, the input to output 3 dB point is approximately 2 kHz, and the output noise is less than 15 mV. If a lower output impedance drive is needed, a two-pole active filter is recommended as an output stage.

Although the F/V conversion technique used in this circuit is quite simple, it is also very limited in terms of its frequency response and output ripple. The frequency response is limited by the integrator time constant and while it is possible to decrease that time constant, either signal range or output ripple must be sacrificed. The performance of the circuit of Figure 6 is shown in the photograph below. The top trace is the input signal, the middle trace is the frequency-modulated signal at the optocoupler's output, and the bottom trace is the recovered signal at the output of the F/V converter.

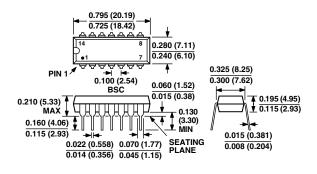

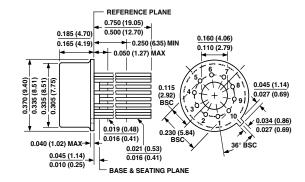

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

14-Lead Plastic DIP (N-14)

TO-100 (H-10A)

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Voltage to Frequency & Frequency to Voltage category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below:

TC9400EOD AD537JH AD652SQ/883B AD652AQ 5962-9322201MEA AD537JD AD537KD AD537SD/883B AD537SH AD650AD

AD650JN AD650JNZ AD650JPZ AD650KNZ AD650SD AD652BQ AD652JPZ AD652JPZ-REEL7 AD652KPZ AD652SQ AD654JNZ

AD7740KRMZ AD7740KRMZ-REEL7 AD7740YRMZ AD7740YRTZ-REEL7 AD7741BNZ AD7741BRZ-REEL7 AD654JRZ

AD654JRZ-REEL7 AD7741YRZ AD7741BRZ AD654JRZ-REEL ADVFC32SH TC9400COD TC9400CPD TC9402CPD NJM4151M

045166AB LM231N/NOPB LM2907M-8/NOPB LM2907N-8/NOPB LM2907N/NOPB LM2917M-8/NOPB LM2917N/NOPB

LM331N/NOPB VFC320BP VFC32KP VFC32KU ADVFC32BH AD537KH