### LTC2937

### Programmable Six Channel Sequencer and Voltage Supervisor with EEPROM

The LTC<sup>®</sup>2937 is a 6-channel power supply sequencer

and voltage supervisor. Supplies are enabled or disabled

with precise user controlled order and time spacing. To

detect power supply output faults during sequencing and

monitoring, the LTC2937 accurately monitors supply

turn-on/-off delays and output voltage levels. In the event

of a fault, response actions include complete power supply

shutdown and optional restarts. Root cause of power

faults are logged to EEPROM. For systems with high

supply count, a simple single wire connection between

multiple LTC2937 devices allows sequencing expansion

to 300 supplies. After successful sequencing and supply

voltage stabilization, the reset output pulls high to initiate

microprocessor or other system activity. To accommodate

supply margin testing, the reset output can be disabled.

Upon supply turn-off, integrated current sources are available as needed to discharge slowly decaying supplies.

Configuration EEPROM supports autonomous operation

All registered trademarks and trademarks are the property of their respective owners. Protected

DESCRIPTION

without software.

by U.S. Patents including 8627132.

### FEATURES

- Time and Event Based Sequencing

- 12 Programmable Undervoltage (UV) and Overvoltage (OV) Comparators: ±0.75% Accuracy

- I<sup>2</sup>C/SMBus Interface

- Stalled Power Supply Detection

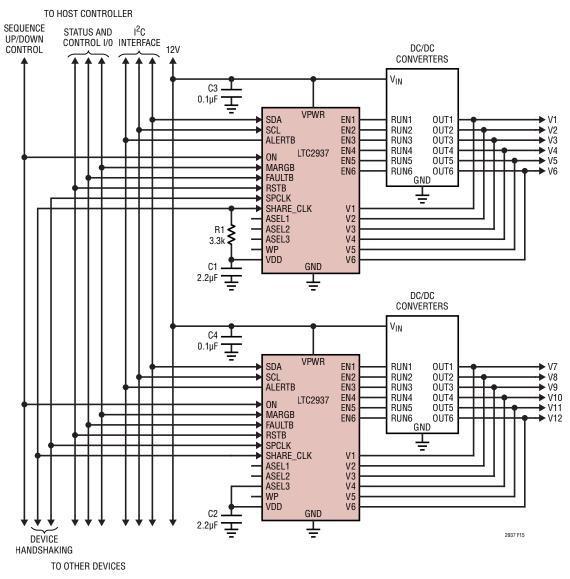

- Single Wire Synchronization Allows Controller Expansion to 50 Devices (300 Power Supplies)

- Configuration and Fault Logging in EEPROM

- EEPROM Specified Over Entire Temperature Range, Rated to 125°C, 10k Writes, 20yr Retention

- Supported by LTpowerPlay<sup>®</sup> GUI

- Fault and System Status Registers

- Reset Output with Programmable Delay

- Wide Input Supply Voltage Range: 2.9V to 16.5V

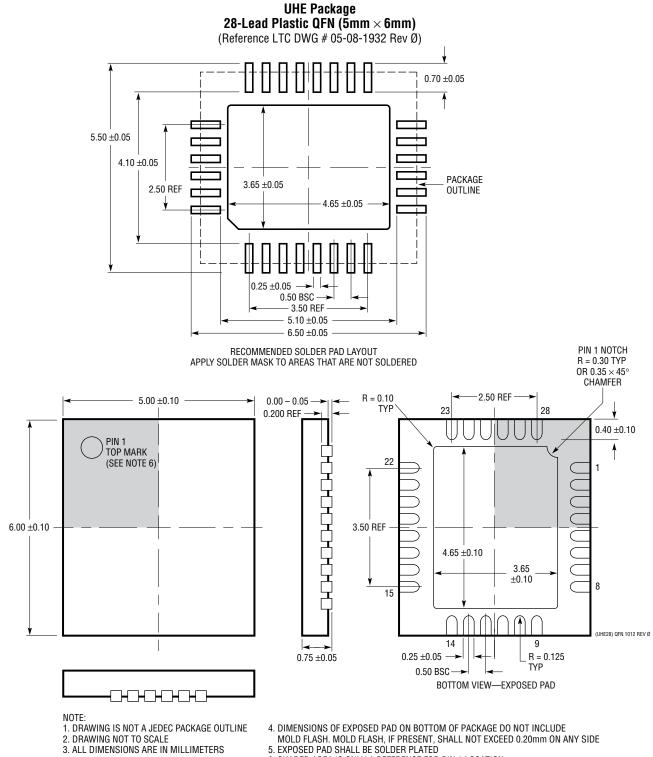

- 28-Lead QFN (5mm × 6mm) Package

### **APPLICATIONS**

- Network Servers

- Data Storage Systems

- Telecom Equipment

- High Availability Computer Systems

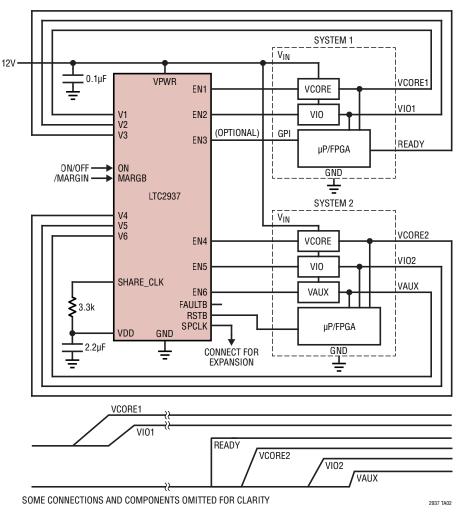

### TYPICAL APPLICATION

#### DC/DC CONVERTERS 12V VIN VPWR EN1 RUN1 OUT1 SDA 5.0\ I<sup>2</sup>C/SMBus EN2 RUN2 OUT2 3.3V SCI INTERFACE EN3 RUN3 ALERTB OUT3 2.5 EN4 RUN4 OUT4 1.8 LTC2937 ON EN5 RUN5 OUT5 1.5V MARGB TO/FROM EN6 RUN6 OUT6 2\ FAULTB GND OTHER RSTB DEVICES SPCI K SHARE CLK V1 V2 ASEL1 V3 R1 ASEL2 V4 ASEL3 3.3 WP V5 VDD V6 C1 GND 2.2µF Ŧ 2937 TA01

Six Power Supply Sequencer and Supervisor

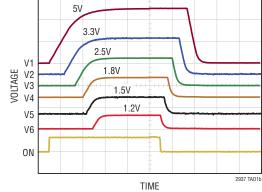

### Sequenced Power Supply Waveforms

### TABLE OF CONTENTS

| Features                                 |    |

|------------------------------------------|----|

| Applications                             | 1  |

| Typical Application                      | 1  |

| Description                              |    |

| Absolute Maximum Ratings                 |    |

| Order Information                        |    |

| Pin Configuration                        |    |

| Electrical Characteristics               |    |

| Serial Bus Timing Diagram                |    |

| Sequence-Up Threshold Timing Diagram     |    |

| Sequence-Down Event Based Timing Diagram |    |

| Sequence-Down Time Based Timing Diagram  |    |

| Typical Performance Characteristics      |    |

| Pin Functions                            |    |

| Block Diagram                            |    |

| Operation                                |    |

| Slave Addresses                          |    |

| I <sup>2</sup> C Interface               |    |

| Condensed Command Summary                |    |

|                                          |    |

| WRITE_PROTECTION                         | 10 |

| SPECIAL_LOT<br>ON_OFF_CONTROL            | 10 |

| V_RANGE                                  |    |

| V_THRESHOLD_n                            |    |

| Voltage Threshold Encoding               | 21 |

| TON_TIMERS_n                             | 21 |

| TOFF_TIMERS_n                            |    |

| SEQ_UP_POSITION_n                        |    |

| SEQ_DOWN_POSITION_n                      |    |

| RSTB_CONFIG                              |    |

| FAULT RESPONSE                           |    |

| MONITOR_STATUS_HISTORY                   | 29 |

| CLEAR_ALERTB                             |    |

| STORE                                    |    |

| RESTORE                                  | 30 |

| CLEAR                                    | 30 |

| STATUS_INFORMATION                       |    |

| BREAK_POINT                              | 32 |

| SEQ_POSITION_COUNT                       |    |

| MONITOR_BACKUP                           | 33 |

|                                          |    |

| MONITOR_STATUS                                 | 34 |

|------------------------------------------------|----|

| DEVICE_ID                                      |    |

| Applications Information                       | 35 |

| Introduction                                   |    |

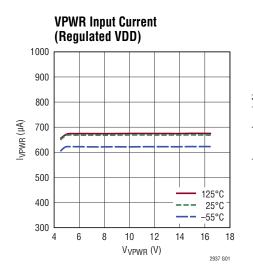

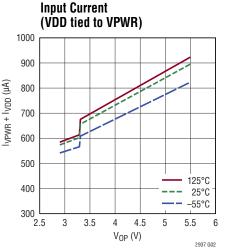

| Powering the LTC2937                           | 35 |

| Write Protection                               |    |

| Updating Volatile or Nonvolatile Memory        | 35 |

| Sequence Position Clock (SPCLK)                |    |

| System Configuration                           | 37 |

| Sequence-Up and Sequence-Down Control          | 37 |

| Sequence-Up Parameters                         | 38 |

| Voltage Supervision                            |    |

| Voltage Monitor Range                          |    |

| UV and OV Thresholds                           |    |

| UV Thresholds and Sequence-Up Hysteresis       | 39 |

| Selecting Resistors for Adjustable Range       | 39 |

| OV Thresholds in Adjustable Applications       | 40 |

| RSTB Response                                  | 41 |

| Sequence-Down Parameters                       | 41 |

| Discharge Thresholds                           |    |

| Active Supply Discharge                        | 42 |

| Fault Descriptions                             | 43 |

| CONTROL Faults                                 | 43 |

| SEQUENCE Faults                                |    |

| SUPERVISOR Faults                              | 43 |

| EXTERNAL Faults                                | 43 |

| SHARE_CLK Faults                               | 43 |

| Fault Reporting                                | 44 |

| Fault Management                               |    |

| Fault Debugging Tools                          |    |

| Share Clock (SHARE_CLK)                        |    |

| Asynchronous Supply Control                    | 46 |

| LTpowerPlay: An Interactive GUI for Power Syst |    |

| Management                                     |    |

| External Connection Design Checklist           |    |

| Minimum Connections for Programming            |    |

| Interconnect Between Multiple LTC2937s         |    |

| System Event Based Sequencing                  |    |

| Package Description                            |    |

| Revision History                               |    |

| Typical Application                            |    |

| Related Parts                                  | 52 |

### **ABSOLUTE MAXIMUM RATINGS**

(Notes 1, 2)

| VPWR0.3V to 18V<br>EN1, EN2, EN3, EN4, EN5, EN60.3V to 16V |

|------------------------------------------------------------|

| VDD, ALERTB, FAULTB, MARGB, RSTB,                          |

| ON, SCL, SDA, SHARE_CLK, SPCLK, WP,                        |

| V1, V2, V3, V4, V5, V6–0.3V to 6V                          |

| ASEL1, ASEL2, ASEL30.3V to VDD                             |

| Input Currents                                             |

| V1, V2, V3, V4, V5, V6–1mA                                 |

| Operating Junction Temperature Range                       |

| LTC2937C 0°C to 70°C                                       |

| LTC2937I–40°C to 85°C                                      |

| LTC2937H–40°C to 125°C                                     |

| LTC2937MP55°C to 125°C                                     |

| Storage Temperature Range65°C to 150°C                     |

| Maximum Junction Temperature 130°C                         |

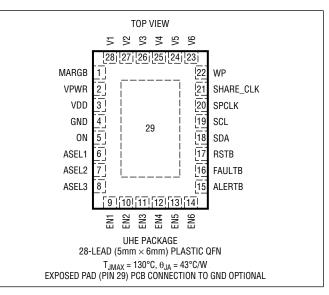

### PIN CONFIGURATION

### **ORDER INFORMATION**

| LEAD FREE FINISH | TAPE AND REEL      | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|--------------------|---------------|---------------------------------|-------------------|

| LTC2937CUHE#PBF  | LTC2937CUHE#TRPBF  | 2937          | 28-Lead (5mm × 6mm) Plastic QFN | 0°C to 70°C       |

| LTC2937IUHE#PBF  | LTC2937IUHE#TRPBF  | 2937          | 28-Lead (5mm × 6mm) Plastic QFN | -40°C to 85°C     |

| LTC2937HUHE#PBF  | LTC2937HUHE#TRPBF  | 2937          | 28-Lead (5mm × 6mm) Plastic QFN | -40°C to 125°C    |

| LTC2937MPUHE#PBF | LTC2937MPUHE#TRPBF | 2937          | 28-Lead (5mm × 6mm) Plastic QFN | -55°C to 125°C    |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

Rev. B

## **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C and VPWR = 12V. (Note 2)

| SYMBOL                 | PARAMETER                                                 | CONDITIONS                                                                                                                                           |   | MIN                                               | ТҮР                                                  | MAX                                                 | UNITS                                        |

|------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------------------------------------|------------------------------------------------------|-----------------------------------------------------|----------------------------------------------|

| Device Pow             | er                                                        |                                                                                                                                                      |   |                                                   |                                                      |                                                     |                                              |

| V <sub>VPWR</sub>      | VPWR Supply Input Operating Range                         |                                                                                                                                                      | • | 4.5                                               |                                                      | 16.5                                                | V                                            |

| I <sub>VPWR</sub>      | VPWR Supply Current                                       | Sequencing Complete, No VDD Load Writing to EEPROM                                                                                                   | • |                                                   |                                                      | 1<br>3                                              | mA<br>mA                                     |

| VDD <sub>REG</sub>     | VDD Regulated Output                                      | VPWR $\ge 4.5V$ , I <sub>VDD</sub> = -1mA                                                                                                            | • | 3.234                                             | 3.3                                                  | 3.366                                               | V                                            |

| V <sub>OP</sub>        | VDD Operating Range                                       | VDD Connected to VPWR                                                                                                                                | • | 2.9                                               |                                                      | 5.5                                                 | V                                            |

| V <sub>UVL</sub>       | VDD Undervoltage Lockout                                  | VDD Rising                                                                                                                                           | • | 2.5                                               | 2.7                                                  | 2.85                                                | V                                            |

| V <sub>UVL(HYST)</sub> | VDD Undervoltage Lockout Hysteresis                       | VDD Falling                                                                                                                                          |   |                                                   | 75                                                   |                                                     | mV                                           |

| V1, V2, V3,            | V4, V5, V6                                                |                                                                                                                                                      |   |                                                   |                                                      |                                                     |                                              |

| V <sub>MON</sub>       | Vn Monitoring Thresholds<br>( $n = 1$ through 6) (Note 3) | Adjustable Range<br>Low Range<br>High Range                                                                                                          | • | 0.2<br>0.5<br>1                                   |                                                      | 1.2<br>3<br>6                                       | V<br>V<br>V                                  |

| V <sub>RES</sub>       | V <i>n</i> Threshold Programming LSB Resolution           | Adjustable Range<br>Low Range<br>High Range                                                                                                          |   |                                                   | 4<br>10<br>20                                        |                                                     | mV<br>mV<br>mV                               |

| V <sub>MON(ACC)</sub>  | V <i>n</i> Threshold Accuracy by Code<br>(Note 4)         | C-, I-Grades:<br>Codes 155 to 255<br>Codes 55 to 154<br>Codes 5 to 54<br>H-, MP-Grades:<br>Codes 155 to 255<br>Codes 55 to 154<br>Codes 5 to 54      | • |                                                   |                                                      | ±0.75<br>±0.75<br>±1.5<br>±1<br>±1<br>±1<br>±1.5    | %<br>%<br>%<br>%                             |

| V <sub>MON(HYST)</sub> | Temporary Sequence-Up Threshold<br>Hysteresis (Note 5)    | Sequence Up Threshold Achieved                                                                                                                       | • | -4                                                | -5                                                   | -6                                                  | %                                            |

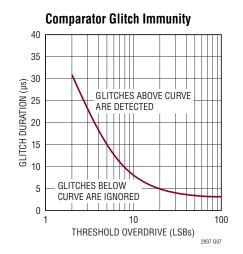

| t <sub>PD</sub>        | V <i>n</i> Comparator Propagation Delay                   | 2 LSB Overdrive of Configured Threshold<br>10 LSB Overdrive of Configured Threshold                                                                  | • |                                                   | 35<br>10                                             | 25                                                  | μs<br>µs                                     |

| R <sub>IN</sub>        | V <i>n</i> Input Resistance                               | Low Range and High Range                                                                                                                             | • | 400                                               | 600                                                  | 900                                                 | kΩ                                           |

| I <sub>LKG</sub>       | V <i>n</i> Input Leakage Current                          | Adjustable Range, V = 1.2V                                                                                                                           | • |                                                   |                                                      | ±15                                                 | nA                                           |

| R <sub>ON</sub>        | V <i>n</i> Discharge On Resistance                        | V = 0.4V                                                                                                                                             | • | 25                                                | 40                                                   | 50                                                  | Ω                                            |

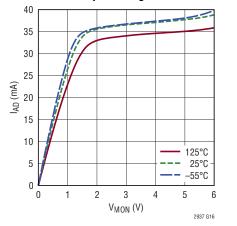

| I <sub>AD(MAX)</sub>   | V <i>n</i> Discharge Current                              | V = 1.8V                                                                                                                                             | • | 20                                                | 35                                                   | 45                                                  | mA                                           |

| V <sub>DTH</sub>       | V <i>n</i> Discharge Threshold                            | High and Low Range<br>Adjustable Range (Positive Polarity)<br>Adjustable Range (Negative Polarity)                                                   | • | 300<br>50<br>1.12                                 | 400<br>120<br>1.2                                    | 500<br>190<br>1.28                                  | mV<br>mV<br>V                                |

| EEPROM                 |                                                           |                                                                                                                                                      |   |                                                   |                                                      |                                                     |                                              |

|                        | Retention                                                 | (Notes 6, 7)                                                                                                                                         | • | 20                                                |                                                      |                                                     | Years                                        |

|                        | Endurance                                                 | 1 Cycle = 1 STORE Command (Notes 6, 7)                                                                                                               | • | 10,000                                            |                                                      |                                                     | Cycles                                       |

| t <sub>PT</sub>        | Programming Time (Note 8)                                 | STORE Command                                                                                                                                        | • |                                                   |                                                      | 130                                                 | ms                                           |

| t <sub>RT</sub>        | Restore Time                                              | RESTORE Command                                                                                                                                      | • |                                                   |                                                      | 2                                                   | ms                                           |

| RSTB                   |                                                           |                                                                                                                                                      |   |                                                   |                                                      |                                                     |                                              |

| t <sub>RST</sub>       | Programmable Reset Delay<br>(Register 0x22, RSTB_CONFIG)  | b[15:13] = 000b<br>b[15:13] = 001b<br>b[15:13] = 010b<br>b[15:13] = 011b<br>b[15:13] = 100b<br>b[15:13] = 101b<br>b[15:13] = 110b<br>b[15:13] = 111b |   | 0<br>1.4<br>5.8<br>22<br>46<br>180<br>370<br>1480 | 0.05<br>1.6<br>6.4<br>26<br>51<br>200<br>410<br>1640 | 0.1<br>1.9<br>7.5<br>30<br>60<br>230<br>475<br>1900 | ms<br>ms<br>ms<br>ms<br>ms<br>ms<br>ms<br>ms |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C and VPWR = 12V. (Note 2)

| SYMBOL                | PARAMETER                                                                                      | CONDITIONS                                                                                                                                           |                            | MIN                                               | ТҮР                                                       | MAX                                      | UNITS                                       |

|-----------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------|-----------------------------------------------------------|------------------------------------------|---------------------------------------------|

| Sequence <sup>•</sup> | Timers                                                                                         |                                                                                                                                                      |                            |                                                   |                                                           |                                          |                                             |

| t <sub>on_max</sub>   | ton_max time<br>(Registers 0x0A through 0x0F)                                                  |                                                                                                                                                      |                            | ∞<br>136<br>540<br>2.2<br>8.7<br>35<br>140<br>560 | $\infty$<br>160<br>640<br>2.6<br>10.2<br>41<br>164<br>655 | $^{\infty}$ 195 780 3.2 12.4 50 200 800  | s<br>μs<br>ms<br>ms<br>ms<br>ms<br>ms<br>ms |

| t <sub>OND</sub>      | ton_delay Time (Registers 0x0A through 0x0F)                                                   | Timer Register Value N = b[12:0]                                                                                                                     | •                          | 68 • N                                            | 80 • N                                                    | 96 • N                                   | μs                                          |

| t <sub>off_max</sub>  | toff_max Time<br>(Registers 0x10 through 0x15)                                                 | b[15:13] = 000b<br>b[15:13] = 001b<br>b[15:13] = 010b<br>b[15:13] = 011b<br>b[15:13] = 100b<br>b[15:13] = 101b<br>b[15:13] = 110b<br>b[15:13] = 111b | 0<br>0<br>0<br>0<br>0<br>0 | ∞<br>2.2<br>8.7<br>35<br>140<br>560<br>2.3<br>9   | ∞<br>2.6<br>10.2<br>41<br>164<br>655<br>2.6<br>10.5       | ${}^{\infty}$ 3.2 12.4 50 200 800 3.2 13 | s<br>ms<br>ms<br>ms<br>ms<br>s<br>s         |

| t <sub>OFFD</sub>     | toff_delay Time (Registers 0x10 through 0x15)                                                  | Timer Register Value N = b[12:0]                                                                                                                     | •                          | 68 • N                                            | 80 • N                                                    | 96 • N                                   | μs                                          |

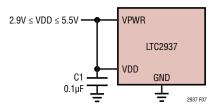

| SPCLK                 | ·                                                                                              |                                                                                                                                                      |                            |                                                   |                                                           |                                          |                                             |

| t <sub>onsq</sub>     | ON Input to Start of SPCLK                                                                     | (Note 9)                                                                                                                                             |                            | 40                                                | 80                                                        | 120                                      | μs                                          |

| I <sub>PU</sub>       | SPCLK Pull-Up Current                                                                          | V <sub>SPCLK</sub> = GND                                                                                                                             | •                          | -30                                               | -55                                                       | -80                                      | μA                                          |

| t <sub>LO</sub>       | Minimum SPCLK Low Time                                                                         |                                                                                                                                                      |                            | 16                                                | 20                                                        | 26                                       | μs                                          |

| t <sub>HI</sub>       | Minimum SPCLK High Time                                                                        |                                                                                                                                                      |                            | 48                                                | 60                                                        | 75                                       | μs                                          |

| t <sub>FLOAT</sub>    | SPCLK Float High Time                                                                          | End of Sequencing                                                                                                                                    |                            | 260                                               | 320                                                       | 400                                      | μs                                          |

| SHARE_CL              | К                                                                                              |                                                                                                                                                      |                            |                                                   |                                                           |                                          |                                             |

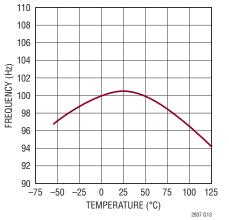

| f <sub>SHR</sub>      | Share Clock Frequency                                                                          |                                                                                                                                                      |                            | 85                                                | 100                                                       | 110                                      | kHz                                         |

| Analog and            | d Digital I/O                                                                                  |                                                                                                                                                      |                            |                                                   |                                                           |                                          |                                             |

| V <sub>TH</sub>       | Input Threshold: ON, MARGB, WP,<br>RSTB, FAULTB, SHARE_CLK, SPCLK                              |                                                                                                                                                      | •                          | 1                                                 | 1.2                                                       | 1.4                                      | V                                           |

| V <sub>TH(HYST)</sub> | Input Threshold Hysteresis: ON,<br>MARGB, WP, RSTB, FAULTB, SHARE_<br>CLK, SPCLK               |                                                                                                                                                      |                            |                                                   | 50                                                        |                                          | mV                                          |

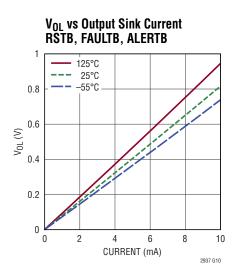

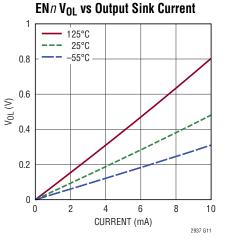

| V <sub>OL</sub>       | Voltage Output Low: ALERTB, RSTB,<br>FAULTB, SHARE_CLK, SPCLK, EN1,<br>EN2, EN3, EN4, EN5, EN6 | I <sub>SINK</sub> = 3mA                                                                                                                              | •                          |                                                   | 0.2                                                       | 0.4                                      | V                                           |

| I <sub>PU</sub>       | Internal Pull-Up Current: ON, MARGB,<br>WP, ALERTB, RSTB, FAULTB                               | V = GND                                                                                                                                              | •                          | -4                                                | -10                                                       | -16                                      | μA                                          |

## **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C and VPWR = 12V. (Note 2)

| SYMBOL                   | PARAMETER                                                                                    | CONDITIONS                  |   | MIN       | ТҮР       | MAX       | UNITS    |

|--------------------------|----------------------------------------------------------------------------------------------|-----------------------------|---|-----------|-----------|-----------|----------|

|                          | Leakage Current: ALERTB, RSTB,<br>FAULTB<br>Leakage Current: EN1, EN2, EN3, EN4,<br>EN5, EN6 | V = 5.5V<br>V = 15V         | • |           |           | ±1<br>±1  | μΑ<br>μΑ |

| V <sub>OH</sub>          | Voltage Output High: ALERTB, RSTB, FAULTB                                                    | I <sub>SOURCE</sub> = −1μA  | • | VDD – 1   |           |           | V        |

| t <sub>PW</sub>          | Minimum Detectable Pulse Width: ON, FAULTB                                                   |                             | • | 25        |           |           | μs       |

| Serial Bus I             | nterface and Address Inputs                                                                  | ·                           |   |           |           |           |          |

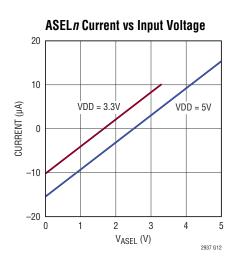

| V <sub>ASEL(H)</sub>     | ASEL Input High Threshold                                                                    |                             | • | VDD-0.4   |           |           | V        |

| V <sub>ASEL(L)</sub>     | ASEL Input Low Threshold                                                                     |                             | • |           |           | 0.4       | V        |

| V <sub>ASEL(OC)</sub>    | ASEL Open Circuit Voltage                                                                    |                             |   | (         | ).5 • VDE | )         | V        |

| V <sub>ASEL(OCR)</sub>   | ASEL Allowable Open Circuit Voltage<br>Range                                                 |                             | • | 0.4 • VDD |           | 0.6 • VDD | V        |

| I <sub>ASEL(HZ)</sub>    | Allowable Leakage in Open State                                                              |                             | • |           |           | ±1        | μA       |

|                          | ASEL Input Resistance                                                                        |                             | • | 120       | 180       | 280       | kΩ       |

| V <sub>STH</sub>         | SDA, SCL Input Threshold                                                                     |                             | • | 1.5       | 1.8       | 2         | V        |

| I <sub>STH</sub>         | SDA, SCL Input Current                                                                       | SDA or SCL = 5.5V           | • |           | 0         | ±2        | μA       |

| V <sub>SDA(OL)</sub>     | SDA Output Low Voltage                                                                       | I <sub>SDA</sub> = 3mA      | • |           | 0.3       | 0.4       | V        |

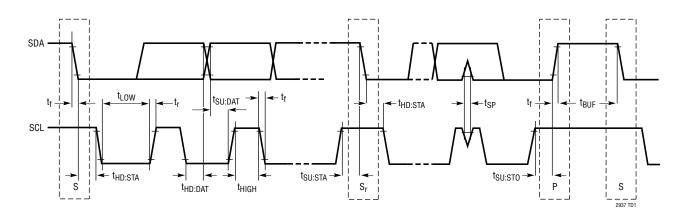

| Serial Bus               | Fiming (Note 10)                                                                             |                             |   |           |           |           |          |

| f <sub>SCL(MIN)</sub>    | Minimum Serial Clock Frequency                                                               |                             | • |           |           | 10        | kHz      |

| f <sub>SCL(MAX)</sub>    | Maximum Serial Clock Frequency                                                               |                             | • | 400       |           |           | kHz      |

| t <sub>LOW(MIN)</sub>    | Serial Clock Low Period                                                                      |                             | • |           |           | 1.3       | μs       |

| t <sub>HIGH(MIN)</sub>   | Serial Clock High Period                                                                     |                             | • |           |           | 0.6       | μs       |

| t <sub>BUF(MIN)</sub>    | Bus Free Time Between Stop and Start                                                         |                             | • |           |           | 1.3       | μs       |

| t <sub>HD,STA(MIN)</sub> | Start Condition Hold Time                                                                    |                             | • |           |           | 600       | ns       |

| t <sub>SU,STA(MIN)</sub> | Start Condition Setup Time                                                                   |                             | • |           |           | 600       | ns       |

| t <sub>SU,STO(MIN)</sub> | Stop Condition Setup Time                                                                    |                             | • |           |           | 600       | ns       |

| t <sub>HD,DAT(MIN)</sub> | Data Hold Time                                                                               | (LTC2937 Receiving Data)    | • |           |           | 0         | ns       |

| t <sub>HD,DAT</sub>      | Data Hold Time                                                                               | (LTC2937 Transmitting Data) | • | 300       |           | 900       | ns       |

| t <sub>SU,DAT(MIN)</sub> | Data Setup Time                                                                              |                             | • |           |           | 100       | ns       |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: All currents into device pins are positive. All currents out of device pins are negative. All voltages are referenced to GND unless otherwise specified.

**Note 3:** Subscript (or placeholder) *n* denotes a channel number and is applied throughout this document.

Note 4: Threshold codes 0 through 4 are not used.

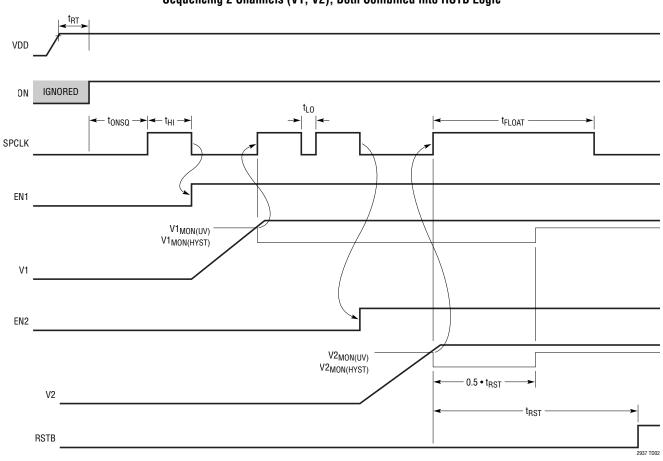

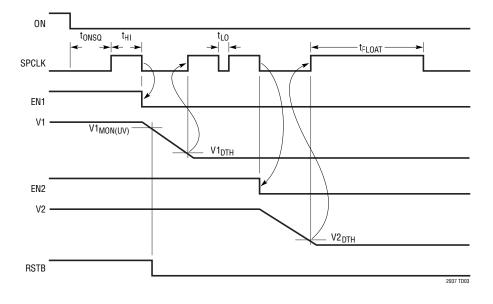

**Note 5:** During sequence-up operation, undervoltage comparators participating in sequencing receive a temporary 5% hysteresis after the respective monitored voltage exceeds its threshold for the first time. The hysteresis remains active until 50% of the programmed reset delay time

has been completed. See the timing diagram and applications information for more details.

**Note 6:** EEPROM endurance and retention are guaranteed by design, characterization and correlation with statistical process controls.

Note 7: EEPROM endurance and retention will be degraded when T<sub>.1</sub> > 85°C.

Note 8: The LTC2937 will not acknowledge any commands while a STORE command is being executed.

Note 9: If multiple LTC2937s are in use, t<sub>ONSQ</sub> can stretch indefinitely until all devices are ready to sequence.

Note 10: Maximum capacitive load, C<sub>B</sub>, for SCL and SDA is 400pF. Data and clock rise time ( $t_r$ ) and fall time ( $t_f$ ) are: (20 + 0.1 • C<sub>B</sub>) (ns) <  $t_r$  < 300ns and  $(20 + 0.1 \cdot C_B)$  (ns) < t<sub>f</sub> < 300ns. C<sub>B</sub> = capacitance of one bus line in pF. SCL and SDA external pull-up voltage,  $V_{10}$ , is 2.9V <  $V_{10}$  < 5.5V.

### **SERIAL BUS TIMING DIAGRAM**

### SEQUENCE-UP THRESHOLD TIMING DIAGRAM

Sequencing 2 Channels (V1, V2), Both Combined into RSTB Logic

### SEQUENCE-DOWN EVENT BASED TIMING DIAGRAM

Sequencing 2 Channels (V1, V2), Both Combined into RSTB Logic

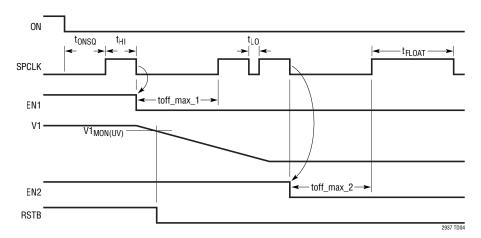

### SEQUENCE-DOWN TIME BASED TIMING DIAGRAM

Sequencing 2 Channels (V1, V2), Both Combined into RSTB Logic. toff\_max Timers Used for Post Disable Sequencing Delay; ON\_OFF\_CONTROL b[0] = 1

Rev. B

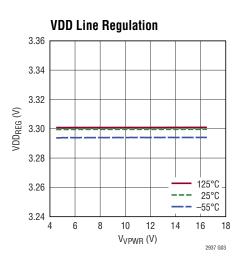

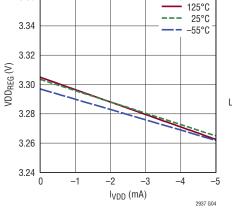

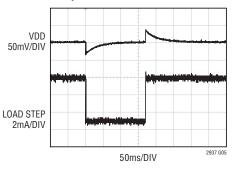

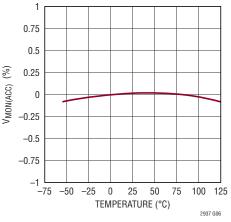

### **TYPICAL PERFORMANCE CHARACTERISTICS**

## 3.36 VDD Load Regulation

VDD Load Step Transient Response

Comparator Threshold Accuracy vs Temperature

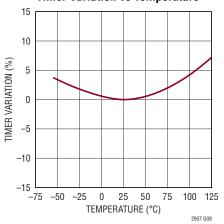

Timer Variation vs Temperature

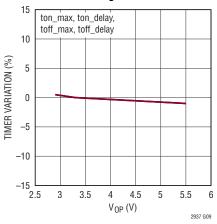

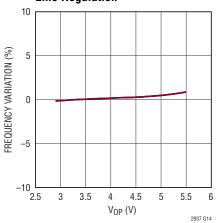

**Timer Line Regulation**

10

### **TYPICAL PERFORMANCE CHARACTERISTICS**

SHARE\_CLK Frequency vs Temperature

Active Discharge Current vs Monitor Input Voltage

SHARE\_CLK Frequency Line Regulation

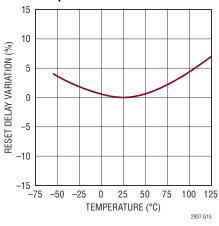

Reset Delay Variation vs Temperature

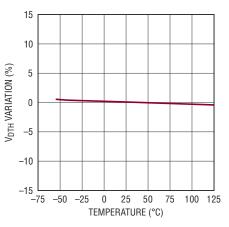

Discharge Threshold Variation vs Temperature

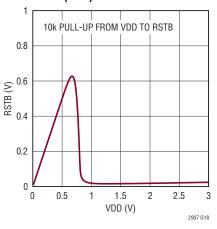

RSTB (Low) vs VDD

### PIN FUNCTIONS

**ALERTB:** Alert Open-Drain Output with 10µA Pull-Up to VDD. Asserts low in response to any designated fault. Conforms to SMBus standard. Apply the Alert Response Protocol to clear the ALERTB output and to identify the alerting device. Performing a read from the CLEAR\_ALERTB register will also remove ALERTB pull-down.

**ASEL1, ASEL2, ASEL3:** Three-State Address-Select Inputs. Connect to GND, VDD or open to encode 1 of 27 device addresses. Consult the Operation section for the address look-up table.

**EN1, EN2, EN3, EN4, EN5, EN6:** Power Supply Enable Outputs. Connect these open-drain outputs to a respective power supply enable input or to a gate of an N-channel MOSFET (for pass applications). The enable outputs must be pulled up externally (to a maximum of 15V) if necessary. Some power supply enable inputs have internal pull-up sources, which eliminates the need for an external pull-up.

Exposed Pad: Leave open or connect to device GND.

**FAULTB:** Fault I/O with  $10\mu$ A Pull-Up to VDD. Asserts low in response to any designated fault. Configure fault behavior in the FAULT\_RESPONSE register. External devices may also pull down on FAULTB to initiate an optional fault response.

GND: Device Ground.

**MARGB:** Margin Input. Pull to ground to disable RSTB and prevent SUPERVISOR faults. Typically applied prior to margining supplies high or low during system test. Leave open or pull to VDD when not margining.

**ON:** Sequencing Up/Down Control Input. ON input response is gated by settings in the ON\_OFF\_CONTROL register. Internally pulled up to VDD with 10µA current source.

**RSTB:** Reset I/O with  $10\mu$ A Pull-Up to VDD. Pulls low in response to designated voltage comparator violations. Pulls high when selected voltage sense thresholds are satisfied (ie not UV and/or not OV), and can be used as a system power-on-reset. The reset assertion delay after satisfying thresholds is programmable. May be pulled low by external devices and detected with b[12] of the MONITOR\_STATUS command.

**SCL:** Serial Clock Input (400kHz Maximum). Requires external pull-up resistor.

**SDA:** Bidirectional Serial Data I/O. Requires external pull-up resistor.

**SHARE\_CLK:** Clock Sharing Node. Connect multiple SHARE\_CLK nodes together to establish a common time base between devices. Pull-up with a 3.3k to 10k resistor to VDD.

**SPCLK:** Sequence Position Clock I/O. Connect multiple LTC2937 SPCLK lines together for automatic sequence position control between devices. Pull-up devices are not recommended. Leave unconnected in a single device application. Minimize capacitance on this line to ensure reliable operation.

**V1, V2, V3, V4, V5, V6:** Undervoltage, Overvoltage and Discharge Comparator Inputs. There are three sense ranges. Adjustable: 0.2V to 1.2V in 4mV increments, Low: 0.5V to 3V in 10mV increments, and High: 1V to 6V in 20mV increments. When monitored supplies are shut off, internal pull-down current sources can be activated to accelerate the discharge of supply capacitance. Connect to device GND if unused.

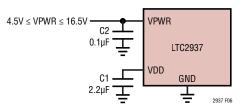

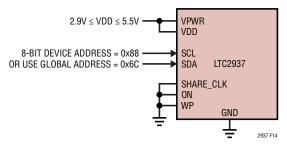

**VDD:** 3.3V Internal Regulator Output. Bypass with a  $2.2\mu$ F (or greater) capacitor to GND. Use this output to bias the address inputs or an external resistor network for sensing negative supply voltages. Do not load the regulated output with more than 5mA. Override the regulated output with an external supply (2.9V to 5.5V) connected to VPWR and VDD.

**VPWR:** Supply Voltage Input. Power supply operating range is 4.5V to 16.5V. Tie to VDD if unused. Bypass with  $0.1\mu$ F (or greater) capacitor to GND.

**WP:** Write Protection Input. Pull to GND to enable write capability into the device. Leave open or tie to VDD to keep write protection active. The software controlled lock bit in the WRITE\_PROTECTION register may also need deactivation to enable write capability.

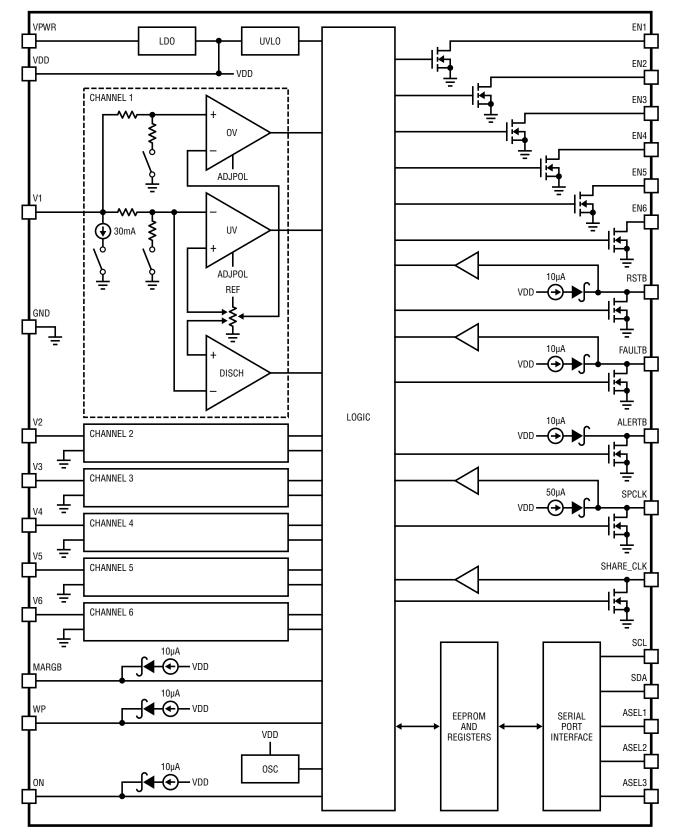

### **BLOCK DIAGRAM**

## OPERATION

The LTC2937 is a six-channel programmable power supply sequencer and supervisor that can perform the following operations:

- Control the timing relationships and sequence order for six power supplies per device. Sequence supplies on the basis of time delays and/or qualifying events.

- Monitor power supplies for undervoltage (UV) and overvoltage (OV) conditions using two independent comparators on each of six inputs.

- Generate a system reset that is a function of user selected inputs with a programmable release delay.

- Synchronize sequencing across multiple controllers with a one wire connection (SPCLK).

- Synchronize timing across multiple controllers with a one wire connection (SHARE\_CLK).

- Discharge slowly decaying supplies with built-in pulldown current sources.

- Monitor power supplies for discharge condition using the discharge comparators.

- Accept I<sup>2</sup>C/SMBus programming commands.

- Initiate supply sequencing from an external source and/or programming command.

- Retrieve real-time system status.

- Generate a fault related interrupt on the ALERTB output and respond to an issued SMBus Alert Response.

- Respond to fault conditions by continuing operation indefinitely or disabling supplies immediately. Optionally, sequencing may be retried multiple times automatically (0 to 6 or unlimited) after a supply shutdown event.

- Report voltage and/or timing limit violations upon request.

- Pause sequencing operations to help identify system power problems.

- Store system configuration to EEPROM.

- Restore EEPROM contents to operating memory through programming or when VDD is applied on power-up.

- Recall first fault violations logged to EEPROM.

- EEPROM reads and writes over the entire specified supply voltage and temperature range.

- Provide two stage write protection to prevent inadvertent writes to memory.

- Disable system reset when performing voltage margining of supplies.

- Monitor negative power supplies.

### OPERATION

#### Slave Addresses

The LTC2937 responds to one of 27 addresses. Connect the ASEL1, ASEL2 and ASEL3 inputs to VDD, GND, or leave open, as shown in Table 1. The LTC2937 always responds to the Global and Alert Response addresses regardless of the ASEL input states. The ASEL inputs are always active and operate in real time.

| DESCRIPTION    | HEX DEVIC | BINARY DEVICE ADDRESS |   |   |   |   |   |   |   | ADDRESS INPUTS |       |       |       |

|----------------|-----------|-----------------------|---|---|---|---|---|---|---|----------------|-------|-------|-------|

|                | 7-Bit     | 8-Bit                 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | R/W            | ASEL3 | ASEL2 | ASEL1 |

| Alert Response | 00        | 19                    | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1              | Х     | Х     | Х     |

| Global         | 36        | 6C                    | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0              | Х     | Х     | Х     |

|                | 37        | 6E                    | 0 | 1 | 1 | 0 | 1 | 1 | 1 | Х              | L     | L     | L     |

|                | 38        | 70                    | 0 | 1 | 1 | 1 | 0 | 0 | 0 | Х              | L     | L     | NC    |

|                | 39        | 72                    | 0 | 1 | 1 | 1 | 0 | 0 | 1 | Х              | L     | L     | Н     |

|                | 3A        | 74                    | 0 | 1 | 1 | 1 | 0 | 1 | 0 | Х              | L     | NC    | L     |

|                | 3B        | 76                    | 0 | 1 | 1 | 1 | 0 | 1 | 1 | Х              | L     | NC    | NC    |

|                | 3C        | 78                    | 0 | 1 | 1 | 1 | 1 | 0 | 0 | Х              | L     | NC    | Н     |

|                | 3D        | 7A                    | 0 | 1 | 1 | 1 | 1 | 0 | 1 | Х              | L     | Н     | L     |

|                | 3E        | 70                    | 0 | 1 | 1 | 1 | 1 | 1 | 0 | Х              | L     | Н     | NC    |

|                | 3F        | 7E                    | 0 | 1 | 1 | 1 | 1 | 1 | 1 | Х              | L     | Н     | Н     |

|                | 40        | 80                    | 1 | 0 | 0 | 0 | 0 | 0 | 0 | Х              | NC    | L     | L     |

|                | 41        | 82                    | 1 | 0 | 0 | 0 | 0 | 0 | 1 | Х              | NC    | L     | NC    |

|                | 42        | 84                    | 1 | 0 | 0 | 0 | 0 | 1 | 0 | Х              | NC    | L     | Н     |

|                | 43        | 86                    | 1 | 0 | 0 | 0 | 0 | 1 | 1 | Х              | NC    | NC    | L     |

|                | 44        | 88                    | 1 | 0 | 0 | 0 | 1 | 0 | 0 | Х              | NC    | NC    | NC    |

|                | 45        | 8A                    | 1 | 0 | 0 | 0 | 1 | 0 | 1 | Х              | NC    | NC    | Н     |

|                | 46        | 8C                    | 1 | 0 | 0 | 0 | 1 | 1 | 0 | Х              | NC    | Н     | L     |

|                | 47        | 8E                    | 1 | 0 | 0 | 0 | 1 | 1 | 1 | Х              | NC    | Н     | NC    |

|                | 48        | 90                    | 1 | 0 | 0 | 1 | 0 | 0 | 0 | Х              | NC    | Н     | Н     |

|                | 49        | 92                    | 1 | 0 | 0 | 1 | 0 | 0 | 1 | Х              | Н     | L     | L     |

|                | 4A        | 94                    | 1 | 0 | 0 | 1 | 0 | 1 | 0 | Х              | Н     | L     | NC    |

|                | 4B        | 96                    | 1 | 0 | 0 | 1 | 0 | 1 | 1 | Х              | Н     | L     | Н     |

|                | 4C        | 98                    | 1 | 0 | 0 | 1 | 1 | 0 | 0 | Х              | Н     | NC    | L     |

|                | 4D        | 9A                    | 1 | 0 | 0 | 1 | 1 | 0 | 1 | Х              | Н     | NC    | NC    |

|                | 4E        | 90                    | 1 | 0 | 0 | 1 | 1 | 1 | 0 | Х              | Н     | NC    | Н     |

|                | 4F        | 9E                    | 1 | 0 | 0 | 1 | 1 | 1 | 1 | Х              | Н     | Н     | L     |

|                | 50        | A0                    | 1 | 0 | 1 | 0 | 0 | 0 | 0 | Х              | Н     | Н     | NC    |

|                | 51        | A2                    | 1 | 0 | 1 | 0 | 0 | 0 | 1 | X              | Н     | Н     | Н     |

#### Table 1. LTC2937 Address Look-Up Table

H = Tie to VDD, L = Tie to GND, NC = No Connect = Open, X = Don't Care

### OPERATION

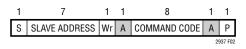

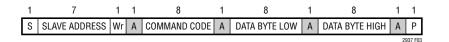

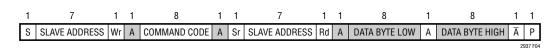

I<sup>2</sup>C Interface

- S START CONDITION

- Sr REPEATED START CONDITION

- Rd READ (BIT VALUE OF 1)

- Wr WRITE (BIT VALUE OF 0)

- x SHOWN UNDER A FIELD INDICATES THAT THAT FIELD IS REQUIRED TO HAVE THE VALUE OF x

- A ACKNOWLEDGE

- A NOT ACKNOWLEDGE

- P STOP CONDITION MASTER TO SLAVE

- SLAVE TO MASTER

2937 F01

#### Figure 2. Send Byte Protocol

Figure 3. Write Word Protocol

Figure 4. Read Word Protocol

| _1 | 1 7           |    | 1 | 8              | 1 | 1       |

|----|---------------|----|---|----------------|---|---------|

| S  | SLAVE ADDRESS | Rd | А | DEVICE ADDRESS | Ā | Р       |

| _  | 0001100       |    |   |                | 2 | 937 F05 |

Figure 5. Alert Response Protocol

### CONDENSED COMMAND SUMMARY

#### **ON/OFF** Commands

| COMMAND NAME                    | CMD CODE      | DESCRIPTION                                                                                                                                                  | TYPE<br>(Note 11) | WORD<br>LENGTH<br>(BITS) | EEPROM<br>Capacity<br>(Bits) | REF<br>PAGE |

|---------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------|------------------------------|-------------|

| ON_OFF_CONTROL                  | 0x02          | ON input and/or I <sup>2</sup> C directed sequence up/down control settings.                                                                                 | R/W               | 16                       | 16                           | 19          |

| Sequencing-Up Configuration     | n Commands    |                                                                                                                                                              |                   | <u> </u>                 |                              | L           |

| SEQ_UP_POSITION_n               | 0x16 – 0x1B   | Sequence-up position for EN1 through EN6. Asynchronous enable controls.                                                                                      | R/W               | 16                       | 16                           | 24          |

| TON_TIMERS_n                    | 0x0A – 0x0F   | Encode EN <i>n</i> delay time and maximum rise time for V <i>n</i> .                                                                                         | R/W               | 16                       | 16                           | 22          |

| Voltage Supervisor Comman       | ds            |                                                                                                                                                              |                   |                          |                              |             |

| V_RANGE                         | 0x03          | Encode V <i>n</i> comparator ranges and Adjustable Range polarity.                                                                                           | R/W               | 16                       | 16                           | 20          |

| V_THRESHOLD_n                   | 0x04 - 0x09   | Encode high and low thresholds for V <i>n</i> .                                                                                                              | R/W               | 16                       | 16                           | 21          |

| RSTB_CONFIG                     | 0x22          | Select comparator outputs for combination into RSTB response.<br>Select RSTB assertion delay.                                                                | R/W               | 16                       | 16                           | 26          |

| Sequencing-Down Configura       | tion Commands |                                                                                                                                                              |                   |                          |                              |             |

| SEQ_DOWN_POSITION_n             | 0x1C - 0x21   | Sequence-down position for EN1 through EN6. Active discharge select for V1 through V6.                                                                       | R/W               | 16                       | 16                           | 25          |

| TOFF_TIMERS_n                   | 0x10 - 0x15   | Encode EN <i>n</i> delay time and maximum fall time for V <i>n</i> .                                                                                         | R/W               | 16                       | 16                           | 23          |

| Fault, Status and Debugging     | Commands      |                                                                                                                                                              |                   |                          |                              |             |

| FAULT_RESPONSE                  | 0x23          | Configure fault response actions.                                                                                                                            | R/W               | 16                       | 16                           | 27          |

| STATUS_INFORMATION              | 0x29          | Summary of current device faults and status.                                                                                                                 | R                 | 16                       | 0                            | 31          |

| MONITOR_STATUS_<br>HISTORY      | 0x26          | History of voltage monitor violations, SUPERVISOR faults and SEQUENCE faults.                                                                                | R                 | 16                       | 0                            | 29          |

| MONITOR_BACKUP                  | 0x2F          | An EEPROM copy of the MONITOR_STATUS_HISTORY word after the first SUPERVISOR or SEQUENCE fault.                                                              | R                 | 16                       | 16                           | 33          |

| MONITOR_STATUS                  | 0x30          | Live voltage monitor and RSTB status.                                                                                                                        | R                 | 16                       | 0                            | 34          |

| SEQ_POSITION_COUNT              | 0x2B          | Sequence position counter.                                                                                                                                   | R                 | 16                       | 0                            | 32          |

| BREAK_POINT                     | 0x2A          | Enable and configure sequencing break points.                                                                                                                | R/W               | 16                       | 0                            | 32          |

| CLEAR                           | 0x2E          | Clear all status, fault and volatile history information.                                                                                                    | S                 | 0                        | 0                            | 30          |

| CLEAR_ALERTB                    | 0x28          | Clear the ALERTB output by performing a read from this command address. The returned word contains no information.                                           | R                 | 16                       | 0                            | 30          |

| Security and Device Information | tion Commands |                                                                                                                                                              |                   |                          |                              |             |

| WRITE_PROTECTION                | 0x00          | Contains lock key code and software lock bit to prevent accidental overwrites of volatile and nonvolatile memory. Status of WP input.                        | R/W               | 16                       | 16                           | 18          |

| STORE                           | 0x2C          | Store device configuration to EEPROM.                                                                                                                        | S                 | 0                        | 0                            | 30          |

| RESTORE                         | 0x2D          | Restore device configuration from EEPROM.                                                                                                                    | S                 | 0                        | 0                            | 30          |

| SPECIAL_LOT                     | 0x01          | Contains customer specific codes that identify the factory programmed configuration stored in EEPROM. Use as a scratchpad if customer codes are not applied. | R/W               | 16                       | 16                           | 18          |

| DEVICE_ID                       | 0x31          | Read only. Contains 0x2937.                                                                                                                                  | R                 | 16                       | 0                            | 34          |

**Note 11:** R = read, W = write, S = send byte.

### WRITE\_PROTECTION

#### (Command Byte 0x00)

Prevent write operations into EEPROM or volatile memory with the software lock bit b[0] = 1 and/or hardware lock bit b[1] = 1. Deactivate the software lock bit by matching the device key string in b[15:2] while b[1:0] = 00b. Retrieve the state of the external hardware lock input (WP) in b[1]. Improve write security by having at least one bit in the device key set to logic 1. Change the device key if desired, when the device is unlocked.

The contents of any supported command may be read regardless of the lock bit settings. Commands are acknowledged under write protection. However, the device configuration will not change.

| BIT(S)  | SYMBOL      | OPERATION                                                                                           |

|---------|-------------|-----------------------------------------------------------------------------------------------------|

| b[15:2] | device_key  | Must match against programmed string in order to deactivate software write lock (default = 0x0EAA). |

| b[1]    | hw_lock_bit | WP input status.<br>0: Unlocked.<br>1: Locked.                                                      |

| b[0]    | sw_lock_bit | Software lock bit.<br>0: Unlocked.<br>1: Locked (default).                                          |

#### WRITE\_PROTECTION Data Contents

#### SPECIAL\_LOT (Command Byte 0x01)

Read the SPECIAL\_LOT register to retrieve a customer specific code that identifies the factory programmed configuration stored in EEPROM. Use as a scratchpad if customer codes are not applied. Contact LTC Marketing to request a custom factory programmed configuration and special lot number. The default value is 0x0000.

### ON\_OFF\_CONTROL

### (Command Byte 0x02)

Configure the combination of ON input and/or I<sup>2</sup>C inputs needed to control sequencing. Activate margin mode operation using b[6] or the external MARGB input. Specify time or event based sequence-down qualification. Prevent sequence-up initiation if supplies selected for sequencing are not discharged.

| BIT(S)  | SYMBOL          | OPERATION                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b[15:8] | reserved        | Ignore.                                                                                                                                                                                                                                                                                                                                                                                   |

| b[7]    | on_state        | Internal ON status. Representation of the ON input logically modified by the b[5:1] directives below and/or freeze mode bit b[8] from FAULT_RESPONSE (read only).<br>0: Internal ON is low.<br>1: Internal ON is high.                                                                                                                                                                    |

| b[6]    | i2c_margin      | RSTB disable used during supply margining.<br>0: RSTB operates normally (default).<br>1: RSTB is allowed to pull high.                                                                                                                                                                                                                                                                    |

| b[5]    | discharge_start | Sequenced supply discharge threshold qualification.<br>0: Discharged supplies not required to start sequence-up (default).<br>1: Discharged supplies required to start sequence-up.                                                                                                                                                                                                       |

| b[4]    | i2c_on_off      | Serial bus directed sequence on/off control.<br>0: Sequence down (default).<br>1: Sequence up.                                                                                                                                                                                                                                                                                            |

| b[3]    | i2c_on_off_mask | Serial bus on/off control mask.<br>0: Ignore b[4]. If b[3] and b[2] are low, device is in sequence down state (default).<br>1: Listen to b[4]. If b[2] is high, the ON input is also required to initiate sequencing.                                                                                                                                                                     |

| b[2]    | on_input_mask   | ON input mask.<br>0: Ignore the ON input. Sequencing control directed by b[4] if not masked (default).<br>1: Listen to ON input.                                                                                                                                                                                                                                                          |

| b[1]    | on_polarity     | Invert ON input logical state. Changing polarity should be performed with b[2] low because the response is immediate<br>and could initiate a sequencing event.<br>0: Sequence up with ON input at logic high (default).<br>1: Sequence up with ON input at logic low.                                                                                                                     |

| b[0]    | seq_down_qual   | Select time or event based sequence down.<br>0: Event based. Sequence position clock (SPCLK) advances when supplies drop below their discharge threshold (default)<br>1: Time based. Sequence position clock (SPCLK) advances when respective toff_max time has elapsed, including any<br>preceding toff_delay time (if timer set to infinity, operation defaults to voltage decay mode). |

#### ON\_OFF\_CONTROL Data Contents

#### V\_RANGE

#### (Command Byte 0x03)

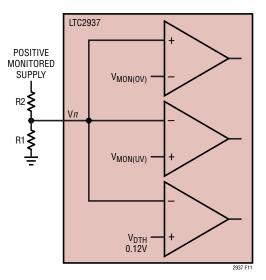

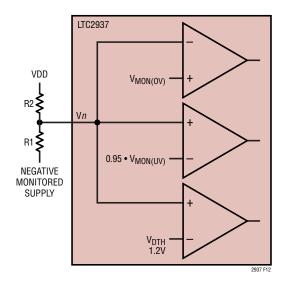

Select the operating threshold range for each of the six voltage monitor inputs. The range selection applies to the OV and UV comparators connected to each input. The High Range covers thresholds between 1V and 6V in 20mV steps. The Low Range covers thresholds between 0.5V and 3V in 10mV steps. The Adjustable Range covers 0.2V to 1.2V in 4mV steps. Select the negative polarity option in the Adjustable Range when sensing negative voltages. Discharge comparator threshold and polarity adjusts automatically in response to the configured range selection.

#### V\_RANGE Data Contents

| BIT(S)   | SYMBOL   | OPERATION                                                                                                                                                     |

|----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b[15:12] | reserved | Ignore.                                                                                                                                                       |

| b[11:10] | v6_range | Select V6 range.<br>00b: High Range (default).<br>01b: Low Range.<br>10b: Adjustable Range (positive polarity).<br>11b: Adjustable Range (negative polarity). |

| b[9:8]   | v5_range | Select V5 range.<br>00b: High Range (default).<br>01b: Low Range.<br>10b: Adjustable Range (positive polarity).<br>11b: Adjustable Range (negative polarity). |

| b[7:6]   | v4_range | Select V4 range.<br>00b: High Range.<br>01b: Low Range (default).<br>10b: Adjustable Range (positive polarity).<br>11b: Adjustable Range (negative polarity). |

| b[5:4]   | v3_range | Select V3 range.<br>00b: High Range.<br>01b: Low Range (default).<br>10b: Adjustable Range (positive polarity).<br>11b: Adjustable Range (negative polarity). |

| b[3:2]   | v2_range | Select V2 range.<br>00b: High Range.<br>01b: Low Range (default).<br>10b: Adjustable Range (positive polarity).<br>11b: Adjustable Range (negative polarity). |

| b[1:0]   | v1_range | Select V1 range.<br>00b: High Range.<br>01b: Low Range (default).<br>10b: Adjustable Range (positive polarity).<br>11b: Adjustable Range (negative polarity). |

#### V\_THRESHOLD\_n

| п            | 1    | 2    | 3    | 4    | 5    | 6    |

|--------------|------|------|------|------|------|------|

| Command Byte | 0x04 | 0x05 | 0x06 | 0x07 | 0x08 | 0x09 |

Program the OV and UV thresholds for each of the six voltage monitor inputs.

#### V\_THRESHOLD\_n Data Contents

| BIT(S)  | SYMBOL                 | OPERATION                                                                                                  |

|---------|------------------------|------------------------------------------------------------------------------------------------------------|

| b[15:8] | ov_threshold_ <i>n</i> | Encode one of 250 thresholds (0x05 through 0xFF). See below for voltage threshold encoding (TE) procedure. |

| b[7:0]  | uv_threshold_ <i>n</i> | Encode one of 250 thresholds (0x05 through 0xFF). See below for voltage threshold encoding (TE) procedure. |

#### Voltage Threshold Encoding

Depending on the selected voltage range, threshold encoding (TE) is determined as follows:

For the high input range of 1V to 6V, the equation is:

$TE = ROUND[50 \bullet (V_{MON} - 0.9)]$

For the low input range of 0.5V to 3V, the equation is:

$TE = ROUND[100 \bullet (V_{MON} - 0.45)]$

For the high impedance adjustable input range of 0.2V to 1.2V, the equation is:

$TE = ROUND[250 \bullet (V_{MON} - 0.18)]$

As an example, consider the channel 1 Low Range defaults from the table below (ov\_threshold\_1 = 1.32V, uv\_threshold\_1 = 1.08V). The threshold encodings (TE) are therefore:

$TE_{OV} = ROUND[100 \bullet (1.32 - 0.45)] = ROUND[100 \bullet (0.87)] = 87 (0x57)$

$TE_{IIV} = ROUND[100 \cdot (1.08 - 0.45)] = ROUND[100 \cdot (0.63)] = 63 (0x3F)$

The 16-bit word contained in the V\_THRESHOLD\_1 register (0x573F) is formed from the simple concatenation of the OV and UV hexadecimal values.

#### Factory Defaults

| п | RANGE | V <sub>MON(OV)</sub> | V <sub>MON(UV)</sub> | TE <sub>OV</sub> | TE <sub>UV</sub> |

|---|-------|----------------------|----------------------|------------------|------------------|

| 1 | Low   | 1.32 V               | 1.08 V               | 0x57             | 0x3F             |

| 2 | Low   | 1.65 V               | 1.35 V               | 0x78             | 0x5A             |

| 3 | Low   | 1.98 V               | 1.62 V               | 0x99             | 0x75             |

| 4 | Low   | 2.75 V               | 2.25 V               | 0xE6             | 0xB4             |

| 5 | High  | 3.63 V               | 2.97 V               | 0x89             | 0x68             |

| 6 | High  | 5.5 V                | 4.5V                 | 0xE6             | 0xB4             |

TON\_TIMERS\_n

| п            | 1    | 2    | 3    | 4    | 5    | 6    |

|--------------|------|------|------|------|------|------|

| Command Byte | 0x0A | 0x0B | 0x0C | 0x0D | 0x0E | 0x0F |

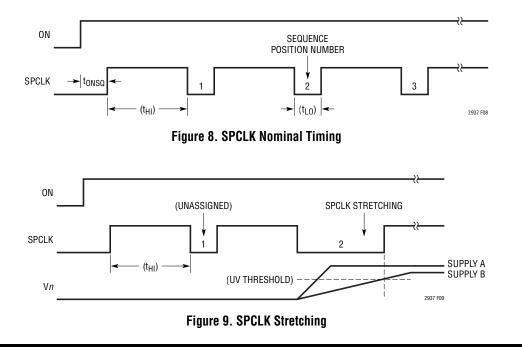

The TON\_TIMER registers encode the enable delay time and the maximum allowable rise time per channel in one 16-bit word. The lowest thirteen bits (*ton\_delay*) determine the amount time delay between the beginning of the programmed sequence position (determined by the SEQ\_UP\_POSITION\_*n* command) and the release of the respective EN*n* output (in 80µs increments).

The upper three bits (*ton\_max*) determine the amount of time that is allowed to elapse between the release of EN*n* and the voltage at the respective V*n* input reaching its UV threshold. Failing this test can cause a sequence-up fault depending on the FAULT\_RESPONSE settings. A setting of  $\infty$  defeats time checking during the sequence-up phase for the respective channel (sequencing will pause indefinitely until the UV threshold is crossed).

| BIT(S)   | SYMBOL              | OPERATION                             |                       |                                                                                                                            |

|----------|---------------------|---------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------|

| b[15:13] | ton_max_ <i>n</i>   | Maximum rise tir<br>UV threshold at t |                       | as the maximum time allowed between EN <i>n</i> release and successful crossing of                                         |

|          |                     | b[15:13]                              | ton_max               |                                                                                                                            |

|          |                     | 000b                                  | $\infty$ (default)    |                                                                                                                            |

|          |                     | 001b                                  | 160µs                 |                                                                                                                            |

|          |                     | 010b                                  | 640µs                 |                                                                                                                            |

|          |                     | 011b                                  | 2.6ms                 |                                                                                                                            |

|          |                     | 100b                                  | 10.2ms                |                                                                                                                            |

|          |                     | 101b                                  | 41ms                  |                                                                                                                            |

|          |                     | 110b                                  | 164ms                 |                                                                                                                            |

|          |                     | 111b                                  | 655ms                 |                                                                                                                            |

| b[12:0]  | ton_delay_ <i>n</i> | ton_delay = 80 •                      | N µs, where N is a 13 | ence position to enable (EN <i>n</i> ) release.<br>-bit unsigned integer in b[12:0].<br>e default setting for b[12:0] = 0. |

#### TOFF\_TIMERS\_n

| п            | 1    | 2    | 3    | 4    | 5    | 6    |

|--------------|------|------|------|------|------|------|

| Command Byte | 0x10 | 0x11 | 0x12 | 0x13 | 0x14 | 0x15 |

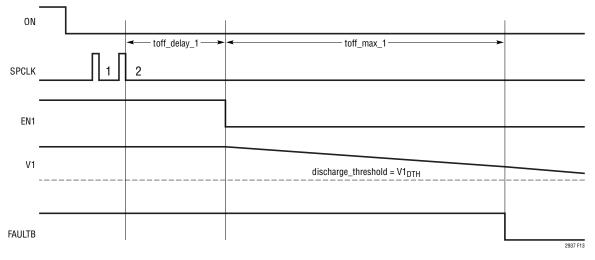

The TOFF\_TIMER registers encode the disable delay time and the maximum allowable fall time per channel in one 16-bit word. The lowest thirteen bits (*toff\_delay*) determine the amount time delay between the beginning of the programmed sequence position (determined by the SEQ\_DOWN\_POSITION\_*n* command) and the pull-down of the respective EN*n* output (in 80µs increments).

The upper three bits (*toff\_max*) determine the amount of time that is allowed to elapse between the pull-down of EN*n* and the voltage at the respective V*n* input falling below its discharge threshold. Failing this test can cause a sequence-down fault depending on the FAULT\_RESPONSE settings. A setting of  $\infty$  defeats time checking during the sequence-down phase for the respective channel (sequencing will pause indefinitely until the monitored voltage decays below its discharge threshold).

Sequence-down progress may also be gated by time instead of voltage decay. Choose the time based mode of operation with b[0] = 1 in the ON\_OFF\_CONTROL register. Use the *toff\_max* settings below to set the time from EN*n* pulling low to the start of next sequence position. If multiple channels occupy the same sequence position, the longest combined time (*toff\_delay\_n* + *toff\_max\_n*) determines the sequence position hold time. In time delay mode, a *toff\_max* setting of  $\infty$  defaults operation to voltage decay mode.