# 60V Synchronous Buck Multi-Chemistry Battery Charger

#### **FEATURES**

- Wide Input Voltage Range: 4.5V to 60V

- Wide Battery Voltage Range: 2.4V to 60V

- Built-In Charge Algorithms for Lead-Acid and Li-Ion

- ±0.5% Float Voltage Accuracy

- ±5% Charge Current Accuracy

- Maximum Power Point Tracking Input Control

- NTC Temperature Compensated Float Voltage

- Two Open Drain Status Pins

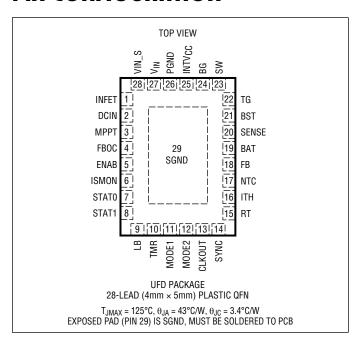

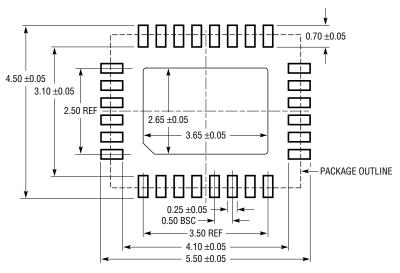

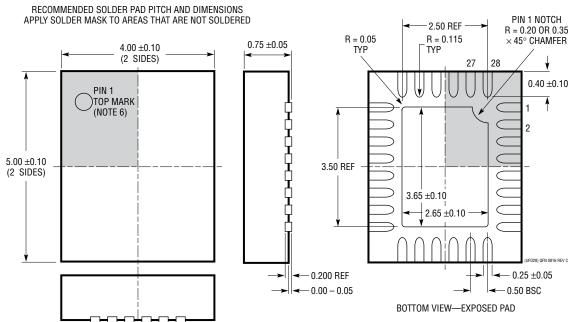

- Thermally Enhanced 28-Lead 4mm × 5mm QFN Package

## **APPLICATIONS**

- Battery Backup for Lighting, UPS Systems, Security Cameras, Computer Control Panels

- Portable Medical Equipment

- Solar-Powered Systems

- Industrial Battery Charging

All registered trademarks and trademarks are the property of their respective owners. All other trademarks are the property of their respective owners. Protected by U.S. Patents, including 02/6383

#### DESCRIPTION

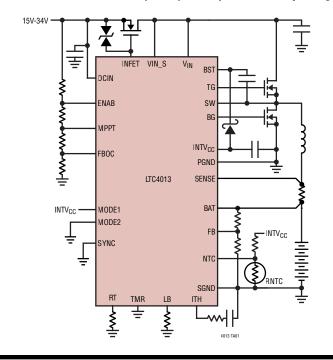

The LTC®4013 is a high voltage battery charger that is well suited for charging a wide range of lead-acid batteries including both vented and sealed types. It supports bulk, float, absorption and equalization charging. The LTC4013 also supports termination options for Li-lon/Polymer and LiFePO $_4$  batteries.

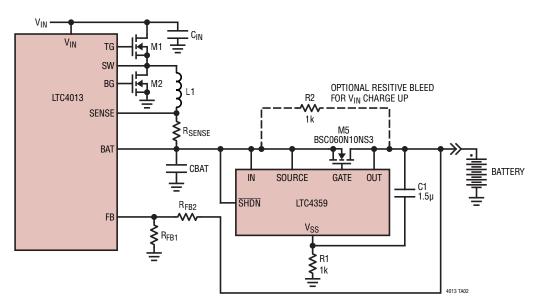

Charging is performed with a high efficiency synchronous buck (step-down) converter that uses external N-channel MOSFETs. Switching frequency is resistor programmable or can be synchronized to an external clock. Charge current is programmed with an external sense resistor.

The LTC4013 also includes maximum power point tracking input-voltage regulation for limited power sources such as solar panels. Other features include user-programmable absorption and equalization times, temperature-compensated charge voltage and an external N-channel MOSFET isolation control circuit.

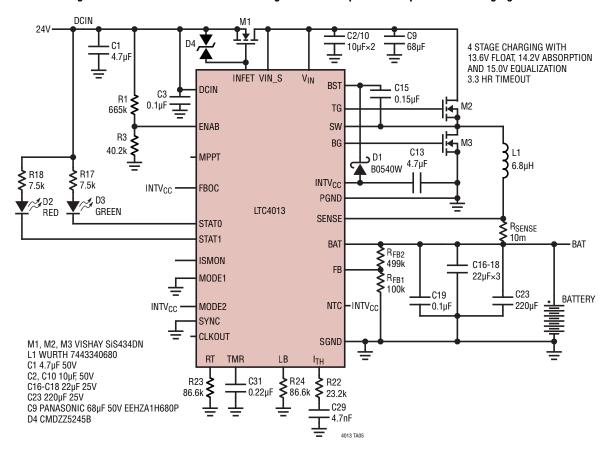

## TYPICAL APPLICATION

15V-34V to 6 Cell Lead-Acid (12.6V) 5A Step-Down Battery Charger

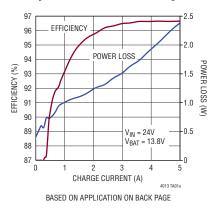

#### **Efficiency and Power Loss vs Charge Current**

Rev B

## **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| DCIN, V <sub>IN</sub> , VIN_S, ENAB, STATO, STAT10.3 | 3V to 60V |

|------------------------------------------------------|-----------|

| INFET0.3                                             | 3V to 73V |

| BST0.3                                               | 3V to 66V |

| STAT0, STAT1                                         | 5mA       |

| SENSE, BAT0.3                                        | 3V to 60V |

| SENSE-BAT0.3                                         | V to 0.3V |

| FBOC, MPPT, FB, MODE1, MODE2, SYNC,                  |           |

| INTV <sub>CC</sub> , NTC0                            | .3V to 6V |

| TMR, LB, ITH0                                        | .3V to 3V |

| Operating Junction Temperature Range                 |           |

| (Note 2)40°C                                         | to 125°C  |

| Storage Temperature Range65°C                        | to 150°C  |

## PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL     | PART MARKING | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|-------------------|--------------|---------------------------------|-------------------|

| LTC4013EUFD#PBF  | LTC4013EUFD#TRPBF | 4013         | 28-Lead (4mm × 5mm) Plastic QFN | -40°C to 125°C    |

| LTC4013IUFD#PBF  | LTC4013IUFD#TRPBF | 4013         | 28-Lead (4mm × 5mm) Plastic QFN | -40°C to 125°C    |

Contact the factory for parts specified with wider operating temperature ranges.

Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2). DCIN,  $V_{IN}$ ,  $VIN_S = 18V$ , ENAB = 1.4V, SYNC = 0V unless otherwise noted.

| PARAMETER                                                 | CONDITIONS                                                                      |   | MIN            | TYP            | MAX            | UNITS    |

|-----------------------------------------------------------|---------------------------------------------------------------------------------|---|----------------|----------------|----------------|----------|

| Input Voltage Range (DCIN, V <sub>IN</sub> )              |                                                                                 | • | 4.5            |                | 60             | V        |

| Battery Voltage Range (BAT)                               |                                                                                 | • | 2.4            |                | 60             | V        |

| ENAB Pin Threshold (Rising)                               |                                                                                 | • | 1.175          | 1.220          | 1.275          | V        |

| Threshold Hysteresis                                      |                                                                                 |   |                | 170            |                | mV       |

| ENAB Pin Bias Current                                     |                                                                                 |   |                | 10             |                | nA       |

| V <sub>IN</sub> UVLO                                      | V <sub>IN</sub> Rising, Power Enabled<br>V <sub>IN</sub> Rising, Power Disabled |   |                | 3.45<br>3.08   |                | V<br>V   |

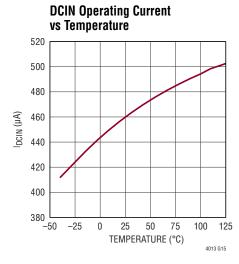

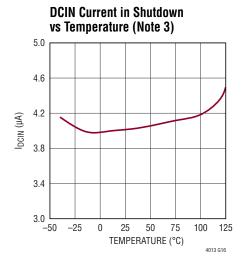

| DCIN Pin Operating Current Shutdown Current               | Not Switching<br>ENAB = 0V                                                      | • |                | 480<br>4       | 625<br>7.9     | μA<br>μA |

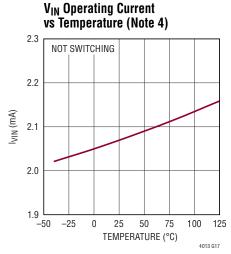

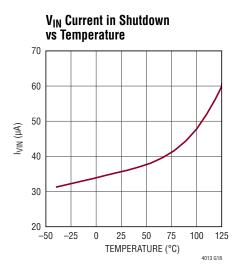

| V <sub>IN</sub> Pin Operating Current<br>Shutdown Current | Not Switching (Notes 3 and 4)<br>ENAB = 0V, RT = 40.2k                          | • |                | 2.1<br>32      | 2.8<br>80      | mA<br>μA |

| BAT Pin Shutdown Current                                  | ENAB = 0V                                                                       | • |                | 0.5            | 1.5            | μΑ       |

| SENSE Pin Shutdown Current                                | ENAB = 0V                                                                       | • |                | 0.4            | 2.5            | μA       |

| SW Pin Current in Shutdown                                | ENAB = 0V, SW = 60V, BST = 66V                                                  |   |                | 0.25           |                | μA       |

| STATO, STAT1 Enabled Voltage                              | STATO, STAT1 Pin Current =1mA<br>STATO, STAT1 Pin Current = 5mA                 |   |                | 0.14<br>0.77   | 0.2<br>1.0     | V        |

| STATO, STAT1 Leakage Current                              | STATO, STAT1 Pin Voltage = 60V                                                  | • |                |                | 1              | μA       |

| FB Regulation Voltage (See Tables 2-5)                    |                                                                                 |   | L              |                |                |          |

| Battery Float Voltage V <sub>FB(FL)</sub>                 | MODE1 = L, H MODE2 = L, H                                                       | • | 2.256<br>2.244 | 2.267<br>2.267 | 2.278<br>2.291 | V        |

|                                                           | MODE1 = M, MODE2 = L, H                                                         | • | 2.189<br>2.178 | 2.200<br>2.200 | 2.211<br>2.223 | V        |

|                                                           | MODE1 = L, MODE2 = M                                                            | • | 2.320<br>2.309 | 2.332<br>2.332 | 2.344<br>2.356 | V        |

| Battery Absorption Voltage V <sub>FB(ABS)</sub>           | MODE1 = H, MODE2 = L, H<br>MODE1 = L, MODE2 = H                                 | • | 2.355<br>2.343 | 2.367<br>2.367 | 2.380 2.392    | V        |

|                                                           | MODE1 = M, MODE2 = L, H                                                         | • | 2.388<br>2.376 | 2.400<br>2.400 | 2.412<br>2.425 | V        |

| Battery Equalization Voltage V <sub>FB(EQ)</sub>          | MODE1 = L, H, MODE2 = H, TMR = Cap                                              | • | 2.487<br>2.475 | 2.500<br>2.500 | 2.513<br>2.526 | V        |

|                                                           | MODE1 = M, MODE2 = H, TMR = Cap                                                 | • | 2.587<br>2.574 | 2.600<br>2.600 | 2.613<br>2.627 | V        |

| Battery Charge Voltage V <sub>FB(CHG)</sub>               | MODE1 = H, MODE2 = M                                                            | • | 2.355<br>2.343 | 2.367<br>2.367 | 2.38<br>2.392  | V        |

|                                                           | MODE1 = M, MODE2 = M                                                            | • | 2.388<br>2.376 | 2.400<br>2.400 | 2.412<br>2.425 | V        |

| Battery Recharge Voltage V <sub>FB(RECHG)</sub>           | MODE1 = M, H MODE2 = M                                                          | • | 2.284<br>2.272 | 2.295<br>2.295 | 2.306<br>2.319 | V        |

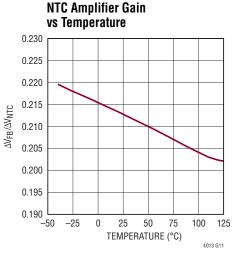

| NTC Amplifier Gain                                        | ΔV <sub>FB(FL)</sub> /ΔV <sub>NTC</sub>                                         |   |                | 0.21           |                | V/V      |

| NTC Amplifier Offset                                      | $\Delta V_{FB(FL)}$ with $V_{NTC} = INTV_{CC}/2$                                |   | -15            | 0              | 15             | mV       |

| FB Pin Current                                            | $V_{FB} = 3V$                                                                   |   |                | 10             |                | nA       |

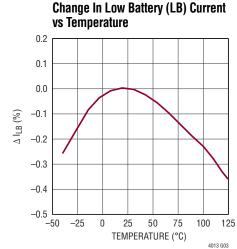

| LB Pin Current                                            | V <sub>LB</sub> = 2V                                                            |   | 19.6           | 20             | 20.4           | μА       |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ (Note 2). DCIN, $V_{IN}$ , $V_{IN}$ , $V_{IN}$ , $V_{IN}$ , $V_{IN}$ and $V_{IN}$ is a period operating junction temperature range, otherwise specifications are at $V_{IN}$ and $V_{IN}$ is a period operating junction temperature range, otherwise specifications are at $V_{IN}$ and $V_{IN}$ is a period operating junction temperature range, otherwise specifications are at $V_{IN}$ and $V_{IN}$ is a period operating junction temperature range, otherwise specifications are at $V_{IN}$ is a period operating junction temperature range, otherwise specifications are at $V_{IN}$ is a period operating junction temperature range, otherwise specifications are at $V_{IN}$ is a period operating junction temperature range.

| PARAMETER                                                            | CONDITIONS                                                                     |   | MIN  | TYP            | MAX   | UNITS    |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------|---|------|----------------|-------|----------|

| Error Amp                                                            |                                                                                |   |      |                |       |          |

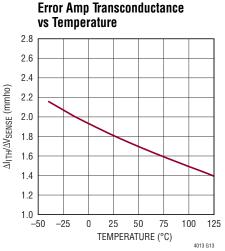

| Error Amp Transconductance                                           | $\Delta I_{ITH}/\Delta (V_{SENSE}-V_{BAT}) V_{ITH} = 1.8V$                     |   | 1300 | 1800           | 2300  | μmho     |

| Error Amp Current Source                                             | V <sub>ITH</sub> =1.8V, V <sub>FB</sub> = 2.0V, (Float) MODE1 = H, MODE2 = L   |   | -6.5 | -10            | -13.5 | μA       |

| Current Sense (all measured as V <sub>SENSE</sub> – V <sub>BAT</sub> | unless otherwise noted)                                                        |   |      |                |       |          |

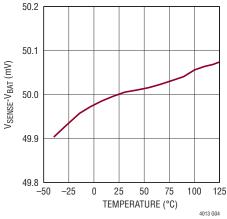

| Maximum Charging Sense Resistor Voltage                              | In Absorption, Float, Li-Ion Charge, BAT = 14V                                 | • | 48   | 50             | 52    | mV       |

| Equalization and Low Battery Charging Sense<br>Resistor Voltage      | BAT = 14V                                                                      | • | 8    | 10             | 12.5  | mV       |

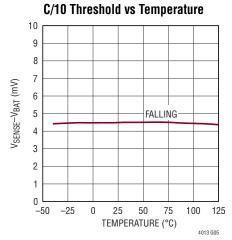

| Current Sense C/10 Threshold                                         | Termination when TMR = 0                                                       | • | 2.0  | 4.6            | 7.0   | mV       |

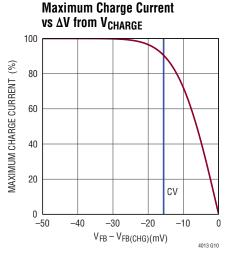

| Constant Voltage (CV) Threshold                                      | V <sub>FB(ABS,EQ)</sub> – V <sub>FB</sub> , Timeout Initiation with Cap on TMR | • |      | 15.6           | 24.5  | mV       |

| Overcurrent Charging Turnoff                                         |                                                                                | • |      | 100            | 106   | mV       |

| ISMON Fullscale Output Voltage                                       | V <sub>SENSE</sub> – V <sub>BAT</sub> = 50mV                                   |   |      | 1.00           |       | V        |

| SENSE Input UVLO                                                     | V <sub>SENSE</sub> Rising (Charging Enabled)                                   | • | 1.86 | 1.97           | 2.07  | V        |

| SENSE Input UVLO Hysteresis                                          | V <sub>SENSE</sub> Rising to Falling (Charging Disabled)                       |   |      | 100            |       | mV       |

| Configuration Pins                                                   |                                                                                |   |      |                |       |          |

| MODE1, MODE2 Pin, Low Threshold                                      |                                                                                | • |      |                | 8.0   | V        |

| MODE1, MODE2 Pin, Mid Threshold                                      |                                                                                | • | 1.3  |                | 1.8   | V        |

| MODE1, MODE2 Pin, High Threshold                                     |                                                                                | • | 2.5  |                |       | V        |

| Timer                                                                |                                                                                |   |      |                |       |          |

| TMR Oscillator High Threshold                                        |                                                                                |   |      | 1.5            |       | V        |

| TMR Oscillator Low Threshold                                         |                                                                                |   |      | 0.97           |       | V        |

| Safety Timer Turn on Voltage                                         | TMR Voltage Rising                                                             | • | 0.45 | 0.5            | 0.65  | V        |

| Safety Timer Turn on Hysteresis Voltage                              |                                                                                |   |      | 250            |       | mV       |

| TMR Source/Sink Current                                              | TMR = 1.25V                                                                    |   | 8.5  | 10.0           | 11.5  | μA       |

| TMR Pin Period                                                       | CTMR = 0.2µF                                                                   |   |      | 20.8           |       | ms       |

| End of Charge Termination Time, t <sub>EOC</sub>                     | CTMR = 0.2µF                                                                   |   |      | 3.03           |       | hr       |

| Equalization Charge Termination Time                                 | CTMR = 0.2µF, MODE1 = M, H<br>CTMR = 0.2µF, MODE1 = L                          |   |      | 0.379<br>0.758 |       | hr<br>hr |

| INTV <sub>CC</sub> Regulator (INTV <sub>CC</sub> Pin)                |                                                                                |   |      |                |       |          |

| INTV <sub>CC</sub> Regulation Voltage                                |                                                                                |   |      | 5.00           |       | V        |

| INTV <sub>CC</sub> Dropout Voltage                                   | DCIN = 4.5V, INTV <sub>CC</sub> = 5mA                                          |   |      | 4.46           |       | V        |

| INTV <sub>CC</sub> Supply Short-Circuit Current                      | INTV <sub>CC</sub> = 0V                                                        |   | 100  | 175            |       | mA       |

| NMOS FET Drivers                                                     |                                                                                |   |      |                |       |          |

| Top Gate Driver Switch On Resistance                                 | BST – SW = 5V, Pull Up<br>BST – SW = 5V, Pull Down                             |   |      | 2.3<br>1.3     |       | Ω        |

| Bottom Gate Driver Switch On Resistance                              | INTV <sub>CC</sub> = 5V, Pull Up<br>INTV <sub>CC</sub> = 5V, Pull Down         |   | 2.3  |                | Ω     |          |

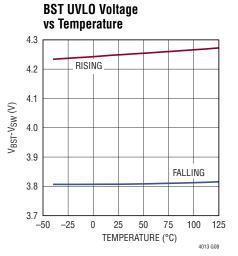

| BST UVLO                                                             | TG Enabled (Rising)<br>TG Disabled (Falling)                                   |   |      | 4.25<br>3.81   |       | V        |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2). DCIN,  $V_{IN}$ ,  $VIN_S = 18V$ , ENAB = 1.4V, SYNC = 0V, unless otherwise noted.

| PARAMETER                               | PARAMETER CONDITIONS                                                                                                                               |   | MIN         | TYP         | MAX  | UNITS      |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------|-------------|------|------------|

| OSC                                     |                                                                                                                                                    |   |             |             |      |            |

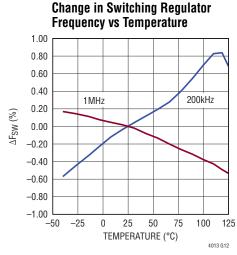

| Switching Frequency                     | $R_T = 40.2k\Omega$ $R_T = 232k\Omega$                                                                                                             | • | 950         | 1000<br>200 | 1050 | kHz<br>kHz |

| SYNC Pin Threshold (Falling Edge)       |                                                                                                                                                    |   | 1.3         | 1.4         | 1.5  | V          |

| SYNC Pin Hysteresis                     |                                                                                                                                                    |   |             | 190         |      | mV         |

| CLK Output Logic Level                  | High<br>Low                                                                                                                                        |   | 4.5         |             | 0.5  | V          |

| Input PowerPath Control                 |                                                                                                                                                    |   |             |             |      |            |

| Reverse Turn-Off Threshold Voltage      | DCIN - V <sub>IN</sub>                                                                                                                             | • | -7.3        | -4.4        | -1.3 | mV         |

| Forward Turn-On Threshold Voltage       | DCIN - V <sub>IN</sub>                                                                                                                             | • | -7.1        | -4.2        | -1.1 | mV         |

| Forward Turn-On Hysteresis Voltage      | DCIN - V <sub>IN</sub>                                                                                                                             |   |             | 0.2         |      | mV         |

| INFET Turn-Off Current                  | INFET = V <sub>IN</sub> + 1.5V                                                                                                                     |   |             | -9.0        |      | mA         |

| INFET Turn-On Current                   | INFET = V <sub>IN</sub> + 1.5V                                                                                                                     |   |             | 60          |      | μА         |

| INFET Clamp Voltage                     | I <sub>INFET</sub> = 2μA , DCIN = 12V to 60V<br>V <sub>IN</sub> = DCIN - 0.1V<br>Measure VINFET - DCIN                                             | • | 11.0 12.5   |             | V    |            |

| INFET Off Voltage                       | I <sub>INFET</sub> = -2μA , DCIN = 12V to 59.9V<br>V <sub>IN</sub> = DCIN +0.1V<br>Measure VINFET - DCIN                                           | • | -2.2 -1.6   |             | V    |            |

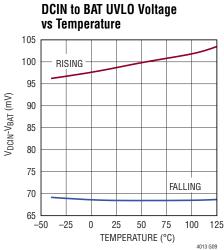

| DCIN to BAT UVLO                        | Switching Regulator Turn Off (V <sub>DCIN</sub> – V <sub>BAT</sub> Falling)                                                                        |   |             | 69          |      | mV         |

|                                         | Switching Regulator Turn On (V <sub>DCIN</sub> – V <sub>BAT</sub> Rising)                                                                          |   |             | 99          |      | mV         |

| MPPT Regulation                         |                                                                                                                                                    |   |             |             |      |            |

| FBOC Voltage Range                      |                                                                                                                                                    | • | 1.0         |             | 3.0  | V          |

| MPPT Sample Period                      |                                                                                                                                                    |   |             | 10.2        |      | S          |

| MPPT Sample Pulse Width                 |                                                                                                                                                    |   |             | 271         |      | μs         |

| Regulation Input Offset                 | Set FBOC Look at MPPT Regulation                                                                                                                   |   | -40         |             | 40   | mV         |

| MPPT Input Burst Mode Turn On Threshold | V <sub>MPPT</sub> – V <sub>FBOC</sub> (Converted) , V <sub>FBOC</sub> = 1.5V<br>V <sub>SENSE</sub> – V <sub>BAT</sub> < C/10 Part Enter Burst Mode | • | -45 -32 -15 |             | mV   |            |

| MPPT Input Burst Mode Hysteresis        | FBOC = 1.5V, V <sub>SENSE</sub> – V <sub>BAT</sub> < C/10<br>MPPT Turn Off – Turn On                                                               | • | 35          | 62          | 85   | mV         |

**Note 1.** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2.** The LTC4013 is tested under pulse loaded conditions such that  $T_J \approx T_A$ . The LTC4013E is guaranteed to meet performance specifications from 0°C to 85°C junction temperature. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC4013I is guaranteed over the full -40°C to 125°C operating junction temperature range. The junction temperature ( $T_J$  in °C) is calculated from the ambient temperature ( $T_A$  in °C) and power dissipation ( $P_D$  in Watts) according to the formula:  $T_J = T_A + P_D \bullet \theta_{JA}$  where  $\theta_{JA}$  (in °C/W) is the package thermal impedance. Note that the maximum ambient

temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal resistance and other environmental factors. This IC includes over temperature protection that is intended to protect the device during momentary overload. Junction temperature will exceed 125°C when over temperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

Note 3.  $V_{\text{IN}}$  does not include switching currents.

**Note 4.**  $I_{VIN}$  current also includes current that charges capacitance on CLKOUT. This current is approximately  $C_{CLKOUT} \bullet 5V \bullet f_{SW}$ . For this test  $C_{CLKOUT}$  was 100pF,  $f_{SW}$  was 1MHz ( $R_T = 40.2k$ ) so the current included is 0.5mA. In normal operation the CLKOUT capacitance is much less.

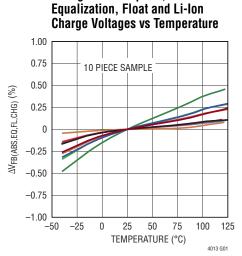

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , unless otherwise noted.

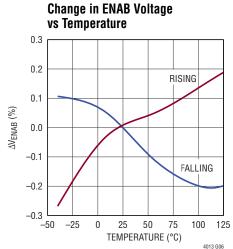

Change in Absorption,

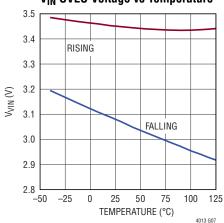

#### **VIN UVLO Voltage vs Temperature**

Rev B

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

## PIN FUNCTIONS

**INFET (Pin 1):** Input PowerPath MOSFET Gate Drive. An internal charge pump provides turn-on drive for this pin. This pin should be connected to the gate of an external N-channel MOSFET to prevent battery discharge when DCIN is less than the battery voltage.

**DCIN (Pin 2):** Input Supply Pin. This pin is used to sense the input voltage to determine whether to enable the INFET charge pump. It also supplies power to the INFET charge pump.

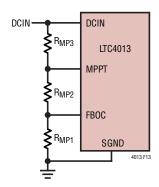

MPPT, FBOC (Pins 3, 4): Maximum Power Point Tracking (MPPT) Regulation Loop Set-Point Pins. The input voltage regulation loop regulates charge current, providing maximum power charging in the presence of a power limited source such as a solar panel. A resistor divider is placed from the input supply to MPPT, FBOC and ground. These pins are used to program the input voltage regulation loop as a percentage of the input open circuit voltage. If the input voltage falls below the programmed percentage of the open-circuit voltage, the MPPT loop will reduce charge current to maintain the target maximum power point voltage at DCIN. If the input voltage regulation feature is not used, connect FBOC to INTV<sub>CC</sub>.

**ENAB (Pin 5):** Precision Threshold Enable Pin. The enable threshold is 1.22V (rising), with 170mV of hysteresis. In shutdown, all charging functions are disabled and input supply current is reduced.

**ISMON (Pin 6):** Charge Current Monitor Pin. The voltage on this pin is twenty times the differential voltage between SENSE and BAT and can be used to monitor charge current.

**STATO, STAT1 (Pins 7, 8):** Open drain outputs that indicate the charger status. These pins can sink 5mA, enabling them to drive an LED. Specific states are detailed in Table 2.

**LB** (**Pin 9**): Low Battery Level Control Pin. A precision  $20\mu\text{A}$  current sourced from LB to an external resistor sets the detection voltage for a deeply discharged battery. If FB stays below LB for 1/8 of the absorption timeout period, charging is stopped. Charging is reinitiated with an ENAB pin toggle, a power cycle or by swapping out the battery.

**TMR (Pin 10):** Timer Capacitor Pin. A capacitor from this pin to ground sets the time the charger spends in various charging stages. The equalization timeout is a ratio of this time, either 1/4 or 1/8 of the absorption time, depending on the MODE pins settings. The low battery timeout period is 1/8 of the absorption time.

**MODE1, MODE2 (Pins 11, 12):** Charge Algorithm Control Pins. See Table 1. The LTC4013 supports 2, 3 and 4-stage lead-acid as well as Li-lon charging algorithms with and without termination. The MODE pins are tri-state and should be strapped to INTV<sub>CC</sub>, ground or left floating.

**CLKOUT (Pin 13):** Oscillator Frequency Output Pin. This logic output is roughly 180 degrees out of phase with the switching regulator's oscillator.

**SYNC (Pin 14):** Frequency Synchronization Pin. This pin allows the switching frequency to be synchronized to an external clock. The  $R_T$  resistor should be chosen to operate the internal clock 20% slower than the SYNC pulse frequency. Ground SYNC when not in use.

**RT (Pin 15):** Switching Regulator Frequency Control Pin. A mandatory resistor from RT to ground sets the switching frequency between 200kHz and 1MHz.

**ITH (Pin 16):** Compensation Control Pin. This pin is used to compensate the switching regulator's constant-current control loop.

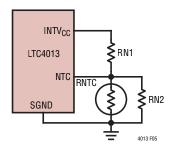

**NTC (Pin 17):** Thermistor Input Pin. With the use of an external NTC thermistor, the NTC pin can be used to develop a temperature dependent charge voltage for lead-acid batteries. NTC pin voltages above 3.3V disable the NTC function. The NTC function is not suitable for Lithium Ion batteries and should be disabled by strapping NTC to  $INTV_{CC}$ .

**FB** (Pin 18): Constant-Voltage Feedback Pin. This pin provides feedback for regulating battery voltage during the constant-voltage phase of charging. A resistor divider from the battery to this pin sets the constant-voltage charging level.

## PIN FUNCTIONS

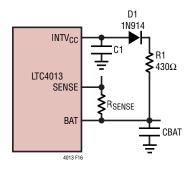

**BAT, SENSE (Pins 19, 20):** Charge Current Sense Pins. Battery charge current is monitored and regulated via a current sense resistor between SENSE and BAT. The constant-current servo voltage between these pins is 50mV. Overcurrent shutdown occurs when the SENSE to BAT voltage exceeds 100mV.

**BST** (**Pin 21**): High Side Gate Drive Supply Pin. BST provides a flying 5V supply for the high-side MOSFET driver. Connect a  $0.22\mu\text{F}$  capacitor from this pin to SW. Connect a diode with its cathode to this pin and its anode to the INTV<sub>CC</sub> pin.

**TG (Pin 22):** Top Gate Drive Pin. TG drives the gate of the top side external N-channel MOSFET.

**SW (Pin 23):** Switching Regulator Power Pin. SW connects to the power supply switch node which includes one side of the inductor, the source of the top side MOSFET, the drain of the bottom side MOSFET and the boost capacitor.

**BG (Pin 24):** Bottom Gate Drive Pin. BG drives the gate of the external bottom side N-channel MOSFET.

**INTV**<sub>CC</sub> (Pin 25): Internal V<sub>CC</sub> Pin. Powered by V<sub>IN</sub>, this pin is the output of a 5V regulator that powers the internal control logic and analog circuits. Connect a ceramic capacitor from INTV<sub>CC</sub> to PGND. The BST pin refresh diode anode should also be connected to INTV<sub>CC</sub>.

**PGND (Pin 26):** Power Ground. This is the power ground for the LTC4013. It services only the BG pin drive.

**V<sub>IN</sub>** (**Pin 27**): Input Supply Pin. V<sub>IN</sub> provides power to the INTV<sub>CC</sub> internal 5V regulator. It is usually tied to the switching regulator high side MOSFET and should be bypassed with one or more low-ESR capacitors to ground.

**VIN\_S (Pin 28):** Input Supply Sense Input. VIN\_S provides a Kelvin input for the  $V_{IN}$  connection of the input PowerPath circuitry.

**SGND** (Exposed Pad Pin 29): Signal Ground Reference. This pin is the quiet ground used as a reference point for critical resistor dividers such as the battery feedback divider, MPPT divider and thermistor. Connect SGND to the output decoupling capacitor negative terminal and battery negative terminal. Solder SGND to a solid ground plane through multiple vias for rated thermal performance.

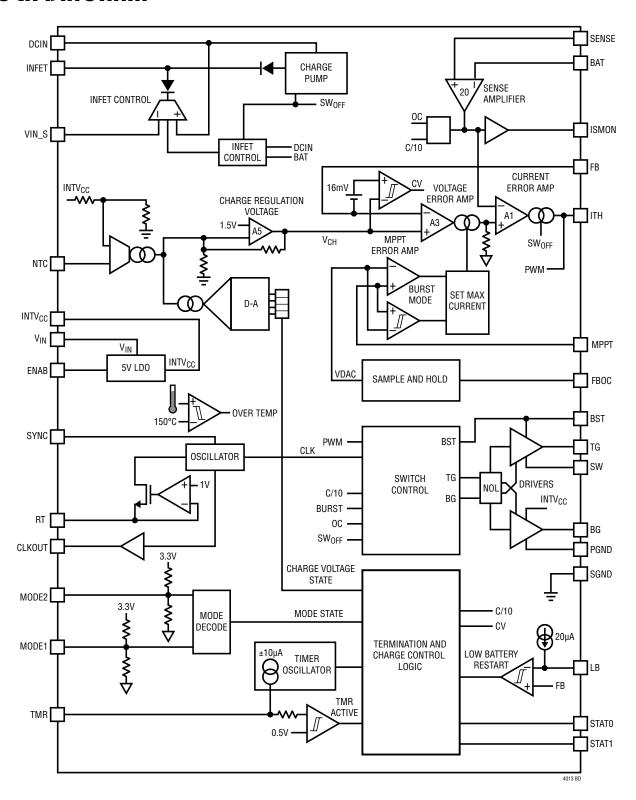

## **BLOCK DIAGRAM**

#### **OVERVIEW**

The LTC4013 is a high-voltage multi-chemistry battery charger with specific focus on lead-acid batteries. It incorporates a step-down (buck) DC/DC synchronous switching controller using external N-channel MOSFETS for high efficiency. It accommodates a wide range of battery voltages from 2.4V to 60V and is optimized for high current charging applications.

Selectable charger profiles are:

2-stage charging: constant-current (bulk) to constant-voltage with and without timer termination.

3-stage lead-acid charging: bulk, absorption and float with low battery restart and either charge-current (C/10) or safety-timer absorption to float transition control.

4-stage lead-acid charging: bulk, absorption, equalization, and float with low battery restart and safety-timer equalization cutoff and safety-timer absorption to float transition control.

Li-lon constant-current to constant-voltage charging with either charge-current (C/10) or safety-timer charge termination.

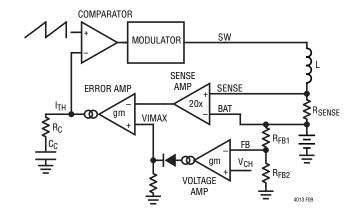

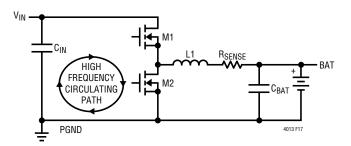

#### DC/DC OPERATION

#### (See Block Diagram)

The LTC4013 uses a fixed-frequency, average current mode DC/DC converter to regulate charge current. When the battery reaches the charge voltage, current is reduced by a voltage regulation loop.

Battery current is sensed via a resistor placed between SENSE and BAT. The amplified signal is compared to a voltage that represents the maximum allowable charge current and regulates the average current by controlling the duty cycle of the output switches. The current control loop servos the differential voltage between SENSE and BAT to 50mV making I<sub>CHGMAX</sub> = 50mV/R<sub>SENSE</sub>. A frequency-compensation pin (ITH) is used to control the constant-current feedback loop stability.

At startup, the maximum current is ramped over approximately 1.6ms to provide soft start. There is an additional burst mode feature used for maximum power point transfer to facilitate low solar panel current operation.

When the battery voltage reaches the programmed charge voltage, error amplifier A3 adjusts the charge current to servo the battery voltage to the programmed level and can reduce the current to zero.

The charge voltage is determined by amplifier A5 and the charge algorithm selected. The voltage can follow a continuous function of temperature controlled by an amplifier connected to the NTC pin. A resistor divider with a thermistor sets the temperature coefficient of the voltage.

The switching regulator's oscillator frequency is set by a resistor from the RT pin to ground. The clock frequency can optionally be synchronized to an external oscillator by using the SYNC pin.

The step-down (buck) switching regulator uses external low  $R_{DS(ON)}$  MOSFETs for both high and low side switches to deliver high charge current. When the current level falls below  $I_{CHGMAX}/10$  the bottom MOSFET is disabled and switching operation is discontinuous with only the bottom side MOSFET body diode used for low side conduction. This diode emulation mode ensures the battery is not discharged by continuous conduction.

Supply voltage for the top gate drive is generated by a boost circuit that uses an external diode and boost capacitor charged from  $\mathsf{INTV}_{\mathsf{CC}}.$  If BST - SW is below 3.8V (e.g. at startup), the bottom side MOSFET is enabled to refresh the BST capacitor.

#### **Solar Panel Maximum Power Point Tracking**

If the MPPT function is enabled (FBOC pin voltage < 3V), the LTC4013 employs an MPPT circuit that compares a stored open-circuit input voltage measurement against the instantaneous DCIN voltage while charging. The LTC4013 then uses an input voltage sense amplifier to reduce the charge current if the DCIN voltage falls below the user

defined percentage of the open-circuit voltage. With this algorithm the LTC4013 optimizes power transfer for a variety of different input sources.

When MPPT is enabled, the LTC4013 periodically measures the open-circuit input voltage. About once every 10.2s the LTC4013 pauses charging, samples the input voltage as measured through a resistor divider at the FBOC pin, and reproduces this value internally with a digital-to-analog converter (DAC). When charging resumes, the DAC voltage, VDAC, is compared against the MPPT pin voltage that is programmed with a resistor divider. If the MPPT voltage falls below VDAC, charge current is reduced to regulate the input voltage at that level. This regulation loop maintains the input voltage at or above a user defined level that corresponds to the peak power available from the applied source. Regular input sampling is useful, for instance, to provide first order temperature compensation of a solar panel.

The sampling time is fixed internally. Switching stops for approximately 1.7ms every 10.2s. There is an initial 1.4ms delay allowing DCIN to rise to its open circuit voltage. During the next 300µs, the FBOC pin voltage is sampled and stored. The sampling of DCIN is done at an extremely low duty cycle to have minimal impact on the total charge current.

#### **MPPT Burst Mode Operation**

In low light, it is desirable to improve switching regulator efficiency for maximum power delivery. The LTC4013 contains proprietary circuitry that improves switching regulator efficiency during these conditions. Efficiency is improved by reducing the maximum switching regulator current and periodically disabling the switching regulator, resulting in burst-mode operation. Burst-mode is enabled when MPPT is below the sampled FBOC voltage by approximately 32mV and the current is below  $I_{CHGMAX}/10$  (SENSE-BAT < 5mV). The LTC4013 stays in burst-mode until the next sampling period when it is reevaluated. If MPPT is above the sampled FBOC voltage by approximately 32mV then burst-mode is disabled. The net result is that in burst-mode the DCIN voltage has approximately a 64mV hysteretic ripple at the FBOC pin.

#### **Battery Charger Operation**

There are a variety of battery chemistries and there are numerous online resources and books available for education. One good resource is www.batteryuniversity.com. Many battery manufacturers also provide detailed information.

The LTC4013 provides constant-current/constant-voltage charging. When the battery voltage is below the constant-voltage servo level, charge current is controlled by the constant-current control loop. As the battery charges, its voltage increases and eventually holds at the constant-voltage servo level whereupon charge current tapers naturally toward zero as the battery tops off.

In constant-current charging the charge current is controlled by the fixed servo voltage of 50mV divided by the external sense resistor between SENSE and BAT.

Once the battery voltage increases and the charger is in the constant-voltage charging phase, the battery charge voltage is controlled by the FB pin.

The FB voltage regulation levels are appropriate for a single-cell lead-acid battery. For instance, a 2.267V single-cell float voltage corresponds to a 6-cell battery voltage of  $6 \cdot 2.267V = 13.6V$ .

The LTC4013 also contains a charge cycle timer. This timer is used for the absorption to float transition in 3-stage and 4-stage lead-acid charging, equalization timeout in 4-stage lead-acid charging and constant-voltage timeout in both Li-Ion and 2-stage charging. The timer is activated by connecting a capacitor from the TMR pin to ground. Grounding TMR disables all timer functions.

The LB pin provides a user adjustable low battery voltage setting that sets the re-start level in 2-stage, 3-stage and 4-stage charging and the low battery fault level in Li-Ion charging. The LB pin produces a precision  $20\mu\text{A}$  current which results in a precision voltage when a resistor is placed from LB to ground. The LB pin is compared internally to the FB pin for low battery determination.

Four possible charging algorithms can be selected by pin strapping or manipulating the MODEO and MODE1 pins (see Table 1). These pins should be tied either low (GND), high (INTV<sub>CC</sub>) or mid (floating). The charge algorithms are described below.

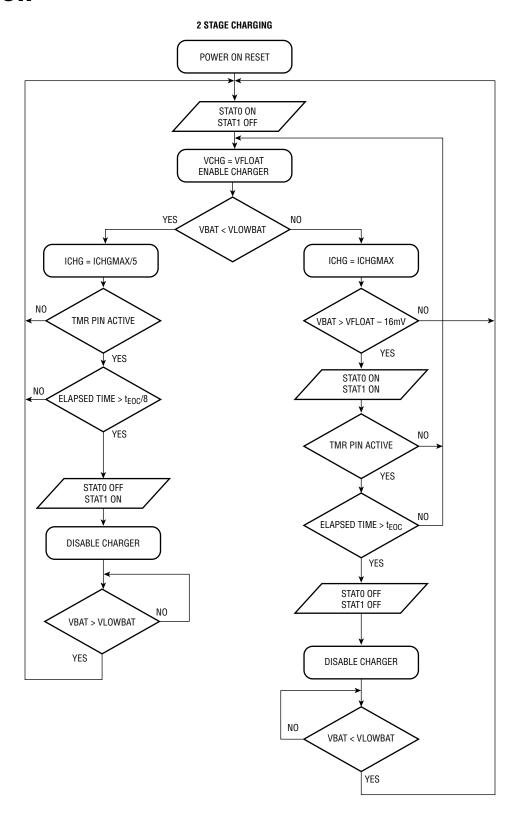

#### 2-Stage Charging

2-stage charging is useful for batteries with no absorption preconditioning. Charging is initiated on input power-up whereupon the battery charges with constant-current at  $I_{CHGMAX}$  toward  $V_{FB(FL)}$ . The STATO pin pulls low immediately indicating that charging has begun. Once the battery terminals approach  $V_{FB(FL)}$ , the constant-voltage control loop takes over holding the battery voltage steady as the charge current naturally tapers to zero. Once the constant-voltage loop takes control, the STAT1 pin also pulls low indicating the change from constant-current to constant-voltage charging.

If a capacitor is used on the TMR pin, the charge cycle terminates after an accumulated period of  $t_{EOC}$  in constant-voltage mode at which time STAT0 and STAT1 will indicate termination by switching off. Alternately, if the TMR pin is grounded, 2-stage charging will charge forever at  $V_{FB(FL)}$  with no termination.

Charging is re-initiated from termination if the FB-referred battery voltage drops below the LB threshold voltage as set by the LB pin, or if the LTC4013 is powered off and back on by cycling the ENAB pin or input power.

Defective battery protection is enabled if the timer capacitor is used. Whenever the FB-referred battery voltage is below the LB threshold, charge current is automatically reduced to  $I_{CHGMAX}/5$ . If a defective battery remains below the low battery threshold longer than 1/8 of the timer period ( $t_{EOC}/8$ ) the charge cycle terminates. A defective battery fault is indicated by STATO turning off and STAT1 turning on.

There are two voltage settings available for 2-stage charging as noted in Table 1.

2-stage charging for a lead-acid battery has the disadvantage of not fully charging the battery, resulting in diminished capacity over time due to increased deposits on the electrodes.

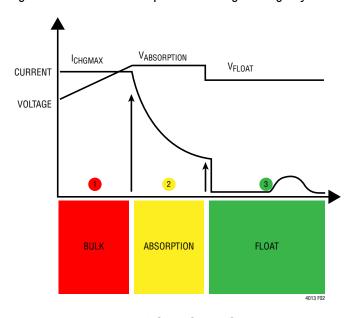

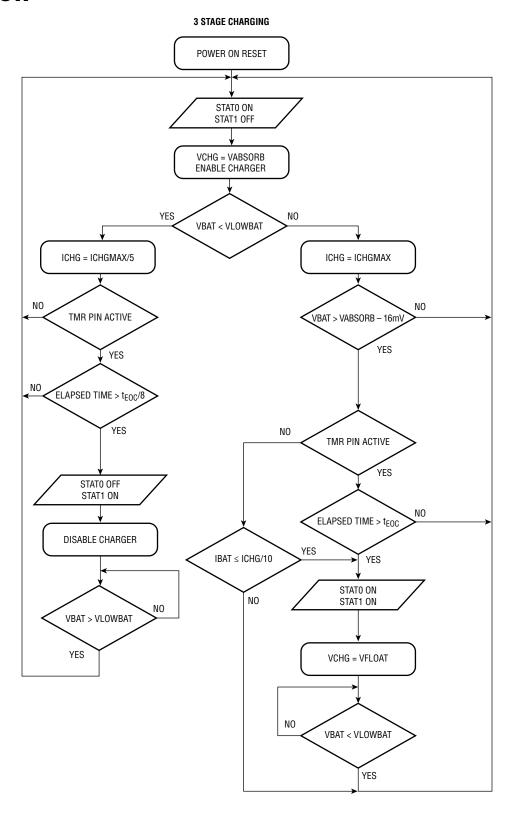

#### 3-Stage Charging

A more complete lead-acid battery charging method is 3-stage charging utilizing an absorption phase which increases the amount of stored charge in the battery. Because the absorption voltage is above the electrochemical float level, the time that the battery stays in this condition should be limited either by a timer (the safest method) or waiting for the charge current to diminish. Minor gassing of water from the battery can occur from charging the battery above the float voltage, so choosing an appropriate absorption voltage is important for best battery life. Always consult the battery manufacturer for their recommendations.

3-stage charging is initiated on input power-up whereupon the battery charges with constant-current at  $I_{CHGMAX}$  toward  $V_{FB(ABS)}$ . The STATO pin pulls low immediately indicating that charging has begun. As the battery voltage approaches  $V_{FB(ABS)}$ , charge current naturally tapers to zero. When the charge current drops to  $I_{CHGMAX}/10$ , STAT1 also pulls low and the charge voltage setting changes to the  $V_{FB(FL)}$  voltage. At this lower level, the constant-voltage control loop will "capture" and hold the battery voltage as it slowly drops from  $V_{FB(ABS)}$  down to  $V_{FB(FL)}$ .

Alternately, the transition from absorption charging to float charging can be controlled with the timer by placing a capacitor on the TMR pin. When the battery voltage reaches constant-voltage in the absorption phase, the timer begins. At the end of the accumulated timer period in constant-voltage mode at  $V_{FB(ABS)}$ , the charge voltage changes to the  $V_{FB(FL)}$  voltage and will remain there. Again, STAT1 turns on, indicating the transition from the  $V_{FB(ABS)}$  charging level to the  $V_{FB(FL)}$  charging level.

If a load subsequently pulls the FB-referred battery voltage below the LB pin, or if the LTC4013 is powered off and back on by cycling the ENAB pin or input power, a new 3-stage charge cycle is initiated with a new absorption phase.

Defective battery protection is enabled if the timer capacitor is used. Whenever the FB-referred battery voltage is below the LB threshold, charge current is automatically reduced to  $I_{CHGMAX}/5$ . If a defective battery remains below the low battery threshold longer than 1/8 of the timer period ( $t_{EOC}/8$ ) the charge cycle terminates. A defective battery fault is indicated by STATO turning off and STAT1 turning on.

There are different options for absorption and float voltages. Table 1 details the MODE pins settings and FB voltages. Figure 1 shows an example of a 3-stage charge cycle.

Figure 1. 3-Stage Charge Cycle

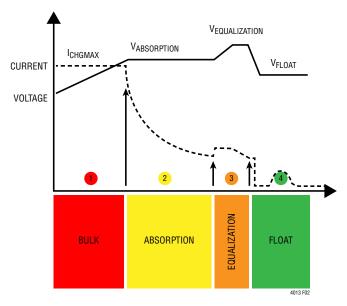

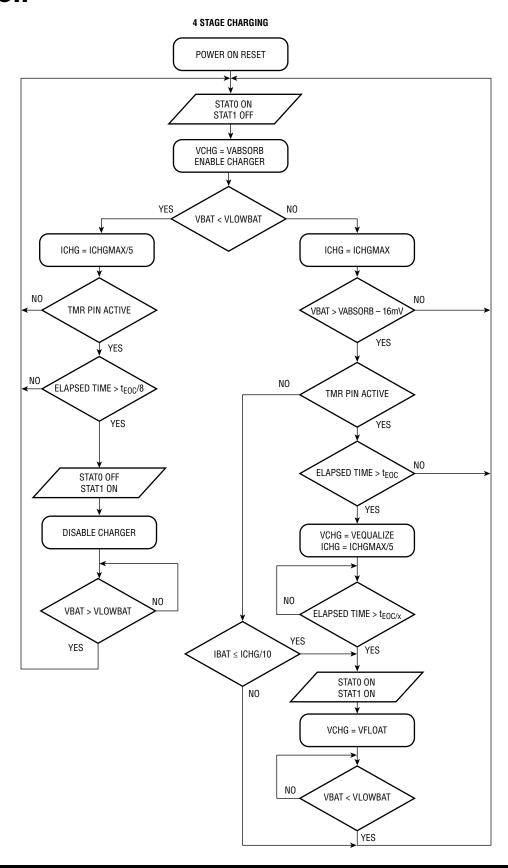

#### 4-Stage Charging

A 4-stage charging algorithm adds an equalization phase to the 3-stage method after the absorption phase. The equalization voltage is significantly higher than the absorption voltage and works in two ways. One is to purposely

introduce gassing which stirs the battery electrolyte and reduces electrolyte stratification. Equalization also electrochemically eliminates sulfates on the electrodes which is the main cause of battery performance degradation. Sulfates typically form in heavily discharged batteries. Equalization is not done with sealed batteries because of the gassing. If lost water is not replaced, the battery will be degraded. An equalization cycle should be performed on a periodic, service-only, basis only if the manufacturer of the battery approves of the technique and should be monitored for dangerous conditions. Use of 4-stage charging is highly discouraged for solar applications as sporadic light patterns can cause multiple equalization cycles per day. Not all batteries can be charged with a 4-stage cycle so you must consult with your battery manufacturer as to its frequency of use and recommended charge voltage.

Charging is initiated on input power-up whereupon the battery charges with constant-current at I<sub>CHGMAX</sub> toward V<sub>FR(ARS)</sub>. The STATO pin pulls low immediately indicating that charging has begun. As the battery voltage approaches V<sub>FR(ARS)</sub>, charge current naturally tapers to zero and the timer starts. At the end of the timer period, the charge voltage setting changes to the equalization voltage  $V_{FB(EQ)}$ . The timer is then restarted and the charge current setting is dropped to  $I_{CHGMAX}/5$ . The equalization phase continues until the end of equalization timeout, either  $t_{EOC}/4$  or  $t_{EOC}/8$ , as programmed by the MODE pins. After the equalization timeout, the charge voltage is reduced to the V<sub>FR(FL)</sub> voltage and STAT1 turns on indicating the end of the charge cycle. The 4-stage cycle always requires the use of a capacitor on the TMR pin as a safety precaution to ensure that charging time at the high equalization voltage is limited. If the TMR pin is grounded, the 4-stage charge cycle will revert to 3-stage charging with no equalization phase.

The LTC4013 ensures that only one equalization phase will run per power-on cycle. After a 4-stage cycle completes, all subsequent low battery (LB) cycles will only trigger a 3-stage cycle with absorption phase and not a 4-stage cycle with equalization. Only a power-off event or ENAB pin cycle will result in a complete 4-stage equalization cycle.

Defective battery protection is enabled if the timer capacitor is used. Whenever the FB-referred battery voltage is below the LB threshold, charge current is automatically reduced to  $I_{CHGMAX}/5$ . If a defective battery remains below the low battery threshold longer than 1/8 of the timer period ( $t_{EOC}/8$ ) the charge cycle terminates. A defective battery fault is indicated by STATO turning off and STAT1 turning on.

Figure 2 shows an example of a 4-stage charge cycle.

Figure 2. 4-Stage Charge Cycle

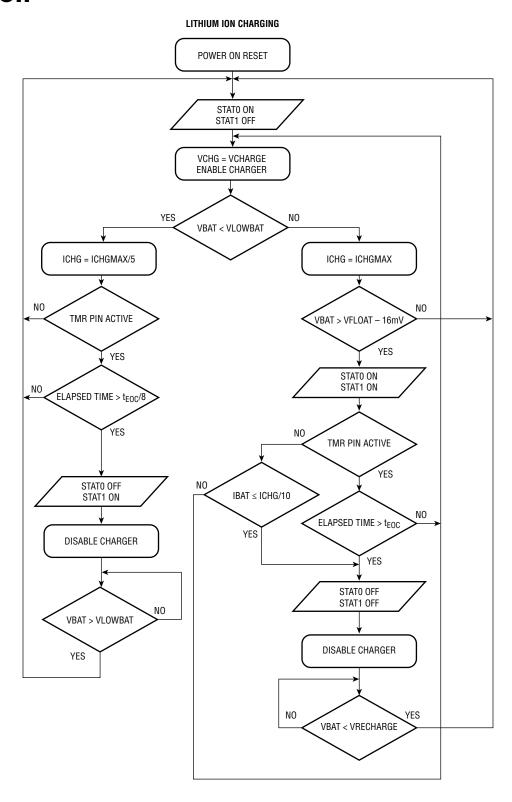

#### Li-Ion Charging

The LTC4013 can also charge Li-Ion batteries including Li-Polymer and LiFePO<sub>4</sub>.

Charging is initiated on input power-up whereupon the battery charges with constant-current at  $I_{CHGMAX}$  toward  $V_{FB(CHG)}$ . The STATO pin pulls low immediately indicating that charging has begun. As the battery voltage approaches  $V_{FB(CHG)}$ , charge current naturally tapers to zero. The STAT1 pin also turns on indicating constant-voltage operation. There are two options for Li-lon charge termination. If a capacitor is included on the TMR pin, the timer starts when the battery reaches the constant-voltage regulation point.

Once the timer expires ( $t_{EOC}$ ), charging is terminated. Alternately, if the TMR pin is grounded, the timer is disabled and charging terminates when the charge current drops to 1/10 of  $l_{CHGMAX}$  (C/10). Termination is indicated by STATO and STAT1 turning off.

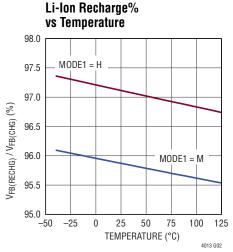

The LTC4013 will begin charging again if the FB-referred battery voltage falls below the Lilon recharge level  $V_{FB(RECHG)}$ . The recharge voltage is either 97.0% or 95.6% of  $V_{FB(CHG)}$  depending on the MODE pins. To avoid frequent recharge events due to voltage sag on LiFePO<sub>4</sub> batteries, the wider difference is recommended.

Defective battery protection is enabled if the timer capacitor is used. Whenever the FB-referred battery voltage is below the LB threshold, charge current is automatically reduced to  $I_{CHGMAX}/5$ . If a defective battery remains below the low battery threshold longer than 1/8 of the timer period ( $t_{EOC}/8$ ) the charge cycle terminates. A defective battery fault is indicated by STATO turning off and STAT1 turning on.

#### **Mode Pins and Battery Charge Voltages**

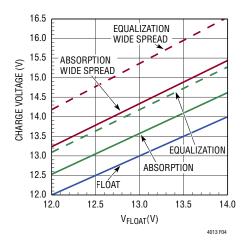

The LTC4013 provides several different options for setting the  $V_{FB(FL)}$ ,  $V_{FB(ABS)}$  and  $V_{FB(EQ)}$  voltages. In normal mode, single-cell absorption is approximately 100mV above float (600mV for 6 cells), equalization is then approximately 133mV above absorption (800mV for 6 cells). Another option uses a wider voltage spread where single-cell absorption voltage is 200mV above float (1.2V for 6 cells) and equalization is 200mV above absorption (1.2V for 6 cells). Absolute voltages are adjusted through the FB resistor divider to gain these voltages up proportionately. It is important to consult your battery manufacturer for their suggestion on charging voltages. There is no industry consensus and it depends heavily on the type of battery and anticipated usage.

Table 1 shows the MODEO/1 pin settings to select the charge algorithm and the range of charge voltage settings for the normal and wide spread voltage modes and Table 2 shows the STATO/1 indicator pin values in various charging states.

Table 1. Mode Pin Settings

| Stages  | Spread | MODE1 | MODE2 | VFLOAT | VRecharge | VAbsorb | VEqualize | TEqualize           |

|---------|--------|-------|-------|--------|-----------|---------|-----------|---------------------|

| Li-lon  | Wide   | M     | M     | 2.400V | 2.295V    |         |           |                     |

| Li-lon  | Normal | Н     | M     | 2.367V | 2.295V    |         |           |                     |

| 2-Stage | n/a    | L     | L     | 2.267V |           |         |           |                     |

| 2-Stage | n/a    | L     | M     | 2.333V |           |         |           |                     |

| 3-Stage | Wide   | M     | L     | 2.200V |           | 2.400V  |           |                     |

| 3-Stage | Normal | Н     | L     | 2.267V |           | 2.367V  |           |                     |

| 4-Stage | Normal | L     | Н     | 2.267V |           | 2.367V  | 2.500V    | t <sub>EOC</sub> /4 |

| 4-Stage | Normal | Н     | Н     | 2.267V |           | 2.367V  | 2.500V    | t <sub>EOC</sub> /8 |

| 4-Stage | Wide   | M     | Н     | 2.200V |           | 2.400V  | 2.600V    | t <sub>EOC</sub> /8 |

**Table 2. Status Pin Indications**

| STAT0 | STAT1 | Li-lon / 2-Stage                      | 3-Stage / 4-Stage           |  |

|-------|-------|---------------------------------------|-----------------------------|--|

| OFF   | OFF   | Not Charging or<br>Terminated         | Not Charging                |  |

| ON    | OFF   | Charging C <sub>C</sub>               | Absorb/Equalize<br>Charging |  |

| ON    | ON    | Charging CV                           | Float Charging              |  |

| OFF   | ON    | Low Battery or Thermal Shutdown Fault |                             |  |

Figure 3. 6 Cell Lead-Acid Charge Voltages with R<sub>FB1</sub>/R<sub>FB2</sub> Change

Figure 3 shows the relationship between the float voltage, the absorption and the equalization voltages for a given feedback divider setting.

The following diagrams show the details of each charge algorithm.

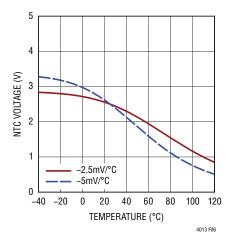

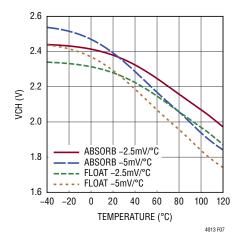

#### **Charge Voltage Temperature Compensation**

The LTC4013 can use a thermistor to adjust the battery charge voltage as a function of temperature. The change in FB-referred charge voltage from its nominal level is given by  $\Delta V_{FB} = (VNTC - VINTV_{CC}/2) - 0.21$ . Voltages above 3.3V disable the NTC feature. The transfer function, when combined with a thermistor, is stronger than necessary. It is configured this way so that any thermistor can be diluted with a low drift resistor to achieve the desired temperature coefficient. To avoid the 3.3V NTC disable threshold, the LTC4013 requires that the dilution resistor be placed in parallel with the thermistor rather than in series. The bias resistor from INTV<sub>CC</sub> to NTC should be equal to the parallel combination of the thermistor at 25°C and the dilution resistor.

Figure 4 shows the NTC circuit configuration and Table 3 shows some common temperature coefficient and associated resistor settings using a 10k,  $\beta$  = 3380K thermistor.

Figure 4. NTC Configuration for Temperature Compensation

Table 3. Charge Voltage TC Examples Using  $\beta = 3380$  RNTC

|                           | <u> </u> |       |

|---------------------------|----------|-------|

| TC (WRT V <sub>FB</sub> ) | RN1      | RN2   |

| −2.5mV/°C                 | 2.49k    | 3.32k |

| -5.0mV/°C                 | 4.99k    | 10.0k |

Figure 5 shows the diluted thermistor voltage vs temperature and Figure 6 shows the resultant charge voltage vs temperature.

Figure 5. Diluted Thermistor Voltage vs Temperature

Figure 6. FB-Referred Charge Voltage vs Temperature

Since the thermistor is used to adjust charge voltage vs battery temperature, it is ideally placed in thermal contact with the battery. This is not always practical so the next best thing is to position the resistor to sense the battery's ambient temperature.

#### **Charge Termination Timer**

The LTC4013 supports timer-based functions wherein battery charge cycle control occurs after a specific amount of time. Timer termination is engaged when a capacitor ( $C_{TMR}$ ) is connected from the TMR pin to ground. For a desired end-of-cycle time ( $t_{EOC}$ )  $C_{TMR}$  follows the relation:

$$C_{TMR} (\mu F) = t_{FOC} (Hr) \cdot 0.066$$

The absorption and Li-Ion termination timer cycles start when the charger transitions from constant-current to constant-voltage charging. Equalization timing starts immediately upon transition to the equalization charge state and low battery timing commences when FB falls below LB.

#### Low Battery (LB) Pin

The LB pin is used to program the low battery level and is compared internally to the FB pin voltage. The LB pin sources a very precise 20µA current so the threshold voltage can be programmed simply by placing a resistor from LB to ground. For instance, 100k to ground sets the LB pin to 2.0V. In 2-stage and Li-lon charging a transition below the LB threshold triggers a new charge cycle if terminated. In 3-stage and 4-stage a transition below the LB threshold returns the charger to the absorption charging phase. In all four modes, Li-lon, 2-stage, 3-stage and 4-stage, and with a timer capacitor present, the low battery fault timer starts and the charge current is reduced to C/5. All four modes terminate charging if the low-battery timer expires.

A commonly used low-battery voltage for a 6 cell battery is 10.4V which represents the voltage with one of 6 cells shorted. This LB voltage is set with an 86.6k resistor for 1.73V/cell, or 10.4V/6 with a 6-to-1 FB divider.

## **Output Current Monitoring**

Charge current can be determined by observing the voltage at the ISMON pin. ISMON follows the expression:

ISMON =

$$20 \bullet (V_{SENSE} - V_{BAT})$$

.

## **Programming Switching Frequency**

The LTC4013 has an operational switching frequency range between 200kHz and 1MHz which is programmed with an external resistor from the RT pin to ground. Table 4 shows resistor values and their corresponding switching frequencies. An approximate formula is:

$$R_T(k\Omega) = \frac{40.2}{f_{SW}^{1.088} \text{ (MHz)}}$$

Table 4. R<sub>T</sub> Resistor Value

| Switching Frequency | $R_T\left(\Omega\right)$ |

|---------------------|--------------------------|

| 1MHz                | 40.2k                    |

| 750kHz              | 54.9k                    |

| 500kHz              | 86.6k                    |

| 300kHz              | 150k                     |

| 200kHz              | 232k                     |

## **Switching Frequency Synchronization**

The internal oscillator may also be synchronized to an external clock through the SYNC pin. The signal applied to the SYNC pin must have a logic low below 1.3V and a logic high above 1.7V. The input sync frequency must be 20% higher than the frequency that would otherwise be determined by the resistor at the RT pin. Input signals outside of these specified parameters cause erratic switching behavior and subharmonic oscillations. When synchronizing to an external clock, be aware that there is a fixed delay from the input clock edge to the edge of the signal at the SW pin. Ground the SYNC pin if synchronization to an external clock is not required.

#### **INFET Behavior**

The LTC4013 controls an input N-Channel MOSFET via an on-chip charge pump on INFET. The MOSFET provides a blocking path to prevent battery discharge when the input voltage is below the battery voltage. It also disconnects the input supply from the charger to measure the input voltage with no load for Maximum Power Point Tracking (MPPT).

#### **Undervoltage Lockouts**

The INFET charge pump and switching regulator are enabled when all four UVLO comparators are satisfied and the ENAB pin is above its precision enable threshold. Specifically,  $V_{IN}$  must be above its absolute threshold of 3.45V, DCIN must be greater than BAT by at least 99mV and must also be within 4mV of  $V_{IN}$ . A fourth UVLO requires that the battery voltage at SENSE be above its UVLO level of approximately 1.97V.

If the conditions above are not met then INFET is turned off and sinks current pulling INFET to approximately 2.2V below the lower voltage of DCIN or  $V_{IN}$ . If the input voltage is more than the gate breakdown of the external transistor, a TVS diode is required to prevent the disable current or pin leakage from pulling INFET all the way to ground. For MPPT applications requiring two transistors at INFET, a conventional diode will suffice as it will pull down the common source node safely.

#### Thermal Shutdown

The LTC4013 has thermal shutdown that disables charging at approximately 160°C. When the LTC4013 has cooled to 150°C, charging resumes. Thermal shutdown protects the device from excessive gate drive power and excess internal LDO power dissipation but does not necessarily prevent excess power dissipation in the external MOSFETS or other external components.

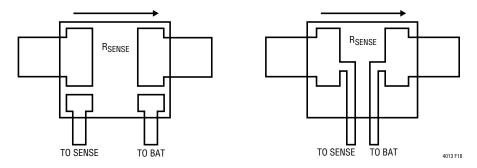

## **Setting Charge Current**

Charge current,  $I_{CHGMAX}$ , is determined by the current sense resistor between SENSE and BAT. The servo voltage is 50mV making the charge current 50mV/R<sub>SENSE</sub>. For a 10A charge current R<sub>SENSE</sub> should be 5m $\Omega$ . Accuracy requires the use of 4-terminal sense resistors or careful attention to ensure a Kelvin connection to the sense resistor. Figure 17 shows two examples. Size the resistor for power dissipation with PR<sub>SENSE</sub> =  $I_{CHGMAX} \bullet 50$ mV. For example, the 10A sense resistor needs to be at least ½Watt. Susumu, Panasonic and Vishay offer a wide variety of accurate sense resistors.

#### **Inductor Selection**

Size the inductor so that the peak-to-peak ripple current is approximately 30% of the maximum charging current. This is a reasonable trade-off between inductor size and ripple. Inductance can be computed with the following equation:

$$L = \frac{V_{IN} \cdot V_{BAT} - V_{BAT}^2}{0.3 \cdot f_{SW} \cdot I_{CHGMAX} \cdot V_{IN}}$$

where  $V_{BAT}$  is the battery voltage,  $V_{IN}$  is the input voltage,  $I_{CHGMAX}$  is the maximum charge current and  $f_{SW}$  is the switching frequency. Choose the saturation current for the inductor to be at least 20% higher than the maximum charge current.

To protect against faults, there is an overcurrent comparator which terminates switching when the voltage between the SENSE and BAT pins exceeds 100mV. When tripped, switching is stopped for a minimum of 4 switch cycles.

## **Switching Regulator MOSFET Selection**

Key parameters for MOSFET selection are: total gate charge  $(Q_G)$ , on-resistance  $(R_{DS(ON)})$ , gate to drain charge  $(Q_{GD})$ , gate-to-source charge  $(Q_{GS})$ , gate resistance  $(R_G)$ , breakdown voltage (maximum  $V_{GS}$  and  $V_{DS}$ ) and drain current (maximum  $I_D$ ). The following guidelines provide information to make the selection process easier. Table 5 lists some recommended manufacturers.

The rated drain current for both MOSFETs must be greater than the maximum inductor current. Peak inductor current is approximately:

$$I_{LMAX} = I_{CHGMAX} + \frac{V_{IN} \cdot V_{BAT} - V_{BAT}^{2}}{2 \cdot f_{SW} \cdot L \cdot V_{IN}}$$

The rated drain current is temperature dependent, and most data sheets include a table or graph of rated drain current versus temperature.

The rated  $V_{DS}$  must be higher than the maximum input voltage (including transients) for both MOSFETs.

The LTC4013 will drive the gates of the switching MOSFETs with about 5V (INTV $_{CC}$ ) with respect to their sources. However, during start-up and recovery conditions, the gate drive signals may be as low as 3V. Therefore, to ensure that the LTC4013 operates properly, use logic level threshold MOSFETs with a V $_{T}$  of about 2V or less. For a robust design, ensure that the rated maximum V $_{GS}$  is at least 7V.

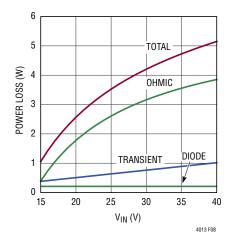

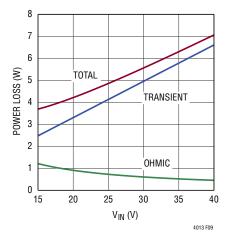

Power loss in the switching MOSFETs is related to the on-resistance,  $R_{DS(ON)}$ ; gate resistance,  $R_G$ ; gate-to-drain charge,  $Q_{GD}$  and gate-to-source charge,  $Q_{GS}$ . Power lost to the on-resistance is an ohmic loss,  $I^2R_{DS(ON)}$ , and usually dominates for input voltages less than 15V. Power lost while charging the gate capacitance typically dominates for voltages greater than 15V. When operating at higher input voltages, efficiency is optimized by selecting a high side MOSFET with higher  $R_{DS(ON)}$  and lower  $Q_G$ . The total power loss in the high side MOSFET is approximated by the sum of ohmic losses and transition losses:

$$\begin{aligned} &P_{HIGH\_LOSS} = \frac{V_{BAT}}{V_{IN}} \bullet I_{L}^{2} \bullet R_{DS(0N)} \bullet \rho_{T} + \\ &\frac{V_{IN} \bullet I_{L}}{5V} \bullet (Q_{GD} + Q_{GS}) \bullet (2 \bullet R_{G} + R_{PU} + R_{PD}) \bullet f_{SW} \end{aligned}$$

$\rho T$  is a dimensionless temperature dependent factor in the MOSFET's on-resistance. Using 70°C as the maximum ambient operating temperature,  $\rho T$  is roughly equal to 1.3. RPD and RPU are the LTC4013 high side gate driver output impedances:  $2.3\Omega$  and  $1.3\Omega$ , respectively.

For the low side MOSFET the power loss is approximated by:

$$\begin{aligned} &P_{LOW\_LOSS} = \left(1 - \frac{V_{BAT}}{V_{IN}}\right) \bullet I_L^2 \bullet R_{DS(ON)} \bullet \rho_T + \\ &\frac{V_{IN} \bullet I_L}{5V} \bullet \left(Q_{GD} + Q_{GS}\right) \bullet \left(2 \bullet R_G + R_{PU} + R_{PD}\right) \bullet f_{SW} \\ &+ V_f \bullet 2 \bullet f_{SW} \bullet I_I \bullet tnoI \end{aligned}$$

Where  $V_f$  is the voltage drop of the lower MOSFET bulk diode, typically 0.7V, and thol is the non-overlap time, approximately 50ns. The last term in this expression represents the loss due to the body diode that is active during the non-overlap time.

In addition to the above requirements, it is desirable for the bottom MOSFET to have lower gate-drain capacitance as it minimizes coupling to BGATE when the SW pin rises. This coupling may momentarily turn on the bottom side MOSFET creating shoot-through that, at best, reduces efficiency and at worst can destroy the MOSFET.

While it is possible to get high and low side MOSFETs bonded in a common package, excessive power dissipation may require two separate packages or even that multiple high or low side MOSFETS be used at the high-power levels. Using multiple packages spreads the heat over a larger PCB area improving overall board temperature and efficiency.

At lower  $V_{IN}$ , the top side MOSFET is on longer and low  $R_{DS(ON)}$  helps lower dissipation but at higher input voltage the transient losses increase and can dominate. For the bottom side MOSFET the opposite is true. Optimization for best efficiency suggests different top and bottom MOSFETs.

A good approach to MOSFET sizing is to select the high side MOSFET first, then the low side MOSFET. The trade-off between  $R_{DS(ON)}$ ,  $Q_G$ , and  $Q_{GS}$  for the high side MOSFET is evident in the following example of charging a 6 cell lead-acid battery from a 30V source at 20A.  $V_{BAT}$  is equal to 14V,  $f_{SW} = 200 \text{kHz}$ .

For the top side MOSFET the BSC018N04LS is a suitable 40V N-channel MOSFETs with an  $R_{DS(ON)}$  of  $2.0m\Omega$  at 4.5V,  $Q_G=60nC$ ,  $Q_{GS}=25nC$ ,  $Q_{GD}=10nC$ ,  $RG=1.3\Omega$ . The bottom side MOSFET is a BSC093N04LS with an  $R_{DS(ON)}$  of 11.0m $\Omega$  at 4.5V,  $Q_G=8.6nC$ ,  $Q_{GS}=4.9nC$ ,  $Q_{GD}=2nC$ ,  $RG=1.0\Omega$ . Power loss for the MOSFETs is shown in Figures 8 and 9. Observe that the total power loss at 30V is just over 5W for the top switch and about 4W for the bottom switch.

Figure 7. Bottom MOSFET Power Loss Example

Figure 8. Top MOSFET Power Loss Example

$R_{DS(ON)}$  and  $Q_G$  are inversely related so selecting a top side MOSFET with higher  $R_{DS(ON)}$  and lower  $Q_G$  might lower top side losses. Conversely the bottom side MOSFET is dominated by ohmic losses so a larger MOSFET may be better if total  $Q_{GD}$  is kept to a minimum.

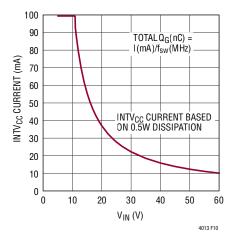

Supplying gate charge current has its own loss and represents a potential limitation at higher voltages, most of which is dissipated from the internal LDO. The power dissipated in the IC is:  $P_{LDO}=(V_{IN}-5)\bullet(Q_{GL}+Q_{GH})\bullet f_{SW}$  where  $Q_{GL}$  is the low side gate charge and  $Q_{GH}$  is the high side gate charge. Figure 9 shows the curve of maximum gate charge current vs input voltage for a power loss of 0.5W. This power level would add 22°C of temperature rise to the die at 43°C/W thermal resistance. Dividing the Y axis value by  $f_{SW}$  gives the maximum  $Q_{G}$  that can be charged (the sum of top and bottom gates). For instance, at 30V and 500kHz  $Q_{G}$  is under 20mA/0.5MHz = 40nC.

Figure 9. Maximum INTV<sub>CC</sub> current

If desired operation places the internal 5V regulator out of the allowable region, gate drive power must be supplied externally. This could be done by carefully driving the  $INTV_{CC}$  pin with tight regulation to 5.5V (do not exceed the 6V absmax) or by supplying 5V power for the BST drive (top gate  $Q_G$ ) via the anode of the BST drive diode. Table 5 lists power MOSFET manufacturers that make devices appropriate for LTC4013.

**Table 5. Suggested MOSFET Suppliers**

| Manufacturer | Web Site              |

|--------------|-----------------------|

| Infineon     | www.infineon.com      |

| Renesas      | www.renesas.com       |

| Fairchild    | www.fairchildsemi.com |

| Vishay       | www.vishay.com        |

| NXP/Philips  | www.nxp.com           |

#### **DCIN Capacitance Selection**

High quality capacitance is required on DCIN as DCIN provides power to the INFET charge pump and is also used for input voltage sensing. Since most of the switching regulator transients are handled by the  $V_{IN}$  capacitor, a smaller capacitor on DCIN is adequate. In fact, DCIN capacitance should be kept low to ensure that the DCIN pin achieves the panel open circuit voltage during the MPPT VOC measurement delay of about 720 $\mu$ s. A maximum 4.7 $\mu$ F high quality ceramic capacitor is recommended.

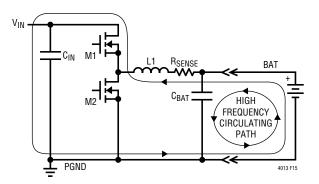

## **Input Supply Capacitor Selection**

The switching power stage draws high current with fast switching edges, so high quality, low ESR, low ESL decoupling capacitors are required to minimize voltage glitches on the  $V_{IN}$  supply. The capacitor(s) must have an adequate ripple current rating. RMS ripple current  $I_{VIN(RMS)}$  follows the relation:

$$I_{VIN(RMS)} \approx I_{CHGMAX} \bullet DC \bullet \sqrt{\frac{1}{DC} - 1}$$

where  $I_{\mbox{\footnotesize{CHGMAX}}}$  is the maximum charge current set by  $R_{\mbox{\footnotesize{SFNSE}}}.$

$$I_{VIN(RMS)} \approx \frac{I_{CHGMAX}}{2}$$

The required input capacitance  $C_{IN}$  is determined by the desired input ripple voltage ( $\Delta V_{IN}$ ):

$$C_{IN} \ge \frac{I_{CHGMAX}}{\Delta V_{IN} \bullet f_{SW}} \bullet \frac{V_{BAT(MAX)}}{V_{IN(MIN)}}$$

where  $f_{SW}$  is the operating frequency,  $V_{BAT(MAX)}$  is the DC/DC converter maximum output voltage and  $V_{IN(MIN)}$

Rev B

is the minimum input operating voltage. Keeping  $\Delta V_{IN}$  below 100mV is a good starting point. As an example, let  $I_{CHGMAX} = 10A$ ,  $\Delta V_{IN} = 0.1V$ ,  $f_{SW} = 500k$ ,  $V_{BAT(MAX)} = 15V$ ,  $V_{IN(MIN)} = 18V$  then  $C_{IN}$  is greater than  $167\mu F$ .

Meeting these requirements at higher voltages may require multiple capacitors and possibly a mixture of capacitor types. Because of the fast switching edges it is important that the total decoupling capacitance have low ESR and ESL to avoid sharp voltage spikes. The best practice is to use several low-ESR ceramic capacitors as part of the capacitance, with higher density capacitors utilized for bulk requirements. X7R capacitors tend to maintain their capacitance over a wide range of operating voltages and temperatures. Minimize the loop created by the input capacitor, the high side MOSFET and the low side MOSFET to reduce radiation components. See Linear Technology application notes AN139 and AN144 for more information on EMI.

#### **Battery Capacitor Selection**

The output of the charger is the battery which represents a large effective capacitance. Because the battery often has significant wiring connecting it to the charger, additional decoupling output capacitors at the charger are needed. The BAT node is also used for voltage sensing so better performance is obtained with lower voltage ripple at the BAT and FB pins. The BAT capacitor needs to have low ESR to reduce output ripple. To achieve the lowest possible ESR, use several low-ESR ceramic capacitors in parallel. Lower output voltage applications may benefit from the use of high density POSCAP capacitors which are easily destroyed when exposed to over-voltage conditions. To prevent this, select POSCAP capacitors that have a voltage rating that is at least 20% higher than the regulated voltage.

The ripple current on these capacitors is the same as the inductor ripple. Since, in general, inductor selection is chosen to have ripple current equal to or below 30% of I<sub>CHGMAX</sub>, an adequate ripple current rating for the BAT capacitor(s) is 0.4 • I<sub>CHGMAX</sub>. The capacitors also need to be surge rated to the maximum output current.

Sizing for output ripple voltage is similar to input decoupling:

$$C_{BAT} \ge \frac{0.4 \cdot I_{CHGMAX}}{\Delta V_{BAT} \cdot f_{SW}}$$

For example, if  $I_{CHGMAX}$  = 10A,  $\Delta V_{BAT}$  = 0.1V,  $f_{SW}$  = 500k then choose  $C_{BAT}$  greater than  $80\mu F$ .

#### INTV<sub>CC</sub> LDO Output, and BST Supply

INTV $_{CC}$  provides power to the LTC4103 but also provides charge to the gate drives. The boosted supply pin allows the use of an N-channel top MOSFET switch for increased conversion efficiency and lower cost. The BST capacitor is connected from SW to BST with a low leakage 1A Schottky diode connected from INTV $_{CC}$  to BST. The diode must be rated for a reverse voltage greater than the input supply voltage maximum.

C<sub>BST</sub> is sized to hold the BST rail reasonably constant when delivering gate charge to the MOSFET. A good rule of thumb is:

$$C_{BST} > 50 \bullet \frac{Q_{GH}}{V_{GS}} = 10 \bullet Q_{GH}$$

where  $Q_{GH}$  is the top side MOSFET  $Q_{G}$  at 5V.

For example, if the top gate charge is 20nC charged to INTV<sub>CC</sub> at 5V, then keep the  $C_{BST}$  capacitance larger than 0.2 $\mu$ F.

Since BST capacitor charge current is drawn from the INTV<sub>CC</sub> capacitor,  $C_{BST}$  needs to be sized to have minimal drop during recharge. A good starting point for high-current MOSFETs with high gate charge is to set  $C_{INTVCC}$  larger than 4.7 $\mu$ F. Connect it as close as possible to the exposed pad underneath the package. Because of the fast high-current edges, use a low-ESR ceramic capacitor with ESR typically lower than 20m $\Omega$ . For driving MOSFETs with gate charge larger than 44nC, size INTV<sub>CC</sub> with 0.5 $\mu$ F/nC of total gate charge (top plus bottom MOSFETs).

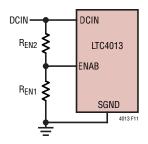

#### Enable (ENAB) Pin

The LTC4013 has an ENAB pin that allows it to be enabled when the input voltage reaches a particular threshold using a resistor divider from DCIN to ENAB (see Figure 10). The turn-on threshold at ENAB is approximately 1.22V (rising), with 170mV of hysteresis. In shutdown, all charging functions are disabled and input supply current is reduced to around  $40\mu A$ .

Typical ENAB pin input bias current is 10nA which needs to be accounted for when using high value resistors. Choose REN1 and then:

$$R_{EN2} = R_{EN1} \bullet \left( \frac{V_{ENAB}}{1.22} - 1 \right)$$

Figure 10. ENAB Resistor Divider

#### **Frequency Compensation**

The LTC4013 uses average current mode control for precise regulation of the charge current. Figure 11 shows an overview of the control loop. The current is measured via the sense amplifier and compared against the target value. The error amplifier, in conjunction with compensation components  $R_{\text{C}}$  and  $C_{\text{C}}$ , sets the duty cycle that controls the inductor current.

Use the following equations to compute the compensation component sizing:

$$R_{C} = \frac{350 V \Omega \bullet f_{SW} \bullet L}{R_{SENSE} \bullet V_{IN}}$$

$$C_{C} \ge \frac{10}{2\pi \bullet \frac{f_{SW}}{10} \bullet R_{C}} = \frac{R_{SENSE} \bullet V_{IN}}{22 V \Omega \bullet f_{SW}^{2} \bullet L}$$

where  $f_{SW}$  is the switching frequency, L is the inductance value,  $V_{IN}$  is the input voltage and  $R_{SENSE}$  is the sense resistor.

Figure 11. Switching Regulator Control Loop

In some circumstances, an additional roll-off capacitor,  $C_{C2}$ , from ITH to ground is helpful. Make  $C_{C2} = C_C / 100$ .

A separate voltage amplifier modulates the maximum current as the battery voltage approaches the charge voltage level. Since the charge voltage regulation loop monitors battery voltage, it is generally controlled by a very slow-moving node. However, the battery ESR, combined with the output capacitance, produces an in-band pole potentially resulting in unstable operation. The voltage regulation loop is compensated by adding a capacitor to the FB input, producing a dominant, low-frequency, pole as shown in Figure 12. The pole frequency, set by the parallel combination of the feedback resistors and the capacitor, is typically set to ~1/1000 of the switching frequency.

$$C_{FB} \ge \frac{200\Omega}{R_{FB2}} \bullet C_{BAT}$$

BAT

LTC4013

BAT

RFB2

RFB1

Figure 12. FB Voltage Filtering

4013 F13

Rev B

#### Maximum Power Point Tracking (MPPT)

MPPT is used to regulate the input voltage to maximize power transfer from a power limited source. The first step is to determine the maximum power voltage. For a solar panel, this can be determined from the data sheet. A resistor divider between the input source and the FBOC and MPPT pins is used to program the LTC4013 to regulate the input source at its maximum power voltage. The FBOC pin is used to sample the input source open circuit voltage when charging is paused while the MPPT pin is used to regulate the maximum power voltage when the charger is running. The MPPT resistor divider should be configured as shown in Figure 13.

Figure 13. Resistor Divider for MPPT

Choose the attenuation ratio of FBOC to DCIN ( $K_F$ ) so  $V_{FBOC}$  is between 1.0V and 3.0V when the input voltage is at its highest (i.e. open circuit,  $V_{DCIN}(OC)$ ). The attenuation ratio of MPPT to DCIN is set so that VMPPT equals the chosen  $V_{FBOC}$  when DCIN is at the maximum power voltage,  $V_{DCIN}(MP)$ . The following equations define those conditions: