## High Voltage Buck-Boost Battery Charge Controller with Maximum Power Point Tracking (MPPT) and I<sup>2</sup>C

#### **FEATURES**

V<sub>IN</sub> Range: 6V to 80VV<sub>BAT</sub> Range: 1.3V to 80V

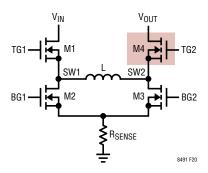

- Single Inductor Allows V<sub>IN</sub> Above, Below, or Equal to V<sub>BAT</sub>

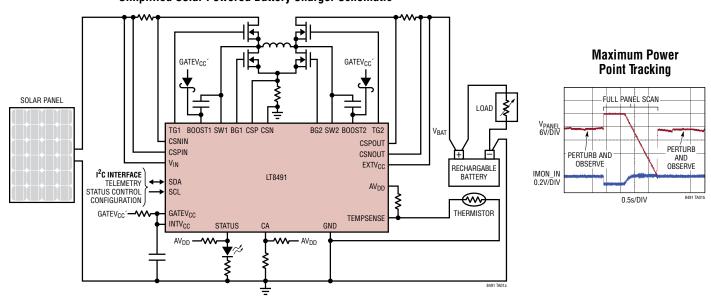

- Automatic MPPT for Solar Powered Charging

- Automatic Temperature Compensation

- I<sup>2</sup>C Telemetry and Configuration

- Internal EEPROM for Configuration Storage

- Operation from Solar Panel or DC Supply

- Four Integrated Feedback Loops

- Synchronizable Fixed Frequency: 100kHz to 400kHz

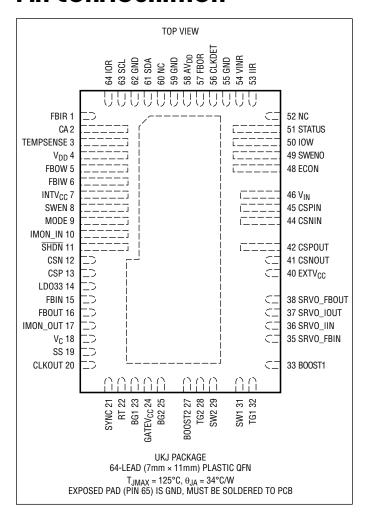

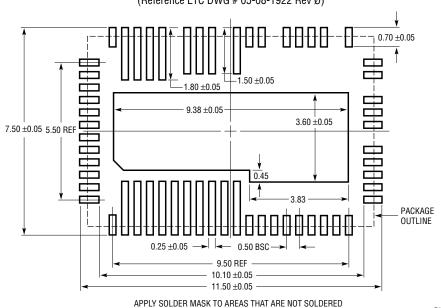

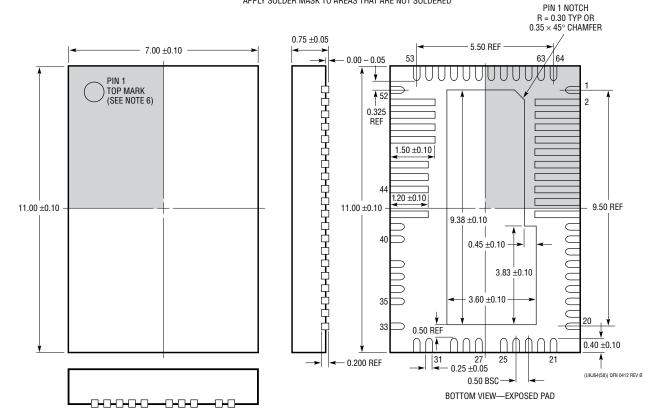

- 64-Lead (7mm × 11mm × 0.75mm) QFN Package

#### **APPLICATIONS**

- Solar Powered Battery Chargers

- Multiple Types of Lead-Acid Battery Charging

- Li-Ion Battery Charger

- Battery Equipped Industrial or Portable Military Equipment

#### DESCRIPTION

The LT®8491 is a buck-boost switching regulator battery charger that implements a constant-current constant-voltage (CCCV) charging profile used for most battery types, including sealed lead-acid (SLA), flooded, gel and lithium-ion.

The device operates from input voltages above, below or equal to the output voltage and can be powered by a solar panel or a DC power supply. On-chip logic provides automatic maximum power point tracking (MPPT) for solar powered applications. The LT8491 can perform automatic temperature compensation by sensing an external thermistor thermally coupled to the battery. The STATUS pin can be used to drive an LED indicator lamp. The device is available in a low profile (0.75mm) 7mm × 11mm 64-lead QFN package.

All registered trademarks and trademarks are the property of their respective owners.

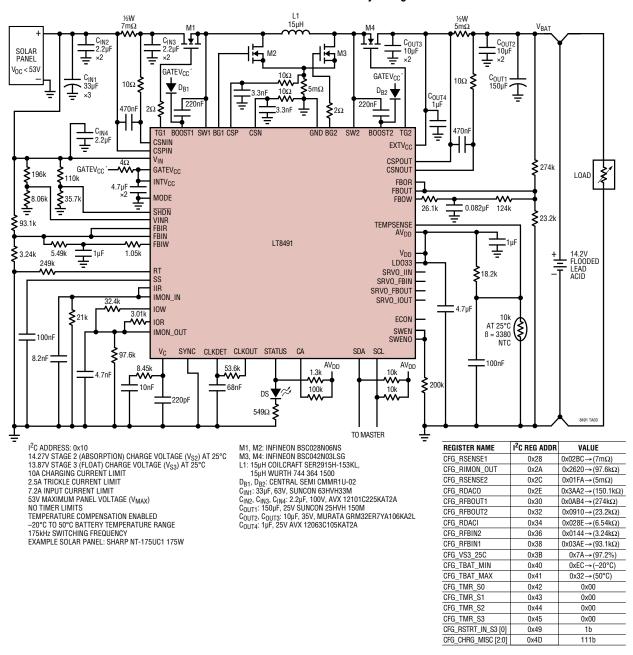

#### TYPICAL APPLICATION

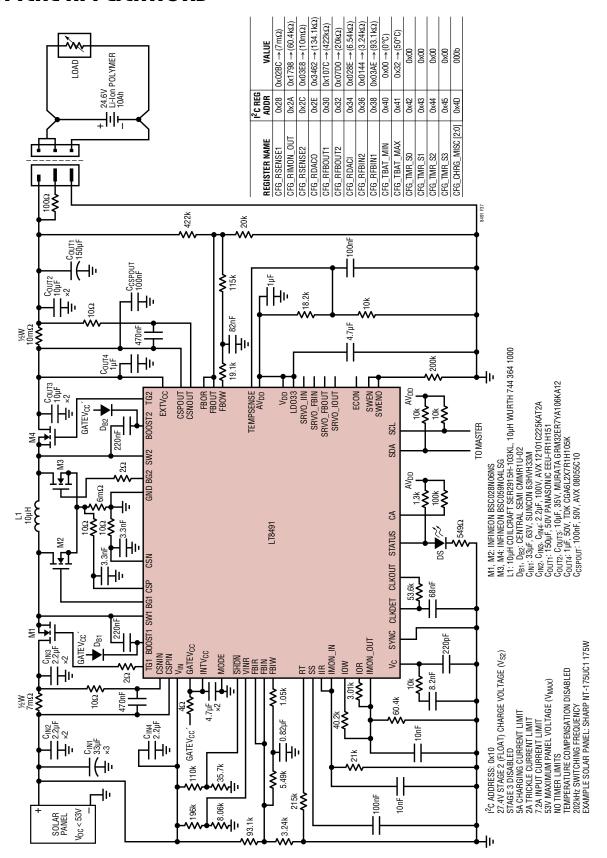

#### Simplified Solar Powered Battery Charger Schematic

## LT8491

## TABLE OF CONTENTS

| Features 1                                      | I <sup>2</sup> C Regist |

|-------------------------------------------------|-------------------------|

| Applications 1                                  | I <sup>2</sup> C Regist |

| Typical Application 1                           | Telemet                 |

| Description 1                                   | TELE                    |

| Absolute Maximum Ratings 4                      | TELE                    |

| Order Information 4                             | TELE                    |

| Pin Configuration 4                             | TELE                    |

| Electrical Characteristics                      | TELE                    |

| Typical Performance Characteristics 8           | TELE                    |

| Pin Functions                                   | TELE                    |

| Block Diagram13                                 | TELE                    |

| Operation14                                     | TELE                    |

| Overview                                        | Status F                |

| I <sup>2</sup> C Serial Interface               | STAT_                   |

| I <sup>2</sup> C: START and STOP Conditions14   | STAT                    |

| I <sup>2</sup> C: ACKnowledge14                 | STAT_                   |

| I <sup>2</sup> C: Chip Addressing15             | STAT_                   |

| I <sup>2</sup> C: Clock Stretching15            | STAT_                   |

| I <sup>2</sup> C: Data Transfer Transactions    | STAT_                   |

| I <sup>2</sup> C: Powering the Interface        | STAT_                   |

| I <sup>2</sup> C Data                           | STAT_                   |

| Data: Memory Regions16                          | Control                 |

| Data: Bytes, Words and Long Words17             | CTRL.                   |

| Data: Min/Max Register Values17                 | CTRL.                   |

| Data: Access Permissions                        | Control                 |

| Startup Sequence                                | CTRL <sub>.</sub>       |

| Battery Charging Algorithm20                    | CTRL <sub>.</sub>       |

| Stage 0: Trickle Charging20                     | CTRL <sub>.</sub>       |

| Stage 1: Full Constant Current                  | CTRL <sub>.</sub>       |

| Stage 2: Constant Voltage                       | CTRL <sub>.</sub>       |

| Stage 3: (Optional) Reduced Constant Voltage 21 | Configu                 |

| Done Charging21                                 | CFG_I                   |

| Charging Faults21                               | CFG_I                   |

| Maximum Power Point Tracking23                  | CFG_I                   |

| Telemetry Operation23                           | CFG_I                   |

| Telemetry: Configuration Settings24             | CFG_I                   |

| Telemetry: Acquisition24                        | CFG_I                   |

| CRC Operation24                                 | CFG_I                   |

| EEPROM Operation25                              | CFG_I                   |

| EEPROM: Startup25                               | CFG_I                   |

| EEPROM: Reading25                               | Configu                 |

| EEPROM: Writing25                               | CFG_I                   |

| C Register Map                       |    |

|--------------------------------------|----|

| <sup>2</sup> C Register Descriptions |    |

| Telemetry Registers                  |    |

| TELE_TBAT                            |    |

| TELE_POUT                            |    |

| TELE_PIN                             |    |

| TELE_EFF                             |    |

| TELE_IOUT                            |    |

| TELE_IIN                             |    |

| TELE_VBAT                            |    |

| TELE_VIN                             |    |

| TELE_VINR                            |    |

| Status Registers                     | 34 |

| STAT_CHARGER                         | 34 |

| STAT_SYSTEM                          |    |

| STAT_SUPPLY                          |    |

| STAT_TSx_REMAIN                      | 36 |

| STAT_CHRG_FAULTS                     | 37 |

| STAT_VERSION                         | 38 |

| STAT_BOOT_CRC                        |    |

| STAT_CFG_CRC                         | 38 |

| Control The EEPROM                   | 39 |

| CTRL_WRT_TO_B00T                     |    |

| CTRL_EE_WRT_EN                       |    |

| Control Other Functions              |    |

| CTRL_HALT_STARTUP                    | 40 |

| CTRL_CHRG_EN                         | 40 |

| CTRL_RESTART_CHIP                    |    |

| CTRL_RESET_FLAG                      | 41 |

| CTRL_UPDATE_TELEM                    |    |

| Configure The Telemetry              |    |

| CFG_RSENSE1                          |    |

| CFG_RIMON_OUT                        |    |

| CFG_RSENSE2                          |    |

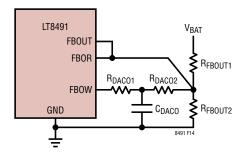

| CFG_RDACO                            |    |

| CFG_RFBOUT1                          |    |

| CFG_RFBOUT2                          |    |

| CFG_RDACI                            |    |

| CFG_RFBIN2                           |    |

| CFG_RFBIN1                           |    |

| Configure Initial Charger Enable     |    |

| CFG_INIT_CHRG_EN                     | 45 |

| Configure V <sub>BAT</sub> for Stages 0, 1 and 3 | 46        |

|--------------------------------------------------|-----------|

| CFG VS3 25C                                      | 46        |

| CFG UV SO                                        |           |

| CFG SO UV                                        |           |

| CFG_S0_S1                                        |           |

| CFG_S1_S0                                        |           |

| Configure Temperature Fault Limits               |           |

| CFG_TBAT_MIN                                     | 50<br>50  |

| CFG_TBAT_MAX                                     | 50        |

| Configure Stage Timeout Limits                   |           |

| CFG_TMR_S0                                       |           |

| CFG_TMR_S1                                       |           |

| CFG_TMR_S2                                       |           |

| OFG_TMD_02                                       | .)।<br>51 |

| Configure Automatic Postart                      | .) <br>[] |

| Configure Automatic Restart                      |           |

| CFG_RSTRT_IN_FLT                                 |           |

| CFG_RSTRT_IN_DONEA                               |           |

| CFG_RSTRT_IN_DONEB                               |           |

| CFG_RSTRT_IN_S3                                  | 55        |

| Configure Charge Termination                     |           |

| CFG_TERMINATE                                    |           |

| Configure Misc.                                  | 56        |

| CFG_SCAN_RATE_LP                                 |           |

| CFG_SCAN_RATE                                    |           |

| CFG_CHRG_MISC                                    |           |

| Configure Temperature Compensation               |           |

| CFG_TC3, CFG_TC2, CFG_TC1                        |           |

| Configure User Code                              |           |

| CFG_USER_CODE                                    |           |

| Manufacturer Data                                |           |

| MFR_DATA1                                        |           |

| MFR_DATA2                                        |           |

| MFR_DATA3                                        | 60        |

| Applications information                                  |     |

|-----------------------------------------------------------|-----|

| Hardware Configuration                                    |     |

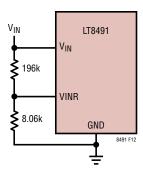

| HW Config: Input Voltage Sensing and Modulation           |     |

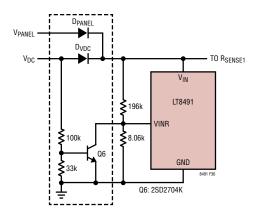

| HW Config: VINR Pin Connections                           |     |

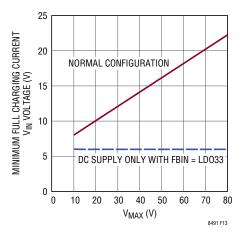

| HW Config: Solar Panel Powered Charging                   | 62  |

| HW Config: DC Supply Powered Charging                     | 63  |

| HW Config: V <sub>BAT</sub> in Stage 2 (V <sub>S2</sub> ) | 63  |

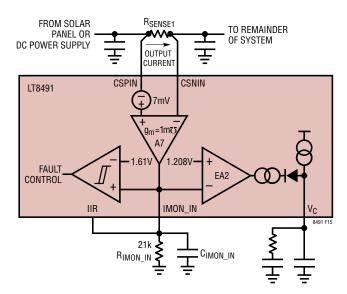

| HW Config: Input Current Sense and Limit                  |     |

| HW Config: Output Current Sense and Limit                 |     |

| HW Config: Current Sense Filtering                        | 66  |

| HW Config: Battery Temperature and Disconnect             |     |

| Sensing                                                   | 67  |

| HW Config: SHDN Pin Connections                           | 67  |

| HW Config: MODE Pin – Current Conduction Mode.            |     |

| HW Config: Driving an LED with the STATUS Pin             |     |

| HW Config: I <sup>2</sup> C Chip Address Pin              | 69  |

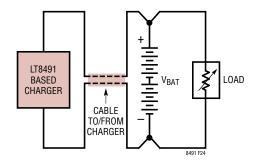

| In-Situ Battery Charging                                  | 69  |

| Hot-Plugging Considerations                               |     |

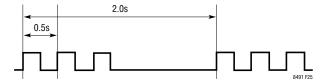

| STATUS Indicator Pin                                      |     |

| Lithium-Ion Battery Charging                              |     |

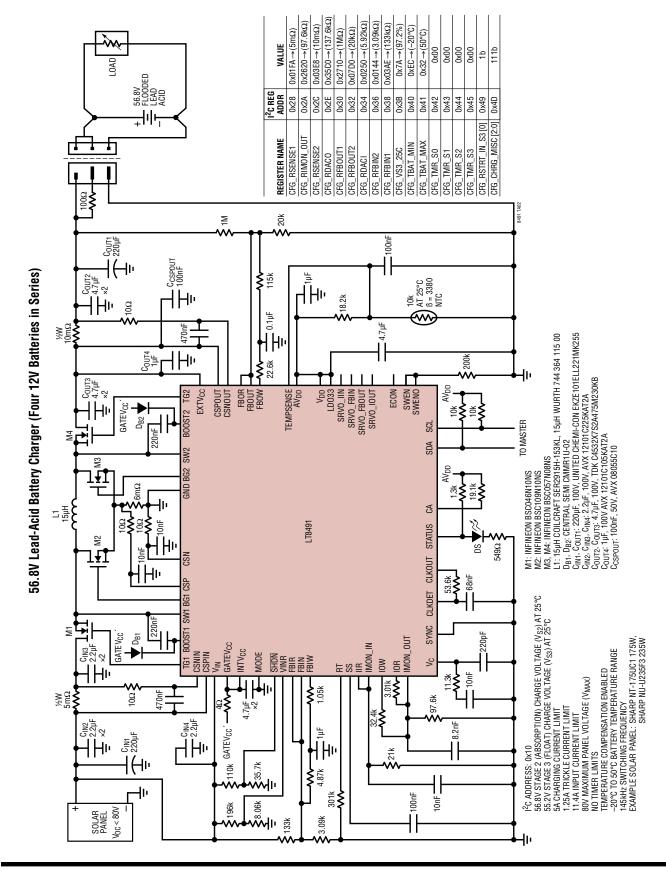

| Lead-Acid Battery Charging                                |     |

| Optional Features                                         | .72 |

| Optional: Low Power Mode                                  | 72  |

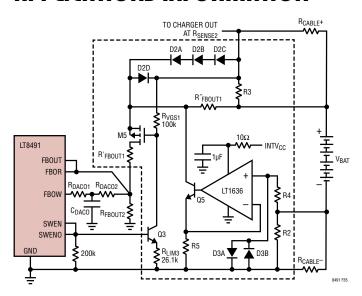

| Optional: Output Feedback Resistor Disconnect             |     |

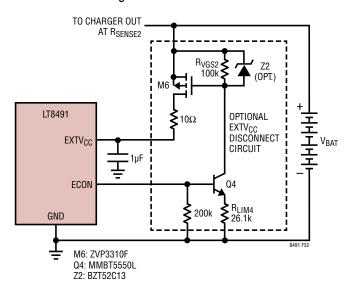

| Optional: EXTV <sub>CC</sub> Disconnect                   | 73  |

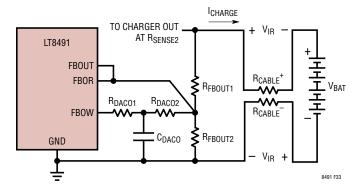

| Optional: Remote Battery Voltage Sensing                  |     |

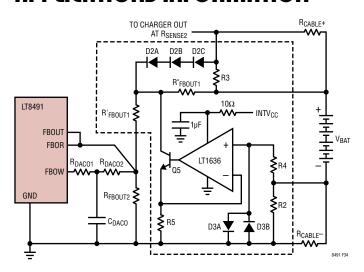

| Optional: DC Supply Detection Circuit                     |     |

| Board Layout Considerations                               |     |

| Design Example                                            |     |

| Typical Applications                                      |     |

| Package Description                                       |     |

| Typical Application                                       |     |

| Polated Parts                                             |     |

#### **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| $V_{CSP} - V_{CSN}$ , $V_{CSPIN} - V_{CSNIN}$ ,                                               |

|-----------------------------------------------------------------------------------------------|

| V <sub>CSPOUT</sub> - V <sub>CSNOUT</sub> 0.3V to 0.3V                                        |

| V <sub>CSPOUT</sub> - V <sub>CSNOUT</sub> 0.3V to 0.3V SS, CLKOUT, CSP, CSN Voltage0.3V to 3V |

| V <sub>C</sub> Voltage (Note 2)0.3V to 2.2V                                                   |

| LDO33, V <sub>DD</sub> , AV <sub>DD</sub> , Voltage0.3V to 5V                                 |

| RT, FBOUT Voltage0.3V to 5V                                                                   |

| IMON_IN, IMON_OUT Voltage0.3V to 5V                                                           |

| SYNC Voltage0.3V to 5.5V                                                                      |

| INTV <sub>CC</sub> , GATEV <sub>CC</sub> Voltage0.3V to 7V                                    |

| $V_{B00ST1} - V_{SW1}$ , $V_{B00ST2} - V_{SW2}$ 0.3V to 7V                                    |

| SWEN, MODE Voltage0.3V to 7V                                                                  |

| SRVO_FBIN, SRVO_FBOUT Voltage0.3V to 30V                                                      |

| SRVO_IIN, SRVO_IOUT Voltage0.3V to 30V                                                        |

| FBIN, SHDN Voltage0.3V to 30V                                                                 |

| CSNIN, CSPIN, CSPOUT,                                                                         |

| CONOLITY II                                                                                   |

| CSNOUT Voltage –0.3V to 80V                                                                   |

|                                                                                               |

| $V_{\text{IN}},\text{EXTV}_{\text{CC}}$<br>Voltage0.3V to 80V                                 |

|                                                                                               |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                          |

| V <sub>IN</sub> , EXTV <sub>CC</sub> Voltage0.3V to 80V SW1, SW2 Voltage81V (Note 5)          |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                          |

#### PIN CONFIGURATION

#### ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL    | PART MARKING* | PACKAGE DESCRIPTION              | TEMPERATURE RANGE |  |  |

|------------------|------------------|---------------|----------------------------------|-------------------|--|--|

| LT8491EUKJ#PBF   | LT8491EUKJ#TRPBF | LT8491UKJ     | 64-Lead (7mm × 11mm) Plastic QFN | -40°C to 125°C    |  |  |

| LT8491IUKJ#PBF   | LT8491IUKJ#TRPBF | LT8491UKJ     | 64-Lead (7mm × 11mm) Plastic QFN | -40°C to 125°C    |  |  |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25\,^{\circ}$ C. $V_{IN} = 12V$ , $V_{DD} = AV_{DD} = 3.3V$ , SHDN = 3V unless otherwise noted. (Note 3)

| PARAMETER                                        | MIN                                                                                                                                                                                                                                                                                                                             | TYP | MAX                        | UNITS              |                            |                      |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------|--------------------|----------------------------|----------------------|

| Voltage Supply and Regulators                    | ·                                                                                                                                                                                                                                                                                                                               |     |                            |                    |                            |                      |

| V <sub>IN</sub> Operating Voltage Range (Note 7) |                                                                                                                                                                                                                                                                                                                                 | •   | 6                          |                    | 80                         | V                    |

| V <sub>IN</sub> Quiescent Current                | Not Switching, V <sub>EXTVCC</sub> = 0, V <sub>DD</sub> = AV <sub>DD</sub> = Float                                                                                                                                                                                                                                              |     |                            | 2.65               | 4.2                        | mA                   |

| V <sub>IN</sub> Quiescent Current in Shutdown    | V <sub>SHDN</sub> = 0V                                                                                                                                                                                                                                                                                                          |     |                            | 0                  | 1                          | μA                   |

| V <sub>DD</sub> Quiescent Current                | $I_{AVDD} + I_{VDD}$ , $V_{DD} = AV_{DD} = 3.3V$                                                                                                                                                                                                                                                                                | •   | 2.5                        | 4                  | 6.5                        | mA                   |

| EXTV <sub>CC</sub> Switchover Voltage            | I <sub>INTVCC</sub> = 20mA, V <sub>EXTVCC</sub> Rising                                                                                                                                                                                                                                                                          | •   | 6.15                       | 6.4                | 6.6                        | V                    |

| EXTV <sub>CC</sub> Switchover Hysteresis         |                                                                                                                                                                                                                                                                                                                                 |     |                            | 0.18               |                            | V                    |

| LD033 Pin Voltage                                | 5mA from LD033 Pin                                                                                                                                                                                                                                                                                                              | •   | 3.23                       | 3.295              | 3.35                       | V                    |

| LD033 Pin Load Regulation                        | I <sub>LD033</sub> = 0.1mA to 5mA                                                                                                                                                                                                                                                                                               |     |                            | -0.25              | -1                         | %                    |

| LD033 Pin Current Limit                          |                                                                                                                                                                                                                                                                                                                                 | •   | 12                         | 17.25              | 22                         | mA                   |

| LD033 Pin Undervoltage Lockout                   | LD033 Falling                                                                                                                                                                                                                                                                                                                   |     | 2.96                       | 3.04               | 3.12                       | V                    |

| LD033 Pin Undervoltage Lockout Hysteresis        |                                                                                                                                                                                                                                                                                                                                 |     |                            | 35                 |                            | mV                   |

| Switching Regulator Control                      |                                                                                                                                                                                                                                                                                                                                 | •   |                            |                    |                            |                      |

| SHDN Input Voltage High                          | SHDN Rising to Enable the Device                                                                                                                                                                                                                                                                                                | •   | 1.184                      | 1.234              | 1.284                      | V                    |

| SHDN Input Voltage High Hysteresis               |                                                                                                                                                                                                                                                                                                                                 |     |                            | 50                 |                            | mV                   |

| SHDN Input Voltage Low                           | Device Disabled, Low Quiescent Current                                                                                                                                                                                                                                                                                          | •   |                            |                    | 0.35                       | V                    |

| SHDN Pin Bias Current                            | V <sub>SHDN</sub> = 3V<br>V <sub>SHDN</sub> = 12V                                                                                                                                                                                                                                                                               |     |                            | 0<br>11            | 1<br>22                    | μA<br>μA             |

| SWEN Rising Threshold Voltage                    |                                                                                                                                                                                                                                                                                                                                 | •   | 1.156                      | 1.206              | 1.256                      | V                    |

| SWEN Threshold Voltage Hysteresis                |                                                                                                                                                                                                                                                                                                                                 |     |                            | 22                 |                            | mV                   |

| MODE Pin Thresholds                              | Discontinuous Mode<br>Automatic DCM/CCM Mode                                                                                                                                                                                                                                                                                    | •   | 0.4                        |                    | 2.3                        | V                    |

| IMON_OUT Rising threshold for CCM Operation      | MODE = 0V                                                                                                                                                                                                                                                                                                                       |     | 168                        | 195                | 224                        | mV                   |

| IMON_OUT Falling threshold for DCM               | MODE = 0V                                                                                                                                                                                                                                                                                                                       |     | 95                         | 122                | 150                        | mV                   |

| Voltage Regulation                               |                                                                                                                                                                                                                                                                                                                                 | •   |                            |                    |                            |                      |

| Regulation Voltage for FBOUT                     | $V_C = 1.2V$ , $EXTV_{CC} = 0$                                                                                                                                                                                                                                                                                                  | •   | 1.193                      | 1.207              | 1.222                      | V                    |

| Regulation Voltage for FBIN                      | $V_C = 1.2V$ , $EXTV_{CC} = 0$                                                                                                                                                                                                                                                                                                  | •   | 1.184                      | 1.205              | 1.226                      | V                    |

| FBOUT Pin Bias Current                           | Current Out of Pin                                                                                                                                                                                                                                                                                                              |     |                            | 15                 |                            | nA                   |

| FBIN Pin Bias Current                            | Current Out of Pin                                                                                                                                                                                                                                                                                                              |     |                            | 10                 |                            | nA                   |

| Current Regulation                               |                                                                                                                                                                                                                                                                                                                                 | •   |                            |                    |                            |                      |

| Regulation Voltage for IMON_IN and IMON_OUT      | $VC = 1.2V$ , $EXTV_{CC} = 0$                                                                                                                                                                                                                                                                                                   | •   | 1.187                      | 1.208              | 1.229                      | V                    |

| IMON_IN Output Current                           | $V_{CSPIN} - V_{CSNIN} = 50$ mV, $V_{CSPIN} = 5.025$ V<br>$V_{CSPIN} - V_{CSNIN} = 50$ mV, $V_{CSPIN} = 5.025$ V<br>$V_{CSPIN} - V_{CSNIN} = 0$ mV, $V_{CSPIN} = 5$ V                                                                                                                                                           | •   | 54<br>53<br>2.5            | 57<br>57<br>7      | 60<br>61<br>11.5           | μΑ<br>μΑ<br>μΑ       |

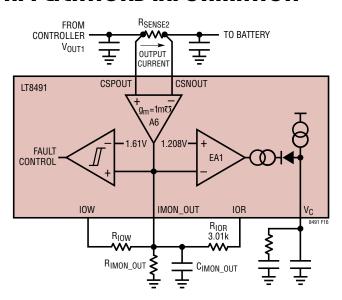

| IMON_IN Overvoltage Threshold                    |                                                                                                                                                                                                                                                                                                                                 | •   | 1.55                       | 1.61               | 1.67                       | V                    |

| IMON_OUT Output Current                          | $\begin{array}{c} V_{CSPOUT} - V_{CSNOUT} = 50 \text{mV}, \ V_{CSPOUT} = 5.025 \text{V} \\ V_{CSPOUT} - V_{CSNOUT} = 50 \text{mV}, \ V_{CSPOUT} = 5.025 \text{V} \\ V_{CSPOUT} - V_{CSNOUT} = 5 \text{mV}, \ V_{CSPOUT} = 5.0025 \text{V} \\ V_{CSPOUT} - V_{CSNOUT} = 5 \text{mV}, \ V_{CSPOUT} = 5.0025 \text{V} \end{array}$ | •   | 47.5<br>47<br>3.25<br>2.75 | 50<br>50<br>5<br>5 | 52.5<br>54.25<br>6.75<br>8 | μΑ<br>μΑ<br>Αμ<br>Αμ |

| IMON_OUT Overvoltage Threshold                   |                                                                                                                                                                                                                                                                                                                                 | •   | 1.55                       | 1.61               | 1.67                       | V                    |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25\,^{\circ}$ C. $V_{IN} = 12V$ , $V_{DD} = AV_{DD} = 3.3V$ , $\overline{SHDN} = 3V$ unless otherwise noted. (Note 3)

| PARAMETER                                                                       |                                                                                                    | MIN | TYP               | MAX                | UNITS             |                   |

|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----|-------------------|--------------------|-------------------|-------------------|

| Switching Regulator Oscillator (OSC1)                                           |                                                                                                    |     |                   |                    |                   |                   |

| Switch Frequency Range                                                          | Syncing or Free Running                                                                            |     | 100               |                    | 400               | kHz               |

| Switching Frequency, f <sub>OSC</sub>                                           | $\begin{aligned} R_T &= 365 k \Omega \\ R_T &= 215 k \Omega \\ R_T &= 124 k \Omega \end{aligned}$  | •   | 102<br>170<br>310 | 120<br>202<br>350  | 142<br>235<br>400 | kHz<br>kHz<br>kHz |

| SYNC High Level for Synchronization                                             |                                                                                                    | •   | 1.3               |                    |                   | V                 |

| SYNC Low Level for Synchronization                                              |                                                                                                    | •   |                   |                    | 0.5               | V                 |

| SYNC Clock Pulse Duty Cycle                                                     | V <sub>SYNC</sub> = 0V to 2V                                                                       |     | 20                |                    | 80                | %                 |

| Recommended Min SYNC Ratio, f <sub>SYNC</sub> /f <sub>OSC</sub>                 |                                                                                                    |     |                   | 3/4                |                   | f/f               |

| CLKOUT Output Voltage HIGH                                                      | 1mA Out of CLKOUT Pin                                                                              |     | 2.3               | 2.45               | 2.55              | V                 |

| CLKOUT Output Voltage LOW                                                       | 1mA into CKLKOUT Pin                                                                               |     |                   | 25                 | 100               | mV                |

| CLKOUT Duty Cycle                                                               | $T_{J} = -40$ °C<br>$T_{J} = 25$ °C<br>$T_{J} = 125$ °C                                            |     |                   | 22.7<br>44.1<br>77 |                   | %<br>%<br>%       |

| Charging Control                                                                |                                                                                                    |     |                   |                    |                   |                   |

| STATUS, FBOW, FBIW, SWENO, IOW, ECON Output<br>Low Voltage                      | $I_{OL} = 5mA$                                                                                     | •   |                   | 0.22               | 0.5               | V                 |

| STATUS, FBOW, FBIW, SWENO, IOW, ECON Output<br>High Voltage                     | $I_{OH} = -5mA$                                                                                    | •   | 2.7               | 3                  |                   | V                 |

| Power Supply Mode Detection Threshold (Note 6)                                  | VINR Pin Falling                                                                                   | •   | 155               | 174                |                   | mV                |

| Power Supply Mode Detection Threshold Hysteresis (Note 6)                       |                                                                                                    |     |                   | 29                 |                   | mV                |

| Minimum VINR Voltage for Startup (Note 6)                                       | Not in Power Supply Mode<br>Low Power Mode Enabled<br>Low Power Mode Disabled                      | •   | 380<br>213        | 395<br>225         | 410<br>237        | mV<br>mV          |

| High Charging Current Threshold on IOR (Note 6)                                 | IOR Rising → ECON Rising                                                                           | •   | 168               | 195                | 224               | mV                |

| Low Charging Current Threshold on IOR (Note 6)                                  | IOR Falling → ECON Falling                                                                         | •   | 95                | 122                | 150               | mV                |

| Minimum TEMPSENSE % of AV <sub>DD</sub> to Detect Battery Disconnected (Note 6) |                                                                                                    | •   | 94.5              | 96                 | 97.5              | %                 |

| V <sub>CSPOUT</sub> – V <sub>CSNOUT</sub> Threshold for C/5 Detection (Note 6)  | $V_{CSxOUT}$ Common Mode = 5.0V, $R_{TOTAL}$ from IMON_OUT to Ground = 24.3k $\Omega$              |     | 9                 | 10                 | 11                | mV                |

| V <sub>CSPOUT</sub> – V <sub>CSNOUT</sub> Threshold for C/10 Detection (Note 6) | $V_{CSxOUT}$ Common Mode = 5.0V, IOR Falling, $R_{TOTAL}$ from IMON_OUT to Ground = 24.3k $\Omega$ |     | 4.25              | 5                  | 5.75              | mV                |

| FBIW, FBOW PWM Frequency (OSC2)                                                 |                                                                                                    |     |                   | 31.25              |                   | kHz               |

| FBIW, FBOW PWM Resolution                                                       |                                                                                                    |     |                   | 8                  |                   | bits              |

| Internal A/D Resolution                                                         |                                                                                                    |     |                   | 10                 |                   | bits              |

## **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25$ °C. $V_{IN} = 12V$ , $V_{DD} = AV_{DD} = 3.3V$ , SHDN = 3V unless otherwise noted. (Note 3)

| PARAMETER                                                | CONDITIONS                                                 |   | MIN     | TYP   | MAX  | UNITS  |

|----------------------------------------------------------|------------------------------------------------------------|---|---------|-------|------|--------|

| EEPROM Characteristics                                   | ·                                                          |   |         |       |      |        |

| Endurance (Note 8)                                       | 0°C < T <sub>J</sub> < 85°C During EEPROM Write Operations |   | 100,000 |       |      | Cycles |

| Digital Input/Output SCL, SDA                            |                                                            |   |         |       |      |        |

| SDA Input Voltage High (V <sub>SDA_VIH</sub> )           |                                                            | • | 2.25    |       |      | V      |

| SDA Input Voltage Low (V <sub>SDA_VIL</sub> )            |                                                            | • |         |       | 0.65 | V      |

| SCL Input Voltage High (V <sub>SCL_VIH</sub> )           |                                                            | • | 2.25    |       |      | V      |

| SCL Input Voltage Low (V <sub>SCL_VIL</sub> )            |                                                            | • |         |       | 0.65 | V      |

| SDA Input Leakage Current (I <sub>LEAK_SDA</sub> )       | SDA = 0V and 3.3V                                          | • |         | <0.05 | ±1   | μА     |

| SCL Input Leakage Current (I <sub>LEAK_SCL</sub> )       | SCL = 0V and 3.3V                                          | • |         | <0.05 | ±1   | μА     |

| SDA Output Low Voltage (V <sub>SDA_OL</sub> )            | 3mA into SDA Pin                                           | • |         |       | 0.4  | V      |

| I <sup>2</sup> C Timing Characteristics                  |                                                            |   |         |       |      |        |

| Serial Clock Frequency (f <sub>SCL</sub> )               |                                                            | • |         |       | 100  | kHz    |

| Serial Clock Low Period (t <sub>LOW</sub> )              |                                                            | • | 4.7     |       |      | μs     |

| Serial Clock High Period (t <sub>HIGH</sub> )            |                                                            | • | 4       |       |      | μs     |

| Bus Free Time Between Stop and Start (t <sub>BUF</sub> ) |                                                            | • | 4.7     |       |      | μs     |

| Start Condition Hold Time (t <sub>HD,STA</sub> )         |                                                            | • | 4       |       |      | μs     |

| Start Condition Setup Time (t <sub>SU,STA</sub> )        |                                                            | • | 4.7     |       |      | μs     |

| Stop Condition Setup Time (t <sub>SU,STO</sub> )         |                                                            | • | 4       |       |      | μs     |

| Data Hold Time (t <sub>HD,DAT</sub> ) (Note 9)           |                                                            | • | 0       |       |      | ns     |

| Data Setup Time (t <sub>SU,DAT</sub> )                   |                                                            | • | 250     |       |      | ns     |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: Do not force voltage on the V<sub>C</sub> pin.

**Note 3:** The LT8491E is guaranteed to meet performance specifications from 0°C to 125°C junction temperature. Specifications over the –40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LT8491I is guaranteed over the full –40°C to 125°C junction temperature range.

**Note 4:** Do not apply a voltage or current source to these pins. They must be connected to capacitive loads only; otherwise permanent damage may occur.

Note 5: Negative voltages on the SW1 and SW2 pins are limited in the applications by the body diodes of the external NMOS devices M2 and  $\,$

M3 or parallel Schottky diodes when present. The SW1 and SW2 pins are tolerant of these negative voltages more than one diode drop below ground, guaranteed by design.

**Note 6:** These thresholds are measured by the internal A/D converter. The A/D reference voltage is  $AV_{DD}$ .  $AV_{DD}$ ,  $V_{DD}$  and an additional 2.8mA load are regulated by LD033 to create the  $AV_{DD}$  reference for these measurements. The absolute threshold voltages will shift with corresponding changes in the  $AV_{DD}$  voltage.

Note 7: 10V minimum  $V_{\text{IN}}$  required for solar powered start-up if low power mode is enabled.

**Note 8:** The EEPROM has an endurance of at least 100,000 write/erase cycles. Data retention of 20 years at 85°C, 100 years at 25°C. These statements are based on published information from vendor.

**Note 9:** A master device must provide a hold time of at least 300ns for the SDA signal (referred to the minimum  $V_{IH}$  of the SCL signal) to bridge the undefined region of the SCL falling edge.

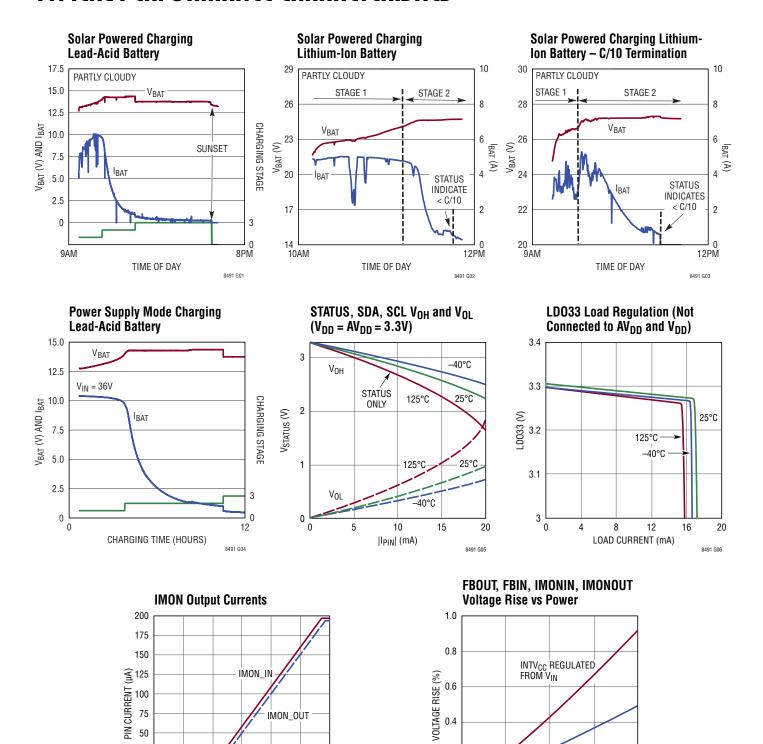

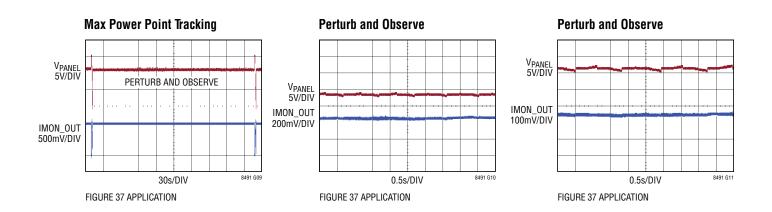

#### TYPICAL PERFORMANCE CHARACTERISTICS

Rev. 0

INTV<sub>CC</sub> REGULATED FROM EXTV<sub>CC</sub>

INTV<sub>CC</sub> REGULATOR POWER (W)

25

0 -25 -100

-50

50

CSxIN-CSxOUT (mV)

100

150

200

0.2

#### TYPICAL PERFORMANCE CHARACTERISTICS

#### PIN FUNCTIONS

**FBIR (Pin 1):** A/D Input Pin. Connects to FBIN pin to measure input voltage.

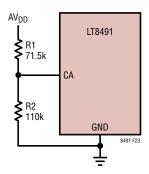

**CA (Pin 2):** A/D Input Pin. Connects to a resistor divider to program the I<sup>2</sup>C address. This pin is measured during the power up sequence.

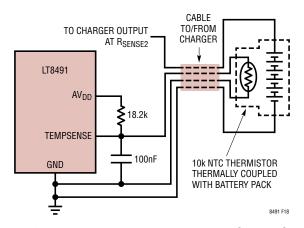

**TEMPSENSE (Pin 3):** A/D Input Pin. Connects to a thermistor divider network for sensing battery temperature or a resistor divider if unused. This pin is frequently monitored for temperature compensation and enforcing temperature limits.

**V<sub>DD</sub>** (**Pin 4**): I<sup>2</sup>C and Control Logic Power Supply Pin. Connect this pin to LDO33 and AV<sub>DD</sub>.

**FBOW (Pin 5):** PWM Digital Output Pin. Connects to FBOUT through an RCR network to temperature compensate the battery voltage.

**FBIW (Pin 6):** PWM Digital Output Pin. Connects to FBIN through an RCR network to adjust the solar panel voltage for MPPT.

**INTV**<sub>CC</sub> (**Pin 7**): Internal 6.35V Regulator Output Pin. Connects to the GATEV<sub>CC</sub> pin. INTV<sub>CC</sub> is powered from EXTV<sub>CC</sub> when the EXTV<sub>CC</sub> voltage is higher than 6.4V, otherwise INTV<sub>CC</sub> is powered from V<sub>IN</sub>. Bypass this pin to ground with a minimum 4.7 $\mu$ F ceramic capacitor. See HW Config: MODE Pin - Current Conduction Mode for additional details.

SWEN (Pin 8): Switch Enable Pin. Tie to the SWENO pin.

**MODE (Pin 9):** Mode Pin. The voltage applied to this pin sets the operating mode of the switching regulator. Tie this pin to  $INTV_{CC}$  to make discontinuous current mode active. Tie this pin to ground to operate in discontinuous current mode for low battery charging currents and continuous current mode for high battery charging currents. Do not float this pin. See HW Config: MODE Pin - Current Conduction Mode for additional details.

**IMON\_IN (Pin 10):** Input Current Monitor and Limit Pin. The current out of this pin is proportional to the input current. See the Applications Information section for more information.

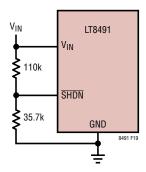

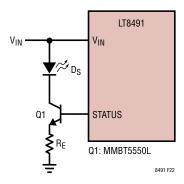

**SHDN** (**Pin 11**): Shutdown Pin. In conjunction with the UVLO (undervoltage lockout) circuit, this pin is used to enable/disable the chip. Do not float this pin.

**CSN (Pin 12):** The (–) Input to the Inductor Current Sense and Reverse Current Detect Amplifier.

**CSP** (Pin 13): The (+) Input to the Inductor Current Sense and Reverse Current Detect Amplifier. The  $V_C$  pin voltage and built-in offsets between the CSP and CSN pins set the inductor current trip threshold.

**LD033 (Pin 14):** 3.3V Regulator Output. This pin provides power to the  $V_{DD}$  and  $AV_{DD}$  pins. Bypass this pin to ground with a minimum 4.7µF ceramic capacitor.

**FBIN (Pin 15):** Input Feedback Pin. This pin is connected to the input error amplifier input.

**FBOUT (Pin 16):** Output Feedback Pin. This pin connects the error amplifier input to an external resistor divider from the output.

**IMON\_OUT (Pin 17):** Output Current Monitor and Limit Pin. The current out of this pin is proportional to the average output current. See the Applications Information section for more information.

**V<sub>C</sub>** (**Pin 18**): Error Amplifier Output Pin. Tie the external compensation network to this pin.

**SS (Pin 19):** Soft-Start Pin. Place 100nF of capacitance from this pin to ground. Upon start-up, this pin will be charged by an internal resistor to 2.5V.

**CLKOUT (Pin 20):** Switching Regulator Clock Output Pin. CLKOUT will toggle at the same frequency as the switching regulator oscillator (OSC1 on the Block Diagram) or as the SYNC pin but is approximately 180° out-of-phase. CLKOUT can also be used as a temperature monitor of the switching regulator since the CLKOUT duty cycle varies linearly with the junction temperature of the switching regulator. It is connected to the CLKDET pin through an RC filter. The CLKOUT pin can drive capacitive loads up to 200pF.

#### PIN FUNCTIONS

**SYNC (Pin 21):** To synchronize the switching frequency to an outside clock, simply drive this pin with a clock. The high voltage level of the clock needs to exceed 1.3V, and the low level should be less than 0.5V. Drive this pin to less than 0.5V to revert to the internal free-running clock (OSC1 in the Block Diagram).

**RT (Pin 22):** Timing Resistor Pin. Adjusts the switching regulator frequency (OSC1) when SYNC is not driven by a clock. Place a resistor from this pin to ground to set the free-running frequency of OSC1. Do not float this pin.

**BG1**, **BG2** (**Pin 23/Pin 25**): Bottom Gate Drive. Drives the gates of the bottom N-channel MOSFETs between ground and GATEV<sub>CC</sub>.

**GATEV<sub>CC</sub> (Pin 24):** Power Supply for Gate Drivers. Must be connected to the INTV<sub>CC</sub> pin. Do not power from any other supply. Locally bypass to ground.

**BOOST1**, **BOOST2** (Pin 33/Pin 27): Boosted Floating Driver Supply. The (+) terminal of the bootstrap capacitor connects here. The BOOST1 pin swings from a diode voltage below GATEV $_{CC}$  up to  $V_{IN}$  + GATEV $_{CC}$ . The BOOST2 pin swings from a diode voltage below GATEV $_{CC}$  up to  $V_{BAT}$  + GATEV $_{CC}$ .

**SW1**, **SW2** (**Pin 31/Pin 29**): Switch Nodes. The (–) terminal of the bootstrap capacitors connect here.

**TG1, TG2 (Pin 32/Pin 28):** Top Gate Drive. Drives the top N-channel MOSFETs with voltage swings equal to GATEV<sub>GC</sub> superimposed on the switch node voltages.

**SRVO\_FBIN (Pin 35):** Open-Drain Logic Output. This pin is pulled to ground when the input voltage feedback loop is active. This pin is unused for most LT8491 applications and can be floated.

**SRVO\_IIN (Pin 36):** Open-Drain Logic Output. This pin is pulled to ground when the input current feedback loop is active. This pin is unused for most LT8491 applications and can be floated.

**SRVO\_IOUT (Pin 37):** Open-Drain Logic Output. This pin is pulled to ground when the output current feedback loop is active. This pin is unused for most LT8491 applications and can be floated.

**SRVO\_FBOUT (Pin 38):** Open-Drain Logic Output. This pin is pulled to ground when the output voltage feedback loop is active. This pin is unused for most LT8491 applications and can be floated.

**EXTV**<sub>CC</sub> (**Pin 40**): External V<sub>CC</sub> Input. When EXTV<sub>CC</sub> exceeds 6.4V (typical), INTV<sub>CC</sub> will be powered from this pin. When EXTV<sub>CC</sub> is lower than 6.22V (typical), INTV<sub>CC</sub> will be powered from V<sub>IN</sub>. See HW Config: MODE Pin - Current Conduction Mode for additional details.

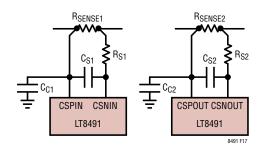

**CSNOUT (Pin 41):** The (–) Input to the Output Current Sense Amplifier.

**CSPOUT (Pin 42):** The (+) Input to the Output Current Sense Amplifier. This pin and the CSNOUT pin measure the voltage across the sense resistor to provide the output current signals.

**CSNIN (Pin 44):** The (-) Input to the Input Current Sense Amplifier. This pin and the CSPIN pin measure the voltage across the sense resistor to provide the instantaneous input current signals.

**CSPIN (Pin 45):** The (+) Input to the Input Current Sense Amplifier.

**V<sub>IN</sub> (Pin 46):** Main Input Supply Pin. Must be bypassed to local ground plane.

**ECON (Pin 48):** Digital Output Pin. Optional control output signal used to disconnect EXTV<sub>CC</sub> from the battery when the average charge current drops below a predetermined threshold.

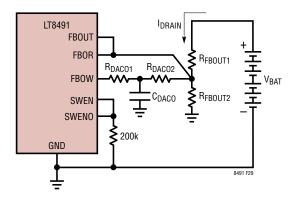

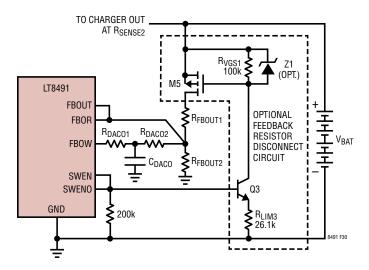

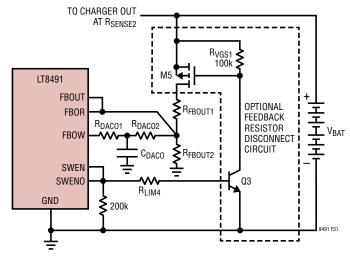

**SWENO (Pin 49):** Digital Output Pin. Connect to SWEN. Enables the switching regulator. A 200k pull-down resistor is required from this pin to ground.

**IOW (Pin 50):** Digital Output Pin. Connects to IMON\_OUT through a resistor. By switching the pin between logic low and high impedance, the total  $R_{IMON\_OUT}$  changes, which changes the output current limit.

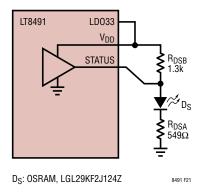

**STATUS (Pin 51):** Digital Output Pin. When used with an LED, this signal provides a visual indication of the progress of the charging algorithm.

#### PIN FUNCTIONS

NC (Pins 52, 60): Not connected.

**IIR (Pin 53):** A/D Input Pin. Connects to IMON\_IN to read input current. Used to manage MPPT and for telemetry.

**VINR (Pin 54):** A/D Input Pin. Connects to resistive divider on  $V_{IN}$  to measure input voltage. Used for telemetry and to manage MPPT and startup.

**CLKDET (Pin 56):** A/D Input Pin. Connects to CLKOUT through an RC filter to detect the duty cycle of CLKOUT. Used to manage startup.

**FBOR (Pin 57):** A/D Input Pin. Connects to FBOUT pin to read charger output voltage. Used to manage the charging algorithm.

$AV_{DD}$  (Pin 58): A/D Positive Reference Pin. Tie this pin to  $V_{DD}$  and LD033.

**SDA (Pin 61):** I<sup>2</sup>C Bidirectional Data Pin.

**SCL (Pin 63):** I<sup>2</sup>C Clock Input Pin (100kHz Maximum).

**IOR (Pin 64):** A/D Input Pin. Connects to IMON\_OUT pin to read the charger output current. Used for telemetry and to manage the charging algorithm.

**GND (Pins 55, 59, 62, Exposed Pad 65):** Ground. Tie directly to local ground plane.

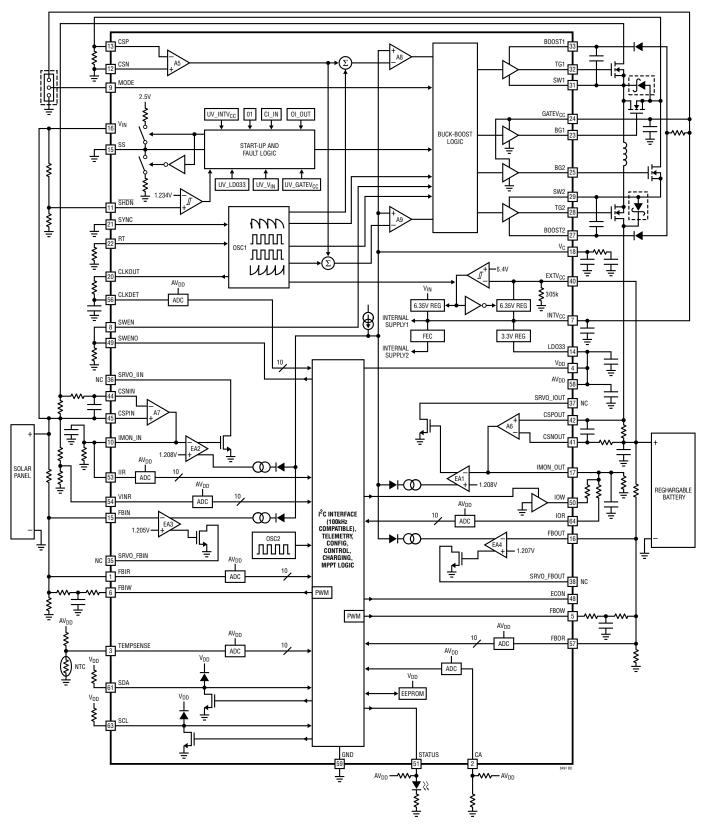

### **BLOCK DIAGRAM**

Figure 1. Block Diagram

#### **OVERVIEW**

The LT8491 is a powerful and easy to use battery charging controller with automatic maximum power point tracking (MPPT), temperature compensation and an I<sup>2</sup>C interface for telemetry, status, control and configuration. The LT8491 is based on the LT8705 buck-boost controller with additional battery charging and MPPT control functions. Refer to the LT8705 data sheet for more detailed information about the switching regulator portions of the LT8491.

Several reference applications are included in this data sheet to simplify system design. Many battery-charging applications can be implemented using one of the reference applications with little or no modification required. Various charging parameters can be configured via the digital I<sup>2</sup>C interface and can be made permanent in the on-chip EEPROM. Since the battery charging and MPPT are controlled by the LT8491, no firmware development is required. Interfacing to the I<sup>2</sup>C pins is only required to configure and/or monitor the charger. For reference, factory default I<sup>2</sup>C configuration settings are listed in the I<sup>2</sup>C Register Map section.

The LT8491 includes four different forms of regulation: output current, input current, input voltage and output voltage (EA1 - EA4 respectively as shown in Figure 1). The commanded inductor current is limited by whichever form of regulation requires the lowest voltage on the  $V_{\text{C}}$  pin. When powered by a solar panel, the MPPT function uses input voltage regulation to locate and track the maximum power point of the solar panel. Input current regulation is used to limit the maximum current drawn from the input supply to safe levels. The output current regulation sets the maximum battery charging current, and the output voltage regulation is used to set the maximum battery charging voltage.

The LT8491 offers user configurable charge timers. If a timer has been set and subsequently expires, the LT8491 will halt charging and communicate this through the  $I^2C$  interface and the STATUS pin. Options for automatic restart of the charging cycle are discussed later in the Configure Automatic Restart section.

The LT8491 also includes a TEMPSENSE pin, which can be connected to an NTC resistor divider network thermally coupled to the battery pack. The TEMPSENSE pin can facilitate several functions including temperature compensated charging, battery temperature telemetry, and charging disable when the battery is outside of safe temperature limits. Detection of the NTC resistor can also give an indication to the charger if the battery is connected or not.

The LT8491 also provides charging telemetry and status through the I<sup>2</sup>C interface and the STATUS pin. Refer to the Telemetry Registers and Status Registers sections for the I<sup>2</sup>C indicators. The behavior of the STATUS pin is described in the STATUS Indicator Pin section.

#### I<sup>2</sup>C SERIAL INTERFACE

The LT8491 includes a slave I<sup>2</sup>C compatible interface facilitating digital control of the charger settings and digital readouts of telemetry and status. The following subsections explain how to read and write data to the LT8491. The I<sup>2</sup>C Register Map and I<sup>2</sup>C Register Descriptions sections provide detailed descriptions of all the I<sup>2</sup>C registers and their functions.

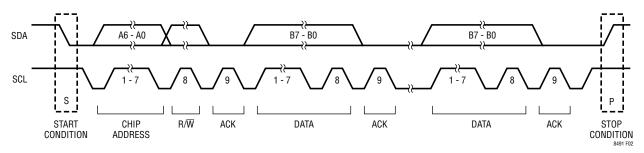

#### I<sup>2</sup>C: START and STOP Conditions

When the bus is idle, both SCL and SDA are high. A bus master signals the beginning of a transmission with a START (S) condition by transitioning SDA from high to low while SCL is high, as shown in Figure 2. When the master has finished communicating with the slave, it issues a STOP (P) condition by transitioning SDA from low to high while SCL is high. The bus is then free for another transmission.

#### I<sup>2</sup>C: ACKnowledge

The acknowledge signal (ACK) is used in handshaking between the transmitter and receiver to indicate that the most recent byte of data was received. When the slave is the receiver, it pulls down the SDA line so that it remains LOW during this pulse to acknowledge receipt of the data. If the slave fails to acknowledge, by leaving SDA high, then the master may abort the transmission by generating a STOP condition. When the master is receiving data

Figure 2. Data Transfer Over I<sup>2</sup>C Bus

from the slave, the master pulls down the SDA line during the clock pulse to indicate receipt of the data. After the last byte has been received the master leaves the SDA line HIGH (NACK) and issues a STOP (P) condition to terminate the transmission.

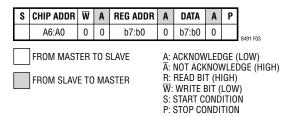

#### I<sup>2</sup>C: Chip Addressing

The CA pin is used to select one of four 7-bit chip addresses (A6:A0). This address is sent by the master to identify which IC it is transferring data with. The CA pin can be tied to ground,  $AV_{DD}$  or connected to a resistor divider to select the desired chip address. See the HW Config:  $I^2C$  Chip Address section for more detailed information.

#### I<sup>2</sup>C: Clock Stretching

The charger supports clock speeds up to 100kHz for the  $I^2C$  interface. The master is required to support  $I^2C$  clock stretching to properly communicate with this charger (slave).

#### I<sup>2</sup>C: Data Transfer Transactions

The LT8491 supports byte-writes, byte-reads, and word-reads using the transaction formats shown in Figure 3 to Figure 5 respectively. Figure 3 shows the required format for writing a byte of data to the LT8491. Again, the required chip address (A6:A0) depends on the CA pin.

A single byte of data is read from the LT8491 using the byte-read transaction shown in Figure 4. The register address selects the data byte that is returned. This transaction requires four I<sup>2</sup>C bytes to read one byte of chip data.

The word-read transaction, shown in Figure 5, should be used to read telemetry such as power, volts and amps that is stored in 16-bit formats. The word-read transaction ensures that both bytes of data are properly paired together and can be combined into a valid word. Due to the time latency between I<sup>2</sup>C transactions, combining bytes from two byte-read transactions may not result in valid 16-bit telemetry data.

Referring again to Figure 5, the register address selects the first byte of data (DATAO) that is returned. Data from the next higher byte address is returned in the second byte (DATA1). When reading Word or Long Word data, note that the least significant byte is at the lowest address location (little-endian). B0 of the register address should typically be set to 0 since all words in the LT8491 are aligned to even register addresses. This transaction requires five I<sup>2</sup>C bytes to read two bytes of chip data and must be repeated for each subsequent word of data that is read.

#### I<sup>2</sup>C: Powering the Interface

The I $^2$ C control logic and I/O are powered from the V $_{DD}$  pin.  $V_{DD}$  is ultimately supplied from either V $_{IN}$  or EXTV $_{CC}$  when the  $\overline{SHDN}$  pin is high. This can be seen in the block diagram which shows that V $_{IN}$  and EXTV $_{CC}$  supply the INTV $_{CC}$  regulator that, in turn, supplies the LDO33 regulator which is finally connected to V $_{DD}$ . After  $\overline{SHDN}$  and V $_{DD}$  rise, I $^2$ C communication is enabled after a delay of 10ms (typical). Note that the LT8491 contains diodes from the SDA and SCL pins to the V $_{DD}$  pin (see Figure 8). These diodes are normally reverse biased and have no effect on the I $^2$ C bus. However, when the LT8491 is unpowered, the V $_{DD}$  pin voltage will drop and may pull down on the SDA and SCL pins, thus effecting communication on the bus.

Figure 3. I<sup>2</sup>C Byte-Write Transaction

| S | CHIP ADDR | W | A | REG ADDR | Α | S | CHIP ADDR | R | Α | DATA  | Ā  | Р       |

|---|-----------|---|---|----------|---|---|-----------|---|---|-------|----|---------|

|   | A6:A0     | 0 | 0 | b7:b0    | 0 |   | A6:A0     | 1 | 0 | b7:b0 | 1  |         |

|   |           |   |   |          |   |   |           |   |   |       | 84 | 491 F04 |

Figure 4. I<sup>2</sup>C Byte-Read Transaction

| Е | S | CHIP ADDR | W | A | REG ADDR | A | S | CHIP ADDR | R | A | DATA0 | A | DATA1 | Ā | P |

|---|---|-----------|---|---|----------|---|---|-----------|---|---|-------|---|-------|---|---|

|   |   | A6:A0     | 0 | 0 | b7:b0    | 0 |   | A6:A0     | 1 |   | b7:b0 | 0 | b7:b0 | 1 |   |

| _ |   |           |   |   |          |   |   |           |   | _ |       | _ |       |   |   |

Figure 5. I<sup>2</sup>C Word-Read Transaction

#### I<sup>2</sup>C DATA

#### **Data: Memory Regions**

Data in the LT8491 is arranged into six regions as shown in Table 1.

Table 1. LT8491 I<sup>2</sup>C Addressable Memory Regions

| REGION        | TYPE      | I <sup>2</sup> C REG<br>ADDR RANGE | DESCRIPTION                                     |

|---------------|-----------|------------------------------------|-------------------------------------------------|

| Telemetry     | Registers | 0x00-0x11                          | Charging telemetry.                             |

| Status        | Registers | 0x12-0x1F                          | Charging and system status.                     |

| Control       | Registers | 0x20-0x27                          | Control charging on/off and EEPROM access.      |

| Configuration | Registers | 0x28-0x5B                          | Charger configuration settings.                 |

| Manufacturer  | Registers | 0x5C-0x61                          | Manufacturer Data.                              |

| Boot          | EEPROM    | 0x88-0xBD                          | Non-volatile storage of start-up configuration. |

Telemetry Region: These read-only registers indicate telemetry such as temperature, voltage, current, power and efficiency. These word-sized values must be read using the I<sup>2</sup>C word-read transaction to avoid retrieving mismatched bytes (see I<sup>2</sup>C: Data Transfer Transactions). See the Telemetry Operation and Telemetry Registers sections for further telemetry information.

Status Region: These read-only registers indicate status such as charging state, solar panel state, faults, timers and others. Detailed status register descriptions are provided in the Status Registers section.

Control Region: These read-write registers are used to start and stop the charger, write to the EEPROM, reset the chip and other related functions. The contents of these registers revert to their default values, as listed in the I<sup>2</sup>C Register Map, after power is cycled or the CTRL\_RESTART\_CHIP register is written to 0x99. Detailed control register descriptions are provided in the I<sup>2</sup>C Register Descriptions section.

Configuration Region: These read-write registers determine the charger settings such as timer limits, restart options, V<sub>BAT</sub> stage voltages, and many others. After power-up or reset, the configuration registers are automatically loaded with data from the EEPROM (see the Startup Sequence section). Factory default EEPROM values are provided in the I<sup>2</sup>C Register Map. Detailed configuration register descriptions are provided in the I<sup>2</sup>C Register Descriptions section.

*Manufacturer Region:* These read-only registers indicate manufacturer data that is determined at the factory.

Boot Region: The boot data is stored in non-volatile EEPROM and is copied into the configuration registers during startup or after the CTRL\_RESTART\_CHIP register is written to 0x99, as described in the Startup Sequence section.

Each EEPROM location in the boot region corresponds to a register in the configuration region. As such, the boot region data is arranged in the exact same order and format as in the configuration region but is read from an I<sup>2</sup>C address 0x60 higher than the corresponding configuration register address. Reading of the boot data is described in the EEPROM: Reading section.

Writing directly to the EEPROM is prohibited. Instead, data can be copied from the configuration registers into the EEPROM by writing to appropriate control registers. Further information about writing the EEPROM is in the EEPROM: Writing section.

#### Data: Bytes, Words and Long Words

LT8491 data is stored in three sizes: bytes, words (2 bytes) and long words (4 bytes). Tables are provided throughout this data sheet indicating the sizes for each piece of data. Since the  $I^2C$  bus addresses one byte at a time, word and long word data is spread across multiple  $I^2C$  register address locations.

Words and long words are stored in an arrangement commonly referred to as little endian. The least significant byte (LSB) is stored at the lower  $I^2C$  register address location. The next most significant byte (MSB) is stored at the next higher  $I^2C$  register address and so on.

As an example, suppose the TELE\_IOUT register is indicating output current of 5.274 Amps (see Telemetry Registers). This 16-bit register, starting at I<sup>2</sup>C address 0x08 will contain the value 0x149A. The two bytes comprising TELE\_IOUT are stored as shown:

Table 2. Example of TELE\_IOUT Word Storage

| I <sup>2</sup> C REG ADDRESS | BYTE VALUE |  |  |

|------------------------------|------------|--|--|

| 0x08                         | 0x9A       |  |  |

| 0x09                         | 0x14       |  |  |

Reading TELE\_IOUT with the word-read transaction from register address 0x08 returns two bytes, DATA0 (0x9A) and then DATA1 (0x14) indicating 5.274 Amps.

The temperature compensation coefficients, in the configuration region, are the only data stored as long words. For example, suppose CFG\_TC1 has the value 1.54e-3 stored as the 32-bit floating point value 0xBAC9D9D3. This data is stored as follows in Table 3:

Table 3. Example of CFG\_TC1 Long Word Storage

| I <sup>2</sup> C REG ADDRESS | BYTE VALUE |

|------------------------------|------------|

| 0x56                         | 0xD3       |

| 0x57                         | 0xD9       |

| 0x58                         | 0xC9       |

| 0x59                         | 0xBA       |

Reading the entire long word requires four byte-read transactions, or two word-read transactions. Writing the entire long word requires four byte-write transactions at addresses 0x56 through 0x59.

#### Data: Min/Max Register Values

Some configuration registers have minimum and maximum acceptable values (i.e. CFG\_VS3\_25C). The value limits for each register (if any) are listed in the I<sup>2</sup>C Register Descriptions section. If a configuration register is written to a value outside of the min/max limits, the LT8491 will automatically modify the register contents to the factory default register value.

#### **Data: Access Permissions**

I<sup>2</sup>C read and/or write access to various regions is conditional. Table 4 and Table 5 illustrate the conditions required to access the various regions. When writing to a register, while write access permission is denied, the data is ignored and not written to the addressed location. When reading from a location while read access permission is denied, the returned data is all zeros.

As shown in Table 4 and Table 5, most address locations can be read unconditionally after startup is complete. However, the boot region is also unreadable while EEPROM writing is ongoing and will return 0x00 during that time.

Table 4. Register Access Permissions (Except Control Region)

| •             | \ .           | <b>3</b> ,                         |                        |                                                                                                   |

|---------------|---------------|------------------------------------|------------------------|---------------------------------------------------------------------------------------------------|

| MEMORY REGION | REGISTER NAME | I <sup>2</sup> C REG ADDRESS RANGE | READ ACCESS            | WRITE ACCESS                                                                                      |

| Telemetry     | All           | 0x00-0x11                          | Always <sup>1</sup>    | Never                                                                                             |

| Status        | All           | 0x12-0x1F                          | Always <sup>1</sup>    | Never                                                                                             |

| Configuration | All           | 0x28-0x5B                          | Always <sup>1</sup>    | Only when CHRG_LOGIC_ON=0 <sup>3</sup> and CTRL_EE_WRT_EN≠0xCC and SYSTEM_BUSY=b00 <sup>3</sup> . |

| Manufacturer  | All           | 0x5D-0x61                          | Always <sup>1</sup>    | Never                                                                                             |

| Boot          | All           | 0x88-0xBD                          | Always <sup>1, 2</sup> | Never<br>See EEPROM: Writing section.                                                             |

<sup>1.</sup> Except when chip is powered down or the I<sup>2</sup>C interface has not been activated yet during the startup sequence.

**Table 5. Control Region Access Permissions**

|                   | I <sup>2</sup> C |                     |                                | WRITE RE                 | QUIRES                   |                                |

|-------------------|------------------|---------------------|--------------------------------|--------------------------|--------------------------|--------------------------------|

| REGISTER NAME     | REG<br>ADDR      | READ<br>ACCESS      | CHRG_LOGIC_ON <sup>3</sup> = 0 | CTRL_EE_WRT_EN ≠<br>0xCC | CTRL_EE_WRT_EN =<br>0xCC | SYSTEM_BUSY <sup>3</sup> = 00b |

| CTRL_WRT_TO_BOOT  | 0x20             | Always <sup>1</sup> | ✓                              |                          | ✓                        | 1                              |

| CTRL_EE_WRT_EN    | 0x21             |                     | ✓                              |                          |                          | 1                              |

| CTRL_HALT_STARTUP | 0x22             |                     |                                |                          |                          |                                |

| CTRL_CHRG_EN      | 0x23             |                     | ✓4                             | ✓                        |                          | 1                              |

| CTRL_RESTART_CHIP | 0x24             |                     | ✓                              |                          |                          | 1                              |

| CTRL_RESET_FLAG   | 0x25             |                     |                                |                          |                          | 1                              |

| CTRL_UPDATE_TELEM | 0x26             |                     | ✓                              | ✓                        |                          | 1                              |

| Reserved          | 0x27             |                     |                                | Writes to this reserved  | register always ignored. |                                |

<sup>4.</sup> Only required when writing 1 to CHRG\_EN bit.

All I<sup>2</sup>C byte-write registers have conditions under which the data is accepted. These conditions prevent changes to the charger configuration while the charging is ongoing and to help prevent inadvertent changes to the configuration and/or EEPROM.

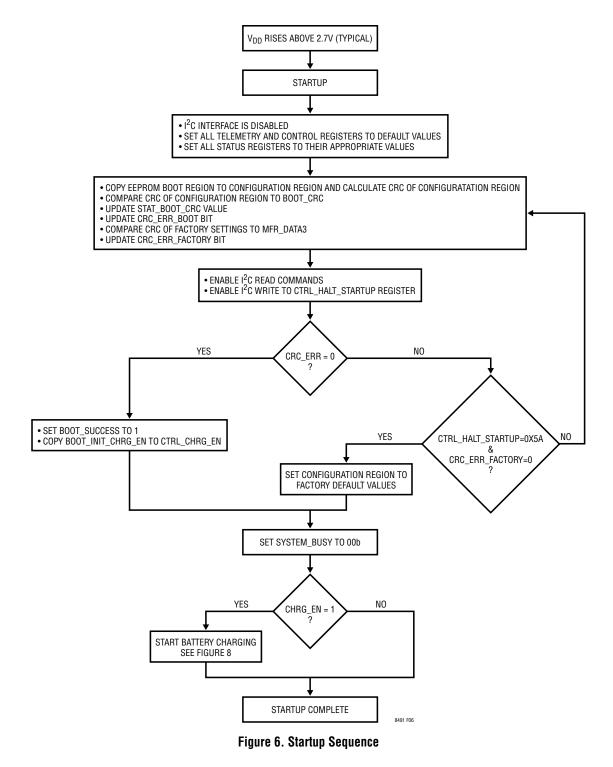

#### STARTUP SEQUENCE

Figure 6 illustrates the startup sequence for the LT8491. Not all details are shown. The sequence is initiated when the  $V_{DD}$  pin rises above 2.7V (typical). If the device is already powered on and CTRL\_CHRG\_EN=0, the startup sequence can be re-initiated by writing CTRL\_RESTART\_CHIP to 0x99.

At the beginning of the startup sequence the  $I^2C$  interface is disabled and the default values for the telemetry, status and control registers are set as indicated in the  $I^2C$  Register Map section.

Next, a CRC check of the EEPROM boot region and factory settings is performed. If the boot region fails the CRC check, the LT8491 recalculates the CRC indefinitely until the CRC check passes, or the process is interrupted by writing CTRL\_HALT\_STARTUP to 0x5A. If startup is halted then the configuration registers revert to their factory default values, as listed in the I<sup>2</sup>C Register Map, before completing startup. If the factory settings fail the CRC check, the LT8491 recalculates the CRC indefinitely

<sup>2.</sup> Except when EEPROM write operation is occurring. This is indicated by a read of 10b from STAT\_SYSTEM→SYSTEM\_BUSY, or a read of 1 from CTRL\_WRT\_TO\_BOOT→RDY\_BUSY.

<sup>3.</sup> CHRG\_LOGIC\_ON is a read-only bit in the STAT\_CHARGER register. It is cleared shortly after CTRL\_CHRG\_EN is written 0x00. SYSTEM\_BUSY are read-only bits in the STAT\_SYSTEM register.

until the CRC check passes. More information about the CRC checking is discussed in the CRC Operation section.

When the boot CRC and the factory CRC check passes, the STAT\_SYSTEM $\rightarrow$ BOOT\_SUCCESS bit is set to 1.

Subsequently, CTRL\_CHRG\_EN is preset with the value read from BOOT\_MISC in the EEPROM. This determines if the charging starts automatically, at the end of the sequence, or not.

Rev.

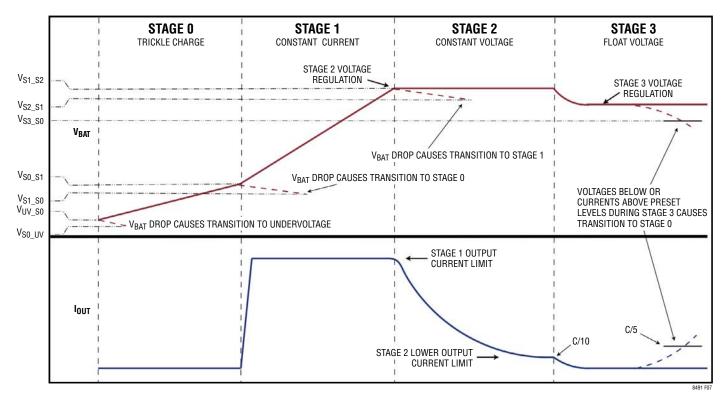

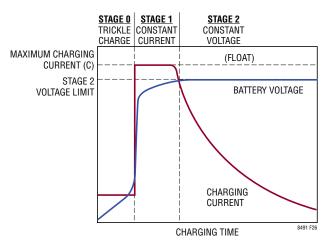

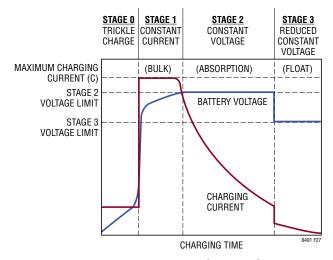

Figure 7. Typical Battery Charging Cycle

#### BATTERY CHARGING ALGORITHM

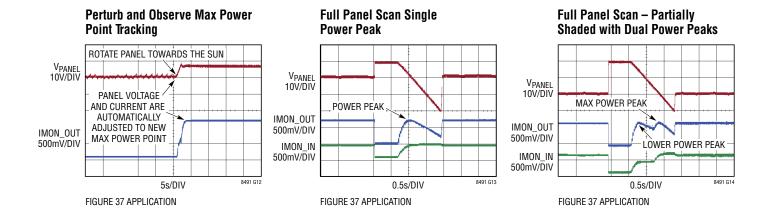

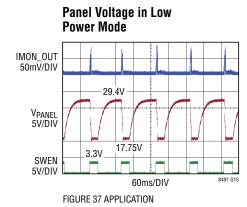

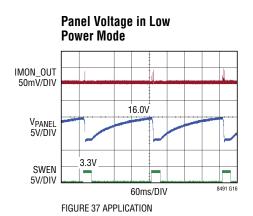

The LT8491 implements a CCCV charging algorithm. The idealized charging profile is shown in Figure 7 and assumes constant temperature and adequate input power. As battery temperature and illumination conditions on the panel change, the actual current and voltage seen by the battery will vary accordingly.

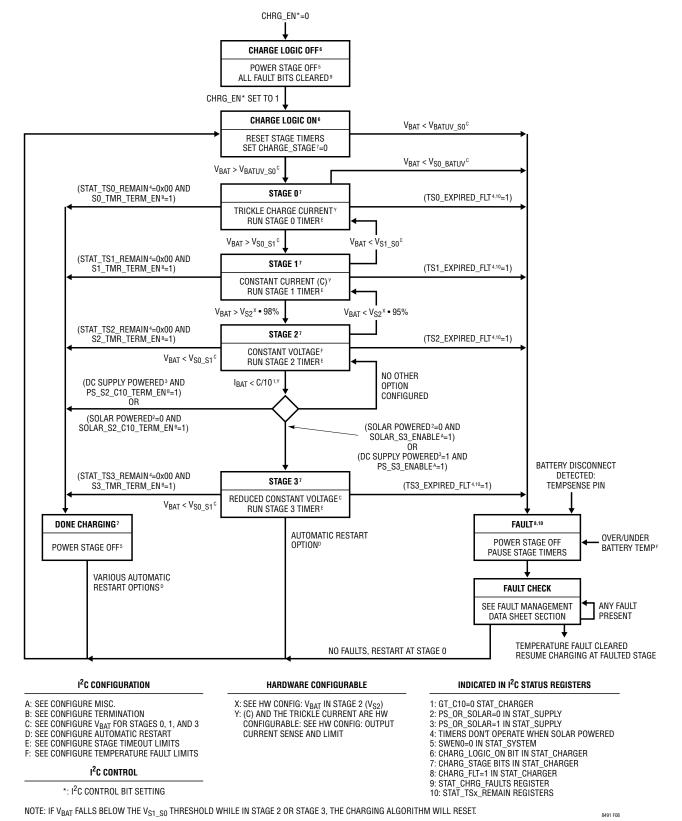

Figure 8 illustrates a flow chart for the charging algorithm. Many options are available to configure the algorithm as needed. Options include...

- · Stage 3 is enabled or not

- Stop charging when  $I_{OUT} < C/10$  or not

- · Timer expiration indicates a fault or not

- Various automatic restart options

Footnotes at the bottom of Figure 8 indicate configurable aspects of the algorithm and the related thresholds.

#### Stage 0: Trickle Charging

In Stage 0 the LT8491 charges the battery with a reduced constant current that is hardware configurable (see HW Config: Output Current Sense and Limit section). This stage typically occurs for battery voltages between 35% to 70% of the Stage 2 battery voltage limit ( $V_{S2}$ ). However, the Stage 0 battery thresholds are I<sup>2</sup>C configurable as discussed in the Configure  $V_{BAT}$  for Stages 0, 1 and 3 section. Stage 0 charging is indicated in the STAT\_CHARGER register when the CHRG\_STAGE bits are 000b and the CHRG\_LOGIC\_ON bit is 1.