# $100V\ V_{IN}$ and $V_{OUT}$ Synchronous 4-Switch Buck-Boost DC/DC Controller with Pass-Thru

## **FEATURES**

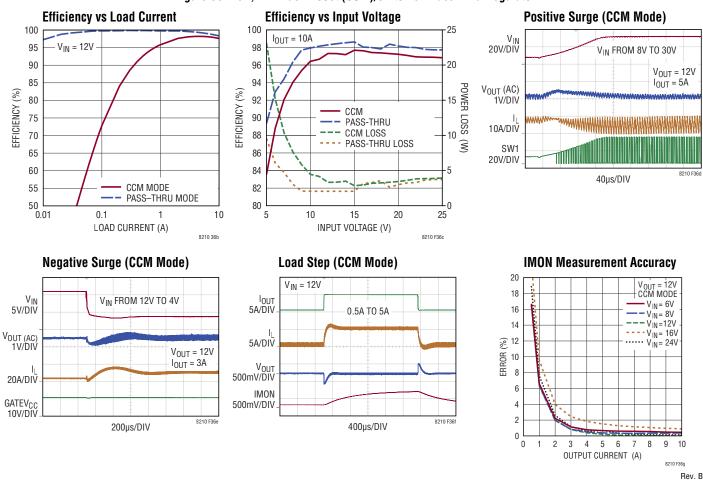

- Pin-Selectable Pass-Thru or Fixed Output CCM, DCM, Burst Mode® Operation

- Programmable Non-Switching Pass-Thru Window

- 18µA Pass-Thru Mode I<sub>0</sub> with 99.9% Efficiency

- V<sub>IN</sub> Range: 2.8V to 100V (4.5V for Start-Up)

- V<sub>OUT</sub> Range: 1V to 100V

- Reverse Input Protection to -40V

- ±1.25% Output Voltage Accuracy (-40°C to 125°C)

- ±3% Accurate Current Monitoring

- ±5% Accurate Current Regulation

- 10V Quad N-Channel MOSFET Gate Drivers

- EXTV<sub>CC</sub> LDO Powers Drivers from V<sub>OUT</sub>/External Rail

- ±20% Cycle-by-Cycle Inductor Current Limit

- No Top MOSFET Refresh Noise in Buck or Boost

- Fixed/Phase-Lockable Frequency: 80kHz to 400kHz

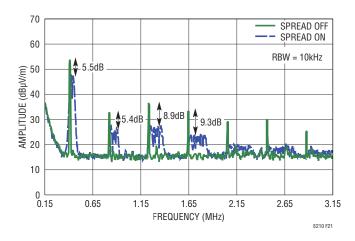

- Spread Spectrum Frequency Modulation for Low EMI

- Power Good Output Voltage/Overcurrent Monitor

- Available in a 38-Lead TSSOP and 40-Lead (6mm x 6mm) QFN Packages

## **APPLICATIONS**

- Automotive, Industrial, Telecom, Avionics Systems

- Automotive Start-Stop, Emergency Call Applications

- ISO 7637, ISO 16750, MIL-1275, DO-160 Applications

#### DESCRIPTION

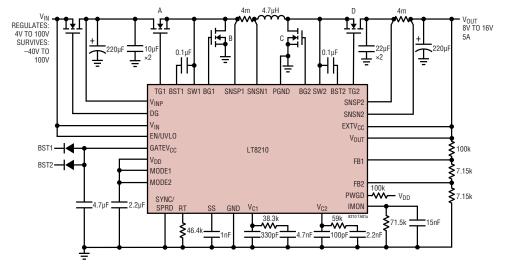

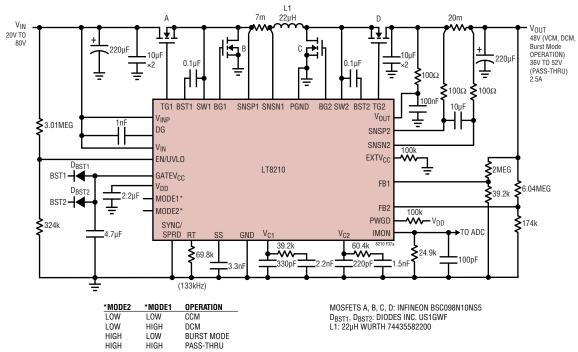

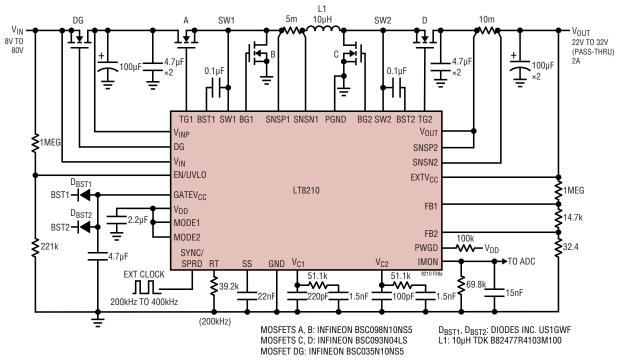

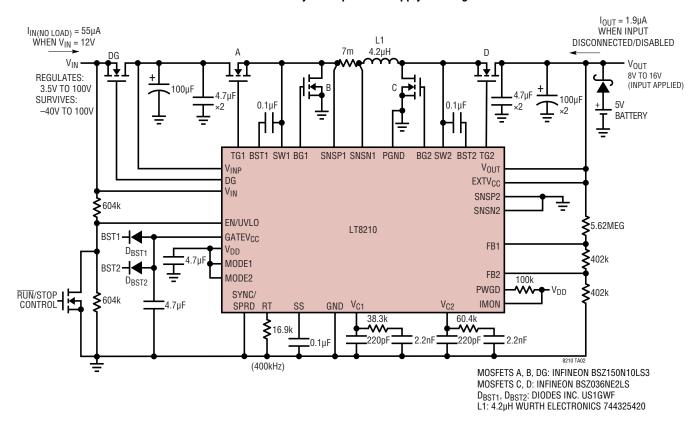

The LT®8210 is a 4-switch synchronous buck-boost DC/DC controller that can operate in pass-thru, forced continuous, pulse-skipping and Burst Mode® operation. Pass-Thru is a feature that passes the input directly to the output when the input is within a user programmable window. Pass-Thru mode eliminates switching losses and EMI along with maximizing efficiency. For input voltages above or below the pass-thru window, the buck or boost regulation loops maintain the output at the set maximum or minimum values, respectively.

The GATEV $_{CC}$  driver supply is regulated to 10.6V allowing the use of standard-level MOSFETs and can be powered through the EXTV $_{CC}$  pin for improved efficiency. The GATEV $_{CC}$  regulator is back-drive-protected to ride through input brownouts while maintaining regulation. Optional reverse input protection down to -40V can be implemented with the addition of a single N-channel MOSFET. The LT8210 includes a precision current sense amplifier that can accurately monitor and limit output or input average current.

All registered trademarks and trademarks are the property of their respective owners. Protected by U.S. patents, including 10135340.

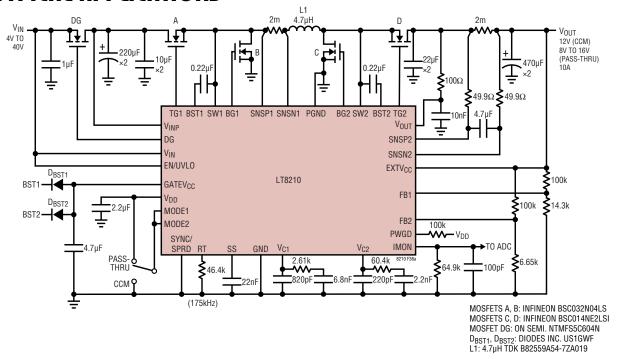

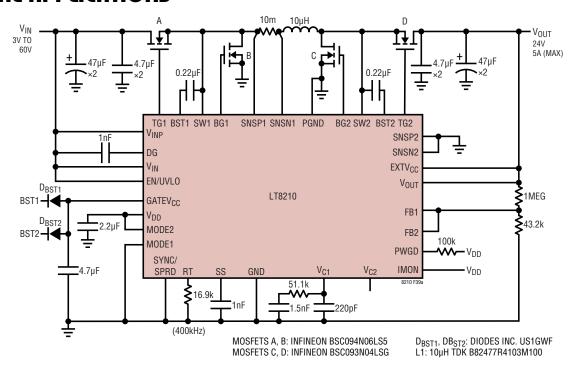

## TYPICAL APPLICATION

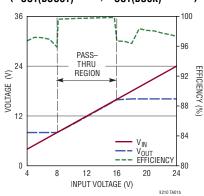

## Pass-Thru Transfer Characteristic (V<sub>OUT(BUCK)</sub> = 8V, V<sub>OUT(BUCK)</sub> = 16V)

Rev. B

1

## LT8210

## TABLE OF CONTENTS

| Features                                                        | 1  |

|-----------------------------------------------------------------|----|

| Applications                                                    | 1  |

| Typical Application                                             | 1  |

| Description                                                     |    |

| Table of Contents                                               |    |

| Absolute Maximum Ratings                                        |    |

| Pin Configuration                                               |    |

| Order Information                                               |    |

| Electrical Characteristics                                      |    |

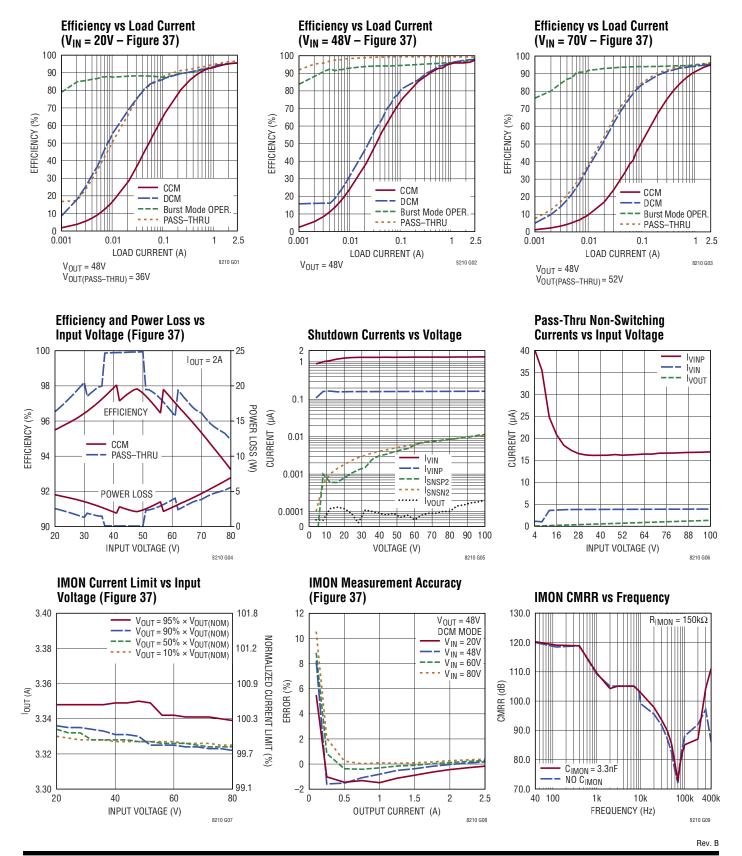

| Typical Performance Characteristics                             |    |

| Pin Functions                                                   |    |

| Block Diagram                                                   |    |

| Operation                                                       |    |

| Overview                                                        |    |

| Continuous Conduction Mode (CCM)                                |    |

| Discontinuous Conduction Mode (DCM)                             |    |

| Burst Mode Operation                                            |    |

| Pass-Thru Mode                                                  |    |

|                                                                 | 10 |

| Power Switch Control (CCM, DCM, Burst                           | 10 |

| Mode Operation)                                                 | 10 |

| Power Switch Control: Buck Region                               | 47 |

| (V <sub>INP</sub> > 1.19 • V <sub>OUT</sub> )                   | 17 |

| Power Switch Control: Boost Region                              |    |

| (V <sub>INP</sub> < 0.84 • V <sub>OUT</sub> )                   | 17 |

| Power Switch Control: Buck-Boost Region                         |    |

| $(0.84 \bullet V_{OUT} < V_{INP} < 1.19 \bullet V_{OUT}) \dots$ |    |

| Power Switch Control (Pass-Thru Mode)                           |    |

| Transitioning Between Operating Modes                           |    |

| Enable and Start-Up                                             | 19 |

| EXTVcc/GATEVcc/Vnn Power Supplies                               | 19 |

|    | Reverse input Protection                                      | . 20 |

|----|---------------------------------------------------------------|------|

|    | Current Monitoring and Regulation                             | . 20 |

|    | Buck Foldback                                                 |      |

|    | Bootstrap Capacitor Voltage                                   | . 21 |

|    | PWGD Pin                                                      | .22  |

| ۱p | plications Information                                        |      |

|    | Maximum Output Current and $R_{\text{SENSE}}$ Selection       | . 23 |

|    | Inductor Selection                                            | . 24 |

|    | Switching Frequency Selection                                 | . 25 |

|    | RT Set Switching Frequency                                    |      |

|    | Frequency Synchronization                                     |      |

|    | Spread-Spectrum Frequency Modulation                          |      |

|    | Power MOSFET Selection                                        |      |

|    | C <sub>IN</sub> and C <sub>OUT</sub> Selection                |      |

|    | Bootstrap Capacitors (C <sub>BST1</sub> , C <sub>BST2</sub> ) |      |

|    | Bootstrap Diodes (D <sub>BST1</sub> , D <sub>BST2</sub> )     |      |

|    | EXTV <sub>CC</sub> , GATEV <sub>CC</sub> and V <sub>DD</sub>  | . 30 |

|    | Programming Output Voltage                                    | . 31 |

|    | Programming Input or Output Current Limit                     |      |

|    | Programming V <sub>IN</sub> UVLO                              |      |

|    | Soft-Start                                                    |      |

|    | Loop Compensation                                             |      |

|    | Optional DG MOSFET Selection                                  |      |

|    | Component Optimization for Pass-Thru Operation                |      |

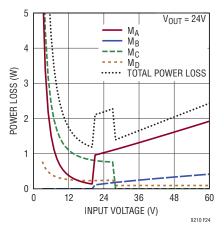

|    | Efficiency Considerations                                     |      |

|    | PC Board Layout Checklist                                     |      |

| •  | pical Applications                                            |      |

| 36 | evision History                                               | 45   |

| y  | pical Application                                             | 46   |

| ), | Noted Darte                                                   | 16   |

## **ABSOLUTE MAXIMUM RATINGS**

| ( | Note | 1) |

|---|------|----|

| ١ |      | -, |

| V <sub>IN</sub> , EN/UVLO Voltage                          | 40V to 100V   |

|------------------------------------------------------------|---------------|

| DG Voltage                                                 | 40V to 113V   |

| DG – V <sub>IN</sub> Voltage                               | 0.3V to 13V   |

| V <sub>INP</sub> , V <sub>OUT</sub> , SNSP2, SNSN2 Voltage | 0.3V to 100V  |

| SNSP1 – SNSN1, SNSP2 – SNSN2 Voltage.                      | 0.5V to 0.5V  |

| BST1, BST2 Voltage                                         | 0.3V to 115V  |

| SW1, SW2, SNSP1, SNSN1 Voltage                             | 100V (Note 5) |

| BST1 – SW1, BST2 – SW2 Voltage                             | 0.3V to 15V   |

| BST1 – SNSP1, BST1 – SNSN1 Voltage                         | 0.3V to 15V   |

| TG1, TG2, BG1, BG2                                         | (Note 3)      |

|                                                            |               |

| GATEV <sub>CC</sub> Voltage0.3V to 15                     | ۷  |

|-----------------------------------------------------------|----|

| EXTV <sub>CC</sub> , PWGD Voltage0.3V to 40               | V  |

| MODE1, MODE2, SYNC/SPRD Voltage0.3V to 6                  | ۷  |

| FB1, FB2, IMON, RT Voltage                                | ۷  |

| V <sub>DD</sub> –0.3V to 6                                | ۷  |

| $V_{C1}$ , $V_{C2}$ , SS Voltage–0.3V to $V_{DD}$ (Note ( | 6) |

| Operating Junction Temperature                            |    |

| LT8210E, LT8210I (Notes 2, 4) –40°C to 125°               | ,C |

| Storage Temperature Range                                 | Ċ  |

| Lead Temperature (Soldering, 10 sec)300°                  | C  |

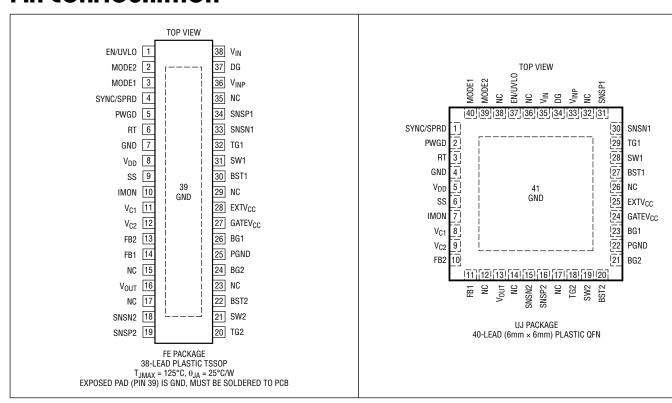

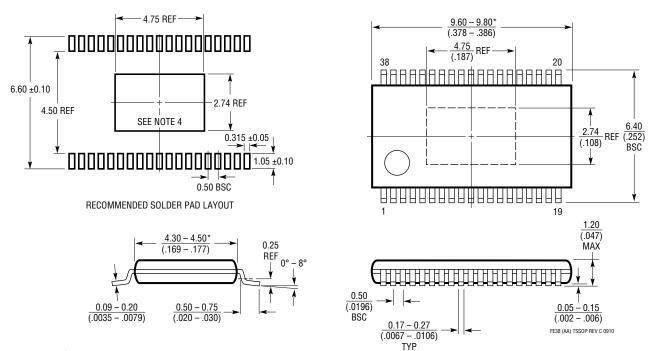

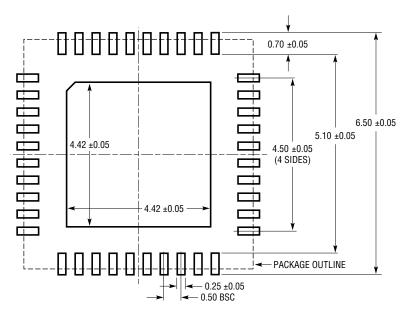

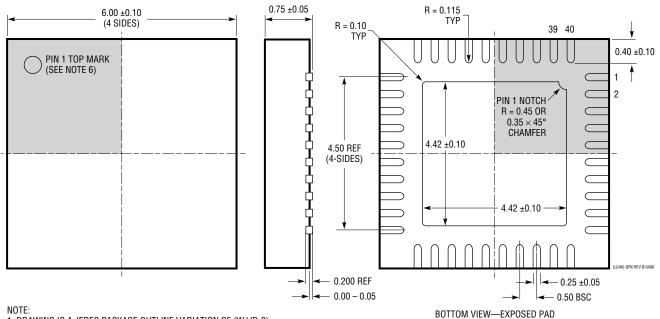

## PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL   | PART MARKING | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|-----------------|--------------|---------------------------------|-------------------|

| LT8210EFE#PBF    | LT8210EFE#TRPBF | LT8210FE     | 38-Lead Plastic TSSOP           | -40°C to 125°C    |

| LT8210IFE#PBF    | LT8210IFE#TRPBF | LT8210FE     | 38-Lead Plastic TSSOP           | -40°C to 125°C    |

| LT8210EUJ#PBF    | LT8210EUJ#TRPBF | 8210UJ       | 40-Lead (6mm x 6mm) Plastic QFN | -40°C to 125°C    |

| LT8210IUJ#PBF    | LT8210IUJ#TRPBF | 8210UJ       | 40-Lead (6mm x 6mm) Plastic QFN | -40°C to 125°C    |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25\,^{\circ}\text{C}$ . $V_{IN} = 12\text{V}$ , $V_{INP} = 12\text{V}$ , $V_{EN/UVL0} = 3.3\text{V}$

| PARAMETER                                                        | CONDITIONS                                                                                                                                                                                                                                                                          |   | MIN                  | TYP                            | MAX                             | UNITS                      |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------|--------------------------------|---------------------------------|----------------------------|

| Voltage Supplies and Regulators                                  |                                                                                                                                                                                                                                                                                     |   |                      |                                |                                 |                            |

| V <sub>IN</sub> , V <sub>INP</sub> Input Operating Voltage Range | Minimum Voltage for Start-Up (V <sub>EXTVCC</sub> = 0V)                                                                                                                                                                                                                             | • | 4.5                  |                                | 100                             | V                          |

|                                                                  | After Start-Up, V <sub>EXTVCC</sub> = 12V                                                                                                                                                                                                                                           | • | 2.8                  |                                | 100                             | ٧                          |

| V <sub>IN</sub> Quiescent Current                                | Shutdown (V <sub>EN/UVLO</sub> = 0V) Not Switching Internal Charge Pump Enabled (V <sub>DG</sub> - V <sub>IN</sub> = 3.5V)                                                                                                                                                          | • |                      | 1<br>4<br>1400                 | 5<br>15<br>1800                 | μΑ<br>μΑ<br>μΑ             |

| V <sub>INP</sub> Quiescent Current                               | Shutdown (V <sub>EN/UVLO</sub> = 0V) Not Switching Internal Charge Pump Enabled (V <sub>DG</sub> - V <sub>IN</sub> = 3.5V) Burst Mode Operation (Sleep) Pass-Thru (Non-Switching, V <sub>INP</sub> = 48V)                                                                           | • |                      | 0.1<br>650<br>1900<br>65<br>18 | 1.0<br>1300<br>2700<br>90<br>33 | Ац<br>Ац<br>Ац<br>Ац<br>Ац |

| V <sub>OUT</sub> Quiescent Current                               | V <sub>OUT</sub> = 12V                                                                                                                                                                                                                                                              | • |                      | 1.5                            | 3                               | μA                         |

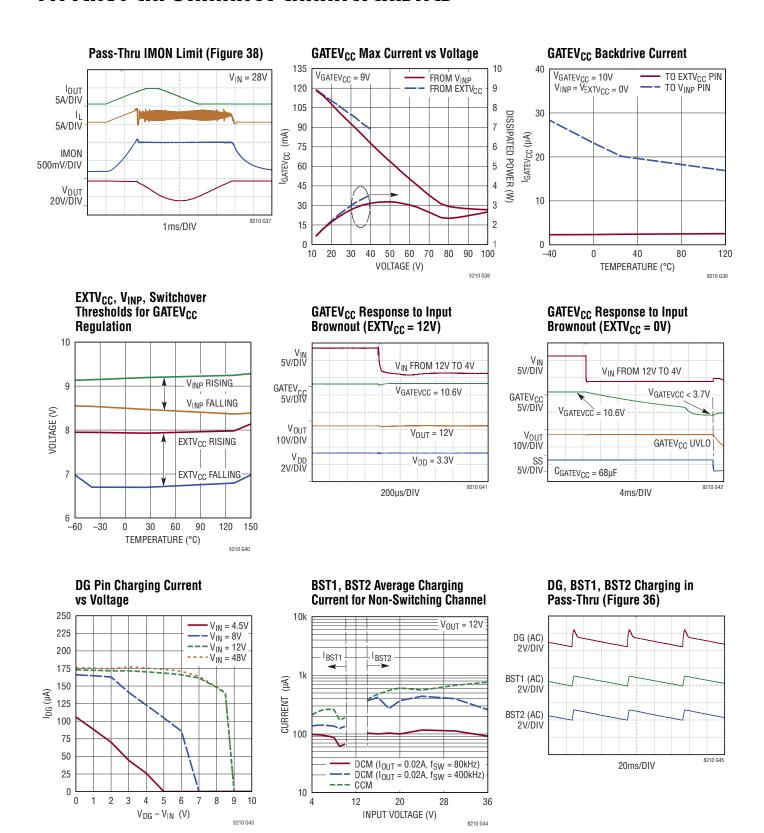

| GATEV <sub>CC</sub> Voltage                                      | I <sub>GATEVCC</sub> = 25mA                                                                                                                                                                                                                                                         | • | 10                   | 10.6                           | 11.2                            | V                          |

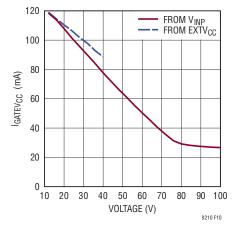

| GATEV <sub>CC</sub> Current Limit                                | Regulated from $V_{INP}$ , $V_{INP} = 12V$ , $V_{GATEVCC} = 9V$<br>Regulated from $V_{INP}$ , $V_{INP} = 100V$ , $V_{GATEVCC} = 9V$<br>Regulated from $EXTV_{CC}$ , $V_{EXTVCC} = 12V$ , $V_{GATEVCC} = 9V$<br>Regulated from $EXTV_{CC}$ , $V_{EXTVCC} = 40V$ , $V_{GATEVCC} = 9V$ | • | 65<br>18<br>80<br>55 | 110<br>25<br>115<br>90         |                                 | mA<br>mA<br>mA<br>mA       |

| GATEV <sub>CC</sub> Load Regulation                              | I <sub>GATEVCC</sub> = 0mA to 50mA                                                                                                                                                                                                                                                  | • |                      | 1.8                            | 5                               | %                          |

| GATEV <sub>CC</sub> Regulator Dropout Voltage                    | V <sub>INP</sub> - V <sub>GATEVCC</sub> : I <sub>GATEVCC</sub> = 50mA<br>V <sub>EXTVCC</sub> - V <sub>GATEVCC</sub> : I <sub>GATEVCC</sub> = 50mA                                                                                                                                   | • |                      | 750<br>600                     | 1600<br>1400                    | mV<br>mV                   |

| GATEV <sub>CC</sub> Undervoltage Lockout Threshold               | Falling                                                                                                                                                                                                                                                                             | • | 3.65                 | 3.75                           | 3.85                            | V                          |

| GATEV <sub>CC</sub> Undervoltage Lockout Hysteresis              |                                                                                                                                                                                                                                                                                     |   |                      | 0.20                           |                                 | V                          |

| GATEV <sub>CC</sub> Backdrive Current                            | To V <sub>INP</sub> Pin, V <sub>GATEVCC</sub> = 10V, V <sub>INP</sub> = 0V<br>To EXTV <sub>CC</sub> Pin, V <sub>GATEVCC</sub> = 10V, V <sub>EXTVCC</sub> = 0V                                                                                                                       |   |                      | 20<br>3                        |                                 | μA<br>μA                   |

| EXTV <sub>CC</sub> Switchover Voltage                            | Rising                                                                                                                                                                                                                                                                              | • | 7.3                  | 8                              | 8.8                             | V                          |

| EXTV <sub>CC</sub> Switchover Hysteresis                         |                                                                                                                                                                                                                                                                                     |   |                      | 1.2                            |                                 | V                          |

| V <sub>DD</sub> Voltage                                          |                                                                                                                                                                                                                                                                                     | • | 3.2                  | 3.3                            | 3.4                             | V                          |

| V <sub>DD</sub> Current Limit                                    | $V_{DD} = 3V$                                                                                                                                                                                                                                                                       |   | 10                   |                                |                                 | mA                         |

| V <sub>DD</sub> Undervoltage Lockout Threshold                   | Falling                                                                                                                                                                                                                                                                             | • | 2.7                  | 2.8                            | 2.9                             | V                          |

| V <sub>DD</sub> Undervoltage Lockout Hysteresis                  |                                                                                                                                                                                                                                                                                     |   |                      | 140                            |                                 | mV                         |

| Enable Comparator                                                |                                                                                                                                                                                                                                                                                     |   |                      |                                |                                 |                            |

| EN/UVLO Enable Threshold                                         | Rising                                                                                                                                                                                                                                                                              | • | 1.28                 | 1.45                           | 1.61                            | V                          |

| EN/UVLO Enable Hysteresis                                        |                                                                                                                                                                                                                                                                                     |   |                      | 100                            |                                 | mV                         |

| EN/UVLO Pin Bias Current                                         | V <sub>EN/UVLO</sub> = 100V                                                                                                                                                                                                                                                         | • |                      | 0.08                           | 0.3                             | μA                         |

| Reverse Input Protection                                         |                                                                                                                                                                                                                                                                                     |   |                      |                                |                                 |                            |

| DG Gate Drive Voltage (V <sub>DG</sub> – V <sub>IN</sub> )       | Non-Switching                                                                                                                                                                                                                                                                       | • | 7.0                  | 8.5                            |                                 | V                          |

| Reverse Input Disconnect Threshold (V <sub>IN</sub> )            | I <sub>DG</sub> = 100 μA                                                                                                                                                                                                                                                            | • | -1.8                 | -1.2                           | -0.5                            | ٧                          |

| DG Pin Pull-Down Current                                         | $V_{IN} = -4V$ , $V_{DG} - V_{IN} = 5V$                                                                                                                                                                                                                                             | • | 50                   | 80                             | 130                             | mA                         |

| DG Pin Pull-Up Current                                           | $V_{DG} - V_{IN} = 1.5V$<br>$V_{DG} - V_{IN} = 8.5V$                                                                                                                                                                                                                                | • | 100<br>5             | 180<br>25                      |                                 | μA<br>μA                   |

| DG Undervoltage Threshold (V <sub>DG</sub> – V <sub>IN</sub> )   | Rising                                                                                                                                                                                                                                                                              | • | 2.3                  | 2.8                            | 3                               | V                          |

| DG Undervoltage Hysteresis (V <sub>DG</sub> – V <sub>IN</sub> )  |                                                                                                                                                                                                                                                                                     |   |                      | 700                            |                                 | mV                         |

| Voltage Regulation                                               |                                                                                                                                                                                                                                                                                     |   |                      |                                |                                 |                            |

| FB1 Regulation Voltage                                           | Regulation Voltage for CCM, DCM, Burst Mode Operation, Pass-Thru Mode Boost Loop                                                                                                                                                                                                    | • | 0.9875               | 1.00                           | 1.0125                          | V                          |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25\,^{\circ}\text{C}$ . $V_{IN} = 12\text{V}$ , $V_{INP} = 12\text{V}$ , $V_{EN/UVL0} = 3.3\text{V}$

| PARAMETER                                                                                                | CONDITIONS                                                                                                                                                                                                                                                                       |   | MIN                        | TYP                        | MAX                        | UNITS                |

|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------------|----------------------------|----------------------------|----------------------|

| FB2 Regulation Voltage                                                                                   | Regulation Voltage Pass-Thru Mode Buck Loop                                                                                                                                                                                                                                      | • | 0.985                      | 1.00                       | 1.015                      | V                    |

| FB1, FB2 Input Bias Current                                                                              |                                                                                                                                                                                                                                                                                  | • |                            | 0.001                      | 0.04                       | μA                   |

| FB1, FB2 Line Regulation                                                                                 | V <sub>INP</sub> = 3V to 100V                                                                                                                                                                                                                                                    | • |                            | 0.001                      | 0.007                      | %/V                  |

| FB1, FB2 Error Amplifier Transconductance                                                                |                                                                                                                                                                                                                                                                                  |   |                            | 450                        |                            | μA/V                 |

| V <sub>C1</sub> , V <sub>C2</sub> Output Impedance                                                       |                                                                                                                                                                                                                                                                                  |   |                            | 5                          |                            | MΩ                   |

| V <sub>C1</sub> , V <sub>C2</sub> Maximum Sourcing Current                                               | $V_{FB1} = V_{FB2} = 0V$                                                                                                                                                                                                                                                         |   |                            | 35                         |                            | μА                   |

| V <sub>C1</sub> , V <sub>C2</sub> Maximum Sinking Current                                                | $V_{FB1} = V_{FB2} = 2V$                                                                                                                                                                                                                                                         |   |                            | -35                        |                            | μА                   |

| Soft-Start Charging Current                                                                              | V <sub>SS</sub> = 0.5V                                                                                                                                                                                                                                                           | • | 4                          | 5                          | 6                          | μА                   |

| Soft-Start Pull-Down Resistance                                                                          |                                                                                                                                                                                                                                                                                  | • |                            | 140                        | 250                        | Ω                    |

| Average Current Monitoring and Regulation                                                                |                                                                                                                                                                                                                                                                                  |   |                            |                            |                            |                      |

| SNSP2, SNSN2 Operating Voltage Range                                                                     |                                                                                                                                                                                                                                                                                  | • | 0                          |                            | 100                        | ٧                    |

| SNSP2, SNSN2 Pin Bias Current                                                                            | V <sub>SNSP2</sub> = V <sub>SNSN2</sub> = 100V<br>V <sub>SNSP2</sub> = V <sub>SNSN2</sub> = 0V                                                                                                                                                                                   | • | -3                         | 1<br>0                     | 3                          | μΑ<br>μΑ             |

| IMON Output Current<br>Common Mode Voltage = 12V                                                         | V <sub>SNSP2</sub> - V <sub>SNSN2</sub> = 150mV<br>V <sub>SNSP2</sub> - V <sub>SNSN2</sub> = 50mV<br>V <sub>SNSP2</sub> - V <sub>SNSN2</sub> = 10mV                                                                                                                              | • | 87.3<br>28.6<br>5.1        | 90<br>30<br>6              | 92.7<br>31.4<br>6.6        | μΑ<br>μΑ<br>μΑ       |

| IMON Output Current<br>Common Mode Voltage = 0V                                                          | V <sub>SNSP2</sub> - V <sub>SNSN2</sub> = 150mV<br>V <sub>SNSP2</sub> - V <sub>SNSN2</sub> = 50mV<br>V <sub>SNSP2</sub> - V <sub>SNSN2</sub> = 10mV                                                                                                                              | • | 85<br>27<br>4              | 90.5<br>30<br>6            | 95<br>33<br>8.5            | μΑ<br>μΑ<br>μΑ       |

| Common Mode Switchover Voltage                                                                           | V <sub>SNSP2</sub> = V <sub>SNSN2</sub>                                                                                                                                                                                                                                          |   |                            | 1.8                        |                            | V                    |

| IMON DC CMRR                                                                                             | V <sub>SNSP2</sub> – V <sub>SNSN2</sub> = 150mV, V <sub>SNSP2</sub> = 3V to 100V                                                                                                                                                                                                 |   |                            | 120                        |                            | dB                   |

| IMON Error Amplifier Transconductance                                                                    |                                                                                                                                                                                                                                                                                  |   |                            | 200                        |                            | μA/V                 |

| IMON Regulation Voltage (V <sub>IMON</sub> )                                                             |                                                                                                                                                                                                                                                                                  | • | 0.98                       | 1.01                       | 1.03                       | V                    |

| Sense Regulation Voltage (V <sub>SNSP2</sub> – V <sub>SNSN2</sub> )                                      | R <sub>IMON</sub> = 33.2k                                                                                                                                                                                                                                                        | • | 48                         | 50.5                       | 53                         | mV                   |

| Over-Current Warning Threshold (V <sub>IMON</sub> )                                                      | Rising                                                                                                                                                                                                                                                                           | • | 1.15                       | 1.2                        | 1.24                       | V                    |

| Over-Current Warning Hysteresis                                                                          |                                                                                                                                                                                                                                                                                  |   |                            | 45                         |                            | mV                   |

| IMON Disable Threshold (V <sub>IMON</sub> )                                                              | Rising                                                                                                                                                                                                                                                                           | • | 2.3                        | 2.5                        | 2.8                        | V                    |

| IMON Disable Hysteresis                                                                                  |                                                                                                                                                                                                                                                                                  |   |                            | 400                        |                            | mV                   |

| Cycle-by-Cycle Inductor Current Limiting                                                                 |                                                                                                                                                                                                                                                                                  |   |                            |                            |                            |                      |

| Maximum Current Sense Threshold (V <sub>SNSP1</sub> – V <sub>SNSN1</sub> )                               | Buck Regulation ( $V_{INP}$ = 24V, $V_{OUT}$ = 0V)<br>Buck Regulation ( $V_{INP}$ = 24V, $V_{OUT}$ = 12V)<br>Boost Regulation ( $V_{INP}$ = 6V, $V_{OUT}$ = 12V)<br>Buck Regulation ( $V_{INP}$ = 100V, $V_{OUT}$ = 48V)<br>Boost Regulation ( $V_{INP}$ = 24V, $V_{OUT}$ = 48V) | • | 45<br>55<br>45<br>73<br>36 | 53<br>62<br>51<br>85<br>45 | 60<br>69<br>58<br>96<br>54 | mV<br>mV<br>mV<br>mV |

| Maximum Non-Switching Current Sense<br>Threshold in Pass-Thru (V <sub>SNSP1</sub> – V <sub>SNSN1</sub> ) | V <sub>OUT</sub> = V <sub>INP</sub> , FB1 = 1.2V, FB2 = 0.8V<br>MODE1 = MODE2 = 3.3V                                                                                                                                                                                             | • | 57                         | 63                         | 70                         | mV                   |

| Reverse Current Sense Threshold (V <sub>SNSP1</sub> – V <sub>SNSN1</sub> )                               | DCM/Pass-Thru/Burst Mode Operation<br>Pass-Thru Buck-Boost Regions                                                                                                                                                                                                               |   |                            | 3<br>-6                    |                            | mV<br>mV             |

| Negative Current Sense Threshold (V <sub>SNSP1</sub> – V <sub>SNSN1</sub> )                              | CCM Operating Mode (MODE1 = MODE2 = 0V)                                                                                                                                                                                                                                          |   |                            | -55                        |                            | mV                   |

| MOSFET Gate Drivers                                                                                      |                                                                                                                                                                                                                                                                                  |   |                            |                            |                            |                      |

| TG1, TG2 Gate Driver Pull-Up Resistance                                                                  |                                                                                                                                                                                                                                                                                  |   |                            | 3                          |                            | Ω                    |

| TG1, TG2 Gate Driver Pull-Down Resistance                                                                |                                                                                                                                                                                                                                                                                  |   |                            | 1                          |                            | Ω                    |

| BG1, BG2 Gate Driver Pull-Up Resistance                                                                  |                                                                                                                                                                                                                                                                                  |   |                            | 2.6                        |                            | Ω                    |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25 \,^{\circ}\text{C}$ . $V_{IN} = 12 \,^{\circ}\text{V}$ , $V_{EN/UVLO} = 3.3 \,^{\circ}\text{V}$

| PARAMETER                                              | CONDITIONS                                                                                                                         |   | MIN              | TYP               | MAX               | UNITS             |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---|------------------|-------------------|-------------------|-------------------|

| BG1, BG2 Gate Driver Pull-Down Resistance              |                                                                                                                                    |   |                  | 1                 |                   | Ω                 |

| TG1, TG2 Rise Time                                     | C <sub>LOAD</sub> = 3300pF (10% to 90%)                                                                                            |   |                  | 25                |                   | ns                |

| TG1, TG2 Fall Time                                     | C <sub>LOAD</sub> = 3300pF (10% to 90%)                                                                                            |   |                  | 15                |                   | ns                |

| BG1, BG2 Rise Time                                     | C <sub>LOAD</sub> = 3300pF (10% to 90%)                                                                                            |   |                  | 20                |                   | ns                |

| BG1, BG2 Fall Time                                     | C <sub>LOAD</sub> = 3300pF (10% to 90%)                                                                                            |   |                  | 15                |                   | ns                |

| TG Off to BG On-Delay                                  | C <sub>LOAD</sub> = 3300pF                                                                                                         |   |                  | 60                |                   | ns                |

| BG Off to TG On-Delay                                  | C <sub>LOAD</sub> = 3300pF                                                                                                         |   |                  | 60                |                   | ns                |

| Minimum TG1 On-Time                                    | C <sub>LOAD</sub> = 3300pF                                                                                                         |   |                  | 200               |                   | ns                |

| Minimum BG2 On-Time                                    | C <sub>LOAD</sub> = 3300pF                                                                                                         |   |                  | 220               |                   | ns                |

| BST1, BST2 Bias Current                                | Top Gate High, V <sub>BST</sub> – V <sub>SW</sub> = 10V<br>Top Gate High, V <sub>BST</sub> – V <sub>SW</sub> = 10V, Pass-Thru Mode |   |                  | 5<br>0.6          |                   | μA<br>μA          |

| BST1, BST2 Charging Current                            | Non-Switching, V <sub>BST</sub> – V <sub>SW</sub> = 8.25V<br>Non-Switching, V <sub>BST</sub> – V <sub>SW</sub> = 3V                |   |                  | 50<br>610         |                   | μA<br>μA          |

| Oscillator                                             |                                                                                                                                    |   |                  |                   |                   |                   |

| Switching Frequency Range                              | RT Set/Synchronized                                                                                                                | • | 80               |                   | 400               | kHz               |

| Switching Frequency                                    | RT = 110k<br>RT = 39.2k<br>RT = 16.9k                                                                                              | • | 91<br>190<br>380 | 100<br>200<br>400 | 108<br>210<br>420 | kHz<br>kHz<br>kHz |

| SYNC/SPRD Input Low Level                              |                                                                                                                                    | • |                  |                   | 0.8               | V                 |

| SYNC/SPRD Input High Level                             |                                                                                                                                    | • | 1.17             |                   |                   | V                 |

| Spread-Spectrum Max. Frequency (% of f <sub>SW)</sub>  | V <sub>SYNC/SPRD</sub> = 3.3V                                                                                                      |   |                  | 112.5             |                   | %                 |

| Spread-Spectrum Min. Frequency (% of f <sub>SW</sub> ) | V <sub>SYNC/SPRD</sub> = 3.3V                                                                                                      |   |                  | 100               |                   | %                 |

| Logic Inputs/Outputs                                   |                                                                                                                                    |   |                  |                   |                   |                   |

| MODE1,2 Input Low Level                                |                                                                                                                                    | • |                  |                   | 0.8               | V                 |

| MODE1,2 Input High Level                               |                                                                                                                                    | • | 1.17             |                   |                   | V                 |

| MODE1,2 Leakage Current                                | V <sub>MODE1,2</sub> = 6 V                                                                                                         |   |                  | 0.01              | 1                 | μA                |

| PWGD Output Low Voltage                                | I <sub>PWGD</sub> = 1mA                                                                                                            | • |                  | 0.07              | 0.2               | V                 |

| PWGD Trip Level                                        | V <sub>FB1</sub> Falling<br>V <sub>FB2</sub> Rising                                                                                | • | -13<br>8         | –10<br>10         | -8<br>12          | %<br>%            |

| PWGD Anti-Glitch Delay                                 | V <sub>PWGD</sub> Rising or Falling                                                                                                | • | 2                | 10                | 20                | μs                |

| PWGD Leakage Current                                   | V <sub>PWGD</sub> = 40V                                                                                                            |   |                  | 0.01              | 1                 | μА                |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LT8210E is guaranteed to meet performance specifications from 0°C to 125°C junction temperature. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LT8210I is guaranteed over the full -40°C to 125°C junction temperature range.

**Note 3:** Do not apply a voltage or current source to these pins. They must be connected to capacitive loads only, otherwise permanent damage may occur.

**Note 4:** This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed the maximum operating junction temperature when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature range may impair the device reliability.

**Note 5:** Negative voltages on the SW1, SW2, SNSP1 and SNSN1 pins are limited, in an application, by the body diodes of the external NMOS devices,  $M_B$  and  $M_C$ , or parallel Schottky diodes when present. These pins are tolerant of these negative voltages in excess of one diode drop below ground, guaranteed by design.

Note 6: Do not force voltage on the  $V_{C1},\,V_{C2},\,$  or SS pin.

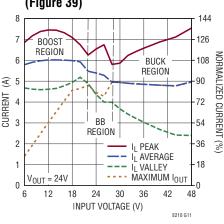

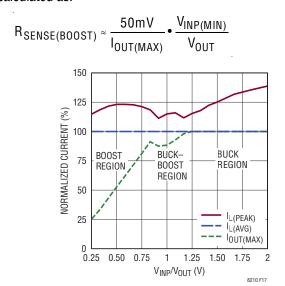

**Maximum Inductor Current:**  $f_{SW} = f_{SW(Optimal)}$ (Figure 39) BOOST BUCK REGION REGION

NORMALIZED CURRENT (% 108 90 € 5 CURRENT REGION 3 36 2 PEAK AVERAGE 18 VALLEY MAXIMUM I<sub>OUT</sub> V<sub>OUT</sub> = 24V 0 12 18 24 30 36 42 48 INPUT VOLTAGE (V)

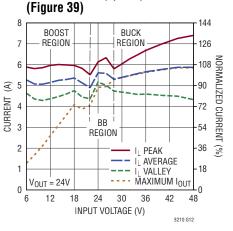

**Maximum Inductor Current:**  $f_{SW} = 0.7 \times f_{SW(Optimal)}$ (Figure 39)

**Maximum Inductor Current:**  $f_{SW} = 1.3 \times f_{SW(Optimal)}$

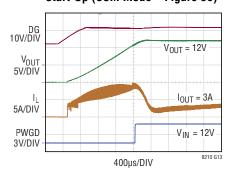

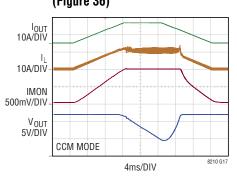

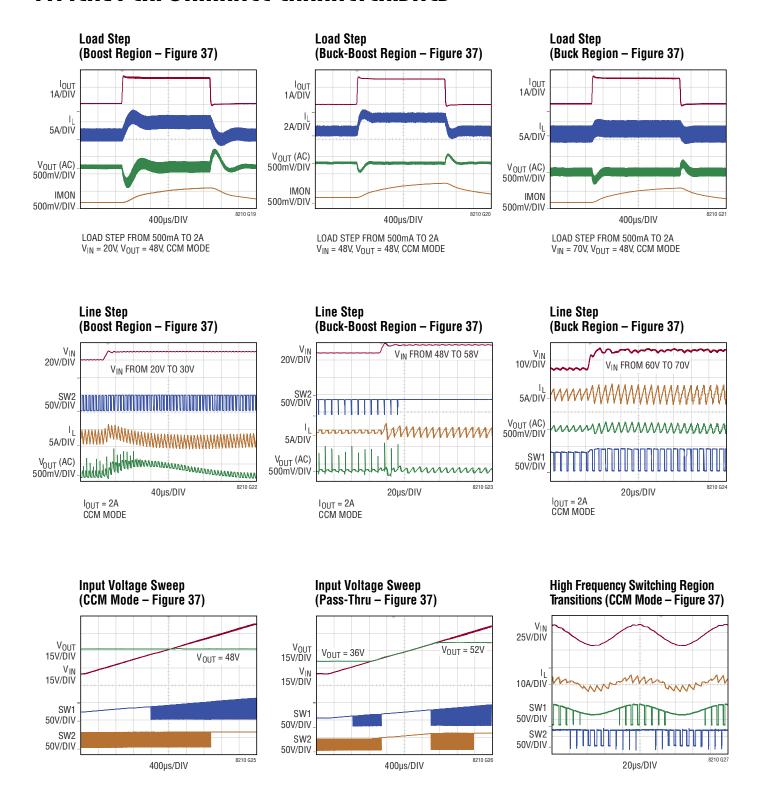

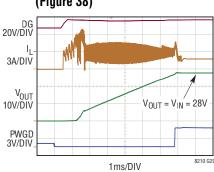

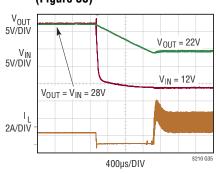

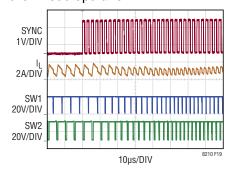

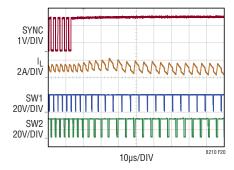

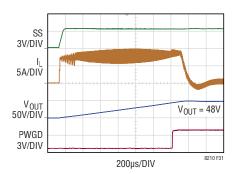

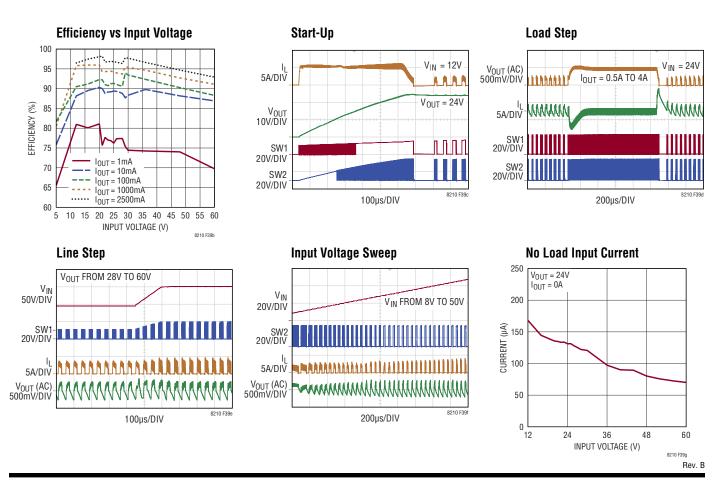

Start-Up (CCM Mode - Figure 36)

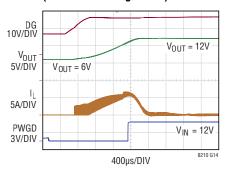

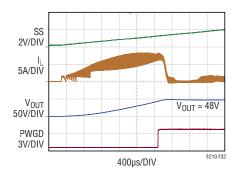

Pre-Biased Output Start-Up (CCM Mode - Figure 36)

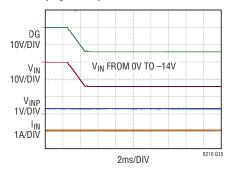

**Static Reverse Input Protection** (Figure 36)

**Dynamic Reverse Input Protection** (Figure 36)

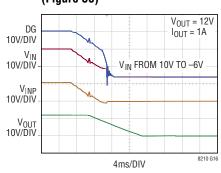

**Transition to Current Regulation** (Figure 36)

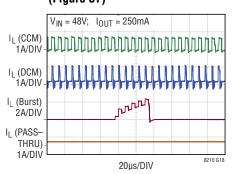

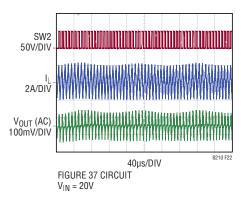

**Inductor Current at Light Load** (Figure 37)

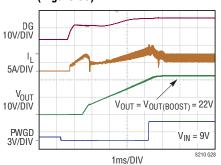

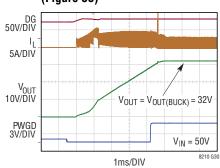

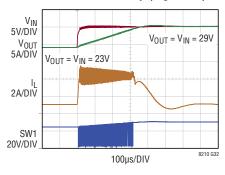

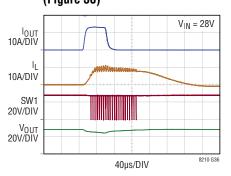

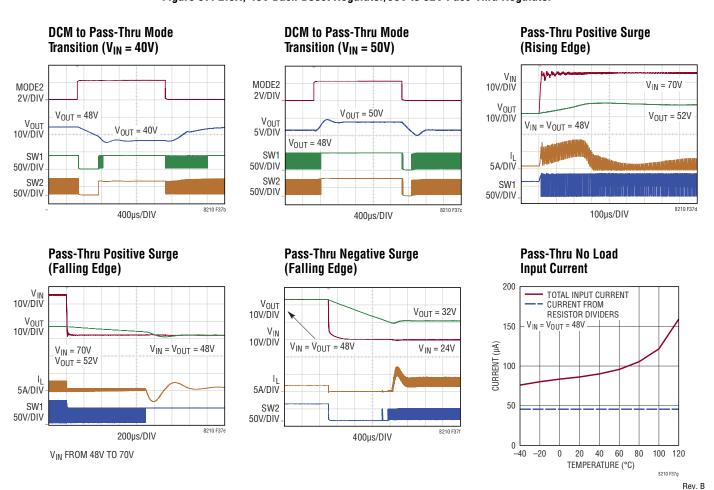

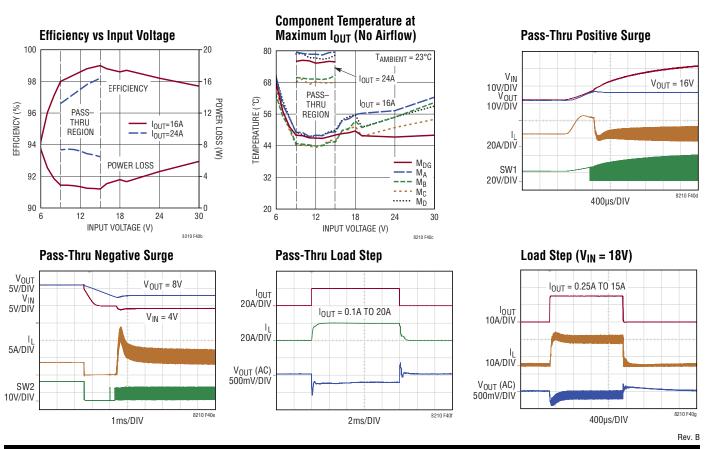

Pass-Thru Start-Up: V<sub>IN</sub> Below Pass-Thru Window (Figure 38)

Pass-Thru Start-Up: V<sub>IN</sub> in Pass-Thru Window (Figure 38)

Pass-Thru Start-Up: V<sub>IN</sub> Above Pass-Thru Window (Figure 38)

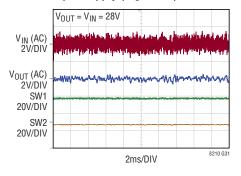

Pass-Thru Regulation with Noisy Input Supply (Figure 38)

Pass-Thru Line Step (Figure 38)

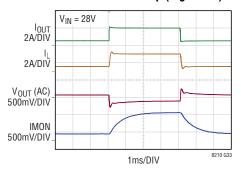

Pass-Thru Load Step (Figure 38)

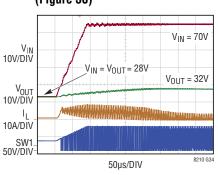

Pass-Thru Positive Surge (Figure 38)

Pass-Thru Negative Surge (Figure 38)

Pass-Thru Current Limit (Figure 38)

## PIN FUNCTIONS (TSSOP/QFN)

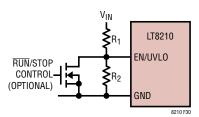

**EN/UVLO** (Pin 1/Pin 37): Precision Enable Input. The LT8210 is enabled when this pin is pulled above 1.45V. A voltage below 1.35V on this pin will cause the LT8210 to reside in a low-power shutdown mode. Tie to  $V_{IN}$  for always-on operation. Connect to a resistor divider between  $V_{IN}$  and ground to set an undervoltage lockout threshold. EN/UVLO can tolerate negative voltages to -40V.

**MODE2** (Pin 2/Pin 39): Operating Mode Selection Input #2. Used in conjunction with MODE1 pin to select between continuous conduction switching (CCM), discontinuous switching (DCM), Burst Mode operation, and pass-thru operating modes. Refer to Table 1 in the Operation section for operating mode pin settings.

**MODE1** (Pin 3/Pin 40): Operating Mode Selection Input #1. Used in conjunction with MODE2 pin to select between continuous conduction switching (CCM), discontinuous switching (DCM), Burst Mode operation, and pass-thru operating modes. Refer to Table 1 in the Operation section for operating mode pin settings.

**SYNC/SPRD (Pin 4/Pin 1):** External Clock Synchronization Input. For external sync apply a clock signal between 80kHz and 400kHz to this pin. An internal PLL will synchronize the oscillator to the external clock signal. Connect this pin to the  $V_{DD}$  pin to enable spread spectrum operation on the RT set switching frequency, otherwise connect to ground.

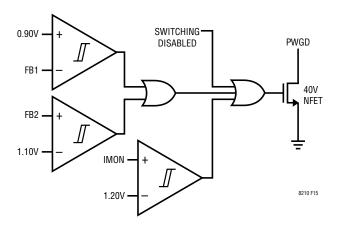

**PWGD** (Pin 5/Pin 2): Power Good Indicator. Open-drain logic output which is pulled to ground when the output voltage is outside  $\pm 10\%$  of its programmed value or the IMON pin voltage is greater than 1.20V. This pin can be connected to any voltage rail up to 40V through a pull-up resistor. Using either  $V_{DD}$  or GATEV<sub>CC</sub> for the pull-up supply has the advantage that PWGD will be in the correct state when the part is disabled.

**RT (Pin 6/Pin 3):** Frequency Set Pin. Place a resistor from this pin to GND to set the switching frequency. The range of frequency adjustment is between 80kHz and 400kHz. Refer to Table 2 in Applications Information.

**GND** (Exposed Pad Pin 7/Pin 4): Signal Ground. All small-signal components and compensation components should connect to this ground, which in turn connects to the PCB ground at one location away from high currents and switching noise. The exposed pad must be soldered

to the PCB and connect to the GND pin using top layer metal.

$V_{DD}$  (Pin 8/Pin 5): Internally Regulated 3.3V Supply Rail. Bypass this pin to ground with a minimum of 2.2µF ceramic capacitor.  $V_{DD}$  can be used for tying MODE1, MODE2, and SYNC/SPRD pins logic high.

SS (Pin 9/Pin 6): Soft-Start Input. A capacitor to ground at this pin sets the ramp rate of the inductor current at start-up via internal clamping of the  $V_{C1}$  and  $V_{C2}$  voltages. The SS pin sources  $5\mu A$  once switching is enabled and is held at ground while switching is disabled.

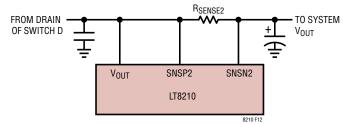

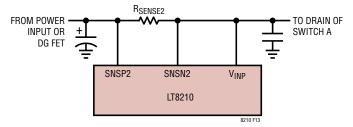

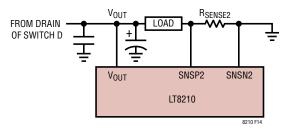

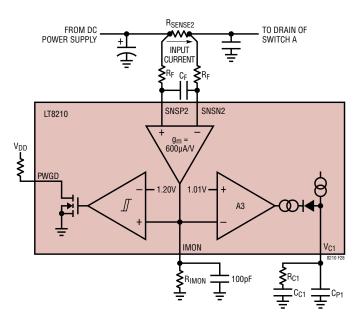

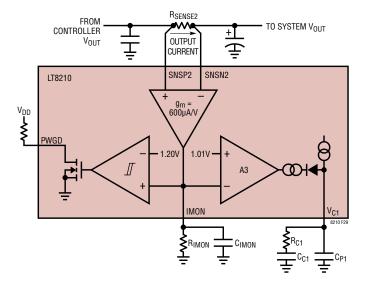

**IMON (Pin 10/Pin 7):** Current Monitor Output. The current sourced from this pin is proportional to the voltage difference between the SNSP2 and SNSN2 inputs. Place a resistor from the IMON pin to ground to set the average current limit. The loop will transition from voltage to current regulation when the voltage on IMON exceeds 1.01V.

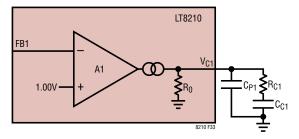

**V<sub>C1</sub>** (**Pin 11/Pin 8**): Error Amplifier Output and Switching Regulator Compensation Point for CCM, DCM and Burst Mode Operation. In pass-thru mode, this pin is the compensation point for the boost regulator loop. The current mode comparator trip point increases with this control voltage.

$V_{C2}$  (Pin 12/Pin 9): Error Amplifier Output and Switching Regulator Compensation Point for Buck Loop When in Pass-Thru Mode. The current mode comparator trip point increases with this control voltage. If pass-thru mode is not used leave  $V_{C2}$  floating.

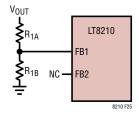

**FB2** (Pin 13/Pin 10): Error Amplifier Feedback Input for Buck Regulation Loop When in Pass-Thru Mode. Receives the feedback voltage for the buck controller from an external resistive divider across the output. If pass-thru mode is not used leave this pin floating.

**FB1 (Pin 14/Pin 11):** Error Amplifier Feedback Input for CCM, DCM, Burst Operation Modes. Feedback input for boost regulation loop in pass-thru mode. Receives the feedback voltage from an external resistive divider across the output.

**V<sub>OUT</sub>** (**Pin 16/Pin 13**): Output Voltage Sense. This pin must have a Kelvin connection to the drain of switch D.

## PIN FUNCTIONS (TSSOP/QFN)

Use a small RC low-pass filter (e.g.,  $50\Omega$  and 22nF) for improved jitter performance when  $V_{OUT}$  ripple is large.

SNSP2, SNSN2 (Pins 19,18/Pins 16,15): Positive (+) and Negative (-) Inputs for the Average Current Sense Monitor. SNSP2, SNSN2 should connect to the positive and negative terminals of a sense resistor placed in series with the input, output or load. A current linearly proportional to difference in voltage between the SNSP2 and SNSN2 pins is sourced from the IMON pin and can be used for current monitoring and limiting with the selection of the  $R_{IMON}$  resistor.

**TG2** (Pin 20/Pin 18): Top Gate Drive for Boost Regulator. Drives top N-channel MOSFET with a voltage swing equal to  $GATEV_{CC}$  superimposed onto the SW2 node voltage. When operating in the buck region or within the pass-thru window TG2 is held roughly at  $V_{OUT}$  +  $GATEV_{CC}$ .

**SW2 (Pin 21/Pin 19):** Boost Regulator Switch Node. The (–) terminal of the bootstrap capacitor connects here.

**BST2** (**Pin 22/Pin 20**): Boosted Floating Driver Supply for Boost Regulator. The (+) terminal of the bootstrap capacitor connects here. The BST2 pin swings from roughly GATEV<sub>CC</sub> to  $V_{OUT}$  + GATEV<sub>CC</sub> when the boost regulation loop is switching. When operating in the buck region or the within pass-thru window this pin is held roughly at  $V_{OUT}$  + GATEV<sub>CC</sub>.

**BG2** (Pin 24/Pin 21): Bottom Gate Drive for Boost Regulator. Drives bottom N-channel MOSFET with a voltage swing between GATEV<sub>CC</sub> and PGND.

**PGND (Pin 25/Pin 22):** Driver Power Ground. Connect to  $C_{IN}$ ,  $C_{OLIT}$  and sources of MOSFETs,  $M_C$  and  $M_D$ .

**BG1 (Pin 26/Pin 23):** Bottom Gate Drive for Buck Regulator. Drives bottom N-channel MOSFET with a voltage swing between GATEV<sub>CC</sub> and PGND.

**GATEV<sub>CC</sub> (Pin 27/Pin 24):** Power Supply for Gate Drivers. Internally regulated to 10.6V. Bypass this pin to ground with a minimum 4.7µF ceramic capacitor.

**EXTV**<sub>CC</sub> (Pin 28/Pin 25): External Power Supply Input for the GATEV<sub>CC</sub> Regulator. GATEV<sub>CC</sub> will be linearly regulated from EXTV<sub>CC</sub> if its voltage is higher than 8V and is simultaneously lower than  $V_{INP}$ . May be driven with voltages

up to 40V. If this feature is not used, connect this pin to ground through a 100k resistor.

**BST1** (Pin 30/Pin 27): Boosted Floating Driver Supply for Buck Regulator. The (+) terminal of the bootstrap capacitor connects here. The BST1 pin swings from roughly GATEV $_{CC}$  to  $V_{IN}$  + GATEV $_{CC}$  when the buck regulation loop is switching. When operating in the boost region or within the pass-thru window this pin is held roughly at  $V_{IN}$  + GATEV $_{CC}$ .

**SW1 (Pin 31/Pin 28):** Buck Regulator Switch Node. The (–) terminal of the bootstrap capacitor connects here.

**TG1** (Pin 32/Pin 29): Top Gate Drive for Buck Regulator. Drives top N-channel MOSFET with a voltage swing equal to  $GATEV_{CC}$  superimposed onto the SW1 node voltage. When operating in the boost region or within the pass-thru window TG1 pin is held roughly at  $V_{IN}$  +  $GATEV_{CC}$  continuously.

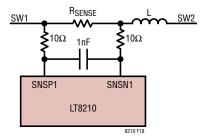

SNSP1, SNSN1 (Pins 34, 33/Pin 31,30): Positive (+) and Negative (-) Inputs for the Inductor Current Sense Amplifier. Place an appropriately valued shunt resistor in series with the inductor on the SW1 side and connect to SNSP1 and SNSN1. The SNSP1 – SNSN1 voltage is used for current mode control and reverse current detection.

$V_{INP}$  (Pin 36/Pin 33): Protected Main Input Supply. This pin must connect to the drain terminal of switch A. Use a small RC low-pass filter (e.g.,  $1\Omega$  and  $1\mu$ F) for improved jitter performance. When reverse input protection is implemented connect this pin to the drain of the DG MOSFET, otherwise connect to  $V_{IN}$ .

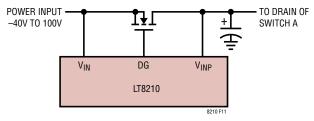

**DG** (**Pin 37/Pin 34**): Reverse Input Protection Gate Drive Output. When  $V_{IN}$  is pulled below -1.2V, this pin is clamped internally to  $V_{IN}$  with a low resistance switch forcing an external MOSFET between the  $V_{IN}$  and  $V_{INP}$  pins into cutoff. In normal operation, this pin is charged to roughly  $V_{IN}$  + GATEV<sub>CC</sub> with an internal charge pump to fully enhance the external MOSFET. DG can tolerate negative voltages down to -40V.

$V_{IN}$  (Pin 38/Pin 35): Input Voltage Pin. This pin is used for powering start-up circuitry and the internal charge pump.  $V_{IN}$  can withstand negative voltages down to -40V without damaging the regulator or drawing large currents.

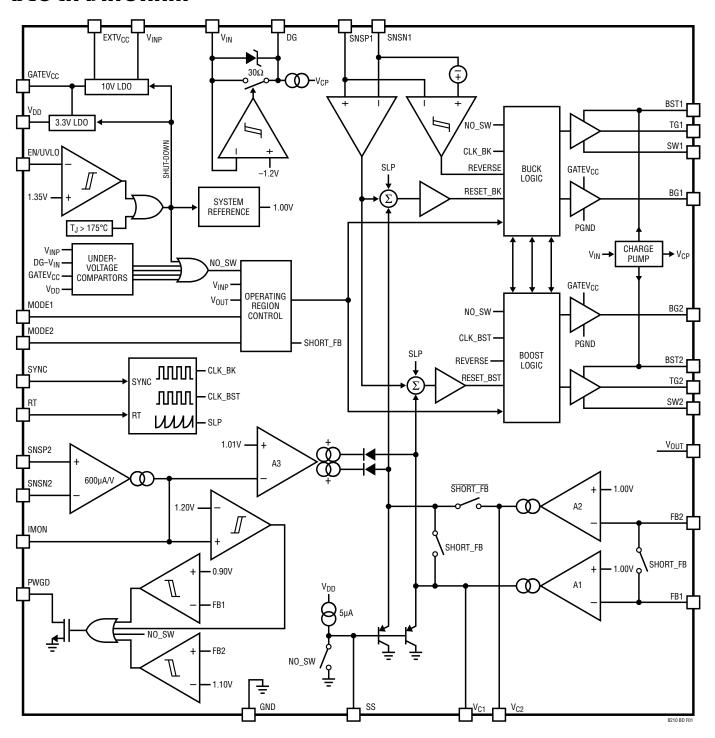

## **BLOCK DIAGRAM**

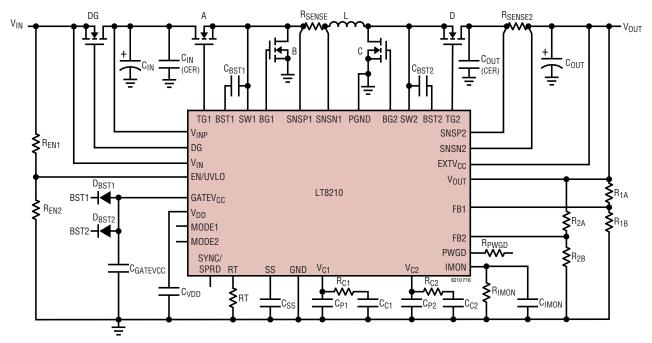

Figure 1. Block Diagram

Refer to the Block Diagram (Figure 1) when reading the following sections about the operation of the LT8210.

#### Overview

The LT8210 has four different operating modes that can be selected by setting the MODE1 and MODE2 pins either high (>1.17V) or low (<0.80V). The threshold voltage of the MODE1 and MODE2 pins allow them to be driven with 1.8V, 2.5V, 3.3V or 5V logic levels for dynamic control. If the operating mode is fixed, tie MODE1 and MODE 2 pins to  $V_{DD}$  to set high or to ground to set low.

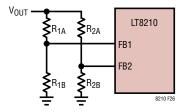

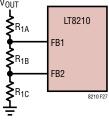

Table 1 shows the operating mode corresponding to the various MODE1, MODE2 pin combinations. In continuous conduction mode (CCM), discontinuous conduction mode (DCM) and Burst Mode operation, the LT8210 operates as a conventional buck-boost controller with the output regulated to a voltage set by the resistive divider between  $V_{OUT}$ , FB1 and GND. In pass-thru mode the output voltage is regulated to a window defined by a minimum and maximum value programmed using the FB1 and FB2 resistor dividers, respectively.

Table 1. LT8210 Operating Modes

| MODE2 | MODE1 | OPERATING MODE                      |  |  |

|-------|-------|-------------------------------------|--|--|

| LOW   | LOW   | Continuous Conduction Mode (CCM)    |  |  |

| LOW   | HIGH  | Discontinuous Conduction Mode (DCM) |  |  |

| HIGH  | LOW   | Burst Mode Operation                |  |  |

| HIGH  | HIGH  | Pass-Thru Mode                      |  |  |

#### **Continuous Conduction Mode (CCM)**

Continuous conduction mode allows the inductor current to reverse directions once the voltage at the SS pin has exceeded 2.5V (typical). This precaution is intended to prevent large negative inductor currents during start-up when the output is pre-biased to a non-zero voltage. Once CCM mode is enabled, a negative current sense limit with a magnitude roughly equal to the positive current sense limit sets the lower bound on the inductor current. This ensures that the inductor current is limited on a cycle-by-cycle basis whether the direction of current flow is forward or reverse. The maximum recommended switching frequency for CCM operation is 350kHz.

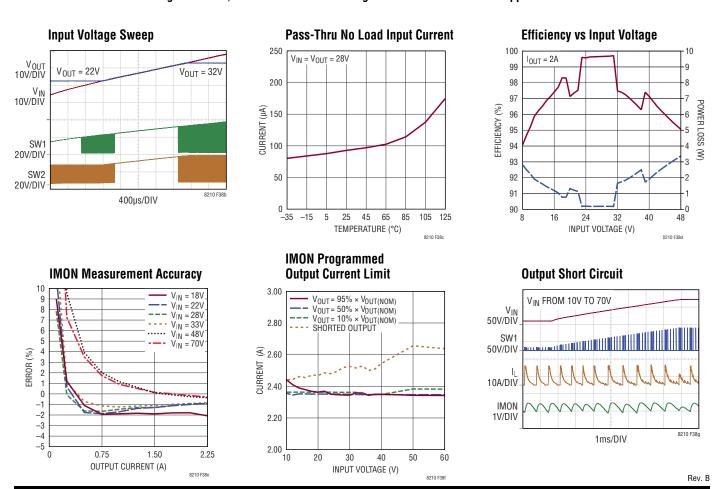

### **Discontinuous Conduction Mode (DCM)**

Discontinuous conduction mode prevents the inductor current from reversing direction at low output currents. DCM operation improves light load efficiency and also blocks significant current draw from the output back into the input. Reverse current is detected when the SNSP1 – SNSN1 voltage drops below its reverse current threshold (typically 3mV) while either switch B or D is conducting. When operating in either the buck or buck-boost regions, the on-time of switch B is ended upon reverse current detection. Similarly, in the boost and buck-boost regions the on-time of switch D is ended when reverse inductor current is detected. At very light loads the LT8210 may be forced to skip multiple switching pulses to maintain output voltage regulation in DCM. This situation arises when the average inductor current exceeds the load current even while switching at duty cycle limits. If pulse-skipping behavior is undesired it may be possible to resolve by increasing the size of the inductor or reducing the switching frequency. Otherwise, the LT8210 can be operated in CCM for full switching frequency operation.

## **Burst Mode Operation**

Burst Mode operation sets a  $V_{C1}$  level, with approximately 25mV of hysteresis, below which switching activity is inhibited and above which switching activity is re-enabled. A typical example is when, at light output currents,  $V_{OUT}$  rises and forces the  $V_{C1}$  pin below the threshold that temporarily inhibits switching. After  $V_{OUT}$  drops slightly and  $V_{C1}$  rises ~25mV, the switching is resumed. Burst Mode operation can increase efficiency at light load currents by eliminating unnecessary switching activity and related power losses. The LT8210 supply current drops to 65 $\mu$ A (typical) in the non-switching state to maximize light load efficiency. Burst Mode operation inhibits reverse inductor current in the same manner as DCM mode.

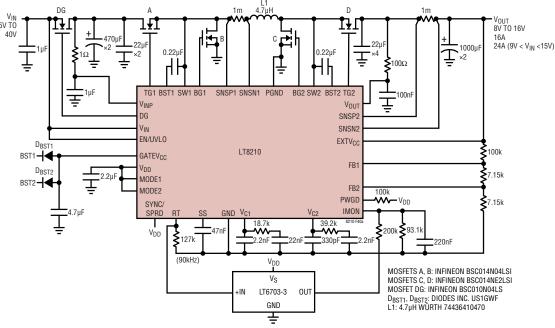

#### **Pass-Thru Mode**

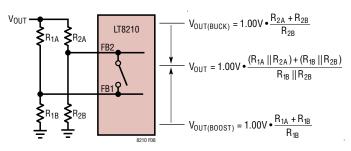

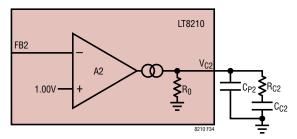

In pass-thru mode, the respective output voltages for the buck and boost loops,  $V_{OUT(BUCK)}$  and  $V_{OUT(BOOST)}$ , are programmed independently. The output voltage is regulated to a window defined by a minimum at  $V_{OUT(BUCK)}$  and a maximum at  $V_{OUT(BUCK)}$ .  $V_{OUT(BUCK)}$  is set with a

resistive divider between V<sub>OUT</sub>, FB2 and GND. The FB2 voltage is compared with the 1.00V system reference and the resulting output of amplifier A2,  $V_{C2}$ , controls the inductor current when the buck loop is active. Similarly,  $V_{OUT(BOOST)}$  is set with a resistive divider between  $V_{OUT}$ , FB1 and GND. The voltage on FB1 is compared with the 1.00V system reference using amplifier A1 and resulting output on the  $V_{C1}$  pin controls the inductor current when the boost loop is active. The boost loop will control the inductor current and regulate the output to V<sub>OUT(BOOST)</sub> when V<sub>INP</sub> is less than or equal to V<sub>OUT(BOOST)</sub>. Likewise, when the input voltage is greater than or equal to V<sub>OUT(BUCK)</sub> the buck loop will control the inductor current and regulate the output to V<sub>OUT(BUCK)</sub>. Near the boundaries of the pass-thru window interleaved buckboost switching is used to avoid pulse-skipping. When the input voltage lies between  $V_{OUT(BOOST)}$  and  $V_{OUT(BUCK)}$ , both top switches will turn on continuously once  $V_{OUT}$ has settled close in value to  $V_{INP}$  In this state,  $V_{OUT}$  follows V<sub>INP</sub> and the LT8210 enters a power saving mode with typical quiescent currents on the  $V_{IN}$  and  $V_{INP}$  pins of 4µA, 18µA, respectively. Switching will recommence if the SNSP1 – SNSN1 voltage exceeds 63mV (typical) to limit the maximum inductor current. Similarly, if a current regulation loop is implemented, switching will resume when the IMON pin voltage approaches 1.01V. With no switching losses and extremely low quiescent current, it is possible to achieve efficiencies greater than 99.9% in the pass-thru region.

# Power Switch Control (CCM, DCM, Burst Mode Operation)

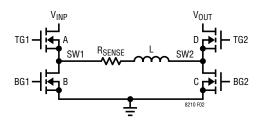

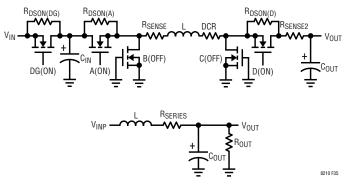

The LT8210 is a current mode buck-boost controller that regulates the output voltage above, equal to or below the input voltage. The LTC® proprietary topology and control architecture employs a current-sensing resistor in series with the inductor that is used for current mode control and provides clean transitions between buck, buck-boost, and boost switching regions. When the LT8210 is configured

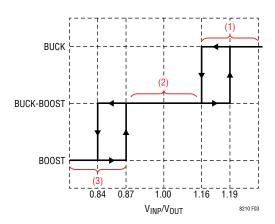

for CCM, DCM or Burst Mode operation, the inductor current is controlled by the voltage on the V<sub>C1</sub> pin. If a current regulation loop is implemented, then the V<sub>C1</sub> voltage will be controlled by either the sensed feedback voltage (FB1) or the sensed current when the IMON pin voltage approaches 1.01V. Figure 2 shows a simplified diagram of how the power switches A, B, C, D are connected to the inductor L, the current sense resistor R<sub>SENSE</sub>, the power input  $V_{\text{INP}}$ , power output  $V_{\text{OUT}}$ , and ground. Switches A and B form the synchronous buck power stage, while switches C and D form the synchronous boost power stage. The current sense resistor R<sub>SENSE</sub> is connected to the SNSP1 and SNSN1 pins and provides the inductor current information for both current mode control and reverse current detection. Figure 3 shows the switching region as a function of the V<sub>INP</sub>/V<sub>OUT</sub> ratio. The power switches are controlled to smoothly transition between switching regions with hysteresis added to prevent chattering between modes.

Figure 2. Simplified Diagram of the Power Switches

Figure 3. Switching Region vs V<sub>INP</sub>/V<sub>OUT</sub> Ratio

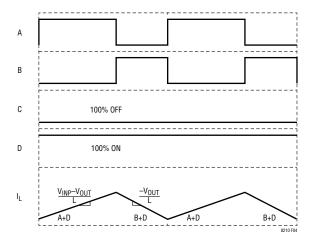

# Power Switch Control: Buck Region (V<sub>INP</sub> > 1.19 • V<sub>OUT</sub>)

When  $V_{INP}$  is greater than  $V_{OUT}$  by 19% (typical) or more, the part will run in the buck region. In the buck region, switch D is always on while switch C is always off. Switches A and B will toggle on and off acting as a synchronous buck regulator. If the inductor current should drop below the reverse current sense threshold in DCM or negative current sense threshold in CCM, switch B will be turned off for the remainder of the switching cycle, preventing the inductor current from falling any further.

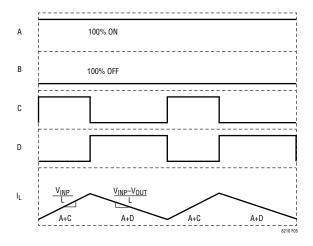

# Power Switch Control: Boost Region (V<sub>INP</sub> < 0.84 • V<sub>OLIT</sub>)

When  $V_{INP}$  is less than  $V_{OUT}$  by more than 16%, the part will run in the boost region. In this region, switch A is always on while switch B is always off. Switches C and D will toggle on and off acting as a synchronous boost regulator. The ontime of switch D will be terminated if the inductor current drops below the reverse current sense threshold in DCM or the negative current sense threshold in CCM.

# Power Switch Control: Buck-Boost Region $(0.84 \bullet V_{OUT} < V_{INP} < 1.19 \bullet V_{OUT})$

When  $V_{INP}$  is within -16% to +19% of  $V_{OUT}$ , the part operates in the buck-boost region where all four power switches (A, B, C, D) are active. The buck-boost region can be thought of as an over-lapping of the buck and boost control regions where the buck and boost regulation loops both control the inductor current. The sharing of inductor current control between the buck and boost loops avoids abrupt handoffs within the buck-boost region that can perturb the inductor current and output voltage. The ontime of switches B and D will be terminated if the inductor current drops below the reverse current sense threshold in DCM or the negative current sense threshold in CCM.

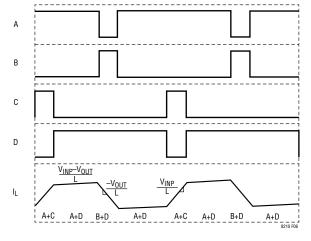

Figure 4. Buck Region Switching Waveforms

Figure 5. Boost Region Switching Waveforms

Figure 6. Buck-Boost Region Switching Waveforms

### Power Switch Control (Pass-Thru Mode)

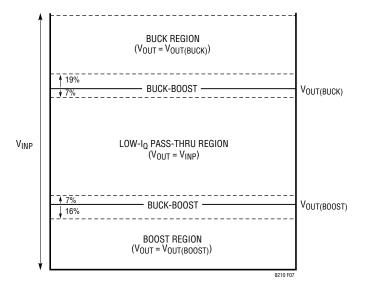

In pass-thru mode, the buck and boost regulation loops function independently after start-up. Separate error amps are used to create a pass-thru window by setting the programmed output voltage for the buck regulation,  $V_{OUT(BUCK)}$ , higher than the programmed output voltage for boost regulation,  $V_{OUT(BOOST)}$ . Figure 7 shows the different switching regions in pass-thru mode versus input voltage.

When V<sub>INP</sub> >> V<sub>OUT(BUCK)</sub>, the LT8210 will operate in the buck region. In this region switch D is always on while switch C is always off, switches A and B will toggle on and off, acting as a synchronous buck regulator, while maintaining the output at  $V_{OUT(BUCK)}$ . When  $V_{IN}$  is between 93% to 119% of V<sub>OUT(BUCK)</sub>, switch D will also begin switching to avoid the need for pulse skipping. Switch C will alternate with D in this region. When  $V_{INP} \ll V_{OUT(BOOST)}$  switch A is always on while switch B is always off, switches C and D toggle on and off acting as a synchronous boost requlator to maintain the output at  $V_{OUT(BOOST)}$ . When  $V_{IN}$  is between 84% to 107% of V<sub>OUT(BOOST)</sub>, switch A will also begin switching, alternating with switch B. When V<sub>INP</sub> is between  $V_{OUT(BOOST)}$  and  $V_{OUT(BUCK)}$ , the output voltage will track the input. Once  $V_{OUT}$  has settled close to  $V_{INP}$ , the LT8210 will enter a low power state where switches A and D are turned on continuously and switches B and C are off. In pass-thru mode reverse-current is handled

Figure 7. Pass-Thru Regions vs V<sub>INP</sub>

in a similar manner to DCM while switching. In the non-switching state reverse-current is detected through direct comparison of the  $V_{INP}$  and  $V_{OUT}$  voltages. If the voltage on  $V_{OUT}$  exceeds that on  $V_{INP}$  by a set percentage, switches A, C and D are turned off and the output is only reconnected after it has discharged to be nearly equal with  $V_{INP}$ . If a positive line transient occurs while in the non-switching pass-thru window causing  $V_{INP}$  to exceed  $V_{OUT}$  by a set percentage, switching will recommence to prevent large amplitude ringing in the inductor current. The output will be driven to the input voltage in a manner similar to soft-start and switches A and D will turn on continuously again after  $V_{OUT}$  settles close to  $V_{INP}$ .

#### **Transitioning Between Operating Modes**

It is possible to dynamically transition between passthru mode and CCM, DCM, or Burst Mode operation by toggling the MODE1 and/or MODE2 pins. While in CCM, DCM, or Burst Mode operation, the FB1 and FB2 pins are internally connected with a low resistance switch. In passthru mode, this switch is disabled after start-up allowing the feedback pins to move independently. When exiting pass-thru mode the FB1 and FB2 pins will once again be connected. By scaling the relative magnitudes of R<sub>2B</sub>, R<sub>2A</sub>, R<sub>1B</sub> and R<sub>1A</sub> resistors, the fixed output voltage in CCM, DCM, or Burst Mode operation can be placed at any desired voltage between the  $V_{OUT(BUCK)}$  and  $V_{OUT(BOOST)}$ voltages that define the top and bottom of the pass-thru window (Figure 8). Cycling into and out of pass-thru mode allows the user to exchange wider output voltage tolerance for no switching losses or noise as the conditions in the application change.

Figure 8. Output Voltage when Exiting Pass-Thru Mode

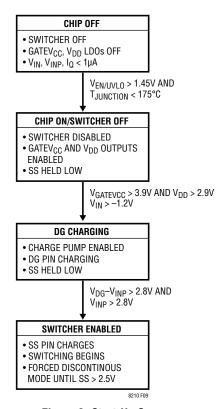

#### **Enable and Start-Up**

The LT8210 start-up sequence is shown in Figure 9.

When the voltage on the EN/UVLO pin is less than the turn on threshold (typically 1.45V), the LT8210 resides in a low power shutdown mode where the internal GATEV<sub>CC</sub> and V<sub>DD</sub> regulators are disabled and the quiescent current of the  $V_{IN}$  and  $V_{INP}$  pins drops to approximately 1µA. When the EN/UVLO voltage is pulled above 1.45V, the GATEV<sub>CC</sub> and V<sub>DD</sub> regulators are activated and are only disabled if the die temperature exceeds the internal thermal shutdown limit of 175°C. After both the GATEV<sub>CC</sub> and  $V_{DD}$  voltages have risen beyond their undervoltage lockout thresholds (typical values of 3.95V and 2.94V, respectively), the internal charge pump will begin sourcing current from the DG pin. When the DG to  $V_{\text{IN}}$  voltage has charged to greater than 2.8V (typical), the switching control logic is initialized. A brief delay allows analog circuitry to settle prior to start-up after which a 5µA current is sourced from the SS pin initiating the soft-start ramp and the LT8210 will begin switching. Connect EN/UVLO to V<sub>IN</sub> for always-on

Figure 9. Start-Up Sequence

operation or to a resistive divider between  $V_{IN}$  and ground to program an undervoltage lockout (UVLO) threshold.

#### EXTV<sub>CC</sub>/GATEV<sub>CC</sub>/V<sub>DD</sub> Power Supplies