# Six-Phase, Synchronous Bidirectional Buck or Boost Controller

# **FEATURES**

- Unique Architecture Allows Dynamic Regulation of Input Voltage, Output Voltage or Current

- Operates with External Gate Drivers and MOSFETs

- V<sub>HIGH</sub> Voltages Up to 100V; V<sub>LOW</sub> Voltages Up to 60V

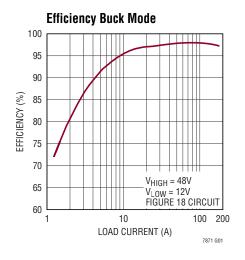

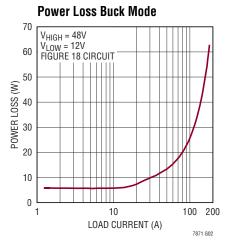

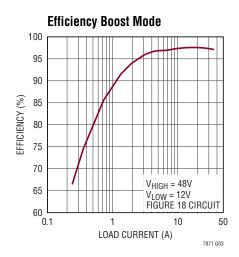

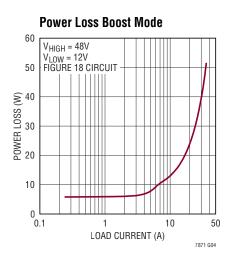

- Synchronous Rectification: Up to 98% Efficiency

- ADI-Proprietary Advanced Current Mode Control

- ±1% Voltage Regulation Accuracy Overtemperature

- Accurate, Programmable Inductor Current Monitoring and Bidirectional Regulation

- SPI Compliant Serial Interface

- Operation Status and Fault Report

- Programmable V<sub>HIGH</sub>, V<sub>LOW</sub> Margining

- Phase-Lockable Frequency: 60kHz to 750kHz

- Optional Spread Spectrum Modulation

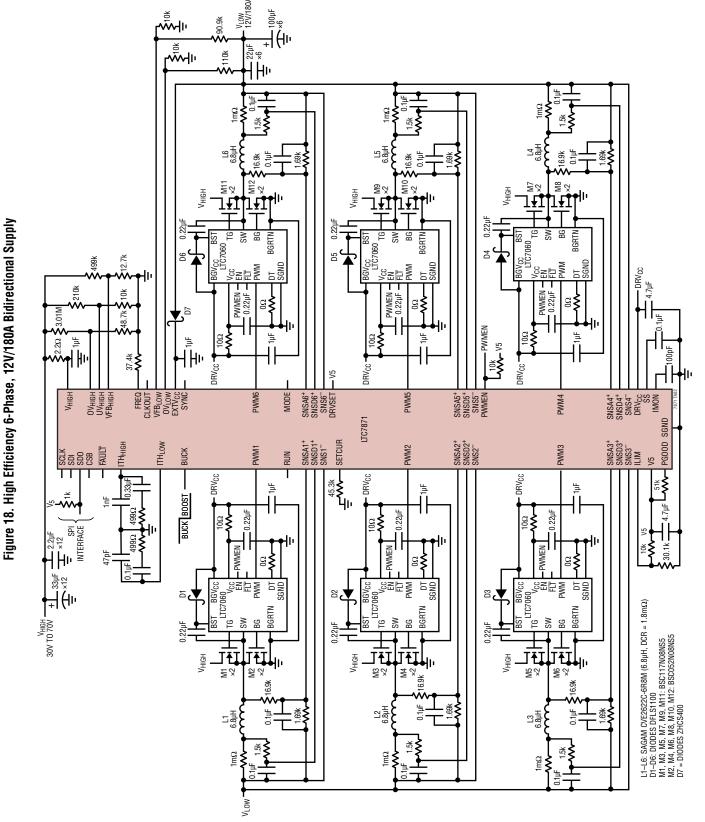

- Multiphase/Multi-ICs Operation Up to 24 Phases

- Selectable CCM/DCM/Burst Mode Operation

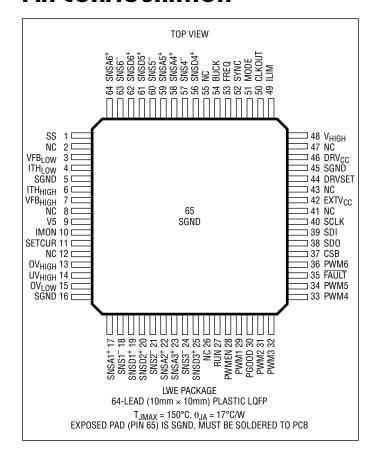

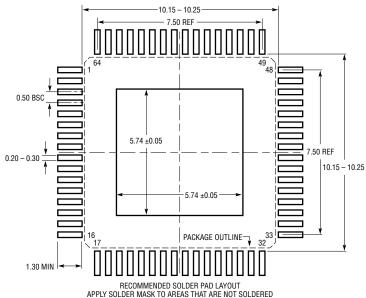

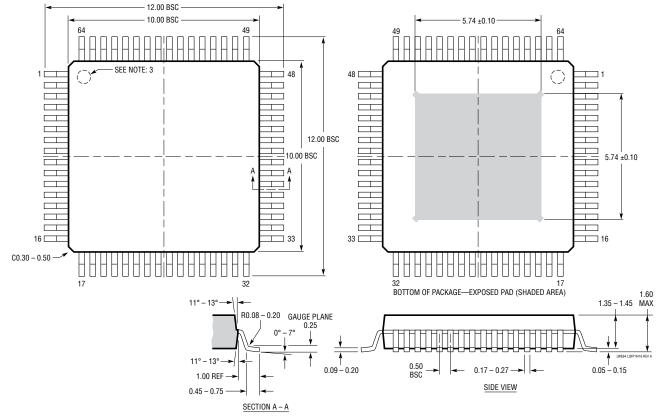

- Thermally Enhanced 64-Lead LQFP Package

- AEC-Q100 Qualification in Progress

# **APPLICATIONS**

- Automotive 48V/12V Dual Battery Systems

- Backup Power Systems

# DESCRIPTION

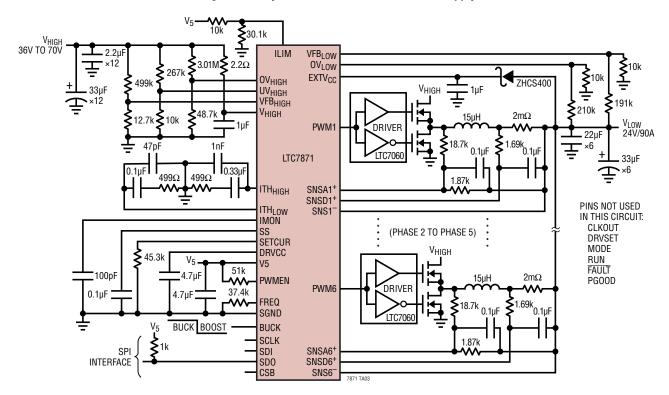

The LTC®7871 is a high performance bidirectional buck or boost switching regulator controller that operates in either buck or boost mode on demand. It regulates in buck mode from  $V_{HIGH}$ -to- $V_{LOW}$  and boost mode from  $V_{LOW}$ -to- $V_{HIGH}$  depending on a control signal, making it ideal for 48V/12V automotive dual battery systems. An accurate current programming loop regulates the maximum current that can be delivered in either direction. The LTC7871 allows both batteries to supply energy to the load simultaneously by driving energy from either battery to the other.

Its proprietary constant frequency current mode architecture enhances the signal-to-noise ratio enabling low noise operation and provides excellent current matching between phases. Additional features include an SPI-compliant serial interface, discontinuous or continuous mode of operation, OV/UV monitors, independent loop compensation for buck and boost operation, accurate inductor current monitoring and overcurrent protection.

The LTC7871 is available in a 64 pin  $10mm \times 10mm$  LWE package.

All registered trademarks and trademarks are the property of their respective owners.

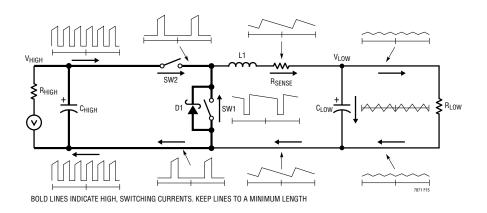

# TYPICAL APPLICATION

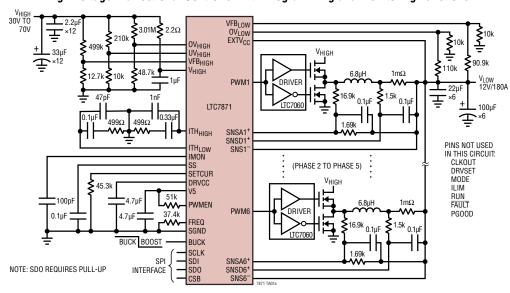

High Voltage Bidirectional Controller with Programming and Monitoring Functions

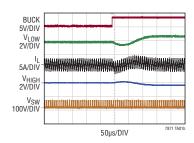

#### **Boost-to-Buck Transition**

Rev. A

1

# LTC7871

# TABLE OF CONTENTS

| Features                            |    |

|-------------------------------------|----|

| Applications                        |    |

| Typical Application                 |    |

| Description                         | _  |

| Absolute Maximum Ratings            |    |

| Order Information                   |    |

| Pin Configuration                   |    |

| Electrical Characteristics          | 4  |

| Typical Performance Characteristics |    |

| Pin Functions                       |    |

| Block Diagram                       |    |

| Operation                           |    |

| Applications Information            |    |

| Serial Port                         |    |

| Serial Port Register Details        | 35 |

| Typical Applications                | 47 |

| Package Description                 |    |

| Revision History                    |    |

| Typical Application                 |    |

| Related Parts                       | 50 |

# **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| -0.3V to 100V                                                                                    |

|--------------------------------------------------------------------------------------------------|

| V <sub>HIGH</sub> –0.3V to 100V                                                                  |

| Current Sense Voltages                                                                           |

| (SNSD+, SNSA+, SNS- Phase 1 to 6)0.3V to 60V                                                     |

| $(SNSA^+ - SNS^-)$ $-0.3V$ to $0.3V$                                                             |

| (SNSD+ – SNS-) –0.3V to 0.3V                                                                     |

| EXTV <sub>CC</sub> 0.3V to 60V                                                                   |

| DRV <sub>CC</sub> 0.3V to 11V                                                                    |

| RUN, OV <sub>HIGH</sub> , UV <sub>HIGH</sub> , OV <sub>LOW</sub> 0.3V to 6V                      |

| V50.3V to 6V                                                                                     |

| SCLK, SDI, SDO, CSB0.3V to 6V                                                                    |

| PWM1, PWM2, PWM3                                                                                 |

| PWM4, PWM5, PWM6, PWMEN0.3V to V5                                                                |

| ITH <sub>HIGH</sub> , ITH <sub>I OW</sub> , VFB <sub>HIGH</sub> , VFB <sub>I OW</sub> 0.3V to V5 |

| FAULT, SETCUR, DRVSET, PGOOD0.3V to V5                                                           |

| IMON, ILIM, SS, BUCK, MODE0.3V to V5                                                             |

| FREQ, SYNC, CLKOUT –0.3V to V5                                                                   |

| Operating Junction Temperature Range                                                             |

|                                                                                                  |

| (Notes 2, 3)                                                                                     |

| Storage Temperature Range –65°C to 150°C                                                         |

| DRV <sub>CC</sub> /EXTV <sub>CC</sub> Peak Current                                               |

| (Guarantee by Design)150mA                                                                       |

|                                                                                                  |

# PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH    | PART MARKING* | PACKAGE DESCRIPTION*               | TEMPERATURE RANGE |

|---------------------|---------------|------------------------------------|-------------------|

| LTC7871ELWE#PBF     | LTC7871       | 64-Lead (10mm × 10mm) Plastic LQFP | -40°C to 125°C    |

| LTC7871ILWE#PBF     | LTC7871       | 64-Lead (10mm × 10mm) Plastic LQFP | -40°C to 125°C    |

| LTC7871JLWE#PBF     | LTC7871       | 64-Lead (10mm × 10mm) Plastic LQFP | -40°C to 150°C    |

| LTC7871HLWE#PBF     | LTC7871       | 64-Lead (10mm × 10mm) Plastic LQFP | -40°C to 150°C    |

| AUTOMOTIVE PRODUCTS | **            |                                    |                   |

| LTC7871ELWE#WPBF    | LTC7871       | 64-Lead (10mm × 10mm) Plastic LQFP | -40°C to 125°C    |

| LTC7871ILWE#WPBF    | LTC7871       | 64-Lead (10mm × 10mm) Plastic LQFP | -40°C to 125°C    |

| LTC7871JLWE#WPBF    | LTC7871       | 64-Lead (10mm × 10mm) Plastic LQFP | -40°C to 150°C    |

| LTC7871HLWE#WPBF    | LTC7871       | 64-Lead (10mm × 10mm) Plastic LQFP | -40°C to 150°C    |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. This product is available in 160-piece trays.

<sup>\*\*</sup>Versions of this part are available with controlled manufacturing to support the quality and reliability requirements of automotive applications. These models are designated with a #W suffix. Only the automotive grade products shown are available for use in automotive applications. Contact your local Analog Devices account representative for specific product ordering information and to obtain the specific Automotive Reliability reports for these models.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ , $V_{HIGH} = 48V$ , $V_{RUN} = 5V$ unless otherwise noted. (Note 2)

| SYMBOL               | PARAMETER CONDITIONS                                                                                                                     |                                                                                                                                                                                            | MIN | TYP               | MAX               | UNITS             |                |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------|-------------------|-------------------|----------------|

| Main Contro          | l Loops                                                                                                                                  |                                                                                                                                                                                            |     |                   |                   |                   |                |

| V <sub>HIGH</sub>    | V <sub>HIGH</sub> Supply Voltage Range                                                                                                   |                                                                                                                                                                                            |     | 6                 |                   | 100               | V              |

| $\overline{V_{LOW}}$ | V <sub>LOW</sub> Supply Voltage Range                                                                                                    | V <sub>HIGH</sub> > 6V                                                                                                                                                                     |     | 1.2               |                   | 60                | ٧              |

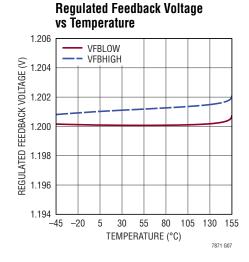

|                      | V <sub>LOW</sub> Regulated Feedback Voltage                                                                                              | (Note 4); ITH <sub>LOW</sub> Voltage = 1.5V                                                                                                                                                | •   | 1.188             | 1.200             | 1.212             | V              |

|                      | V <sub>HIGH</sub> Regulated Feedback Voltage                                                                                             | (Note 4); ITH <sub>HIGH</sub> Voltage = 0.5V                                                                                                                                               | •   | 1.188             | 1.200             | 1.212             | V              |

|                      | V <sub>LOW</sub> EA Feedback Current                                                                                                     | (Note 4)                                                                                                                                                                                   |     |                   | -10               | -40               | nA             |

|                      | V <sub>HIGH</sub> EA Feedback Current                                                                                                    | (Note 4)                                                                                                                                                                                   |     |                   | -10               | -40               | nA             |

|                      | Reference Voltage Line Regulation                                                                                                        | (Note 4); V <sub>HIGH</sub> = 7V to 80V                                                                                                                                                    |     |                   | 0.02              | 0.2               | %              |

|                      | V <sub>HIGH</sub> /V <sub>LOW</sub> Voltage Load Regulation                                                                              | Measured in Servo Loop, $\Delta$ ITH Voltage = 1.0V to 1.5V Measured in Servo Loop, $\Delta$ ITH Voltage = 1.0V to 0.5V                                                                    |     |                   | 0.01<br>-0.01     | 0.2<br>-0.2       | %<br>%         |

| g <sub>m-buck</sub>  | Buck Mode Transconductance<br>Amplifier g <sub>m-buck</sub>                                                                              | (Note 4) ITH <sub>LOW</sub> = 1.5V, Sink/Source 5µA                                                                                                                                        |     |                   | 2                 |                   | mmho           |

| g <sub>m-boost</sub> | Boost Mode Transconductance<br>Amplifier g <sub>m-boost</sub>                                                                            | (Note 4) ITH <sub>HIGH</sub> = 0.5V, Sink/Source 5µA                                                                                                                                       |     |                   | 1                 |                   | mmho           |

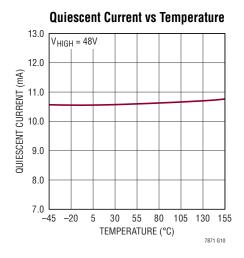

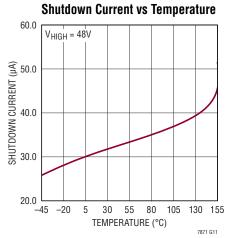

| IQ                   | V <sub>HIGH</sub> DC Supply Current<br>Shutdown Mode, V <sub>HIGH</sub> Supply Current<br>Shutdown Mode, V <sub>LOW</sub> Supply Current | (Note 5)<br>V <sub>RUN</sub> = 0V; V <sub>HIGH</sub> = 48V<br>V <sub>RUN</sub> = 0V; V <sub>LOW</sub> = 12V                                                                                |     |                   | 10<br>30<br>20    | 16                | mA<br>μΑ<br>μΑ |

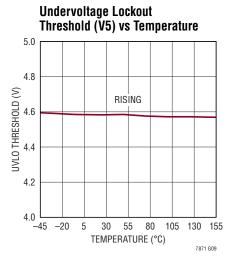

| UVL0                 | DRV <sub>CC</sub> Undervoltage Lockout<br>Threshold                                                                                      | DRV <sub>CC</sub> Ramping Down, V <sub>DRVSET</sub> = V <sub>V5</sub> DRV <sub>CC</sub> Ramping Down, V <sub>DRVSET</sub> = Float DRV <sub>CC</sub> Ramping Down, V <sub>DRVSET</sub> = 0V |     | 6.9<br>4.8<br>3.9 | 7.2<br>5.0<br>4.1 | 7.5<br>5.2<br>4.3 | V<br>V<br>V    |

|                      | DRV <sub>CC</sub> Undervoltage Hysteresis                                                                                                | V <sub>DRVSET</sub> = Float, V <sub>V5</sub><br>V <sub>DRVSET</sub> = 0V                                                                                                                   |     |                   | 0.8<br>0.5        |                   | V              |

|                      | V5 Undervoltage Lockout Threshold                                                                                                        | V5 Ramping Down, V <sub>DRVSET</sub> = Float, V <sub>V5</sub><br>V5 Ramping Down, V <sub>DRVSET</sub> = 0V                                                                                 |     | 4.2<br>3.9        | 4.4<br>4.1        | 4.6<br>4.3        | V              |

|                      | V5 Undervoltage Hysteresis                                                                                                               | V <sub>DRVSET</sub> = Float, V <sub>V5</sub><br>V <sub>DRVSET</sub> = 0V                                                                                                                   |     |                   | 0.2<br>0.5        |                   | V              |

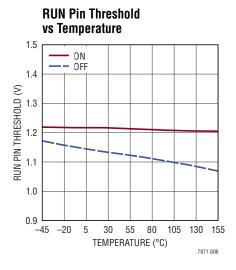

|                      | RUN Pin On Threshold                                                                                                                     | V <sub>RUN</sub> Rising                                                                                                                                                                    |     | 1.1               | 1.22              | 1.35              | V              |

|                      | RUN Pin On Hysteresis                                                                                                                    |                                                                                                                                                                                            |     |                   | 80                |                   | mV             |

|                      | RUN Pin Source Current                                                                                                                   | V <sub>RUN</sub> < 1.1V                                                                                                                                                                    | •   | 0.6               | 2                 |                   | μA             |

|                      | RUN Pin Hysteresis Current                                                                                                               | V <sub>RUN</sub> > 1.3V                                                                                                                                                                    | •   | 2                 | 6                 |                   | μA             |

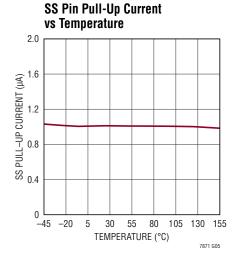

| I <sub>SS</sub>      | Soft-Start Charging Current                                                                                                              | V <sub>SS</sub> = 1.2V                                                                                                                                                                     |     | 0.8               | 1.0               | 1.2               | μA             |

|                      | BUCK Pin Input Threshold                                                                                                                 | V <sub>BUCK</sub> Rising<br>V <sub>BUCK</sub> Falling                                                                                                                                      |     |                   | 2.2<br>1.7        |                   | V              |

|                      | BUCK Pin Pull-Up Resistance                                                                                                              | BUCK Pin to V5                                                                                                                                                                             |     |                   | 200               |                   | kΩ             |

|                      | Maximum Duty Cycle                                                                                                                       | Buck Mode<br>Boost Mode                                                                                                                                                                    |     | 96                | 98<br>92          |                   | %<br>%         |

| <b>Current Mor</b>   | nitoring and Regulation Functions                                                                                                        |                                                                                                                                                                                            |     |                   | -                 |                   |                |

| I <sub>SNSA</sub> +  | SNSA+ Pins Input Current                                                                                                                 |                                                                                                                                                                                            |     |                   | ±0.05             | ±1                | μA             |

| I <sub>SNSD</sub> +  | SNSD+ Pins Input Current                                                                                                                 |                                                                                                                                                                                            |     |                   | ±0.05             | ±1                | μA             |

| I <sub>SNS</sub> -   | SNS <sup>-</sup> Pins Input Current                                                                                                      |                                                                                                                                                                                            |     |                   | 1                 |                   | mA             |

|                      | ILIM Pin Input Resistance                                                                                                                |                                                                                                                                                                                            |     |                   | 100               |                   | kΩ             |

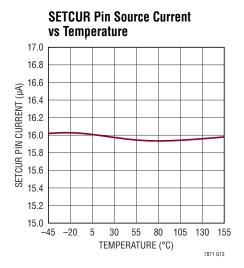

| I <sub>SETCUR</sub>  | SETCUR Pin Sourcing Current                                                                                                              | MFR_IDAC_SETCUR = 0x00                                                                                                                                                                     | •   | 15.0              | 16.0              | 17.0              | μA             |

|                      | IMON Current Proportional to V <sub>LOW</sub> at Max Current                                                                             | $V_{ILIM}$ = Float, $R_{SENSE}$ = $3m\Omega$                                                                                                                                               |     |                   |                   | ±10               | %              |

|                      | I <sub>MON</sub> Zero Current Voltage                                                                                                    |                                                                                                                                                                                            |     | 1.240             | 1.250             | 1.260             | V              |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ , $V_{HIGH} = 48V$ , $V_{RUN} = 5V$ unless otherwise noted. (Note 2)

| SYMBOL                                         | PARAMETER                                                                                                 | CONDITIONS                                                                                                                                     |   | MIN            | TYP            | MAX            | UNITS    |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|----------------|----------------|----------|

|                                                | Current Sense Pin Voltage                                                                                 | V <sub>ILIM</sub> = 0V, 1/4 V <sub>V5</sub>                                                                                                    |   |                | 40             |                | V/V      |

|                                                | (V <sub>SNSD</sub> <sup>+</sup> – V <sub>SNS</sub> <sup>-</sup> ) to IMON Gain                            | $V_{\text{ILIM}}$ = Float, 3/4 $V_{\text{V5}}$ , $V_{\text{V5}}$                                                                               |   |                | 20             |                | V/V      |

|                                                | Total DC Sense Signal Gain                                                                                | DCR Configuration                                                                                                                              |   |                | 5              |                | V/V      |

|                                                | Total DC Sense Signal Gain                                                                                | R <sub>SENSE</sub> Configuration                                                                                                               |   |                | 4              |                | V/V      |

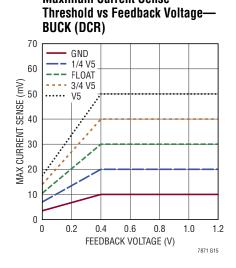

| V <sub>SENSE(MAX)</sub><br>(DCR                | Maximum Current Sense Threshold (Buck and Boost Mode)                                                     | $\begin{vmatrix} V_{\text{ILIM}} = 0V \\ V_{\text{ILIM}} = 1/4 V_{V5} \end{vmatrix}$                                                           |   | 6.5<br>17.0    | 10.0<br>20.0   | 13.5<br>23.0   | mV<br>mV |

| Configuration)                                 | (Duck and Doost Mode)                                                                                     | V <sub>ILIM</sub> = 1/4 VV5<br>V <sub>ILIM</sub> = Float                                                                                       |   | 27.0           | 30.0           | 33.0           | mV       |

|                                                |                                                                                                           | $V_{ILIM} = 3/4 V_{V5}$                                                                                                                        | • | 36.0           | 40.0           | 44.0           | mV       |

|                                                | Marianum Cruwant Canaa Thuashald                                                                          | V <sub>ILIM</sub> = V <sub>V5</sub>                                                                                                            | • | 44.0           | 50.0           | 56.0           | mV       |

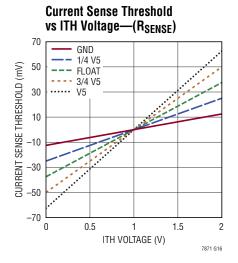

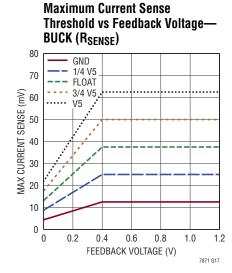

| V <sub>SENSE(MAX)</sub><br>(R <sub>SENSE</sub> | Maximum Current Sense Threshold (Buck and Boost Mode)                                                     | $V_{ILIM} = 0V$<br>$V_{ILIM} = 1/4 V_{V5}$                                                                                                     |   | 8.1<br>21.2    | 12.5<br>25.0   | 16.9<br>28.8   | mV<br>mV |

| Configuration)                                 | ,                                                                                                         | V <sub>ILIM</sub> = Float                                                                                                                      | • | 33.7           | 37.5           | 41.3           | mV       |

|                                                |                                                                                                           | $V_{ILIM} = 3/4 V_{V5}$ $V_{ILIM} = V_{V5}$                                                                                                    |   | 45.0<br>55.0   | 50.0<br>62.5   | 55.0<br>70.0   | mV<br>mV |

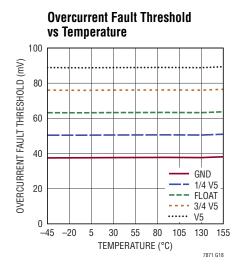

| V <sub>OCFT</sub>                              | Overcurrent Fault Threshold,                                                                              | V <sub>ILIM</sub> = 0V                                                                                                                         | • | 31.0           | 37.5           | 44.0           | mV       |

| - 0011                                         | V <sub>SNSD</sub> <sup>+</sup> - V <sub>SNS</sub> <sup>-</sup>                                            | $V_{ILIM} = 1/4 V_{V5}$                                                                                                                        | • | 43.0           | 50.0           | 57.0           | mV       |

|                                                |                                                                                                           | $V_{ILIM}$ = Float $V_{ILIM}$ = 3/4 $V_{V5}$                                                                                                   |   | 54.0<br>65.0   | 62.5<br>75.0   | 71.0<br>85.0   | mV<br>mV |

|                                                |                                                                                                           | $V_{\text{ILIM}} = 0.7 \text{ to } \sqrt{5}$                                                                                                   | • | 76.0           | 87.5           | 99.0           | mV       |

| V <sub>NOCFT</sub>                             | Negative Overcurrent Fault Threshold,                                                                     | V <sub>ILIM</sub> = 0V                                                                                                                         | • | -45.0          | -37.5          | -30.0          | mV       |

|                                                | V <sub>SNSD</sub> <sup>+</sup> - V <sub>SNS</sub> <sup>-</sup>                                            | V <sub>ILIM</sub> = 1/4 V <sub>V5</sub><br>V <sub>ILIM</sub> = Float                                                                           |   | -58.0<br>-72.0 | -50.0<br>-62.5 | -42.0<br>-53.0 | mV<br>mV |

|                                                |                                                                                                           | $V_{ILIM} = 3/4 V_{V5}$                                                                                                                        | • | -86.0          | -75.0          | -64.0          | mV       |

|                                                |                                                                                                           | $V_{ILIM} = V_{V5}$                                                                                                                            | • | -100.0         | -87.5          | -75.0          | mV       |

|                                                | Overcurrent Fault Threshold                                                                               | $V_{\text{ILIM}} = 0V$                                                                                                                         |   |                | 25<br>31       |                | mV<br>mV |

| DRVoc and V5                                   | Hysteresis,  V <sub>SNSD</sub> <sup>+</sup> - V <sub>SNS</sub> <sup>-</sup>  <br><b>Linear Regulators</b> | $V_{ILIM} = 1/4 V_{V5}$ , Float, 3/4 $V_{V5}$ , $V_{V5}$                                                                                       |   |                | 31             |                | 1117     |

| V <sub>DRVCC</sub>                             | DRV <sub>CC</sub> Regulation Voltage                                                                      | 12V < V <sub>EXTVCC</sub> < 60V, V <sub>DRVSET</sub> = V <sub>V5</sub>                                                                         |   | 9.5            | 10             | 10.5           | V        |

| V DKVCC                                        | Brive riogalation voltage                                                                                 | 12V < V <sub>EXTVCC</sub> < 60V, V <sub>DRVSET</sub> = Float                                                                                   |   | 7.6            | 8              | 8.4            | V        |

|                                                |                                                                                                           | 12V < V <sub>EXTVCC</sub> < 60V, V <sub>DRVSET</sub> = 0V                                                                                      |   | 4.8            | 5              | 5.2            | V        |

| -                                              | DRV <sub>CC</sub> Load Regulation                                                                         | I <sub>DRVCC</sub> = 0mA to 100mA, V <sub>EXTVCC</sub> = 14V                                                                                   |   |                | 1.6            | 3.0            | %        |

|                                                | EXTV <sub>CC</sub> Switchover Voltage                                                                     | EXTV <sub>CC</sub> Ramping Positive, V <sub>DRVSET</sub> = V <sub>V5</sub><br>EXTV <sub>CC</sub> Ramping Positive, V <sub>DRVSET</sub> = Float |   |                | 10.7<br>8.5    |                | V<br>V   |

|                                                |                                                                                                           | EXTV <sub>CC</sub> Ramping Positive, V <sub>DRVSET</sub> = 110at<br>EXTV <sub>CC</sub> Ramping Positive, V <sub>DRVSET</sub> = 0V              |   |                | 6.9            |                | V        |

|                                                | EXTV <sub>CC</sub> Hysteresis                                                                             | 33 1 3 3.1132.                                                                                                                                 |   |                | 12             |                | %        |

| V5                                             | V5 Regulation Voltage                                                                                     | 6V < V <sub>DRVCC</sub> < 10V                                                                                                                  |   | 4.8            | 5.0            | 5.2            | V        |

|                                                | V5 Load Regulation                                                                                        | I <sub>V5</sub> = 0mA to 20mA                                                                                                                  |   |                | 0.5            | 1              | %        |

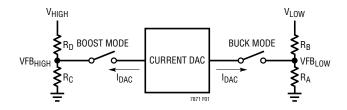

| Current DACs                                   | (IDAC)                                                                                                    |                                                                                                                                                |   |                |                |                |          |

|                                                | V <sub>HIGH</sub> /V <sub>LOW</sub> IDAC Accuracy                                                         | MFR_IDAC_V <sub>LOW/HIGH</sub> = 0x40 or 0x7F                                                                                                  |   | -1             |                | 1              | %        |

|                                                | V <sub>HIGH</sub> /V <sub>LOW</sub> IDAC Program Range                                                    |                                                                                                                                                |   | -64            |                | 63             | μA       |

|                                                | SETCUR IDAC Program Range                                                                                 |                                                                                                                                                |   | 0              |                | 31             | μA       |

| LSB                                            | V <sub>HIGH</sub> /V <sub>LOW</sub> IDAC LSB<br>SETCUR IDAC LSB                                           |                                                                                                                                                |   |                | 1<br>1         |                | μA<br>μA |

| Oscillator and                                 | Phase-Locked Loop                                                                                         |                                                                                                                                                |   |                |                |                |          |

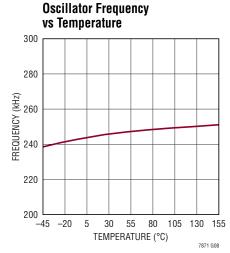

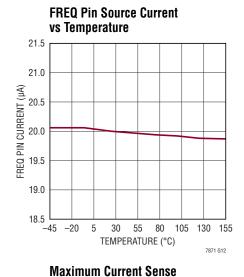

| I <sub>FREQ</sub>                              | FREQ Pin Output Current                                                                                   |                                                                                                                                                | • | 19             | 20             | 21             | μA       |

|                                                | Nominal Frequency                                                                                         | V <sub>SYNC</sub> = 0V, R <sub>FREQ</sub> = 51.1k                                                                                              |   | 230            | 250            | 270            | kHz      |

| $f_{LOW}$                                      | Low Fixed Frequency                                                                                       | V <sub>SYNC</sub> = 0V, R <sub>FREQ</sub> = 27.4k                                                                                              |   | 55             | 70             | 85             | kHz      |

| f <sub>HIGH</sub>                              | High Fixed Frequency                                                                                      | $V_{SYNC} = 0V$ , $R_{FREQ} = 105k$                                                                                                            |   | 640            | 710            | 780            | kHz      |

# **ELECTRICAL CHARACTERISTICS** The ullet denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25 \,^{\circ}\text{C}$ , $V_{HIGH} = 48 \,^{\circ}\text{V}$ , $V_{RUN} = 5 \,^{\circ}\text{V}$ unless otherwise noted. (Note 2)

| SYMBOL                              | PARAMETER                                                                                          | CONDITIONS                                                                                                           |   | MIN      | TYP       | MAX  | UNITS  |

|-------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---|----------|-----------|------|--------|

|                                     | Synchronizable Frequency                                                                           | SYNC = External Clock                                                                                                | • | 60       |           | 750  | kHz    |

|                                     | Spread Spectrum Frequency<br>Modulation Range                                                      | V <sub>SYNC</sub> = 5V, R <sub>FREQ</sub> = 51.1k, MFR_SSFM = 0x00                                                   |   | -12      |           | 12   | %      |

| $\theta_2 - \theta_1$               | Phase 2 Relative to Phase 1                                                                        |                                                                                                                      |   |          | 180       |      | Deg    |

| $\theta_3 - \theta_1$               | Phase 3 Relative to Phase 1                                                                        |                                                                                                                      |   |          | 60        |      | Deg    |

| $\theta_4 - \theta_1$               | Phase 4 Relative to Phase 1                                                                        |                                                                                                                      |   |          | 240       |      | Deg    |

| $\theta_5 - \theta_1$               | Phase 5 Relative to Phase 1                                                                        |                                                                                                                      |   |          | 120       |      | Deg    |

| $\theta_6 - \theta_1$               | Phase 6 Relative to Phase 1                                                                        |                                                                                                                      |   |          | 300       |      | Deg    |

| $\theta_{\text{CLKOUT}} - \theta_1$ | CLKOUT Phase to Phase 1                                                                            |                                                                                                                      |   |          | 30        |      | Deg    |

|                                     | Clock Output High Voltage                                                                          | I <sub>LOAD</sub> = 0.5mA                                                                                            |   | V5 – 0.2 | V5        |      | V      |

| -                                   | Clock Output Low Voltage                                                                           | $I_{LOAD} = -0.5 \text{mA}$                                                                                          |   |          |           | 0.2  | V      |

|                                     | SYNC Pin Input Threshold                                                                           | SYNC Pin Rising<br>SYNC Pin Falling                                                                                  |   | 2        |           | 1.1  | V      |

|                                     | SYNC Pin Input Resistance                                                                          |                                                                                                                      |   |          | 100       |      | kΩ     |

| Power Good                          | and FAULT                                                                                          |                                                                                                                      |   |          |           |      |        |

|                                     | PGOOD Voltage Low                                                                                  | I <sub>PGOOD</sub> = 2mA                                                                                             |   |          | 0.1       | 0.3  | V      |

|                                     | PGOOD Leakage Current                                                                              | V <sub>PGOOD</sub> = 5V                                                                                              |   |          |           | ±1   | μА     |

|                                     | PGOOD Trip Level, VFB <sub>HIGH</sub> /VFB <sub>LOW</sub><br>With Respect to the Regulated Voltage | VFB <sub>HIGH</sub> /VFB <sub>LOW</sub> Ramping Negative<br>VFB <sub>HIGH</sub> /VFB <sub>LOW</sub> Ramping Positive |   |          | -10<br>10 |      | %<br>% |

|                                     | PGOOD Delay                                                                                        | PGOOD Pin High to Low                                                                                                |   |          | 40        |      | μs     |

|                                     | FAULT Voltage Low                                                                                  | I <sub>FAULT</sub> = 2mA                                                                                             |   |          | 0.1       | 0.3  | V      |

|                                     | FAULT Voltage Leakage Current                                                                      | V <sub>FAULT</sub> = 5V                                                                                              |   |          |           | ±1   | μА     |

|                                     | FAULT Delay                                                                                        | FAULT Pin High to Low                                                                                                |   |          | 120       |      | μs     |

|                                     | V <sub>LOW</sub> OV Comparator Threshold                                                           |                                                                                                                      |   | 1.15     | 1.2       | 1.25 | V      |

|                                     | V <sub>LOW</sub> OV Comparator Hysteresis                                                          | V <sub>OVLOW</sub> > 1.2V                                                                                            |   |          | 5         |      | μА     |

|                                     | V <sub>HIGH</sub> OV Comparator Threshold                                                          |                                                                                                                      |   | 1.15     | 1.2       | 1.25 | ٧      |

|                                     | V <sub>HIGH</sub> OV Comparator Hysteresis                                                         | V <sub>OVHIGH</sub> > 1.2V                                                                                           |   |          | 5         |      | μА     |

|                                     | V <sub>HIGH</sub> UV Comparator Threshold                                                          |                                                                                                                      |   | 1.15     | 1.2       | 1.25 | ٧      |

|                                     | V <sub>HIGH</sub> UV Comparator Hysteresis                                                         | V <sub>UVHIGH</sub> < 1.2V                                                                                           |   |          | 5         |      | μА     |

| PWM Outputs                         | •                                                                                                  |                                                                                                                      | ' |          |           |      |        |

|                                     | PWM Output High Voltage                                                                            | I <sub>LOAD</sub> = 0.5mA                                                                                            | • | V5 – 0.5 |           |      | V      |

|                                     | PWM Output Low Voltage                                                                             | $I_{LOAD} = -0.5 \text{mA}$                                                                                          | • |          |           | 0.5  | V      |

|                                     | PWM Output Current in Hi-Z State                                                                   |                                                                                                                      |   |          |           | ±5   | μА     |

| DIGITAL I/O:                        | CSB, SCLK, SDI, SDO                                                                                |                                                                                                                      | • |          |           |      |        |

| $\overline{V_{IL}}$                 | Digital Input Low Voltage                                                                          | Pins CSB, SCLK, SDI                                                                                                  |   |          |           | 0.5  | V      |

| $\overline{V_{IH}}$                 | Digital Input High Voltage                                                                         | Pins CSB, SCLK, SDI                                                                                                  |   | 1.8      |           |      | ٧      |

| $\overline{V_{0L}}$                 | Digital Output Voltage Low                                                                         | Pin SDO, Sinking 1mA                                                                                                 |   |          |           | 0.3  | V      |

| R <sub>CSB</sub>                    | CSB Pin Pull-Up Resistor                                                                           |                                                                                                                      |   |          | 300       |      | kΩ     |

| R <sub>SCLK</sub>                   | SCLK Pin Pull-Down Resistor                                                                        |                                                                                                                      |   |          | 300       |      | kΩ     |

| R <sub>SDI</sub>                    | SDI Pin Pull-Down Resistor                                                                         |                                                                                                                      |   |          | 300       |      | kΩ     |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25$ °C, $V_{HIGH} = 48V$ , $V_{RUN} = 5V$ unless otherwise noted. (Note 2)

| SYMBOL                                                                            | PARAMETER              | CONDITIONS |  | MIN | TYP | MAX | UNITS |

|-----------------------------------------------------------------------------------|------------------------|------------|--|-----|-----|-----|-------|

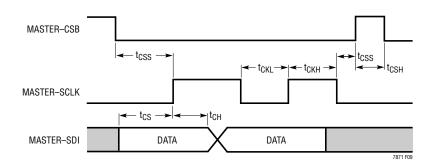

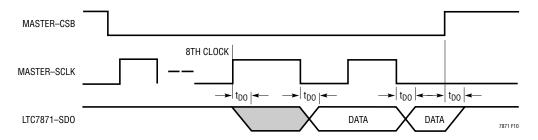

| SPI Interface Timing Characteristics (Refer to Timing Diagram in Figure 9 and 10) |                        |            |  |     |     |     |       |

| t <sub>CKH</sub>                                                                  | SCLK High Time         |            |  | 45  |     |     | ns    |

| t <sub>CSS</sub>                                                                  | CSB Setup Time         |            |  | 40  |     |     | ns    |

| t <sub>CSH</sub>                                                                  | CSB High Time          |            |  | 60  |     |     | ns    |

| t <sub>CS</sub>                                                                   | SDI to SCLK Setup Time |            |  | 40  |     |     | ns    |

| t <sub>CH</sub>                                                                   | SDI to SCLK Hold Time  |            |  | 20  |     |     | ns    |

| t <sub>DO</sub>                                                                   | SCLK to SDO Time       |            |  | 90  |     |     | ns    |

| t <sub>C%</sub>                                                                   | SCLK Duty Cycle        |            |  | 45  | 50  | 55  | %     |

| f <sub>SCLK(MAX)</sub>                                                            | Maximum SCLK Frequency |            |  | 5   |     |     | MHz   |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC7871 is tested under pulsed load conditions such that  $T_J \approx T_A$ . The LTC7871E is guaranteed to meet performance specifications from 0°C to 85°C junction temperature. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC7871I is guaranteed over the -40°C to 125°C operating junction temperature range. The LTC7871J is guaranteed over the -40°C to 150°C operating junction temperature range. High

junction temperature degrades operating lifetimes; operating lifetime is derated for junction temperatures greater than 125°C. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors.

**Note 3:**  $T_J$  is calculated from the ambient temperature  $T_A$  and power dissipation  $P_D$  according to the following formula:

$$T_J = T_A + (P_D \cdot 17^{\circ}C/W)$$

**Note 4:** The LTC7871 is tested in a feedback loop that servos V<sub>ITHHIGH</sub> and V<sub>ITHLOW</sub> to a specified voltage and measures the resultant VFB<sub>HIGH</sub>, VFB<sub>LOW</sub>, respectively.

**Note 5:** Dynamic supply current may be higher due to the loading current at  $\mathsf{DRV}_\mathsf{CC}$  linear regulator.

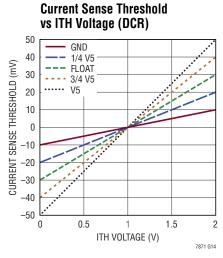

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

# PIN FUNCTIONS

**RUN (Pin 27):** Enable Control Input. A voltage above 1.22V turns on the IC. There is a  $2\mu$ A pull-up current on this pin. Once the RUN pin rises above the 1.22V threshold, the pull-up current increases to  $6\mu$ A.

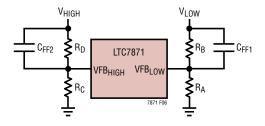

**VFB<sub>HIGH</sub> (Pin 7):** V<sub>HIGH</sub> Voltage Sensing Error Amplifier Noninverting Input.

**VFB<sub>LOW</sub>** (**Pin 3**): V<sub>LOW</sub> Voltage Sensing Error Amplifier Inverting Input.

ITH<sub>HIGH</sub>/ITH<sub>LOW</sub> (Pins 6 and 4): Current Control Threshold and Error Amplifier Compensation Point. The current comparator's threshold varies with the ITH control voltage.

**SS (Pin 1):** Soft-Start Input. The voltage ramp rate at this pin sets the voltage ramp rate of the regulated voltage. A capacitor to ground accomplishes soft-start. This pin has a 1µA pull-up current.

**MODE (Pin 51):** Mode Set Pin. Tying this pin to SGND enables forced continuous mode in buck or boost modes. Floating this pin results in burst mode in buck mode and discontinuous mode in boost mode. Tying this pin to V5 enables discontinuous mode in buck or boost modes. The input impedance of this pin is  $90k\Omega$ .

**SYNC (Pin 52):** Switching Frequency Synchronization or Spread Spectrum Set Pin. Applying an external clock between 60kHz to 750kHz to this pin causes the switching frequency to synchronize to the clock signal. If SYNC is low, a resistor from the FREQ pin to SGND sets the switching frequency. Tying this pin to V5 allows switching frequency spread spectrum. This pin has a  $100k\Omega$  internal resistor to ground.

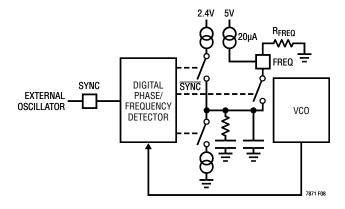

**FREQ (Pin 53):** Frequency Set Pin. A resistor between this pin and SGND sets the switching frequency. This pin sources 20µA current.

**DRVSET (Pin 44):** The voltage setting on this pin programs the DRV<sub>CC</sub> output voltage. There are two internal resistors,  $200k\Omega$  and  $160k\Omega$ , connecting this pin to the V5 and SGND, respectively.

**CLKOUT (Pin 50):** Clock Output Pin. Use this pin to synchronize multiple LTC7871 ICs. Signal swing is from V5 to ground.

**V5 (Pin 9):** Internal 5V Regulator Output. The control circuits are powered from this voltage. Bypass this pin to SGND with a minimum of  $4.7\mu F$  low ESR tantalum or ceramic capacitor.

**DRV**<sub>CC</sub> (**Pin 46**): Gate Driver Current Supply LDO Output. The voltage on this pin can be set to 5V, 8V, or 10V by the DRVSET pin. Bypass this pin to ground plane with a minimum of  $4.7\mu\text{F}$  low ESR tantalum or ceramic capacitor.

**EXTV**<sub>CC</sub> (**Pin 42**): External Power Input to an Internal LDO Connected to DRV<sub>CC</sub>. This LDO supplies DRV<sub>CC</sub> power, bypassing the internal LDO powered from  $V_{HIGH}$ , whenever EXTV<sub>CC</sub> is higher than its switchover threshold. Do not exceed 60V on this pin.

**ILIM (Pin 49):** Current Comparator Sense Voltage Limit Selection Pin. The input impedance of this pin is  $100k\Omega$ .

SNSD1+/SNSD2+/SNSD3+/SNSD4+/SNSD5+/SNSD6+ (Pins 19, 20, 25, 56, 61, and 62): DC Positive Current Sense Comparator Inputs. These inputs amplify the DC portion of the current signal to the IC's current comparators and current sense amplifiers.

SNS1<sup>-</sup>/SNS2<sup>-</sup>/SNS3<sup>-</sup>/SNS4<sup>-</sup>/SNS5<sup>-</sup>/SNS6<sup>-</sup> (Pins 18, 21, 24, 57, 60, and 63): Negative Current Sense Comparator Inputs. The negative input of the current comparator is normally connected to the  $V_{LOW}$ .

SNSA1\*/SNSA2\*/SNSA3\*/SNSA4\*/SNSA5\*/SNSA6\* (Pins 17, 22, 23, 58, 59, and 64): AC Positive Current Sense Comparator Inputs. These inputs amplify the AC portion of the current signal to the IC's current comparator.

$V_{HIGH}$  (Pin 48): Main  $V_{HIGH}$  Supply. Bypass this pin to ground with a capacitor (0.1 $\mu$ F to 1 $\mu$ F).

**FAULT (Pin 35):** Fault Indicator Output. Open-drain output that pulls to ground during a fault condition.

**PGOOD (Pin 30):** Power Good Indictor Output for the Regulated  $V_{HIGH}/V_{LOW}$ . Open drain logic out that is pulled to ground when the regulated  $V_{HIGH}/V_{LOW}$  exceeds  $\pm 10\%$  regulation window, after the internal  $40\mu S$  power bad mask timer expires.

# PIN FUNCTIONS

**UV<sub>HIGH</sub>** (**Pin 14**):  $V_{HIGH}$  Undervoltage Threshold Set Pin. A resistor divider from  $V_{HIGH}$  is needed to set this threshold. When the voltage on this pin falls below the 1.2V trip point, a 5 $\mu$ A current is sunk in to the pin to provide externally adjustable hysteresis.

$OV_{HIGH}$  (Pin 13):  $V_{HIGH}$  Overvoltage Threshold Set Pin. A resistor divider from  $V_{HIGH}$  is needed to set this threshold. When the voltage on this pin rises past the 1.2V trip point, a 5µA current is sourced out of the pin to provide externally adjustable hysteresis.

$OV_{LOW}$  (Pin 15):  $V_{LOW}$  Overvoltage Threshold Set Pin. A resistor divider from  $V_{LOW}$  is needed to set this threshold. When the voltage on this pin rises past the 1.2V trip point, a 5µA current is sourced out of the pin to provide externally adjustable hysteresis.

**BUCK (Pin 54):** The voltage on this pin determines if the IC is regulating the  $V_{LOW}$  or  $V_{HIGH}$  voltage/current. Float or tie this pin to V5 for buck mode operation. Ground this pin for boost mode operation.

**IMON (Pin 10):** Current Monitor Pin. The voltage on this pin is directly proportional to the average inductor currents of all 6 channels. 1.25V on this pin indicates zero average inductor current per phase.

**SETCUR (Pin 11):** This pin sets the maximum average inductor current in buck or boost mode. This pin sources 16µA current and it is programmable by the SPI interface.

**PWM1**, **PWM2**, **PWM3**, **PWM4**, **PWM5**, **PWM6** (**Pins 29**, **31**, **32**, **33**, **34**, **and 36**): (Top) Gate Signal Output. This signal goes to the PWM or top gate input of the external gate driver or integrated driver MOSFET. This is a three-state compatible output.

**PWMEN (Pin 28):** Enable Pin for External Gate Drivers. Open drain logic that is pulled to ground when the LTC7871 shut downs the external gate drivers. When this pin is low, all the PWM pin outputs are high impedance.

CSB, SDO, SDI, SCLK (Pins 37, 38, 39 and 40): 4-Wire Serial Peripheral Interface (SPI). Active low chip select (CSB), serial clock (SCLK) and serial data in (SDI) are digital Inputs. Serial data out (SDO) is an open-drain NMOS output pin. SDO requires an external pull-up resistor. Refer to the Serial Port section for more details.

NC (Pins 2, 8, 12, 26, 41, 43, 47, and 55): No Connect Pins.

**SGND** (Pins 5, 16, 45 and Exposed Pad): Ground. Must be soldered to PCB ground for rated thermal performance. Connect this pin closely to negative terminal of  $V_{HIGH}$ , DRV<sub>CC</sub>, V5 bypass capacitors. All small signal components and compensation components should connect here.

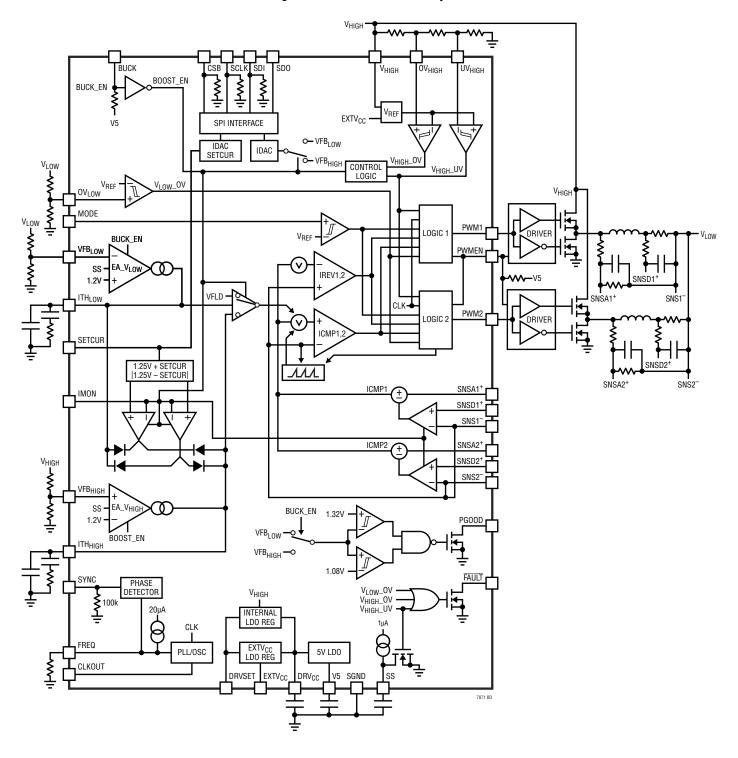

# **BLOCK DIAGRAM** Functional Diagram Shows Two Channels Only.

#### **Main Control Loop**

The LTC7871 is a bidirectional, constant-frequency, current mode buck or boost switching regulator controller with six channels operating equally out of phase. The LTC7871 is capable of delivering power from V<sub>HIGH</sub> to V<sub>LOW</sub> as well as from V<sub>LOW</sub> back to V<sub>HIGH</sub>. When power is delivered from  $V_{HIGH}$  to  $V_{IOW}$ , the LTC7871 operates as a peak-current mode constant-frequency buck regulator; and when power delivery is reversed, it operates as a valley current mode constant-frequency boost regulator. Four control loops, two for current and two for voltage. allow control of voltage or bidirectional current on either V<sub>HIGH</sub> or V<sub>I OW</sub>. The LTC7871 uses an ADI proprietary current sensing, current mode architecture. During normal buck mode operation, the top MOSFET is turned on every cycle when the oscillator sets the RS latch, and turned off when the main current comparator, I<sub>CMP</sub>, resets the RS latch. The peak inductor current at which I<sub>CMP</sub> resets the RS latch is controlled by the voltage on the ITH pin, which is the output of the error amplifier, EA. The error amplifier receives the feedback signal and compares it to the internal 1.2V reference. When the load current increases, it causes a slight change in the feedback pin voltage relative to the 1.2V reference, which in turn causes the ITH voltage to change until the inductor's average current equals the new load current. After the top MOSFET has turned off, the bottom synchronous MOSFET is turned on until the beginning of the next cycle.

In either buck or boost mode, the two current control loops always monitor the maximum average inductor current. When it increases above the thresholds, the current loops will take over the ITH pin control from the voltage loop. As a result, the maximum average inductor current is limited.

The main control loop is shut down by pulling the RUN pin low. Releasing the RUN pin allows an internal  $2\mu A$  current source to pull it up. When the RUN pin reaches 1.22V, the IC is powered up and the pull-up current increases to  $6\mu A$ . When the RUN pin is low, all functions are kept in a controlled shutdown state.

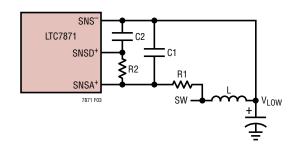

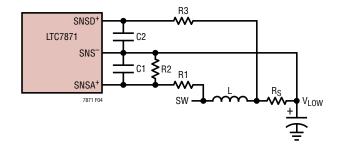

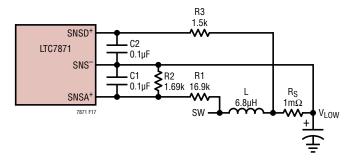

### Current Sensing with Low DCR or R<sub>SENSE</sub>

The LTC7871 employs a unique architecture to enhance the signal-to-noise ratio with low current sense offsets. This enables it to operate with a small current sense signal from a very low value inductor DCR to improve power efficiency, and reduce jitter due to switching noise which could corrupt the signal. Each channel has two positive current sense pins, SNSD+ and SNSA+, which share the negative current sense pin SNS-. These sense pins acquire signals and process them internally to provide the response equivalent to a DCR sense signal that has a 14dB (5 times) signal-to-noise ratio. Accordingly, the current limit threshold is still a function of the inductor peak-current and its DCR value and can be accurately set from 10mV to 50mV in 10mV steps with the ILIM pin.

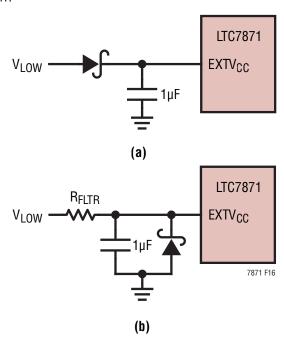

#### DRV<sub>CC</sub>/EXTV<sub>CC</sub>/V5 Power

Power for the external top and bottom MOSFET drivers is derived from the DRV<sub>CC</sub> pin. The DRV<sub>CC</sub> voltage can be set to 5V, 8V, or 10V using the DRVSET pin. When the EXTV<sub>CC</sub> pin is left open or tied to a voltage less than the switchover voltage programmed by the DRVSET pin, an internal linear regulator supplies DRV<sub>CC</sub> power from V<sub>HIGH</sub>. When EXTV<sub>CC</sub> is taken above the switchover voltage, the internal regulator between  $V_{HIGH}$  and DRV<sub>CC</sub> is turned off, and a second internal regulator is turned on between EXTV<sub>CC</sub> and DRV<sub>CC</sub>. Each top MOSFET driver is biased from a floating bootstrap capacitor, which normally recharges during each off cycle through an external diode when the top MOSFET turns off. If the input voltage,  $V_{HIGH}$ , decreases to a voltage close to  $V_{LOW}$ , the loop may enter dropout and attempt to turn on the top MOSFET continuously. The dropout detector detects this and forces the top MOSFET off for about one-twelfth of the clock period plus 160ns every fifth cycle to allow the bootstrap capacitor to recharge.

Most of the internal circuitry is powered from the V5 rail that is generated by an internal linear regulator from DRV<sub>CC</sub>. The V5 pin needs to be bypassed with a minimum  $4.7\mu F$  external capacitor to SGND. This pin provides a 5V output that can supply up to 20mA of current. See the Applications Information section for more details.

#### Soft-Start (Buck Mode)

By default, the start-up of the  $V_{LOW}$  voltage is normally controlled by an internal soft-start ramp. The internal soft-start ramp represents a noninverting input to the error amplifier. The VFB<sub>LOW</sub> pin is regulated to the lowest of the error amplifier's three noninverting inputs (the internal soft-start ramp, the SS pin or the internal 1.2V reference). As the ramp voltage rises from 0V to 1.2V over approximately 1ms, the  $V_{LOW}$  voltage rises smoothly from its prebiased value to its final set value. Certain applications can require the start-up of the converter into a non-zero load voltage, where residual charge is stored on the  $V_{LOW}$  capacitor at the onset of converter switching. In order to prevent the  $V_{LOW}$  from discharging under these conditions, the top and bottom MOSFETs are disabled until soft-start is greater than VFB<sub>LOW</sub>.

#### Soft-Start (Boost Mode)

The same internal soft-start capacitor and external softstart capacitor are also active if the controller starts with boost mode of operation. The error amplifier for boost mode also tries to regulate to the lowest reference during start-up. However, the topology of the boost converter limits the effectiveness of this soft-start mechanism until the boost output voltage reaches its input voltage level. Therefore, it is recommended that the controller starts in buck mode of operation.

#### Shutdown and Start-Up (RUN and SS Pins)

The LTC7871 can be shut down using the RUN pin. Pulling the RUN pin below 1.22V shuts down the main control loop for the controller and most internal circuits, including the DRV<sub>CC</sub> and V5 regulators. Releasing the RUN pin allows an internal 2 $\mu$ A current to pull up the pin and enable the controller. Alternatively, the RUN pin may be externally pulled up or driven directly by logic. Be careful not to exceed the absolute maximum rating of 6V on this pin. The start-up of the controller's V<sub>LOW</sub> voltage is controlled by the voltage on the SS pin. When the voltage on the SS pin is less than the 1.2V internal reference, the LTC7871 regulates the VFB<sub>LOW</sub> voltage to the SS pin voltage instead of the 1.2V reference. This allows the SS

pin to be used to program a soft-start by connecting an external capacitor from the SS pin to SGND. An internal  $1\mu A$  pull-up current charges this capacitor, creating a voltage ramp on the SS pin. As the SS voltage rises linearly from 0V to 1.2V (and beyond), the  $V_{LOW}$  voltage rises smoothly from zero to its final value. When the RUN pin is pulled low to disable the controller, or when V5 drops below its undervoltage lockout threshold, the SS pin is pulled low by an internal MOSFET. When in undervoltage lockout, the controller is disabled and the external MOSFETs are held off. External circuitry can be added to discharge the soft-start capacitor during fault conditions to ensure a soft-start when the faults are cleared.

# Frequency Selection, Spread Spectrum, and Phase-Locked Loop (FREQ and SYNC Pins)

The selection of switching frequency is a trade-off between efficiency and component size. Low frequency operation increases efficiency by reducing MOSFET switching losses, but requires larger inductance and/or capacitance to maintain low output ripple voltage.

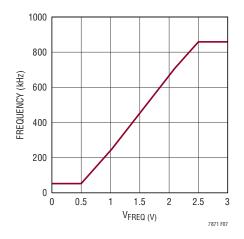

If the SYNC pin is tied to SGND, the FREQ pin can be used to program the controller's operating frequency from 67kHz to 725kHz. There is a precision 20µA current flowing out of the FREQ pin so that the user can program the controller's switching frequency with a single resistor to SGND. A curve is provided later in the Applications Information section showing the relationship between the voltage on the FREQ pin and switching frequency (Figure 7).

Switching regulators can be particularly troublesome for applications when electromagnetic interface (EMI) is a concern. To improve EMI, the LTC7871 can operate in spread spectrum mode, which is enabled by tying the SYNC pin to V5. This feature varies the switching frequency at low frequency rate (switching frequency/512, by default) with a triangular frequency modulation of ±12%. For example, if the LTC7871's frequency is programmed to switch at 200kHz, enabling spread spectrum will modulate the frequency between 176kHz and 224kHz at a 0.4kHz rate. These spread spectrum parameters are programmed by the MFR\_SSFM register.

A phase-locked loop (PLL) is available on the LTC7871 to synchronize the internal oscillator to an external clock source that is connected to the SYNC pin. The PLL loop filter network is integrated inside the LTC7871. The phase locked loop is capable of locking to any frequency within the range of 60kHz to 750kHz. The frequency setting resistor should always be present to set the controller's initial switching frequency before locking to the external clock. The controller operates in the user selected mode when it is synchronized.

### **Undervoltage Lockout**

The LTC7871 has two functions that help protect the controller in case of undervoltage conditions. Two precision UVLO comparators constantly monitor the V5 and DRV $_{\rm CC}$  voltages to ensure that adequate voltages are present. The switching action is stopped when V5 or DRV $_{\rm CC}$  is below the undervoltage lockout threshold. To prevent oscillation when there is a disturbance on the V5 or DRV $_{\rm CC}$ , the UVLO comparators have precision hysteresis.

Another way to detect an undervoltage condition is to monitor the  $V_{HIGH}$  supply. Because the RUN pin has a precision turn-on reference of 1.22V, one can use a resistor divider to  $V_{HIGH}$  to turn on the IC when  $V_{HIGH}$  is high enough. An extra  $4\mu A$  of current flows out of the RUN pin once the RUN pin voltage passes 1.22V. The RUN comparator itself has about 80mV of hysteresis. Additional hysteresis for the RUN comparator can be programmed by adjusting the values of the resistive divider. For accurate  $V_{HIGH}$  undervoltage detection,  $V_{HIGH}$  needs to be higher than 5V.

# Fault Flag (FAULT, OV<sub>HIGH</sub>, OV<sub>LOW</sub> and UV<sub>HIGH</sub> Pins)

The FAULT pin is connected to the open-drain of an internal N-channel MOSFET. It can be pulled high with an external resistor connected to a voltage up to 6V, such as V5 or an external bias voltage. The FAULT pin is pulled low when at least one of the following conditions is met:

- a. The RUN pin is below its turn on threshold.

- b. When V5 or DRV<sub>CC</sub> is below its UVLO threshold.

- c. Any of the three OV/UV comparators has been tripped.

- d. During a startup sequence until the SS pin charges up past 1.2V.

- e. When any channel is in overcurrent fault status.

- f. When the IC is over temperature.

The  $OV_{LOW}$  and  $OV_{HIGH}$  thresholds are set using an external resistor divider off  $V_{LOW}$  and  $V_{HIGH}$ , respectively. When the voltage at the pin exceeds the comparator threshold of 1.2V, a  $5\mu A$  hysteresis current is sourced out of the respective pin and the  $\overline{FAULT}$  signal goes low after a 120 $\mu$ s delay. The  $UV_{HIGH}$  threshold is also set using an external resistor divider off  $V_{HIGH}$ . When the voltage at the pin falls below the comparator threshold of 1.2V, a  $5\mu A$  hysteresis current is sunk into the  $UV_{HIGH}$  pin and the  $\overline{FAULT}$  signal goes low after a 120 $\mu$ s delay. The amount of hysteresis can be adjusted by changing the total impedance of the resistor divider, while the resistor ratio sets the UV/OV trip point.

Besides flagging the  $\overline{\text{FAULT}}$  pin, the UV/OV comparators also affect the operation of the controller, as shown in Table 1. When the OV<sub>LOW</sub> comparator crosses its 1.2V threshold:

- a. In buck mode, the controller stops switching.

- b. In boost mode, the controller continues to switch.

- c. ITH and SS are unaffected in both buck and boost modes. Whenever a fault is detected, discharge the SS pin as needed externally.

When the  $OV_{HIGH}$  comparator crosses its 1st threshold of 1.2V:

- a. The controller stops switching in both buck and boost modes.

- b. ITH and SS are unaffected in both buck and boost modes. Whenever a fault is detected, discharge the SS pin as needed externally.

When the  $OV_{HIGH}$  comparator crosses its 2nd threshold of 2.4V:

a. The controller stops switching in both buck and boost modes.

- b. Both ITH and IMON pins are driven into high impedance. This feature allows the users to isolate one LTC7871 from a multiphase system in case a fault is detected on one particular IC.

- c. The SS pin is unaffected.

When the UV<sub>HIGH</sub> comparator crosses its 1.2V threshold:

- a. In buck mode, the controller stops switching after a 120µs delay, and the SS pin pulls to SGND.

- b. In boost mode, the controller continues to switch. The SS pin is unaffected.

- c. ITH is unaffected in both buck and boost modes.

Table 1. OV/UV Faults

| FAULT                   | MODE  | SWITCHING | ITH PINS  | IMON      | SS            |

|-------------------------|-------|-----------|-----------|-----------|---------------|

| 0V <sub>LOW</sub> 1.2V  | Buck  | Stops     | No Effect | No Effect | No Effect     |

| Threshold               | Boost | Continues | No Effect | No Effect | No Effect     |

| OV <sub>HIGH</sub> 1.2V | Buck  | Stops     | No Effect | No Effect | No Effect     |

| Threshold               | Boost | Stops     | No Effect | No Effect | No Effect     |

| OV <sub>HIGH</sub> 2.4V | Buck  | Stops     | Hi-Z      | Hi-Z      | No Effect     |

| Threshold               | Boost | Stops     | Hi-Z      | Hi-Z      | No Effect     |

| UV <sub>HIGH</sub> 1.2V | Buck  | Stops     | No Effect | No Effect | Pulls to SGND |

| Threshold               | Boost | Continues | No Effect | No Effect | No Effect     |

# Current Monitoring and Regulation (IMON, SETCUR Pins)

The inductor current can be sensed using either its DCR or a R<sub>SENSE</sub> resistor. The current monitoring pin, IMON, outputs a voltage that is proportional to the average inductor current of the six channels sensed by the LTC7871. The operational range of IMON is 0.4V to 2.5V. When the average inductor current is zero, the IMON pin voltage rests at 1.25V. As the inductor current increases in buck mode, the IMON voltage proportionally increases; As the inductor current increases in boost mode, the IMON voltage proportionally decreases. Use the following equation to calculate the voltages on IMON:

$$V_{IMON} = V_{ZERO} + \frac{K \cdot I_{L(ALL)} \cdot R_{SENSE}}{6}; \text{ Buck Mode}$$

$$V_{IMON} = V_{ZERO} - \frac{K \cdot I_{L(ALL)} \cdot R_{SENSE}}{6}; \text{ Boost Mode}$$

where:

$V_{ZERO}$  is the IMON voltage when average output current is zero;  $V_{ZERO} = 1.25 V$  typically

K = 40 if the ILIM voltage is 0V or 1/4  $V_{V5}$

K = 20 if the ILIM voltage is float, 3/4  $V_{V5}$  or  $V_{V5}$

$I_{L(ALL)}$  is the total average inductor current including all six channels

R<sub>SENSE</sub> is the current sensing resistor value.

An external voltage can be applied to the SETCUR pin to regulate the maximum average inductor current. The SETCUR pin voltage should be set as:

$$V_{SETCUR} = \frac{K \cdot I_{L(MAX)} \cdot R_{SENSE}}{6}$$

where:

$I_{L(MAX)}$  is the maximum total average inductor current including all six channels

The SETCURP and SETCURN are internally generated voltages based on the SETCUR pin:

$$SETCURP = 1.25V + V_{SETCUR}$$

$$SETCURN = |1.25V - V_{SETCUR}|$$

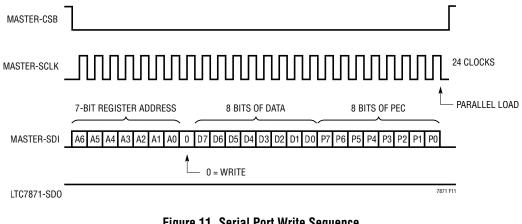

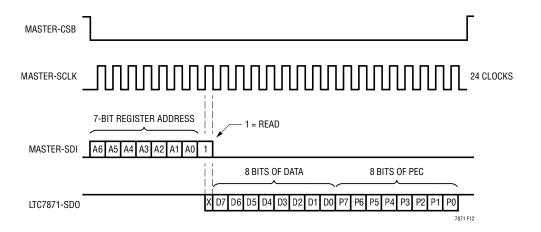

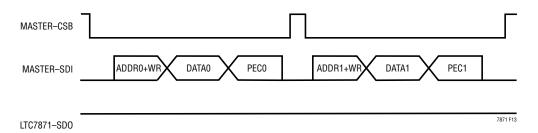

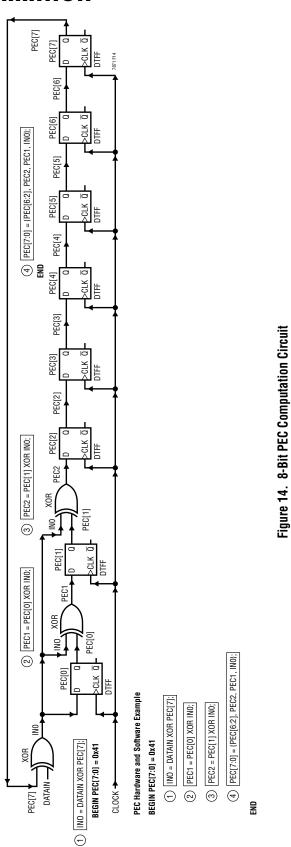

SETCURP, SETCURN, and IMON are the three inputs to the current regulation loop error amplifier with SETCURP and SETCURN acting as the reference. When the IMON pin voltage approaches SETCURP or SETCURN, the ITH pin control is taken over by the current loop error amplifier from the voltage loop error amplifier.