# 20V, 4-Channel Buck DC/DC with 8x Configurable 1.5A Power Stages

#### **FEATURES**

- Wide V<sub>IN</sub> Range: 3V to 20V

- Wide V<sub>OUT</sub> Range: 0.4V to 0.83 V<sub>IN</sub>

- 8x 1.5A Buck Power Stages Configurable as 1 to 4 Output Channels

- 15 Unique Pin Selectable Output Configurations (1.5A to 12A per Channel)

- Internal Boost Capacitors for Reduced PCB Space

- No Load I<sub>Q</sub> 27μA 1 Buck Enabled; 42μA All Bucks Enabled

- 1% V<sub>OUT</sub> Accuracy on All Channels

- Peak Current Mode Control (Burst Mode® Operation/Forced Continuous)

- Precision RUN Inputs, Individual PGOOD Outputs for Power Sequencing

- 1MHz to 3MHz Frequency (RT Programmable, PLL SYNC, or Internal 2MHz Oscillator)

- TEMP Pin Output Indicates Die Temperature

- Output Current Monitors

- Differential Output Sense

# **APPLICATIONS**

- Telecom/Industrial

- 12V Distributed Power Systems

#### DESCRIPTION

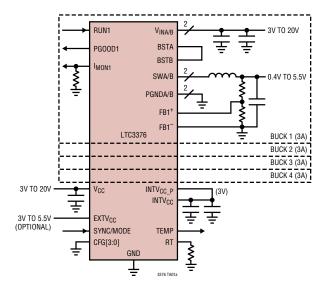

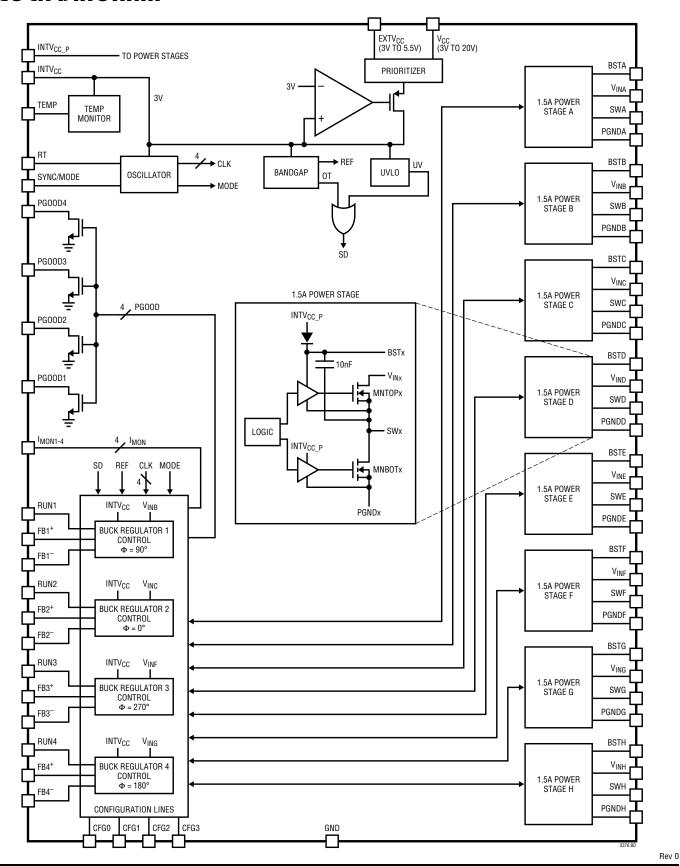

The LTC®3376 is a highly flexible multioutput power supply IC. The device includes four synchronous buck converters, configured to share eight 1.5A power stages, powered from independent 3V to 20V inputs. The DC/DCs are assigned to one of fifteen power configurations via pin strappable CFG0 to CFG3 pins. The LTC3376 includes the integration of ceramic capacitors into the package for the BST pins thereby saving PCB space. The common buck switching frequency may be programmed with an external resistor, synchronized to an external oscillator, or set to a default internal 2MHz clock.

The operating mode for all DC/DCs may be programmed via the SYNC/MODE pin for Burst Mode or forced continuous mode operation. The PGOOD1 to PGOOD4 outputs indicate when each enabled DC/DC is within a specified percentage of its final output.

Current monitors allow for external monitoring of each buck's load. The EXTV<sub>CC</sub> pin allows for the internal circuitry to run from a 3V to 5.5V rail for improved efficiency.

Precision RUN pin thresholds facilitate power-up sequencing. The LTC3376 is available in a 64 lead 7mm × 7mm BGA (0.8mm ball pitch).

All registered trademarks and trademarks are the property of their respective owners.

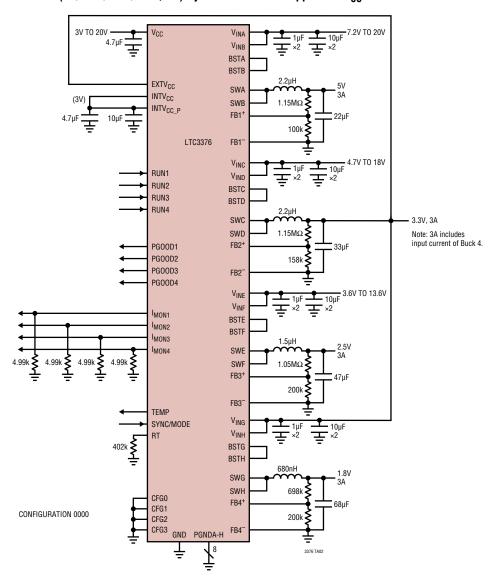

### TYPICAL APPLICATION

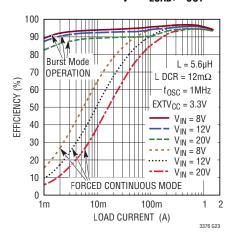

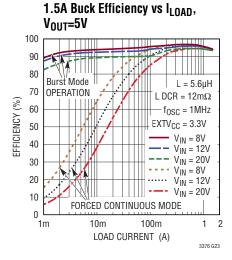

#### 1.5A Buck Efficiency vs I<sub>LOAD</sub>, V<sub>OUT</sub>=5V

Rev 0

#### **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| V <sub>CC</sub> , V <sub>INA-H</sub> 0.3V to 2                      | 2V  |

|---------------------------------------------------------------------|-----|

| FB1-4+, RUN1-4, CFG1-3, EXTV <sub>CC</sub> , PGOOD1-4,              |     |

| INTV <sub>CC</sub> , INTV <sub>CC</sub> P. SYNC/MODE0.3V to         | 6V  |

| CFG0, RT, TEMP, $I_{MON1-4}$ $-0.3V$ to (INTV <sub>CC</sub> + $0.3$ | 3V) |

| INTV <sub>CC</sub> – INTV <sub>CC</sub> <sub>P</sub> –0.3V to 0.    | .3V |

| FB1-4 <sup>-</sup> 0.3V to 0.                                       | .3V |

| l <sub>PG00D1-4</sub> 5i                                            | mΑ  |

| Operating Junction Temperature                                      |     |

| (Notes 2, 3)40°C to 125                                             | 5°C |

| Storage Temperature Range65°C to 150                                | )°C |

| Maximum Reflow (Package Body) Temperature 260                       | )°C |

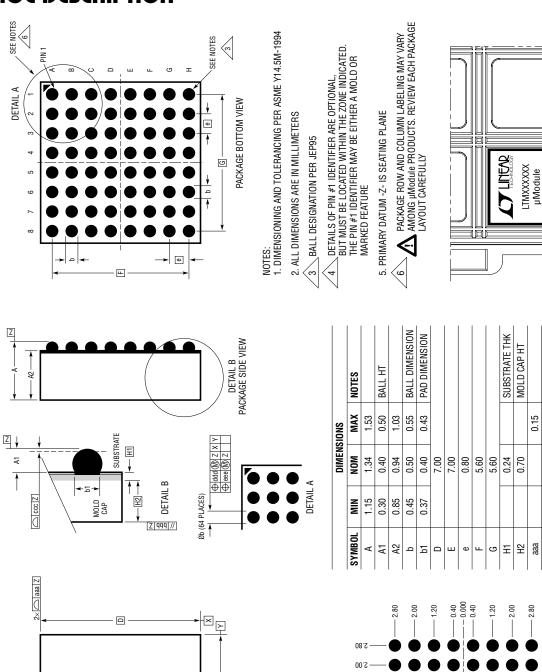

#### PIN CONFIGURATION

#### ORDER INFORMATION

|               |                    | PART MARKING* |             | PACKAGE | MSL    | TEMPERATURE RANGE |

|---------------|--------------------|---------------|-------------|---------|--------|-------------------|

| PART NUMBER   | PAD OR BALL FINISH | DEVICE        | FINISH CODE | TYPE    | RATING | (SEE NOTE 2)      |

| LTC3376EY#PBF | SAC305 (RoHS)      | LTC3376       | of PC       | BGA     | 2      | -40°C to 125°C    |

| LTC3376IY#PBF | 3AC303 (NUNS)      | LTC3376       | e1          | DGA     | 3      | -40°C to 125°C    |

- Contact the factory for parts specified with wider operating temperature ranges. \*Pad or ball finish code is per IPC/JEDEC J-STD-609.

- Recommended LGA and BGA PCB Assembly and Manufacturing Procedures

- Device temperature grade is indicated by a label on the shipping container. LGA and BGA Package and Tray Drawings

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the specified operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ (Note 2). $V_{CC} = V_{INA-H} = 12V$ , RT tied to INTV<sub>CC</sub>, $V_{FB1-4^-} = 0V$ , unless otherwise stated.

| SYMBOL              | PARAMETER                                                     | CONDITIONS                                                                                                                                                                                      |   | MIN | TYP                  | MAX            | UNITS                |

|---------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|----------------------|----------------|----------------------|

| $\overline{V_{CC}}$ | V <sub>CC</sub> Voltage Range                                 |                                                                                                                                                                                                 | • | 3   |                      | 20             | V                    |

| lvcc                | V <sub>CC</sub> Input Supply Current, EXTV <sub>CC</sub> = 0V | All Bucks in Shutdown 1 Buck on, Sleeping, V <sub>FB</sub> <sup>+</sup> = 0.41V Each Additional Buck, Sleeping 1 Buck on (Configured to 1 Power Stage), SYNC/MODE = INTV <sub>CC</sub> (Note 3) |   |     | 9<br>61<br>17<br>4.5 | 15<br>90<br>30 | μΑ<br>μΑ<br>μΑ<br>mA |

|                     | $V_{CC}$ Input Supply Current, EXTV <sub>CC</sub> = 3.3V      | At Least One Buck On                                                                                                                                                                            |   |     | 7                    | 12             | μA                   |

Rev 0

# **ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ (Note 2). $V_{CC} = V_{INA-H} = 12V$ , RT tied to $INTV_{CC}$ , $V_{FB1-4^-} = 0V$ , unless otherwise stated.

| SYMBOL                       | PARAMETER                                                          | CONDITIONS                                                                                                                                                                                                        |   | MIN          | TYP             | MAX          | UNITS          |

|------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------|-----------------|--------------|----------------|

|                              | Total System Current Bootstrapped                                  | 1 Buck on, Sleeping, V <sub>FB</sub> <sup>+</sup> = 0.41V (Note 4)<br>2 Bucks on, Sleeping, V <sub>FB</sub> <sup>+</sup> = 0.41V (Note 4)<br>All Bucks on (Note 4)                                                |   |              | 27<br>32<br>42  |              | μΑ<br>μΑ<br>μΑ |

|                              | EXTV <sub>CC</sub> Input Supply Current, EXTV <sub>CC</sub> = 3.3V | 1 Buck on, Sleep, V <sub>FB</sub> <sup>+</sup> = 0.41V<br>Each Additional Buck, Sleep<br>1 Buck on (Configured to 1 Power Stage),<br>SYNC/MODE = INTV <sub>CC</sub> (Note 3)                                      |   |              | 56<br>17<br>4.5 | 85<br>30     | μΑ<br>μΑ<br>mA |

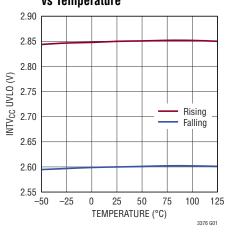

|                              | Undervoltage Threshold on INTV <sub>CC</sub>                       | INTV <sub>CC</sub> Voltage Falling                                                                                                                                                                                | • | 2.55         | 2.6             | 2.65         | V              |

|                              | Undervoltage Hysteresis on INTV <sub>CC</sub>                      |                                                                                                                                                                                                                   |   |              | 250             |              | mV             |

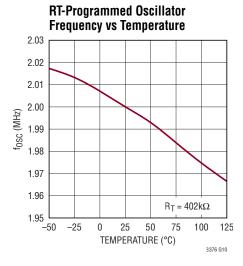

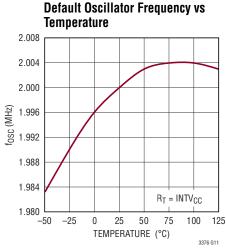

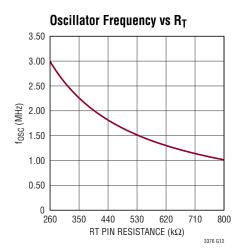

| f <sub>osc</sub>             | Internal Oscillator Frequency                                      | RT = INTV <sub>CC</sub> , SYNC/MODE = 0V<br>RT = 402k, SYNC/MODE = 0V                                                                                                                                             | • | 1.84<br>1.84 | 2<br>2          | 2.16<br>2.16 | MHz<br>MHz     |

|                              | Synchronization Frequency                                          |                                                                                                                                                                                                                   | • | 1            |                 | 3            | MHz            |

| External Lo                  | ow Voltage Supply (If Used)                                        |                                                                                                                                                                                                                   |   |              |                 |              |                |

| EXTV <sub>CC</sub>           | Optional External Supply Range                                     |                                                                                                                                                                                                                   | • | 3            |                 | 5.5          | V              |

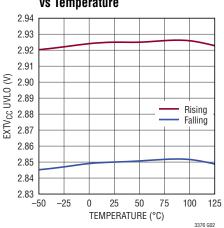

|                              | Undervoltage Threshold on EXTV <sub>CC</sub>                       | EXTV <sub>CC</sub> Voltage Falling                                                                                                                                                                                | • | 2.8          | 2.85            | 2.95         | V              |

|                              | Undervoltage Hysteresis on EXTV <sub>CC</sub>                      |                                                                                                                                                                                                                   |   |              | 75              |              | mV             |

| 1.5A Buck                    | Regulators                                                         |                                                                                                                                                                                                                   |   |              |                 |              |                |

| V <sub>IN</sub>              | Buck Input Voltage Range                                           |                                                                                                                                                                                                                   | • | 3            |                 | 20           | V              |

|                              | Undervoltage Threshold on V <sub>IN</sub>                          | V <sub>IN</sub> Voltage Falling<br>Hysteresis                                                                                                                                                                     | • | 2.5          | 2.6<br>0.2      | 2.7          | V              |

|                              | V <sub>INA-H</sub> Input Supply Current, V <sub>INA-H</sub> = 12V  | All Bucks Off VINB, VINC, VINF, VING VINA, VIND, VINE, VINH                                                                                                                                                       |   |              | 0.7<br>0        | 1.4          | μΑ<br>μΑ       |

|                              |                                                                    | Buck On, Sleeping, V <sub>FB</sub> <sup>+</sup> = 0.41V<br>V <sub>INB</sub> , V <sub>INC</sub> , V <sub>INF</sub> , V <sub>ING</sub><br>V <sub>INA</sub> , V <sub>IND</sub> , V <sub>INE</sub> , V <sub>INH</sub> |   |              | 0.7<br>0        | 1.4          | μA<br>μA       |

|                              |                                                                    | Buck On, SYNC/MODE=INTV <sub>CC</sub>                                                                                                                                                                             |   |              | 5.2             |              | mA             |

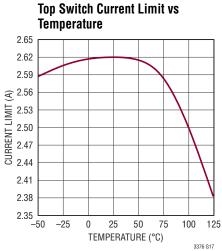

|                              | Top Switch Current Limit, Duty < 18%                               | (Note 5)                                                                                                                                                                                                          |   | 2.3          | 2.62            | 3.0          | A              |

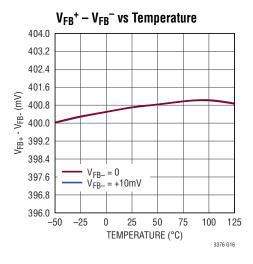

| $V_{FB}^+$                   | Feedback Regulation Voltage                                        |                                                                                                                                                                                                                   | • | 396          | 400             | 404          | mV             |

| I <sub>FB</sub> <sup>+</sup> | Feedback Leakage Current                                           | $V_{FB}^{+} = 0.41V$                                                                                                                                                                                              |   | -30          |                 | 30           | nA             |

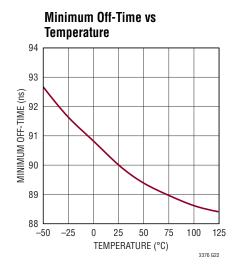

|                              | Minimum Off-Time                                                   |                                                                                                                                                                                                                   |   |              | 90              | 140          | ns             |

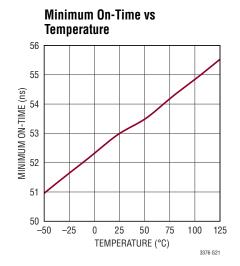

|                              | Minimum On-Time                                                    |                                                                                                                                                                                                                   | • |              | 53              | 85           | ns             |

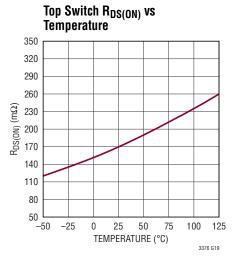

|                              | Top Switch Power FET On-Resistance                                 |                                                                                                                                                                                                                   |   |              | 170             |              | mΩ             |

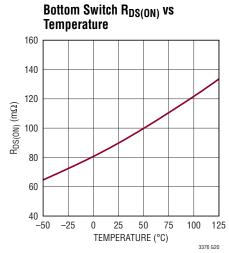

|                              | Bottom Switch Power FET On-Resistance                              |                                                                                                                                                                                                                   |   |              | 90              |              | mΩ             |

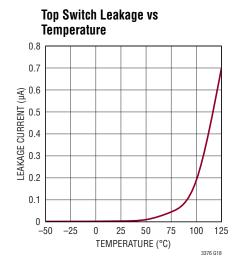

|                              | Top Switch Power FET Leakage                                       | V <sub>INA-H</sub> = 20V, SWA-H = 0V                                                                                                                                                                              |   |              |                 | 0.1          | μA             |

|                              | Bottom Switch Power FET Leakage                                    | V <sub>INA-H</sub> = SWA-H = 20V                                                                                                                                                                                  |   |              | 0.003           | 1            | μA             |

|                              | SW Pull-Down Resistance in Shutdown                                | RUN1-4 = 0V per Output Channel                                                                                                                                                                                    |   |              | 1               |              | kΩ             |

| t <sub>SS</sub>              | Soft-Start Time                                                    | (Note 6)                                                                                                                                                                                                          | • | 0.3          | 1               | 2.5          | ms             |

|                              | Start-Up Delay Time                                                | Starting Up from All EN's Low<br>When at Least One EN Is Already High                                                                                                                                             |   | 100<br>40    | 250<br>100      | 500<br>250   | μs<br>μs       |

|                              | PGOOD Lower Threshold                                              | V <sub>FB</sub> <sup>+</sup> Falling, Percentage of Regulated V <sub>FB</sub> <sup>+</sup>                                                                                                                        | • | 95           | 96.75           | 98.5         | %              |

|                              | PGOOD Lower Threshold Hysteresis                                   |                                                                                                                                                                                                                   |   |              | 1               |              | %              |

|                              | PGOOD Upper Threshold                                              | V <sub>FB</sub> <sup>+</sup> Rising, Percentage of Regulated V <sub>FB</sub> <sup>+</sup>                                                                                                                         | • | 104.5        | 107.5           | 110.5        | %              |

|                              | PGOOD Upper Threshold Hysteresis                                   |                                                                                                                                                                                                                   |   |              | 2.5             |              | %              |

|                              | PGOOD Filtering Time                                               |                                                                                                                                                                                                                   |   |              | 100             | <u></u>      | μs             |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the specified operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ (Note 2). $V_{CC} = V_{INA-H} = 12V$ , RT tied to INTV<sub>CC</sub>, $V_{FB1-4^-} = 0V$ , unless otherwise stated.

| SYMBOL                           | PARAMETER                                | CONDITIONS                                                      | MIN        | TYP        | MAX         | UNITS    |

|----------------------------------|------------------------------------------|-----------------------------------------------------------------|------------|------------|-------------|----------|

| Buck Regula                      | tors Combined                            |                                                                 | •          |            |             |          |

|                                  | Top Switch Current Limit, Duty < 18%     | 1 Buck with 2 Power Stages Combined (Note 5)                    |            | 5.25       |             | A        |

|                                  |                                          | 1 Buck with 3 Power Stages Combined (Note 5)                    |            | 7.88       |             | A        |

|                                  |                                          | 1 Buck with 4 Power Stages Combined (Note 5)                    |            | 10.5       |             | А        |

|                                  |                                          | 1 Buck with 5 Power Stages Combined (Note 5)                    |            | 13.1       |             | A        |

|                                  |                                          | 1 Buck with 6 Power Stages Combined (Note 5)                    |            | 15.8       |             | А        |

|                                  |                                          | 1 Buck with 7 Power Stages Combined (Note 5)                    |            | 18.4       |             | А        |

|                                  |                                          | 1 Buck with 8 Power Stages Combined (Note 5)                    |            | 21         |             | А        |

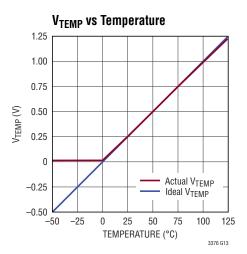

| Temperature                      | Monitor                                  |                                                                 | •          |            |             |          |

| V <sub>TEMP(ROOM)</sub>          | TEMP Voltage at 25°C                     |                                                                 | 220        | 250        | 280         | mV       |

| ΔV <sub>TEMP/°C</sub>            | V <sub>TEMP</sub> Slope                  |                                                                 |            | 10         |             | mV/°C    |

| OT                               | Overtemperature Shutdown (Note 7)        | Temperature Rising                                              |            | 165        |             | °C       |

|                                  | Overtemperature Hysteresis               |                                                                 |            | 10         |             | °C       |

| Current Moni                     | itors                                    |                                                                 | •          | -          |             |          |

|                                  | I <sub>MON1-4</sub> Voltage at 1.5A Load | R <sub>IMON</sub> = 10k, Duty Cycle = 25%                       | 0.9        | 1          | 1.1         | V        |

|                                  | I <sub>MON1-4</sub> Voltage at No Load   | SYNC/MODE = INTV <sub>CC</sub>                                  |            | 0          |             | V        |

|                                  | I <sub>MON1-4</sub> Slope                | R <sub>IMON</sub> = 10k                                         |            | 0.667      |             | V/A      |

| Interface Log                    | gic Pins (CFG0-3, SYNC/MODE, PG00D1-4    | )                                                               |            |            |             |          |

| I <sub>OH</sub>                  | Output High Leakage Current              | PG00D1-4 at 5.5V                                                |            |            | 1           | μА       |

| $V_{OL}$                         | Output Low Voltage                       | PGOOD1-4, 3mA into Pin                                          |            | 0.03       | 0.4         | V        |

| $V_{IH}$                         | Input High Threshold                     | CFG0-3, SYNC/MODE                                               | 1.2        |            |             | V        |

| $V_{IL}$                         | Input Low Threshold                      | CFG0-3, SYNC/MODE                                               | )          |            | 0.4         | V        |

| I <sub>IH,</sub> I <sub>IL</sub> | Input High, Low Leakage Current          | CFG0-3 Pins at INTV <sub>CC</sub> & 0V                          |            |            | 1           | μА       |

|                                  |                                          | SYNC/MODE Pin at 5.5V & 0V                                      |            |            | 1           | μA       |

| Interface Log                    | jic Pins (RUN1-4)                        |                                                                 | 1          |            |             |          |

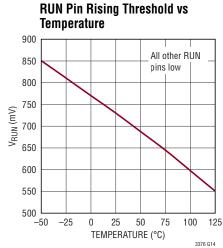

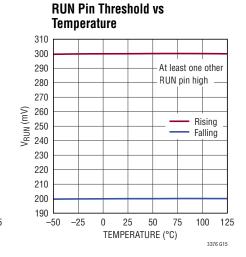

|                                  | RUN Rising Threshold                     | First Regulator Turning On One Regulator or More Already in Use | 350<br>280 | 730<br>300 | 1200<br>320 | mV<br>mV |

|                                  | RUN Falling Threshold                    | Last Regulator Turning Off                                      | 100        | 690        |             | mV       |

|                                  | RUN Falling Threshold                    | One Regulator or More Kept On                                   | 180        | 200        | 220         | mV       |

|                                  | RUN Pin Leakage Current                  | RUN1-4 = 5.5V                                                   |            |            | 1           | μA       |

#### **ELECTRICAL CHARACTERISTICS**

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: The LTC3376 is tested under pulsed load conditions such that  $T_J \sim T_A.$  The LTC3376E is guaranteed to meet specifications from 0°C to 85°C junction temperature. Specifications over the  $-40^{\circ}C$  to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC3376I is guaranteed over the  $-40^{\circ}C$  to 125°C operating junction temperature range. High junction temperatures degrade operating lifetimes; operating lifetime is derated for junction temperatures greater than 125°C. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors. The junction temperature ( $T_J$  in °C) is calculated from ambient temperature ( $T_A$  in °C) and power dissipation ( $P_D$  in Watts) according to the formula:

$T_J = T_A + (P_D \bullet \theta_{JA})$  where  $\theta_{JA}$  (in °C/W) is the package thermal impedance.

**Note 3:** There will be additional switching current on  $V_{INA-H}$  pins.

**Note 4:** Total System current is defined as total current from  $V_{CC} + V_{INA-H}$  when all bucks are on (in Sleep),  $V_{CC} = V_{INA-H} = 12V$ , and EXTV<sub>CC</sub> is bootstrapped to run off of a 3.3V buck.

**Note 5:** The current limit features of this part are intended to protect the IC from short term or intermittent fault conditions. Continuous operation above the specified maximum pin current rating may result in device degradation over time.

**Note 6:** The Soft-Start Time is the time from the start of switching until  $V_{FB}^+ - V_{FB}^-$  reaches 360mV.

**Note 7:** The LTC3376 includes overtemperature protection which protects the device during momentary overload conditions. Junction temperature exceeds the maximum operating junction temperature when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

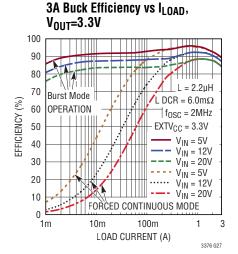

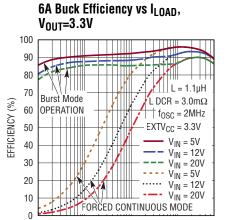

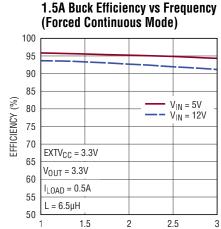

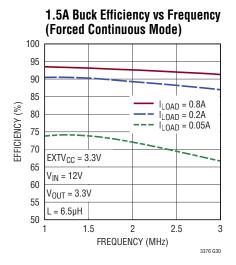

# TYPICAL PERFORMANCE CHARACTERISTICS TA = 25°C, unless otherwise noted.

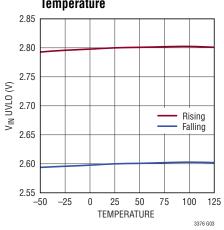

EXTV<sub>CC</sub> Undervoltage Threshold vs Temperature

V<sub>IN</sub> Undervoltage Threshold vs Temperature

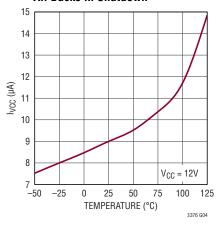

V<sub>CC</sub> Current vs Temperature with All Bucks in Shutdown

V<sub>CC</sub> Current vs Temperature with One Buck On (Sleeping, Not Bootstrapped)

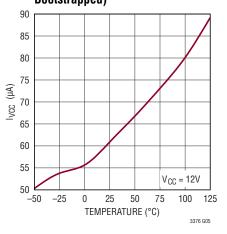

Total System Current vs Temperature with One Buck On (Sleeping, Bootstrapped)

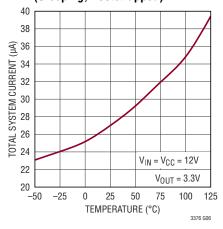

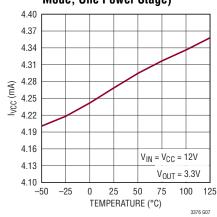

V<sub>CC</sub> Current vs Temperature with One Buck On (Forced Continuous Mode, One Power Stage)

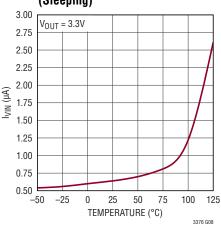

V<sub>IN</sub> Current vs Temperature (Sleeping)

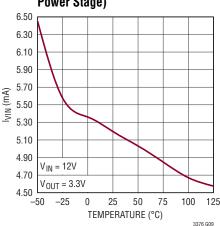

V<sub>IN</sub> Current vs Temperature (Forced Continuous Mode, One Power Stage)

Rev 0

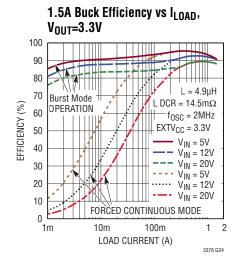

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , unless otherwise noted.

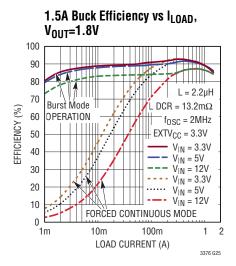

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

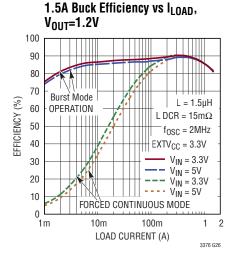

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

1m

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , unless otherwise noted.

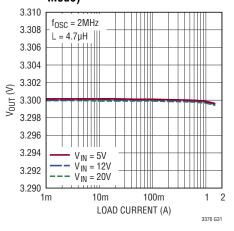

1.5A Buck Regulator Load Regulation (Forced Continuous Mode)

10m

100m

3376 G28

LOAD CURRENT (A)

FREQUENCY (MHz)

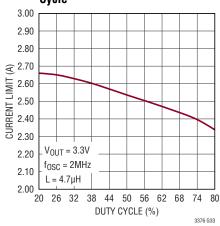

1.5 Buck Current Limit vs Duty Cycle

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

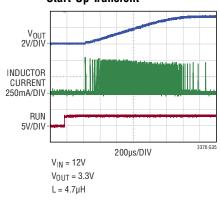

#### 1.5A Buck Regulator No Load **Start-Up Transient**

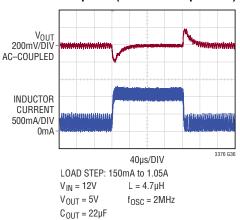

#### 1.5A Buck Regulator, Transient Response (Burst Mode Operation)

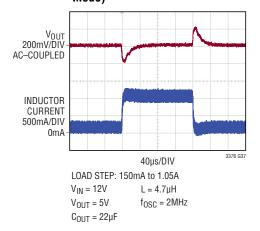

#### 1.5A Buck Regulator, Transient **Response (Forced Continuous** Mode)

**BSTA (Pin A1):** Boost Node for Power Stage A.

BSTB (Pin B2): Boost Node for Power Stage B.

**BSTC (Pin G2):** Boost Node for Power Stage C.

**BSTD** (Pin H1): Boost Node for Power Stage D.

**BSTE (Pin H8):** Boost Node for Power Stage E.

**BSTF (Pin G7):** Boost Node for Power Stage F.

**BSTG (Pin B7):** Boost Node for Power Stage G.

**BSTH (Pin A8):** Boost Node for Power Stage H.

**CFG0 (Pin F2):** Configuration Input Bit. With CFG1, CFG2 and CFG3, CFG0 configures the Buck output current power stage combinations. CFG0 should be tied to either INTV $_{\rm CC}$  or GND. Do not float.

**CFG1 (Pin G6):** Configuration Input Bit. With CFG0, CFG2, and CFG3, CFG1 configures the Buck output current power stage combinations. CFG1 should be tied to either  $INTV_{CC}$  or GND. Do not float.

**CFG2 (Pin G4):** Configuration Input Bit. With CFG0, CFG1, and CFG3, CFG2 configures the Buck output current power stage combinations. CFG2 should be tied to either  $INTV_{CC}$  or GND. Do not float.

**CFG3 (Pin F7):** Configuration Input Bit. With CFG0, CFG1 and CFG2, CFG3 configures the Buck output current power stage combinations. CFG3 should be tied to either  $INTV_{CC}$  or GND. Do not float.

**EXTV**<sub>CC</sub> (**Pin C2**): External V<sub>CC</sub> Low Voltage Supply. The internal LDO regulator draws current from EXTV<sub>CC</sub> instead of from V<sub>CC</sub> when EXTV<sub>CC</sub> is tied to a voltage higher than 3V. For output voltages of 3.3V and above this pin can be tied to that V<sub>OUT</sub>. If this pin is tied to a supply other than a buck output, use a  $4.7\mu F$  local bypass capacitor on this pin. EXTV<sub>CC</sub> should be tied to ground if not used. Do not float.

**FB1+ (Pin D4):** Positive Feedback Pin for Buck Regulator 1. Receives feedback by a resistor divider connected across the output.

**FB2+** (**Pin E4**): Positive Feedback Pin for Buck Regulator 2. Receives feedback by a resistor divider connected across the output.

**FB3+** (**Pin E5**): Positive Feedback Pin for Buck Regulator 3. Receives feedback by a resistor divider connected across the output.

**FB4+** (**Pin D5**): Positive Feedback Pin for Buck Regulator 4. Receives feedback by a resistor divider connected across the output.

**FB1**<sup>-</sup> (**Pin C3**): Negative Feedback Pin for Buck Regulator 1. Connect directly to the GND side of the feedback resistor divider that connects across the output.

**FB2**<sup>-</sup> (**Pin F3**): Negative Feedback Pin for Buck Regulator 2. Connect directly to the GND side of the feedback resistor divider that connects across the output.

**FB3**<sup>-</sup> (**Pin F6**): Negative Feedback Pin for Buck Regulator 3. Connect directly to the GND side of the feedback resistor divider that connects across the output.

**FB4**<sup>-</sup> (**Pin C6**): Negative Feedback Pin for Buck Regulator 4. Connect directly to the GND side of the feedback resistor divider that connects across the output.

**GND (Pin B5):** LTC3376 Ground Pin. Connect this pin to system ground and to the ground plane. Do not float.

**I**<sub>MON1</sub> (**Pin D3**): Current Monitor Pin for Buck Regulator 1. I<sub>MON1</sub> outputs a current of 100μA (typical) at 1.5A load current for each power stage configured. Connect a resistor from I<sub>MON1</sub> to GND. The value of this resistor should be chosen so that I<sub>MON1</sub> is 1V at full load (1.5A per power stage). The I<sub>MON1</sub> voltage will decrease by 0.67V/A at lower load currents. The I<sub>MON1</sub> output current will be 0 when the regulator is sleeping in Burst Mode or is disabled.

$I_{MON2}$  (Pin E3): Current Monitor Pin for Buck Regulator 2.  $I_{MON2}$  outputs a current of 100μA (typical) at 1.5A load current for each power stage configured. Connect a resistor from  $I_{MON2}$  to GND. The value of this resistor should be chosen so that  $I_{MON2}$  is 1V at full load (1.5A per power stage). The  $I_{MON2}$  voltage will decrease by 0.67V/A at lower load currents. The  $I_{MON2}$  output current will be 0 when the regulator is sleeping in Burst Mode or is disabled.

**I**<sub>MON3</sub> (**Pin E6**): Current Monitor Pin for Buck Regulator 3. I<sub>MON3</sub> outputs a current of 100μA (typical) at 1.5A load current for each power stage configured. Connect a resistor from I<sub>MON3</sub> to GND. The value of this resistor should be chosen so that I<sub>MON3</sub> is 1V at full load (1.5A per power stage). The I<sub>MON3</sub> voltage will decrease by 0.67V/A at lower load currents. The I<sub>MON3</sub> output current will be 0 when the regulator is sleeping in Burst Mode or is disabled.

$I_{MON4}$  (Pin D6): Current Monitor Pin for Buck Regulator 4.  $I_{MON4}$  outputs a current of 100μA (typical) at 1.5A load current for each power stage configured. Connect a resistor from  $I_{MON4}$  to GND. The value of this resistor should be chosen so that  $I_{MON4}$  is 1V at full load (1.5A per power stage). The  $I_{MON4}$  voltage will decrease by 0.67V/A at lower load currents. The  $I_{MON4}$  output current will be 0 when the regulator is sleeping in Burst Mode or is disabled.

INTV<sub>CC</sub> (Pin B3): Internal 3V V<sub>CC</sub> Regulator Bypass Pin. The control circuits are powered from this voltage. Do not load the INTV<sub>CC</sub> pin with external circuitry exceeding 2mA. If overloaded the LTC3376 will shut down. INTV<sub>CC</sub> current is supplied from EXTV<sub>CC</sub> if V<sub>EXTVCC</sub> > 3V, otherwise current is drawn from V<sub>CC</sub>. Bypass to GND with a single  $4.7\mu F$  or larger low ESR ceramic capacitor.

**INTV**<sub>CC\_P</sub> (**Pin B6**): Internal V<sub>CC</sub> Power Stage Supply. The internal power drivers are powered from this voltage. The INTV<sub>CC\_P</sub> pin is for internal use only. Bypass to GND with a single 10 $\mu$ F or larger low ESR ceramic capacitor. In all applications, INTV<sub>CC\_P</sub> must connect to INTV<sub>CC</sub>.

**PGNDA (Pin A4):** Ground Supply for Power Stage A. Connect the GND side of the  $V_{INA}$  bypass capacitors directly to this pin and then to the ground plane.

**PGNDB (Pin D1):** Ground Supply for Power Stage B. Connect the GND side of the  $V_{INB}$  bypass capacitors directly to this pin and then to the ground plane.

**PGNDC (Pin E1):** Ground Supply for Power Stage C. Connect the GND side of the  $V_{INC}$  bypass capacitors directly to this pin and then to the ground plane.

**PGNDD** (Pin H4): Ground Supply for Power Stage D. Connect the GND side of the  $V_{IND}$  bypass capacitors directly to this pin and then to the ground plane.

**PGNDE (Pin H5):** Ground Supply for Power Stage E. Connect the GND side of the  $V_{INE}$  bypass capacitors directly to this pin and then to the ground plane.

**PGNDF (Pin E8):** Ground Supply for Power Stage F. Connect the GND side of the V<sub>INF</sub> bypass capacitors directly to this pin and then to the ground plane.

**PGNDG (Pin D8):** Ground Supply for Power Stage G. Connect the GND side of the  $V_{ING}$  bypass capacitors directly to this pin and then to the ground plane.

**PGNDH (Pin A5):** Ground Supply for Power Stage H. Connect the GND side of the  $V_{INH}$  bypass capacitors directly to this pin and then to the ground plane.

**PGOOD1** (Pin D2): Power Good Pin for Buck Regulator 1 (Active High). Open-drain output. This pin is driven low when Buck 1's regulated output voltage falls below its PGOOD threshold or rises above its overvoltage threshold. PGOOD1 is also pulled low in the following scenarios: if the buck is disabled, if the buck is going through soft-start, if  $INTV_{CC}$  is below the UVLO threshold, or if the LTC3376 is in OT.

**PGOOD2** (**Pin E2**): Power Good Pin for Buck Regulator 2 (Active High). Open-drain output. This pin is driven low when Buck 2's regulated output voltage falls below its PGOOD threshold or rises above its overvoltage threshold. PGOOD2 is also pulled low in the following scenarios: if the buck is disabled, if the buck is going through soft-start, if  $INTV_{CC}$  is below the UVLO threshold, or if the LTC3376 is in OT.

**PGOOD3** (Pin E7): Power Good Pin for Buck Regulator 3 (Active High). Open-drain output. This pin is driven low when Buck 3's regulated output voltage falls below its PGOOD threshold or rises above its overvoltage threshold. PGOOD3 is also pulled low in the following scenarios: if the buck is disabled, if the buck is going through soft-start, if INTV<sub>CC</sub> is below the UVLO threshold, or if the LTC3376 is in OT.

**PGOOD4 (Pin D7):** Power Good Pin for Buck Regulator 4 (Active High). Open-drain output. This pin is driven low when Buck 4's regulated output voltage falls below its PGOOD threshold or rises above its overvoltage threshold. PGOOD4 is also pulled low in the following scenarios: if the buck is disabled, if the buck is going through soft-start, if INTV<sub>CC</sub> is below the UVLO threshold, or if the LTC3376 is in OT.

**RT (Pin G5):** Timing Resistor Pin for Setting Oscillator Frequency. This pin provides two modes of setting the switching frequency when not synchronizing to an external clock. Connecting a resistor from RT to GND sets the switching frequency based on the resistor value. If RT is tied to INTV<sub>CC</sub> the default internal 2MHz oscillator is used. Do not float.

**RUN1 (Pin C4):** Enable Input for Buck Regulator 1. Active high. Do not float.

**RUN2 (Pin F4):** Enable Input for Buck Regulator 2. Active high. In configurations where the Enable Input for Buck 2 is not used, tie RUN2 to GND. Do not float.

**RUN3 (Pin F5):** Enable Input for Buck Regulator 3. Active high. In configurations where the Enable Input for Buck 3 is not used, tie RUN3 to GND. Do not float.

**RUN4 (Pin C5):** Enable Input for Buck Regulator 4. Active high. In configurations where the Enable Input for Buck 4 is not used, tie RUN4 to GND. Do not float.

**SWA (Pin A2):** Switch Node for Power Stage A. External inductor connects to this pin.

**SWB (Pin B1):** Switch Node for Power Stage B. External inductor connects to this pin.

**SWC (Pin G1):** Switch Node for Power Stage C. External inductor connects to this pin.

**SWD (Pin H2):** Switch Node for Power Stage D. External inductor connects to this pin.

**SWE (Pin H7):** Switch Node for Power Stage E. External inductor connects to this pin.

**SWF (Pin G8):** Switch Node for Power Stage F. External inductor connects to this pin.

**SWG (Pin B8):** Switch Node for Power Stage G. External inductor connects to this pin.

**SWH (Pin A7):** Switch Node for Power Stage H. External inductor connects to this pin.

**SYNC/MODE (Pin G3):** Oscillator Synchronization and Mode Select Pin. Driving SYNC/MODE with an external clock signal synchronizes all switches to the applied frequency, and configures the buck converters to operate in forced continuous mode. Slope compensation automatically adapts to the external clock frequency. The absence of an external clock signal enables the frequency to be programmed by the RT pin. When not synchronizing to an external clock this input determines how the LTC3376 operates at light loads. Connecting this pin to ground selects Burst Mode operation. Connecting this pin to INTV<sub>CC</sub> selects forced continuous mode operation. Do not float.

**TEMP (Pin C7):** Temperature Indication Pin. TEMP outputs a voltage of 250mV (typical) at 25°C. The TEMP voltage changes by 10mV/°C (typical) giving an external indication of the LTC3376 internal die temperature.

$V_{CC}$  (Pin B4): Internal Bias Supply. Bypass to GND with a 4.7µF or larger ceramic capacitor.  $V_{CC}$  has to be present even when the EXTV<sub>CC</sub> pin is used and must come up before EXTV<sub>CC</sub>.

$V_{INA}$  (Pin A3): Input Supply for Power Stage A. Bypass to PGNDA with a 1µF ceramic capacitor and 10µF or larger ceramic capacitor.

$V_{INB}$  (Pin C1): Input Supply for Power Stage B. Bypass to PGNDB with a 1µF ceramic capacitor and 10µF or larger ceramic capacitor.

$V_{INC}$  (Pin F1): Input Supply for Power Stage C. Bypass to PGNDC with a 1µF ceramic capacitor and 10µF or larger ceramic capacitor.

$V_{IND}$  (Pin H3): Input Supply for Power Stage D. Bypass to PGNDD with a 1µF ceramic capacitor and 10µF or larger ceramic capacitor.

$V_{INE}$  (Pin H6): Input Supply for Power Stage E. Bypass to PGNDE with a 1µF ceramic capacitor and 10µF or larger ceramic capacitor.

$V_{INF}$  (Pin F8): Input Supply for Power Stage F. Bypass to PGNDF with a 1µF ceramic capacitor and 10µF or larger ceramic capacitor.

$V_{ING}$  (Pin C8): Input Supply for Power Stage G. Bypass to PGNDG with a 1µF ceramic capacitor and 10µF or larger ceramic capacitor.

$V_{INH}$  (Pin A6): Input Supply for Power Stage H. Bypass to PGNDH with a 1µF ceramic capacitor and 10µF or larger ceramic capacitor.

### **BLOCK DIAGRAM**

16

#### **Buck Switching Regulators**

The LTC3376 is a 20V monolithic, constant frequency, four channel, 12A configurable, peak current mode step-down DC/DC converter. The device includes four synchronous buck converters, configured to share eight 1.5A power stages. The LTC3376 includes the integration of ceramic capacitors into the package for all BST pins. These capacitors reduce PC board space by eliminating the need for external BST capacitors.

The buck switching regulators are internally compensated and require external feedback resistors to set the output voltage. An internal oscillator, which can be synchronized to an external oscillator, turns on the internal top power switch at the beginning of each clock cycle. Current in the inductor ramps up until the top switch current comparator trips and turns off the top power switch. The peak inductor current at which the top switch turns off is controlled by an internal V<sub>C</sub> voltage which the error amplifier regulates by comparing the voltage on the feedback pin with an internal 400mV reference. When the load current increases. it causes a reduction in the feedback voltage relative to the reference causing the error amplifier to raise the V<sub>C</sub> voltage until the average inductor current matches the new load current. When the top power switch turns off, the bottom power switch turns on until the next clock cycle begins or, if in Burst Mode, until the inductor current falls to zero.

Each buck converter can operate at an independent V<sub>IN</sub> voltage and has its own FB+, FB-, RUN, I<sub>MON</sub>, and PGOOD pins to maximize flexibility. The RUN pins have two different enable threshold voltages that depend on the operating state of the LTC3376. The first buck regulator to turn on will have a RUN pin rising threshold of 730mV(typ). The last buck regulator to turn off will have a RUN pin falling threshold of 690mV(typ). If any one buck regulator is on, all other RUN pins will use the bandgap-based precision thresholds off 300mV(typ) rising and 200mV(typ) falling. The precision RUN thresholds may be used to provide event-based power-up sequencing by connecting the RUN pin to the output of another buck through a resistor divider. All buck regulators have forward and reverse-current limiting, short-circuit protection, and soft-start to limit inrush current during start-up. If the RUN pin of a buck is low, that buck is shut down to a low quiescent current state and the SW pin is pulled to PGND through a 1k resistor. If all buck regulators are off, most top level circuits are shut down, and the quiescent current of the LTC3376 is  $9\mu$ A(typ). When a buck is enabled there is a  $100\mu$ s(typ) delay before switching commences and the soft start ramp begins. If a buck is the first one to be enabled, then this delay is  $250\mu$ s(typ).

The buck switching regulators are phased in 90° steps to reduce noise and input ripple. The phase step determines the fixed edge of the switching sequence, which is when the top switch turns on. The top switch off (bottom switch on) phase is subject to the duty cycle demanded by the regulator. Buck 2 is set to 0°. Buck 1 is set to 90°. Buck 4 is set to 180°. Buck 3 is set to 270°.

#### **Buck Regulators with Combined Power Stages**

Up to four buck regulators may be combined in a masterslave configuration in various combinations by setting the CFG0, CFG1, CFG2, and CFG3 pins. These configuration pins should either be tied to ground or tied to INTV<sub>CC</sub> in accordance with the desired configuration (Table 1). Any combined SW pins must be tied together, as must any of the combined V<sub>IN</sub> and BST pins. The bucks have a com $mon\,V_{IN}$  but each  $V_{IN}$  pin should have its own input bypass capacitors (see Applications Information). RUN1, FB1+, FB1<sup>-</sup>, I<sub>MON1</sub>, and PGOOD1 are utilized by Buck 1. RUN2, FB2+, FB2-, I<sub>MON2</sub>, and PGOOD2 are utilized by Buck 2. RUN3, FB3+, FB3-, I<sub>MON3</sub>, and PGOOD3 are utilized by Buck 3. RUN4, FB4+, FB4-, I<sub>MON4</sub>, and PGOOD4 are utilized by Buck 4. If a buck is not utilized in a particular configuration, then the RUN, FB+, and FB-, I<sub>MON</sub>, PGOOD pins should be tied to GND. Its V<sub>IN</sub>, SW, and BST pins will be used as a slave to another master and must be connected to that master's respective power pins.

Buck regulators can be combined to provide 3A, 4.5A, 6A, 7.5A, 9A, 10.5A, or 12A of output load current. For example, code 0110 (CFG[3:0]) configures Buck 1 to operate as a 4.5A regulator through  $V_{\text{IN}}/\text{SW/BST}$  pairs A, B, and H, while Buck 2 is disabled, Buck 3 operates as a 6A regulator through  $V_{\text{IN}}/\text{SW/BST}$  pairs C, D, E, and F, and Buck 4 operates as a 1.5A regulator through  $V_{\text{IN}}/\text{SW/BST}$  pair G.

Table 1. Master-Slave Program Combinations (Each Letter Corresponds to a V<sub>IN</sub>/SW/BST/PGND Pair)

|      |      |      |      | OUT      | PUT CONF | IGURATIO | N      |

|------|------|------|------|----------|----------|----------|--------|

| CFG3 | CFG2 | CFG1 | CFG0 | BUCK 1   | BUCK 2   | BUCK 3   | BUCK 4 |

| 0    | 0    | 0    | 0    | AB       | CD       | EF       | GH     |

| 0    | 0    | 0    | 1    | ABH      | CD       | EF       | G      |

| 0    | 0    | 1    | 0    | ABH      | CDE      | F        | G      |

| 0    | 0    | 1    | 1    | ABDH     | С        | EF       | G      |

| 0    | 1    | 0    | 0    | AB       | CDE      | -        | FGH    |

| 0    | 1    | 0    | 1    | ABCD     | -        | EF       | GH     |

| 0    | 1    | 1    | 0    | ABH      | -        | CDEF     | G      |

| 0    | 1    | 1    | 1    | ABCD     | -        | -        | EFGH   |

| 1    | 0    | 0    | 0    | ABDEH    | С        | F        | G      |

| 1    | 0    | 0    | 1    | ABCDH    | -        | EF       | G      |

| 1    | 0    | 1    | 0    | ABCDE    | -        | -        | FGH    |

| 1    | 0    | 1    | 1    | ABCDEH   | -        | F        | G      |

| 1    | 1    | 0    | 0    | ABCDEF   | -        | -        | GH     |

| 1    | 1    | 0    | 1    | ABCDEFH  | -        | -        | G      |

| 1    | 1    | 1    | 0    | ABCDEFGH | -        | -        | -      |

| 1    | 1    | 1    | 1    | AB       | CD       | EF       | GH     |

#### **Mode Selection**

The buck switching regulators can operate in two different modes set by the SYNC/MODE pin: Burst Mode (when the SYNC/MODE pin is set low) and forced continuous PWM mode (when the SYNC/MODE pin is set high). The SYNC/MODE pin sets the same operating mode for all buck switching regulators.

Inforced continuous mode, the oscillator runs continuously and the buck switch currents are allowed to reverse under light load conditions to maintain regulation. This mode allows the buck to run at a fixed frequency with minimal output ripple, even with zero output load.

In Burst Mode operation, at light loads the output capacitor is charged to a voltage slightly higher than its regulation point. The regulator then goes into a sleep state, during which time the output capacitor provides the load current. In sleep most of the regulator's circuitry is powered down, helping conserve input power. When the output capacitor drops below its programmed value, the circuitry is powered on and another burst cycle begins. The sleep time decreases as load current increases. In Burst Mode operation, the

regulator will burst only at light loads. At higher loads it will operate in constant frequency PWM mode.

#### Synchronizing the Oscillator to an External Clock

Selection of the operating frequency is a trade-off between efficiency and component size. High frequency operation allows the use of smaller inductor and capacitor values and improves transient response. Operation at lower frequencies improves efficiency by reducing internal gate charge losses and allows more extreme  $V_{\mbox{\scriptsize IN}}$  to  $V_{\mbox{\scriptsize OUT}}$  ratios. However, this also requires larger inductance values and/or capacitance to maintain low output voltage ripple. The LTC3376 has a default operating frequency of 2MHz.

The LTC3376's internal oscillator can alternatively be synchronized through an internal PLL circuit to an external frequency by applying a square wave clock signal to the MODE/SYNC pin. During synchronization, the top power device turn-on of buck 2 is locked to 110ns after the rising edge of the external frequency source. Buck 1 will be 90° out of phase with Buck 2. Buck 4 will be 180° out of phase with Buck 2. Buck 3 will be 270° out of phase with Buck 2. When synchronizing to an external clock, the buck regulators operate in forced continuous mode. The synchronization frequency range is 1MHz to 3MHz.

After detecting an external clock on the first rising edge of the SYNC pin, the internal PLL starts at the default frequency. The internal PLL then requires up to 1ms to gradually adjust its operating frequency to match the frequency and phase of the SYNC signal.

When the external clock is removed the LTC3376 will detect the absence of the external clock, and the oscillator gradually adjusts its operating frequency back to the default.

### Power Failure Reporting Via PGOOD Pins

Power failure conditions are reported back by each buck's associated PGOOD pin. Each buck switching regulator has an internal power good (PGOOD\_INT) signal. When the regulated output voltage of an enabled switcher rises above 97.75% of its regulation output voltage the PGOOD\_INT signal transitions high. If the regulated output voltage subsequently falls below 96.75%(typ) of the regulation

output voltage the PGOOD\_INT signal is pulled low. If a buck is enabled, its PGOOD\_INT signal must be high for its external PGOOD pin to be high. An enabled buck's internal PGOOD\_INT signal must stay low for greater than 100µs(typ) before its external PGOOD pin is pulled low, indicating to a microprocessor that a power failure fault has occurred. This 100µs filter time prevents the pin from being pulled low during a load transient. In addition, whenever the internal PGOOD\_INT signal transitions high there will also be a 100µs assertion delay.

The LTC3376 also reports overvoltage conditions at the PGOOD pins. If an enabled buck regulator's output voltage rises above 107.5% (typ) of the regulation value, its PGOOD pin is pulled low after 100µs. Similarly, if an enabled output that is overvoltage subsequently falls below 105% (typ) of its regulated output voltage, its PGOOD pin transitions high again after 100µs.

An error condition that pulls the PGOOD pin low is not latched. When the error condition goes away, the PGOOD pin is released and is pulled high if no other error condition exists. PGOOD is also pulled low in the following scenarios: if the buck is disabled, if the buck is going through soft-start, if  $INTV_{CC}$  is below the UVLO threshold, or if the LTC3376 is in OT (see below).

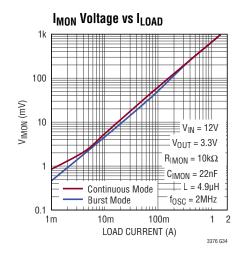

#### **Current Monitors**

Each buck regulator has a current monitor that supplies a current to the  $I_{MON}$  pin that is proportional to the average buck load current. The external resistor required from the  $I_{MON}$  pin to ground is a function of how many power stages are configured for a particular buck. If a buck regulator is configured to have only one power stage then a 10k resistor should be connected from  $I_{MON}$  to ground. At full load (1.5A) the voltage on the  $I_{MON}$  pin will be 1V (typical). At half load (0.75A) the voltage on the  $I_{MON}$  pin will be 0.5V. For combined output stages, the resistor required at the  $I_{MON}$  pin is given by:

$$R_{IMON} = \frac{10k\Omega}{[\# of channels]}$$

(1)

The  $I_{MON}$  pin voltage represents the average buck load and will take a few 100 $\mu$ s to settle. The current monitor is designed to be most accurate in continuous conduction

mode but can function in Burst Mode at moderate loads with reduced accuracy if an external capacitor is applied to the  $I_{MON}$  pin. This capacitor should be selected such that the RC time constant is about 250 $\mu$ s or larger. The capacitor value to use on the  $I_{MON}$  pin (if desired) is given by:

$$C_{\text{IMON}} \ge \frac{250 \mu s}{R_{\text{IMON}}} \tag{2}$$

#### Temperature Monitoring and Overtemperature Protection

To prevent thermal damage to the LTC3376 and its surrounding components, the LTC3376 incorporates an overtemperature (OT) function. When the LTC3376 die temperature reaches 165°C (typical) all enabled buck switching regulators are shut down and remain in shutdown until the die temperature falls to 155°C (typical).

The die temperature may be read by sampling the analog TEMP pin voltage. The temperature, T, indicated by the TEMP pin voltage is given by:

$$T = \frac{V_{TEMP}}{10mV} \cdot 1^{\circ}C \tag{3}$$

where  $V_{\mbox{\scriptsize TEMP}}$  is the voltage on the TEMP pin.

The typical voltage at the TEMP pin is 250mV at 25°C.  $V_{TEMP}$  readings are valid for die temperatures higher than approximately 10°C. A bypass cap is not needed on the TEMP pin. If stray capacitance is present on the TEMP pin that is greater than 30pF, then a 15k resistor must be added in series at the pin to ensure the stability of the temperature monitor. If temperature monitoring functionality is not needed, the user may shut down the temperature monitor by tying TEMP to INTV<sub>CC</sub>. This will reduce quiescent current by 5 $\mu$ A (typical). If none of the buck switching regulators are enabled, the temperature monitor is also shutdown to reduce quiescent current.

## INTV<sub>CC</sub> Regulator

An internal low dropout (LDO) regulator produces a 3V supply from  $V_{CC}$  that powers the INTV<sub>CC</sub> pin and internal bias circuitry. The INTV<sub>CC</sub> can supply enough current for the LTC3376's circuitry and must be bypassed to ground with a minimum of 4.7µF ceramic capacitor. The INTV<sub>CC</sub> P

Rev (

pin powers all of the MOSFET gate drivers, must have its own  $10\mu\text{F}$  bypass cap, and must be connected on the board to INTV<sub>CC</sub>. Good bypassing is necessary to supply the high transient currents required by the power MOSFET drivers.

To improve efficiency the internal LDO can also draw current from the EXTV $_{CC}$  pin if the EXTV $_{CC}$  pin is 3V or higher.  $V_{CC}$  has to be present even if EXTV $_{CC}$  is used. Typically the EXTV $_{CC}$  pin can be tied to an output of one of the LTC3376 bucks, or it can be tied to an external supply of

3V or above. If EXTV<sub>CC</sub> is connected to a supply other than a buck output, be sure to bypass it with a local ceramic capacitor. If the EXTV<sub>CC</sub> pin is below 2.8V, the internal LDO will consume current from V<sub>CC</sub>. Applications with high input voltage and high switching frequency in which the LDO pulls current from V<sub>CC</sub> will increase die temperature because of the higher power dissipation in the LDO. Do not load the INTV<sub>CC</sub> pin with external circuitry exceeding 2mA.

#### **APPLICATIONS INFORMATION**

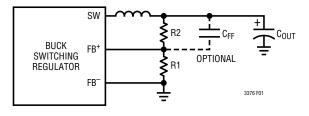

# Buck Switching Regulator Output Voltage and Feedback Network

The output voltage of each buck switching regulator is programmed by a resistor divider across the switching regulator's output connecting to its feedback pin and is given by  $V_{OUT} = V_{FB}^+(1 + R2/R1)$  as shown in Figure 1 where  $V_{FB}^+ = 400 \text{mV}$ . Typical values for R1 range from 20k to 200k. 1% or better resistors are recommended to maintain output voltage accuracy. The buck regulator transient response may improve with an optional phase lead capacitor  $C_{FF}$  that helps cancel the pole created by the feedback resistors and the input capacitance of the FB+ pin. Experimentation with capacitor values between 2pF and 22pF may improve transient response if the resistor divider has a large  $V_{OUT}/V_{FB}^+$  ratio.

The LTC3376 includes low offset, high input impedance differential sense for applications that require remote sensing. Connect FB<sup>+</sup> to the center tap of the feedback divider across the output load, and FB<sup>-</sup> to the load ground.

Figure 1. Feedback Components

#### **Operating Frequency Selection and Trade-Offs**

Selection of the operating frequency is a trade-off between efficiency, component size, transient response, and input voltage range. The advantage of high frequency operation is that smaller inductor and capacitor values may be used. Higher switching frequencies allow for higher control loop bandwidth and, therefore, faster transient response. The disadvantages of higher switching frequencies are lower efficiency, because of increased switching losses, and a smaller input voltage range, because of minimum switch on-time limitations.

The operating frequency for all of the LTC3376 buck regulators can be determined by an external resistor that is connected from the RT pin to ground. The operating frequency is calculated using the following equation:

$$f_{OSC} = 2MHz \left( \frac{402k\Omega}{R_T} \right) \tag{4}$$

While the LTC3376 is designed to function with operating frequencies between 1MHz and 3MHz, it has internal safety clamps that prevent the oscillator from running faster than 4MHz (typical) or slower than 500kHz (typical). Tying the RT pin to INTV<sub>CC</sub> sets the oscillator to the default internal operating frequency of 2MHz (typical).

Although the maximum programmable switching frequency is 3MHz for the LTC3376, the minimum on-time of the LTC3376 imposes a minimum operating duty cycle. The typical minimum on-time is 53ns. The highest

Rev 0

#### APPLICATIONS INFORMATION

switching frequency (f<sub>SW(MAX)</sub>) for low duty cycle applications can be calculated as follows:

$$f_{SW(MAX)} = \frac{V_{OUT} + V_{BOTSW}}{t_{ON(MIN)} (V_{IN(MAX)} - V_{TOPSW} + V_{BOTSW})} (5)$$

where  $V_{IN(MAX)}$  is the maximum input voltage,  $V_{OUT}$  is the output voltage,  $V_{TOPSW}$  and  $V_{BOTSW}$  are the internal switch drops, and  $t_{ON(MIN)}$  is the minimum top switch on-time. This equation shows that a slower switching frequency is necessary to accommodate a very high  $V_{IN}/V_{OLIT}$  ratio.

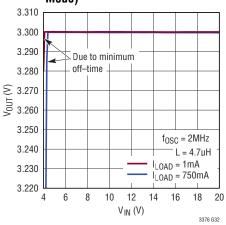

For higher duty cycle applications, the minimum off-time also imposes a max switching frequency which can be calculated as follows:

$$f_{SW(MAX)} = \frac{V_{IN} - V_{OUT} - V_{TOPSW}}{t_{OFF(MIN)} (V_{IN} + V_{BOTSW} - V_{TOPSW})}$$

(6)

where  $t_{OFF(MIN)}$  is the minimum top switch off-time. This equation shows that a slower switching frequency is also necessary to accommodate a very low  $V_{IN}/V_{OLIT}$  ratio.

#### **Inductor Selection and Maximum Output Current**

Considerations in choosing an inductor are inductance value, RMS current rating, saturation current rating, DCR, and core loss.

If the duty cycle of operation is 50% or less, choose the inductor based on the following equation:

$$L = V_{OUT} \cdot \frac{1 - \frac{V_{OUT}}{V_{IN(MAX)}}}{0.2 \cdot I_{MAX} \cdot f_{SW}} \text{ for } \frac{V_{OUT}}{V_{IN}} \le 0.5$$

(7)

where  $f_{SW}$  is the switching frequency,  $V_{IN(MAX)}$  is the maximum input voltage that the buck will run at, and  $I_{MAX}$  is 1.5A times the number of power stages (the maximum rated load current for the LTC3376). For operation at duty cycles higher than 50%, use instead the following equation to select the inductor:

$$L = 1.25 \bullet \frac{V_{IN(MAX)}}{f_{SW} \bullet I_{MAX}} \text{ for } \frac{V_{OUT}}{V_{IN}} > 0.5$$

(8)

To avoid overheating of the inductor, choose an inductor with an RMS current rating that is greater than the maximum expected output load of the application. Overload and short-circuit conditions should also be taken into consideration.

In addition, ensure that the saturation current rating (typically labeled  $I_{SAT}$ ) is higher than the maximum expected load plus half the inductor ripple:

$$I_{SAT} > I_{LOAD(MAX)} + \frac{1}{2}\Delta I_{L}$$

(9)

where  $I_{LOAD(MAX)}$  is the maximum output load current and  $\Delta I_{L}$  is the inductor ripple current as calculated by:

$$\Delta I_{L} = \frac{V_{OUT}}{L \cdot f_{SW}} \cdot \left(1 - \frac{V_{OUT}}{V_{IN(MAX)}}\right)$$

(10)

A more conservative choice would be to choose an inductor with an I<sub>SAT</sub> rating higher than the maximum current limit of the LTC3376 which is 3.0A per power stage.

For highest efficiency, choose an inductor with the lowest series resistance (DCR). The core material should be intended for high frequency applications. Table 2 shows recommended inductors from several manufacturers.

#### **Input Capacitors**

The LTC3376 has individual input supply pins for each buck power stage. All of these pins must be decoupled with low ESR capacitors to their own PGND. These capacitors should be placed as close to the pins as possible. Ceramic dielectric capacitors are a good compromise between high dielectric constant and stability versus temperature and DC bias. Note that the capacitance of a capacitor deteriorates at higher DC bias. It is important to consult manufacturer data sheets and obtain the true capacitance of a capacitor at the DC bias voltage that it will operate at. For this reason, avoid the use of Y5V dielectric capacitors. The X5R/X7R dielectric capacitors offer good overall performance. See Table 3 for recommended ceramic capacitor manufacturers.

Regardless of how the power stages are configured, each input supply voltage pin, V<sub>INA-H</sub>, needs to be decoupled

# **APPLICATIONS INFORMATION**

Table 2. Recommended Inductors

| PART NUMBER                                                          | L<br>(µH)               | MAX DCR<br>(mΩ)              | CURRENT RATING<br>(A)                                        | DIMENSIONS<br>(L × W × H)                                                                | VENDOR                                      |

|----------------------------------------------------------------------|-------------------------|------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------|

| XEL4030-102MEB<br>XFL4020-152MEB<br>XEL4030-222MEB<br>XFL4020-472MEB | 1<br>1.5<br>2.2<br>4.7  | 9.78<br>15.8<br>22.1<br>57.4 | 15.8 9.1 4.3mm × 4.3mm × 2.1mm<br>22.1 7.8 4mm × 4mm × 3.1mm |                                                                                          | Coilcraft<br>www.coilcraft.com              |

| 744383360068<br>74438357010<br>74404042015<br>74439344022            | 0.68<br>1<br>1.5<br>2.2 | 27<br>13.5<br>31<br>10.5     | 4.5<br>7.4<br>2.95<br>8                                      | 3mm × 3mm × 2mm<br>4.1mm × 4.1mm × 3.1mm<br>4mm × 4mm × 1.8mm<br>6.65mm × 6.65mm × 3.3mm | Wurth Electronics Inc.<br>www.we-online.com |

| PCMB042T-1R0MS<br>PCMB053T-1R5MS                                     | 1<br>1.5                | 27<br>20                     | 4.5<br>6                                                     | 4.15mm × 4mm × 1.8mm<br>4.7mm × 4.85mm × 2.8mm                                           | Susumu<br>www.susumu-usa.com                |

| FDSD0420-H-R68M=P3<br>FDSD0420D-1R0M=P3<br>FDSD0420D-2R2M=P3         | 0.68<br>1<br>2.2        | 22<br>29<br>47               | 6.5<br>5.1<br>3.6                                            | 4.2mm × 4.2mm × 2mm<br>4.2mm × 4.2mm × 2mm<br>4.2mm × 4.2mm × 2mm                        | Murata<br>www.murata.com                    |

independently to PGNDA-H with a  $1\mu F$  capacitor as close to the pins as possible and at least a  $10\mu F$  capacitor. Connect each ground of each capacitor to a wide PCB trace on the top layer of the PCB that connects directly to the PGND pin and then to the GND plane.

Note that larger input capacitance is required when a lower switching frequency is used. If the input power source has high impedance, or if there is significant inductance due to long wires or cables, additional bulk capacitance may be necessary. This can be provided with a low performance electrolytic capacitor.

A ceramic input capacitor combined with trace or cable inductance forms a high quality (underdamped) tank circuit. If the LTC3376 circuit is plugged in to a live supply, the input voltage can ring to twice its nominal value, possibly exceeding the LTC3376's voltage rating. This situation is easily avoided (see Linear Technology Application Note 88).

**Table 3. Ceramic Capacitor Manufacturers**

| VENDOR      | URL             |

|-------------|-----------------|

| AVX         | www.avxcorp.com |

| Murata      | www.murata.com  |

| TDK         | www.tdk.com     |

| Taiyo Yuden | www.t-yuden.com |

#### Output Capacitor, Output Ripple, and Loop Response

The output capacitor has two essential functions. Along with the inductor, it filters the square wave generated at

the LTC3376 SW pins to produce the DC output. In this role it determines the output ripple. Thus, low impedance at the switching frequency is important. The second function is to store energy in order to satisfy transient loads and to stabilize the LTC3376's control loop. Ceramic capacitors have very low equivalent series resistance (ESR) and provide the best ripple performance. For good starting values, see the Typical Applications. Use X5R or X7R ceramic capacitors. This choice will provide low output ripple and good transient response.

The LTC3376 is internally compensated and has been designed to operate at a high bandwidth for fast transient response capability. The selection of  $C_{OUT}$  will affect the bandwidth of the system and the optimal value is given by the following equation:

$$C_{OUT} = 100 \bullet \frac{\text{(# of power stages)}}{f_{SW} \bullet V_{OUT}}$$

(11)

where f<sub>SW</sub> is the switching frequency.

This calculated C<sub>OUT</sub> value is the capacitance required after voltage and temperature derating. A lower value of output capacitor can be used to save space and cost but transient performance will suffer and may cause loop instability. See the Typical Applications in this data sheet for suggested capacitor values.

When choosing a capacitor, special attention should be given to the data sheet to calculate the effective capacitance under the relevant operating conditions of voltage

Rev 0

#### APPLICATIONS INFORMATION

bias and temperature. A physically larger capacitor or one with a higher voltage rating may be required.

#### **PCB Considerations**

When laying out the printed circuit board, the following list should be followed to ensure proper operation of the LTC3376:

- 1. The input supply pins ( $V_{INA-H}$ ) should each have local decoupling capacitors with their ground pins connecting back to the PGND pin (PGNDA-H) of the IC with as short and wide a trace as possible before connecting to the GND plane. The  $V_{IN}$  and PGND pins are placed next to each other on the outer edge of the IC for this purpose. Note that large switched currents flow in the LTC3376's  $V_{IN}$  and PGND pins, and in the  $V_{IN}$  input capacitor. The loop formed by the input capacitor should be made as tight as possible by placing the capacitor adjacent to the  $V_{IN}$  and PGND pins and choosing a small case size such as 0402 for the  $1\mu$ F capacitor and 0603 for the  $10\mu$ F capacitor. Place a local, unbroken ground plane under the application circuit on the layer closest to the surface layer.

- 2. When connecting BST pins together for ganging, the BST trace should be as short as possible.

- The switching power traces connecting SWA-H to their respective inductors should be short and wide to reduce radiated EMI and parasitic coupling. Due to the large voltage swing of the switching nodes, high

- input impedance sensitive nodes, such as the feedback nodes, should be kept far away or shielded from the switching nodes or poor performance could result.

- 4. Keep the FB+, FB-, RT, TEMP, and RUN nodes small so that ground traces will shield them from the SW and BST nodes.

- 5. The GND pin should connect directly to the ground side of the INTV $_{\rm CC}$  bypass cap and then connect to the ground connection of other analog components (RT resistor, I $_{\rm MON}$  resistor, V $_{\rm CC}$  and EXTV $_{\rm CC}$  bypass caps) before connecting down to the GND plane.

- 6. The bypass capacitor from  $INTV_{CC}$  to GND should be as close to the  $INTV_{CC}$  pin as possible and connected with a wide trace.

- 7. The bypass capacitor from  $INTV_{CC\_P}$  to GND should be as close to the  $INTV_{CC\_P}$  pin as possible and connected with a wide trace. The ground side of this capacitor should connect directly to the GND plane.

- 8. The GND side of the switching regulator output capacitors should connect to the GND plane.

- 9. The FB<sup>-</sup> pin should connect directly to the GND side of the feedback resistor.

- 10. The power stages should have a symmetric layout with respect to V<sub>IN</sub>, PGND, BST, and SW traces.

- 11. See Evaluation Kit Design Files for recommended layouts.

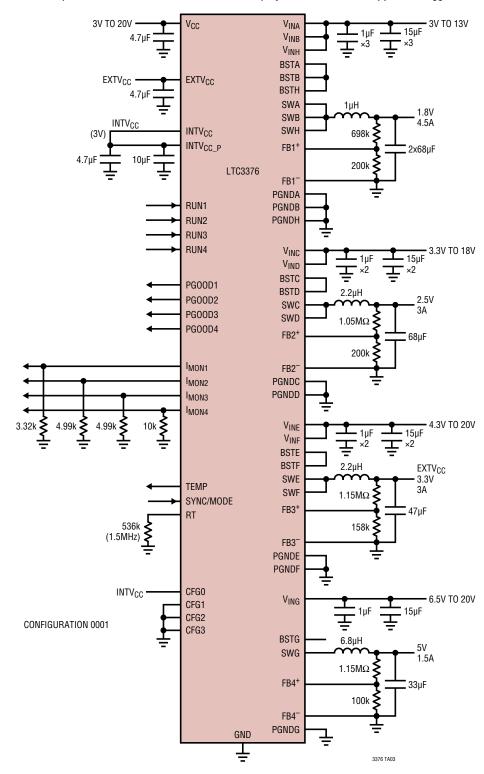

# TYPICAL APPLICATIONS

Four Rail (1.8V/4.5A, 2.5V/3A, 3.3V/3A, 5V/1.5A) System with Bootstrapped EXTV<sub>CC</sub> Drive

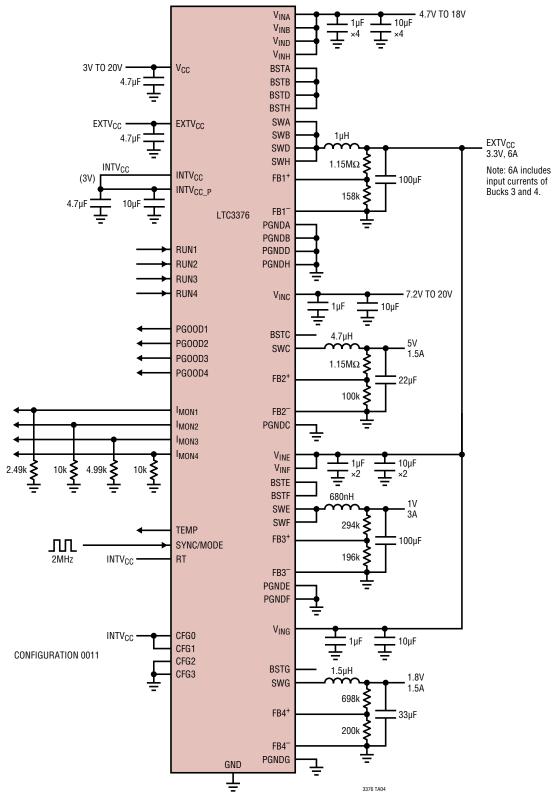

#### TYPICAL APPLICATIONS

Four Rail (3.3V/6A, 5V/1.5A, 1V/3A, 1.8V/1.5A) System with Bootstrapped EXTV<sub>CC</sub> Drive

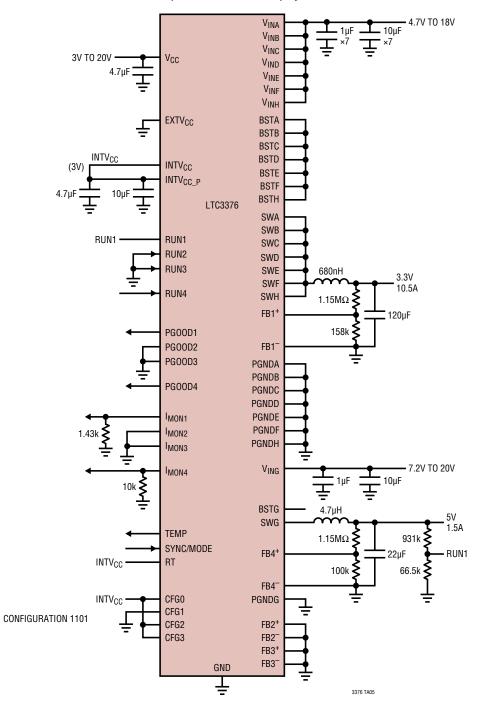

# TYPICAL APPLICATIONS

Two Rail (3.3V/10.5A, 5V/1.5A) System

BGA 64 0717 REV Ø

PACKAGE IN TRAY LOADING ORIENTATION

TRAY PIN 1

64

NUMBER OF BALLS:

TOTAL

0.08

COMPONENT \_\_

0.20 0.20

qqq

aaa

ppp

999

000

SUGGESTED PCB LAYOUT TOP VIEW

## PACKAGE DESCRIPTION

64-Lead (7.00mm imes 7.00mm imes 1.34mm)

**BGA Package**

(Reference LTC DWG # 05-08-1587 Rev Ø)

Rev 0

000.0

0.40 ±0.025 Ø 64x

PACKAGE TOP VIEW

2× C | 888 | Z |

ш

PIN "A1" CORNER

# TYPICAL APPLICATION

Four Rail (5V/3.3V/2.5V/1.8V, 3A) System with Bootstrapped EXTV<sub>CC</sub> Drive

# **RELATED PARTS**

| PART NUMBER         | DESCRIPTION                                            | COMMENTS                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC3370/<br>LTC3371 | 4-Channel 8A Configurable 1A<br>Buck DC/DCs            | Four Synchronous Buck Regulators with 8× 1A Power Stages. Can Connect Up to Four Power Stages in Parallel to Make a High Current Output (4A Max) with a Single Inductor. 8 Configurations Possible, Precision PGOOD Indication. 800mV FB Regulation. LTC3371 Has a Watchdog Timer; Buck 1 Accuracy ±1%, others ±2.5%; LTC3370: 32-Lead 5mm × 5mm QFN. LTC3371: 38-Lead 5mm × 7mm QFN and TSSOP. |

| LTC3374/<br>LTC3375 | 8-Channel Parallelable 1A Buck<br>DC/DCs               | Eight 1A Synchronous Buck Regulators. Can Connect Up to Four Power Stages in Parallel to Make a High Current Output (4A Max) with a Single Inductor. 15 Configurations Possible. 800mV FB Regulation. All Bucks ±2.5% Accuracy. LTC3375 Has I <sup>2</sup> C Programming with a Watchdog Timer and Pushbutton; LTC3374: 38-Lead 5mm × 7mm QFN and TSSOP, LTC3375: 48-Lead 7mm × 7mm QFN.        |

| LTC3374A            | High Accuracy 8-Channel<br>Parallelable 1A Buck DC/DCs | Eight 1A Synchronous Buck Regulators. Can Connect Up to Four Power Stages in Parallel to Make a High Current Output (4A Max) with a Single Inductor; 15 Configurations Possible. 800mV FB Regulation. Buck 1 Accuracy ±1%, Others ±2%; Overvoltage Monitor Included in PGOOD.                                                                                                                   |

|                     |                                                        | Rev                                                                                                                                                                                                                                                                                                                                                                                             |

© ANALOG DEVICES, INC. 2019

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Power Management IC Development Tools category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below:

EVAL-ADM1168LQEBZ EVB-EP5348UI MIC23451-AAAYFL EV MIC5281YMME EV DA9063-EVAL ADP122-3.3-EVALZ ADP1300.8-EVALZ ADP130-1.2-EVALZ ADP130-1.5-EVALZ ADP130-1.8-EVALZ ADP1714-3.3-EVALZ ADP1716-2.5-EVALZ ADP1740-1.5EVALZ ADP1752-1.5-EVALZ ADP1828LC-EVALZ ADP1870-0.3-EVALZ ADP1871-0.6-EVALZ ADP1873-0.6-EVALZ ADP1874-0.3EVALZ ADP1882-1.0-EVALZ ADP199CB-EVALZ ADP2102-1.25-EVALZ ADP2102-1.875EVALZ ADP2102-1.8-EVALZ ADP2102-2EVALZ ADP2102-3-EVALZ ADP2102-4-EVALZ ADP2106-1.8-EVALZ ADP2147CB-110EVALZ AS3606-DB BQ24010EVM

BQ24075TEVM BQ24155EVM BQ24157EVM-697 BQ24160EVM-742 BQ24296MEVM-655 BQ25010EVM BQ3055EVM

NCV891330PD50GEVB ISLUSBI2CKIT1Z LM2744EVAL LM2854EVAL LM3658SD-AEV/NOPB LM3658SDEV/NOPB LM3691TL1.8EV/NOPB LM4510SDEV/NOPB LM5033SD-EVAL LP38512TS-1.8EV EVAL-ADM1186-1MBZ EVAL-ADM1186-2MBZ