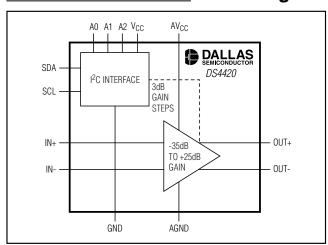

### **General Description**

The DS4420 is a fully differential, programmable-gain amplifier for audio applications. It features a -35dB to +25dB gain range controlled by an I<sup>2</sup>C interface and it is optimized to drive loads as low as  $50\Omega$ . The gain is adjustable in 3dB increments across the entire range. Three address inputs, used to select the I<sup>2</sup>C slave address, enable up to eight devices on a common bus.

The product operates from a single 5V supply over a -20°C to +70°C temperature range. It is offered in a 3mm x 3mm TDFN package.

#### **Applications**

Telephone Headsets Audio Volume Control Microphone Gain Control

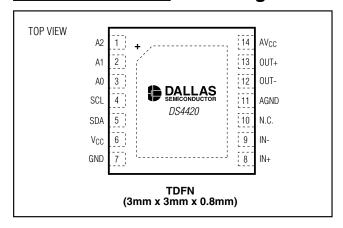

#### **Pin Configuration**

### **Features**

- ♦ Differential Inputs and Outputs

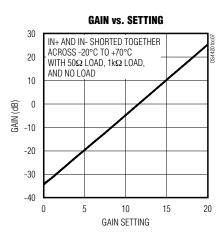

- ◆ -35dB to +25dB Adjustable Gain

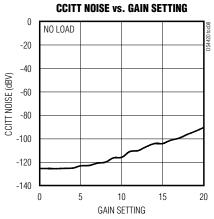

- **♦ Low Output Noise**

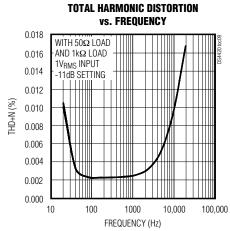

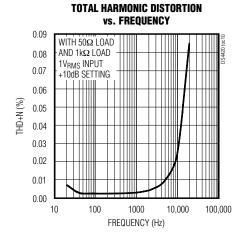

- ♦ Low-Distortion Driving into a 50Ω Load

- ♦ 3dB Gain Steps Programmed through I<sup>2</sup>C Interface

- ♦ 5V Single Supply

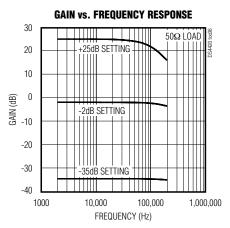

- ♦ 20kHz Bandwidth for All Gain Settings

- ♦ Small 3mm x 3mm x 0.8mm TDFN Package

- ♦ Up to Eight DS4420s can be Placed on the Same I<sup>2</sup>C Bus

### **Ordering Information**

| PART    | TEMP RANGE     | PIN-PACKAGE |

|---------|----------------|-------------|

| DS4420+ | -20°C to +70°C | 14 TDFN-EP* |

- +Denotes lead-free package.

- \*EP = Exposed paddle.

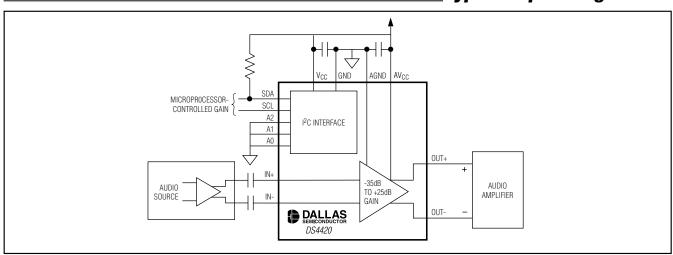

## **Typical Operating Circuit**

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltage on V <sub>CC</sub> , SDA, and SCL<br>Relative to GND0.5V to +6.0V | Voltage on AV <sub>CC</sub> Relative to V <sub>CC</sub> 0.3V to +0.3V Voltage on AGND Relative to GND0.3V to +0.3V |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Voltage on A0, A1, and A2                                                 | Output Current                                                                                                     |

| Relative to GND0.5V to (V <sub>CC</sub> + 0.5V;<br>not to exceed 6.0V)    | Operating Temperature Range20°C to +70°C Storage Temperature                                                       |

| Voltage on IN+, IN-, OUT-, and OUT+                                       |                                                                                                                    |

| Relative to AGND0.5V to (AV <sub>CC</sub> + 0.5V;                         |                                                                                                                    |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

$(T_A = -20^{\circ}C \text{ to } +70^{\circ}C.)$

| PARAMETER                            | SYMBOL | CONDITIONS     | MIN  | TYP | MAX                       | UNITS |

|--------------------------------------|--------|----------------|------|-----|---------------------------|-------|

| Digital Supply Voltage               | Vcc    | (Note 1)       | +4.5 |     | +5.5                      | V     |

| Analog Supply Voltage                | AVCC   |                |      | Vcc |                           | V     |

| Analog Ground                        | AGND   | (See Figure 5) |      | GND |                           | V     |

| Input Logic 1 (SCL, SDA, A0, A1, A2) | VIH    |                | 2.0  |     | V <sub>C</sub> C<br>+ 0.3 | V     |

| Input Logic 0 (SCL, SDA, A0, A1, A2) | VIL    |                | -0.3 |     | +0.8                      | V     |

#### **ELECTRICAL CHARACTERISTICS**

( $V_{CC}$  = +4.5V to +5.5V,  $T_A$  = -20°C to +70°C, unless otherwise noted.)

| PARAMETER                            | SYMBOL             | CONDITIONS                                                             | MIN                        | TYP                       | MAX                        | UNITS |

|--------------------------------------|--------------------|------------------------------------------------------------------------|----------------------------|---------------------------|----------------------------|-------|

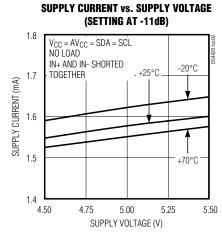

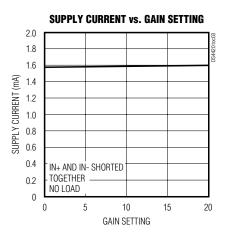

| Supply Current                       | Icc                | $V_{CC} = 5.5V$ , $R_L = \infty$ , $V_{IN} = 0V$ differential (Note 9) |                            | 1.7                       | 3                          | mA    |

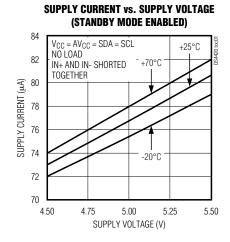

| Standby Current                      | ISTBY              | V <sub>CC</sub> = 5.5V (Notes 2, 9)                                    |                            |                           | 140                        | μΑ    |

| Input Leakage (SDA, SCL, A2, A1, A0) | IլL                | V <sub>CC</sub> = 5.5V                                                 |                            |                           | 1                          | μΑ    |

| Output Leakage (SDA)                 | ΙL                 |                                                                        |                            |                           | 1                          | μΑ    |

| Output Current Law (CDA)             | la.                | $V_{OL} = 0.4V$                                                        | 3                          |                           |                            | A     |

| Output-Current Low (SDA)             | loL                | V <sub>OL</sub> = 0.6V                                                 | 6                          |                           |                            | mA    |

| Input Voltage Range                  | VIN                | Differential                                                           |                            | -19                       | +1                         | dBV   |

| Max Peak-to-Peak Input Level         | V <sub>INP-P</sub> | Differential                                                           |                            |                           | 3.2                        | V     |

| Input Resistance                     | R <sub>IN</sub>    | Differential, active mode (Note 3)                                     | 29                         | 49                        | 60                         | kΩ    |

| Input Common-Mode Voltage            | V <sub>IN:CM</sub> |                                                                        | 0.45 x<br>V <sub>C</sub> C |                           | 0.55 x<br>V <sub>C</sub> C | V     |

| Output Voltage                       | Vo                 | $R_L = 50\Omega$ differential                                          |                            |                           | 6                          | dBV   |

| Output Peak-to-Peak Signal Swing     | Vop-p              | Differential                                                           |                            |                           | 5.6                        | V     |

| Output Common-Mode Voltage           | Vo:cm              |                                                                        | 0.45 x<br>V <sub>CC</sub>  | 0.5 x<br>V <sub>C</sub> C | 0.55 x<br>V <sub>C</sub> C | V     |

| Output Offset Voltage                | V <sub>O:OS</sub>  | $A_V = +25dB$                                                          | -20                        |                           | +20                        | mV    |

| Amplifier Output Current             | 1                  | V <sub>OUT</sub> = GND                                                 | 95                         |                           |                            | 0     |

| (Sourcing)                           | I <sub>OS1</sub>   | V <sub>OUT</sub> = V <sub>CC</sub> - 0.75V                             | 64                         |                           |                            | mA    |

### **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>CC</sub> = +4.5V to +5.5V,  $T_A$  = -20°C to +70°C, unless otherwise noted.)

| PARAMETER                           | SYMBOL           | CONDITIONS                                                          | MIN    | TYP  | MAX  | UNITS |  |

|-------------------------------------|------------------|---------------------------------------------------------------------|--------|------|------|-------|--|

| Amplifier Output Current            | laa.             | Vout = Vcc                                                          | 89     |      |      | mA    |  |

| (Sinking)                           | I <sub>OS2</sub> | V <sub>OUT</sub> = 0.75V                                            | 64     |      |      | IIIA  |  |

| Resistive Load Range                | RL               | Differential                                                        | 50     |      | 50k  | Ω     |  |

| Capacitive Load                     | CL               | Cap to GND (Note 4)                                                 |        |      | 100  | рF    |  |

| Closed-Loop Bandwidth               |                  | All gain settings (Note 5)                                          | 20     |      | 20k  | Hz    |  |

| Passband Flatness                   |                  | 20Hz to 20kHz (Notes 2, 5)                                          | -1     |      | +1   | dB    |  |

| Output Naiss (Note 5)               | No               | A = -35dB, 300Hz to 3.4kHz                                          |        | -123 |      | dBV   |  |

| Output Noise (Note 5)               | No               | A = +25dB, 300Hz to 3.4kHz                                          | lz -88 |      |      |       |  |

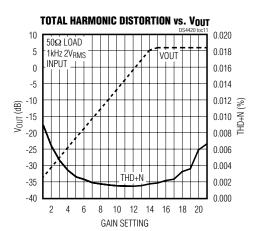

| T-t-111-marsis Distriction (Nata 5) | TUD              | $f = 1kHz$ , $A = \pm 16dB$                                         |        | 0.03 | 1.0  | - %   |  |

| Total Harmonic Distortion (Note 5)  | THD              | $R_L = 1k\Omega$ , $V_O \le +6dBV$ ,<br>$f = 1kHz$ , $A = \pm 16dB$ |        |      |      |       |  |

| Gain Range                          | А                |                                                                     | -35    |      | +25  | dB    |  |

| Gain Step Size                      | As               |                                                                     | 2.0    | 3.0  | 4.0  | dB    |  |

| Gain Accuracy                       | AERR1            | (Note 10)                                                           | -2.5   |      | +2.5 | dB    |  |

| Mute and Standby Mode Gain          | Amute            | (Note 5)                                                            |        |      | -90  | dB    |  |

| Standby Mode Exit Time              | tpu              | (Note 6)                                                            |        |      | 10   | μs    |  |

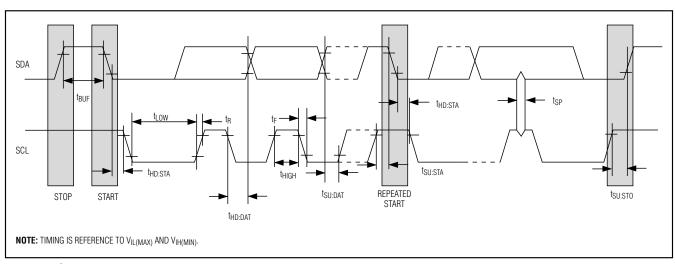

### I<sup>2</sup>C AC ELECTRICAL CHARACTERISTICS (See Figure 3)

$(V_{CC} = +4.5 \text{V to } +5.5 \text{V}, T_A = -20 ^{\circ}\text{C} \text{ to } +70 ^{\circ}\text{C}, \text{ timing referenced to } V_{IL(MAX)} \text{ and } V_{IH(MIN)}, \text{ unless otherwise noted.})$

|                                                 |                | , , , , ,  |                           |     |     |       |

|-------------------------------------------------|----------------|------------|---------------------------|-----|-----|-------|

| PARAMETER                                       | SYMBOL         | CONDITIONS | MIN                       | TYP | MAX | UNITS |

| SCL Clock Frequency                             | fscl           | (Note 7)   | 0                         |     | 400 | kHz   |

| Bus Free Time Between STOP and START Conditions | tBUF           |            | 1.3                       |     |     | μs    |

| Hold Time (Repeated) START<br>Condition         | tHD:STA        |            | 0.6                       |     |     | μs    |

| Low Period of SCL                               | tLOW           |            | 1.3                       |     |     | μs    |

| High Period of SCL                              | tHIGH          |            | 0.6                       |     |     | μs    |

| Data Hold Time                                  | thd:dat        |            | 0                         |     | 0.9 | μs    |

| Data Setup Time                                 | tsu:dat        |            | 100                       |     |     | ns    |

| Start Setup Time                                | tsu:sta        |            | 0.6                       |     |     | μs    |

| SDA and SCL Rise Time                           | t <sub>R</sub> | (Note 8)   | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

| SDA and SCL Fall Time                           | tF             | (Note 8)   | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

| STOP Setup Time                                 | tsu:sto        |            | 0.6                       |     |     | μs    |

| SDA and SCL Capacitive Loading                  | Св             | (Note 8)   |                           |     | 400 | рF    |

- Note 1: All voltages are referenced to ground. Currents entering the IC are specified positive, and currents exiting the IC are negative.

- Note 2: Standby supply current specified with SDA = SCL = V<sub>CC</sub>, the output disconnected, and A0, A1, and A2 driven to within 100mV of V<sub>CC</sub> or GND.

- Note 3: Input resistance during mute and power-down is approximately one-half of the active-mode resistance.

- Note 4: Each output is capable of driving a 100nF capacitive load to ground using an external 10Ω series resistor. However, output capacitance should be minimal for optimal distortion performance.

- Note 5: Guaranteed by design.

- **Note 6:** This is the time it takes for the output to become active after exiting standby mode.

- Note 7: I<sup>2</sup>C interface timing shown is for fast-mode (400kHz) operation. This device is also backward-compatible with I<sup>2</sup>C standard-mode timing.

- **Note 8:**  $C_B$  = total capacitance of one bus line in picofarads.

- **Note 9:** The current specified is the sum of V<sub>CC</sub> and AV<sub>CC</sub> supply currents.

- Note 10: Gain accuracy specified assuming the output impedance of signal source driving of the DS4420 is ≤ 2.5kΩ.

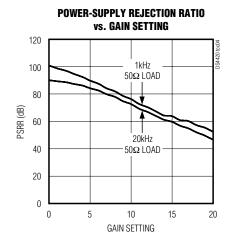

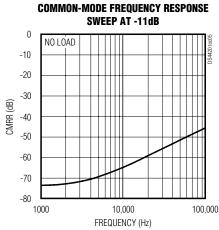

## Typical Operating Characteristics

$(T_A = +25$ °C,  $V_{CC} = AV_{CC} = 5.0V$ , unless otherwise noted.)

## \_Typical Operating Characteristics (continued)

$(T_A = +25^{\circ}C, V_{CC} = AV_{CC} = 5.0V, unless otherwise noted.)$

### **Pin Description**

| PIN | NAME | FUNCTION                                                                                                                             |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------|

| 1   | A2   |                                                                                                                                      |

| 2   | A1   | Address Select Inputs—Determine I <sup>2</sup> C Slave Address. Device address is 1010A <sub>2</sub> A <sub>1</sub> A <sub>0</sub> . |

| 3   | A0   |                                                                                                                                      |

| 4   | SCL  | I <sup>2</sup> C Serial Clock—Input for I <sup>2</sup> C Clock                                                                       |

| 5   | SDA  | I <sup>2</sup> C Serial Data—Input/Output for I <sup>2</sup> C Data                                                                  |

| 6   | Vcc  | Digital Power-Supply Terminal                                                                                                        |

| 7   | GND  | Ground                                                                                                                               |

| 8   | IN+  | Differential Audia Input Cianal                                                                                                      |

| 9   | IN-  | Differential Audio Input Signal                                                                                                      |

| 10  | N.C. | No Connection                                                                                                                        |

| 11  | AGND | Analog Ground (Must be Connected to GND)                                                                                             |

| 12  | OUT- | Differential Audia Output Canal                                                                                                      |

| 13  | OUT+ | Differential Audio Output Signal                                                                                                     |

| 14  | AVCC | Analog Power Supply (Must be Connected to V <sub>CC</sub> )                                                                          |

| EP  | EP   | Exposed Paddle. Connect to GND and AGND.                                                                                             |

### Detailed Description

The key features of the DS4420 are illustrated in the *Block Diagram*.

#### **Controlling the DS4420**

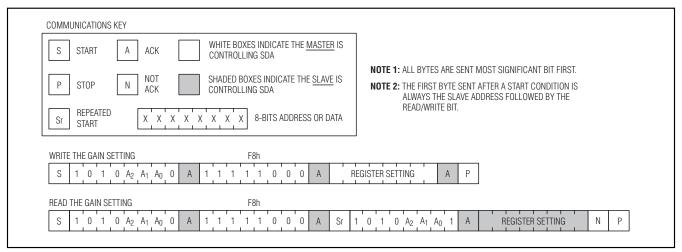

The DS4420 is controlled through the I<sup>2</sup>C serial interface. Gain, mute, and standby settings all reside in one control register located at memory address F8h (see Figure 1). Writes to other memory addresses are invalid.

#### Programmable Gain

The gain is adjustable from -35dB to +25dB in 3dB increments. The gain is determined by the five LSBs of the control register as shown in Figure 1. Gain settings greater than 14h are invalid.

#### Mute Mode

The DS4420 is placed in mute mode by setting the mute bit located in the control register (see Figure 1). When in this mode, the output of the amplifier is muted and is independent of the gain setting. The input-to-output attenuation is specified in the *Electrical Characteristics* table as AMUTE.

#### Standby Mode

Standby mode is entered by setting the standby control bit (see Figure 1). Setting the standby control bit mutes the output of the amplifier and places the DS4420 into a

#### **Block Diagram**

low-current (ISTBY) consumption state. Unlike mute mode, however, standby mode is intended for use when no input signal is present. While in standby mode, the DS4420 maintains input and output common-mode bias voltages. The device produces no audible clicks or pops when entering or exiting the standby state. The time required for the output to become active when exiting standby mode is specified as tpu.

| wer-Up Def | ault:   | 1000 00                                                                   | 000 b                                                    |               |                   |             |       |       |

|------------|---------|---------------------------------------------------------------------------|----------------------------------------------------------|---------------|-------------------|-------------|-------|-------|

| F8h        | Standby | ×                                                                         | x Mute Gain Setting[4:0]                                 |               |                   |             |       |       |

|            | bit 7   |                                                                           |                                                          | bit 4         | bit 3             | bit 2       | bit 1 | bit 0 |

|            | bit 7   | 0 = Normal o                                                              | aces the DS4420<br>peration.<br>ne DS4420 in star        | •             |                   |             |       |       |

| _          | bit 6   | Don't care.                                                               |                                                          |               |                   |             |       |       |

|            | bit 5   | 0 = Normal o                                                              | the amplifier outperation. (Power-<br>a amplifier output | -up default.) | of the current ga | in setting. |       |       |

|            | bit 4:0 | Gain Setting: Five-bit gain setting. The power-up default is setting 00h. |                                                          |               |                   |             |       |       |

|            |         |                                                                           | GAIN<br>SETTIN<br>(hex)                                  |               |                   | G GAI       |       |       |

|            |         |                                                                           | 00h                                                      | -35           | 0Bh               | -2          |       |       |

|            |         |                                                                           | 01h                                                      | -32           | 0Ch               | +1          |       |       |

|            |         |                                                                           | 02h                                                      | -29           | 0Dh               | +4          |       |       |

|            |         |                                                                           | 03h                                                      | -26           | 0Eh               | +7          |       |       |

|            |         |                                                                           | 04h                                                      | -23           | 0Fh               | +10         | )     |       |

|            |         |                                                                           | 05h                                                      | -20           | 10h               | +13         | 3     |       |

|            |         |                                                                           | 06h                                                      | -17           | 11h               | +16         | 3     |       |

|            |         |                                                                           | 07h                                                      | -14           | 12h               | +19         | 9     |       |

|            |         |                                                                           | 08h                                                      | -11           | 13h               | +22         | 2     |       |

|            |         |                                                                           | 09h                                                      | -8            | 14h               | +25         | 5     |       |

|            |         |                                                                           | 0Ah                                                      | -5            | 15h to 1          | Fh Illeg    | al    |       |

Figure 1. Control Register Description

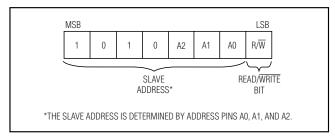

#### **Slave Address Byte and Address Pins**

The slave address byte consists of a 7-bit slave address plus a R/W bit (see Figure 2). The DS4420's slave address is determined by the state of the A0, A1, and A2 address pins. These pins allow up to eight DS4420s to reside on the same I<sup>2</sup>C bus. Address pins connected to GND result in a '0' in the corresponding bit position in the slave address. Conversely, address pins connected to V<sub>CC</sub> result in a '1' in the corresponding bit positions. For example, the DS4420's slave address byte is A0h when A0, A1, and A2 pins are grounded. I<sup>2</sup>C communication is described in detail in the I<sup>2</sup>C Serial Interface Description section.

Figure 2. DS4420 Slave Address Byte

Figure 3. I<sup>2</sup>C Timing Diagram

## I<sup>2</sup>C Serial Interface Description I<sup>2</sup>C Definitions

The following terminology is commonly used to describe  $I^2C$  data transfers. See the timing diagram (Figure 3) and the  $I^2C$  AC Electrical Characteristics table for additional information.

**Master Device:** The master device controls the slave devices on the bus. The master device generates SCL clock pulses, start and stop conditions.

**Slave Devices:** Slave devices send and receive data at the master's request.

**Bus Idle or Not Busy:** Time between stop and start conditions when both SDA and SCL are inactive and in their logic-high states.

**Start Condition:** A start condition is generated by the master to initiate a new data transfer with a slave. Transitioning SDA from high to low while SCL remains high generates a start condition.

**Stop Condition:** A stop condition is generated by the master to end a data transfer with a slave. Transitioning SDA from low to high while SCL remains high generates a stop condition.

Repeated Start Condition: The master can use a repeated start condition at the end of one data transfer to indicate that it will immediately initiate a new data transfer following the current one. Repeated starts are commonly used during read operations to identify a specific memory address to begin a data transfer. A repeated start condition is issued identically to a normal start condition.

**Bit Write:** Transitions of SDA must occur during the low state of SCL. The data on SDA must remain valid and unchanged during the entire high pulse of SCL plus the setup and hold time requirements. Data is shifted into the device during the rising edge of the SCL.

**Bit Read:** At the end of a write operation, the master must release the SDA bus line for the proper amount of setup time before the next rising edge of SCL during a bit read. The device shifts out each bit of data on SDA at the falling edge of the previous SCL pulse and the data bit is valid at the rising edge of the current SCL pulse. Remember that the master generates all SCL clock pulses including when it is reading bits from the slave.

Acknowledgement (ACK and NACK): An Acknowledgement (ACK) or Not Acknowledge (NACK) is always the 9th bit transmitted during a byte transfer. The device receiving data (the master during a read or the slave during a write operation) performs an ACK by transmitting a zero during the 9th bit. A device performs a NACK by transmitting a one (done by releasing SDA) during the 9th bit. Timing (Figure 3) for the ACK and NACK is identical to all other bit writes. An ACK is the acknowledgment that the device is properly receiving data. A NACK is used to terminate a read sequence or as an indication that the device is not receiving data.

**Byte Write:** A byte write consists of 8 bits of information transferred from the master to the slave (most significant bit first) plus a 1-bit acknowledgement from the slave to the master. The 8 bits transmitted by the master are done according to the bit write definition and the acknowledgement is read using the bit read definition.

**Byte Read:** A byte read is an 8-bit information transfer from the slave to the master plus a 1-bit ACK or NACK from the master to the slave. The 8 bits of information that are transferred (most significant bit first) from the slave to the master are read by the master using the bit read definition above, and the master transmits an ACK using the bit write definition to receive additional data bytes. The master must NACK the last byte read to terminate communication so the slave will return control of SDA to the master.

**Slave Address Byte:** Each slave on the I<sup>2</sup>C bus responds to a slave address byte sent immediately following a start condition. The slave address byte contains the slave address in the most significant 7 bits and the R/W bit in the least significant bit.

The DS4420's slave address is determined by the state of the A0, A1, and A2 address pins as shown in Figure 2. Address pins connected to GND result in a '0' in the corresponding bit position in the slave address. Conversely, address pins connected to  $V_{CC}$  result in a '1' in the corresponding bit positions.

When the  $R\overline{W}$  bit is 0 (such as in A0h), the master is indicating it will write data to the slave. If  $R\overline{W}$  is set to a 1, (A1h in this case), the master is indicating it wants to read from the slave.

If an incorrect (nonmatching) slave address is written, the DS4420 will assume the master is communicating with another I<sup>2</sup>C device and ignore the communication until the next start condition is sent.

**Memory Address:** During an I<sup>2</sup>C write operation to the DS4420, the master must transmit a memory address to identify the memory location where the slave is to store

the data. The memory address is always the second byte transmitted during a write operation following the slave address byte.

#### I<sup>2</sup>C Communication

Writing a Single Byte to a Slave: The master must generate a start condition, write the slave address byte (R/W = 0), write the memory address, write the byte of data, and generate a stop condition. The master must read the slave's acknowledgement during all byte write operations.

**Reading a Single Byte from a Slave:** Unlike the write operation that uses the specified memory address byte to define where the data is to be written, the read operation occurs at the present value of the memory address counter. A dummy write cycle can be used to force the address pointer to a desired location. To do this, the master generates a start condition, writes the slave address byte  $(R/\overline{W}=0)$ , writes the memory address where it desires to read, generates a repeated start condition, writes the slave address byte  $(R/\overline{W}=1)$ , reads the data byte with a NACK to indicate the end of the transfer, and generates a stop condition.

See Figure 4 for I<sup>2</sup>C communication examples.

### Applications Information

#### **Power-Supply Decoupling**

The DS4420 has separate supply voltages for its analog and digital circuitry. For best noise and distortion performance, place a  $0.1\mu F$  or  $0.01\mu F$  capacitor from VCC to GND and from AVCC to AGND. These capacitors should be placed as close as possible to the supply and ground pins of the device.

Figure 4. I<sup>2</sup>C Communication Examples

#### **Exposed Paddle**

The DS4420 exposed paddle is not electrically isolated. It must be soldered to ground for proper operation.

#### **Input-Coupling Capacitors**

The DS4420 is designed to be operated with an AC-coupled input signal. The input resistance,  $R_{\text{IN}}$ , is sufficiently large to allow the use of small and inexpensive external capacitors. The input resistance combined with the AC-coupling capacitor will create a highpass filter. The -3dB cutoff frequency of the highpass, fC, is given by:

$$f_C = \frac{1}{2\pi \times C_{IN} \times R_{IN}}$$

where  $C_{\text{IN}}$  is the external coupling capacitor and  $R_{\text{IN}}$  is the internal input resistance.

At the cutoff frequency, the input signal will be attenuated 3dB, with less attenuation as the signal's frequency increases beyond the cutoff frequency. To guarantee passband flatness, the cutoff frequency of the filter should be designed using the specified minimum input resistance, and placed well below the desired flat band of the circuit. The typical input resistance should only be used to estimate typical performance.

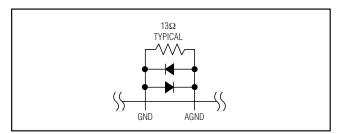

#### **Internal Ground Connections**

The DS4420's ground pins, GND and AGND, must be connected together externally. Internally, they are connected as shown in Figure 5.

Figure 5. Internal Ground Connections

Chip Topology

TRANSISTOR COUNT: 5347

SUBSTRATE CONNECTED TO: Ground

### Package Information

For the latest package outline information, go to <a href="www.maxim-ic.com/DallasPackInfo">www.maxim-ic.com/DallasPackInfo</a>.

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

0 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Audio Amplifiers category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below:

LV47002P-E NCP2890AFCT2G NTE1192 LC706200CM IS31AP4915A-QFLS2-TR TDA1591T TS2012EIJT NCP2809BMUTXG

NJW1157BFC2 IS31AP4996-GRLS2-TR NCP2823BFCT1G BD88420GUL-E2 LA4450L-E IS31AP2036A-CLS2-TR NTE1110 NTE7100

NTE7114 NTE7163 NTE7168 NTE7177 NTE7178 NTE7186 NTE7198 NTE7202 NTE7217 BD88400GUL-E2 BD88200GUL-E2

SABRE9601K THAT1646W16-U PAM8965ZLA40-13 TSDP10XX1NLGXZBX TSDP11XX1NBGIZBX TSDP11XX1NLGXZBX

TSDP10XX1NBGIZBX NJM4580CV-TE1 NJU7084R-TE1 OPA1655DR LV4910T-MPB-E NCP2890AFCT2 NCV2211DR2G

SCY99091FCT2G TAS5720MRSMR AW87389FCR AW8737AFCR TDA2005R TDA2030 TDA7265L-J11-A-T CD2050CZ

AW88261FCR TDA7377-JSM