### DC - 7 GHz FRACTIONAL-N DIVIDER AND FREQUENCY SWEEPER

#### Typical Applications

The DC - 7 GHz FRACTIONAL-N DIVIDER is suitable for:

- Test Equipment

- · Portable Instruments

- High Performance Fractional-N Frequency Synthesizers with Ultra Low Spurious

- Stand-Alone Divider and/or Delta-Sigma Modulator

#### **Features**

Wideband: DC - 7 GHz Input -20-bit Frequency Divider

Low Noise: -160 dBc/Hz

Low Spurious: Largest Spurious - 95 dBc

48-bit 100 MHz Delta-Sigma Modulator (DSM)

- Configurable DSM Size

- Programmable Seed

- Phase Step

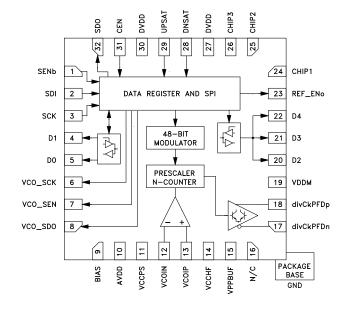

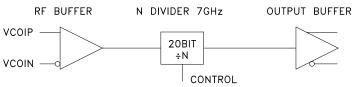

#### **Functional Diagram**

Product covered by US and Foreign Patents including US Pat. No. 8,531,217.

#### Features (Continued)

Integrated Frequency Sweeper

- Linear, Coherent Sweeps

- 2-Way, 1-Way, & User Defined Sweep Modes

- Automatic or Triggered

- Programmable Seed

- -SPI & External Triggering

5-GPIO's, can be used for External DSM

Cycle Slip Prevention Support with PFD Chip (HMC984LP4E)

Differential VCO Input & Divider Output

Programmable Output Current Control:

-5 mA to 17.5 mA Open Collector Output Driver

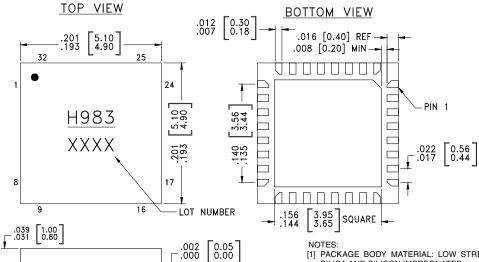

32 pin, 5 x 5 mm, LP5 Package

#### General Description

DC - 7 GHz FRACTIONAL-N DIVIDER is a fractional frequency divider targeted for fractional-N frequency synthesis, and stand-alone low noise frequency divider applications that require exceptional spurious performance.

Although the DC - 7 GHz FRACTIONAL-N DIVIDER can work with any VCO and/or compatible Phase Detector, best performance and features will be achieved when paired with the companion part, the HMC984LP4E.

Fabricated in SiGe BiCMOS process, the DC - 7 GHz FRACTIONAL-N DIVIDER features a 48-bit Delta Sigma Fractional Modulator (DSM) with programmable phase accumulator size, enabling precise control of frequency step size and resolution. Integrated DSM can generate frequencies with nearly 0 Hz frequency error. The DSM also includes a built-in programmable frequency sweep capability, with various automatic and user defined sweep modes and triggering options, including hardware trigger pin, or SPI trigger with optional delayed trigger.

DC - 7 GHz FRACTIONAL-N DIVIDER is a versatile part capable of various configurations. It has 5 general purpose I/Os (GPIOs). DSM outputs are made available from the GPIO port, enabling the DC - 7 GHz FRACTIONAL-N DIVIDER to import and/or export DSM sequences for various configuration options.

DC - 7 GHz FRACTIONAL-N DIVIDER divider outputs are differential, open collector with programmable current to accommodate different off-chip loads.

### DC - 7 GHz FRACTIONAL-N DIVIDER AND FREQUENCY SWEEPER

#### **Table 1. Electrical Specifications**

TA = +25 °C, AVDD, VCCPS, VCCHF, VDDM, DVDD = 3 V  $\pm$  10%; VPPBUF = 5 V  $\pm$  10%; GND = 0 V

| Parameter                                                 | Conditions                                                         | Min.     | Тур.      | Max.       | Units  |

|-----------------------------------------------------------|--------------------------------------------------------------------|----------|-----------|------------|--------|

| RF Input Characteristics                                  |                                                                    |          |           |            |        |

| RF Input Frequency range                                  |                                                                    | DC       |           | 7          | GHz    |

| RF Input Sensitivity                                      |                                                                    | -15      | -10       | 0          | dBm    |

| RF Input Capacitance                                      | External Match Recommended                                         |          |           | 3          | pF     |

| Divider Range (20-bit)                                    |                                                                    |          |           |            |        |

| Integer Mode                                              |                                                                    | 32       |           | 1,048,575  |        |

| Fractional Mode                                           |                                                                    | 36       |           | 1,048,571  |        |

| Divider Output Characteristics                            |                                                                    |          |           |            |        |

| Output Buffer Current                                     | Programmable in 2.5 mA Steps                                       | 5        | 12.5      | 17.5       | mA     |

| Output Voltage Swing                                      | Single- Ended, Vpullup = 5 V                                       | 0.75     | 1         | 2          | V      |

| Output Frequency Range<br>Integer Mode<br>Fractional Mode | Mode A and Mode B                                                  | DC<br>DC |           | 150<br>125 | MHz    |

| Phase Noise                                               | 50 MHz PFD, 6 GHz Input, Integer Mode                              |          | -160      |            | dBc/Hz |

| Fractional Spurious                                       | Largest observed at 10 kHz Fractional Offset from Integer Boundary |          | -95       | -85        | dBc    |

| Logic Inputs                                              |                                                                    |          |           |            |        |

| Input High Voltage (VIH)                                  |                                                                    |          |           | DVDD-0.4   | V      |

| Input Low Voltage (VIL)                                   |                                                                    | 0.4      |           |            | V      |

| Logic Outputs                                             |                                                                    |          |           |            |        |

| Output High Voltage (VOH)                                 |                                                                    |          |           | DVDD-0.4   | V      |

| Output Low Voltage (VOL)                                  |                                                                    | 0.4      |           |            | V      |

| DC Load                                                   |                                                                    |          |           | 1.5        | mA     |

| Serial Port Clock Frequency                               | Main SPI and AUXSPI                                                |          |           | 30         | MHz    |

| Power Supplies                                            |                                                                    |          |           |            |        |

| AVDD, VCCPS, VCCHF                                        | Analog Supplies. AVDD should be equal to DVDD.                     | 2.7      | 3         | 3.3        | ٧      |

| VPPBUF                                                    | Output Buffer Supply.                                              | 4.5      | 5         | 5.5        | V      |

| VDDM, DVDD                                                | Digital Supplies                                                   | 2.7      | 3         | 3.3        | V      |

| Current Consumption                                       |                                                                    |          | •         |            |        |

| IDD - Total Current Consumption                           | Integer Mode / Fractional Mode<br>(50 MHz Divider Output)          |          | 104 / 122 |            | mA     |

| I - AVDD (AVDD Current, 3 V)                              | Integer Mode / Fractional Mode                                     |          | 5/5       |            | mA     |

| I - VCCPS (VCCPS Current, 3 V)                            | Integer Mode / Fractional Mode                                     |          | 79 / 79   |            | mA     |

| I - VCCHF (VCCHF Current, 3 V)                            | Integer Mode / Fractional Mode                                     |          | 8/8       |            | mA     |

| I - VDDM (VDDM Current, 3 V)                              | Integer Mode / Fractional Mode                                     |          | 11 / 11   |            | mA     |

| I - DVDD (Total DVDD Current, 3 V)                        | Integer Mode / Fractional Mode                                     |          | 1 / 19    |            | mA     |

| I - VPPBUF (Total VPPBUF Current, 5 V)                    |                                                                    |          | 5         |            | uA     |

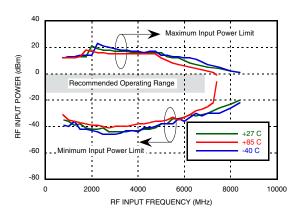

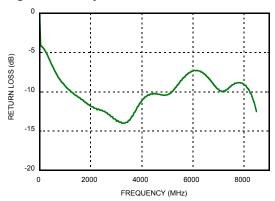

### Figure 1. RF Input Sensitivity 11

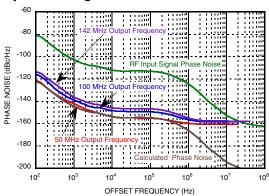

Figure 3. Output Phase Noise with 6 GHz Input in Integer Mode [3]

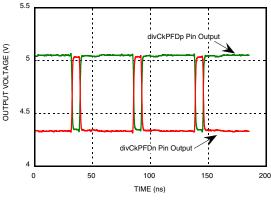

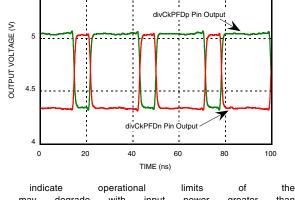

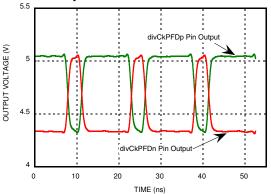

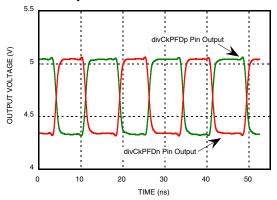

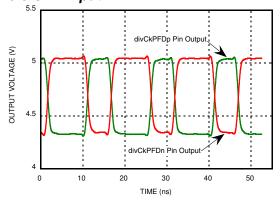

Figure 5. Time Domain 18 MHz Output, 6.5 GHz Input [4]

maximum GHz FRACTIONAL-N 0 dBm for frequencies higher than 6500 MHz.

The

minimum DIVIDER.

levels Performance

indicate degrade may

5.5

with

### DC - 7 GHz FRACTIONAL-N DIVIDER AND FREQUENCY SWEEPER

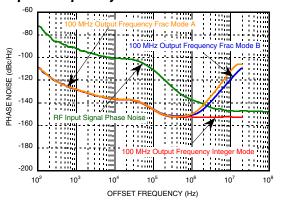

Figure 2. Output Phase Noise, 6 GHz Input Frequency [2]

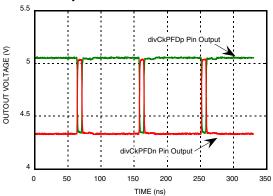

Figure 4. Time Domain 10 MHz Output, 6.5 GHz Input [4]

Figure 6. Time Domain 35 MHz Output, 6.5 GHz Input [4]

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

and

<sup>[2]</sup> Due to Delta Sigma modulation in fractional mode, the output phase noise peaks at frequency offset of fout/2 from the output. Agilent MXG N5182A used as a signal source.

<sup>[3]</sup> Rohde & Schwarz SMBV100A used as a signal source.

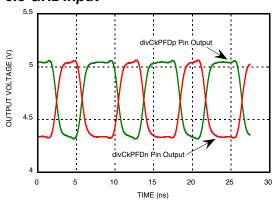

Figure 7. Time Domain 124 MHz Output, 6.5 GHz Input

| Output | O

Figure 9. Time Domain 61 MHz Output, 6.5 GHz Input [5]

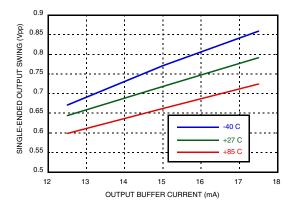

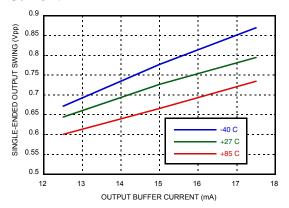

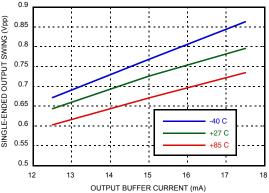

Figure 11. 10 MHz Output Swing vs Buffer Current [6]

### DC - 7 GHz FRACTIONAL-N DIVIDER AND FREQUENCY SWEEPER

Figure 8. Time Domain 66 MHz Output, 6.5 GHz Input

| Output | Ou

Figure 10. Time Domain 66 MHz Output, 6.5 GHz Input [5]

Figure 12. 50 MHz Output Swing vs Buffer Current 6

[4] Measured with 50  $\Omega$  impedance per line, integer Mode, 15 mA Output Buffer Current (Reg 0Fh[4:2]) selected

[5] Measured with 50 Ω impedance per line, integer Mode, 15 mA Output Buffer Current (Reg 0Fh[4:2]) selected

### Figure 13. 100 MHz Output Swing vs **Buffer Current** [7]

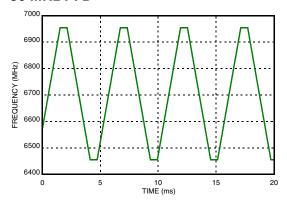

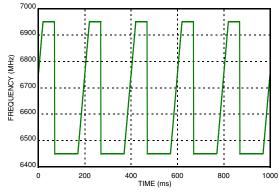

Figure 15. Two Way Frequency Sweep, 50 MHz PFD [8]

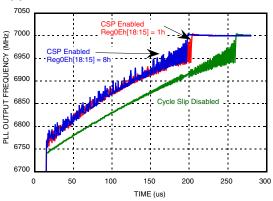

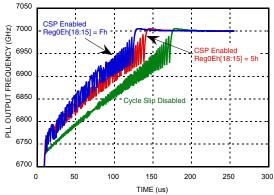

Figure 17. PLL Cycle Slip Prevention, 100 MHz PFD [8]

v02.0112

Figure 14. Input Return Loss

Figure 16. One Way Frequency Sweep, 10 MHz PFD and 10 Hz external trigger [8]

Figure 18. PLL Cycle Slip Prevention, 50 MHz PFD [8]

- [6] Measured with 50  $\Omega$  impedance per line. Buffer current is controlled via Reg 0Fh[4:2].

- [7] Measured with 50 Ω impedance per line. Buffer current is controlled via Reg 0Fh[4:2].

- [8] Measured with HMC983LP5E/HMC984LP4E chip set as fractional-N synthesizer. Crystal input frequency = 100 MHz, CP current = 2.5 mA, CP offset current = 245 uA, Loop filter bandwidth = 87 KHz, DSM Mode B selected. Cycle Slip Prevention (CSP) is disabled in HMC984LP4E by setting Reg 01h [4] = 0. Setting Reg 01h [4] = 1 enables CSP in the two chip PLL

**Table 2. Pin Descriptions**

| Pin Number    | Function                        | Description                                                                                                            | Interface Schematic                                                  |

|---------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 1,<br>2,<br>3 | SENb<br>SDI<br>SCK              | Main SPI Data Input                                                                                                    | SDI SENЬ SCK                                                         |

| 4,<br>5       | D1<br>D0                        | GPIO bit 1<br>GPIO bit 0                                                                                               | OE D1 D0                                                             |

| 6,<br>7,<br>8 | AUX_SCLK<br>AUX_SENb<br>AUX_SDO | Auxiliary SPI Clock Output<br>Auxiliary SPI Enable<br>Auxiliary SPI Data Output                                        | DVDD  AUX_SDO AUX_SCLK AUX_SENb                                      |

| 9             | BIAS                            | External Decoupling for Analog Bias Circuits                                                                           |                                                                      |

| 10            | AVDD                            | 3 Volt Power Supply Pin for Internal Reference Cur-<br>rent Sources                                                    |                                                                      |

| 11            | VCCPS                           | 3 Volt Power Supply Pin for Prescaler                                                                                  |                                                                      |

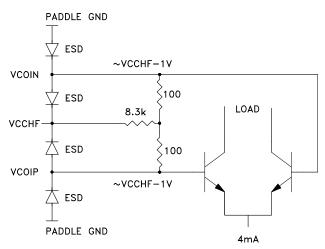

| 12,<br>13     | VCOIN,<br>VCIOP                 | Negative Pin for Prescaler Differential Input, AC-Coupled<br>Positive Pin for Prescaler Differential Input, AC-Coupled | PADDLE GND  VCOIN  ESD  VCCHF-1V  VCOIP  ESD  VCOIP  PADDLE GND  Ama |

| 14            | VCCHF                           | 3 Volt Power Supply Pin for Prescaler Input Buffer                                                                     |                                                                      |

| 15            | VPPBUF                          | 5 Volt Power Supply Pin for Divider Output Buffer                                                                      |                                                                      |

| 16            | N/C                             | No Connect Pin                                                                                                         |                                                                      |

Table 2. Pin Descriptions (Continued)

|                  |                           | Continuou                                                                                                      | T                       |  |

|------------------|---------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------|--|

| Pin Number       | Function                  | Description                                                                                                    | Interface Schematic     |  |

| 17,<br>18        | divCkPFDn,<br>divCkPFDp   | Negative Pin for Open Collector Divider Output Driver<br>Positive Pin for Open Collector Divider Output Driver | divCkPFDp divCkPFDn     |  |

| 19               | VDDM                      | 3V Supply Pin for Digital Section of the Frequency Divider                                                     |                         |  |

| 20,<br>21,<br>22 | D2,<br>D3,<br>D4          | GPIO bit 2,<br>GPIO bit 3,<br>GPIO bit 4                                                                       | OE                      |  |

| 23               | REF_Eno                   | Gate Control (Output) to request TCXO Clock Export from HMC984LP4E                                             |                         |  |

| 24,<br>25,<br>26 | CHIP1,<br>CHIP2,<br>CHIP3 | Chip Address Pin 1,<br>Chip Address Pin 2,<br>Chip Address Pin 3                                               | CHIP1<br>CHIP2<br>CHIP3 |  |

| 27, 30           | DVDD                      | 3V Power Supply for Digital                                                                                    |                         |  |

| 28,              | DNSAT,                    | VCO Saturation Input flag from HMC984LP4E Chip                                                                 | DNSAT O                 |  |

Table 2. Pin Descriptions (Continued)

| Pin Number | Function | Description                                          | Interface Schematic |

|------------|----------|------------------------------------------------------|---------------------|

| 29         | UPSAT    | Reference Saturation Input flag from HMC984LP4E Chip | UPSAT O             |

| 31         | CEN      | Chip Enable                                          | CEN DVDD            |

| 32         | SDO      | Main SPI Data Output                                 | ODVDD SDO           |

#### Table 3. Absolute Maximum Ratings

| Nominal 3V Supplies to GND                       | -0.3 to 3.6 V         |

|--------------------------------------------------|-----------------------|

| Nominal 3V Digital Supply to 3V<br>Analog Supply | -0.3 to +0.3 V        |

| Nominal 5V Supply to GND (VPPBUF)                | -0.3 to 5.5 V         |

| divCkp, divCkn common mode DC                    | VCCPS + 0.5 V min     |

| VCOIP, VCOIN Single Ended AC 50 $\Omega$ Source  | + 7 dBm               |

| VCOIP, VCOIN Differential AC 50 $\Omega$ Source  | + 13 dBm              |

| Digital Input Voltage Range                      | -0.25 to DVDD + 0.5 V |

| Minimum Digital Load                             | 1 kΩ                  |

| Operating Temperature Range                      | -40 °C to +85 °C      |

| Maximum Junction Temperature                     | 125 °C                |

| Storage Temperature                              | -65 to +125 °C        |

| Thermal Resistance (Rth) (junction to ground paddle)       | 40 °C/W        |

|------------------------------------------------------------|----------------|

| Reflow Soldering Peak Temperature Time at Peak Temperature | 260 °C<br>40 s |

| ESD Sensitivity (HBM)                                      | Class 1B       |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### ELECTROSTATIC SENSITIVE DEVICE OBSERVE HANDLING PRECAUTIONS

### **Outline Drawing**

SEATING

-C-

v02.0112

- [1] PACKAGE BODY MATERIAL: LOW STRESS INJECTION MOLDED PLASTIC SILICA AND SILICON IMPREGNATED

- LEAD AND GROUND PADDLE MATERIAL: COPPER ALLOY. LEAD AND GROUND PADDLE PLATING: 100% MATTE TIN.

- DIMENSIONS ARE IN INCHES [MILLIMETERS].

- LEAD SPACING TOLERANCE IS NON-CUMULATIVE.

PAD BURR LENGTH SHALL BE 0.15 mm MAX. PAD BURR HEIGHT SHALL BE

- PACKAGE WARP SHALL NOT EXCEED 0.05 mm

ALL GROUND LEADS AND GROUND PADDLE MUST BE SOLDERED TO PCB

- [9] REFER TO HITTITE APPLICATION NOTE FOR SUGGESTED PCB LAND PATTERN.

#### Package Information

△ .003[0.08] C

| Part Number          | Package Body Material                              | Lead Finish   | MSL Rating [2] | Package Marking [1] |

|----------------------|----------------------------------------------------|---------------|----------------|---------------------|

| D3GHERACTIONALNDMDER | RoHS-compliant Low Stress Injection Molded Plastic | 100% matte Sn | MSL1           | <u>H983</u><br>XXXX |

[1] 4-Digit lot number XXXX

[2] Max peak reflow temperature of 260 °C

# DC - 7 GHz FRACTIONAL-N DIVIDER AND FREQUENCY SWEEPER

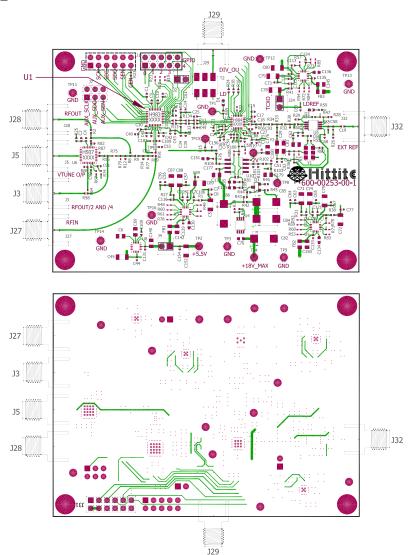

#### **Evaluation PCB**

The circuit board used in the application should use RF circuit design techniques. Signal lines should have 50 Ohms impedance while the package ground leads and exposed paddle should be connected directly to the ground plane similar to that shown unless mentioned otherwise. A sufficient number of via holes should be used to connect the top and bottom ground planes. The evaluation circuit board shown is available from Hittite upon request.

**Table 4. Evaluation Order Information**

| Item           | Contents                                                                                                                                                                                                       | Part Number                              |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| Evaluation Kit | DC - 7 GHz FRACTIONAL-N DIVIDER and HMC984LP4E PLL Chipset Evaluation PCB USB Interface Board 6' USB A Male to USB B Female Cable CD ROM (Contains User Manual, Evaluation PCB Schematic, Evaluation Software) | E K I T 0 1 -<br>DC7GHJFRACTIONAL-NDMDER |

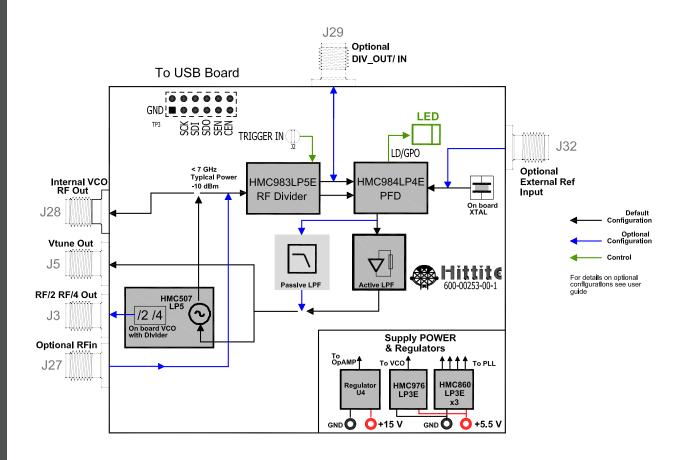

#### **Evaluation PCB Block Diagram**

### DC - 7 GHz FRACTIONAL-N DIVIDER AND FREQUENCY SWEEPER

#### **Theory of Operation**

The DC - 7 GHz FRACTIONAL-N DIVIDER can be used in following configurations:

- 1. Fractional-N or Integer Mode RF Frequency Divider or Prescaler

- 2. Fractional-N Frequency Synthesizer with an appropriate Phase Detector and VCO

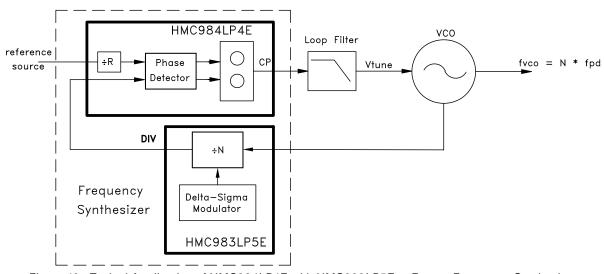

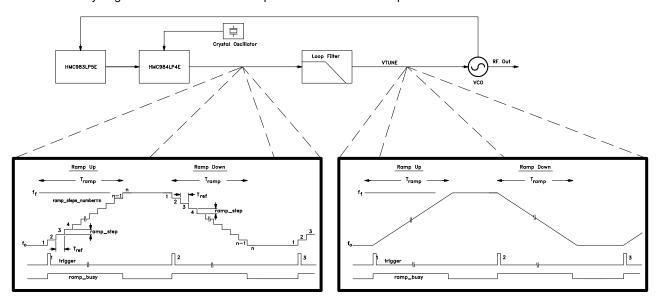

Primary target application of the DC - 7 GHz FRACTIONAL-N DIVIDER is to be used in conjunction with the AND FREQUENCY SWEEPER as shown in <u>Figure 19</u>. Together these two components form a high performance, low noise, ultra low spurious emissions fractional-N frequency synthesizer.

Figure 19. Typical Application of HMC984LP4E with HMC983LP5E to Form a Frequency Synthesizer

The DC - 7 GHz FRACTIONAL-N DIVIDER consists of the following functional blocks

- RF Input Buffer

- 2. 7 GHz Frequency Prescaler and Multi Modulus Divider

- 3. 48-bit Configurable Fractional Delta Sigma Modulator

- 4. Bias Circuit

- 5. Differential Output Driver

- 6. Frequency Sweeper

- 7. Main Serial Port Interface

- 8. Auxiliary Serial Port Interface (Output Only)

- General Purpose Digital IO

- 10. Power On Reset Circuit

#### **RF Input Buffer**

The RF input stage provides the path from the external VCO to the fractional RF Divider. The RF input path is rated to operate nominally from DC to 7 GHz. The DC - 7 GHz FRACTIONAL-N DIVIDER RF input stage is a differential common emitter stage with DC coupling, and is protected by ESD diodes as shown in Figure 20. RF input is not matched to 50  $\Omega$  due to wide input frequency range. At low frequencies, a simple shunt 50  $\Omega$  resistor can be used external to the package to provide a 50  $\Omega$  match. For better performance it is recommended to match the RF inputs externally and provide differential drive from the VCO. In most applications the input is used single-ended into either the VCOIP or VCOIN pin with the other input connected to ground through a DC blocking capacitor. The preferred input level for best spectral performance is -10 dBm.

Figure 20. RF Input Stage

#### RF Path Fractional-N Divider

The RF input buffer is followed by a high frequency prescaler and a multi modulus divider. The divider has been designed for the best output phase noise and spurious performance in both fractional and integer mode. The fractional-N divider can divide input frequencies from 32 to  $2^{20}$ -1 (1048575) in integer mode and from 36 to  $2^{20}$ -5 (1048571) in fractional-N mode. The divider output pulse width depends on the RF input period and is adjustable via SPI setting (refer to Duty Cycle Setting in register Reg 00h Chip ID, Soft Reset, Read Register[14:12]). The output pulse width recommended setting is 40% to 60% where possible. At low output frequencies it may not be possible to set 50% duty cycle. In such cases the maximum pulse width setting is recommended.

Figure 21. Divider Path

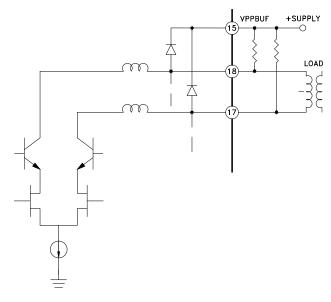

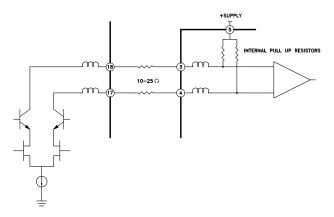

#### **Divider Output Buffer**

The divider output is differential and the output buffer stage is an open collector amplifier with off-chip pull-up resistors. Due to sharp rise and fall times at the divider output, the external path should be designed differentially using RF techniques.

When DC - 7 GHz FRACTIONAL-N DIVIDER and AND FREQUENCY SWEEPER are operating together as a frequency synthesizer, 50  $\Omega$  pull-up resistors are provided in AND FREQUENCY SWEEPER.

VPPBUF pin should be connected to 5 V power supply. This pin does not sink DC current and is only used to bias the internal ESD diodes and to provide an appropriate voltage level for the phase detector chip (AND FREQUENCY SWEEPER). The two possible interface configurations are shown in Figure 22 and Figure 23 below.

The rising edge of the HMC983LP5E divider output divCkPFDp and falling edge of divCkPFDn are conditioned and resynchronized for best spectral performance. The alternative edges are not This means for best spectral performance the HMC983LP5E must be used with a PFD, not an analog mixer.

Figure 22. Generic Divider Output Interface

Figure 23. Divider Interface with AND FREQUENCY SWEEPER

#### Chip Address Pins

The DC - 7 GHz FRACTIONAL-N DIVIDER has three SPI chip address pins (SPI address [2:0] = 'CHIP3, CHIP2, CHIP1'), which enable multiple DC - 7 GHz FRACTIONAL-N DIVIDER devices to use the same SPI bus. SPI chip address bits are read at power up, or every time DC - 7 GHz FRACTIONAL-N DIVIDER is reset. By default, all three pins are internally pulled to DVDD, thus there is no need to connect the pins to DVDD to set them to logic high. To assign a '0' to any chip address bit, the corresponding pin should be connected to ground.

When used on the same SPI bustogether with the companion part (the AND FREQUENCY SWEEPER), to form a frequency synthesizer, some SPI commands, such as changing the reference division ratio to the AND FREQUENCY SWEEPER may also require an action by the DC - 7 GHz FRACTIONAL-N DIVIDER. In order to avoid the necessity to write two separate SPI transfers to implement one command (one to configure AND FREQUENCY SWEEPER, and the other one to configure the DC - 7 GHz FRACTIONAL-N DIVIDER), it is possible to write the SPI address of the companion part (AND FREQUENCY SWEEPER) into Reg 09h of the DC - 7 GHz FRACTIONAL-N DIVIDER. In such cases, the DC - 7 GHz FRACTIONAL-N DIVIDER is able to recognize an SPI command to the companion part (the AND FREQUENCY SWEEPER) that requires its own action, and act accordingly to update its own corresponding

### DC - 7 GHz FRACTIONAL-N DIVIDER AND FREQUENCY SWEEPER

registers. Writing DC - 7 GHz FRACTIONAL-N DIVIDER's own chip address to the companion chip address register Reg 09h will disable this feature.

#### Saturation Detection Input Pins DNSAT, UPSAT

When the DC-7 GHz FRACTIONAL-N DIVIDER is operating with its companion chip the AND FREQUENCY SWEEPER as a frequency synthesizer, it automatically detects large phase errors and tries to tune the VCO faster by using its algorithm for cycle-slip prevention (CSP). The UPSAT and DNSAT provide indication which frequency is higher (VCO or Reference) from the counterpart Phase Detector/Charge Pump (the AND FREQUENCY SWEEPER). The CSP algorithm manipulates the RF Divider and the Phase Detector at appropriate intervals to lock faster. See AND FREQUENCY SWEEPER data sheet for more details. These pins should be connected to ground if not used.

#### **REF Eno Pin**

REF\_Eno pin is a digital output pin that is used by the DC - 7 GHz FRACTIONAL-N DIVIDER to request crystal oscillator clock from the Phase Detector / Charge Pump chip (the AND FREQUENCY SWEEPER).

The crystal oscillator clock is multiplexed on the DC - 7 GHz FRACTIONAL-N DIVIDER's DNSAT pin. The internal frequency divider, programmed in Reg 02h, is used to generate the actual reference frequency present at the phase detector. The imported clock is only used to communicate through the AUXSPI. At all other times, the clock and the local reference dividers are turned off.

In stand-alone applications, if the DC - 7 GHz FRACTIONAL-N DIVIDER is required to communicate through the auxiliary SPI, the DC - 7 GHz FRACTIONAL-N DIVIDER will expect to receive the auxiliary SPI clock on DNSAT pin. Setting Reg 04h[15] = 1 keeps the auxiliary SPI clock enabled on the DNSAT pin.

#### Multi Purpose Digital IO Pins D0, D1, D2, D3, D4 (GPIO Pins)

The five general purpose digital input/outputs can be used for various modes of operation as well as test/debugging purposes. GPIO pins are enabled by writing Reg 01h[4] = 1 (GPIO master enable). Setting Reg 01h[4] = 0 places the GPIO pins in tri-state high impedance mode.

GPIO pins are configured in  $\frac{\text{Reg 08h}}{13:0}$ . All of the pins can configured to be either inputs or outputs by writing to  $\frac{\text{Reg 08h}}{13:0}$ . In frequency sweep mode, pin D4 can be used as an external trigger pin, by writing  $\frac{\text{Reg 08h}}{13:0} = 0$ .

Writing to Reg 08h[3:0] selects DC - 7 GHz FRACTIONAL-N DIVIDER's internal signals to be multiplexed out on the GPIO pins, as shown in Table 5. Signals include:

- 1. The output of the Delta-Sigma Modulator Reg 08h[3:0] = '0010'b.

- 2. GPIO test signals Reg 08h[3:0] = '0000'b, which outputs data written to Reg 08h[8:4] to test the GPIO pins.

- Sweep status flags, when the DC 7 GHz FRACTIONAL-N DIVIDER is configured to be in sweep mode Reg 08h[3:0] = '1000'b.

#### Table 5. GPIO Pin Assignment and Output Signals

| Dog 09b(2.01 | DC - 7 GHz FRACTIONAL-N DIVIDER GPIO Pins |                 |                 |                 |                 |  |

|--------------|-------------------------------------------|-----------------|-----------------|-----------------|-----------------|--|

| Reg 08h[3:0] | D4                                        | D3              | D2              | D1              | D0              |  |

| 0000         | gpo_test_out[4]                           | gpo_test_out[3] | gpo_test_out[2] | gpo_test_out[1] | gpo_test_out[0] |  |

| 0001         | reserved                                  | reserved        | reserved        | reserved        | reserved        |  |

| 0010         | DSM_OUT[4]                                | DSM_OUT[3]      | DSM_OUT[2]      | DSM_OUT[1]      | DSM_OUT[0]      |  |

| 0011         | reserved                                  | reserved        | reserved        | reserved        | reserved        |  |

| 0100         | reserved                                  | reserved        | reserved        | reserved        | reserved        |  |

| 0101         | reserved                                  | reserved        | reserved        | reserved        | reserved        |  |

### DC - 7 GHz FRACTIONAL-N DIVIDER AND FREQUENCY SWEEPER

#### Table 5. GPIO Pin Assignment and Output Signals

| Dog 09b(2.01 | DC - 7 GHz FRACTIONAL-N DIVIDER GPIO Pins |                 |                |                |          |

|--------------|-------------------------------------------|-----------------|----------------|----------------|----------|

| Reg 08h[3:0] | D4                                        | D3              | D2             | D1             | D0       |

| 0110         | reserved                                  | reserved        | reserved       | 0              | 0        |

| 0111         | reserved                                  | reserved        | reserved       | reserved       | reserved |

| 1000         | ramp_ready_flag                           | ramp_start_flag | ramp_stop_flag | ramp_busy_falg | reserved |

| 1001-1111    | 0                                         | 0               | 0              | 0              | 0        |

#### Fractional Mode of Operation

In addition to providing simple integer division ratios, the DC - 7 GHz FRACTIONAL-N DIVIDER has a sophisticated, configurable 48-bit Delta Sigma Modulator (DSM), that allows fractional division of the input frequency in ultra fine steps. The DSM's size can be configured to 16/24/32/48 bits (Reg 16h[5:0]). DC - 7 GHz FRACTIONAL-N DIVIDER's auto-seed mode allows coherent frequency sweeps.

The DC - 7 GHz FRACTIONAL-N DIVIDER with its counterpart (the AND FREQUENCY SWEEPER), together with an external VCO comprise a fully functional fractional-N synthesizer. In that case, the output frequency of the external VCO is given by:

$$f_{vco} = \frac{f_{xtal}}{R} \cdot N_{int} + \frac{f_{xtal}}{R \cdot 2^L} \cdot N_{frac} = f_{int} + f_{frac}$$

(Eq 1)

When the DC - 7 GHz FRACTIONAL-N DIVIDER is being used as frequency divider, the output frequency is given by;

$$f_{out} = \frac{f_{vco}}{N_{int} + \frac{N_{frac}}{2^L}}$$

(Eq 2)

Where

$f_{vco}$  is the VCO frequency in Hz;

f<sub>xtal</sub> is the crystal oscillator frequency in Hz;

N<sub>int</sub> is the integer part of frequency division ratio (set in Reg 05h[19:0]);

$N_{frac}$  is the fractional part of frequency division ratio ( $N_{frac}[47:18] = \frac{\text{Reg 06h}}{29:0}$ ,  $N_{frac}[17:0] = \frac{\text{Reg 07h}}{29:0}$

R is the reference frequency division ratio;

L is the size of the DSM accumulators (set in Reg 16h[5:0])

**Example 1:** Calculate the VCO frequency with the following parameters;

$$\begin{split} f_{xtal} &= 50 \text{ MHz}; & f_{pfd} = 25 \text{ MHz} \\ N_{int} &= 25; & N_{free} = 1; & L = 24 \end{split}$$

Where  $f_{PFD}$  is the frequency at the phase detector, thus R = 2. According to (Eq 1), the VCO frequency with the above parameters will be;

$$f_{vco} = \frac{50MHz}{2} \cdot 25 + \frac{50MHz}{2 \cdot 2^{24}} \cdot 1 = 2500MHz + 1.49Hz$$

If accumulator width (L) is changed to 48-bit, then the frequency resolution will improve and the fractional resolution of the VCO frequency will be 88.8178 nano-Hz.

Example 2: Set the VCO frequency to 4600.025 MHz using 100 MHz Crystal, R = 2 and L = 16. Compare if L = 32.

For this example the  $f_{PFD} = 100 \text{ MHz/2} = 50 \text{ MHz}$ ,

The overall division ratio is 4600.025 MHz/50 MHz = 92.0005

The nearest integer would be 92, thus  $N_{int} = \frac{\text{Reg } 05h}{19:0} = 92d = 5Ch$ .

For L = 16,  $N_{frac}$  = 32.768 or 33d rounded up. Thus  $N_{frac}$  = 33d or 21h (Reg 06h[29:0] = 0, Reg 07h[17:0] = 21h).

For L = 32,  $N_{frac}$  = 2147483.648 or 2147484d rounded up. Thus  $N_{frac}$  = 20C49Ch (Reg 06h[29:0] = 8h, Reg 07h[17:0] = '00110001001100'd).

Since  $N_{frac}$  must be an integer, the actual frequencies in the two cases will have an error of + 177.02 Hz for L = 16 and only +0.004098 Hz for L = 32.

#### Phase Noise in Integer and Fractional Modes

In a normal integer frequency divider the in-band phase noise is scaled from the input phase noise by 20Log10(N), where N is the divider value. In HMC983LP5E fractional mode, the frequency divider is modulated by the Delta Sigma Modulator to generate output frequencies that are fractional multiple of the input frequency. Delta Sigma Modulator shapes the quantization noise such that quantization noise density has a high pass shape which peaks at Fs/2, where Fs is the sampling frequency (the divider output frequency in case of HMC983LP5E). In fractional mode this quantization noise peak appears at an offset frequency of Fout/2. In the PLL, this peak is attenuated by the loop filter. However, when the HMC983LP5E is used stand-alone in fractional mode its output will exhibit the quantization noise as shown in Figure 2 and Figure 3. As a result, it is not possible to achieve the same noise floor in fractional mode as in integer mode without further filtering.

#### **CW Frequency Sweeper**

The DC - 7 GHz FRACTIONAL-N DIVIDER features a built-in frequency sweeper function that supports automatic or externally triggered sweeps. External triggering can be executed via an external trigger pin D4 or the SPI interface.

DC - 7 GHz FRACTIONAL-N DIVIDER sweep function can be configured to operate in the following modes:

- 2-Way sweep mode

- Repeating alternating positive and negative frequency sweep ramps

- Frequency increments swept with automatic sequencer

- Automatic or triggered

- Symmetric or asymmetric (the positive ramp can have a different slope from that of the negative ramp)

- 1-Way Sweep Mode

- Repeating one directional frequency sweeps followed by a reset to the starting frequency

- · Frequency increments swept with automatic sequencer

- Triggered

#### User defined sweep mode

- · Manually programmed user defined sweep patterns

- Triggered

- Symmetric or asymmetric (the positive ramp can have a different slope from that of the negative ramp)

### DC - 7 GHz FRACTIONAL-N DIVIDER AND FREQUENCY SWEEPER

In all sweep modes, the starting sweep direction can be set to positive (increasing) or negative (decreasing). The trigger can be applied instantaneously or delayed by a programmable time delay.

DC - 7 GHz FRACTIONAL-N DIVIDER's sweep function is illustrated in <u>Figure 24</u>. The DC - 7 GHz FRACTIONAL-N DIVIDER generates a frequency sweep by implementing automatic, or triggered in User Defined Mode, discrete miniature frequency increments in time. A smooth and continuous sweep is then generated, at the output of the VCO, after the stepped signal is filtered by the loop filter, as shown in <u>Figure 24</u>. The stepped sweep approach enables the frequency synthesizer (comprising of DC - 7 GHz FRACTIONAL-N DIVIDER together with its counterpart, the HMC984LP4E) to be in lock for the entire duration of the sweep. This approach results in a number of advantages over conventional methods including:

- The ability to generate a linear sweep.

- The ability to have phase coherence between different sweep ramps, so that the phase profile of each sweep is identical.

- The ability to generate user defined sweeps in User Defined Sweep Mode.

Figure 24. DC - 7 GHz FRACTIONAL-N DIVIDER Sweep Function

It is important to note that the synthesized ramp is subject to normal phase locked loop dynamics. If the loop bandwidth in use is much wider than the rate of frequency increments then the locking will be fast and the ramp will have a staircase shape. If the update rate is higher than the loop bandwidth, as is normally the case, the loop will not fully settle before a new frequency step is received. Hence the swept output will have a lag and will sweep in a near continuous fashion.

In all sweep modes, ramp\_busy flag indicates an active sweep and will stay high between the 1st and nth ramp increment. ramp\_busy may be monitored on pin D1 by setting Reg 08h[3:0] = 8h.

#### Triggering

In sweep mode, the DC - 7 GHz FRACTIONAL-N DIVIDER can be triggered via one of two methods

- SPI trigger by setting Reg 0Eh[12]=1. This triggering method is asynchronous to the reference clock. To enable SPI trigger write Reg 0Eh[13] = 0.

- or applying an external trigger on pin D4. Setting Reg 0Eh[13] = 1 and Reg 08h[13] = 0h configures DC 7 GHz FRACTIONAL-N DIVIDER's pin D4 as external trigger input. External trigger on pin D4 is triggered on the rising edge of the trigger. GPIO master enable (Reg 01h[4] = 1) is also required.

External triggering method can be synchronized with the reference clock, by enabling trigger delay (Reg 0Eh [7] = 1), and programming a trigger delay in Reg 05h[20:0] = number of delayed reference periods.

Writing Reg 05h[20:0] = 1 for example ensures that the trigger is applied at the instant of the rising edge of the next reference rising edge. To disable trigger delay write Reg 0Eh [7] = 0.

#### 2-Way Sweep Mode

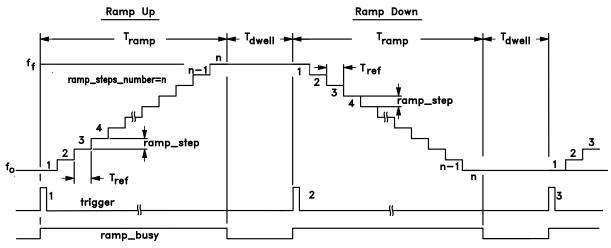

DC - 7 GHz FRACTIONAL-N DIVIDER's 2-Way sweep mode is shown in <u>Figure 25</u>. The 2-Way sweep mode can be automatic or triggered. In automatic 2-way sweep, the trigger is generated internally based on user defined 2-way sweep mode configuration. In a triggered 2-way sweep, frequency ramps are triggered either by external pin D4, or SPI trigger.

Figure 25. DC - 7 GHz FRACTIONAL-N DIVIDER 2-Way Triggered Sweep

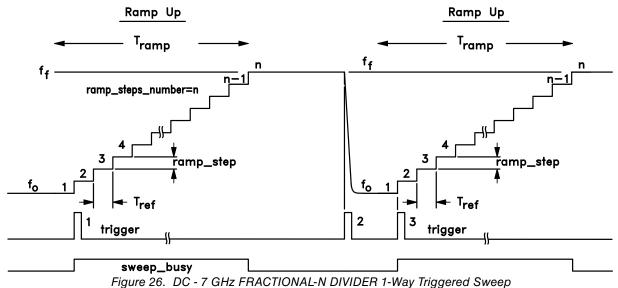

#### **Triggered 1-Way Sweeps**

DC - 7 GHz FRACTIONAL-N DIVIDER's 1-Way sweeps is shown in <u>Figure 26</u>. Unlike 2-Way sweeps, 1-Way sweeps require that the VCO hop back to the start frequency after the dwell period. Triggered 1-Way sweeps also require a 3rd trigger to start the new sweep. The 3rd trigger must be timed appropriately to allow the VCO to settle after the large frequency hop back to the start frequency. Subsequent odd numbered triggers will start each sweep and repeat the process.

### DC - 7 GHz FRACTIONAL-N DIVIDER AND FREQUENCY SWEEPER

1-Way sweeps are not recommended in auto-sweep mode since in auto-sweep the new sweep will start immediately

#### **User Defined Sweep Mode**

after the 2nd trigger, as it does in 2-Way mode.

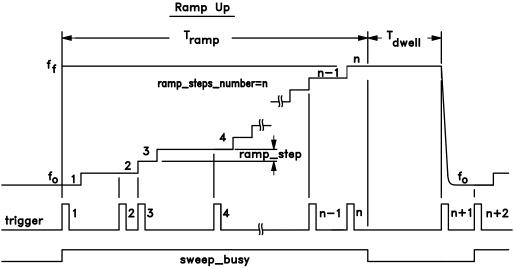

In User Defined Sweep mode, the DC - 7 GHz FRACTIONAL-N DIVIDER is able to generate various user-defined sweep patterns by adjusting the time interval between adjacent frequency increments, which are executed by trigger events. DC - 7 GHz FRACTIONAL-N DIVIDER's User Defined Sweep Mode is shown in <a href="Figure 27">Figure 27</a>. In this mode, an external trigger is required for each frequency increment of the sweep.

Figure 27. DC - 7 GHz FRACTIONAL-N DIVIDER User Defined Sweep

User defined sweep can function in both 1-Way or 2-Way sweep mode. In 1-Way sweep mode, the n+1 trigger will cause the ramp to jump to the start frequency, and the n+2 trigger will restart the 1-way sweep.

#### **Detailed Sweeper Configuration**

Recommended procedure for configuring DC - 7 GHz FRACTIONAL-N DIVIDER sweeper in all three modes is shown in Table 6.

# DC - 7 GHz FRACTIONAL-N DIVIDER AND FREQUENCY SWEEPER

#### Table 6. DC - 7 GHz FRACTIONAL-N DIVIDER Sweeper Configuration Sequence

|       | B                                                                                               | Sweeper Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                              |  |

|-------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Steps | Description                                                                                     | 2-Way Sweep Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                     | User Defined Sweep Mode                                                                                                                                                                                                                                                                                                                          | 1-Way Sweep Mode                                                                                                                                                                                                                                                                             |  |

| 1     | Lock to start<br>frequency (f <sub>0</sub> )                                                    | set the integer (Reg 05h) and fractional (Reg 06h and Reg 07h) divider values.     Optionally, if required the seed (Reg 0Ah and Reg 0Bh) can also be programmed                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                              |  |

| 2     | Place the DSM in sweep mode                                                                     | • Write Reg 0Eh[11] = 1                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                              |  |

| 3     | Configure<br>sweep mode                                                                         | Disable single step ramp mode (Reg OEh[24] = 0), so that each frequency increment will be incremented automatically     Enable 2-way sweep mode (Disable 1-way sweep mode (Reg OEh[25] = 0))     ToplacetheDC7GH2FRACTIONAL-NDIVIDER in automatic sweep mode write Reg OEh[2:3] = '11'. To place the DC-7GH2FRACTIONAL-NDIVIDERin triggered mode write Reg OEh[2:3] = '00'.                                                                                          | Enable the single step ramp mode (Reg_0Eh[24] = 1), so that each frequency increment will require a trigger     Enable 1-way sweep mode (Reg_0Eh[25] = 1), or enable 2-Way sweep mode (Reg_0Eh[25] = 1)     ToplacetheDC7GHzFRACTIONAL-NDIVIDER in triggered mode write Reg_0Eh[2:3] = '00'. Automatic User Defined Sweep mode is not supported. | Disable single step ramp mode (Reg OEh[24] = 0), so that each frequency increment will be incremented automatically  Enable 1-way sweep mode (Reg OEh[25] = 1)  ToplacetheDC7GH2FRACTIONAL-NDMIDER in triggered mode write Reg OEh[2:3] = '00'. Automatic 1-Way Sweep mode is not supported. |  |

| 4     | Program<br>Sweep<br>Direction                                                                   | • Reg 0Eh[26] = 1 begin sweep in positive direction, Reg 0Eh[26] = 0 begin sweep in negative direction                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                              |  |

| 5     | Configure<br>symmetrical/<br>asymmetrical<br>sweep                                              | Program ramp mode (symmetrical - Reg 0Eh[22] = 1, asymmetrical - Reg 0Eh[22] = 0). If symmetrical ramp mode is selected (Reg 0Eh[22] = 1), only Up sweep parameters will be used for both positive and negative sweeps, and hence down sweep parameters don't need to be programmed. In symmetrical ramp mode the positive and negative ramps are identical and opposite in direction.  Program Reg 0Eh[22] = 1. Asymmetrical sweep is not defin in 1-Way Sweep mode |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                              |  |

| 6     | Program<br>Up Sweep<br>Parameters                                                               | • Set step size (step size[47:18] = Reg                                                                                                                                                                                                                                                                                                                                                                                                                              | 10h[29:0], dwell time[17:0] = Reg 11h[17<br>12h[29:0], step size[17:0] = Reg 13h[17:0<br>number of steps[47:18] = Reg 14h[29:0],                                                                                                                                                                                                                 | ])                                                                                                                                                                                                                                                                                           |  |

| 7     | Program Down Sweep Parameters (Only if using asymmetrical sweep (if Reg 0Eh[22] = 0) in Step 5) | Set dwell time (dwell time[47:0] = ROTh[17:0]) Set step size (step size[47:18] = FOTH[17:0]) Independent of steps in a sweep (normal number of steps[17:0] = Reg ODh[17:0]                                                                                                                                                                                                                                                                                           | Reg 19h[29:0], step size[17:0] = Reg umber of steps[47:18] = Reg 0Ch[29:0],                                                                                                                                                                                                                                                                      | Asymmetrical sweep is not defined in 1-Way Sweep mode                                                                                                                                                                                                                                        |  |

| 8     | Configure and apply trigger                                                                     | To use external trigger on pin D4 writt  Oh to configure pin D4 to be an inpu Enable trigger delay (Reg 0Eh[7] =  If using trigger delay, write delay                                                                                                                                                                                                                                                                                                                | = 0 to select SPI trigger. SPI trigger is exe Reg 0Eh[13] = 1 to configure pin D4 ast. Applying master enable to GPIO pins 1), or disable trigger delay (Reg 0Eh[7] value to Reg 05h[20:0], where Reg 05 1 for example ensures that the trigger is                                                                                               | s an external trigger. Write Reg 08h[13] (Reg 01h[4] = 1 ) is required. = 0). h[20:0] = number of delayed reference                                                                                                                                                                          |  |

#### DC - 7 GHz FRACTIONAL-N DIVIDER sweep parameters are defined in the following way:

| $f_o$ | Initial frequency of the synthesizer                 |

|-------|------------------------------------------------------|

| $f_f$ | Frequency of the synthesizer at the end of the sweep |

| R     | Reference divider value(Reg 02h[13:0])               |

| stepsize          | frequency increment step size. In case of symmetric and UP sweeps, stepsize[47:18] = $\frac{\text{Reg 12h}}{\text{[29:0]}}, \text{ stepsize}[17:0] = \frac{\text{Reg 13h}}{\text{[17:0]}}. \text{ In case of asymmetric sweeps,}$ $(\text{downsweep stepsize}[47:18] = \frac{\text{Reg 12h}}{\text{[29:0]}}, \text{ down sweep stepsize}[17:0] = \frac{\text{Reg 13h}}{\text{[17:0]}}$ |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\Delta f_{step}$ | Frequency step size = $stepsize \cdot \frac{f_{xtal}}{2^{L} \cdot R}$ ,                                                                                                                                                                                                                                                                                                                |

| L                 | Size of the DSM (set in Reg 16h[5:0])                                                                                                                                                                                                                                                                                                                                                  |

| T <sub>ref</sub>  | Period of the divided reference ( $f_{PFD}$ ) at the phase detector. $T_{ref} = \frac{R}{f_{xtal}}$                                                                                                                                                                                                                                                                                    |

| N                 | Total number of frequency step increments in a single sweep. N [47:18] = $\frac{\text{Reg 14h}}{\text{[29:0]}}$ , N[17:0] = $\frac{\text{Reg 15h}}{\text{[17:0]}}$                                                                                                                                                                                                                     |

| $T_{ramp}$        | Total time of one frequency sweep from $f_o$ to $f_f$ . $T_{ramo} = T_{ref} \times N$                                                                                                                                                                                                                                                                                                  |

Then final frequency  $f_f$  is given by:  $f_f = f_o + (\Delta f_{step} \times N)$

Setting autoseed ( $\underline{\text{Reg 0Eh}}[8] = 1$ ) ensures that different sweeps have identical phase profile. This is achieved by loading the seed (seed[47:18] =  $\underline{\text{Reg 0Ah}}[29:0]$ , seed[17:0] =  $\underline{\text{Reg 0Bh}}[17:0]$ ) into the phase accumulator at the beginning of each ramp.

Example: Calculate sweep parameters for an asymmetric 2-Way sweep from  $f_0 = 3000$  MHz to  $f_f = 3105$  MHz with positive  $T_{ramp} \approx 2$  ms, and negative  $T_{ramp} \approx 4$  ms, and positive dwell time = negative dwell time = 2  $\mu$ s, with  $f_{PD} = 50$  MHz, and a 48-bit delta-sigma modulator size. Assuming R = 1.

- 1. Calculate the integer and fractional divider values for initial start frequency f<sub>0</sub>

- Start Nint =  $\frac{\text{Reg } 05h}{\text{Start Nint}}$  = 60d

- Start Nfrac = <u>Reg 06h</u> = <u>Reg 07h</u> = 0d

- 2. Calculate the number of divided (R = 1) reference periods in the sweep = number of frequency increments N

- Nup = 2 ms/(1/50 MHz) = 100000

- Ndown = 4 ms/(1/50 MHz) = 2000000

- 3. Calculate stepsize (size of frequency increments)

- stepssize  $up = abs(f_f f_0)/Nup = abs(3000 MHz 3105 MHz)/100000 = 1050 Hz$ . Then as  $per \underline{Table 6}$ ,  $\underline{Reg} \underline{12h}[29:0] = 0h$ ,  $\underline{Reg 13h}[17:0] = 1050d = 41Ah$

- stepsize down = abs(ff f0)/Ndown = abs(3000 MHz 3105 MHz)/200000 = 525 Hz Then as per <u>Table 6</u>, Reg 19h[29:0] = 0h, Reg 1Ah[17:0] = 1050d = 41Ah

Note that it is possible to have a case where the frequency  $f_f$  cannot be generated exactly. In that case it is required to approximate the final frequency to  $f_f = f_o + (\Delta f_{step} \times N) \approx$  desired final frequency.

- Calculate number of divided (R = 1) reference periods in required dwell time

- Up dwell time ( $\frac{\text{Reg 10h}}{29:0}$ ],  $\frac{\text{Reg 11h}}{17:0}$ ) = down dwell time ( $\frac{\text{Reg 06h}}{29:0}$ ],  $\frac{\text{Reg 07h}}{17:0}$ ) = dwell time/ (1/50 MHz) = 2  $\mu$ s/(1/50 MHz) = 100. Then as per  $\frac{\text{Table 6}}{19:0}$ ,  $\frac{\text{Reg 10h}}{19:0}$ ] =  $\frac{\text{Reg 06h}}{19:0}$ ] = 0h, and  $\frac{\text{Reg 11h}}{17:0}$ ] =  $\frac{\text{Reg 07h}}{17:0}$ ] = 100d = 64h.

Then proceed to configure the sweep according to the steps outlined in Table 6.

#### Serial Port Interface

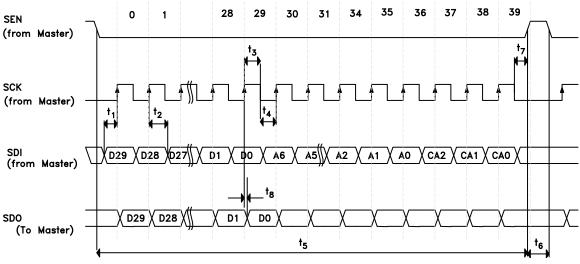

The DC - 7 GHz FRACTIONAL-N DIVIDER features a four wire serial port for simple communication with the host controller. Typical serial port operation can be run with SCK at speeds up to 30 MHz.

The details of SPI access for the DC - 7 GHz FRACTIONAL-N DIVIDER is provided in the following sections. Note that the READ operation below is always preceded by a WRITE operation to Register 0 to define the register to be queried. Also note that every READ cycle is also a WRITE cycle in that data sent to the SPI while reading the data will also be stored by the DC - 7 GHz FRACTIONAL-N DIVIDER when SENb goes high. If this is not desired then it is suggested to write to Register 0 during the READ operation so that the status of the device will be unaffected.

### DC - 7 GHz FRACTIONAL-N DIVIDER AND FREQUENCY SWEEPER

#### Power on Reset and Soft Reset

The DC - 7 GHz FRACTIONAL-N DIVIDER has a built in Power On Reset (POR) and a serial port accessible Soft Reset (SR). POR is accomplished when power is cycled for the DC - 7 GHz FRACTIONAL-N DIVIDER while SR is accomplished via the SPI by writing Reg 00h = 80h, followed by writing Reg 00h = 00h. All chip registers will be reset to default states approximately 250 us after power up.

#### Serial Port WRITE Operation

The host changes the data on the falling edge of SCK and the DC - 7 GHz FRACTIONAL-N DIVIDER reads the data on the rising edge.

A typical WRITE cycle is shown in Figure 28. It is 40 clock cycles long.

- 1. The host both asserts SENb (active low Serial Port Enable) and places the MSB of the data on SDI followed by a rising edge on SCK.

- 2. DC 7 GHz FRACTIONAL-N DIVIDER reads SDI (the MSB) on the 1st rising edge of SCK after SENb.

- 3. DC 7 GHz FRACTIONAL-N DIVIDER registers the data bits, D29:D0, in the next 29 rising edges of SCK (total of 30 data bits).

- 4. Host places the 5 register address bits, A6:A0, on the next 7 falling edges of SCK (MSB to LSB) while the DC 7 GHz FRACTIONAL-N DIVIDER reads the address bits on the corresponding rising edge of SCK.

- 5. Host places the 3 chip address bits, CA2:CA0=[110], on the next 3 falling edges of SCK (MSB to LSB). Note the DC 7 GHz FRACTIONAL-N DIVIDER chip address is fixed as "7d" or "111b".

- 6. SENb goes from low to high after the 40th rising edge of SCK. This completes the WRITE cycle.

- 7. DC 7 GHz FRACTIONAL-N DIVIDER also exports data back on the SDO line. For details see the section on READ operation.

#### Serial Port READ Operation

The SPI can read from the internal registers in the chip. The data is available on SDO pin. This pin itself is tri-stated when the device is not being addressed. However when the device is active and has been addressed by the SPI master, the DC - 7 GHz FRACTIONAL-N DIVIDER controls the SDO pin and exports data on this pin during the next SPI cycle.

DC - 7 GHz FRACTIONAL-N DIVIDER changes the data to the host on the rising edge of SCK and the host reads the data from DC - 7 GHz FRACTIONAL-N DIVIDER on the falling edge.

A typical READ cycle is shown in <u>Figure 28</u>. Read cycle is 40 clock cycles long. To specifically read a register, **the address of that register must be written to dedicated Reg 0h**. This requires two full cycles, one to write the required address, and a 2nd to retrieve the data. A read cycle can then be initiated as follows;

- 1. The host asserts SENb (active low Serial Port Enable) followed by a rising edge SCK.

- 2. DC 7 GHz FRACTIONAL-N DIVIDER reads SDI (the MSB) on the 1st rising edge of SCK after SENb.

- 3. DC 7 GHz FRACTIONAL-N DIVIDER registers the data bits in the next 29 rising edges of SCK (total of 30 data bits). The LSBs of the data bits represent the address of the register that is intended to be read.

- 4. Host places the 7 register address bits on the next7 falling edges of SCK (MSB to LSB) while the DC 7 GHz FRACTIONAL-N DIVIDER reads the address bits on the corresponding rising edge of SCK. For a read operation this is "0000000".

- 5. Host places the 3 chip address bits [111] on the next 3 falling edges of SCK (MSB to LSB).

- 6. SENb goes from low to high after the 40th rising edge of SCK. This completes the first portion of the READ cycle.

- 7. The host asserts SENb (active low Serial Port Enable) followed by a rising edge SCK.

### DC - 7 GHz FRACTIONAL-N DIVIDER AND FREQUENCY SWEEPER

- 8. DC 7 GHz FRACTIONAL-N DIVIDER places the 30 data bits, 7 address bits, and 3 chip id bits, on the SDO, on each rising edge of the SCK, commencing with the first rising edge beginning with MSB.

- 9. The host de-asserts SENb (i.e. sets SENb high) after reading the 40 bits from the SDO output. The 40 bits consists of 30 data bits, 7 address bits, and the 3 chip id bits. This completes the read cycle.

Note that the data sent to the DC - 7 GHz FRACTIONAL-N DIVIDER SPI during this portion of the READ operation is stored in the SPI when SENb is de-asserted. It is recommended that during the second phase of the READ operation that Reg 00h is addressed with either the same address or the address of another register to be read during the next cycle.

Figure 28. SPI Timing Diagram

$DVDD = 5 V \pm 10\%$ , GND = 0 V

#### Table 7. Main SPI Timing Characteristics

| Parameter      | Conditions            | Min | Тур | Max | Units |

|----------------|-----------------------|-----|-----|-----|-------|

| t <sub>1</sub> | SDI to SCK Setup Time | 8   |     |     | nsec  |

| t <sub>2</sub> | SDI to SCK Hold Time  | 8   |     |     | nsec  |

| t <sub>3</sub> | SCK High Duration [1] | 10  |     |     | nsec  |

| t <sub>4</sub> | SCK Low Duration      | 10  |     |     | nsec  |

| t <sub>5</sub> | SENb Low Duration     | 20  |     |     | nsec  |

| t <sub>6</sub> | SENb High Duration    | 20  |     |     | nsec  |

| t <sub>7</sub> | SCK to SENb [2]       | 8   |     |     | nsec  |

| t <sub>8</sub> | SCK to SDO out [3]    |     |     | 8   | nsec  |

<sup>[1]</sup> The SPI is relatively insensitive to the duty cycle of SCK.

<sup>[2]</sup> SENb must rise after the 32<sup>nd</sup> falling edge of SCK but before the next rising SCK edge. If SCK is shared amongst several devices this timing must be respected.

<sup>[3]</sup> Typical load to SDO is 10 pF, maximum 20 pF

### DC - 7 GHz FRACTIONAL-N DIVIDER AND FREQUENCY SWEEPER

#### Register Map

#### Table 8. Reg 00h Chip ID, Soft Reset, Read Register

| BIT    | TYPE | NAME                  | W  | DEFLT  | DESCRIPTION                                                                                                                                  |

|--------|------|-----------------------|----|--------|----------------------------------------------------------------------------------------------------------------------------------------------|

| [6:0]  | R/W  | Read Register Address | 7  | 0      | Address of the register to be read in the next cycle.                                                                                        |

| [7]    | R/W  | Soft Reset            | 1  | 0      | Soft Reset. Writing 1 generates soft reset. Resets all the digital and registers to default states. Writing 0 resumes normal chip operation. |

| [31:8] | R/W  | Chip ID               | 24 | 97330h | Part Number, Description. Read reg00h returns chip ID.                                                                                       |

#### Table 9. Reg 01h - Settings Register

| BIT | TYPE | NAME                    | W | DEFLT | DESCRIPTION                                       |

|-----|------|-------------------------|---|-------|---------------------------------------------------|

| [0] | R/W  | VCO Buffer Enable       | 1 | 1     | Enables VCO input RF buffer.                      |

| [1] | R/W  | Reserved                | 1 | 1     | Write 0 to this bit.                              |

| [2] | R/W  | AUXSPI Enable           | 1 | 1     | Enables Auxiliary SPI.                            |

| [3] | R/W  | Sigma Delta Enable      | 1 | 1     | Enables Sigma Delta Function.                     |

| [4] | R/W  | GPIO Enable             | 1 | 1     | Enables output from all GPIO pins.                |

| [5] | R/W  | RF Divider Enable       | 1 | 1     | Enables RF Divider.                               |

| [6] | R/W  | Output Buffer Enable    | 1 | 1     | Enables Divider Output Driver.                    |

| [7] | R/W  | Bias Enable             | 1 | 1     | Enables bias generator for all blocks.            |

| [8] | R/W  | PSCLK to Digital Enable | 1 | 1     | Enable Prescaler clock going to digital counters. |

| [9] | R/W  | Unused                  | 1 | 1     |                                                   |

#### Table 10. Reg 02h R-Divider Register

| BIT    | TYPE | NAME            | W  | DEFLT | DESCRIPTION                               |

|--------|------|-----------------|----|-------|-------------------------------------------|

| [13:0] | R/W  | R Divider Ratio | 14 | 1h    | Local value for reference division ratio. |

#### **Auxiliary SPI Registers**

The following two registers define the communication through the AUXSPI. If the AUXSPI is enabled (Reg 04h[4] = 0), writes to AUXSPI are executed via Reg 03h. The auxiliary device address is expected in Reg 04h[2:0]. If DC - 7 GHz FRACTIONAL-N DIVIDER is working as a standalone frequency divider the AUXSPI clock is expected on the DNSAT pin, and Reg 04h[15] must be set to 1. It is recommended to disable AUXSPI when not used.

#### Table 11. Reg 03h AUX. VCO Data Register

| BIT    | TYPE | NAME                    | W | DEFLT | DESCRIPTION                                            |

|--------|------|-------------------------|---|-------|--------------------------------------------------------|

| [3:0]  | R/W  | AUXSPI Register Address | 4 | 0h    | 4-bit Register address for the auxiliary device SPI.   |

| [12:4] | R/W  | AUXSPI Data             | 9 | 000h  | 9-bit long Register Data for the auxiliary device SPI. |

# DC - 7 GHz FRACTIONAL-N DIVIDER AND FREQUENCY SWEEPER

#### Table 12. Reg 04h - AUX. VCO Settings Register

| BIT     | TYPE      | NAME                         | W | DEFLT | DESCRIPTION                                                                             |

|---------|-----------|------------------------------|---|-------|-----------------------------------------------------------------------------------------|

| [2:0]   | R/W       | Auxiliary Device Address     | 3 | 000h  | Chip address used by AUXSPI.                                                            |

| [3]     | R/W       | Divide Clock by 4 for AUXSPI | 1 | 0     | 0 = Use XTAL for AUXSPI clock.                                                          |

| [-]     | ,         |                              |   |       | 1 = Use XTAL divided by 4 for AUXSPI clock.                                             |

| [4]     | R/W       | Start AUXSPI                 | 4 | 0     | 0 = Start AUXSPI when data is written to Reg03h.                                        |

| [4]     | I I I V V | Start AUASFI                 | ' |       | 1 = reserved.                                                                           |

| [7:5]   | R/W       | Reserved                     | 3 | 4h    |                                                                                         |

| [9:8]   | R/W       | Reserved                     | 2 | 2h    |                                                                                         |

| [13:10] | R/W       | Reserved                     | 4 | 8h    |                                                                                         |

| [14]    | R/W       | Reserved                     | 1 | 0     |                                                                                         |

| [15]    | R/W       | Keep Xtal Gate Open          | 1 | 0     | When 1, keeps the XTAL gate open to get XTAL from the companion PFD/CP chip HMC984LP4E. |

| [18:16] | R/W       | Reserved                     | 3 | 0h    |                                                                                         |

#### Table 13. Reg 05h Integer Set-Point, Trigger Delay Register

| BIT    | TYPE | NAME                   | W  | DEFLT | DESCRIPTION                                                                                                                                                                     |

|--------|------|------------------------|----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [19:0] | R/W  | Integer Division Ratio | 20 | 200d  | Sigma-Delta Modulator integer set point. Specifies the integer part of the division ratio for the RF Divider in fractional mode or the integer division ration in integer mode. |

|        |      | Ramp Trigger Delay     |    |       | Also used as delay counter for hardware ramp trigger (Pin D4) in ramp mode. This value is valid when Reg 0Eh [11] = 1.                                                          |

#### Table 14. Reg 06h Fractional Set-Point, Down Dwell Register (MSB)

| BIT    | TYPE | NAME                                               | W  | DEFLT | DESCRIPTION                                                                                                           |

|--------|------|----------------------------------------------------|----|-------|-----------------------------------------------------------------------------------------------------------------------|

| [29:0] | R/W  | Fractional Division Ratio (MSB)                    |    |       | Most significant 30 bits to specify fractional set point for Sigma-<br>Delta Modulator. Total Fractional bits are 48. |

| [29:0] | H/VV | Down Dwell for Asymmetric<br>Frequency. Ramp (MSB) | 30 | U     | Defines the MSB portion of the dwell down time in the asymmetric frequency sweep mode, valid when Reg 0Eh[11]=1.      |

#### Table 15. Reg 07h Fractional Set-Point, Down Dwell Register (LSB)

|        | •    |                                                 | ,  |       | • , ,                                                                                                                 |

|--------|------|-------------------------------------------------|----|-------|-----------------------------------------------------------------------------------------------------------------------|

| BIT    | TYPE | NAME                                            | W  | DEFLT | DESCRIPTION                                                                                                           |

| [47:0] | R/W  | Fractional Division Ratio (LSB)                 |    | _     | Least significant 18 bits to specify fractional set point for Sigma-<br>Delta Modulator. Total Fractional bit are 48. |

| [17:0] |      | Down Dwell for Asymmetric Frequency. Ramp (LSB) | 18 |       | Defines the LSB portion of the dwell down time in the asymmetric frequency sweep mode, valid when Reg0E[11]=1.        |

FREQUENCY DIVIDERS & DETECTORS - SMT

### DC - 7 GHz FRACTIONAL-N DIVIDER AND FREQUENCY SWEEPER

#### Table 16. Reg 08h GPIO Configuration Register

| BIT    | TYPE | NAME                  | W | DEFLT  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                      |

|--------|------|-----------------------|---|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [3:0]  | R/W  | GPO Output Select     | 4 | 0h     | Selects exported output signals to GPIO pins. See <u>Table 5</u> for details. Master enable for GPIO Reg 01h[4] = 1 is required.                                                                                                                                                                                                                 |