# 1.95 GHz to 3.4 GHz, Tunable Band-Pass Filter

Data Sheet HMC891ALP5E

#### **FEATURES**

Amplitude settling time: 200 ns

Re-entry rejection (wideband rejection): ≥30 dB

Single-chip replacement for mechanically tuned designs

RoHs compliant, 32-lead, 5 mm x 5 mm LFCSP package

#### **APPLICATIONS**

Testing and measurement equipment

Military radar and electronic warfare/electronic counter

measure (ECM)

Satellite communication and space Industrial and medical equipment

#### **GENERAL DESCRIPTION**

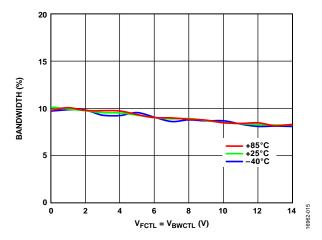

The HMC891ALP5E is a monolithic microwave integrated circuit (MMIC) band-pass filter that features a user-selectable pass band frequency. The 3 dB filter bandwidth is approximately 9% and the 20 dB filter bandwidth is approximately 23%. The center frequency ( $f_{\text{CENTER}}$ ) can be varied between 1.95 GHz and 3.4 GHz by applying an analog tune voltage between 0 V and 14 V.

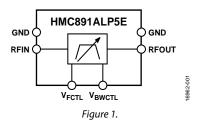

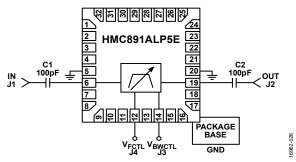

#### **FUNCTIONAL BLOCK DIAGRAM**

This tunable filter can be used as a smaller alternative to physically large switched filter banks and cavity tuned filters.

The HMC891ALP5E has excellent microphonics due to the monolithic design, and provides a dynamically adjustable solution in advanced communications applications.

Trademarks and registered trademarks are the property of their respective owners.

## **TABLE OF CONTENTS**

| Features                                    | . ] |

|---------------------------------------------|-----|

| Applications                                | . 1 |

| Functional Block Diagram                    |     |

| General Description                         |     |

| Revision History                            |     |

| Specifications                              |     |

| Absolute Maximum Ratings                    |     |

| Pin Configuration and Function Descriptions |     |

| Typical Performance Characteristics    | 6  |

|----------------------------------------|----|

| Theory of Operation                    | 9  |

| Applications Information               | 10 |

| Typical Application Circuit            | 10 |

| Evaluation Printed Circuit Board (PCB) | 10 |

| Outline Dimensions                     | 11 |

| Ordering Guide                         | 11 |

### **REVISION HISTORY**

9/2018—Revision 0: Initial Version

## **SPECIFICATIONS**

$T_{\text{A}} = 25^{\circ}\text{C}, \text{ center frequency control voltage } (V_{\text{FCTL}}) = bandwidth \ control \ voltage \ (V_{\text{BWCTL}}), \ unless \ otherwise \ noted.$

Table 1.

| Parameter                                                | Min  | Тур                             | Max | Unit   | Test Conditions/Comments                                                          |

|----------------------------------------------------------|------|---------------------------------|-----|--------|-----------------------------------------------------------------------------------|

| FREQUENCY RANGE                                          |      |                                 |     |        |                                                                                   |

| Center Frequency (fcenter)                               | 1.95 |                                 | 3.4 | GHz    |                                                                                   |

| BANDWIDTH                                                |      |                                 |     |        |                                                                                   |

| 3 dB                                                     |      | 9                               |     | %      |                                                                                   |

| 3 dB Bandwidth Control (V <sub>BWCTL</sub> )             |      | ±3                              |     | %      | Percent change of bandwidth over fcenter as voltage changes                       |

| REJECTION                                                |      |                                 |     |        |                                                                                   |

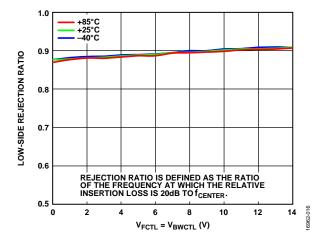

| Low-Side                                                 |      | $0.89 \times f_{CENTER}$        |     |        | ≥20 dB                                                                            |

| High-Side                                                |      | $1.13 \times f_{\text{CENTER}}$ |     |        | ≥20 dB                                                                            |

| Re-entry                                                 |      | $6.40 \times f_{\text{CENTER}}$ |     |        | ≤30 dB                                                                            |

| LOSS                                                     |      |                                 |     |        |                                                                                   |

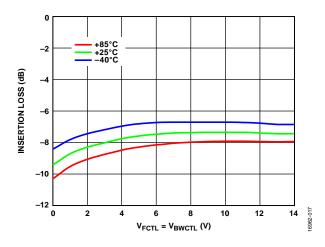

| Insertion Loss                                           |      | 8                               |     | dB     |                                                                                   |

| Return Loss                                              |      | 10                              |     | dB     |                                                                                   |

| DYNAMIC PERFORMANCE                                      |      |                                 |     |        |                                                                                   |

| Max Input Power for Linear<br>Operation                  |      |                                 | 10  | dBm    |                                                                                   |

| Input Third-Order Intercept<br>(Input IP3)               |      | 32                              |     | dBm    | Input power $(P_{IN}) = 20$ dBm, two tone                                         |

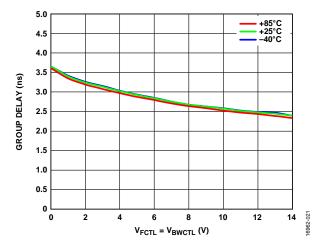

| Group Delay                                              |      | 3                               |     | ns     |                                                                                   |

| Phase Sensitivity                                        |      | 3.6                             |     | Rad/V  |                                                                                   |

| Amplitude Settling                                       |      | 200                             |     | ns     | Time to settle to minimum insertion loss, within ≤0.5 dB of static insertion loss |

| Drift Rate                                               |      | 0.6                             |     | MHz/°C |                                                                                   |

| RESIDUAL PHASE NOISE                                     |      |                                 |     |        |                                                                                   |

| 1 MHz Offset                                             |      | -165                            |     | dBc/Hz |                                                                                   |

| TUNING                                                   |      |                                 |     |        |                                                                                   |

| Voltages (V <sub>FCTL</sub> , V <sub>BWCTL</sub> )       | 0    |                                 | 14  | V      | Each pin can be driven independently                                              |

| Current                                                  |      |                                 |     |        |                                                                                   |

| Center Frequency Control<br>Current (I <sub>FCTL</sub> ) |      |                                 | ±1  | μΑ     | Rated current for each pin                                                        |

| Bandwidth Control Current<br>(IBWCTL)                    |      |                                 | ±1  | μΑ     | Rated current for each pin                                                        |

## **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                                                                                                   | Rating          |  |

|-------------------------------------------------------------------------------------------------------------|-----------------|--|

| Tuning                                                                                                      |                 |  |

| Voltage (V <sub>FCTL</sub> , V <sub>BWCTL</sub> )                                                           | −0.5 V to +15 V |  |

| Current (I <sub>FCTL</sub> , I <sub>BWCTL</sub> )                                                           | ±1 mA           |  |

| RF Input Power                                                                                              | 27 dBm          |  |

| Temperature                                                                                                 |                 |  |

| Operating Temperature Range                                                                                 | -40°C to +85°C  |  |

| Storage Temperature Range                                                                                   | −65°C to +150°C |  |

| Junction Temperature for 1 Million Mean<br>Time to Failure (MTTF)                                           | 175°C           |  |

| Nominal Junction Temperature<br>(Electronic Pad Temperature, $T_{EPAD} = +85^{\circ}C$ , $P_{IN} = 10$ dBm) | 90°C            |  |

| Electrostatic Discharge (ESD) Rating                                                                        |                 |  |

| Human Body Model (HBM)                                                                                      | 1500 V          |  |

| Field Induced Charge Device Model (FICDM)                                                                   | 1250 V          |  |

| Moisture Sensitivity Level (MSL) Rating                                                                     | MSL3            |  |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

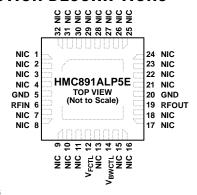

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

#### NOTES

- I. NIC = NOT INTERNALLY CONNECTED. ALL DATA SHOWN HEREIN WAS MEASURED WITH THESE PINS CONNECTED TO RF/DC GROUND EXTERNALLY.

2. EXPOSED PAD. THE PACKAGE BOTTOM HAS AN EXPOSED PAD THAT MUST BE CONNECTED TO RF/DC GROUND.

Figure 2. Pin Configuration

**Table 3. Pin Function Descriptions**

| Pin No.                                    | Mnemonic          | Description                                                                                                                                                 |

|--------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 to 4, 7 to 11, 13, 15 to<br>18, 21 to 32 | NIC               | Not Internally Connected. These pins are not connected internally. All data shown herein was measured with these pins externally connected to RF/dc ground. |

| 5, 20                                      | GND               | Ground. Connect these pins to RF/dc ground.                                                                                                                 |

| 6                                          | RFIN              | Radio Frequency Input. This pin is dc-coupled and matched to $50 \Omega$ . Do not apply an external voltage to this pin.                                    |

| 12                                         | V <sub>FCTL</sub> | Center Frequency Control Voltage. This pin controls the fcenter of the device.                                                                              |

| 14                                         | $V_{BWCTL}$       | Bandwidth Control Voltage. This pin controls the bandwidth of the device.                                                                                   |

| 19                                         | RFOUT             | Radio Frequency Output. This pin is dc-coupled and matched at 50 $\Omega$ . Do not apply an external voltage to this pin.                                   |

|                                            | EPAD              | Exposed Pad. The package bottom has an exposed metal pad that must be connected to RF/dc ground.                                                            |

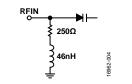

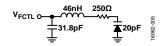

#### **INTERFACE SCHEMATICS**

Figure 3. GND Interface Schematic

Figure 4. RFIN Interface Schematic

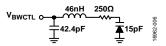

Figure 5. V<sub>FCTL</sub> Interface Schematic

Figure 6. V<sub>BWCTL</sub> Interface Schematic

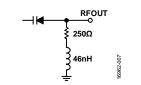

Figure 7. RFOUT Interface Schematic

## TYPICAL PERFORMANCE CHARACTERISTICS

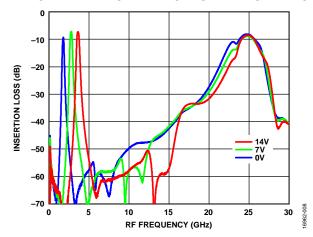

Figure 8. Insertion Loss vs. Broadband RF Frequency at Various  $V_{\text{FCTL}} = V_{\text{BWCTL}}$ Voltages

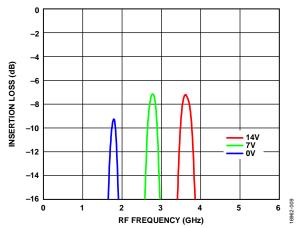

Figure 9. Insertion Loss vs. RF Frequency at Various  $V_{FCTL} = V_{BWCTL}$  Voltages

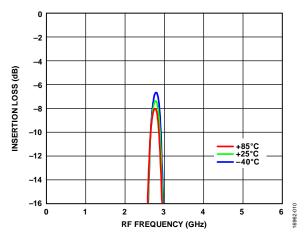

Figure 10. Insertion Loss vs. RF Frequency at Various Temperatures,  $V_{FCTL} = V_{BWCTL} = 7 V$

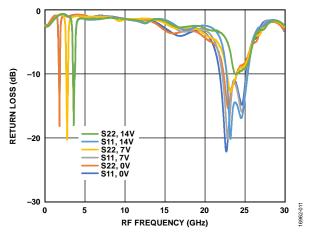

Figure 11. Return Loss vs. Broadband RF Frequency at Various  $V_{FCTL} = V_{BWCTL}$ Voltages

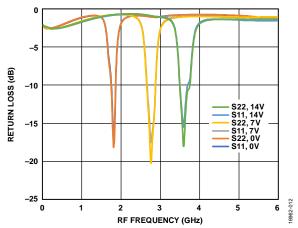

Figure 12. Return Loss vs. RF Frequency at Various  $V_{FCTL} = V_{BWCTL}$  Voltages

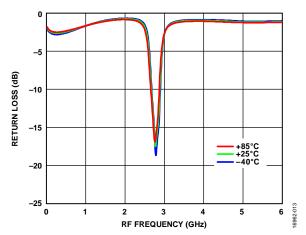

Figure 13. Return Loss vs. RF Frequency at Various Temperatures,  $V_{FCTL} = V_{BWCTL} = 7 V$

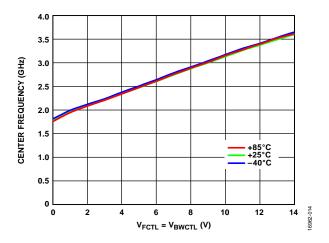

Figure 14. Center Frequency ( $f_{CENTER}$ ) vs.  $V_{FCTL} = V_{BWCTL}$  at Various Temperatures

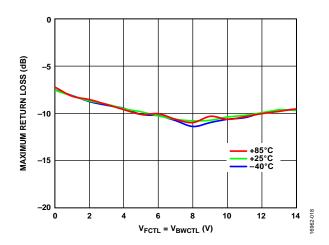

Figure 15. 3 dB Bandwidth vs.  $V_{FCTL} = V_{BWCTL}$  at Various Temperatures

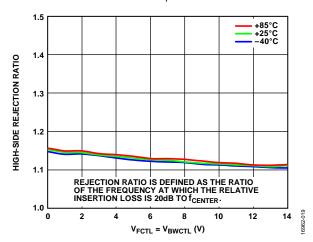

Figure 16. Low-Side Rejection Ratio vs.  $V_{FCTL} = V_{BWCTL}$ at Various Temperatures

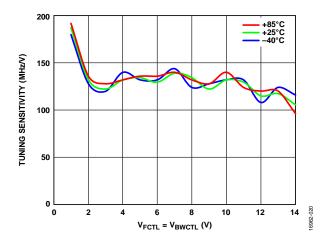

Figure 17. Insertion Loss vs.  $V_{FCTL} = V_{BWCTL}$  at Various Temperatures

Figure 18. Maximum Return Loss in a 2 dB Bandwidth vs.  $V_{FCTL} = V_{BWCTL}$  at Various Temperatures

Figure 19. High-Side Rejection Ratio vs.  $V_{FCTL} = V_{BWCTL}$  at Various Temperatures

Figure 20. Tuning Sensitivity vs.  $V_{FCTL} = V_{BWCTL}$  at Various Temperatures

Figure 21. Group Delay vs.  $V_{FCTL} = V_{BWCTL}$  at Various Temperature

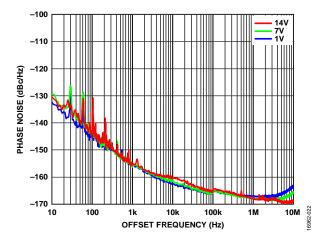

Figure 22. Residual Phase Noise vs. Offset Frequency at  $Various\ V_{FCTL} = V_{BWCTL}\ Voltages$

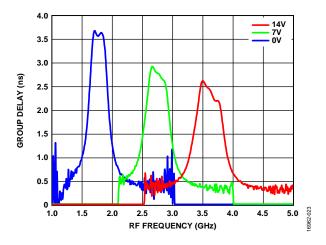

Figure 23. Group Delay vs. RF Frequency at Various  $V_{FCTL} = V_{BWCTL}$  Voltages

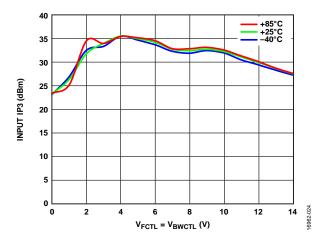

Figure 24. Input IP3 vs.  $V_{FCTL} = V_{BWCTL}$  at Various Temperatures, Input Power  $(P_{IN}) = 20 \text{ dBm}$

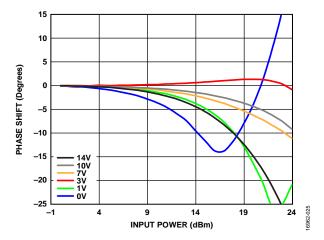

Figure 25. Phase Shift vs. Input Power ( $P_{IN}$ ), at Various  $V_{FCTL} = V_{BWCTL}$  Voltages

## THEORY OF OPERATION

The HMC891ALP5E is a MMIC band-pass filter that features a user-selectable pass band frequency. Varying the applied analog tuning voltage between 0 V and 14 V at V<sub>FCTL</sub> varies the f<sub>CENTER</sub> frequency between 1.95 GHz and 3.4 GHz. The bandwidth of the filter is adjustable by using the V<sub>BWCTL</sub> control voltage, which can vary from 0 V to 14 V. Typical operation is to tie the V<sub>FCTL</sub> and V<sub>BWCTL</sub> control voltages together.

## APPLICATIONS INFORMATION TYPICAL APPLICATION CIRCUIT

Figure 26 shows the typical application circuit for the HMC891ALP5E. The RFIN and RFOUT pins are dc-coupled and require external, 100 pF series capacitors (C1 and C2).

Figure 26. Typical Application Circuit

#### **EVALUATION PRINTED CIRCUIT BOARD (PCB)**

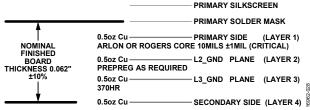

All RF traces are routed on Layer 1 (primary side) and the remaining three layers are ground planes that provide a solid ground for RF transmission lines, as shown in Figure 27. The top dielectric material is Rogers 4350, which offers low loss performance. The prepreg material in Layer 2 attaches the Isola 370HR core layer with copper traces layers above and below the core layer. The prepreg material and the Isola 370HR core layer are used to achieve the required board finish thickness.

Figure 27. Cross Sectional View of the EV1HMC891ALP5 PCB Layers

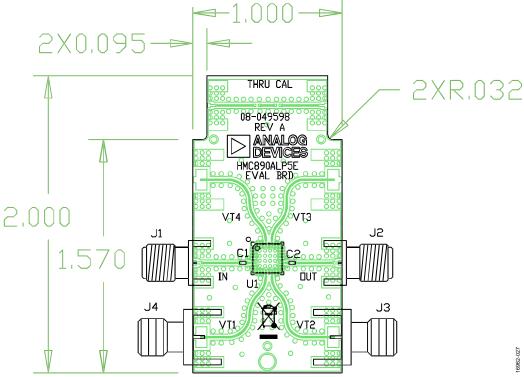

The circuit board in this application uses RF circuit design techniques. Signal lines must have an impedance of 50  $\Omega$ , and the package ground leads and exposed pad must be connected directly to the ground plane (see Figure 27). Use a sufficient number of via holes to connect the top and bottom ground planes. The evaluation circuit board shown in Figure 28 is available from Analog Devices, Inc. upon request.

Table 4. Bill of Materials for the EV1HMC891ALP5

| Item   | Description                                            |

|--------|--------------------------------------------------------|

| J1, J2 | PCB mount, Subminiature Version A (SMA) connector, SRI |

| J3, J4 | PCB mount SMA connector, Johnson                       |

| C1, C2 | Capacitor, 100 pF, 0402                                |

| U1     | HMC891ALP5E                                            |

| PCB    | 08-049598 <sup>2</sup> evaluation PCB                  |

- <sup>1</sup> Circuit board material is Arlon 25FR or Rogers 25FR.

- <sup>2</sup> 08-049598 is the raw, bare PCB identifier. Reference the EV1HMC891ALP5 when ordering the complete evaluation PCB.

Figure 28. Evaluation PCB, Top Layer Outline Dimensions

## **OUTLINE DIMENSIONS**

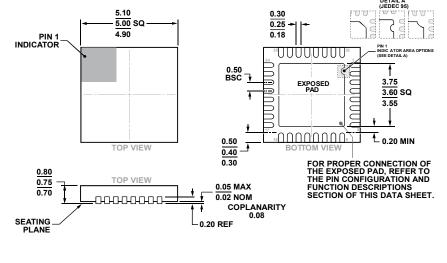

COMPLIANT TO JEDEC STANDARDS MO-220-WHHD-5

Figure 29. 32-Lead Lead Frame Chip Scale Package [LFCSP] 5 mm × 5 mm Body and 0.75 mm Package Height (CP-32-12) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                           | Package Option |

|--------------------|-------------------|-----------------------------------------------|----------------|

| HMC891ALP5E        | −40°C to +85°C    | 32-Lead Lead Frame Chip Scale Package [LFCSP] | CP-32-12       |

| HMC891ALP5ETR      | −40°C to +85°C    | 32-Lead Lead Frame Chip Scale Package [LFCSP] | CP-32-12       |

| EV1HMC891ALP5      |                   | Evaluation PCB                                |                |

<sup>&</sup>lt;sup>1</sup> All models are RoHS-Compliant Parts.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Active Filter Development Tools category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below:

MAXFILTERBRD+ DC1418A-A DC962A-B DC962A-E DC962A-A DC338B-B 131200-HMC900LP5E EKIT01-HMC1023LP5

EVAL01-HMC1044LP3E AFS1410-EVAL AFS2016-EVAL ADMV8432-EVALZ DC048A DC1251A-B DC1418A-B DC1418A-C

DC1418A-D DC962A-D EV1HMC881ALP5 EV1HMC882ALP5 EV1HMC891ALP5 EVAL-FW-HPMFB2 EVAL-FW-LPMFB2 3-109

440 3-111-353 EVAL-FW-BPDF2 EVAL-FW-HPMFB1 EVAL-FW-HPSK2 DC1251A-A 3-115-037 TPS7A3501EVM-547