# Quad, Current-Output, Serial-Input 16-/14-Bit DACs

### **Data Sheet**

### **FEATURES**

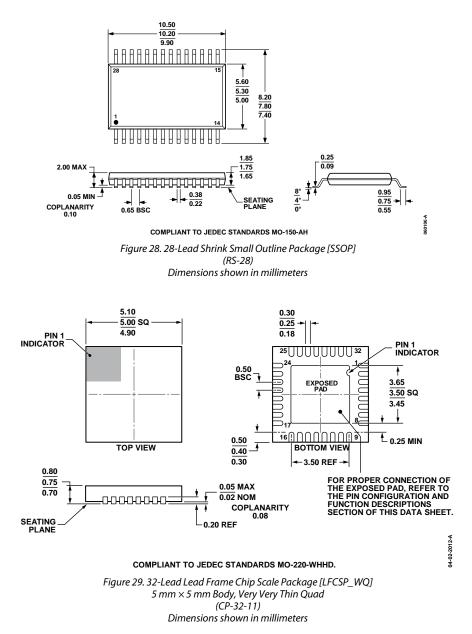

AD5544: 16-bit resolution INL of ±1 LSB (B Grade) AD5554: 14-bit resolution INL of ±0.5 LSB (B Grade) 2 mA full-scale current  $\pm$  20%, with V<sub>REF</sub> =  $\pm$ 10 V 0.9 µs settling time to ±0.1% 12 MHz multiplying bandwidth Midscale glitch of -1 nV-sec Midscale or zero-scale reset 4 separate, 4-quadrant multiplying reference inputs SPI-compatible, 3-wire interface **Double-buffered registers enable** Simultaneous multichannel change Internal power-on reset Temperature range: -40°C to +125°C Compact 28-lead SSOP and 32-lead LFCSP

#### **APPLICATIONS**

Rev. H

**Automatic test equipment** Instrumentation **Digitally controlled calibration**

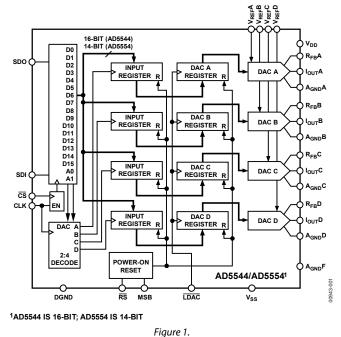

### **GENERAL DESCRIPTION**

The AD5544/AD5554 quad, 16-/14-bit, current output, digitalto-analog converters (DACs) are designed to operate from a 2.7 V to 5.5 V supply range.

The applied external reference input voltage (V<sub>REF</sub>x) determines the full-scale output current. Integrated feedback resistors (R<sub>FB</sub>) provide temperature-tracking, full-scale voltage outputs when combined with an external I-to-V precision amplifier.

A double-buffered serial data interface offers high speed, 3-wire, SPI- and microcontroller-compatible inputs using serial data in (SDI), a chip select (CS), and clock (CLK) signals. In addition, a serial data out pin (SDO) allows for daisy-chaining when multiple packages are used. A common, level-sensitive, load DAC strobe (LDAC) input allows the simultaneous update of all DAC outputs from previously loaded input registers. Additionally, an internal power-on reset forces the output voltage to 0 at system turn-on. The MSB pin allows system reset assertion (RS) to force all registers to zero code when MSB = 0 or to half-scale code when MSB = 1.

# AD5544/AD5554

#### FUNCTIONAL BLOCK DIAGRAM

The AD5544 is packaged in the compact 28-lead SSOP and 32-lead LFCSP. The AD5554 is packaged in the compact 28-lead SSOP.

The EV-AD5544/45SDZ is available for evaluating DAC performance. For more information, see the UG-285 evaluation board user guide.

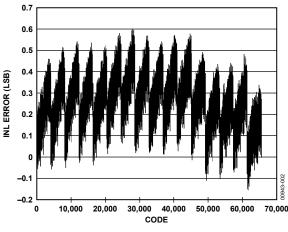

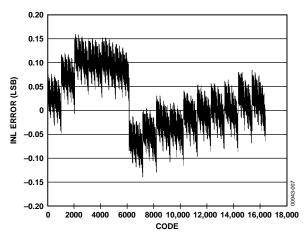

Figure 2. AD5544 INL vs. Code Plot ( $T_A = 25^{\circ}$ C)

**Document Feedback** Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2000–2015 Analog Devices, Inc. All rights reserved. **Technical Support** www.analog.com

# **TABLE OF CONTENTS**

| Features 1                                   |

|----------------------------------------------|

| Applications1                                |

| Functional Block Diagram 1                   |

| General Description                          |

| Revision History                             |

| Specifications                               |

| AD5544 Electrical Characteristics            |

| AD5554 Electrical Characteristics            |

| Timing Diagrams7                             |

| Absolute Maximum Ratings                     |

| ESD Caution                                  |

| Pin Configurations and Function Descriptions |

| Typical Performance Characteristics          |

| Theory of Operation14                        |

### **REVISION HISTORY**

| 9/15—Rev. G to Rev. H           |            |

|---------------------------------|------------|

| Changed NC to DNC               | Throughout |

| Changes to Figure 1             |            |

| Changes to Figure 6 and Table 4 | 9          |

### 5/13—Rev. F to Rev. G

| Changes to General Description Section              | 1  |

|-----------------------------------------------------|----|

| Deleted Evaluation Board for the AD5544 Section and |    |

| Figure 30 to Figure 35; Renumbered Sequentially     | 22 |

| Updated Outline Dimensions                          | 21 |

| Changes to Ordering Guide                           | 22 |

### 1/12—Rev. E to Rev. F

| Changes to Figure 1                            |

|------------------------------------------------|

| Added Figure 18; Renumbered Sequentially 11    |

| Changes to Evaluation Board Schematics Section |

### 6/11—Rev. D to Rev. E

| out  |

|------|

| 3    |

| 5    |

|      |

| 7    |

|      |

|      |

| . 19 |

| . 21 |

| . 17 |

| . 18 |

|      |

| Digital-to-Analog Converter (DAC) | 14 |

|-----------------------------------|----|

| Serial Data Interface             | 16 |

| Truth Tables                      | 17 |

| Power-On Reset                    |    |

| ESD Protection Circuits           |    |

| Power Supply Sequence             |    |

| Layout and Power Supply Bypassing | 19 |

| Grounding                         | 19 |

| Applications Information          |    |

| Reference Selection               |    |

| Amplifier Selection               |    |

| Outline Dimensions                | 22 |

| Ordering Guide                    |    |

|                                   |    |

### 9/09—Rev. C to Rev. D

| Changes to Features Section    | 1 |

|--------------------------------|---|

| Changes to Table 1             | 3 |

| Changes to Table 2             |   |

| Changes to Figure 12           |   |

| Changes to Figure 19           |   |

| Changes to Table 8 and Table 9 |   |

| Changes to Ordering Guide      |   |

|                                |   |

### 8/09—Rev. B to Rev. C

| Change to | Table 1 | .3 |

|-----------|---------|----|

| Change to | Table 2 | .4 |

#### 8/09—Rev. A to Rev. B

| Changes to Features Section                            | 1  |

|--------------------------------------------------------|----|

| Changes to Figure 2                                    | 1  |

| Changes to Table 1                                     | 3  |

| Changes to Table 2                                     | 4  |

| Moved Timing Diagram                                   | 5  |

| Added Figure 4; Renumbered Sequentially                | 5  |

| Change to Table 3                                      | 6  |

| Changes to Table 4                                     | 7  |

| Changes to Typical Performance Characteristics Section | 8  |

| Changes to Figure 19                                   | 10 |

| Moved Table 5, Table 6, and Table 7                    | 12 |

| Moved Truth Tables Section                             | 13 |

| Deleted Figure 27; Renumbered Sequentially             | 14 |

| Updated Outline Dimensions                             | 16 |

| Changes to Ordering Guide                              | 16 |

|                                                        |    |

### 12/04—Rev. 0 to Rev. A

| Updated Format                              | Universal |

|---------------------------------------------|-----------|

| Change to Electrical Characteristics Tables | 4         |

| Change to Pin Description Table             | 10        |

| Addition of Power Supply Sequence Section   | 19        |

| Addition of Layout and Power Supply Bypassing Section | 19 |

|-------------------------------------------------------|----|

| Addition of Grounding Section                         | 19 |

| Addition of Figure 32                                 | 19 |

4/00—Revision 0: Initial Version

# **SPECIFICATIONS**

### **AD5544 ELECTRICAL CHARACTERISTICS**

$V_{DD} = 2.7 \text{ V}$  to 5.5 V,  $V_{SS} = 0 \text{ V}$ ,  $I_{OUT}x = virtual \text{ GND}$ ,  $A_{GND}x = 0 \text{ V}$ ,  $V_{REF}A = V_{REF}B = V_{REF}C = V_{REF}D = 10 \text{ V}$ ,  $T_A = \text{full operating temperature range of } -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ , unless otherwise noted.

| Table 1 | ι. |

|---------|----|

|---------|----|

| Parameter                                                     | Symbol                | Test Condition/Comments                                                                             | Min  | Тур   | Мах  | Unit     |

|---------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------|------|-------|------|----------|

| STATIC PERFORMANCE <sup>1</sup>                               |                       |                                                                                                     |      |       |      |          |

| Resolution                                                    | N                     | $1 \text{ LSB} = V_{\text{REF}} x / 2^{16} = 153 \mu \text{V}$ when $V_{\text{REF}} = 10 \text{ V}$ |      |       | 16   | Bits     |

| Relative Accuracy                                             | INL                   | AD5544BRSZ                                                                                          |      |       | ±1   | LSB      |

|                                                               |                       | AD5544ARSZ                                                                                          |      |       | ±2   | LSB      |

|                                                               |                       | AD5544BCPZ                                                                                          |      |       | ±1   | LSB      |

|                                                               |                       | AD5544ACPZ-1                                                                                        |      |       | ±4   | LSB      |

| Differential Nonlinearity                                     | DNL                   | AD5544BRSZ                                                                                          |      |       | ±1   | LSB      |

| ,                                                             |                       | AD5544ARSZ                                                                                          |      |       | ±1.5 | LSB      |

|                                                               |                       | AD5544BCPZ                                                                                          |      |       | ±1   | LSB      |

|                                                               |                       | AD5544ACPZ-1                                                                                        |      |       | ±1   | LSB      |

| Output Leakage Current                                        | I <sub>OUT</sub> x    | Data = $0x0000, T_A = 25^{\circ}C$                                                                  |      |       | 10   | nA       |

|                                                               | -001                  | Data = $0x0000, T_A = 85^{\circ}C$                                                                  |      |       | 20   | nA       |

| Full-Scale Gain Error                                         | G <sub>FSE</sub>      | Data = 0xFFFF                                                                                       |      | ±0.75 | ±3   | mV       |

| Full-Scale Tempco <sup>2</sup>                                | TCV <sub>FS</sub>     |                                                                                                     |      | 1     |      | ppm/°C   |

| Feedback Resistor                                             | R <sub>FB</sub> x     | $V_{DD} = 5 V$                                                                                      | 4    | 6     | 8    | kΩ       |

| REFERENCE INPUT                                               | FR                    |                                                                                                     |      | ~     | ~    |          |

| V <sub>REF</sub> x Range                                      | V <sub>REF</sub> x    |                                                                                                     | -15  |       | +15  | v        |

| Input Resistance                                              | R <sub>REF</sub> X    |                                                                                                     | 4    | 6     | 8    | kΩ       |

| Input Resistance Match                                        | R <sub>REF</sub> X    | Channel-to-channel                                                                                  | -    | 0.35  | 0    | %        |

| Input Capacitance <sup>2</sup>                                | C <sub>REF</sub> X    |                                                                                                     |      | 5     |      | pF       |

| ANALOG OUTPUT                                                 | CREFA                 |                                                                                                     |      | 5     |      | Pi       |

| Output Current                                                |                       | Data = 0xFFF                                                                                        | 1.25 |       | 2.5  | mA       |

| Output Capacitance <sup>2</sup>                               | l <sub>out</sub> x    | Code dependent                                                                                      | 1.25 | 35    | 2.5  | pF       |

| LOGIC INPUT AND OUTPUT                                        | C <sub>OUT</sub> x    |                                                                                                     |      | 55    |      | Pi       |

| Logic Input Low Voltage                                       | V                     |                                                                                                     |      |       | 0.8  | v        |

| Logic Input High Voltage                                      | V <sub>IL</sub>       |                                                                                                     | 2.4  |       | 0.0  | v        |

| Input Leakage Current                                         | V <sub>IH</sub>       |                                                                                                     | 2.4  |       | 1    | -        |

| Input Capacitance <sup>2</sup>                                |                       |                                                                                                     |      |       | 10   | μA<br>pE |

| Logic Output Low Voltage                                      | C <sub>IL</sub>       | 1 - 16 m                                                                                            |      |       | 0.4  | pF<br>V  |

|                                                               | V <sub>oL</sub>       | $I_{OL} = 1.6 \text{ mA}$                                                                           | 4    |       | 0.4  | v        |

| Logic Output High Voltage<br>INTERFACE TIMING <sup>2, 3</sup> | V <sub>OH</sub>       | I <sub>OH</sub> = 100 μA                                                                            | 4    |       |      | v        |

|                                                               |                       |                                                                                                     | 25   |       |      |          |

| Clock Width High                                              | t <sub>CH</sub>       |                                                                                                     | 25   |       |      | ns       |

| Clock Width Low                                               | t <sub>CL</sub>       |                                                                                                     | 25   |       |      | ns       |

| CS to Clock Setup                                             | t <sub>css</sub>      |                                                                                                     | 0    |       |      | ns       |

| Clock to CS Hold                                              | t <sub>csh</sub>      |                                                                                                     | 25   |       |      | ns       |

| Clock to SDO Propagation<br>Delay                             | t <sub>PD</sub>       |                                                                                                     | 2    |       | 20   | ns       |

| Load DAC Pulse Width                                          | $t_{LDAC}$            |                                                                                                     | 25   |       |      | ns       |

| Data Setup                                                    | t <sub>DS</sub>       |                                                                                                     | 20   |       |      | ns       |

| Data Hold                                                     | t <sub>DH</sub>       |                                                                                                     | 20   |       |      | ns       |

| Load Setup                                                    | t <sub>LDS</sub>      |                                                                                                     | 5    |       |      | ns       |

| Load Hold                                                     | t <sub>LDH</sub>      |                                                                                                     | 25   |       |      | ns       |

| SUPPLY CHARACTERISTICS                                        |                       |                                                                                                     |      |       |      |          |

| Power Supply Range                                            | V <sub>DD RANGE</sub> |                                                                                                     | 2.7  |       | 5.5  | V        |

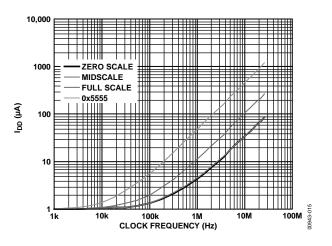

| Positive Supply Current                                       | I <sub>DD</sub>       | Logic inputs = $0 V$                                                                                |      |       | 5    | μΑ       |

| Negative Supply Current                                       | I <sub>ss</sub>       | Logic inputs = $0 V$ , $V_{ss} = -5 V$                                                              |      | 0.001 | 9    | μA       |

### **Data Sheet**

# AD5544/AD5554

| Parameter                                         | Symbol                                | Test Condition/Comments                                                        | Min | Тур | Max   | Unit   |

|---------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------|-----|-----|-------|--------|

| Power Dissipation                                 | P <sub>DISS</sub>                     | Logic inputs = 0 V                                                             |     |     | 1.25  | mW     |

| Power Supply Sensitivity                          | PSS                                   | $\Delta V_{DD} = \pm 5\%$                                                      |     |     | 0.006 | %/%    |

| AC CHARACTERISTICS <sup>4</sup>                   |                                       |                                                                                |     |     |       |        |

| Output Voltage Settling Time                      | ts                                    | To $\pm 0.1\%$ of full scale, data = 0x0000 to 0xFFFF to 0x0000                |     | 0.9 |       | μs     |

| Reference Multiplying BW – 3 dB<br>Bandwidth (BW) |                                       | $V_{REF}x = 5 V p-p$ , data = 0xFFFF, $C_{FB} = 2.0 pF$ ,                      |     | 12  |       | MHz    |

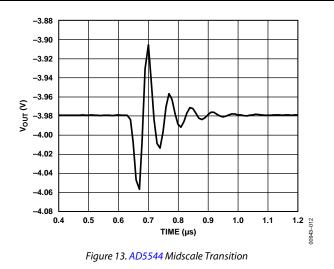

| DAC Glitch Impulse                                | Q                                     | V <sub>REF</sub> x = 8 V, data = 0x0000 to 0x8000 to 0x0000                    |     | -1  |       | nV-sec |

| Feedthrough Error                                 | V <sub>OUT</sub> x/V <sub>REF</sub> x | Data = 0x0000, V <sub>REF</sub> x = 100 mV rms, f = 100 kHz                    |     | -65 |       | dB     |

| Crosstalk Error                                   | V <sub>OUT</sub> A/V <sub>REF</sub> B | Data = 0x0000, $V_{REF}B = 100 \text{ mV rms}$ , adjacent channel, f = 100 kHz |     | -90 |       | dB     |

| Digital Feedthrough                               | Q                                     | $\overline{CS} = 1$ , $f_{CLK} = 1$ MHz                                        |     | 0.6 |       | nV-sec |

| Total Harmonic Distortion                         | THD                                   | V <sub>REF</sub> x = 5 V p-p, data = 0xFFFF, f = 1 kHz                         |     | -98 |       | dB     |

| Output Spot Noise Voltage                         | e <sub>N</sub>                        | f = 1  kHz, BW = 1  Hz                                                         |     | 7   |       | nV/√Hz |

<sup>1</sup> All static performance tests (except  $I_{OUT}x$ ) are performed in a closed-loop system using an external precision OP177 l-to-V converter amplifier. The AD5544 R<sub>FB</sub> terminal is tied to the amplifier output. Typical values represent average readings measured at 25°C. <sup>2</sup> These parameters are guaranteed by design and not subject to production testing. <sup>3</sup> All input control signals are specified with  $t_R = t_F = 2.5$  ns (10% to 90% of 3 V) and timed from a voltage level of 1.5 V. <sup>4</sup> All ac characteristic tests are performed in a closed-loop system using an AD8038 l-to-V converter amplifier.

### **AD5554 ELECTRICAL CHARACTERISTICS**

$V_{DD} = 2.7 \text{ V}$  to 5.5 V,  $V_{SS} = 0 \text{ V}$ ,  $I_{OUT}x = virtual GND$ ,  $A_{GND}x = 0 \text{ V}$ ,  $V_{REF}A = V_{REF}B = V_{REF}C = V_{REF}D = 10 \text{ V}$ ,  $T_A =$ full operating temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise noted.

#### Table 2.

| Parameter                        | Symbol             | Test Condition/Comments                                                                             | Min  | Тур | Max  | Unit   |

|----------------------------------|--------------------|-----------------------------------------------------------------------------------------------------|------|-----|------|--------|

| STATIC PERFORMANCE <sup>1</sup>  |                    |                                                                                                     |      |     |      |        |

| Resolution                       | N                  | $1 \text{ LSB} = V_{\text{REF}} x/2^{14} = 610 \mu \text{V}$ when $V_{\text{REF}} x = 10 \text{ V}$ |      |     | 14   | Bits   |

| Relative Accuracy                | INL                |                                                                                                     |      |     | ±0.5 | LSB    |

| Differential Nonlinearity        | DNL                |                                                                                                     |      |     | ±1   | LSB    |

| Output Leakage Current           | I <sub>OUT</sub> x | $Data = 0x0000, T_A = 25^{\circ}C$                                                                  |      |     | 10   | nA     |

|                                  |                    | $Data = 0x0000, T_A = 85^{\circ}C$                                                                  |      |     | 20   | nA     |

| Full-Scale Gain Error            | G <sub>FSE</sub>   | Data = 0x3FFF                                                                                       |      | ±2  | ±10  | mV     |

| Full-Scale Tempco <sup>2</sup>   | TCV <sub>FS</sub>  |                                                                                                     |      | 1   |      | ppm/°C |

| Feedback Resistor                | R <sub>FB</sub> x  | $V_{DD} = 5 V$                                                                                      | 4    | 6   | 8    | kΩ     |

| REFERENCE INPUT                  |                    |                                                                                                     |      |     |      |        |

| V <sub>REF</sub> x Range         | V <sub>REF</sub> x |                                                                                                     | -15  |     | +15  | V      |

| Input Resistance                 | R <sub>REF</sub> x |                                                                                                     | 4    | 6   | 8    | kΩ     |

| Input Resistance Match           | R <sub>REF</sub> x | Channel-to-channel                                                                                  |      | 1   |      | %      |

| Input Capacitance <sup>2</sup>   | C <sub>REF</sub> X |                                                                                                     |      | 5   |      | pF     |

| ANALOG OUTPUT                    |                    |                                                                                                     |      |     |      |        |

| Output Current                   | I <sub>out</sub> x | Data = 0x3FFF                                                                                       | 1.25 |     | 2.5  | mA     |

| Output Capacitance <sup>2</sup>  | C <sub>OUT</sub> x | Code dependent                                                                                      |      | 80  |      | pF     |

| LOGIC INPUT AND OUTPUT           |                    |                                                                                                     |      |     |      |        |

| Logic Input Low Voltage          | V <sub>IL</sub>    |                                                                                                     |      |     | 0.8  | V      |

| Logic Input High Voltage         | V <sub>IH</sub>    |                                                                                                     | 2.4  |     |      | V      |

| Input Leakage Current            | I                  |                                                                                                     |      |     | 1    | μA     |

| Input Capacitance <sup>2</sup>   | C <sub>IL</sub>    |                                                                                                     |      |     | 10   | pF     |

| Logic Output Low Voltage         | V <sub>OL</sub>    | $I_{OL} = 1.6 \text{ mA}$                                                                           |      |     | 0.4  | V      |

| Logic Output High Voltage        | V <sub>OH</sub>    | I <sub>OH</sub> = 100 μA                                                                            | 4    |     |      | V      |

| INTERFACE TIMING <sup>2, 3</sup> |                    |                                                                                                     |      |     |      |        |

| Clock Width High                 | t <sub>cH</sub>    |                                                                                                     | 25   |     |      | ns     |

| Clock Width Low                  | t <sub>CL</sub>    |                                                                                                     | 25   |     |      | ns     |

| CS to Clock Setup                | t <sub>CSS</sub>   |                                                                                                     | 0    |     |      | ns     |

| Parameter                               | Symbol                                | Test Condition/Comments                                               | Min | Тур   | Max   | Unit   |

|-----------------------------------------|---------------------------------------|-----------------------------------------------------------------------|-----|-------|-------|--------|

| Clock to CS Hold                        | t <sub>csh</sub>                      |                                                                       | 25  |       |       | ns     |

| Clock to SDO Propagation<br>Delay       | t <sub>PD</sub>                       |                                                                       | 2   |       | 20    | ns     |

| Load DAC Pulse Width                    | t <sub>LDAC</sub>                     |                                                                       | 25  |       |       | ns     |

| Data Setup                              | t <sub>DS</sub>                       |                                                                       | 20  |       |       | ns     |

| Data Hold                               | t <sub>DH</sub>                       |                                                                       | 20  |       |       | ns     |

| Load Setup                              | t <sub>LDS</sub>                      |                                                                       | 5   |       |       | ns     |

| Load Hold                               | t <sub>LDH</sub>                      |                                                                       | 25  |       |       | ns     |

| SUPPLY CHARACTERISTICS                  |                                       |                                                                       |     |       |       |        |

| Power Supply Range                      | V <sub>DD RANGE</sub>                 |                                                                       | 2.7 |       | 5.5   | V      |

| Positive Supply Current                 | I <sub>DD</sub>                       | Logic inputs = 0 V                                                    |     |       | 5     | μΑ     |

| Negative Supply Current                 | I <sub>ss</sub>                       | Logic inputs = 0 V, $V_{ss} = -5 V$                                   |     | 0.001 | 9     | μΑ     |

| Power Dissipation                       | P <sub>DISS</sub>                     | Logic inputs = 0 V                                                    |     |       | 1.25  | mW     |

| Power Supply Sensitivity                | PSS                                   | $\Delta V_{DD} = \pm 5\%$                                             |     |       | 0.006 | %/%    |

| AC CHARACTERISTICS <sup>4</sup>         |                                       |                                                                       |     |       |       |        |

| Output Voltage Settling Time            | t <sub>s</sub>                        | To $\pm 0.1\%$ of full scale, data = 0x0000 to 0x3FFF to 0x0000       |     | 0.9   |       | μs     |

| Reference Multiplying<br>Bandwidth (BW) | BW – 3 dB                             | $V_{REF}x = 5 V p-p, data = 0xFFFF, C_{FB} = 2.0 pF$                  |     | 12    |       | MHz    |

| DAC Glitch Impulse                      | Q                                     | V <sub>REF</sub> x = 8 V, data = 0x0000 to 0x2000 to 0x0000           |     | -1    |       | nV-sec |

| Feedthrough Error                       | $V_{OUT} x / V_{REF} x$               | Data = 0x0000, V <sub>REF</sub> x = 100 mV rms, f = 100 kHz           |     | -65   |       | dB     |

| Crosstalk Error                         | V <sub>OUT</sub> A/V <sub>REF</sub> B | Data = 0x0000, $V_{REF}B$ = 100 mV rms, adjacent channel, f = 100 kHz |     | -90   |       | dB     |

| Digital Feedthrough                     | Q                                     | $\overline{CS} = 1$ , $f_{CLK} = 1$ MHz                               |     | 0.6   |       | nV-sec |

| Total Harmonic Distortion               | THD                                   | V <sub>REF</sub> x = 5 V p-p, data = 0x3FFF, f = 1 kHz                |     | -98   |       | dB     |

| Output Spot Noise Voltage               | e <sub>N</sub>                        | f = 1  kHz, BW = 1  Hz                                                |     | 7     |       | nV/√Hz |

<sup>1</sup> All static performance tests (except  $I_{OUT}$ ) are performed in a closed-loop system using an external precision OP177 I-to-V converter amplifier. The AD5554 R<sub>FB</sub> terminal is tied to the amplifier output. Typical values represent average readings measured at 25°C. <sup>2</sup> These parameters are guaranteed by design and not subject to production testing. <sup>3</sup> All input control signals are specified with  $t_R = t_F = 2.5$  ns (10% to 90% of 3 V) and timed from a voltage level of 1.5 V. <sup>4</sup> All ac characteristic tests are performed in a closed-loop system using an AD8038 I-to-V converter amplifier,.

### **TIMING DIAGRAMS**

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 3.

| 14010 5.                                          |                                 |

|---------------------------------------------------|---------------------------------|

| Parameter                                         | Rating                          |

| V <sub>DD</sub> to GND                            | –0.3 V, +8 V                    |

| V <sub>ss</sub> to GND                            | +0.3 V, -7 V                    |

| V <sub>REF</sub> x to GND                         | –18 V, +18 V                    |

| Logic Input and Output to GND                     | –0.3 V, +8 V                    |

| V(I <sub>OUT</sub> x) to GND                      | -0.3 V, V <sub>DD</sub> + 0.3 V |

| A <sub>GND</sub> x to DGND                        | –0.3 V, +0.3 V                  |

| Input Current to Any Pin Except Supplies          | ±50 mA                          |

| Package Power Dissipation                         | $(T_J max - T_A)/\theta_{JA}$   |

| Thermal Resistance                                | $\theta_{JA}$                   |

| 28-Lead SSOP                                      | 100°C/W                         |

| 32-Lead LFCSP                                     | 32.5°C/W                        |

| Maximum Junction Temperature (T <sub>J</sub> Max) | 150°C                           |

| Operating Temperature Range                       | -40°C to +125°C                 |

| Storage Temperature Range                         | –65°C to +150°C                 |

| Lead Temperature                                  |                                 |

| Vapor Phase, 60 Sec                               | 215°C                           |

| Infrared, 15 Sec                                  | 220°C                           |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

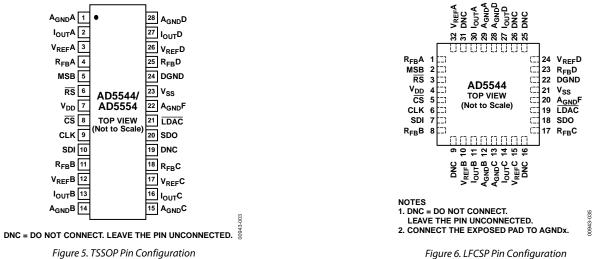

# **PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS**

#### Table 4. Pin Function Descriptions

| TSSOP   | LFCSP                |                    |                                                                                                                                                                                                                                       |

|---------|----------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No. | Pin No.              | Mnemonic           | Description                                                                                                                                                                                                                           |

| 1       | 29                   | A <sub>GND</sub> A | DAC A Analog Ground.                                                                                                                                                                                                                  |

| 2       | 30                   | I <sub>OUT</sub> A | DAC A Current Output.                                                                                                                                                                                                                 |

| 3       | 32                   | V <sub>REF</sub> A | DAC A Reference Voltage Input Terminal. Establishes DAC A full-scale output voltage. This pin can be tied to the V <sub>DD</sub> pin.                                                                                                 |

| 4       | 1                    | R <sub>FB</sub> A  | DAC A Feedback Resistor Connection. Establish the voltage output for DAC A by connecting this pin to an external amplifier output.                                                                                                    |

| 5       | 2                    | MSB                | MSB Bit. Set this pin during a reset pulse ( $\overline{RS}$ ) or at system power-on if tied to ground or V <sub>DD</sub> .                                                                                                           |

| 6       | 3                    | RS                 | Reset Pin, Active Low Input. Input registers and DAC registers are set to all 0s or half-scale code (0x8000 for the AD5544 and 0x2000 for the AD5554), determined by the voltage on the MSB pin. Register data = 0x0000 when MSB = 0. |

| 7       | 4                    | V <sub>DD</sub>    | Positive Power Supply Input. Specified range of operation: 5 V $\pm$ 10%.                                                                                                                                                             |

| 8       | 5                    | <u>cs</u>          | Chip Select, Active Low Input. Disables shift register loading when high. Transfers serial register data to the input register when CS/LDAC returns high. Does not affect LDAC operation.                                             |

| 9       | 6                    | CLK                | Clock Input. Positive edge clocks data into the shift register.                                                                                                                                                                       |

| 10      | 7                    | SDI                | Serial Data Input. Input data loads directly into the shift register.                                                                                                                                                                 |

| 11      | 8                    | R <sub>FB</sub> B  | DAC B Feedback Resistor Connection. Establish the voltage output for DAC B by connecting this pin to an external amplifier output.                                                                                                    |

| 12      | 10                   | V <sub>REF</sub> B | DAC B Reference Voltage Input Terminal. Establishes DAC B full-scale output voltage. This pin can be tied to the V <sub>DD</sub> pin.                                                                                                 |

| 13      | 11                   | I <sub>OUT</sub> B | DAC B Current Output.                                                                                                                                                                                                                 |

| 14      | 12                   | A <sub>GND</sub> B | DAC B Analog Ground.                                                                                                                                                                                                                  |

| 15      | 13                   | A <sub>GND</sub> C | DAC C Analog Ground.                                                                                                                                                                                                                  |

| 16      | 14                   | I <sub>out</sub> C | DAC C Current Output.                                                                                                                                                                                                                 |

| 17      | 15                   | V <sub>REF</sub> C | DAC C Reference Voltage Input Terminal. Establishes DAC C full-scale output voltage. This pin can be tied to the V <sub>DD</sub> pin.                                                                                                 |

| 18      | 17                   | R <sub>FB</sub> C  | DAC C Feedback Resistor Connection. Establish the voltage output for DAC C by connecting this pin to an external amplifier output.                                                                                                    |

| 19      | 9, 16, 25,<br>26, 31 | DNC                | Do Not Connect. Leave these pins unconnected.                                                                                                                                                                                         |

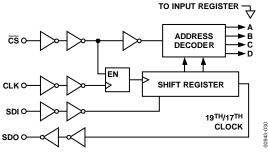

| 20      | 18                   | SDO                | Serial Data Output. Input data loads directly into the shift register. Data appears at SDO at 19 clock pulses for the AD5544 and 17 clock pulses for the AD5554 after input at the SDI pin.                                           |

| 21      | 19                   | LDAC               | Load DAC Register Strobe, Level Sensitive Active Low. Transfers all input register data to DAC registers. Asynchronous active low input. See Table 8 and Table 9 for operation.                                                       |

| TSSOP<br>Pin No. | LFCSP<br>Pin No. | Mnemonic           | Description                                                                                                                           |

|------------------|------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 22               | 20               | A <sub>GND</sub> F | High Current Analog Force Ground.                                                                                                     |

| 23               | 21               | V <sub>ss</sub>    | Negative Bias Power Supply Input. Specified range of operation: –5.5 V to +0.3 V.                                                     |

| 24               | 22               | DGND               | Digital Ground Pin.                                                                                                                   |

| 25               | 23               | R <sub>FB</sub> D  | DAC D Feedback Resistor Connection. Establish the voltage output for DAC D by connecting this pin to an external amplifier output.    |

| 26               | 24               | $V_{\text{REF}}D$  | DAC D Reference Voltage Input Terminal. Establishes DAC D full-scale output voltage. This pin can be tied to the V <sub>DD</sub> pin. |

| 27               | 27               | I <sub>out</sub> D | DAC D Current Output.                                                                                                                 |

| 28               | 28               | A <sub>GND</sub> D | DAC D Analog Ground.                                                                                                                  |

| N/A <sup>1</sup> |                  | EPAD               | Connect the exposed pad to AGNDx.                                                                                                     |

<sup>1</sup> N/A means not applicable.

# **TYPICAL PERFORMANCE CHARACTERISTICS**

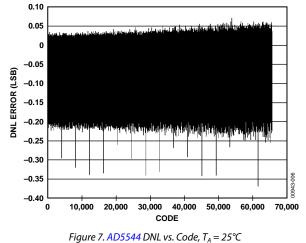

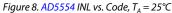

Figure 9. AD5554 DNL vs. Code,  $T_A = 25^{\circ}C$

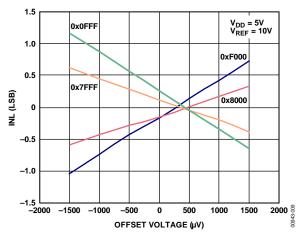

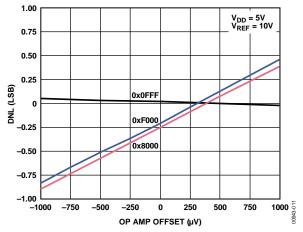

Figure 10. AD5544 Integral Nonlinearity Error vs. Op Amp Offset

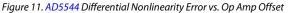

Figure 12. AD5544 Gain Error vs. Op Amp Offset

**Data Sheet**

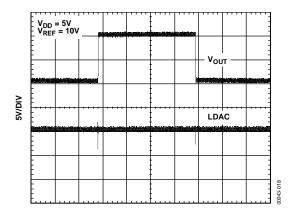

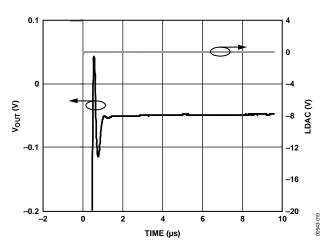

Figure 14. AD5544 Large Signal Settling Time

Figure 15. AD5544 Small Signal Settling Time

Figure 16. AD5544 Power Supply Current vs. Clock Frequency

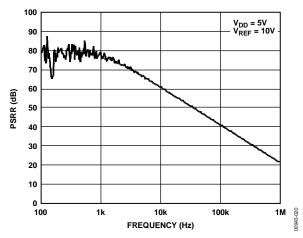

Figure 17. AD5544/AD5554 Power Supply Rejection vs. Frequency

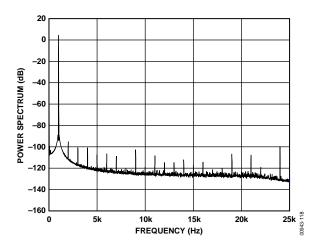

Figure 18. AD5544/AD5554 Analog THD

# **Data Sheet**

# AD5544/AD5554

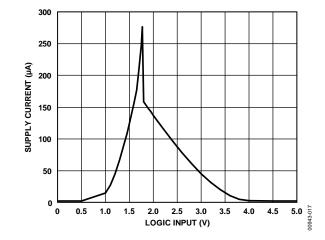

Figure 19. AD5544/AD5554 Power Supply Current vs. Logic Input Voltage

### THEORY OF OPERATION

The AD5544 and the AD5554 contain four 16-bit and 14-bit, current output DACs, respectively. Each DAC has its own independent multiplying reference input. Both the AD5544 and the AD5554 use a 3-wire, SPI-compatible serial data interface, with a configurable asynchronous  $\overline{\text{RS}}$  pin for half-scale (MSB = 1) or zero-scale (MSB = 0) preset. In addition, an  $\overline{\text{LDAC}}$  strobe enables 4-channel, simultaneous updates for hardware synchronized output voltage changes.

### **DIGITAL-TO-ANALOG CONVERTER (DAC)**

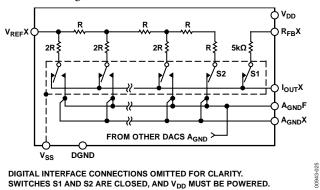

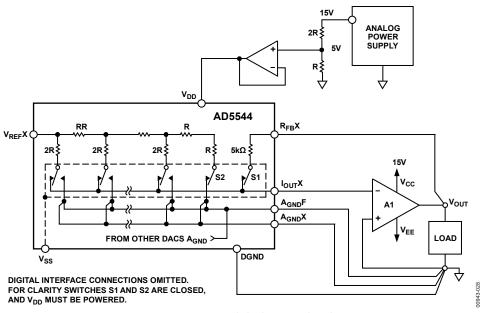

Each part contains four current-steering R-R ladder DACs. Figure 20 shows a typical equivalent DAC. Each DAC contains a matching feedback resistor for use with an external I-to-V converter amplifier. The  $R_{FB}x$  pin connects to the output of the external amplifier. The  $I_{OUT}x$  terminal connects to the inverting input of the external amplifier. The  $A_{GND}x$  pin should be Kelvinconnected to the load point, requiring full 16-bit accuracy. These DACs are designed to operate with both negative and positive reference voltage.

The  $V_{DD}$  power pin is used only by the logic to drive the DAC switches on and off. Note that a matching switch is used in series with the internal 5 k $\Omega$  feedback resistor. If users attempt to measure the value of  $R_{FB}$  power must be applied to  $V_{DD}$  to achieve continuity. An additional  $V_{SS}$  bias pin is used to guard the substrate during high temperature applications, minimizing zeroscale leakage currents that double every 10°C. The DAC output voltage is determined by  $V_{REF}$  and the digital data (D) in the following equations:

$$V_{OUT} = -V_{REF} \times \frac{D}{65,536}$$

(for the AD5544) (1)

$$V_{OUT} = -V_{REF} \times \frac{D}{16,384}$$

(for the AD5554) (2)

Note that the output polarity is opposite the  $V_{\mbox{\tiny REF}}$  polarity for dc reference voltages.

Figure 20. Typical Equivalent DAC Channel

These DACs are also designed to accommodate ac reference input signals. Both the AD5544 and the AD5554 accommodate input reference voltages in the range of -15 V to +15 V. The reference voltage inputs exhibit a constant nominal input resistance of 5 k $\Omega$  ± 30%. On the other hand, the  $I_{OUT}A$ ,  $I_{OUT}B$ ,  $I_{OUT}C$ , and  $I_{OUT}D$ DAC outputs are code dependent and produce various output resistances and capacitances. The choice of external amplifier should take into account the variation in impedance generated by the AD5544/AD5554 on the inverting input node of the amplifier. The feedback resistance, in parallel with the DAC ladder resistance, dominates output voltage noise. For multiplying mode applications, an external feedback compensation capacitor, C<sub>FB</sub>, may be needed to provide a critically damped output response for step changes in reference input voltages. Figure 21 shows the gain vs. frequency performance at various attenuation settings using a 23 pF external feedback capacitor connected across the IOUTX and REEX terminals for the AD5544 and the AD5554, respectively. To maintain good analog performance, power supply bypassing of 0.01 µF, in parallel with 1 µF, is recommended. Under these conditions, a clean power supply with low ripple voltage capability should be used. Switching power supplies is usually not suitable for this application due to the higher ripple voltage and PSS frequency-dependent characteristics. It is best to derive the supply of the AD5544/AD5554 from system analog supply voltages. Do not use the digital supply (see Figure 22).

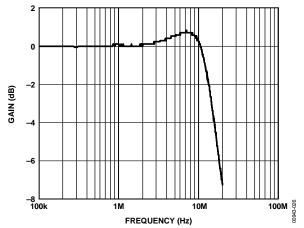

Figure 21. AD5554 Reference Multiplying Bandwidth vs. Code

Figure 22. Recommended Kelvin-Sensed Hookup

. ...

I SR

### **SERIAL DATA INTERFACE**

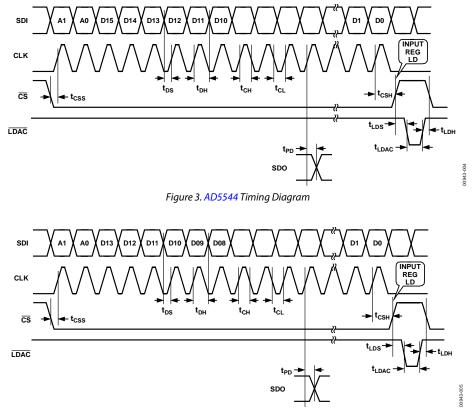

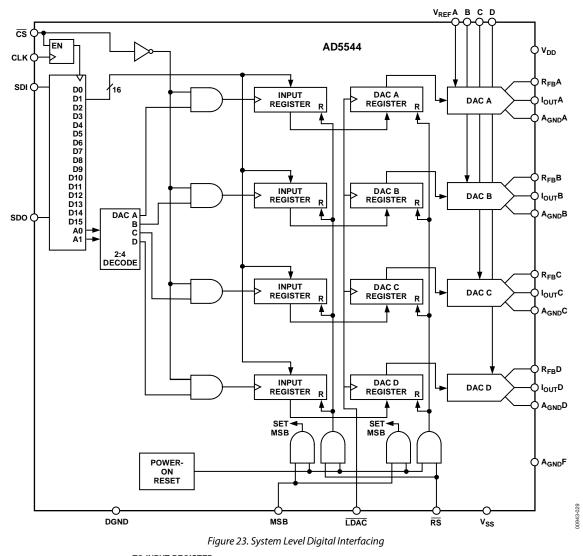

The AD5544/AD5554 use a 3-wire  $(\overline{CS}, SDI, CLK)$ , SPI-compatible serial data interface. Serial data of the AD5544/AD5554 is clocked into the serial input register in an 18-bit and 16-bit data-word format, respectively. The MSB bits are loaded first. Table 5 defines the 18 data-word bits for the AD5544, and Table 6 defines the 16 data-word bits for the AD5554. Data is placed on the SDI pin and clocked into the register on the positive clock edge of CLK, subject to the data setup and data hold time requirements specified in the interface timing specifications (see Table 1 and Table 2).

Data can be clocked in only while the  $\overline{CS}$  chip select pin is active low. For the AD5544, only the last 18 bits clocked into the serial register are interrogated when the  $\overline{CS}$  pin returns to the logic high state; extra data bits are ignored. For the AD5554, only the last 16 bits clocked into the serial register are interrogated when the  $\overline{CS}$  pin returns to the logic high state. Because most microcontrollers output serial data in 8-bit bytes, three right justified data bytes can be written to the AD5544. Keeping the  $\overline{CS}$  line low between the first, second, and third byte transfers results in a successful serial register update. Similarly, two right justified data bytes can be written to the AD5554. Keeping the  $\overline{\text{CS}}$  line low between the first and second byte transfer results in a successful serial register update.

When the data is properly aligned in the shift register, the positive edge of the  $\overline{CS}$  initiates the transfer of new data to the target DAC register, determined by the decoding of Address Bit A1 and Address Bit A0. For the AD5544, Table 5, Table 7, Table 8, and Figure 3 define the characteristics of the software serial interface.

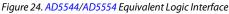

For the AD55554, Table 6, Table 7, Table 9, and Figure 4 define the characteristics of the software serial interface. Figure 23 and Figure 24 show the equivalent logic interface for the key digital control pins for the AD5544. The AD5554 has a similar configuration, except that it has 14 data bits. Two additional pins,  $\overline{\text{RS}}$  and MSB, provide hardware control over the preset function and DAC register loading. If these functions are not needed, the  $\overline{\text{RS}}$ pin can be tied to logic high. The asynchronous input  $\overline{\text{RS}}$  pin forces all input and the DAC registers to either the zero-code state (MSB = 0) or the half-scale state (MSB = 1).

### Table 5. AD5544 Serial Input Register Data Format (Data Is Loaded in the MSB-First Format)<sup>1</sup> MSB

| INI2R |     |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    | L2R |

|-------|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|-----|

| B17   | B16 | B15 | B14 | B13 | B12 | B11 | B10 | B9 | B8 | B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0  |

| A1    | A0  | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

<sup>1</sup> Only the last 18 bits of data clocked into the serial register (address + data) are inspected when the positive edge of the CS line returns to logic high. At this point, an internally generated load strobe transfers the serial register data contents (Bit D15 to Bit D0) to the decoded DAC input register address determined by Bit A1 and Bit A0. Any extra bits clocked into the AD5544 shift register are ignored; only the last 18 bits clocked in are used. If double-buffered data is not needed, the LDAC pin can be tied logic low to disable the DAC registers.

#### Table 6. AD5554 Serial Input Register Data Format (Data Is Loaded in the MSB-First Format)<sup>1</sup> MSB

|     |     |     |     |     |     |    |    |    |    |    | 200 |    |    |    |    |

|-----|-----|-----|-----|-----|-----|----|----|----|----|----|-----|----|----|----|----|

| B15 | B14 | B13 | B12 | B11 | B10 | B9 | B8 | B7 | B6 | B5 | B4  | B3 | B2 | B1 | B0 |

| A1  | A0  | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4  | D3 | D2 | D1 | D0 |

<sup>1</sup> Only the last 16 bits of data clocked into the serial register (address + data) are inspected when the positive edge of the CS line returns to logic high. At this point, an internally generated load strobe transfers the serial register data contents (Bit D13 to Bit D0) to the decoded DAC input register address determined by Bit A1 and Bit A0. Any extra bits clocked into the AD5554 shift register are ignored; only the last 16 bits clocked in are used. If double-buffered data is not needed, the LDAC pin can be tied logic low to disable the DAC registers.

#### Table 7. Address Decode

| A1 | A0 | DAC Decoded |

|----|----|-------------|

| 0  | 0  | DAC A       |

| 0  | 1  | DAC B       |

| 1  | 0  | DAC C       |

| 1  | 1  | DAC D       |

### **TRUTH TABLES**

| CS               | CLK              | LDAC             | RS   | MSB <sup>2</sup> | Serial Shift Register Function <sup>3</sup> | Input Register Function                                                   | DAC Register          |

|------------------|------------------|------------------|------|------------------|---------------------------------------------|---------------------------------------------------------------------------|-----------------------|

| High             | Х                | High             | High | Х                | No effect                                   | Latched                                                                   | Latched               |

| Low              | Low              | High             | High | Х                | No effect                                   | Latched                                                                   | Latched               |

| Low              | ↑ + <sup>3</sup> | High             | High | х                | Shift register data advanced one bit        | Latched                                                                   | Latched               |

| Low              | High             | High             | High | х                | No effect                                   | Latched                                                                   | Latched               |

| ↑ + <sup>3</sup> | Low              | High             | High | х                | No effect                                   | Selected DAC updated with<br>current shift register contents <sup>4</sup> | Latched               |

| High             | Х                | Low              | High | Х                | No effect                                   | Latched                                                                   | Transparent           |

| High             | Х                | High             | High | Х                | No effect                                   | Latched                                                                   | Latched               |

| High             | Х                | ↑ + <sup>3</sup> | High | х                | No effect                                   | Latched                                                                   | Latched               |

| High             | х                | High             | Low  | 0                | No effect                                   | Latched data = 0x0000                                                     | Latched data = 0x0000 |

| High             | х                | High             | Low  | High             | No effect                                   | Latched data = 0x8000                                                     | Latched data = 0x8000 |

### Table 8. AD5544<sup>1</sup> Control Logic Truth Table

<sup>1</sup> For the AD5544, data appears at the SDO pin 19 clock pulses after input at the SDI pin.

<sup>2</sup> X means don't care. <sup>3</sup> + is a positive logic transition. <sup>4</sup> At power-on, both the input register and the DAC register are loaded with all 0s.

### Table 9. AD5554<sup>1</sup> Control Logic Truth Table

| Table            | Table 9. AD5554 Control Logic Truth Table |      |      |                  |                                             |                                                                        |                       |  |  |  |  |  |

|------------------|-------------------------------------------|------|------|------------------|---------------------------------------------|------------------------------------------------------------------------|-----------------------|--|--|--|--|--|

| CS               | CLK                                       | LDAC | RS   | MSB <sup>2</sup> | Serial Shift Register Function <sup>3</sup> | Input Register Function <sup>3</sup>                                   | DAC Register          |  |  |  |  |  |

| High             | Х                                         | High | High | Х                | No effect                                   | Latched                                                                | Latched               |  |  |  |  |  |

| Low              | L                                         | High | High | Х                | No effect                                   | Latched                                                                | Latched               |  |  |  |  |  |

| Low              | ↑ + <sup>3</sup>                          | High | High | Х                | Shift register data advanced one bit        | Latched                                                                | Latched               |  |  |  |  |  |

| Low              | High                                      | High | High | Х                | No effect                                   | Latched                                                                | Latched               |  |  |  |  |  |

| ↑ + <sup>3</sup> | Low                                       | High | High | Х                | No effect                                   | Selected DAC updated with current shift register contents <sup>4</sup> | Latched               |  |  |  |  |  |

| High             | Х                                         | Low  | High | Х                | No effect                                   | Latched                                                                | Transparent           |  |  |  |  |  |

| High             | Х                                         | High | High | Х                | No effect                                   | Latched                                                                | Latched               |  |  |  |  |  |

| High             | Х                                         | ↑ +³ | High | Х                | No effect                                   | Latched                                                                | Latched               |  |  |  |  |  |

| High             | Х                                         | High | Low  | 0                | No effect                                   | Latched data = 0x0000                                                  | Latched data = 0x0000 |  |  |  |  |  |

| High             | Х                                         | High | Low  | High             | No effect                                   | Latched data = $0x2000$                                                | Latched data = 0x2000 |  |  |  |  |  |

<sup>1</sup> For the AD5554, data appears at the SDO pin 17 clock pulses after input at the SDI pin.

<sup>2</sup> X means don't care.

<sup>3</sup> t + is a positive logic transition.

<sup>4</sup> At power-on, both the input register and the DAC register are loaded with all 0s.

### **POWER-ON RESET**

When the  $V_{DD}$  power supply is turned on, an internal reset strobe forces all the input and DAC registers to the zero-code state or half-scale state, depending on the MSB pin voltage. The  $V_{DD}$  power supply should have a smooth positive ramp without drooping to have consistent results, especially in the region of  $V_{DD} = 1.5$  V to 2.3 V. The  $V_{SS}$  supply has no effect on the power-on reset performance. The DAC register data stays at a zero-scale or half-scale setting until a valid serial register data load takes place.

### **ESD PROTECTION CIRCUITS**

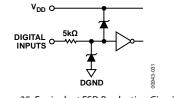

All logic input pins contain back-biased ESD protection Zener diodes that are connected to ground (DGND) and  $V_{DD}$ , as shown in Figure 25.

### POWER SUPPLY SEQUENCE

As standard practice, it is recommended that  $V_{DD}$ ,  $V_{SS}$ , and ground be powered up prior to any reference. The ideal power-up sequence is as follows:  $A_{GND}x$ , DGND,  $V_{DD}$ ,  $V_{SS}$ ,  $V_{REF}x$ , and the digital inputs. A noncompliance power-up sequence may elevate the reference current, but the devices resume normal operation once  $V_{DD}$  and  $V_{SS}$  are powered up.

### LAYOUT AND POWER SUPPLY BYPASSING

It is good practice to employ a compact, minimum lead length layout design. The leads to the input should be as direct as possible with a minimum conductor length. Ground paths should have low resistance and low inductance.

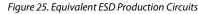

Similarly, it is good practice to bypass the power supplies with quality capacitors for optimum stability. Supply leads to the device should be bypassed with 0.01  $\mu$ F to 0.1  $\mu$ F disc or chip ceramic capacitors. Low ESR 1  $\mu$ F to 10  $\mu$ F tantalum or electrolytic capacitors should also be applied at V<sub>DD</sub> to minimize any transient disturbance and filter any low frequency ripple (see Figure 26). Users should not apply switching regulators for V<sub>DD</sub> due to the power supply rejection ratio (PSRR) degradation over frequency.

Figure 26. Power Supply Bypassing and Grounding Connection

### GROUNDING

The DGND and A<sub>GND</sub>x pins of the AD5544/AD5554 serve as digital and analog ground references. To minimize the digital ground bounce, the DGND terminal should be joined remotely at a single point to the analog ground plane (see Figure 26).

## **APPLICATIONS INFORMATION**

The AD5544/AD5554 are, inherently, two-quadrant multiplying DACs. That is, they can be easily set up for unipolar output operation. The full-scale output polarity is the inverse of the reference input voltage.

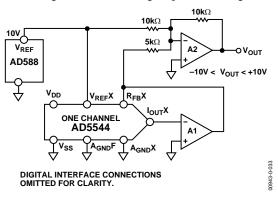

In some applications, it may be necessary to generate the full four-quadrant multiplying capability or a bipolar output swing. This is easily accomplished using an additional external amplifier (A2) configured as a summing amplifier (see Figure 27).

Figure 27. Four-Quadrant Multiplying Application Circuit

In this circuit, the first and second amplifiers (A1 and A2) provide a total gain of 2, which increases the output voltage span to 20 V. Biasing the external amplifier with a 10 V offset from the reference voltage results in a full four-quadrant multiplying circuit. The transfer equation of this circuit shows that both negative and positive output voltages are created as the input data (D) is incremented from code zero ( $V_{OUT} = -10$  V) to midscale ( $V_{OUT} = 0$  V) to full scale ( $V_{OUT} = 10$  V).

$$V_{OUT}\left(\frac{D}{32,768} - 1\right) \times - V_{REF} \text{ (for the AD5544)}$$

(3)

$$V_{OUT}\left(\frac{D}{8192} - 1\right) \times - V_{REF} \text{ (for the AD5554)}$$

(4)

### **REFERENCE SELECTION**

When selecting a reference for use with the AD55xx series of current output DACs, pay attention to the output voltage, temperature coefficient specification of the reference. Choosing a precision reference with a low output temperature coefficient minimizes error sources. Table 10 lists some of the references available from Analog Devices, Inc., that are suitable for use with this range of current output DACs.

### **AMPLIFIER SELECTION**

The primary requirement for the current-steering mode is an amplifier with low input bias currents and low input offset voltage. Because of the code-dependent output resistance of the DAC, the input offset voltage of an op amp is multiplied by the variable gain of the circuit. A change in this noise gain between two adjacent digital fractions produces a step change in the output voltage due to the amplifier's input offset voltage. This output voltage change is superimposed upon the desired change in output between the two codes and gives rise to a differential linearity error, which, if large enough, can cause the DAC to be nonmonotonic.

The input bias current of an op amp also generates an offset at the voltage output because of the bias current flowing in the feedback resistor,  $R_{FB}$ .

Common-mode rejection of the op amp is important in voltageswitching circuits because it produces a code-dependent error at the voltage output of the circuit.

Provided that the DAC switches are driven from true wideband, low impedance sources ( $V_{IN}$  and AGND), they settle quickly. Consequently, the slew rate and settling time of a voltage-switching DAC circuit is determined largely by the output op amp. To obtain minimum settling time in this configuration, minimize capacitance at the  $V_{REF}$  node (the voltage output node in this application) of the DAC. This is done by using low input capacitance buffer amplifiers and careful board design.

Analog Devices offers a wide range of amplifiers for both precision dc and ac applications, as listed in Table 11 and Table 12.

| Part No. | Output Voltage<br>(V) | Initial Tolerance<br>(%) | Maximum<br>Temperature<br>Drift (ppm/°C) | l <sub>ss</sub> (mA) | Output Noise (µV p-p) | Package(s)               |

|----------|-----------------------|--------------------------|------------------------------------------|----------------------|-----------------------|--------------------------|

| ADR01    | 10                    | 0.05                     | 3                                        | 1                    | 20                    | 8-lead SOIC              |

| ADR01    | 10                    | 0.05                     | 9                                        | 1                    | 20                    | 5-lead TSOT, 5-lead SC70 |

| ADR02    | 5.0                   | 0.06                     | 3                                        | 1                    | 10                    | 8-lead SOIC              |

| ADR02    | 5.0                   | 0.06                     | 9                                        | 1                    | 10                    | 5-lead TSOT, 5-lead SC70 |

| ADR03    | 2.5                   | 0.1                      | 3                                        | 1                    | 6                     | 8-lead SOIC              |

| ADR03    | 2.5                   | 0.1                      | 9                                        | 1                    | б                     | 5-lead TSOT, 5-lead SC70 |

| ADR06    | 3.0                   | 0.1                      | 3                                        | 1                    | 10                    | 8-lead SOIC              |

| ADR06    | 3.0                   | 0.1                      | 9                                        | 1                    | 10                    | 5-lead TSOT, 5-lead SC70 |

| ADR420   | 2.048                 | 0.05                     | 3                                        | 0.5                  | 1.75                  | 8-lead SOIC, 8-lead MSOP |

| ADR421   | 2.50                  | 0.04                     | 3                                        | 0.5                  | 1.75                  | 8-lead SOIC, 8-lead MSOP |

| ADR423   | 3.00                  | 0.04                     | 3                                        | 0.5                  | 2                     | 8-lead SOIC, 8-lead MSOP |

| ADR425   | 5.00                  | 0.04                     | 3                                        | 0.5                  | 3.4                   | 8-lead SOIC, 8-lead MSOP |

| ADR431   | 2.500                 | 0.04                     | 3                                        | 0.8                  | 3.5                   | 8-lead SOIC, 8-lead MSOP |

| ADR435   | 5.000                 | 0.04                     | 3                                        | 0.8                  | 8                     | 8-lead SOIC, 8-lead MSOP |

| ADR391   | 2.5                   | 0.16                     | 9                                        | 0.12                 | 5                     | 5-lead TSOT              |

| ADR395   | 5.0                   | 0.10                     | 9                                        | 0.12                 | 8                     | 5-lead TSOT              |

### Table 10. Suitable Analog Devices Precision References

### Table 11. Suitable Analog Devices Precision Op Amps

| Part No.  | Supply Voltage<br>(V) | V <sub>os</sub><br>Maximum<br>(μV) | l <sub>в</sub><br>Maximum<br>(nA) | 0.1 Hz to 10 Hz<br>Noise (μV p-p) | Supply Current<br>(µA) | Package(s)                  |

|-----------|-----------------------|------------------------------------|-----------------------------------|-----------------------------------|------------------------|-----------------------------|

| OP97      | ±2 to ±20             | 25                                 | 0.1                               | 0.5                               | 600                    | 8-lead SOIC, 8-lead PDIP    |

| OP1177    | ±2.5 to ±15           | 60                                 | 2                                 | 0.4                               | 500                    | 8-lead MSOP, 8-lead SOIC    |

| AD8675    | ±5 to ±18             | 75                                 | 2                                 | 0.1                               | 2300                   | 8-lead MSOP, 8-lead SOIC    |

| AD8671    | ±5 to ±15             | 75                                 | 12                                | 0.077                             | 3000                   | 8-lead MSOP, 8-lead SOIC    |

| ADA4004-1 | ±5 to ±15             | 125                                | 90                                | 0.1                               | 2000                   | 8-lead SOIC, 5-lead SOT-23  |

| AD8603    | 1.8 to 5              | 50                                 | 0.001                             | 2.3                               | 40                     | 5-lead TSOT                 |

| AD8607    | 1.8 to 5              | 50                                 | 0.001                             | 2.3                               | 40                     | 8-lead MSOP, 8-lead SOIC    |

| AD8605    | 2.7 to 5              | 65                                 | 0.001                             | 2.3                               | 1000                   | 5-lead WLCSP, 5-lead SOT-23 |

| AD8615    | 2.7 to 5              | 65                                 | 0.001                             | 2.4                               | 2000                   | 5-lead TSOT                 |

| AD8616    | 2.7 to 5              | 65                                 | 0.001                             | 2.4                               | 2000                   | 8-lead MSOP, 8-lead SOIC    |

Table 12. Suitable Analog Devices High Speed Op Amps

| Part No.  | Supply Voltage (V) | BW at ACL (MHz) | Slew Rate (V/µs) | V <sub>os</sub> (Max) (μV) | l <sub>B</sub> (Max) (nA) | Package(s)                 |

|-----------|--------------------|-----------------|------------------|----------------------------|---------------------------|----------------------------|

| AD8065    | 5 to 24            | 145             | 180              | 1500                       | 0.006                     | 8-lead SOIC, 5-lead SOT-23 |

| AD8066    | 5 to 24            | 145             | 180              | 1500                       | 0.006                     | 8-lead SOIC, 8-lead MSOP   |

| AD8021    | 5 to 24            | 490             | 120              | 1000                       | 10,500                    | 8-lead SOIC, 8-lead MSOP   |

| AD8038    | 3 to 12            | 350             | 425              | 3000                       | 750                       | 8-lead SOIC, 5-lead SC70   |

| ADA4899-1 | 5 to 12            | 600             | 310              | 35                         | 100                       | 8-lead LFCSP, 8-lead SOIC  |

| AD8057    | 3 to 12            | 325             | 1000             | 5000                       | 500                       | 5-lead SOT-23, 8-lead SOIC |

| AD8058    | 3 to 12            | 325             | 850              | 5000                       | 500                       | 8-lead SOIC, 8-lead MSOP   |

| AD8061    | 2.7 to 8           | 320             | 650              | 6000                       | 350                       | 5-lead SOT-23, 8-lead SOIC |

| AD8062    | 2.7 to 8           | 320             | 650              | 6000                       | 350                       | 8-lead SOIC, 8-lead MSOP   |

| AD9631    | ±3 to ±6           | 320             | 1300             | 10,000                     | 7000                      | 8-lead SOIC, 8-lead PDIP   |

### **OUTLINE DIMENSIONS**

Rev. H | Page 22 of 24

### **ORDERING GUIDE**

|                    |                |         |         | Temperature     |                                             | Package  |

|--------------------|----------------|---------|---------|-----------------|---------------------------------------------|----------|

| Model <sup>1</sup> | <b>RES Bit</b> | INL LSB | DNL LSB | Range           | Package Description                         | Option   |

| AD5544ARS          | 16             | ±2      | ±1.5    | -40°C to +125°C | 28-Lead Shrink Small Outline Package [SSOP] | RS-28    |

| AD5544ARSZ         | 16             | ±2      | ±1.5    | -40°C to +125°C | 28-Lead Shrink Small Outline Package [SSOP] | RS-28    |

| AD5544ARSZ-REEL7   | 16             | ±2      | ±1.5    | -40°C to +125°C | 28-Lead Shrink Small Outline Package [SSOP] | RS-28    |

| AD5544BRSZ         | 16             | ±1      | ±1      | -40°C to +125°C | 28-Lead Shrink Small Outline Package [SSOP] | RS-28    |

| AD5544BRSZ-REEL7   | 16             | ±1      | ±1      | -40°C to +125°C | 28-Lead Shrink Small Outline Package [SSOP] | RS-28    |

| AD5544ACPZ-1-R2    | 16             | ±4      | ±1      | -40°C to +125°C | 32-Lead LFCSP_WQ                            | CP-32-11 |

| AD5544ACPZ-1-RL7   | 16             | ±4      | ±1      | –40°C to +125°C | 32-Lead LFCSP_WQ                            | CP-32-11 |

| AD5544BCPZ-R2      | 16             | ±1      | ±1      | -40°C to +125°C | 32-Lead LFCSP_WQ                            | CP-32-11 |

| AD5544BCPZ-RL7     | 16             | ±1      | ±1      | -40°C to +125°C | 32-Lead LFCSP_WQ                            | CP-32-11 |

| AD5554BRSZ         | 14             | ±0.5    | ±1      | -40°C to +125°C | 28-Lead Shrink Small Outline Package [SSOP] | RS-28    |

| EV-AD5544/45SDZ    |                |         |         |                 | Evaluation Board                            |          |

<sup>1</sup> Z = RoHS Compliant Part.

# **Data Sheet**

### NOTES

I<sup>2</sup>C refers to a communications protocol originally developed by Philips Semiconductors (now NXP Semiconductors).

©2000–2015 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D00943-0-9/15(H)

www.analog.com

Rev. H | Page 24 of 24

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Data Conversion IC Development Tools category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below :