# 12-Bit, High Voltage DAC with SPI Interface

# AD5501

### FEATURES

Single-channel high voltage DAC 12-bit resolution Pin-selectable 30 V or 60 V output range Integrated precision reference Low power serial interface with readback capability Integrated temperature sensor alarm function Power-on reset Wide operating temperature range: -40°C to +105°C

#### **APPLICATIONS**

Programmable voltage sources High voltage LED drivers Receiver bias in optical communications

#### **GENERAL DESCRIPTION**

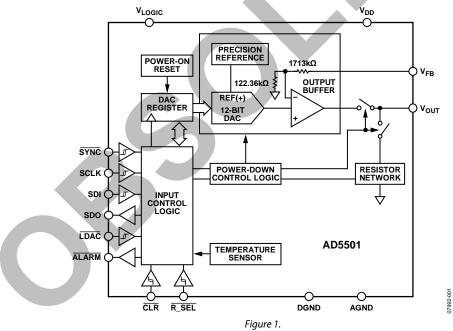

The AD5501 is a single-channel, 12-bit, serial input, digital-toanalog converter (DAC) with an on-chip high voltage output amplifier and an integrated precision reference. The DAC output voltage range is programmable via the range select pin ( $R\_SEL$ ). If  $R\_SEL$  is held high, the DAC output range is 0 V to 30 V. If  $R\_SEL$  is held low, the DAC output range is 0 V to 60 V. The on chip output amplifier allows an output swing within the range of AGND + 0.5 V to  $V_{DD} - 0.5$  V.

The AD5501 has a high speed serial interface, which is compatible with SPI\*-, QSPI\*-, MICROWIRE<sup>™</sup>-, and DSP-interface standards and can handle clock speeds of up to 16.667 MHz.

#### FUNCTIONAL BLOCK DIAGRAM

#### Rev. C Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# TABLE OF CONTENTS

| Features                                    | 1    |

|---------------------------------------------|------|

| Applications                                | 1    |

| General Description                         | 1    |

| Functional Block Diagram                    | 1    |

| Revision History                            | 2    |

| Specifications                              | 4    |

| AC Characteristics                          | 5    |

| Timing Characteristics                      | 6    |

| Absolute Maximum Ratings                    | 8    |

| Thermal Resistance                          | 8    |

| ESD Caution                                 | 8    |

| Pin Configuration and Function Descriptions | 9    |

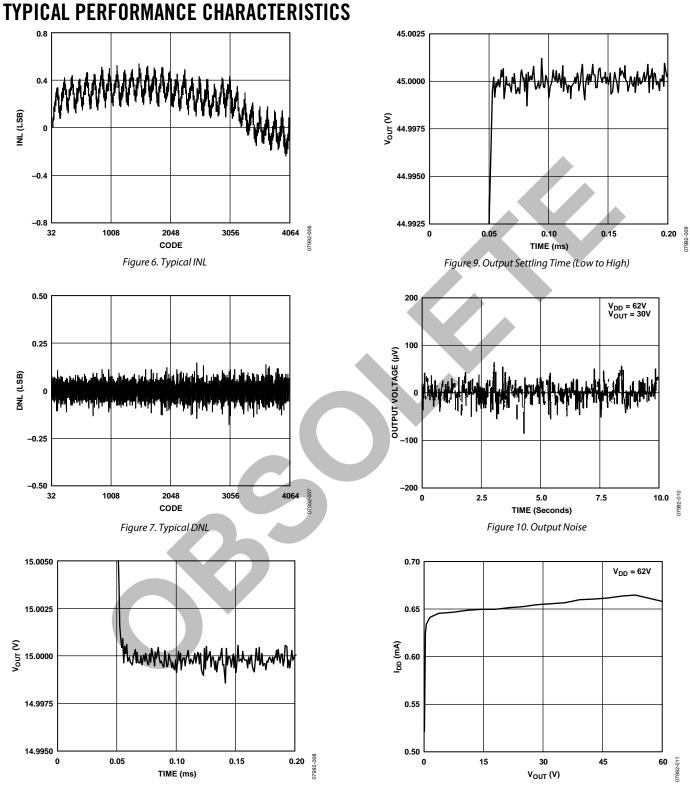

| Typical Performance Characteristics         | . 10 |

| Terminology                                 | . 12 |

| Theory of Operation                         | . 13 |

| Power-Up State                              | . 13 |

### **REVISION HISTORY**

| 12/12—Rev. B to Rev. C                                      |    |

|-------------------------------------------------------------|----|

| Changes to t <sub>4</sub> Parameter, Table 4                | 6  |

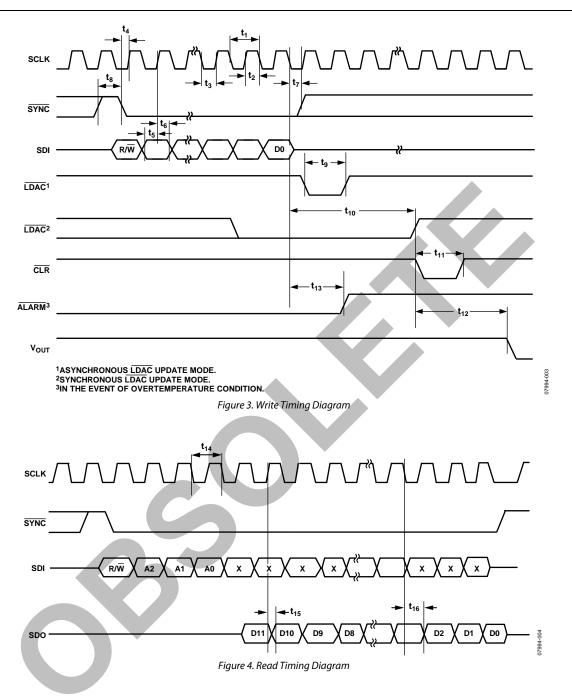

| Changes to Figure 3 and Figure 4                            | 7  |

| Changes to Pin 2 Description, Table 7 and Pin 3 Description | 1, |

| Table 7                                                     | 9  |

| Changes to Write Mode Section                               | 15 |

| Changes to Table 10                                         | 16 |

|                                                             |    |

| Power-Down Mode                 |    |

|---------------------------------|----|

| DAC Channel Architecture        |    |

| V <sub>FB</sub> Pin             |    |

| Selecting the Output Range      |    |

| CLR Function                    |    |

| LDAC Function                   | 14 |

| Temperature Sensor              | 14 |

| Power Dissipation               |    |

| Power Supply Sequencing         |    |

| Serial Interface                | 15 |

| Write Mode                      | 15 |

| Read Mode                       | 15 |

| Writing to the Control Register | 15 |

| Interfacing Examples            |    |

| Outline Dimensions              | 17 |

| Ordering Guide                  |    |

### 4/12—Rev. A to Rev. B

| Cł | nges to Product Title             | 1 |

|----|-----------------------------------|---|

|    | nges to Figure 15 and Figure 16 1 |   |

**10/10—Rev. 0 to Rev. A** Changes to Figure 3 and Figure 4.....7

7/09—Revision 0: Initial Version

The serial interface offers the user the capability of both writing to, and reading from, most internal registers.

To reduce power consumption at power up, only the digital section of the AD5501 is powered up initially. This gives the user the ability to program the DAC registers to the required value while typically consuming only 30  $\mu$ A of supply current. The AD5501 incorporates power-on reset circuitry that ensures the DAC registers power up in a known condition and remain there until a valid write to the device has occurred. The analog section is powered up by issuing a power-up command via the SPI interface. The AD5501 provides software-selectable output loads while in the power-down mode.

The AD5501 has on on-chip temperature sensor. If the temperature on the die exceeds 110°C, the ALARM pin (an active low CMOS output pin) flags an alarm and the AD5501 enters a temperature power-down mode that disconnects the output amplifier, thus removing the short-circuit condition. The AD5501 remains in power-down mode until a software power-up command is executed.

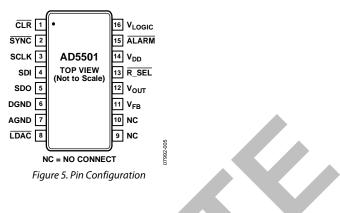

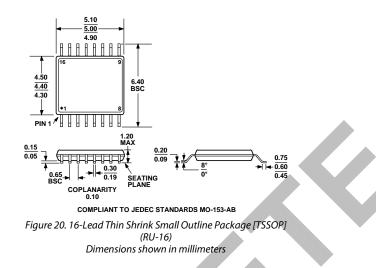

The AD5501 is available in a compact 16-lead TSSOP. The AD5501 is guaranteed to operate over the extended temperature range of  $-40^{\circ}$ C to  $+105^{\circ}$ C.

| Part No. | Description                                          |

|----------|------------------------------------------------------|

| AD5504   | High Voltage, Quad Channel 12-Bit Voltage Output DAC |

|          |                                                      |

# **SPECIFICATIONS**

$V_{\rm DD} = 10 \text{ V to } 62 \text{ V}; V_{\rm LOGIC} = 2.3 \text{ V to } 5.5 \text{ V}; R_{\rm L} = 60 \text{ k}\Omega; C_{\rm L} = 200 \text{ pF}; -40^{\circ}\text{C} < T_{\rm A} < +105^{\circ}\text{C}, \text{ unless otherwise noted.}$

| Table 2.                                                            |                  |                     |                  |                       |               |                                               |

|---------------------------------------------------------------------|------------------|---------------------|------------------|-----------------------|---------------|-----------------------------------------------|

| Parameter                                                           | Symbol           | Min                 | Typ <sup>1</sup> | Max                   | Unit          | <b>Test Conditions/Comments</b>               |

| ACCURACY <sup>2</sup>                                               |                  |                     |                  |                       |               |                                               |

| Resolution                                                          |                  |                     | 12               |                       | Bits          |                                               |

| Differential Nonlinearity                                           | DNL              | -1                  |                  | +1                    | LSB           |                                               |

| Integral Nonlinearity                                               | INL              |                     |                  |                       |               |                                               |

| 60 V Mode                                                           |                  | -1                  |                  | +1                    | LSB           | $V_{DD} = 62 V$                               |

| 30 V Mode                                                           |                  | -2                  |                  | +2                    | LSB           | $V_{DD} = 62 V$                               |

| V <sub>OUT</sub> Temperature Coefficient <sup>3, 4</sup>            |                  |                     | 50               |                       | ppm/°C        | DAC code = half scale                         |

| Offset Error                                                        | V <sub>OE</sub>  | -65                 |                  | +100                  | mV            |                                               |

| Offset Error Drift <sup>4</sup>                                     | 01               |                     | 60               |                       | μV/°C         |                                               |

| Zero-Scale Error                                                    | V <sub>ZSE</sub> |                     |                  | 80                    | mV            |                                               |

| Zero-Scale Error Drift <sup>4</sup>                                 | 232              |                     | 50               |                       | μV/°C         | 60 V mode                                     |

| Full-Scale Error                                                    | V <sub>FSE</sub> | -325                |                  | +275                  | mV            |                                               |

| Full-Scale Error Drift <sup>4</sup>                                 | FSE              |                     | 1                |                       | mV/°C         | -40°C to +25°C; 60 V mode                     |

|                                                                     |                  |                     | 350              |                       | μV/°C         | +25°C to +105°C; 60 V mode                    |

| Gain Error                                                          |                  | -0.6                |                  | +0.6                  | % of FSR      |                                               |

| Gain Temperature Coefficient <sup>4</sup>                           |                  |                     | 10               |                       | ppm of FSR/°C |                                               |

| OUTPUT CHARACTERISTICS                                              |                  |                     |                  |                       |               |                                               |

| Output Voltage Range <sup>5</sup>                                   |                  | AGND + 0.5          |                  | V <sub>DD</sub> - 0.5 | V             |                                               |

| Short-Circuit Current <sup>4, 6</sup>                               |                  |                     | 2                | TDD 01.5              | mA            |                                               |

| Capacitive Load Stability <sup>4</sup>                              |                  |                     | 2                |                       |               | 1 V to 4 V step                               |

| $R_1 = 60 \text{ k}\Omega \text{ to }\infty$                        |                  |                     |                  | 1                     | nF            | TV to 4 v step                                |

| $R_L = 60 \text{ K}\Omega \log \infty$<br>Load Current <sup>4</sup> |                  | -1                  |                  | . 1                   | mA            |                                               |

|                                                                     |                  | -1                  |                  | +1                    |               |                                               |

| Feedback Resistance <sup>7</sup>                                    |                  |                     | 3                | 100                   | ΩΩ            |                                               |

| DC Output Impedance <sup>4</sup>                                    |                  |                     |                  |                       |               |                                               |

| DC Output Leakage <sup>4</sup>                                      |                  |                     | 10               |                       | μΑ            |                                               |

| DIGITAL INPUTS                                                      |                  |                     |                  |                       |               |                                               |

| Input Logic High                                                    | V <sub>IH</sub>  | 2.0                 |                  |                       | V             | $V_{LOGIC} = 4.5 \text{ V to } 5.5 \text{ V}$ |

|                                                                     |                  | 1.8                 |                  |                       | V             | $V_{LOGIC} = 2.3 V \text{ to } 3.6 V$         |

| Input Logic Low                                                     | VIL              |                     |                  | 0.8                   | V             | $V_{LOGIC} = 2.3 V \text{ to } 5.5 V$         |

| Input Current                                                       |                  |                     |                  | ±1                    | μΑ            |                                               |

| Input Capacitance <sup>4</sup>                                      | I <sub>IC</sub>  |                     | 5                |                       | pF            |                                               |

| DIGITAL OUTPUTS                                                     |                  |                     |                  |                       |               |                                               |

| Output High Voltage                                                 | V <sub>OH</sub>  | $V_{LOGIC} - 0.4 V$ |                  |                       | V             | $I_{SOURCE} = 200 \ \mu A$                    |

| Output Low Voltage                                                  | V <sub>OL</sub>  |                     |                  | DGND + 0.4 V          | V             | $I_{SINK} = 200 \ \mu A$                      |

| Three-State Leakage Current                                         |                  |                     |                  |                       |               |                                               |

| SDI, SDO, SCLK, LDAC, CLR,                                          |                  | -1                  |                  | +1                    | μΑ            |                                               |

| R_SEL Pins                                                          |                  |                     |                  |                       |               |                                               |

| ALARM Pin                                                           |                  | -10                 |                  | +10                   | μΑ            |                                               |

| Output Capacitance <sup>4</sup>                                     |                  |                     | 5                |                       | pF            |                                               |

# AD5501

| Parameter                         | Symbol                 | Min | <b>Typ</b> <sup>1</sup> | Max  | Unit | Test Conditions/Comments                       |

|-----------------------------------|------------------------|-----|-------------------------|------|------|------------------------------------------------|

| POWER SUPPLIES                    |                        |     |                         |      |      |                                                |

| V <sub>DD</sub>                   |                        | 10  |                         | 62   | V    |                                                |

| V <sub>LOGIC</sub>                |                        | 2.3 |                         | 5.5  | V    |                                                |

| Quiescent Supply Current          | I <sub>QUIESCENT</sub> |     | 0.6                     | 0.75 | mA   | Static conditions; DAC output = midscale       |

| Logic Supply Current<br>DC PSRR⁴  | I <sub>LOGIC</sub>     |     | 0.4                     | 2    | μΑ   | $V_{IH} = V_{LOGIC}$ ; $V_{IL} = DGND$         |

| 30 V mode                         |                        |     | 76                      |      | dB   | DAC output = full scale                        |

| 60 V mode                         |                        |     | 68                      |      | dB   | DAC output = full scale                        |

| POWER-DOWN MODE                   |                        |     |                         |      |      |                                                |

| Supply Current                    | I <sub>DD PWD</sub>    |     |                         |      |      |                                                |

| Software Power-Down Mode          |                        |     | 30                      | 50   | μA   |                                                |

| Junction Temperature <sup>6</sup> | T                      |     |                         | 130  | °C   | $T_{J} = T_{A} + P_{TOTAL} \times \theta_{JA}$ |

$^1$  Typical specifications represent average readings at 25°C,  $V_{\rm DD}$  = 62 V, and  $V_{\rm LOGIC}$  = 5 V.  $^2$  Valid in the output voltage range of (AGND + 0.5 V) to (V\_{\rm DD} - 0.5 V). Output is unloaded.

<sup>3</sup> Includes linearity, offset, and gain drift.

<sup>4</sup> Guaranteed by design and characterization. Not production tested.

<sup>5</sup> The DAC architecture gives a fixed linear voltage output range of 0 V to 30 V if R\_SEL is held high and 0 V to 60 V if R\_SEL is held low. As the output voltage range is limited by output amplifier compliance, V<sub>DD</sub> should be set to at least 0.5 V higher than the maximum output voltage to ensure compliance.

<sup>6</sup> If the die temperature exceeds 110°C, the AD5501 enters a temperature power-down mode putting the DAC output into a high impedance state thereby removing the short-circuit condition. Overheating caused by long term short-circuit condition(s) is detected by an integrated thermal sensor. After power-down, the AD5501 remains powered down until a software power-up command is executed.

$^7$  Maximum resistance between  $V_{\text{OUT}}$  and  $V_{\text{FB}}$  pins.

### **AC CHARACTERISTICS**

$V_{DD} = 10 \text{ V}$  to 62 V;  $V_{LOGIC} = 2.3 \text{ V}$  to 5.5 V;  $R_L = 60 \text{ k}\Omega$ ;  $C_L = 200 \text{ pF}$ ;  $-40^{\circ}\text{C} < T_A < +105^{\circ}\text{C}$ , unless otherwise noted.

#### Table 3.

| Parameter <sup>1, 2</sup>       | Min | Тур  | Max | Unit   | Test Conditions/Comments <sup>3</sup>                                   |

|---------------------------------|-----|------|-----|--------|-------------------------------------------------------------------------|

| AC CHARACTERISTICS              |     |      |     |        |                                                                         |

| Output Voltage Settling Time    |     |      |     |        | $^{1}$ /4 to $^{3}$ /4 scale settling to ±1 LSB, R <sub>L</sub> = 60 kΩ |

| 60 V Mode                       |     | 45   | 55  | μs     |                                                                         |

| 30 V Mode                       |     | 25   | 35  | μs     |                                                                         |

| Slew Rate                       |     | 0.65 |     | V/µs   |                                                                         |

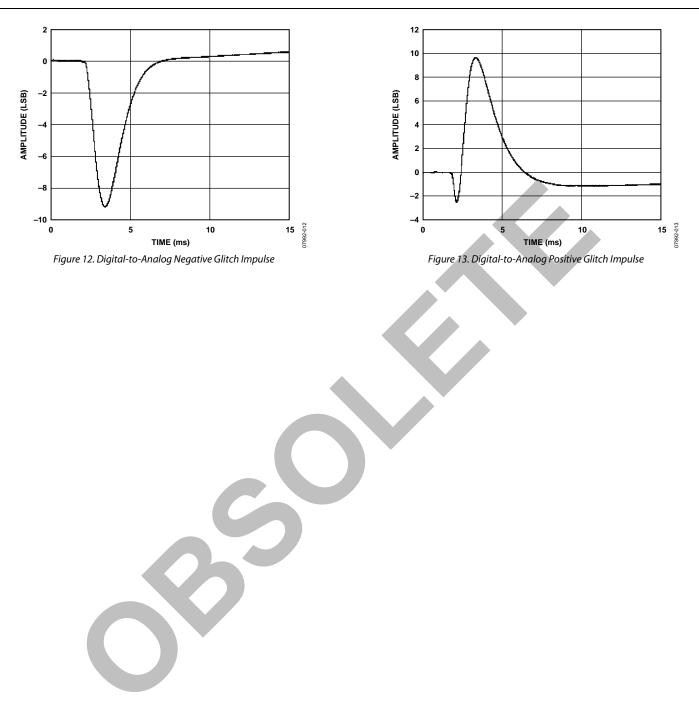

| Digital-to-Analog Glitch Energy |     | 300  |     | nV-s   | 1 LSB change around major carry in 60 V mode                            |

| Glitch Impulse Peak Amplitude   |     | 170  |     | mV     | 60 V mode                                                               |

| Digital Feedthrough             |     | 5    |     | nV-s   |                                                                         |

| Peak-to-Peak Noise              |     | 140  |     | μV р-р | 0.1 Hz to 10 Hz; DAC code = 0x800                                       |

|                                 |     | 4    |     | mV p-p | 0.1 Hz to 10 kHz; DAC code = 0x800                                      |

<sup>1</sup> Guaranteed by design and characterization; not production tested.

<sup>2</sup> See the Terminology section.

<sup>3</sup> Temperature range is -40°C to + 105°C, typical at 25°C.

### **TIMING CHARACTERISTICS**

$V_{DD}$  = 30 V,  $V_{LOGIC}$  = 2.3 V to 5.5 V, and -40°C <  $T_A$  < +105°C, all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| Table 4.                     |                    |        |                                                                                   |  |  |

|------------------------------|--------------------|--------|-----------------------------------------------------------------------------------|--|--|

| Parameter                    | Limit <sup>1</sup> | Unit   | Test Conditions/Comments                                                          |  |  |

| t <sub>1</sub> <sup>2</sup>  | 60                 | ns min | SCLK cycle time                                                                   |  |  |

| t <sub>2</sub>               | 10                 | ns min | SCLK high time                                                                    |  |  |

| t <sub>3</sub>               | 10                 | ns min | SCLK low time                                                                     |  |  |

| t <sub>4</sub>               | 25                 | ns min | SYNC falling edge to SCLK rising edge setup time                                  |  |  |

| t <sub>5</sub>               | 15                 | ns min | Data setup time                                                                   |  |  |

| t <sub>6</sub>               | 5                  | ns min | Data hold time                                                                    |  |  |

| t <sub>7</sub>               | 0                  | ns min | SCLK falling edge to SYNC rising edge                                             |  |  |

| t <sub>8</sub>               | 20                 | ns min | Minimum SYNC high time                                                            |  |  |

| t <sub>9</sub>               | 20                 | ns min | LDAC pulse width low                                                              |  |  |

| t <sub>10</sub>              | 50                 | ns min | SCLK falling edge to LDAC rising edge                                             |  |  |

| t <sub>11</sub>              | 15                 | ns min | CLR pulse width low                                                               |  |  |

| t <sub>12</sub>              | 100                | ns typ | CLR pulse activation time                                                         |  |  |

| t <sub>13</sub>              | 20                 | μs typ | ALARM clear time                                                                  |  |  |

| t <sub>14</sub>              | 110                | ns min | SCLK cycle time in read mode                                                      |  |  |

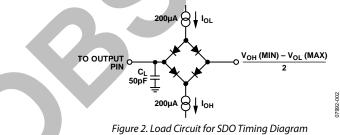

| t <sub>15</sub> <sup>3</sup> | 55                 | ns max | SCLK rising edge to SDO valid                                                     |  |  |

| t <sub>16</sub> <sup>3</sup> | 25                 | ns min | SCLK to SDO Data hold time                                                        |  |  |

| t <sub>17</sub> <sup>4</sup> | 50                 | µs max | Power-on-reset time (this is not shown in the timing figures)                     |  |  |

| t <sub>18</sub> 5            | 50                 | μs max | Power-on time (this is not shown in the timing figures)                           |  |  |

| t <sub>19</sub>              | 5                  | μs typ | ALARM clear to output amplifier turn on (this is not shown in the timing figures) |  |  |

<sup>1</sup> All input signals are specified with tr = tf = 1 ns/V (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of ( $V_{IL} + V_{IH}$ )/2. <sup>2</sup> Maximum SCLK frequency is 16.667 MHz.

<sup>3</sup> Under the load conditions that are outlined in Figure 2.

<sup>4</sup> Time from when V<sub>DD</sub> or V<sub>LOGIC</sub> supplies are powered-up to when a digital interface command can be executed. <sup>5</sup> Time required from execution of power-on software command to when the DAC output has settled to 1 V.

#### **Circuit and Timing Diagrams**

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}$ C, unless otherwise noted. Transient currents of up to 100 mA do not cause SCR latch-up.

#### Table 5.

| Parameter                                                | Rating                               |

|----------------------------------------------------------|--------------------------------------|

| V <sub>DD</sub> to AGND                                  | -0.3 V to +64 V                      |

| V <sub>LOGIC</sub> to DGND                               | –0.3 V to +7 V                       |

| V <sub>OUT</sub> to AGND                                 | -0.3 V to V <sub>DD</sub> + 0.3 V    |

| Digital Input to DGND                                    | -0.3 V to V <sub>LOGIC</sub> + 0.3 V |

| SDO Output to DGND                                       | -0.3 V to V <sub>LOGIC</sub> + 0.3 V |

| AGND to DGND                                             | –0.3 V to +0.3 V                     |

| Maximum Junction Temperature<br>(T <sub>J</sub> Maximum) | 150℃                                 |

| Storage Temperature Range                                | -65°C to +150°C                      |

| Reflow Soldering                                         |                                      |

| Peak Temperature                                         | 260°C                                |

| Time at Peak Temperature Range                           | 20 sec to 40 sec                     |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

Thermal resistance is for a JEDEC 4-layer (2S2P) printed circuit board (PCB).

#### Table 6. Thermal Resistance

| Package Type  | θ <sub>JA</sub> | Unit |

|---------------|-----------------|------|

| 16-Lead TSSOP | 112.60          | °C/W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

#### Table 7. Pin Function Descriptions

| Pin No. | Mnemonic         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | CLR              | Asynchronous Clear Input. The CLR input is falling edge sensitive. When CLR is low, all LDAC pulses are ignored. When CLR is activated, the input register and the DAC register are set to 0x000 and the output to zero scale.                                                                                                                                                                                                                          |

| 2       | SYNC             | Falling Edge Synchronization Signal. This is the frame synchronization signal for the input data. When SYNC goes low, it enables the input shift register and data is transferred in on the rising edges of the following clocks. The selected DAC register is updated on the 16th falling SCLK, unless SYNC is taken high before this edge, in which case, the rising edge of SYNC acts as an interrupt, and the write sequence is ignored by the DAC. |

| 3       | SCLK             | Serial Data Input. This part has a 16-bit shift register. Data is clocked into the register on the rising edge of the serial clock input.                                                                                                                                                                                                                                                                                                               |

| 4       | SDI              | Serial Data Input. This part has a 16-bit shift register. Data is clocked into the register on the falling edge of the serial clock input.                                                                                                                                                                                                                                                                                                              |

| 5       | SDO              | Serial Data Output. CMOS output. This pin serves as the readback function for all DAC and control registers. Data is clocked out on the rising edge of SCLK and is valid on the falling edge of SCLK.                                                                                                                                                                                                                                                   |

| 6       | DGND             | Digital Ground Pin.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7       | AGND             | Analog Ground Pin.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 8       | LDAC             | Load DAC Input. Pulsing this pin low updates the DAC with the value in the input register. If the LDAC pin is tied low, the DAC output is updated automatically when data is written to the input register.                                                                                                                                                                                                                                             |

| 9, 10   | NC               | Not Connected. These pins remain unconnected.                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11      | V <sub>FB</sub>  | Voltage Feedback Pin. Feedback node for the output amplifier.                                                                                                                                                                                                                                                                                                                                                                                           |

| 12      | V <sub>OUT</sub> | Buffered Analog Output Voltage from the DAC.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 13      | R_SEL            | Range Select Pin. Tying this pin to DGND selects a DAC output range of 0 V to 60 V, alternatively tying $\overline{R}_{SEL}$ to $V_{LOGIC}$ selects a DAC output range of 0 V to 30 V.                                                                                                                                                                                                                                                                  |

| 14      | V <sub>DD</sub>  | Positive Analog Power Supply. 10 V to 62 V for the specified performance. Decouple this pin with 0.1 $\mu$ F ceramic capacitors and 10 $\mu$ F capacitors.                                                                                                                                                                                                                                                                                              |

| 15      | ALARM            | Active Low CMOS Output Pin. Flags an alarm if the temperature on the die exceeds 110°C.                                                                                                                                                                                                                                                                                                                                                                 |

| 16      | VLOGIC           | Logic Power Supply; 2.3 V to 5.5 V. Decouple this with 0.1 $\mu$ F ceramic capacitors and 10 $\mu$ F capacitors.                                                                                                                                                                                                                                                                                                                                        |

# AD5501

Figure 8. Output Settling Time (High to Low)

Figure 11. I<sub>DD</sub> vs. V<sub>OUT</sub>

# AD5501

# TERMINOLOGY

#### Relative Accuracy (Integral Nonlinearity)

For the DAC, relative accuracy, or integral nonlinearity (INL), is a measure of the maximum deviation in LSBs from a straight line passing through the endpoints of the DAC transfer function.

#### **Differential Nonlinearity**

Differential nonlinearity (DNL) is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of  $\pm$ 1 LSB maximum ensures monotonicity. This DAC is guaranteed monotonic by design.

#### Zero-Code Error

Zero-code error is a measure of the output error when zero code (0x000) is loaded into the DAC register. Ideally, the output should be 0 V. The zero-code error is always positive in the AD5501 because the output of the DAC cannot go below 0 V due to a combination of the offset errors in the DAC and the output amplifier. Zero-code error is expressed in millivolts.

#### Zero-Code Error Drift

Zero-code error drift is a measure of the change in zero-code error with a change in temperature expressed in  $\mu V/^{\circ}C.$

#### **Offset Error**

A measure of the difference between  $V_{OUT}$  (actual) and  $V_{OUT}$  (ideal) expressed in millivolts in the linear region of the transfer function. Offset error is measured on the AD5501 with Code 32 loaded in the DAC registers for 60 V mode and with Code 64 loaded in the DAC registers for 30 V mode. Offset error is expressed in millivolts.

#### **Offset Error Drift**

Offset error drift is a measure of the change in offset error with a change in temperature. It is expressed in  $\mu V/^{\circ}C$ .

#### **Full-Scale Error**

Full-scale error is a measure of the output error when full-scale code (0xFFF) is loaded into the DAC register expressed in millivolts.

#### Full-Scale Error Drift

Full-scale error drift is a measure of the change in full-scale error with a change in temperature. It is expressed in  $\mu V/^{\circ}C$ .

#### **Gain Error**

Gain error is a measure of the span error of the DAC. It is the deviation in slope of the DAC transfer characteristic from the ideal, expressed as a percentage of the full-scale range.

#### **Gain Temperature Coefficient**

The gain temperature coefficient is a measure of the change in gain with changes in temperature. It is expressed in (ppm of full-scale range)/°C.

#### Digital-to-Analog Glitch Impulse

Digital-to-analog glitch impulse is the impulse injected into the analog output when the input code in the DAC register changes state. It is normally specified as the area of the glitch in nV-s and is measured when the digital input code is changed by 1 LSB at the major carry transition.

#### DC Power Supply Rejection Ratio (PSRR)

PSRR indicates how the output of the DAC is affected by changes in the supply voltage. PSRR is the ratio of the change in  $V_{\rm OUT}$  to a change in  $V_{\rm DD}$  for full-scale output of the DAC. It is measured in decibels.  $V_{\rm DD}$  is dc varied  $\pm 10\%$ .

#### AC Power Supply Rejection Ratio (PSRR)

PSRR indicates how the output of the DAC is affected by changes in the supply voltage. PSRR is the ratio of the change in  $V_{OUT}$  to a change in  $V_{DD}$  for full-scale output of the DAC. It is measured in decibels.  $V_{DD}$  is ac varied ±10%.

### **Digital Feedthrough**

Digital feedthrough is a measure of the impulse injected into the analog output of the DAC from the digital input pins of the device but is measured when the DAC is not being written to  $\overline{(SYNC)}$  held high). It is specified in nV-s and measured with a full-scale change on the digital input pins, that is, from all 0s to all 1s or vice versa.

#### **Capacitive Load Stability**

Capacitive load stability refers to the ability of the amplifier to drive a capacitive load. An amplifier output is considered stable if any overshoot or ringing has stopped before approximately 1.5 times the settling time of the DAC has elapsed.

## THEORY OF OPERATION

The AD5501 contains a 12-bit DAC, an output amplifier, and a precision reference in a single package. The architecture of the DAC channel consists of a 12-bit resistor string DAC followed by an output buffer amplifier. The part operates from a single-supply voltage of 10 V to 62 V. The DAC output voltage range is selected via the range select,  $\overline{R}$ \_SEL, pin. The DAC output range is 0 V to 30 V if  $\overline{R}$ \_SEL is held high and 0 V to 60 V if  $\overline{R}$ \_SEL is held low. Data is written to the AD5501 in a 16-bit word format (see Table 8), via a serial interface.

### **POWER-UP STATE**

On power-up, the power-on reset circuitry clears the bits of the control register to 0x40 (see Table 10) ensuring that the analog section is initially powered down, which helps reduce power consumption. The user can program the DAC register to the required value while typically consuming only 30  $\mu$ A of supply current. The power-on reset circuitry also ensures that the input and DAC registers power up in a known condition, 0x000, and remain there until a valid write to the device has taken place. The analog section can be powered up by setting Bit C2 of the control register to 1.

### **POWER-DOWN MODE**

The DAC channel can be powered up or powered down by programming Bit C2 in the control register (see Table 10). When the DAC channel is powered down, the associated analog circuitry turns off to reduce power consumption. The digital section of the AD5501 remains powered up. The output of the DAC amplifier can be three-stated or connected to AGND via an internal 20 k $\Omega$ resistor, depending on the state of Bit C6 in the control register. The power-down mode does not change the contents of the DAC register to ensure that the DAC channel returns to its previous voltage when the power-down bit is set to 1. The AD5501 also offers the user the flexibility of updating the DAC registers during power-down. The control register can be read back at any time to check the status of the bits.

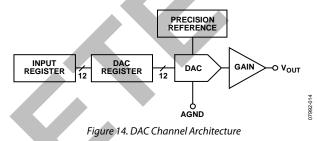

### DAC CHANNEL ARCHITECTURE

The architecture of the DAC channel consists of a 12-bit resistor string DAC followed by an output buffer amplifier (see Figure 14). The resistor string section is simply a string of resistors, each of Value R from V<sub>REF</sub> generated by the precision reference to AGND. This type of architecture guarantees DAC monotonicity. The 12-bit binary digital code loaded to the DAC register determines at which node on the string the voltage is tapped off before being fed into the output amplifier. The output amplifier multiplies the DAC output voltage to give a fixed linear voltage output range of 0 V to 60 V if  $\overline{R}$ \_SEL = 0 or 0 V to 30 V if  $\overline{R}$ \_SEL = 1. Each output amplifier is capable of driving a 60 k $\Omega$  load while allowing an output swing within the range of AGND + 0.5 V to V<sub>DD</sub> - 0.5 V.

Because the DAC architecture gives a fixed voltage output range of 0 V to 30 V or 0 V to 60 V, the user should set  $V_{\rm DD}$  to at least 30.5 V or 60.5 V to use the maximum DAC resolution. The data format for the AD5501 is straight binary and the output voltage follows the formula

$$V_{OUT} = \frac{D}{4096} \times Range$$

where:

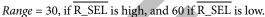

*D* is the code loaded to the DAC.

### V<sub>FB</sub> PIN

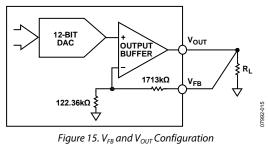

The voltage feedback pin (V<sub>FB</sub>) is part of the feedback loop of the gain amplifier. To compensate for any voltage drop between the V<sub>OUT</sub> pin and the load, connect (in a force sense configuration) V<sub>FB</sub> to the V<sub>OUT</sub> pin, as shown in Figure 15.

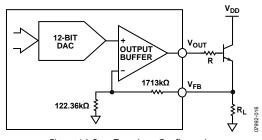

The  $V_{FB}$  pin can also be used to control a pass transistor where more current is required than can be supplied by the AD5501. The configuration is shown in Figure 16.

Figure 16. Pass Transistor Configuration

### SELECTING THE OUTPUT RANGE

The output range of the DAC is selected by the  $\overline{R\_SEL}$  pin. When the  $\overline{R\_SEL}$  pin is connected to a Logic 1, the DAC output voltage can be set between 0 V and 30 V. When the  $\overline{R\_SEL}$  pin is connected to a Logic 0, the DAC output voltage can be set between 0 V and 60 V. The state of  $\overline{R\_SEL}$  can be changed any time when the serial interface is not being used, that is, not during a read or write operation. When the  $\overline{R\_SEL}$  pin is changed, the voltage on the output pin remains the same until the next write to the DAC register (and  $\overline{LDAC}$  is brought low). For example, if the user writes 0x800 to the DAC register when in 30 V mode ( $\overline{R\_SEL} = 1$ ), the output voltage is 15 V (assuming  $\overline{LDAC}$  is low or has been pulsed low). When the user switches to 60 V mode ( $\overline{R\_SEL} = 0$ ), the output stays at 15 V until the user writes a new value to the DAC register.  $\overline{LDAC}$  must be low or be pulsed low for the output to change.

### **CLR** FUNCTION

The AD5501 has a hardware  $\overline{\text{CLR}}$  pin that is an asynchronous clear input. The  $\overline{\text{CLR}}$  input is falling edge sensitive. Bringing the  $\overline{\text{CLR}}$  line low clears the contents of the input register and the DAC registers to 0x000. The  $\overline{\text{CLR}}$  pulse activation time, that is, the falling edge of  $\overline{\text{CLR}}$  to when the output starts to change, is typically 100 ns.

### LDAC FUNCTION

The DAC output can be updated using the hardware  $\overline{\text{LDAC}}$  pin.  $\overline{\text{LDAC}}$  is normally high. On the falling edge of  $\overline{\text{LDAC}}$ , data is copied from the input register to the DAC register and the DAC output is updated (asynchronous update mode, see Figure 3). If the  $\overline{\text{LDAC}}$  is kept low or is low on the falling edge of the 16<sup>th</sup> SCLK, the DAC register and DAC output are updated automatically when new data is received in the input register (synchronous update mode, see Figure 3).

### **TEMPERATURE SENSOR**

The AD5501 has an integrated temperature sensor, which causes the part to enter thermal shutdown mode when the temperature on the die exceeds 110°C. In thermal shutdown mode, the analog section of the device powers down and the DAC output is disconnected but the digital section remains operational, which is equivalent to setting the power-down bit in the control register. To indicate that the AD5501 has entered temperature shutdown mode, Bit 0 of the control register is set to 1 and the ALARM pin goes low. The AD5501 remains in temperature shutdown mode with Bit 0 set to 1 and the ALARM pin low, even if the die temperature falls, until Bit 0 in the control register is cleared to 0.

### **POWER DISSIPATION**

Drawing current from the  $V_{OUT}$  pin causes a temperature rise in the die and package of the AD5501. The package junction temperature (T<sub>1</sub>) should not exceed 130°C for normal operation. If the die temperature exceeds 110°C, the AD5501 enters thermal shutdown mode as described in the previous section. The amount of heat generated can be calculated using the formula

$$T_{J} = T_{A} + (P_{TOTAL} \times \theta_{JA})$$

where:

$T_I$  is the package junction temperature.

$T_A$  is the ambient temperature.

$P_{TOTAL}$  is the total power being consumed by the AD5501.  $\theta_{JA}$  is the thermal impedance of the AD5501 package (see the Absolute Maximum Ratings section for this value).

### POWER SUPPLY SEQUENCING

The power supplies for the AD5501 can be applied in any order without affecting the device. However, before the power supplies are applied, connect the AGND and DGND pins to the relevant ground plane. Do not allow any of the digital input pins (SCLK, SDI, SYNC, R\_SEL, and CLR) to float during power up. The digital input pins can be connected to pull-up (to  $V_{LOGIC}$ ) or pull-down (to DGND) resistors as required.

The AD5501 has a serial interface (SYNC, SCLK, SDI, and SDO), which is compatible with SPI standards, as well as with most DSPs. The AD5501 allows writing of data, via the serial interface, to the input and control registers. The DAC register is not directly writeable or readable.

The input shift register is 16 bits wide (see Table 8). The 16-bit word consists of one read/write  $(R/\overline{W})$  control bit, followed by three address bits and 12 DAC data bits. Data is loaded MSB first.

### WRITE MODE

To write to a register, the  $R/\overline{W}$  bit should be 0. The three address bits in the input register (see Table 9) then determine the register to update. The address bits (A2 to A0) should be 001 to write to the DAC input register or 111 to write to the control register. Data is clocked into the selected register during the remaining 12 clocks of the same frame. Figure 3 shows a timing diagram of a typical AD5501 write sequence. The write sequence begins by bringing the SYNC line low. Data on the SDI line is clocked into the 16-bit shift register on the rising edge of SCLK. On the 16th falling clock edge, the last data bit is clocked in and the programmed function is executed (that is, a change in the selected DAC input register or a change in the mode of operation). The AD5501 does not require a continuous SCLK and dynamic power can be saved by transmitting clock pulses during a serial write only. At this stage, the SYNC line can be kept low or be brought high. In either case, it must be brought high for a minimum of 20 ns before the next write sequence for a falling edge of SYNC to initiate the next write sequence. Operate all interface pins close to the supply rails to minimize power consumption in the digital input buffers.

#### **READ MODE**

The AD5501 allows data readback via the serial interface from the DAC input register and the control register. To read back a register, it is first necessary to tell the AD5501 that a readback is required. This is achieved by setting the R/W bit to 1. The three address bits then determine the register from which data is to be read back. Data from the selected register is clocked out of the SDO pin on the next 12 clocks of the same frame.

The SDO pin is normally three-stated but becomes driven on the rising edge of the fifth clock pulse. The pin remains driven until the data from the register has been clocked out or the  $\overline{\text{SYNC}}$  pin is returned high. Figure 4 shows the timing requirements during a read operation. Note that due to timing requirements of  $t_{14}$  (110 ns), the maximum speed of the SPI interface during a read operation should not exceed 9 MHz.

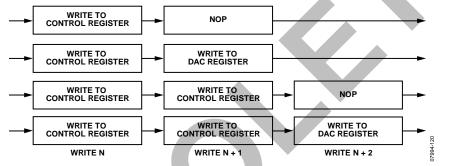

### WRITING TO THE CONTROL REGISTER

The control register is written when Bits[DB14:DB12] are 1. The control register sets the power-up state of the DAC output. A write to the control register must be followed by another write operation. The second write operation can be a write to a DAC input register or a NOP write. Figure 17 shows some typical combinations.

| Table 8. I | Input Re | gister Bi | t Map |      |      |     |     |     |     |     |     |     |     |     |     |

|------------|----------|-----------|-------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| DB15       | DB14     | DB13      | DB12  | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

| R/W        | A2       | A1        | A0    |      | Data |     |     |     |     |     |     |     |     |     |     |

| Bit        | Description                                                                           |    |    |                    |  |  |  |  |

|------------|---------------------------------------------------------------------------------------|----|----|--------------------|--|--|--|--|

| R/W        | Indicates a read from or a write to the addressed register.                           |    |    |                    |  |  |  |  |

| A2, A1, A0 | These bits determine if the input register or the control register is to be accessed. |    |    |                    |  |  |  |  |

|            | A2                                                                                    | A1 | AO | Function           |  |  |  |  |

|            | 0                                                                                     | 0  | 0  | NOP <sup>1</sup>   |  |  |  |  |

|            | 0                                                                                     | 0  | 1  | DAC input register |  |  |  |  |

|            | 0                                                                                     | 1  | 0  | Reserved           |  |  |  |  |

|            | 0                                                                                     | 1  | 1  | Reserved           |  |  |  |  |

|            | 1                                                                                     | 0  | 0  | Reserved           |  |  |  |  |

|            | 1                                                                                     | 0  | 1  | Reserved           |  |  |  |  |

|            | 1                                                                                     | 1  | 0  | Reserved           |  |  |  |  |

|            | 1                                                                                     | 1  | 1  | Control register   |  |  |  |  |

| D11:D0     | Data bits.                                                                            |    |    |                    |  |  |  |  |

#### Table 9. Input Register Bit Functions

<sup>1</sup> No operation command

#### Table 10. Control Register Functions Bit Map

| DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 <sup>1</sup> |

|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------------------|

| R/W  | 1    | 1    | 1    | 0    | 0    | 0   | 0   | 0   | C6  | C5  | C4  | C3  | C2  | C1  | C0               |

<sup>1</sup> Read only bit. This bit should be 0 when writing to the control register

#### Table 11. Control Register Function Bit Descriptions

| Bit No. | Bit Name | Description                                                                          |

|---------|----------|--------------------------------------------------------------------------------------|

| DB0     | C0       | C0 = 0: the device is not in thermal shutdown mode.                                  |

|         |          | C0 = 1: the thermal shutdown mode is activated.                                      |

| DB1     | C1       | C1 = 0: reserved. This bit should be 0 when writing to the control register.         |

| DB2     | C2       | C2 = 0: DAC channel power-down (default).                                            |

|         |          | C2 = 1: DAC channel power-up.                                                        |

| DB[3:5] | C3 to C5 | C3 to C5 = 0: reserved. These bits should be 0 when writing to the control register. |

| DB6     | C6       | C6 = 0: output connected to AGND through a 20 k $\Omega$ resistor.                   |

|         |          | C6 = 1: output is three-stated (default).                                            |

Figure 17. Control Register Write Sequences

#### **INTERFACING EXAMPLES**

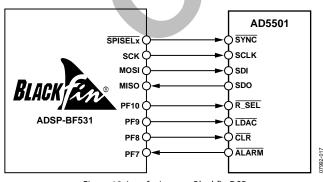

The SPI interface of the AD5501 is designed to allow it to be easily connected to industry-standard DSPs and microcontrollers. Figure 18 shows how the AD5501 can be connected to the Analog Devices, Inc., Black*fin*<sup>\*</sup> DSP. The Black*fin* has an integrated SPI port that can be connected directly to the SPI pins of the AD5501. Programmable input/output pins are also available and can be used to read or set the state of the digital input or output pins associated with the interface.

Figure 18. Interfacing to a Blackfin DSP

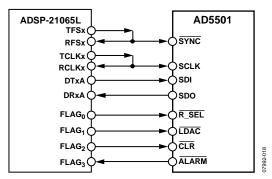

The Analog Devices ADSP-21065L is a floating point DSP with two serial ports (SPORTs). Figure 19 shows how one SPORT can be used to control the AD5501. In this example, the transmit frame synchronization (TFS) pin is connected to the receive frame synchronization (RFS) pin. The transmit and receive clocks (TCLK and RCLK) are also connected together. The user can write to the AD5501 by writing to the transmit register. When a read operation is performed, the data is clocked out of the AD5501 on the last 12 SCLKs. The DSP receive interrupt can be used to indicate when the read operation is complete.

Figure 19. Interfacing to an ADSP-21065L DSP

# **OUTLINE DIMENSIONS**

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                               | Package Option |

|--------------------|-------------------|---------------------------------------------------|----------------|

| AD5501BRUZ         | -40°C to +105°C   | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| AD5501BRUZ-REEL    | -40°C to +105°C   | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| EVAL-AD5501EBZ     |                   | Evaluation Board                                  |                |

$^{1}$  Z = RoHS Compliant Part.

# AD5501

# NOTES

# NOTES

# AD5501

# NOTES

www.analog.com

©2009-2012 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D07992-0-12/12(C)

Rev. C | Page 20 of 20

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Data Conversion IC Development Tools category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below :

EVAL-AD5063EBZ EVAL-AD5422LFEBZ EVAL-AD7265EDZ EVAL-AD7641EDZ EVAL-AD7674EDZ EVAL-AD7719EBZ EVAL-AD7767-1EDZ EVAL-AD7995EBZ AD9114-DPG2-EBZ AD9211-200EBZ AD9251-20EBZ AD9251-65EBZ AD9255-125EBZ AD9284-250EBZ AD9613-170EBZ AD9627-125EBZ AD9629-20EBZ AD9709-EBZ AD9716-DPG2-EBZ AD9737A-EBZ AD9787-DPG2-EBZ AD9993-EBZ DAC8555EVM ADS5482EVM ADS8372EVM EVAL-AD5061EBZ EVAL-AD5062EBZ EVAL-AD5443-DBRDZ EVAL-AD5570SDZ EVAL-AD7450ASDZ EVAL-AD7677EDZ EVAL-AD7992EBZ EVAL-AD7994EBZ AD9119-MIX-EBZ AD9148-M5375-EBZ AD9204-80EBZ AD9233-125EBZ AD9265-105EBZ AD9265-80EBZ AD9608-125EBZ AD9629-80EBZ AD9648-125EBZ AD9649-20EBZ AD9650-80EBZ AD9765-EBZ AD9767-EBZ AD9778A-DPG2-EBZ ADS8322EVM LM96080EB/NOPB EVAL-AD5445SDZ