# 16-Channel, 16-Bit/12-Bit Voltage Output denseDACs

Data Sheet AD5766/AD5767

#### **FEATURES**

Complete 16-channel, 12-bit/16-bit DACs

8 software-programmable output ranges: -20 V to 0 V,

- -16 V to 0 V, -10 V to 0 V, -10 V to +6 V, -12 V to +14 V,

- -16 V to +10 V, ±5 V and ±10 V

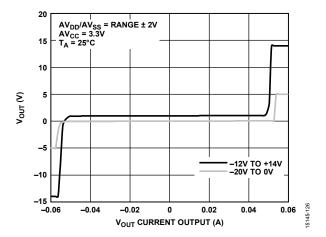

Integrated DAC output buffers with ±20 mA output current capability

4 mm  $\times$  4 mm WLCSP package and 40-lead LFCSP package Integrated reference buffers

2 dither signal input pins

**Channel monitoring multiplexer**

1.8 V logic compatibility

Temperature range: -40°C to +105°C

#### **APPLICATIONS**

Mach Zehnder modulator bias control

Optical networking

Instrumentation

Industrial automation

Data acquisition systems

Analog output modules

#### **GENERAL DESCRIPTION**

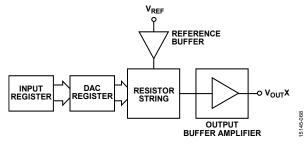

The AD5766/AD5767 are 16-channel, 16-bit/12-bit, voltage output denseDAC\* digital-to-analog converters (DACs).

The DACs generate output voltage ranges from an external 2.5 V reference. Depending on the voltage range selected, the midpoint of the output span can be adjusted, allowing a minimum output

voltage as low as -20 V or a maximum output voltage of up to +14 V. Each of the 16 channels can be monitored with an integrated output voltage multiplexer.

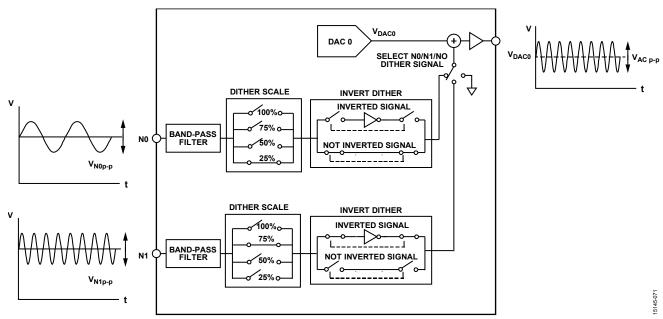

The AD5766/AD5767 have integrated output buffers that can sink or source up to 20 mA. In conjunction with these buffers, a low frequency signal can be superimposed onto each DAC output via dedicated dither pins. These dedicated dither pins simplify the system design by reducing the number of external components required for a similar external implementation, like operational amplifiers or resistors. The reduction of external components makes the AD5766/AD5767 suitable for indium phosphide Mach Zehnder modulator (InP MZM) biasing applications.

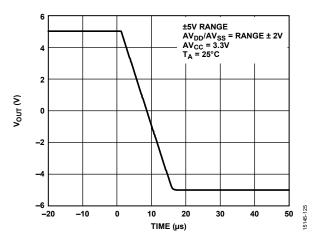

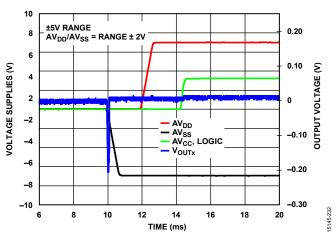

The devices incorporate a power-on reset (POR) circuit that ensures that the DAC outputs are clamped to ground on power up and remain at this level until the output range of the DAC is configured. The outputs of all DACs are updated through register configuration, with the added functionality of user-selectable DAC channels to be simultaneously updated.

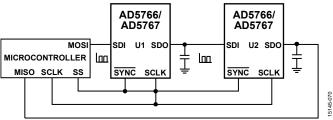

The AD5766/AD5767 use a versatile 4-wire serial interface that operates at clock rates of up to 50 MHz for write mode and is compatible with serial peripheral interface (SPI), QSPI $^{\text{\tiny MS}}$ , MICROWIRE $^{\text{\tiny MS}}$ , and DSP interface standards. The AD5766/AD5767 also contain a  $V_{\text{LOGIC}}$  pin intended for 1.8 V/3.3 V/5 V logic.

The AD5766/AD5767 are available in a 4 mm  $\times$  4 mm WLCSP package and a 40-lead LFCSP package. The AD5766/AD5767 operate at a temperature range of  $-40^{\circ}$ C to  $+105^{\circ}$ C.

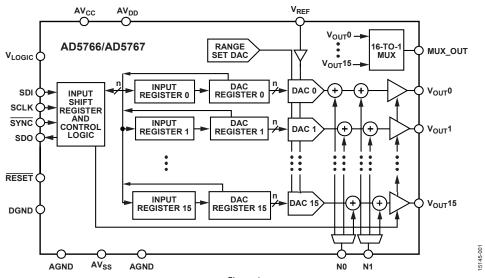

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

Rev. C

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

# **TABLE OF CONTENTS**

| Features                                     | 1  |

|----------------------------------------------|----|

| Applications                                 | 1  |

| General Description                          | 1  |

| Functional Block Diagram                     | 1  |

| Revision History                             | 3  |

| Specifications                               | 4  |

| AC Performance Characteristics               | 8  |

| Timing Characteristics                       | 9  |

| Absolute Maximum Ratings                     | 11 |

| Thermal Resistance                           | 11 |

| ESD Caution                                  | 11 |

| Pin Configurations and Function Descriptions | 12 |

| Typical Performance Characteristics          | 16 |

| Dither Characteristics                       | 25 |

| Terminology                                  | 27 |

| Theory of Operation                          | 29 |

| Digital-to-Analog Converter                  | 29 |

| DAC Architecture                             | 29 |

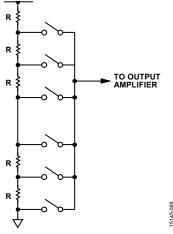

| Resistor String                              | 29 |

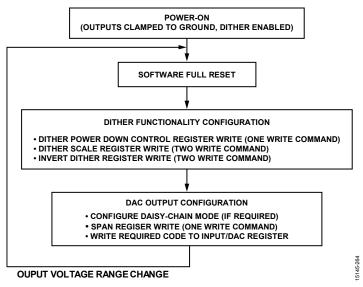

| Power-On Reset (POR)                         | 29 |

| Dither                                       | 31 |

| Dither Power-Down Mode                       | 31 |

| Monitor Mux                                  | 31 |

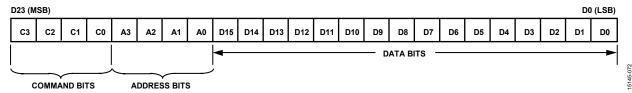

| Serial Interface                             | 32 |

| Register Details                                |

|-------------------------------------------------|

| Input Shift Register                            |

| Monitor Mux Control34                           |

| No Operation35                                  |

| Daisy-Chain Mode35                              |

| Write and Update Commands35                     |

| Span Register36                                 |

| Dither Power Control Register36                 |

| Write Input Data to All DAC Registers36         |

| Software Full Reset                             |

| Select Register for Readback                    |

| Apply N0 or N1 Dither Signal to DACs Register38 |

| Dither Scale                                    |

| Invert Dither Register                          |

| Applications Information                        |

| Dither Configuration                            |

| Thermal Considerations                          |

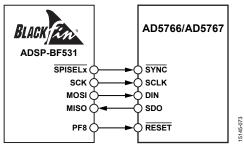

| Microprocessor Interfacing                      |

| AD5766/AD5767 to SPI Interface                  |

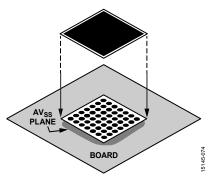

| Layout Guidelines                               |

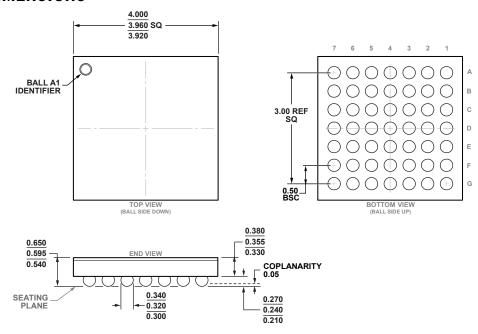

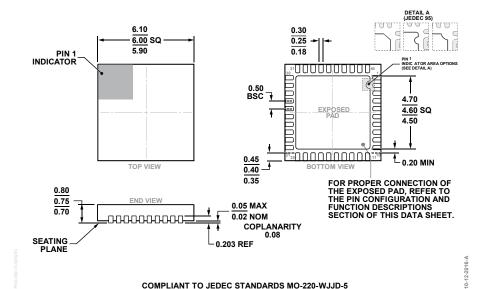

| Outline Dimensions                              |

| Ordering Guide                                  |

#### **REVISION HISTORY**

| 1/2018—Rev. B to Rev. C                                                         |   |

|---------------------------------------------------------------------------------|---|

| Changes to Output Voltage Settling Time Parameter, Table 3                      | 3 |

| Changes to Figure 614                                                           | ł |

| Changes to Figure 1116                                                          | ó |

| Changes to Figure 1317                                                          | 7 |

| Changes to Figure 3721                                                          | Ĺ |

| Change to Terminology Section27                                                 |   |

| Changes to Figure 7232                                                          | 2 |

| Changes to Ordering Guide43                                                     | 3 |

| 10/2017—Rev. A to Rev. B                                                        |   |

| Added AD5766Universa                                                            | l |

| Changes to Features Section, Applications Section, and                          |   |

| General Description Section                                                     | L |

| Changes to Table 14                                                             |   |

| Added Table 2; Renumbered Sequentially                                          |   |

| Changes to Table 3                                                              |   |

| Changes to t <sub>14</sub> and t <sub>15</sub> Parameters, Table 4 and Figure 2 |   |

| Changes to Figure 410                                                           |   |

| Change to AV <sub>CC</sub> Pin Description, Table 713                           |   |

| Change to AV <sub>CC</sub> Pin Description, Table 815                           | ; |

| Changes to Figure 7 to Figure 1216                                              |   |

| Changes to Figure 13 to Figure 1817                                             |   |

| Deleted Figure 30; Renumbered Sequentially17                                    |   |

| Added Figure 19 to Figure 24; Renumbered Sequentially18                         | 3 |

| Added Figure 29 and Figure 3019                                                 |   |

| Added Figure 31 to Figure 3620                                                  | ) |

| Added Figure 37 to Figure 4221                                                  |   |

| Added Figure 43 and Figure 4622                                                 | 2 |

| Changes to Figure 4923                                                          | 3 |

| Added Figure 50 to Figure 5423                                                  | 3 |

| Changes to Figure 5624                                                          | ł |

| Added Figure 6726                                                               | ó |

| Changes to Digital-to-Analog Converter Section, DAC                             |   |

| Architecture Section, and Power-On Reset (POR) Section29                        | ) |

| Added Figure 7030                                                               | ) |

| Changes to Dither Section and Dither Power-Down Mode                            |   |

| Section31                                                                       |   |

| Changes to Table 1033                                                           | 3 |

| Added Table 17 and Table 1935                                                   | ; |

| Changes to Dither Power Control Register Section, Table 26, Write               |   |

| Input Data to All DAC Registers Section, and Table 2836                         | í |

| Changes to Table 32 and Table 33                    | 37        |

|-----------------------------------------------------|-----------|

| Changes to Dither Configuration Section             |           |

| Updated Outline Dimensions                          |           |

| Changes to Ordering Guide                           |           |

| 4/2017—Rev. 0 to Rev. A                             |           |

| Added 40-Lead LFCSP Package                         | Universal |

| Changes to Features                                 |           |

| Changes to General Description                      | 1         |

| Changes to Functional Block Diagram, Figure 1       | 1         |

| Added Figure 6 and Added Table 7; Renumbered        |           |

| Sequentially                                        | 12        |

| Changes to Figure 23 and Figure 24                  | 16        |

| Added Figure 26                                     |           |

| Changes to Figure 28 and Figure 29                  | 17        |

| Changes to Dither DC Shift Section                  |           |

| Changes to Figure 43, Caption Only                  | 23        |

| Changes to Input Shift Register Section and Table 9 | 25        |

| Changes to Table 18                                 |           |

| Changes to Thermal Considerations Section           |           |

| Changes to Layout Guidelines Section and Added Figu |           |

| Updated Outline Dimensions                          |           |

| Changes to Ordering Guide                           | 35        |

#### 1/2017—Revision 0: Initial Version

# **SPECIFICATIONS**

$AV_{CC} = 2.97 \text{ V}$  to 3.6 V,  $V_{LOGIC} = 1.7 \text{ V}$  to 5.5 V,  $AV_{DD} = 2.97 \text{ V}$  to 16 V,  $AV_{SS} = -22 \text{ V}$  to -7 V, AGND = DGND = 0 V,  $V_{REF} = 2.5 \text{ V}$ , output range =  $\pm 5 \text{ V}$ ,  $V_{OUTX}$  unloaded, all specifications  $T_{MIN}$  to  $T_{MAX}$ , typical specifications at  $T_A = 25^{\circ}\text{C}$ , dither powered on, unless otherwise noted.

Table 1.

| Parameter                                          | Min  | Тур   | Max  | Unit       | Test Conditions/Comments       |

|----------------------------------------------------|------|-------|------|------------|--------------------------------|

| STATIC PERFORMANCE                                 |      |       |      |            |                                |

| Resolution                                         | 16   |       |      | Bits       | AD5766                         |

|                                                    | 12   |       |      | Bits       | AD5767                         |

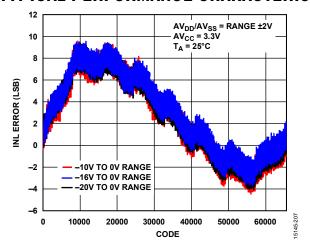

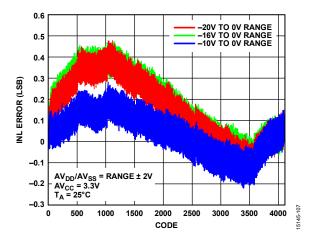

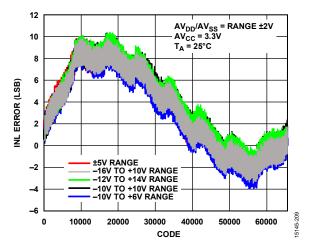

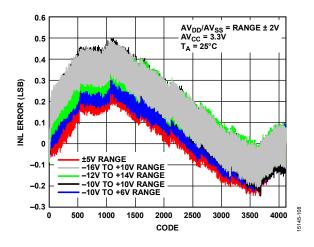

| Relative Accuracy (INL)                            |      |       |      |            |                                |

| AD5766                                             | -16  |       | +16  | LSB        |                                |

| AD5767                                             | -1   |       | +1   | LSB        |                                |

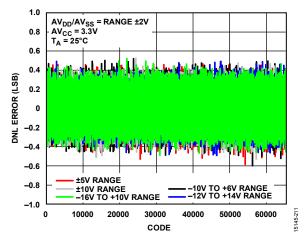

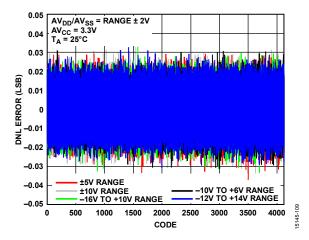

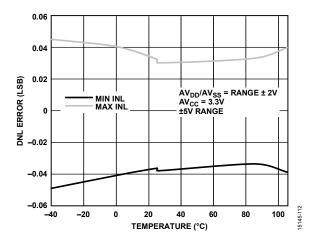

| Differential Nonlinearity                          | -1   |       | +1   | LSB        | Guaranteed monotonic by design |

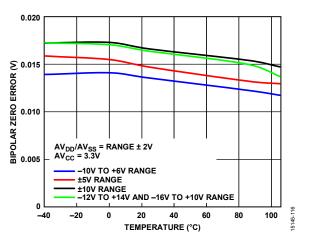

| Bipolar Zero Error                                 | -85  | ±12   | +85  | mV         | ±5 V range                     |

|                                                    | -110 | ±13   | +110 | mV         | -10 V to +6 V range            |

|                                                    | -120 | ±15   | +120 | mV         | ±10 V range                    |

|                                                    | -145 | ±16   | +145 | mV         | -12 V to +14 V range           |

|                                                    | -145 | ±16   | +145 | mV         | -16 V to +10 V range           |

| Bipolar Zero Error Temperature<br>Coefficient (TC) |      | ±2    |      | ppm FSR/°C |                                |

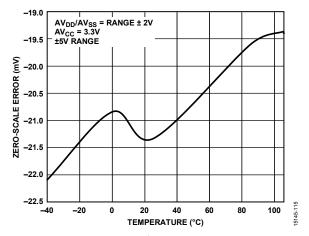

| Zero-Scale Error                                   |      |       |      |            | All 0s loaded to DAC register  |

|                                                    | -80  | ±25   | +80  | mV         | -10 V to 0 V range             |

|                                                    | -80  | ±25   | +80  | mV         | ±5 V range                     |

|                                                    | -110 | ±35   | +110 | mV         | -16 V to 0 V range             |

|                                                    | -110 | ±35   | +110 | mV         | –10 V to +6 V range            |

|                                                    | -130 | ±35   | +130 | mV         | -20 V to 0 V range             |

|                                                    | -130 | ±35   | +130 | mV         | ±10 V range                    |

|                                                    | -140 | ±45   | +140 | mV         | -12 V to +14 V range           |

|                                                    | -140 | ±45   | +140 | mV         | -16 V to +10 V range           |

| Zero-Scale Error Temperature<br>Coefficient (TC)   |      | ±2    |      | ppm FSR/°C |                                |

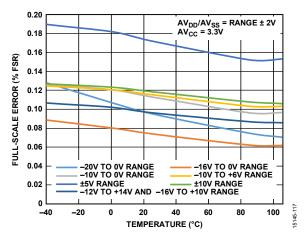

| Full-Scale Error                                   |      |       |      |            | All 1s loaded to DAC register. |

|                                                    | -0.9 | ±0.23 | +0.9 | % FSR      | -10 V to 0 V range             |

|                                                    | -0.9 | ±0.23 | +0.9 | % FSR      | ±5 V range                     |

|                                                    | -0.8 | ±0.2  | +0.8 | % FSR      | -16 V to 0 V range             |

|                                                    | -0.8 | ±0.2  | +0.8 | % FSR      | −10 V to +6 V range            |

|                                                    | -0.7 | ±0.18 | +0.7 | % FSR      | -20 V to 0 V range             |

|                                                    | -0.7 | ±0.18 | +0.7 | % FSR      | ±10 V range                    |

|                                                    | -0.6 | ±0.15 | +0.6 | % FSR      | -12 V to +14 V range           |

|                                                    | -0.6 | ±0.15 | +0.6 | % FSR      | -16 V to +10 V range           |

| Full-Scale Error Drift                             |      | ±3    |      | ppm FSR/°C |                                |

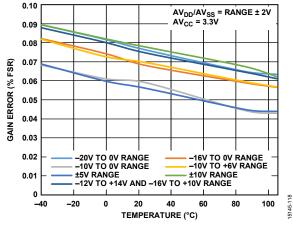

| Gain Error                                         | -0.4 | ±0.07 | +0.4 | % FSR      |                                |

| Gain Error Temperature<br>Coefficient (TC)         |      | ±2    |      | ppm FSR/°C |                                |

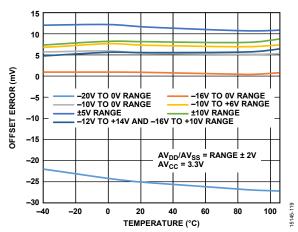

| Offset Error                                       | -80  | ±25   | +80  | mV         | -10 V to 0 V range             |

|                                                    | -80  | ±25   | +80  | mV         | ±5 V range                     |

|                                                    | -110 | ±35   | +110 | mV         | –16 V to 0 V range             |

|                                                    | -110 | ±35   | +110 | mV         | –10 V to +6 V range            |

|                                                    | -130 | ±35   | +130 | mV         | –20 V to 0 V range             |

|                                                    | -130 | ±35   | +130 | mV         | ±10 V range                    |

|                                                    | -140 | ±45   | +140 | mV         | –12 V to +14 V range           |

|                                                    | -140 | ±45   | +140 | mV         | –16 V to +10 V range           |

| Offset Error Drift                                 |      | ±2    |      | μV/°C      |                                |

| Parameter                           | Min                    | Тур        | Max                    | Unit       | Test Conditions/Comments                                                                       |

|-------------------------------------|------------------------|------------|------------------------|------------|------------------------------------------------------------------------------------------------|

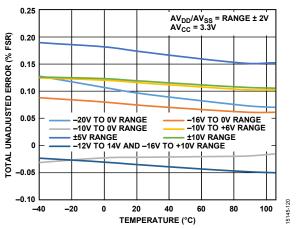

| Total Unadjusted Error              | -0.9                   | ±0.18      | +0.9                   | %FSR       | -10 V to 0 V range                                                                             |

|                                     | -0.9                   | ±0.18      | +0.9                   | %FSR       | ±5 V range                                                                                     |

|                                     | -0.8                   | ±0.15      | +0.8                   | %FSR       | -16 V to 0 V range                                                                             |

|                                     | -0.8                   | ±0.15      | +0.8                   | %FSR       | −10 V to +6 V range                                                                            |

|                                     | -0.7                   | ±0.13      | +0.7                   | %FSR       | -20 V to 0 V range                                                                             |

|                                     | -0.7                   | ±0.13      | +0.7                   | %FSR       | ±10 V range                                                                                    |

|                                     | -0.6                   | ±0.12      | +0.6                   | %FSR       | -12 V to +14 V range                                                                           |

|                                     | -0.6                   | ±0.12      | +0.6                   | %FSR       | -16 V to +10 V range                                                                           |

| DC Crosstalk                        |                        | 30         |                        | μV         | Due to output voltage change                                                                   |

|                                     |                        | 35         |                        | μV/mA      | Due to load current change (1 LSB)                                                             |

| OUTPUT CHARACTERISTICS              |                        |            |                        |            |                                                                                                |

| Output Voltage Ranges1              | -20                    |            | 0                      | V          |                                                                                                |

| . 3 3                               | -16                    |            | 0                      | V          |                                                                                                |

|                                     | -10                    |            | 0                      | V          |                                                                                                |

|                                     | -10                    |            | +6                     | V          |                                                                                                |

|                                     | -12                    |            | +14                    | V          |                                                                                                |

|                                     | -16                    |            | +10                    | V          |                                                                                                |

|                                     | _5                     |            | +5                     | V          |                                                                                                |

|                                     | -10                    |            | +10                    | V          |                                                                                                |

| Output Current                      | -10<br>-20             |            | +20                    | mA         | Refer to the Thermal Considerations section                                                    |

| Capacitive Load Stability           | -20                    |            | 1                      | nF         | Neier to the memal considerations section                                                      |

| DC Output Impedance                 |                        | 0.2        | 1                      | Ω          |                                                                                                |

| Short-Circuit Current               |                        |            |                        |            | Cinale shannel entre                                                                           |

|                                     |                        | ±60        |                        | mA         | Single channel only                                                                            |

| Output Amplifier Bandwidth          |                        | 108        |                        | kHz        |                                                                                                |

| REFERENCE INPUT                     |                        | 2.5        |                        |            | 110/ 6-11-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-                                                   |

| Reference Input Voltage             | 2 275                  | 2.5        | 2.625                  | V          | ±1% for specified performance                                                                  |

| Reference Range                     | 2.375                  |            | 2.625                  | V          | Functional performance only                                                                    |

| DC Input Impedance                  | 2.5                    |            |                        | ΜΩ         |                                                                                                |

| Input Current                       |                        |            | 1                      | μΑ         |                                                                                                |

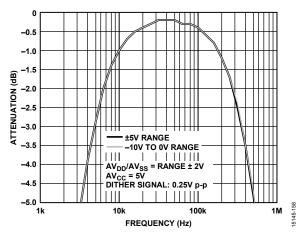

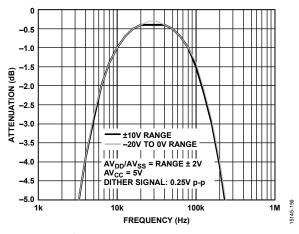

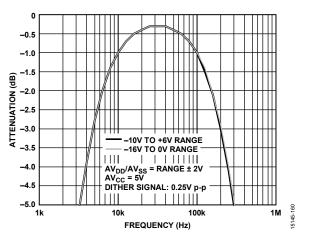

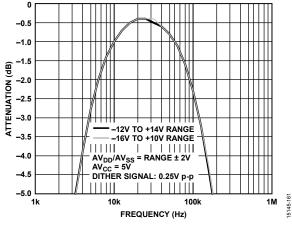

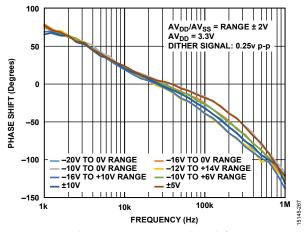

| DITHER INPUTS                       |                        |            |                        |            | For dither input to DAC output attenuation, see Figure 62 to Figure 65 for typical performance |

| Dithor Fraguency                    |                        | 10         |                        | kHz        | Lower –3 dB point                                                                              |

| Dither Frequency                    |                        | 100        |                        | kHz        | Upper –3 dB point                                                                              |

| Amplitudo                           |                        | 100        | 0.25                   |            | Peak-to-peak ac voltage                                                                        |

| Amplitude                           |                        |            |                        | V p-p<br>V | Peak-to-peak ac voltage  Peak-to-peak ac and dc voltage                                        |

| DC Chiff                            | 0                      |            | $AV_CC$                | V          | ,                                                                                              |

| DC Shift                            | 2                      | . 1        | . 2                    | LCD        | See the Terminology section                                                                    |

| AD5766                              | -2                     | ±1         | +2                     | LSB        |                                                                                                |

| AD5767                              | -1                     | ±0.063     | +1                     | LSB        | Dish an analala didicalala di Nio and Nii flactica                                             |

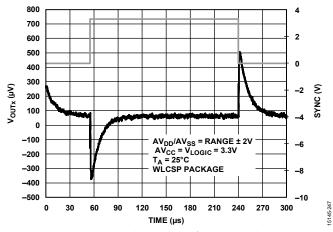

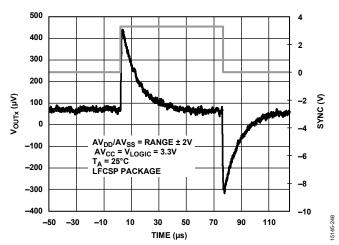

| Dither Transient                    |                        | _          |                        | .,         | Dither enabled/disabled, N0 and N1 floating                                                    |

| Dither Selected Channel             |                        | 5          |                        | nV-sec     | $AV_{CC} = 2.97 \text{ V} \text{ and } AV_{CC} = 3.6 \text{ V}$                                |

| Dither Nonselected Channels         |                        | 2          |                        | nV-sec     | $AV_{CC} = 2.97 \text{ V}$ and $AV_{CC} = 3.6 \text{ V}$                                       |

| Dither Crosstalk <sup>1</sup>       |                        | -70<br>-5  |                        | dB         | 10 kHz dither frequency                                                                        |

| LOCIC INDUTE                        |                        | <b>-55</b> |                        | dB         | 100 kHz dither frequency                                                                       |

| LOGIC INPUTS                        |                        |            |                        | l .,       |                                                                                                |

| Input High Voltage, V <sub>IH</sub> | $0.7 \times V_{LOGIC}$ |            |                        | V          |                                                                                                |

| Input Low Voltage, V <sub>I</sub> L |                        |            | $0.3 \times V_{LOGIC}$ | V          |                                                                                                |

| Input Current                       | -2                     |            | +2                     | μΑ         | Per pin                                                                                        |

|                                     | -6                     |            | +6                     | μΑ         | RESET pin pulled high                                                                          |

|                                     | -57                    |            | +57                    | μΑ         | RESET pin pulled low                                                                           |

| Input Capacitance                   | 1                      | 2          |                        | pF         | Per pin                                                                                        |

| Parameter                                 | Min                      | Тур       | Max       | Unit   | Test Conditions/Comments                                                                                     |

|-------------------------------------------|--------------------------|-----------|-----------|--------|--------------------------------------------------------------------------------------------------------------|

| LOGIC OUTPUT                              |                          |           |           |        |                                                                                                              |

| Output Low Voltage                        |                          |           | 0.4       | V      | Sinking 200 μA                                                                                               |

| Output High Voltage                       | V <sub>LOGIC</sub> – 0.4 | 4         |           | V      | Sourcing 200 μA                                                                                              |

| High Impedance Leakage<br>Current         | -1                       |           | +1        | μΑ     |                                                                                                              |

| High Impedance Output<br>Capacitance      |                          | 5         |           | pF     |                                                                                                              |

| VOLTAGE MONITOR PIN (MUX_OUT)             |                          |           |           |        |                                                                                                              |

| Impedance                                 |                          | 1.3       |           | kΩ     |                                                                                                              |

| Three-State Leakage Current               | -1                       | 0.006     | +1        | μΑ     |                                                                                                              |

| Continuous Current                        | -1                       |           | +1        | mA     | Die temperature below 105°C                                                                                  |

| Glitch Impulse                            |                          | 0.2       |           | nV-sec | V <sub>O∪T</sub> x glitch due to mux enable                                                                  |

| Voltage Settling Time                     |                          | 12        |           | μs     | $1/4$ to $3/4$ scale settling to $\pm 0.5$ LSB, $\pm 5$ V range and $-10$ V to $0$ V range                   |

| POWER SUPPLIES                            |                          |           |           |        |                                                                                                              |

| $AV_DD$                                   | 2.97                     |           | 16        | V      | $AV_{DD}$ – $AV_{SS}$ must be less than or equal to 30 V                                                     |

| $AV_{SS}$                                 | -22                      |           | <b>-7</b> | V      | $AV_{DD}$ – $AV_{SS}$ must be less than or equal to 30 V                                                     |

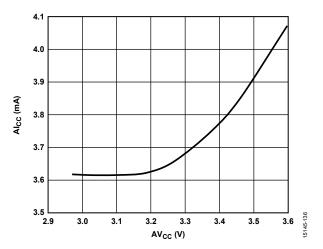

| $AV_CC$                                   | 2.97                     |           | 3.6       | V      |                                                                                                              |

| $V_{LOGIC}$                               | 1.7                      |           | 5.5       | V      |                                                                                                              |

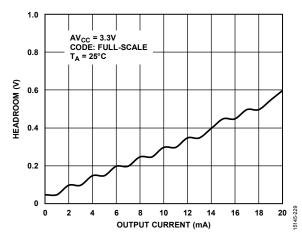

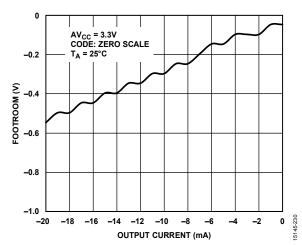

| Headroom/Footroom                         |                          | ±0.7      |           | V      | Output voltage offset to ±2 LSB for 20 mA output load; applies to AV <sub>DD</sub> and AV <sub>SS</sub>      |

|                                           |                          | ±2        |           | V      | Output voltage offset to $\pm 1$ LSB for 20 mA output load; applies to AV <sub>DD</sub> and AV <sub>SS</sub> |

| Normal Mode                               |                          |           |           |        |                                                                                                              |

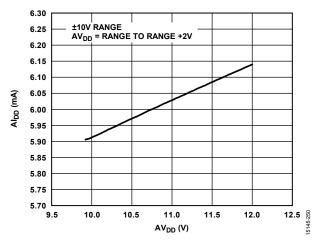

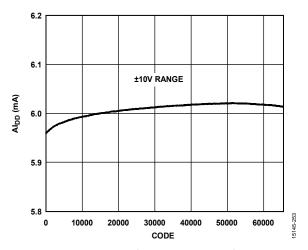

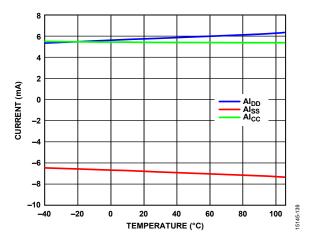

| $AI_DD$                                   |                          | 6         | 9         | mA     | All output ranges, -40°C to +105°C                                                                           |

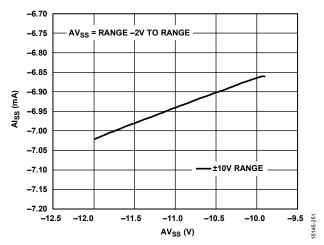

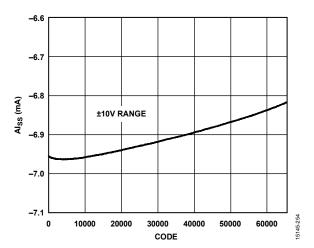

| Alss                                      | -11                      | <b>-9</b> |           | mA     | All output ranges, -40°C to +105°C                                                                           |

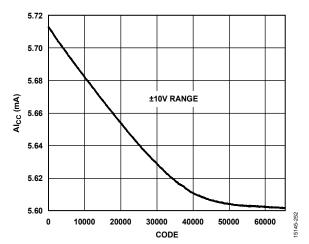

| $AI_CC$                                   |                          | 8.3       | 10        | mA     | All output ranges, -40°C to +105°C                                                                           |

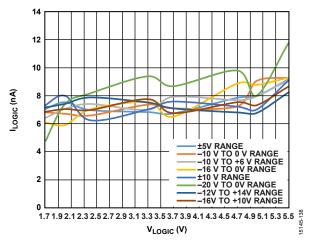

| ILOGIC                                    |                          | 0.02      | 1         | μΑ     | All output ranges, $-40^{\circ}$ C to $+105^{\circ}$ C,<br>$V_{IH} = V_{LOGIC}$ , $V_{IL} = DGND$            |

| DC Power Supply Rejection<br>Ratio (PSRR) |                          | 50        |           | μV/V   | AV <sub>DD</sub> power supply                                                                                |

|                                           |                          | 50        |           | μV/V   | AV <sub>SS</sub> power supply                                                                                |

|                                           |                          | 3         |           | mV/V   | AV <sub>CC</sub> power supply                                                                                |

| AC Power Supply Rejection<br>Ratio (PSRR) |                          | -80       |           | dB     | AV <sub>DD</sub> power supply, at 50 Hz                                                                      |

|                                           |                          | -80       |           | dB     | AVss power supply, at 50 Hz                                                                                  |

|                                           |                          | -50       |           | dB     | AV <sub>cc</sub> power supply, at 50 Hz                                                                      |

$<sup>^{\</sup>rm 1}$  Output amplifier headroom requirement is 2 V minimum.

$AV_{CC} = 2.97 \text{ V}$  to 3.6 V,  $V_{LOGIC} = 1.7 \text{ V}$  to 5.5 V,  $AV_{DD} = 2.97 \text{ V}$  to 16 V,  $AV_{SS} = -22 \text{ V}$  to -7 V, AGND = DGND = 0 V,  $V_{REF} = 2.5 \text{ V}$ , output range =  $\pm 5 \text{ V}$ ,  $V_{OUT}x$  unloaded, all specifications  $T_{MIN}$  to  $T_{MAX}$ , typical specifications at  $T_A = 25^{\circ}\text{C}$ , dither powered off, unless otherwise noted.

Table 2.

| Parameter              | Min  | Тур   | Max  | Unit  | Test Conditions/Comments                         |

|------------------------|------|-------|------|-------|--------------------------------------------------|

| BIPOLAR ZERO ERROR     | -50  | ±11   | +50  | mV    | ±5 V range                                       |

|                        | -75  | ±12   | +75  | mV    | −10 V to +6 V range                              |

|                        | -90  | ±12   | +90  | mV    | ±10 V range                                      |

|                        | -110 | ±13   | +110 | mV    | -12 V to +14 V range                             |

|                        | -110 | ±13   | +110 | mV    | -16 V to +10 V range                             |

| ZERO-SCALE ERROR       |      |       |      |       | All 0s loaded to DAC register                    |

|                        | -50  | ±15   | +50  | mV    | -10 V to 0 V range                               |

|                        | -50  | ±15   | +50  | mV    | ±5 V range                                       |

|                        | -75  | ±20   | +75  | mV    | -16 V to 0 V range                               |

|                        | -75  | ±20   | +75  | mV    | -10 V to +6 V range                              |

|                        | -90  | ±25   | +90  | mV    | -20 V to 0 V range                               |

|                        | -90  | ±25   | +90  | mV    | ±10 V range                                      |

|                        | -110 | ±35   | +110 | mV    | -12 V to +14 V range                             |

|                        | -110 | ±35   | +110 | mV    | -16 V to +10 V range                             |

| FULL-SCALE ERROR       | -0.5 | ±0.15 | +0.5 | % FSR | All 1s loaded to DAC register; all output ranges |

| GAIN ERROR             | -0.3 | ±0.07 | +0.3 | % FSR | All output ranges                                |

| OFFSET ERROR           | -50  | ±15   | +50  | mV    | -10 V to 0 V range                               |

|                        | -50  | ±15   | +50  | mV    | ±5 V range                                       |

|                        | -75  | ±20   | +75  | mV    | -16 V to 0 V range                               |

|                        | -75  | ±20   | +75  | mV    | −10 V to +6 V range                              |

|                        | -90  | ±25   | +90  | mV    | –20 V to 0 V range                               |

|                        | -90  | ±25   | +90  | mV    | ±10 V range                                      |

|                        | -110 | ±35   | +110 | mV    | -12 V to +14 V range                             |

|                        | -110 | ±35   | +110 | mV    | -16 V to +10 V range                             |

| TOTAL UNADJUSTED ERROR | -0.5 | ±0.12 | +0.5 | %FSR  | All output ranges                                |

#### **AC PERFORMANCE CHARACTERISTICS**

$AV_{CC} = 2.97 \text{ V} \text{ to } 3.6 \text{ V}, V_{LOGIC} = 1.7 \text{ V} \text{ to } 5.5 \text{ V}, AV_{DD} = 2.97 \text{ V} \text{ to } 15 \text{ V}, AV_{SS} = -22 \text{ V} \text{ to } -7 \text{ V}, AGND = DGND = 0 \text{ V}, V_{REF} = 2.5 \text{ V}, output$ range = -10 V to 0 V,  $V_{\text{OUTX}}$  unloaded, all specifications  $T_{\text{MIN}}$  to  $T_{\text{MAX}}$ , typical specifications at  $T_{\text{A}} = 25^{\circ}\text{C}$ , dither powered on, analog dither signals not applied, unless otherwise noted.

Table 3.

| Parameter                                  | Min Typ I  | Max Unit | Test Conditions/Comments                                                                                            |

|--------------------------------------------|------------|----------|---------------------------------------------------------------------------------------------------------------------|

| DYNAMIC PERFORMANCE <sup>1</sup>           |            |          |                                                                                                                     |

| Output Voltage Settling Time               |            |          |                                                                                                                     |

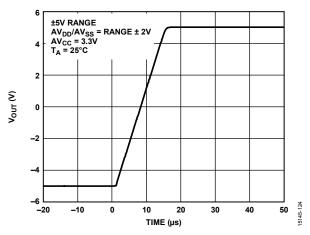

| AD5766                                     | 16         | μs       | $\frac{1}{4}$ to $\frac{3}{4}$ scale settling to $\pm 0.5$ LSB, $\pm 5$ V range, and $-10$ V to 0 V range           |

|                                            | 14         | μs       | 256 LSB step to ±0.5 LSB                                                                                            |

| AD5767                                     | 10         | μs       | $\frac{1}{4}$ to $\frac{3}{4}$ scale settling to $\pm 0.5$ LSB, $\pm 5$ V range, and $-10$ V to 0 V range           |

|                                            | 4          | μs       | 32 LSB step to ±0.5 LSB                                                                                             |

| Slew Rate                                  | 1          | V/µs     |                                                                                                                     |

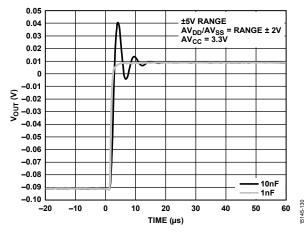

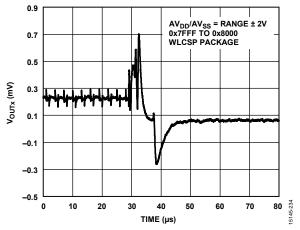

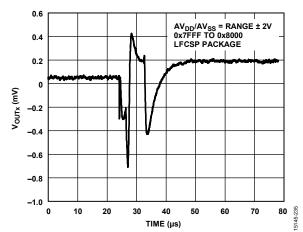

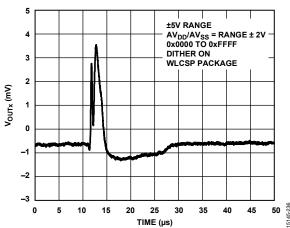

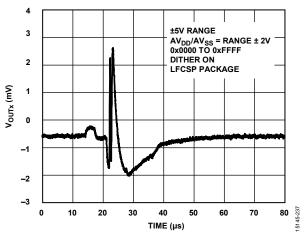

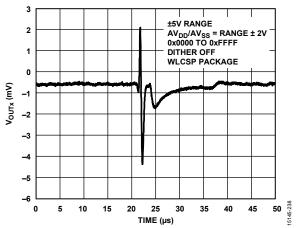

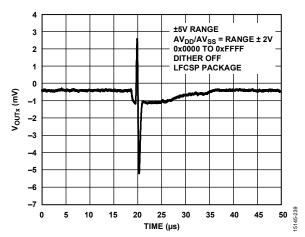

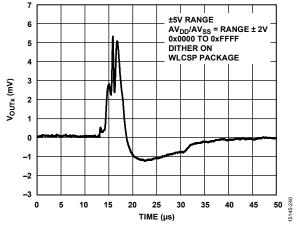

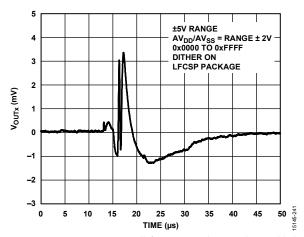

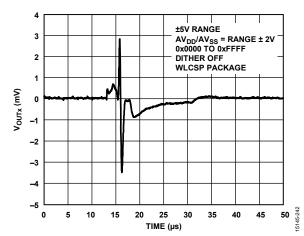

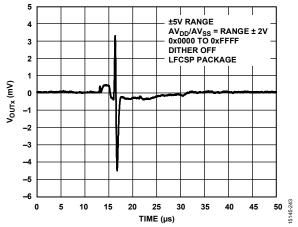

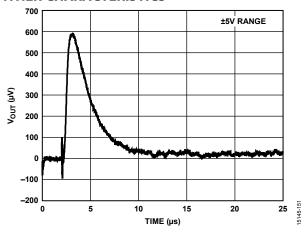

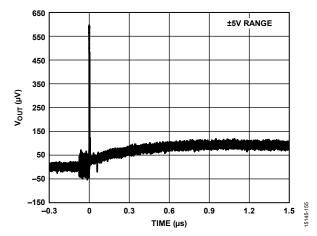

| Digital-to-Analog Glitch Energy            | 10         | nV-se    | 1 LSB change around major carry for 10 V span                                                                       |

| Glitch Impulse Peak Amplitude              | 8          | mV       |                                                                                                                     |

| Digital Feedthrough                        | 1          | nV-se    | c                                                                                                                   |

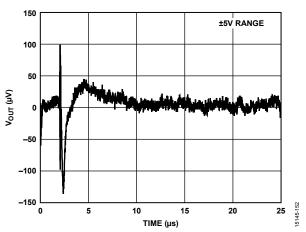

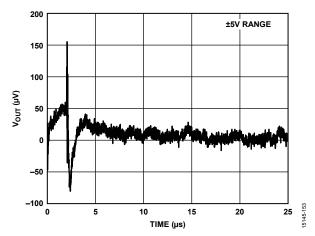

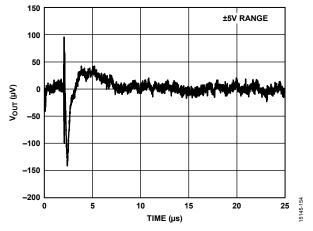

| Digital Crosstalk                          | 2          | nV-se    | oc                                                                                                                  |

| Analog Crosstalk                           | 15         | nV-se    | c                                                                                                                   |

| DAC-to-DAC Crosstalk                       | 15         | nV-se    | oc                                                                                                                  |

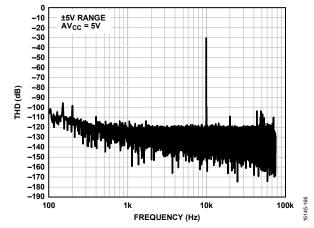

| <b>Total Harmonic Distortion</b>           | -80        | dB       | $V_{REF} = 2.5 \text{ V} \pm 0.1 \text{ V}$ p-p, frequency = 10 kHz, $AV_{CC} = 2.97 \text{ V}$ and $3.6 \text{ V}$ |

|                                            | <b>–75</b> | dB       | $V_{REF} = 2.5 \text{ V} \pm 0.1 \text{ V} \text{ p-p, frequency} = 10 \text{ kHz, } AV_{CC} = 3.6 \text{ V}$       |

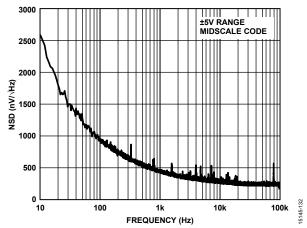

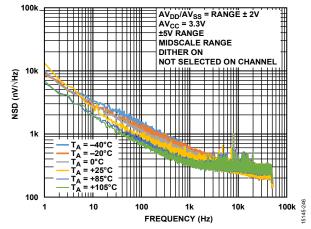

| Output Noise Spectral Density <sup>1</sup> | 375        | nV/√     | $-10 \text{ V}$ to $0 \text{ V}$ and $\pm 5 \text{ V}$ ranges, frequency = $1 \text{ kHz}$                          |

|                                            | 605        | nV/√     | -16  V to $0  V$ and $-10  V$ to $+6  V$ ranges, frequency = $1  kHz$                                               |

|                                            | 750        | nV/√     | $-20 \text{ V}$ to $0 \text{ V}$ and $\pm 10 \text{ V}$ ranges, frequency = 1 kHz                                   |

|                                            | 835        | nV/√     | -12  V to $14  V$ and $-16  V$ to $+10  V$ ranges, frequency = $1  kHz$                                             |

|                                            | 280        | nV/√     | $-10 \text{ V}$ to $0 \text{ V}$ and $\pm 5 \text{ V}$ ranges, frequency = $10 \text{ kHz}$                         |

|                                            | 440        | nV/√     | -16  V to $0  V$ and $-10  V$ to $+6  V$ ranges, frequency = $10  kHz$                                              |

|                                            | 470        | nV/√     | $-20 \text{ V}$ to $0 \text{ V}$ and $\pm 10 \text{ V}$ ranges, frequency = $10 \text{ kHz}$                        |

|                                            | 610        | nV/√     | -12  V to $14  V$ and $-16  V$ to $+10  V$ ranges, frequency = $10  kHz$                                            |

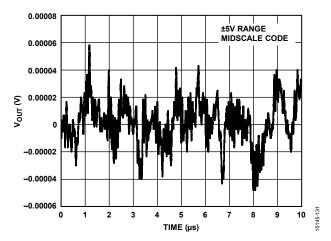

| Output Noise <sup>2</sup>                  |            |          | Dither disabled                                                                                                     |

|                                            | 20         | μV rr    | ns ±5 V range                                                                                                       |

|                                            | 23         | μV rr    | ns -10 V to 0 V range                                                                                               |

|                                            | 33         | μV rr    | ns -10 V to +6 V range                                                                                              |

|                                            | 38         | μV rr    | ns -16 V to 0 V range                                                                                               |

|                                            | 36         | μV rr    | t ±10 V range                                                                                                       |

|                                            | 45         | μV rr    | ns -20 V to 0 V range                                                                                               |

|                                            | 45         | μV rr    | ns -16 V to 10 V range                                                                                              |

|                                            | 45         | μV rr    | ns –12 V to 14 V range                                                                                              |

$<sup>^1</sup>$  DAC code = midscale. AV $_{DD}$  = V $_{OUT\_MAX}$  + 2 V. AV $_{SS}$  = V $_{OUT\_MIN}$  - 2 V.  $^2$  0.1 Hz to 10 Hz. AV $_{DD}$  = V $_{OUT\_MAX}$  + 2 V. AV $_{SS}$  = V $_{OUT\_MIN}$  - 2 V.

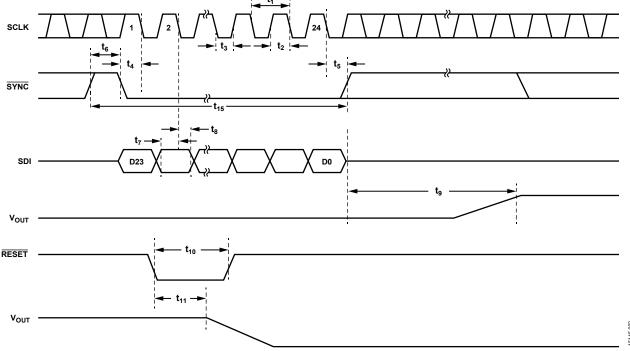

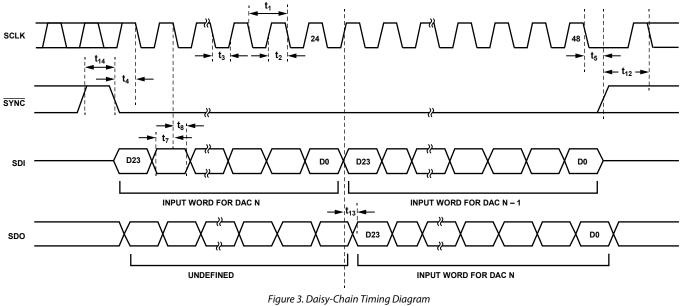

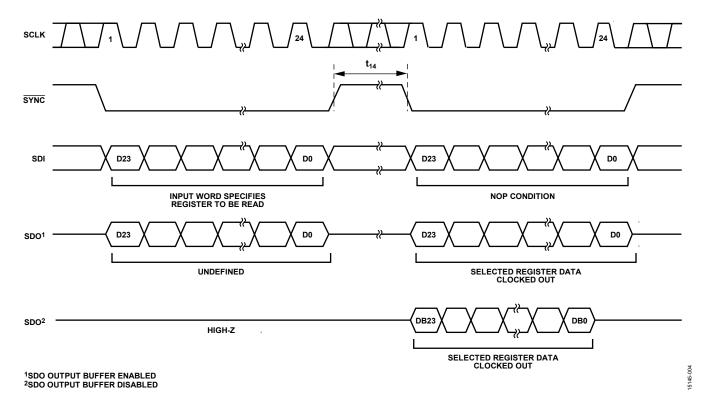

#### **TIMING CHARACTERISTICS**

All input signals are specified with  $t_R = t_F = 1$  ns/V (10% to 90% of AV<sub>DD</sub>) and timed from a voltage level of (V<sub>IL</sub> + V<sub>IH</sub>)/2. See Figure 2, Figure 3, and Figure 4. AV<sub>CC</sub> = 2.97 V to 3.6 V, V<sub>LOGIC</sub> = 1.7 V to 5.5 V, V<sub>REF</sub> = 2.5 V, all specifications  $-40^{\circ}$ C to  $+105^{\circ}$ C, dither powered on, unless otherwise noted.

Table 4.

| Parameter             | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit   | Description                                                                                |

|-----------------------|----------------------------------------------|--------|--------------------------------------------------------------------------------------------|

| t <sub>1</sub> 1      | 20                                           | ns min | SCLK cycle time                                                                            |

| $t_2$                 | 10                                           | ns min | SCLK high time                                                                             |

| t <sub>3</sub>        | 10                                           | ns min | SCLK low time                                                                              |

| t <sub>4</sub>        | 15                                           | ns min | SYNC falling edge to SCLK falling edge setup time                                          |

| $t_5$                 | 15                                           | ns min | SCLK falling edge to SYNC rising edge time                                                 |

| t <sub>6</sub>        | 20                                           | ns min | Minimum SYNC high time (write mode)                                                        |

| <b>t</b> <sub>7</sub> | 5                                            | ns min | Data setup time                                                                            |

| t <sub>8</sub>        | 5                                            | ns min | Data hold time                                                                             |

| <b>t</b> <sub>9</sub> | 4                                            | μs typ | DAC output settling time, 32 code step to $\pm 0.5$ LSB at 12-bit resolution (see Table 3) |

| t <sub>10</sub>       | 100                                          | ns typ | RESET <sup>2</sup> pulse width low                                                         |

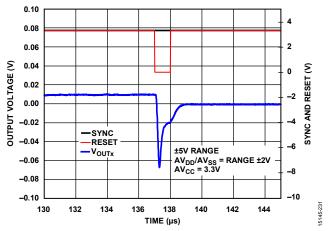

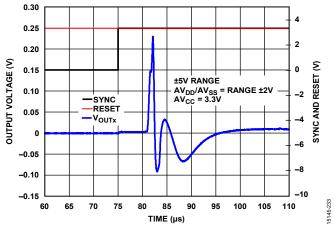

| t <sub>11</sub>       | 100                                          | ns typ | RESET <sup>2</sup> pulse activation time                                                   |

| t <sub>12</sub>       | 10                                           | ns min | SYNC rising edge to SCLK falling edge                                                      |

| t <sub>13</sub>       | 40                                           | ns max | SCLK rising edge to SDO valid ( $C_{L_SDO}^3 = 15 \text{ pF}$ )                            |

| t <sub>14</sub>       | 80                                           | ns min | Minimum SYNC high time (readback/daisy-chain mode)                                         |

| t <sub>15</sub>       | 5                                            | μs typ | SYNC rising edge to SYNC rising edge (DAC register updates)                                |

$<sup>^{\</sup>rm 1}$  Maximum SCLK frequency is 50 MHz for write mode and 10 MHz for readback mode.

#### **Timing Diagrams**

Figure 2. Serial Interface Timing Diagram

<sup>&</sup>lt;sup>2</sup> Minimum time between a reset and the subsequent successful write is typically 25 ns.

<sup>&</sup>lt;sup>3</sup> C<sub>L\_SDO</sub> is the capacitive load on the SDO output.

Figure 4. Readback Timing Diagram

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted. Transient currents of up to 100 mA do not cause silicon controlled rectifier (SCR) latch-up.

Table 5.

| Table 5.                                                  |                                                                     |

|-----------------------------------------------------------|---------------------------------------------------------------------|

| Parameter                                                 | Rating                                                              |

| AV <sub>DD</sub> to AGND                                  | -0.3 V to +34 V                                                     |

| AV <sub>SS</sub> to AGND                                  | +0.3 V to −34 V                                                     |

| AV <sub>DD</sub> to AV <sub>SS</sub>                      | −0.3 V to +34 V                                                     |

| AV <sub>CC</sub> to AGND                                  | −0.3 V to +7 V                                                      |

| AV <sub>CC</sub> to AGND                                  | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$                         |

| V <sub>LOGIC</sub> to DGND                                | −0.3 V to +7 V                                                      |

| Digital Inputs <sup>1</sup> to DGND                       | $-0.3 \mathrm{V}$ to $\mathrm{V}_{\mathrm{LOGIC}} + 0.3 \mathrm{V}$ |

| Digital Output (SDO) to DGND                              | $-0.3 \mathrm{V}$ to $\mathrm{V}_{\mathrm{LOGIC}} + 0.3 \mathrm{V}$ |

| N0, N1 to AGND                                            | $-0.3 \text{ V to AV}_{CC} + 0.3 \text{ V}$                         |

| V <sub>REF</sub> to AGND                                  | −0.3 V to AVcc + 0.3 V                                              |

| V <sub>OUT</sub> x to AGND                                | $AV_{SS} - 0.3 \text{ V to } AV_{DD} + 0.3 \text{ V}$               |

| AGND to DGND                                              | −0.3 V to +0.3 V                                                    |

| Operating Temperature Range,<br>T <sub>A</sub> Industrial | -40°C to +105°C                                                     |

| Storage Temperature Range                                 | −65°C to +150°C                                                     |

| Junction Temperature, T <sub>JMAX</sub>                   | 150°C                                                               |

| Power Dissipation                                         | (T <sub>J MAX</sub> — T <sub>A</sub> )/θ <sub>JA</sub>              |

| Lead Temperature                                          |                                                                     |

| Soldering Reflow                                          | 260°C, as per JEDEC J-STD-020                                       |

<sup>&</sup>lt;sup>1</sup> The digital inputs include RESET, SCLK, SYNC, and SDI.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.

**Table 6. Thermal Resistance**

| Package Type         | θιΑ   | Unit |

|----------------------|-------|------|

| CB-49-4 <sup>1</sup> | 53    | °C/W |

| CP-40-7 <sup>1</sup> | 31.71 | °C/W |

<sup>&</sup>lt;sup>1</sup> Thermal impedance simulated values are based on JEDEC 2S2P thermal test board with 16 thermal vias. See JEDEC JESD51.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

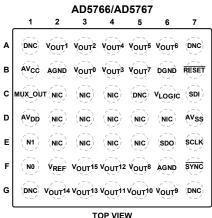

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

TOP VIEW (BALL SIDE DOWN) Not to Scale

NOTES

1. DNC = DO NOT CONNECT. DO NOT CONNECT TO THESE PINS.

2. NIC = NO INTERNAL CONNECTION. THESE PINS SHOULD BE ROUTED TO THERMAL VIAS ON THE PCB TO AID WITH HEAT DISSIPATION. CONNECT THESE PINS TO GROUND.

Figure 5. WLCSP Package Pin Configuration

Table 7. 49-Ball WLCSP Pin Function Descriptions

| Pin No.                  | Mnemonic              | Description                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|--------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Dither                   |                       |                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| F1                       | NO                    | Dither Signal Input Pin 0. A signal connected to this pin can be added to the DAC outputs via register commands. If unused, connect this pin to ground. Refer to the Dither section for more information.                                                                                                                                                                                                                |  |  |  |  |  |

| E1                       | N1                    | Dither Signal Input Pin 1. A signal connected to this pin can be added to the DAC outputs via register commands. If unused, connect this pin to ground. Refer to the Dither section for more information.                                                                                                                                                                                                                |  |  |  |  |  |

| Logic Inputs and Outputs |                       |                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| E7                       | SCLK                  | Serial Clock Input. Data is clocked into the input shift register on the falling edge of the serial clock input. Data can be transferred at rates of up to 50 MHz for write mode and 10 MHz for readback and daisy-chain mode.                                                                                                                                                                                           |  |  |  |  |  |

| F7                       | SYNC                  | Active Low Control Input. SYNC is the frame synchronization signal for the input data. When SYNC goes low, it powers on the SCLK and SDI buffers and enables the input shift register. Data is transferred in on the falling edges of the next 24 clocks. If SYNC is taken high before the 24 <sup>th</sup> falling edge, the rising edge of SYNC acts as an interrupt, and the write sequence is ignored by the device. |  |  |  |  |  |

| C7                       | SDI                   | Serial Data Input. This device has a 24-bit shift register. Data is clocked into the register on the falling edge of the serial clock input.                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| E6                       | SDO                   | Serial Data Output. This pin clocks data from the serial register in daisy-chain or readback mode.  Data is clocked out on the rising edge of SCLK and is valid on the falling edge of SCLK.                                                                                                                                                                                                                             |  |  |  |  |  |

| В7                       | RESET                 | Active Low Reset Input. Asserting this pin logic low returns the AD5766/AD5767 to the default power-on state. After this pin returns to logic high, the device comes out of the reset mode and is ready to accept a new SPI command. This pin can be left floating, because there is a weak internal pull-up resistor.                                                                                                   |  |  |  |  |  |

| Analog Outputs           |                       |                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| B3                       | V <sub>OUT</sub> 0    | Analog Output Voltage from DAC 0.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| A2                       | V <sub>OUT</sub> 1    | Analog Output Voltage from DAC 1.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| A3                       | V <sub>оит</sub> 2    | Analog Output Voltage from DAC 2.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| B4                       | V <sub>OUT</sub> 3    | Analog Output Voltage from DAC 3.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| A4                       | V <sub>OUT</sub> 4    | Analog Output Voltage from DAC 4.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| A5                       | V <sub>OUT</sub> 5    | Analog Output Voltage from DAC 5.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| A6                       | <b>V</b> оит <b>6</b> | Analog Output Voltage from DAC 6.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Pin No.                               | Mnemonic            | Description                                                                                                                                                                       |  |  |  |  |  |

|---------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| B5                                    | V <sub>OUT</sub> 7  | Analog Output Voltage from DAC 7.                                                                                                                                                 |  |  |  |  |  |

| F5                                    | V <sub>оит</sub> 8  | Analog Output Voltage from DAC 8.                                                                                                                                                 |  |  |  |  |  |

| G6                                    | V <sub>OUT</sub> 9  | Analog Output Voltage from DAC 9.                                                                                                                                                 |  |  |  |  |  |

| G5                                    | V <sub>OUT</sub> 10 | Analog Output Voltage from DAC 10.                                                                                                                                                |  |  |  |  |  |

| G4                                    | V <sub>OUT</sub> 11 | Analog Output Voltage from DAC 11.                                                                                                                                                |  |  |  |  |  |

| F4                                    | V <sub>OUT</sub> 12 | Analog Output Voltage from DAC 12.                                                                                                                                                |  |  |  |  |  |

| G3                                    | V <sub>оит</sub> 13 | Analog Output Voltage from DAC 13.                                                                                                                                                |  |  |  |  |  |

| G2                                    | V <sub>OUT</sub> 14 | Analog Output Voltage from DAC 14.                                                                                                                                                |  |  |  |  |  |

| F3                                    | V <sub>OUT</sub> 15 | Analog Output Voltage from DAC 15.                                                                                                                                                |  |  |  |  |  |

| Power Supplies and<br>Reference Input |                     |                                                                                                                                                                                   |  |  |  |  |  |

| F2                                    | $V_{REF}$           | Reference Input Voltage. For specified performance, V <sub>REFIN</sub> = 2.5 V.                                                                                                   |  |  |  |  |  |

| C6                                    | $V_{LOGIC}$         | Digital Power Supply.                                                                                                                                                             |  |  |  |  |  |

| B1                                    | AVcc                | Power Supply Input. The AD5766/AD5767 operates from 2.97 V to 3.6 V. Decouple AV <sub>CC</sub> with a 10 μF capacitor in parallel with a 0.1 μF capacitor to analog ground.       |  |  |  |  |  |

| D1                                    | $AV_{DD}$           | Output Amplifier Positive Analog Supply.                                                                                                                                          |  |  |  |  |  |

| D7                                    | AVss                | Output Amplifier Negative Analog Supply.                                                                                                                                          |  |  |  |  |  |

| B2, F6                                | AGND                | Analog Ground.                                                                                                                                                                    |  |  |  |  |  |

| B6                                    | DGND                | Digital Ground Pin.                                                                                                                                                               |  |  |  |  |  |

| Channel Monitoring                    |                     |                                                                                                                                                                                   |  |  |  |  |  |

| C1                                    | MUX_OUT             | Monitor Output. This pin acts as the output of a 16-to-1 channel multiplexer that can be programmed to multiplex one of 16 channels, Channel 0 to Channel 15, to the MUX_OUT pin. |  |  |  |  |  |

| Do Not Connect                        |                     |                                                                                                                                                                                   |  |  |  |  |  |

| A1, A7, C5, G1, G7                    | DNC                 | Do Not Connect. Do not connect to these pins.                                                                                                                                     |  |  |  |  |  |

| No Internal Connection                |                     |                                                                                                                                                                                   |  |  |  |  |  |

| C2 to C4, D2 to D6,<br>E2 to E5       | NIC                 | No Internal Connection. Route these pins to thermal vias on the PCB to aid with heat dissipation. Connect these pins to ground.                                                   |  |  |  |  |  |

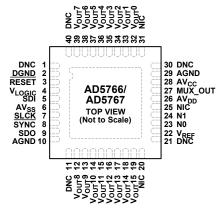

NOTES

1. DNC = DO NOT CONNECT. DO NOT CONNECT TO THESE PINS.

2. NIC = NO INTERNAL CONNECTION. THESE PINS SHOULD BE ROUTED TO THERMAL VIAS ON THE PCB TO AID WITH HEAT DISSIPATION. THESE SHOULD BE CONNECTED TO GROUND.

3. EXPOSED PAD (LFCSP PACKAGE ONLY). CONNECT THIS EXPOSED PAD TO THE POTENTIAL OF THE AVS, PIN, OR, ALTERNATIVELY, LEAVE IT ELECTRICALLY UNCONNECTED. IT IS RECOMMENDED THAT THE PAD BE THERMALLY CONNECTED TO A COPPER PLANE FOR ENHANCED THERMAL PERFORMANCE.

Figure 6. LFCSP Package Pin Configuration

**Table 8. 40-Lead LFCSP Pin Function Descriptions**

| Pin No.                  | Mnemonic           | Description                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dither                   |                    |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 23                       | NO                 | Dither Signal Input Pin 0. A signal connected to this pin can be added to the DAC outputs via register commands. If unused, connect this pin to ground. Refer to the Dither section for more information.                                                                                                                                                                                                                |

| 24                       | N1                 | Dither Signal Input Pin 1. A signal connected to this pin can be added to the DAC outputs via register commands. If unused, connect this pin to ground. Refer to the Dither section for more information.                                                                                                                                                                                                                |

| Logic Inputs and Outputs |                    |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7                        | SCLK               | Serial Clock Input. Data is clocked into the input shift register on the falling edge of the serial clock input. Data can be transferred at rates of up to 50 MHz for write mode and 10 MHz for readback and daisy-chain mode.                                                                                                                                                                                           |

| 8                        | SYNC               | Active Low Control Input. SYNC is the frame synchronization signal for the input data. When SYNC goes low, it powers on the SCLK and SDI buffers and enables the input shift register. Data is transferred in on the falling edges of the next 24 clocks. If SYNC is taken high before the 24 <sup>th</sup> falling edge, the rising edge of SYNC acts as an interrupt, and the write sequence is ignored by the device. |

| 5                        | SDI                | Serial Data Input. This device has a 24-bit shift register. Data is clocked into the register on the falling edge of the serial clock input.                                                                                                                                                                                                                                                                             |

| 9                        | SDO                | Serial Data Output. This pin clocks data from the serial register in daisy-chain or readback mode. Data is clocked out on the rising edge of SCLK and is valid on the falling edge of SCLK.                                                                                                                                                                                                                              |

| 3                        | RESET              | Active Low Reset Input. Asserting this pin logic low returns the AD5766/AD5767 to the default power-on state. After this pin returns to logic high, the device comes out of the reset mode and is ready to accept a new SPI command. This pin can be left floating, because there is a weak internal pull-up resistor.                                                                                                   |

| Analog Outputs           |                    |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 32                       | V <sub>оит</sub> 0 | Analog Output Voltage from DAC 0.                                                                                                                                                                                                                                                                                                                                                                                        |

| 33                       | V <sub>OUT</sub> 1 | Analog Output Voltage from DAC 1.                                                                                                                                                                                                                                                                                                                                                                                        |