# **ANALOG** Low Power, 24-Bit, 31.25 kSPS, Sigma-Delta **ADC** with True Rail\_to\_Rail Ruffers **ADC** with True Rail-to-Rail Buffers

### **Data Sheet**

# AD7172-4

#### **FEATURES**

Fast and flexible output rate: 1.25 SPS to 31.25 kSPS Channel scan data rate of 6.21 kSPS/channel (161 µs settling) **Performance specifications** 17.2 noise free bits at 31.25 kSPS 24 noise free bits at 5 SPS INL: ±2 ppm of FSR 85 dB rejection of 50 Hz and 60 Hz with 50 ms settling User configurable input channels 4 fully differential channels or 8 single-ended channels **Crosspoint multiplexer** True rail-to-rail analog and reference input buffers Internal or external clock Power supply AVDD1 = 3.0 V to 5.5 V, AVDD2 = IOVDD = 2 V to 5.5 V Split supply with AVDD1 and AVSS at ±2.5 V or ±1.65 V ADC current: 1.5 mA Temperature range: -40°C to +105°C 3- or 4-wire serial digital interface (Schmitt trigger on SCLK) Serial port interface (SPI), QSPI-, MICROWIRE-, and DSPcompatible

#### **APPLICATIONS**

**Process control: PLC/DCS modules**

**Temperature and pressure measurement**

Medical and scientific multichannel instrumentation Chromatography

#### **GENERAL DESCRIPTION**

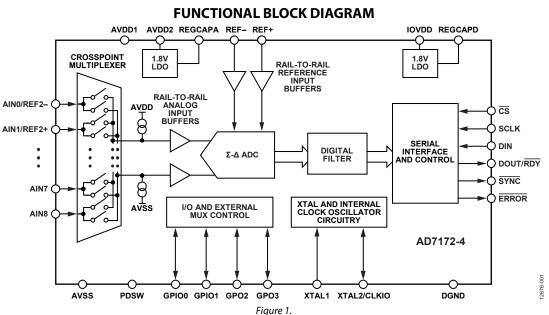

The AD7172-4 is a low noise, low power, multiplexed,  $\Sigma$ - $\Delta$  analogto-digital converter (ADC) with 4- or 8-channel (fully differential/ single-ended) inputs for low bandwidth signals. The AD7172-4 has a maximum channel scan rate of 6.21 kSPS (161 µs) for fully settled data. The output data rates range from 1.25 SPS to 31.25 kSPS.

The AD7172-4 integrates key analog and digital signal conditioning blocks to allow users to configure an individual setup for each analog input channel in use via the SPI. Integrated true rail-torail buffers on the analog inputs and reference inputs provide easy to drive high impedance inputs.

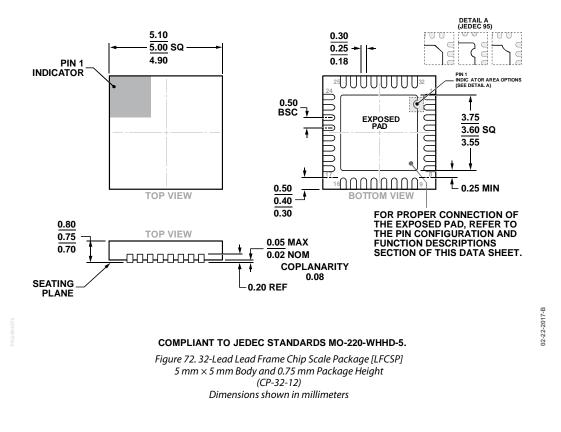

The digital filter allows simultaneous 50 Hz and 60 Hz rejection at a 27.27 SPS output data rate. The user can switch between different filter options according to the demands of each channel in the application, with further digital processing functions such as offset and gain calibration registers, which are configurable on a per channel basis. General-purpose input/outputs (GPIOs) control external multiplexers synchronous to the ADC conversion timing. The specified temperature range is -40°C to +105°C. The AD7172-4 is in a 5 mm  $\times$  5 mm, 32-lead LFCSP.

Note that, throughout this data sheet, the dual function pin names are referenced by the relevant function only.

#### Rev. B

**Document Feedback** Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2015–2017 Analog Devices, Inc. All rights reserved. **Technical Support** www.analog.com

# TABLE OF CONTENTS

| Features 1                                  |

|---------------------------------------------|

| Applications1                               |

| General Description 1                       |

| Functional Block Diagram 1                  |

| Revision History                            |

| Specifications                              |

| Timing Characteristics7                     |

| Timing Diagrams7                            |

| Absolute Maximum Ratings                    |

| Thermal Resistance                          |

| ESD Caution                                 |

| Pin Configuration and Function Descriptions |

| Typical Performance Characteristics11       |

| Noise Performance and Resolution17          |

| Getting Started                             |

| Power Supplies                              |

| Digital Communication19                     |

| AD7172-4 Reset                              |

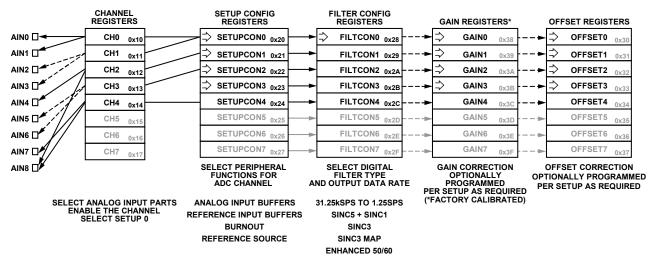

| Configuration Overview20                    |

| Circuit Description                         |

| Buffered Analog Input                       |

| Crosspoint Multiplexer                      |

| AD7172-4 Reference                          |

| Buffered Reference Input28                  |

| Clock Source                                |

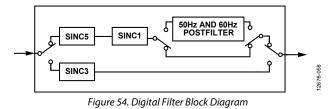

| Digital Filters                             |

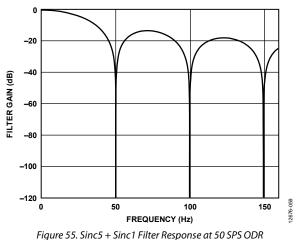

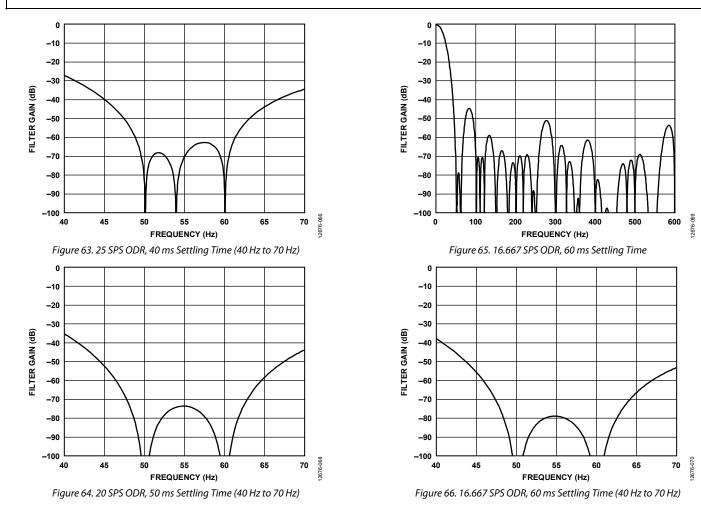

| Sinc5 + Sinc1 Filter                        |

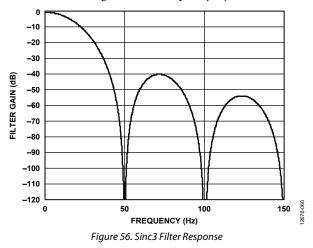

| Sinc3 Filter                                |

| Single Cycle Settling                       |

| Enhanced 50 Hz and 60 Hz Rejection Filters  |

| Operating Modes                             |

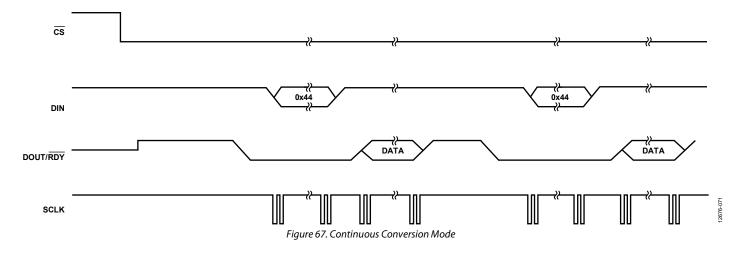

| Continuous Conversion Mode                  |

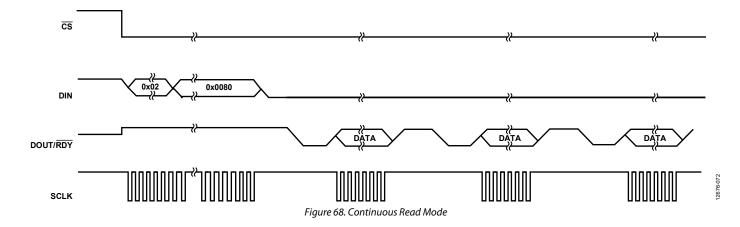

| Continuous Read Mode                        |

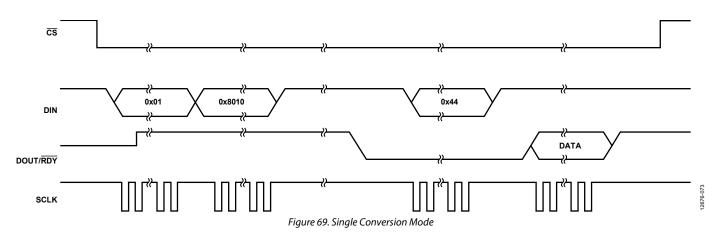

| Single Conversion Mode                      |

| Standby and Power-Down Modes                |

| Calibration                                 |

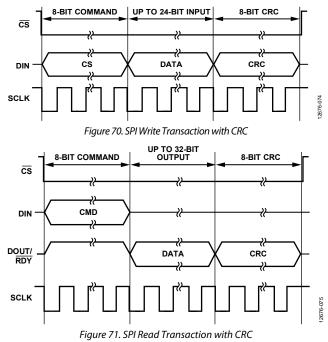

| Digital Interface                           |

| Checksum Protection                         |

| CRC Calculation                                                       |

|-----------------------------------------------------------------------|

| Integrated Functions                                                  |

| General-Purpose Input/Output                                          |

| External Multiplexer Control 42                                       |

| Delay                                                                 |

| 16-Bit/24-Bit Conversions 42                                          |

| DOUT_RESET 42                                                         |

| Synchronization                                                       |

| Error Flags                                                           |

| DATA_STAT                                                             |

| IOSTRENGTH                                                            |

| Grounding and Layout                                                  |

| Register Summary                                                      |

| Register Details                                                      |

| Communications Register                                               |

| Status Register                                                       |

| ADC Mode Register 49                                                  |

| Interface Mode Register 50                                            |

| Register Check                                                        |

| Data Register                                                         |

| GPIO Configuration Register 52                                        |

| ID Register                                                           |

| Channel Register 0 54                                                 |

| Channel Register 1 to Channel Register 7 55                           |

| Setup Configuration Register 056                                      |

| Setup Configuration Register 1 to Setup Configuration                 |

| Register 7 57   Filter Configuration Register 0 58                    |

|                                                                       |

| Filter Configuration Register 1 to Filter Configuration<br>Register 7 |

| Offset Register 0                                                     |

| Offset Register 1 to Offset Register 7                                |

| Gain Register 0                                                       |

| Gain Register 1 to Gain Register 7                                    |

| Outline Dimensions                                                    |

| Ordering Guide61                                                      |

|                                                                       |

#### **REVISION HISTORY**

| 4/2017—Rev. A to Rev. B       |    |

|-------------------------------|----|

| Changes to Outline Dimensions | 68 |

| Changes to Ordering Guide     | 68 |

#### 5/2016—Rev. 0 to Rev. A

| Moved Revision History             | 3  |

|------------------------------------|----|

| Changes to Table 5                 | 9  |

| Changes to Figure 18 and Figure 19 | 13 |

| Changes to Power Supplies Section  | 19 |

5/2015—Revision 0: Initial Version

# SPECIFICATIONS

AVDD1 = 3.0 V to 5.5 V, AVDD2 = IOVDD = 2 V to 5.5 V, AVSS = DGND = 0 V, REF + 2.5 V, REF - AVSS, MCLK = internal master clock = 2 MHz,  $T_A = T_{MIN}$  to  $T_{MAX}$  (-40°C to +105°C), unless otherwise noted.

| Table 1.                             | Test Conditions/Commonts                                                   | A4:         | Turn          | Max          | l lmit     |

|--------------------------------------|----------------------------------------------------------------------------|-------------|---------------|--------------|------------|

|                                      | Test Conditions/Comments                                                   | Min         | Тур           | Max          | Unit       |

| ADC SPEED AND PERFORMANCE            |                                                                            | 1.25        |               | 21 250       | CDC        |

| Output Data Rate (ODR)               |                                                                            | 1.25        |               | 31,250       | SPS        |

| No Missing Codes <sup>1</sup>        | Excluding sinc3 filter $\geq$ 15 kSPS                                      | 24          |               |              | Bits       |

| Resolution                           | See Table 6 and Table 7                                                    |             |               |              |            |

| Noise                                | See Table 6 and Table 7                                                    |             |               |              |            |

| ACCURACY                             |                                                                            |             |               |              |            |

| Integral Nonlinearity (INL)          |                                                                            |             | ±2            | ±5.2         | ppm of FSF |

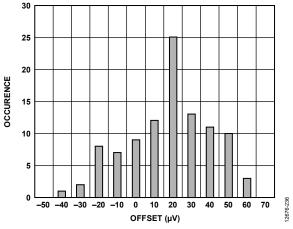

| Offset Error <sup>2</sup>            | Internal short                                                             |             | ±75           |              | μV         |

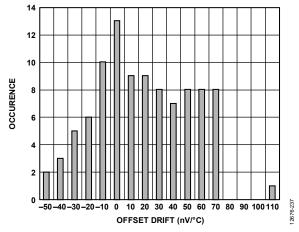

| Offset Drift                         | Internal short                                                             |             | ±230          |              | nV/°C      |

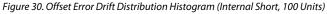

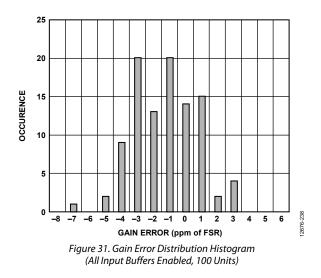

| Gain Error <sup>2</sup>              | AVDD1 = 5 V                                                                |             | ±5            | ±45          | ppm of FSF |

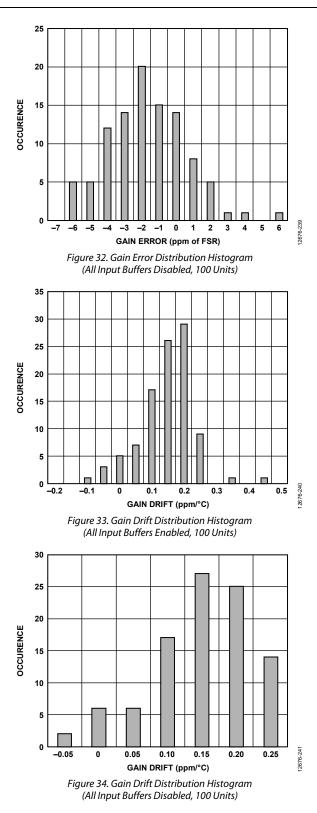

| Gain Drift                           |                                                                            |             | ±0.2          | ±0.5         | ppm/°C     |

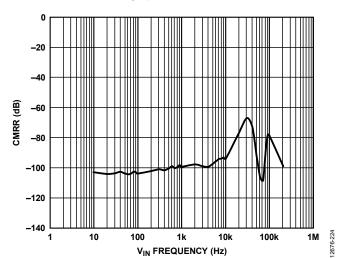

| REJECTION                            |                                                                            |             |               |              |            |

| Power Supply Rejection               | AVDD1, AVDD2, $V_{IN} = 1 V$                                               |             | 98            |              | dB         |

| Common-Mode Rejection                | $V_{IN} = 0.1 V$                                                           |             |               |              |            |

| At DC                                |                                                                            | 95          |               |              | dB         |

| At 50 Hz, 60 Hz <sup>1</sup>         | 20 Hz output data rate (postfilter), 50 Hz $\pm$ 1 Hz and 60 Hz $\pm$ 1 Hz | 120         |               |              | dB         |

| Normal Mode Rejection <sup>1</sup>   | 50 Hz $\pm$ 1 Hz and 60 Hz $\pm$ 1 Hz                                      |             |               |              |            |

|                                      | Internal clock, 20 SPS ODR (postfilter)                                    | 71          | 90            |              | dB         |

|                                      | External clock, 20 SPS ODR (postfilter)                                    | 85          | 90            |              | dB         |

| ANALOG INPUTS                        |                                                                            |             |               |              |            |

| Differential Input Range             | $V_{REF} = (REF+) - (REF-)$                                                |             | $\pm V_{REF}$ |              | v          |

| Absolute Voltage Limits <sup>1</sup> |                                                                            |             |               |              |            |

| Input Buffers Disabled               |                                                                            | AVSS – 0.05 |               | AVDD1 + 0.05 | v          |

| Input Buffers Enabled                |                                                                            | AVSS        |               | AVDD1        | v          |

| Analog Input Current                 |                                                                            |             |               |              |            |

| Input Buffers Disabled               |                                                                            |             |               |              |            |

| Input Current                        |                                                                            |             | ±6            |              | μA/V       |

| Input Current Drift                  |                                                                            |             | ±0.45         |              | nA/V/°C    |

| Input Buffers Enabled                |                                                                            |             |               |              |            |

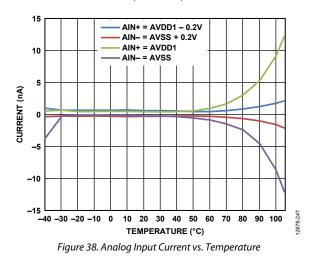

| Input Current                        |                                                                            |             | ±5.5          |              | nA         |

| Input Current Drift                  |                                                                            |             | ±0.1          |              | nA/°C      |

| Crosstalk                            | 1 kHz input                                                                |             | -120          |              | dB         |

| REFERENCE INPUTS                     |                                                                            |             | 120           |              | ub         |

| Differential Input Range             | $V_{REF} = (REF+) - (REF-)$                                                | 1           | 2.5           | AVDD1        | v          |

| Absolute Voltage Limits <sup>1</sup> |                                                                            | 1           | 2.5           | AVDDI        | v          |

| Input Buffers Disabled               |                                                                            | AVSS – 0.05 |               | AVDD1 + 0.05 | v          |

| Input Buffers Enabled                |                                                                            | AVSS = 0.05 |               | AVDD1 + 0.05 | V          |

| REFIN Input Current                  |                                                                            | AV33        |               | AVDDI        | v          |

| Input Buffers Disabled               |                                                                            |             |               |              |            |

|                                      |                                                                            |             |               |              |            |

| Input Current                        | E to set de d                                                              |             | ±9            |              | μΑ/ν       |

| Input Current Drift                  | External clock                                                             |             | ±0.75         |              | nA/V/°C    |

|                                      | Internal clock                                                             |             | ±1            |              | nA/V/°C    |

| Input Buffers Enabled                |                                                                            |             |               |              |            |

| Input Current                        |                                                                            |             | ±100          |              | nA         |

| Input Current Drift                  |                                                                            |             | ±2.5          |              | nA/°C      |

| Normal Mode Rejection <sup>1</sup>   | See the Rejection parameter                                                |             |               |              |            |

| Common-Mode Rejection                |                                                                            |             | 95            |              | dB         |

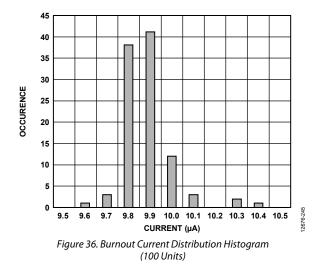

| BURNOUT CURRENTS                     |                                                                            |             |               |              |            |

| Source/Sink Current                  | Analog input buffers must be enabled                                       |             | ±10           |              | μA         |

# **Data Sheet**

| Parameter                               | Test Conditions/Comments                                                                      | Min                 | Тур | Max                 | Unit |

|-----------------------------------------|-----------------------------------------------------------------------------------------------|---------------------|-----|---------------------|------|

| GPIO (GPIO0, GPIO1)                     | With respect to AVSS                                                                          |                     |     |                     |      |

| Input Mode Leakage Current <sup>1</sup> |                                                                                               | -10                 |     | +10                 | μΑ   |

| Floating State Output                   |                                                                                               |                     | 5   |                     | pF   |

| Capacitance                             |                                                                                               |                     |     |                     |      |

| Output Voltage <sup>1</sup>             |                                                                                               |                     |     |                     |      |

| <b>High, V</b> он                       | $I_{SOURCE} = 200 \ \mu A$                                                                    | AVSS + 4            |     |                     | V    |

| Low, V <sub>OL</sub>                    | I <sub>SINK</sub> = 800 μA                                                                    |                     |     | AVSS + 0.4          | V    |

| Input Voltage <sup>1</sup>              |                                                                                               |                     |     |                     |      |

| High, V <sub>⊮</sub>                    |                                                                                               | AVSS + 3            |     |                     | V    |

| Low, V <sub>IL</sub>                    |                                                                                               |                     |     | AVSS + 0.7          | V    |

| CLOCK                                   |                                                                                               |                     |     |                     |      |

| Internal Clock                          |                                                                                               |                     |     |                     |      |

| Frequency                               |                                                                                               |                     | 2   |                     | MHz  |

| Accuracy                                |                                                                                               | -2.6%               |     | +2.5%               | %    |

| Duty Cycle                              |                                                                                               |                     | 50  |                     | %    |

| Output Voltage                          |                                                                                               |                     |     |                     |      |

| Low, V <sub>OL</sub>                    |                                                                                               |                     |     | 0.4                 | V    |

| High, V <sub>он</sub>                   |                                                                                               | $0.8 \times IOVDD$  |     |                     | V    |

| Crystal                                 |                                                                                               |                     |     |                     |      |

| Frequency                               |                                                                                               | 14                  | 16  | 16.384              | MHz  |

| Startup Time                            |                                                                                               |                     | 10  |                     | μs   |

| External Clock (CLKIO)                  |                                                                                               |                     | 2   | 2.048               | MHz  |

| Duty Cycle <sup>1</sup>                 |                                                                                               | 30                  | 50  | 70                  | %    |

| LOGIC INPUTS                            |                                                                                               |                     |     |                     |      |

| Input Voltage <sup>1</sup>              |                                                                                               |                     |     |                     |      |

| High, V <sub>INH</sub>                  | $2 \text{ V} \le \text{IOVDD} < 2.3 \text{ V}$                                                | $0.65 \times IOVDD$ |     |                     | V    |

|                                         | $2.3 \text{ V} \le \text{IOVDD} \le 5.5 \text{ V}$                                            | $0.7 \times IOVDD$  |     |                     | V    |

| Low, V <sub>INL</sub>                   | $2 \text{ V} \leq \text{IOVDD} < 2.3 \text{ V}$                                               |                     |     | $0.35 \times IOVDD$ | V    |

|                                         | $2.3 \text{ V} \le \text{IOVDD} \le 5.5 \text{ V}$                                            |                     |     | 0.7                 | V    |

| Hysteresis <sup>1</sup>                 | $IOVDD \ge 2.7 V$                                                                             | 0.08                |     | 0.25                | V    |

|                                         | IOVDD < 2.7 V                                                                                 | 0.04                |     | 0.2                 | V    |

| Leakage Currents                        |                                                                                               | -10                 |     | +10                 | μΑ   |

| OGIC OUTPUT (DOUT/RDY)                  |                                                                                               |                     |     |                     |      |

| Output Voltage <sup>1</sup>             |                                                                                               |                     |     |                     |      |

| High, V <sub>он</sub>                   | $IOVDD \ge 4.5 V$ , $I_{SOURCE} = 1 mA$                                                       | $0.8 \times IOVDD$  |     |                     | v    |

| 5                                       | $2.7 \text{ V} \leq \text{IOVDD} < 4.5 \text{ V}, \text{I}_{\text{SOURCE}} = 500 \mu\text{A}$ | $0.8 \times IOVDD$  |     |                     | v    |

|                                         | $IOVDD < 2.7 V$ , $I_{SOURCE} = 200 \mu A$                                                    | $0.8 \times IOVDD$  |     |                     | v    |

| Low, V <sub>oL</sub>                    | $IOVDD \ge 4.5 V$ , $I_{SINK} = 2 mA$                                                         |                     |     | 0.4                 | v    |

|                                         | $2.7 \text{ V} \le \text{IOVDD} < 4.5 \text{ V}, \text{I}_{\text{SINK}} = 1 \text{ mA}$       |                     |     | 0.4                 | v    |

|                                         | $IOVDD < 2.7 V$ , $I_{SINK} = 400 \mu A$                                                      |                     |     | 0.4                 | v    |

| Leakage Current                         | Floating state                                                                                | -10                 |     | +10                 | μA   |

| Output Capacitance                      | Floating state                                                                                |                     | 10  |                     | pF   |

| SYSTEM CALIBRATION <sup>1</sup>         |                                                                                               |                     |     |                     |      |

| Full-Scale (FS) Calibration Limit       |                                                                                               |                     |     | $1.05 \times FS$    | v    |

| Zero-Scale Calibration Limit            |                                                                                               | $-1.05 \times FS$   |     |                     | v    |

| Input Span                              |                                                                                               | $0.8 \times FS$     |     | $2.1 \times FS$     | v    |

| POWER REQUIREMENTS                      |                                                                                               |                     |     |                     |      |

| Power Supply Voltage                    |                                                                                               |                     |     |                     |      |

| AVDD1 to AVSS                           |                                                                                               | 3.0                 |     | 5.5                 | v    |

| AVDD to AVSS<br>AVDD2 to AVSS           |                                                                                               | 2                   |     | 5.5                 | v    |

| AVDD2 to AVSS<br>AVSS to DGND           |                                                                                               | -2.75               |     | 0                   | v    |

| IOVDD to DGND                           |                                                                                               | 2                   |     | 5.5                 | v    |

|                                         | 1                                                                                             | -                   |     | J.J                 | V V  |

| Parameter                                            | <b>Test Conditions/Comments</b>                                         | Min | Тур  | Max  | Unit |

|------------------------------------------------------|-------------------------------------------------------------------------|-----|------|------|------|

| POWER SUPPLY CURRENTS                                | All outputs unloaded, digital inputs connected to IOVDD or DGND         |     |      |      |      |

| Full Operating Mode                                  |                                                                         |     |      |      |      |

| AVDD1 Current                                        |                                                                         |     |      |      |      |

| AVDD1 = 5 V Typical,<br>5.5 V Maximum                | $AIN\pmand\;REF\pmbuffers\;disabled$                                    |     | 0.23 | 0.29 | mA   |

|                                                      | AIN± and REF± buffers enabled                                           |     | 1.7  | 2.15 | mA   |

|                                                      | Each buffer: AIN± and REF±                                              |     | 0.38 |      | mA   |

| AVDD1 = 3.3 V Typical,<br>3.6 V Maximum <sup>1</sup> | $AIN\pm$ and $REF\pm$ buffers disabled                                  |     | 0.15 | 0.2  | mA   |

|                                                      | AIN± and REF± buffers enabled                                           |     | 1.45 | 1.9  | mA   |

|                                                      | Each buffer: AIN± and REF±                                              |     | 0.33 |      | mA   |

| AVDD2 Current                                        |                                                                         |     | 1    | 1.1  | mA   |

| IOVDD Current                                        | External clock                                                          |     | 0.33 | 0.5  | mA   |

|                                                      | Internal clock                                                          |     | 0.61 | 0.82 | mA   |

|                                                      | External crystal                                                        |     | 0.98 |      | mA   |

| Standby Mode                                         | LDO on                                                                  |     | 32   |      | μA   |

| Power-Down Mode                                      | Full power-down including LDO                                           |     | 1    | 10   | μA   |

| POWER DISSIPATION                                    |                                                                         |     |      |      |      |

| Full Operating Mode                                  | Unbuffered, external clock; AVDD1 =<br>3.3 V, AVDD2 = 2 V, IOVDD = 2 V  |     | 3.16 |      | mW   |

|                                                      | Unbuffered, external clock;<br>all supplies = 5 V                       |     | 7.8  |      | mW   |

|                                                      | Unbuffered, external clock;<br>all supplies = 5.5 V                     |     |      | 10.4 | mW   |

|                                                      | Fully buffered, internal clock; AVDD1 = 3.3 V, AVDD2 = 2 V, IOVDD = 2 V |     | 8    |      | mW   |

|                                                      | Fully buffered, internal clock;<br>all supplies = 5 V                   |     | 16.6 |      | mW   |

|                                                      | Fully buffered, internal clock;<br>all supplies = 5.5 V                 |     |      | 22.4 | mW   |

| Standby Mode                                         | All supplies = $5 V$                                                    |     | 160  |      | μW   |

| Power-Down Mode                                      | Full power-down, all supplies = 5 V                                     |     | 5    |      | μW   |

|                                                      | Full power-down, all supplies = 5.5 V                                   |     |      | 55   | μW   |

<sup>1</sup> Specification is not production tested but is supported by characterization data at initial product release.

<sup>2</sup> Following a system or internal zero-scale calibration, the offset error is in the order of the noise for the programmed output data rate selected. A system full-scale calibration reduces the gain error to the order of the noise for the programmed output data rate.

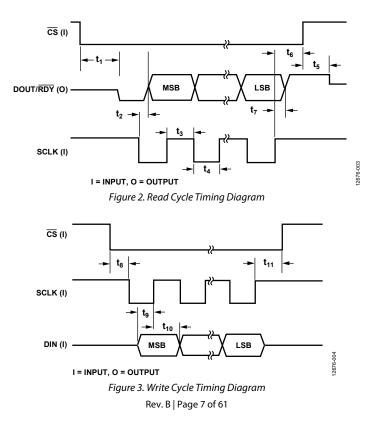

#### TIMING CHARACTERISTICS

IOVDD = 2 V to 5.5 V, DGND = 0 V, Input Logic 0 = 0 V, Input Logic 1 = IOVDD, CLOAD = 20 pF, unless otherwise noted.

| Table 2.                    |                                              |        |                                                             |  |  |  |

|-----------------------------|----------------------------------------------|--------|-------------------------------------------------------------|--|--|--|

| Parameter                   | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit   | Test Conditions/Comments <sup>1, 2</sup>                    |  |  |  |

| SCLK                        |                                              |        |                                                             |  |  |  |

| t <sub>3</sub>              | 25                                           | ns min | SCLK high pulse width                                       |  |  |  |

| <b>t</b> <sub>4</sub>       | 25                                           | ns min | SCLK low pulse width                                        |  |  |  |

| READ OPERATION              |                                              |        |                                                             |  |  |  |

| t1                          | 0                                            | ns min | CS falling edge to DOUT/RDY active time                     |  |  |  |

|                             | 15                                           | ns max | IOVDD = 4.75 V to 5.5 V                                     |  |  |  |

|                             | 40                                           | ns max | IOVDD = 2 V to 3.6 V                                        |  |  |  |

| t <sub>2</sub> <sup>3</sup> | 0                                            | ns min | SCLK active edge to data valid delay <sup>4</sup>           |  |  |  |

|                             | 12.5                                         | ns max | IOVDD = 4.75 V to 5.5 V                                     |  |  |  |

|                             | 25                                           | ns max | IOVDD = 2 V to 3.6 V                                        |  |  |  |

| <b>t</b> 5                  | 2.5                                          | ns min | Bus relinquish time after $\overline{CS}$ inactive edge     |  |  |  |

|                             | 20                                           | ns max |                                                             |  |  |  |

| t <sub>6</sub>              | 0                                            | ns min | SCLK inactive edge to $\overline{CS}$ inactive edge         |  |  |  |

| t <sub>7</sub> 5            | 10                                           | ns min | SCLK inactive edge to DOUT/RDY high/low                     |  |  |  |

| WRITE OPERATION             |                                              |        |                                                             |  |  |  |

| t <sub>8</sub>              | 0                                            | ns min | CS falling edge to SCLK active edge setup time <sup>4</sup> |  |  |  |

| t9                          | 8                                            | ns min | Data valid to SCLK edge setup time                          |  |  |  |

| t10                         | 8                                            | ns min | Data valid to SCLK edge hold time                           |  |  |  |

| <b>t</b> <sub>11</sub>      | 5                                            | ns min | CS rising edge to SCLK edge hold time                       |  |  |  |

<sup>1</sup> Sample tested during initial release to ensure compliance.

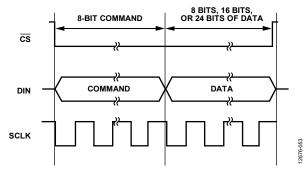

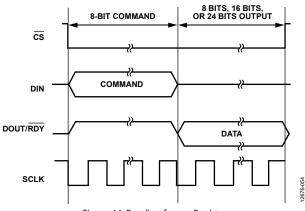

<sup>2</sup> See Figure 2 and Figure 3.

$^3$  This parameter is defined as the time required for the output to cross the  $V_{\text{OL}}$  or  $V_{\text{OH}}$  limits.

<sup>4</sup> The SC<u>LK active edge is the falling edge of SCLK.</u>

<sup>5</sup> DOUT/RDY returns high after a read of the data register. In single conversion mode and continuous conversion mode, the same data can be read again, if required, while DOUT/RDY is high, although care must be taken to ensure that subsequent reads do not occur close to the next output update. If the continuous read feature is enabled, the digital word can be read only once.

#### **TIMING DIAGRAMS**

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 3.

| Parameter                          | Rating                  |

|------------------------------------|-------------------------|

| AVDD1, AVDD2 to AVSS               | –0.3 V to +6.5 V        |

| AVDD1 to DGND                      | –0.3 V to +6.5 V        |

| IOVDD to DGND                      | –0.3 V to +6.5 V        |

| IOVDD to AVSS                      | –0.3 V to +7.5 V        |

| AVSS to DGND                       | -3.25 V to +0.3 V       |

| Analog Input Voltage to AVSS       | -0.3 V to AVDD1 + 0.3 V |

| Reference Input Voltage to AVSS    | –0.3 V to AVDD1 + 0.3 V |

| Digital Input Voltage to DGND      | -0.3 V to IOVDD + 0.3 V |

| Digital Output Voltage to DGND     | -0.3 V to IOVDD + 0.3 V |

| Analog Input/Digital Input Current | 10 mA                   |

| Operating Temperature Range        | -40°C to +105°C         |

| Storage Temperature Range          | –65°C to +150°C         |

| Maximum Junction Temperature       | 150°C                   |

| Lead Soldering, Reflow Temperature | 260°C                   |

| ESD Rating (HBM)                   | 4 kV                    |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for a device soldered on a JEDEC test board for surface-mount packages.

#### Table 4. Thermal Resistance

| Package Type                            | θ」Α | Unit |

|-----------------------------------------|-----|------|

| 32-Lead, 5 mm × 5 mm LFCSP              |     |      |

| 1-Layer JEDEC Board                     | 138 | °C/W |

| 4-Layer JEDEC Board                     | 63  | °C/W |

| 4-Layer JEDEC Board with 9 Thermal Vias | 41  | °C/W |

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

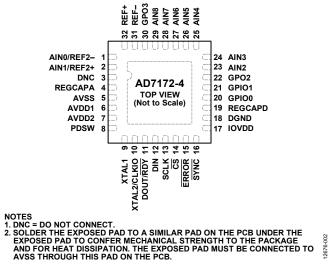

### **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 4. Pin Configuration

#### Table 5. Pin Function Descriptions

| Pin |             |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|-------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. | Mnemonic    | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1   | AIN0/REF2-  | AI                | Analog Input 0/Reference 2 Negative Input Terminal. A reference can be applied between the REF2+ and REF2– pins. REF2– can span from AVSS to AVDD1 – 1 V. Analog Input 0 is selectable through the crosspoint multiplexer. Reference 2 can be selected through the REF_SELx bits in the setup configuration (SETUPCONx) registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2   | AIN1/REF2+  | AI                | Analog Input 1/Reference 2 Positive Input Terminal. A reference can be applied between the REF2+ and REF2- pins. REF2+ can span from AVDD1 to AVSS + 1 V. Analog Input 1 is selectable through the crosspoint multiplexer. Reference 2 can be selected through the REF_SELx bits in the setup configuration (SETUPCONx) registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3   | DNC         |                   | Do Not Connect. Do not connect to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4   | REGCAPA     | AO                | Analog LDO Regulator Output. Decouple this pin to AVSS using a 1 $\mu$ F capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5   | AVSS        | Р                 | Negative Analog Supply. This supply ranges from 0 V to $-2.75$ V and is nominally set to 0 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6   | AVDD1       | Р                 | Analog Supply Voltage 1. This voltage ranges from 3.0 V minimum to 5.5 V maximum with respect to AVSS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7   | AVDD2       | Р                 | Analog Supply Voltage 2. This voltage ranges from 2 V to AVDD1 with respect to AVSS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8   | PDSW        | AO                | Power-Down Switch Connected to AVSS. This pin is controlled by the PDSW bit in the GPIOCON register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

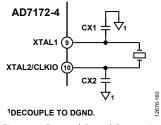

| 9   | XTAL1       | AI                | Input 1 for Crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10  | XTAL2/CLKIO | AI/DI             | Input 2 for Crystal/Clock Input or Output. See the CLOCKSEL bit settings in the ADCMODE register in Table 28 for more information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 11  | DOUT/RDY    | DO                | Serial Data Output/Data Ready Output. DOUT/RDY is a dual purpose pin. This pin is a serial data output pin to access the output shift register of the ADC. The output shift register can contain data from any of the on-chip data or control registers. The data-word/control word information is placed on the DOUT/RDY pin on the SCLK falling edge and is valid on the SCLK rising edge. When $\overline{CS}$ is high, the DOUT/RDY output is tristated. When $\overline{CS}$ is low, and a register is not being read, DOUT/RDY operates as a data ready pin, going low to indicate the completion of a conversion. If the data is not read after the conversion, the pin goes high before the next update occurs. The DOUT/RDY falling edge can be used as an interrupt to a processor, indicating that valid data is available. |

| 12  | DIN         | DI                | Serial Data Input to the Input Shift Register on the ADC. Data in this shift register is transferred to the control registers in the ADC, with the register address (RA) bits of the communications register identifying the appropriate register. Data is clocked in on the rising edge of SCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 13  | SCLK        | DI                | Serial Clock Input. This serial clock input is for data transfers to and from the ADC. The SCLK pin has a Schmitt triggered input, making the interface suitable for opto-isolated applications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Pin<br>No. | Mnemonic | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------|----------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14         | <u></u>  | DI                | Chip Select Input. This is an active low logic input used to select the ADC. $\overline{CS}$ can be used to select the ADC in systems with more than one device on the serial bus. $\overline{CS}$ can be hardwired low, allowing the ADC to operate in 3-wire mode with the SCLK, DIN, and DOUT pins interfacing with the device. When $\overline{CS}$ is high, the DOUT/ $\overline{RDY}$ output is tristated. |

| 15         | ERROR    | DI/O              | This pin can be used in one of the following three modes:                                                                                                                                                                                                                                                                                                                                                        |

|            |          |                   | Active low error input mode: this mode sets the ADC_ERROR bit in the status register.                                                                                                                                                                                                                                                                                                                            |

|            |          |                   | Active low, open-drain error output mode: the status register error bits are mapped to the ERROR pin. The ERROR pins of multiple devices can be wired together to a common pull-up resistor so that an error on any device can be observed.                                                                                                                                                                      |

|            |          |                   | General-purpose output mode: the status of the pin is controlled by the ERR_DAT bit in the GPIOCON register.<br>The pin is referenced between IOVDD and DGND, as opposed to the AVDD1 and AVSS levels used by the<br>GPIO0 and GPIO1 pins. The ERROR pin has an active pull-up in this case.                                                                                                                     |

| 16         | SYNC     | DI                | Synchronization Input. This pin allows synchronization of the digital filters and analog modulators when using multiple AD7172-4 devices.                                                                                                                                                                                                                                                                        |

| 17         | IOVDD    | Ρ                 | Digital Input/Output Supply Voltage. The IOVDD voltage ranges from 2 V to 5 V. IOVDD is independent of AVDD1 and AVDD2. For example, IOVDD can be operated at 3.3 V when AVDD1 or AVDD2 equals 5 V, or vice versa. If AVSS is set to -2.5 V, the voltage on IOVDD must not exceed 3.6 V.                                                                                                                         |

| 18         | DGND     | Р                 | Digital Ground.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 19         | REGCAPD  | AO                | Digital LDO Regulator Output. This pin is for decoupling purposes only. Decouple this pin to DGND using a 1 $\mu$ F capacitor.                                                                                                                                                                                                                                                                                   |

| 20         | GPIO0    | I/O               | General-Purpose Input/Output. 0 The logic input/output on this this pin is referred to the AVDD1 and AVSS supplies.                                                                                                                                                                                                                                                                                              |

| 21         | GPIO1    | I/O               | General-Purpose Input/Output 1. The logic input/output on this this pin is referred to the AVDD1 and AVSS supplies.                                                                                                                                                                                                                                                                                              |

| 22         | GPO2     | 0                 | General-Purpose Output. The logic output on this this pin is referred to the AVDD1 and AVSS supplies.                                                                                                                                                                                                                                                                                                            |

| 23         | AIN2     | AI                | Analog Input 2. Analog Input 2 is selectable through the crosspoint multiplexer.                                                                                                                                                                                                                                                                                                                                 |

| 24         | AIN3     | AI                | Analog Input 3. Analog Input 3 is selectable through the crosspoint multiplexer.                                                                                                                                                                                                                                                                                                                                 |

| 25         | AIN4     | AI                | Analog Input 4. Analog Input 4 is selectable through the crosspoint multiplexer.                                                                                                                                                                                                                                                                                                                                 |

| 26         | AIN5     | AI                | Analog Input 5. Analog Input 5 is selectable through the crosspoint multiplexer.                                                                                                                                                                                                                                                                                                                                 |

| 27         | AIN6     | AI                | Analog Input 6. Analog Input 6 is selectable through the crosspoint multiplexer.                                                                                                                                                                                                                                                                                                                                 |

| 28         | AIN7     | AI                | Analog Input 7. Analog Input 7 is selectable through the crosspoint multiplexer.                                                                                                                                                                                                                                                                                                                                 |

| 29         | AIN8     | AI                | Analog Input 8. Analog Input 8 is selectable through the crosspoint multiplexer.                                                                                                                                                                                                                                                                                                                                 |

| 30         | GPO3     | 0                 | General-Purpose Output. The logic output on this this pin is referred to the AVDD1 and AVSS supplies.                                                                                                                                                                                                                                                                                                            |

| 31         | REF-     | AI                | Reference 1 Input Negative Terminal. REF– can span from AVSS to AVDD1 – 1 V. Reference 1 can be selected through the REF_SELx bits in the setup configuration (SETUPCONx) registers.                                                                                                                                                                                                                             |

| 32         | REF+     | AI                | Reference 1 Input Positive Terminal. A reference can be applied between REF+ and REF REF+ can span from AVDD1 to AVSS + 1 V. Reference 1 can be selected through the REF_SELx bits in the setup configuration (SETUPCONx) registers.                                                                                                                                                                             |

|            | EP       | Ρ                 | Exposed Pad. Solder the exposed pad to a similar pad on the printed circuit board (PCB) under the exposed pad to confer mechanical strength to the package and for heat dissipation. The exposed pad must be connected to AVSS through this pad on the PCB.                                                                                                                                                      |

<sup>1</sup> Al is analog input, AO is analog output, DI/O is bidirectional digital input/output, DO is digital output, DI is digital input, and P is power supply, I/O is input/output, and O is output.

12676-208

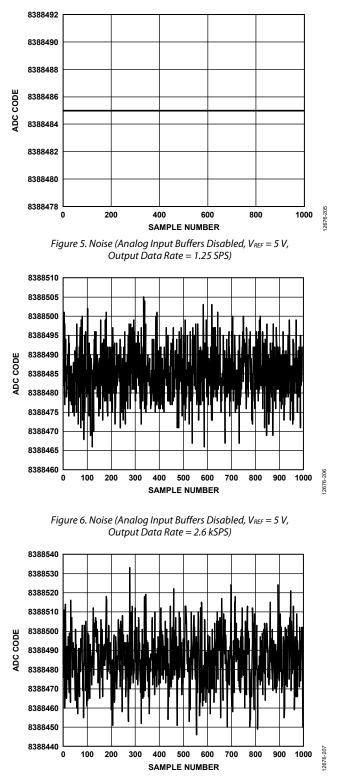

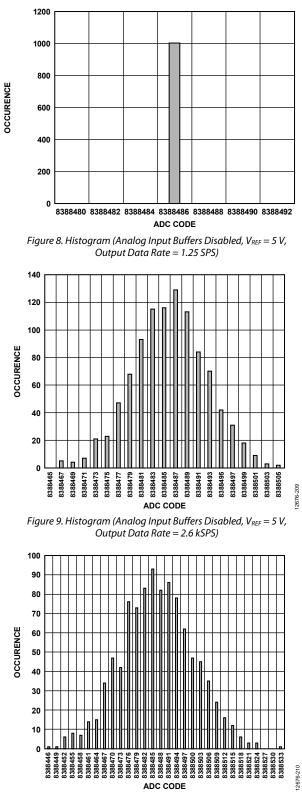

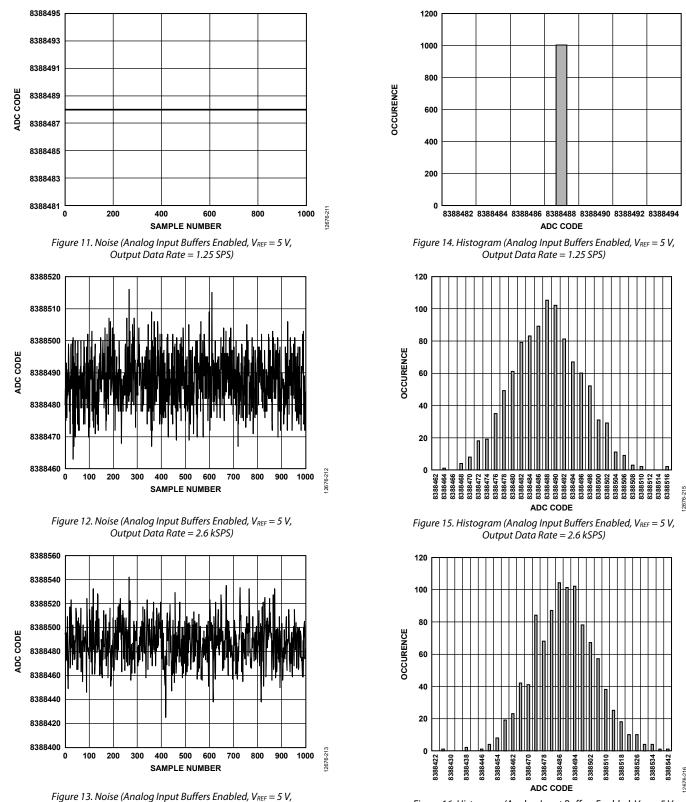

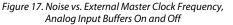

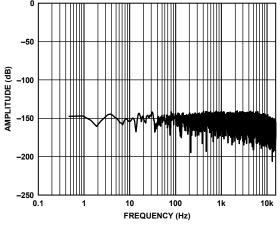

### **TYPICAL PERFORMANCE CHARACTERISTICS**

AVDD1 = 5 V, AVDD2 = 5 V, IOVDD = 3.3 V,  $T_A = 25^{\circ}$ C, unless otherwise noted.

Figure 7. Noise (Analog Input Buffers Disabled,  $V_{REF} = 5 V$ , Output Data Rate = 31.25 kSPS)

Figure 10. Histogram (Analog Input Buffers Disabled,  $V_{REF} = 5 V$ , Output Data Rate = 31.25 kSPS)

12676-214

Figure 16. Histogram (Analog Input Buffers Enabled,  $V_{REF} = 5 V$ , Output Data Rate = 31.25 kSPS)

### **Data Sheet**

0.000020 ANALOG INPUT BUFFERS OFF ANALOG INPUT BUFFERS ON 0.000018 0.000016 0.000014 (sm 0.000012 ₹ 0.000010 NOISE 0.000008 0.000006 0.000004 0.000002 12676-218 1000 201000 401000 601000 8010001001000 2010001401000 601000 801000 FREQUENCY (MHz)

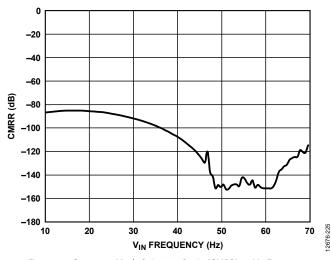

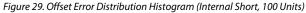

Figure 18. Common-Mode Rejection Ratio (CMRR) vs.  $V_{IN}$  Frequency  $(V_{IN} = 0.1 V, Output Data Rate = 31.25 kSPS)$

Figure 19. Common-Mode Rejection Ratio (CMRR) vs.  $V_{IN}$  Frequency ( $V_{IN} = 0.1 V$ , 10 Hz to 70 Hz, Output Data Rate = 20 SPS, Enhanced Filter)

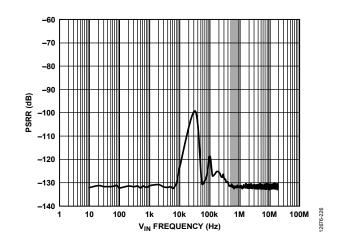

Figure 20. Power Supply Rejection Ratio (PSRR) vs. V<sub>IN</sub> Frequency

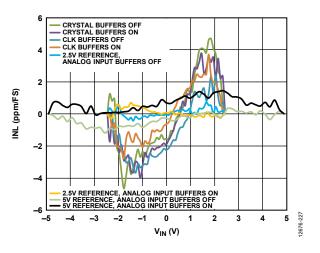

Figure 21. Integral Nonlinearity (INL) vs. V<sub>№</sub> (Differential Input)

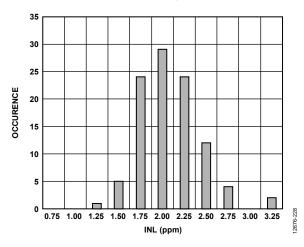

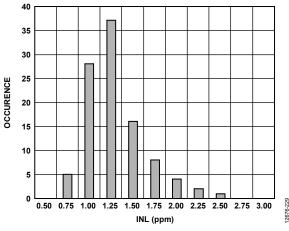

Figure 22. INL Distribution Histogram (Differential Input, All Input Buffers Enabled,  $V_{\text{REF}} = 2.5$  V External, 100 Units)

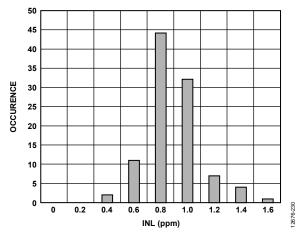

Figure 23. INL Distribution Histogram (Differential Input, All Input Buffers Disabled, V<sub>REF</sub> = 2.5 V External, 100 Units)

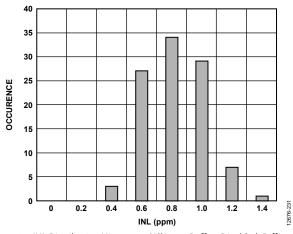

Figure 24. INL Distribution Histogram (All Input Buffers Enabled, Differential Input, V<sub>REF</sub> = 5 V External, 100 Units)

Figure 25. INL Distribution Histogram (All Input Buffers Disabled, Differential Input, V<sub>REF</sub> = 5 V External, 100 Units)

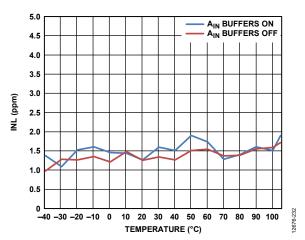

Figure 26. INL vs. Temperature (Differential Input,  $V_{REF} = 2.5 V$  External)

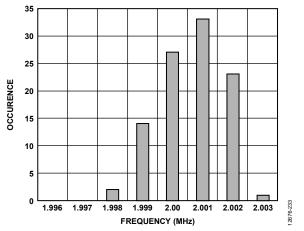

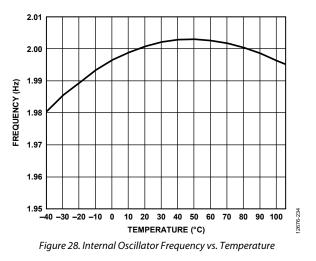

Figure 27. Internal Oscillator Frequency/Accuracy Distribution Histogram (100 Units)

# **Data Sheet**

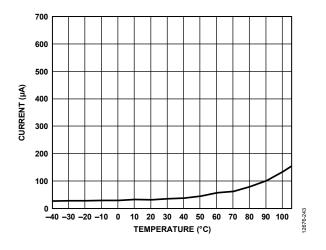

Figure 35. Current Consumption vs. Temperature (Standby Mode)

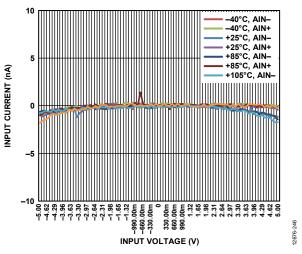

Figure 37. Analog Input Current vs. Input Voltage  $(V_{CM} = 2.5 V)$

### **NOISE PERFORMANCE AND RESOLUTION**

Table 6 and Table 7 show the rms noise, peak-to-peak noise, effective resolution, and the noise free (peak-to-peak) resolution of the AD7172-4 for various output data rates and filters. The numbers given are for the bipolar input range with a 5 V reference. These numbers are typical and are generated with a

differential input voltage of 0 V when the ADC is continuously converting on a single channel. It is important to note that the peak-to-peak resolution is calculated based on the peak-to-peak noise. The peak-to-peak resolution represents the resolution for which there is no code flicker.

| 1 able 6. RMS Noise and Peak-to-Peak Resolution vs. O | utput Data Rate Using the Sinc5 + Sinc1 Filter (Default) <sup>1</sup> |

|-------------------------------------------------------|-----------------------------------------------------------------------|

| Output Data Rate (SPS) | RMS Noise (µV rms) | Effective Resolution (Bits) | Peak-to-Peak Noise (µV p-p) | Peak-to-Peak Resolution (Bits) |

|------------------------|--------------------|-----------------------------|-----------------------------|--------------------------------|

| Input Buffers Disabled |                    |                             |                             |                                |

| 31,250                 | 8.2                | 20.2                        | 66                          | 17.2                           |

| 15,625                 | 7.0                | 20.4                        | 52                          | 17.5                           |

| 10,417                 | 6.0                | 20.7                        | 45                          | 17.8                           |

| 1007                   | 2.2                | 22.2                        | 15                          | 19.3                           |

| 59.52                  | 0.48               | 24                          | 3.2                         | 21.6                           |

| 49.68                  | 0.47               | 24                          | 3.1                         | 21.6                           |

| 16.63                  | 0.25               | 24                          | 1.6                         | 22.6                           |

| 1.25                   | 0.088              | 24                          | 0.32                        | 24                             |

| Input Buffers Enabled  |                    |                             |                             |                                |

| 31,250                 | 9.5                | 20                          | 74                          | 17                             |

| 15,625                 | 8.2                | 20.2                        | 63                          | 17.3                           |

| 10,417                 | 7.1                | 20.4                        | 53                          | 17.5                           |

| 1007                   | 2.6                | 21.9                        | 16                          | 19.3                           |

| 59.52                  | 0.62               | 24                          | 3.6                         | 21.4                           |

| 49.68                  | 0.53               | 24                          | 3.3                         | 21.5                           |

| 16.63                  | 0.32               | 24                          | 1.7                         | 22.2                           |

| 1.25                   | 0.089              | 24                          | 0.35                        | 24                             |

<sup>1</sup> Selected rates only, 1000 samples.

#### Table 7. RMS Noise and Peak-to-Peak Resolution vs. Output Data Rate Using the Sinc3 Filter<sup>1</sup>

| Output Data Rate (SPS) | RMS Noise (µV rms) | Effective Resolution (Bits) | Peak-to-Peak Noise (µV p-p) | Peak-to-Peak Resolution (Bits) |

|------------------------|--------------------|-----------------------------|-----------------------------|--------------------------------|

| Input Buffers Disabled |                    |                             |                             |                                |

| 31,250                 | 211                | 15.5                        | 1600                        | 12.5                           |

| 15,625                 | 27.2               | 18.5                        | 205                         | 15.6                           |

| 10,417                 | 7.9                | 20.3                        | 57                          | 17.4                           |

| 1008                   | 1.6                | 22.6                        | 11                          | 19.8                           |

| 59.98                  | 0.38               | 24                          | 2.5                         | 21.9                           |

| 50                     | 0.35               | 24                          | 2.3                         | 22                             |

| 16.67                  | 0.21               | 24                          | 1.1                         | 23.1                           |

| 1.25                   | 0.054              | 24                          | 0.27                        | 24                             |

| Input Buffers Enabled  |                    |                             |                             |                                |

| 31,250                 | 212                | 15.5                        | 1600                        | 12.5                           |

| 15,625                 | 27.7               | 18.5                        | 210                         | 15.5                           |

| 10,417                 | 8.5                | 20.2                        | 63                          | 17.3                           |

| 1008                   | 1.8                | 22.4                        | 13                          | 19.6                           |

| 59.98                  | 0.45               | 24                          | 2.8                         | 21.8                           |

| 50                     | 0.44               | 24                          | 2.5                         | 22                             |

| 16.67                  | 0.24               | 24                          | 1.2                         | 23                             |

| 1.25                   | 0.073              | 24                          | 0.29                        | 24                             |

<sup>1</sup> Selected rates only, 1000 samples.

2676-040

### **GETTING STARTED**

The AD7172-4 offers the user a fast settling, high resolution, multiplexed ADC with high levels of configurability, including the following features:

- Four fully differential or eight single-ended analog inputs.

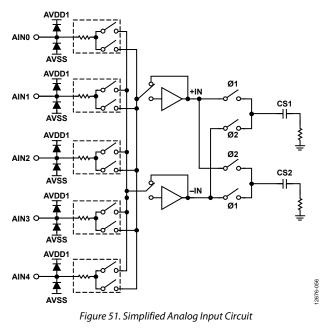

- A crosspoint multiplexer that selects any analog input combination as the input signals to be converted, routing them to the modulator positive or negative input.

- True rail-to-rail buffered analog and reference inputs.

- Fully differential inputs or single-ended inputs relative to any analog input.

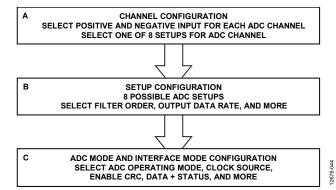

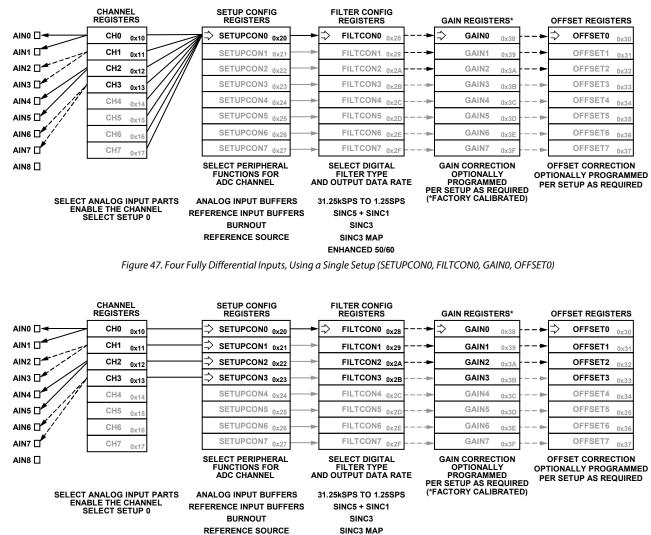

- Per channel configurability—up to eight different setups can be defined. A separate setup can be mapped to each of the channels. Each setup allows the user to configure whether the buffers are enabled or disabled, gain and offset correction, filter type, output data rate, and reference source selection.

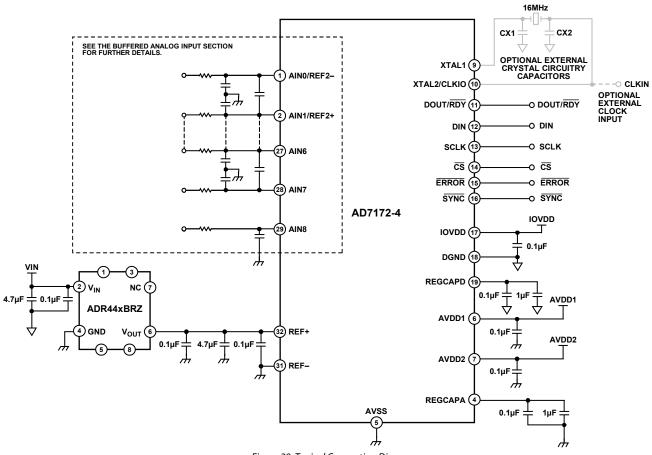

The AD7172-4 includes two separate linear regulator blocks for both the analog and digital circuitry. The analog LDO regulator regulates the AVDD2 supply to 1.8 V, supplying the ADC core. Tie the AVDD1 and AVDD2 supplies together for the easiest connection. If there is already a clean analog supply rail in the system in the range of 2 V (minimum) to 5.5 V (maximum), the user can choose to connect this supply to the AVDD2 input, allowing lower power dissipation.

Figure 39. Typical Connection Diagram

### Data Sheet

The linear regulator for the digital IOVDD supply performs a similar function, regulating the input voltage applied at the IOVDD pin to 1.8 V for the internal digital filtering. The serial interface signals always operate from the IOVDD supply at the pin; meaning, if 3.3 V is applied to the IOVDD pin, the interface logic inputs and outputs operate at this level.

The AD7172-4 can be used across a wide variety of applications, providing high resolution and accuracy. A sample of these scenarios is as follows:

- Fast scanning of analog input channels using the internal multiplexer

- Fast scanning of analog input channels using an external multiplexer with automatic control from the GPIOs

- High resolution at lower speeds in either channel scanning or ADC per channel applications

- Single ADC per channel: the fast low latency output allows further application specific filtering in external micro-controllers, DSPs, or FPGAs

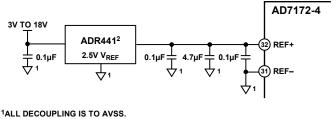

#### **POWER SUPPLIES**

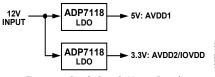

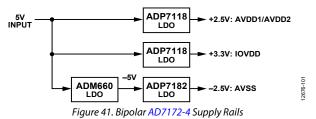

The AD7172-4 has three independent power supply pins: AVDD1, AVDD2, and IOVDD. AVDD1 powers the crosspoint multiplexer and integrated analog and reference input buffers. AVDD1 is referenced to AVSS, and AVDD1 – AVSS = 3.3 V or 5 V. AVDD1 and AVSS can be a single 3.3 V or 5 V supply, or a  $\pm 1.65$  V or  $\pm 2.5$  V split supply. The split supply operation allows true bipolar inputs. When using split supplies, consider the absolute maximum ratings (see the Absolute Maximum Ratings section).

AVDD2 powers the internal 1.8 V analog LDO regulator. This regulator powers the ADC core. AVDD2 is referenced to AVSS, and AVDD2 to AVSS can range from 5.5 V (maximum) to 2 V (minimum).

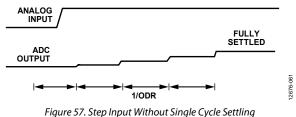

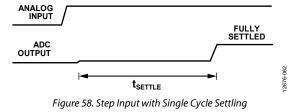

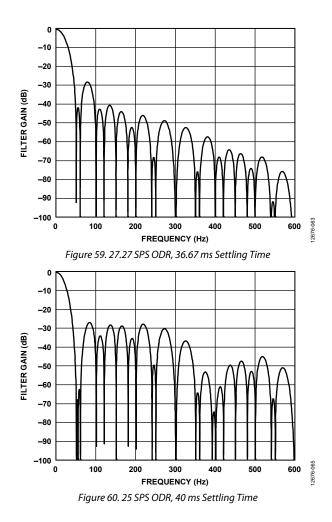

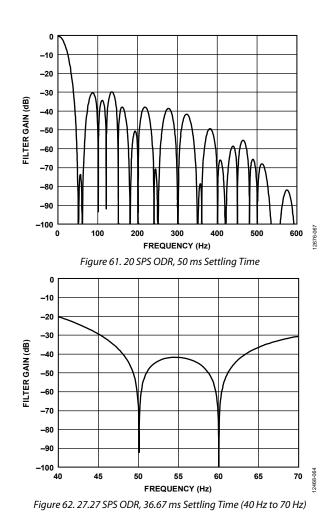

IOVDD powers the internal 1.8 V digital LDO regulator. This regulator powers the digital logic of the ADC. IOVDD sets the voltage levels for the SPI interface of the ADC. IOVDD is referenced to DGND, and IOVDD to DGND can vary from 5.5 V (maximum) to 2 V (minimum).