# Low Cost, 4-Channel, 16-Bit 1 MSPS Pulsar ADC

Enhanced Product AD7655-EP

#### **FEATURES**

4-channel, 16-bit resolution ADC

2 track-and-hold amplifiers

Throughput

1 MSPS (normal mode)

888 kSPS (impulse mode)

Analog input voltage range: 0 V to 5 V

No pipeline delay

Parallel and serial 5 V/3 V interface

SPI®/QSPI™/MICROWIRE™/DSP compatible

Single 5 V supply operation

Power dissipation

120 mW typical

2.6 mW at 10 kSPS

48-lead frame chip scale package (LFCSP)

Pin-to-pin compatible with the AD7654

Low cost

Supports defense and aerospace applications (AQEC standard)

Military temperature range (-55°C to +125°C) Controlled manufacturing baseline Product change notification Qualification data available on request

#### **APPLICATIONS**

AC motor control

3-phase power control

4-channel data acquisition

Uninterrupted power supplies

Communications

#### **GENERAL DESCRIPTION**

The AD7655-EP is a low cost, simultaneous sampling, dual-channel, 16-bit, charge redistribution SAR, analog-to-digital converter that operates from a single 5 V power supply. It contains two low noise, wide bandwidth, track-and-hold amplifiers that allow simultaneous sampling, a high speed 16-bit sampling ADC, an internal conversion clock, error correction circuits, and both serial and parallel system interface ports. Each track-and-hold has a multiplexer in front to provide a 4-channel input ADC. The A0 multiplexer control input allows the choice of simultaneously sampling input pairs INA1/INB1 (A0 = low) or INA2/ INB2 (A0 = high). The part features a very high sampling rate mode (normal) and, for low

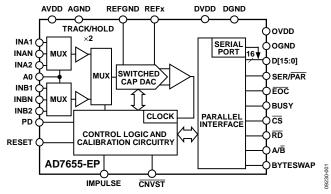

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

Table 1. PulSAR® Selection

| Type/kSPS                               | 100 to 250        | 500 to 570                             | 800 to<br>1000   | >1000            |

|-----------------------------------------|-------------------|----------------------------------------|------------------|------------------|

| Pseudo<br>Differential                  | AD7660/<br>AD7661 | AD7650/<br>AD7652<br>AD7664/<br>AD7666 | AD7653<br>AD7667 |                  |

| True Bipolar<br>True<br>Differential    | AD7663<br>AD7675  | AD7665<br>AD7676                       | AD7671<br>AD7677 | AD7621<br>AD7623 |

| 18 Bit<br>Multichannel/<br>Simultaneous | AD7678            | AD7679<br>AD7654                       | AD7674<br>AD7655 | AD7641           |

power applications, a reduced power mode (impulse) where the power is scaled with the throughput. Operation is specified from  $-55^{\circ}$ C to  $+125^{\circ}$ C.

Full details about this enhanced product are available in the AD7655 data sheet, which should be consulted in conjunction with this data sheet.

#### **PRODUCT HIGHLIGHTS**

- Multichannel ADC.

The AD7655-EP features 4-channel inputs with two sample-and-hold circuits that allow simultaneous sampling.

- Fast Throughput.

The AD7655-EP is a 1 MSPS, charge redistribution, 16-bit SAR ADC with internal error correction circuitry.

- Single-Supply Operation.

The AD7655-EP operates from a single 5 V supply. In impulse mode, its power dissipation decreases with throughput.

- Serial or Parallel Interface.

Versatile parallel or 2-wire serial interface arrangements are compatible with both 3 V and 5 V logic.

## **TABLE OF CONTENTS**

| Features                 |     |

|--------------------------|-----|

| Applications             |     |

| General Description      |     |

| Functional Block Diagram |     |

| Product Highlights       |     |

| Revision History         | . 2 |

| Specifications           | . 3 |

|                          |     |

|                          |     |

| Timing Specifications                        | 5  |

|----------------------------------------------|----|

| Absolute Maximum Ratings                     | 7  |

| ESD Caution                                  | 7  |

| Pin Configurations and Function Descriptions | 8  |

| Outline Dimensions                           | 11 |

| Ordering Guide                               | 12 |

#### **REVISION HISTORY**

#### 1/2018—Rev. A to Rev. B

| Added CP-48-4 Package                   | Universal |

|-----------------------------------------|-----------|

| Change to General Description Section   | 1         |

| Added Figure 5; Renumbered Sequentially | 8         |

| Changes to Figure 4 and Table 6         | 8         |

| Updated Outline Dimensions              | 11        |

| Changes to Ordering Guide               | 11        |

|                                         |           |

|                                         |           |

#### 2/2011—Rev. 0 to Rev. A

| Removed LQFP from Features Section                       | . 1 |

|----------------------------------------------------------|-----|

| Removed Internal Power Dissipation (700 mW) from Table 5 | . 7 |

#### 7/2010—Revision 0: Initial Version

## **SPECIFICATIONS**

$AVDD = DVDD = 5 \ V, OVDD = 2.7 \ V \ to \ 5.25 \ V; \ V_{REF} = 2.5 \ V; \ all \ specifications \ T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted.$

Table 2.

| Parameter                             | Conditions                              | Min       | Тур        | Max        | Unit             |

|---------------------------------------|-----------------------------------------|-----------|------------|------------|------------------|

| RESOLUTION                            |                                         | 16        |            |            | Bits             |

| ANALOG INPUT                          |                                         |           |            |            |                  |

| Voltage Range                         | $V_{INx} - V_{INxN}$                    | 0         |            | $2V_{REF}$ | V                |

| Common-Mode Input Voltage             | V <sub>INxN</sub>                       | -0.1      |            | +0.5       | V                |

| Analog Input CMRR                     | $f_{IN} = 100 \text{ kHz}$              |           | 55         |            | dB               |

| Input Current                         | 1 MSPS throughput                       |           | 45         |            | μΑ               |

| Input Impedance                       |                                         |           |            |            | 1                |

| THROUGHPUT SPEED                      |                                         |           |            |            |                  |

| Complete Cycle (2 Channels)           | Normal mode                             |           |            | 2          | μs               |

| Throughput Rate                       | Normal mode                             | 0         |            | 1          | MSPS             |

| Complete Cycle (2 Channels)           | Impulse mode                            |           |            | 2.25       | μs               |

| Throughput Rate                       | Impulse mode                            | 0         |            | 888        | kSPS             |

| DC ACCURACY                           |                                         |           |            |            |                  |

| Integral Linearity Error <sup>1</sup> |                                         | -6        |            | +6         | LSB <sup>2</sup> |

| No Missing Codes                      |                                         | 15        |            |            | Bits             |

| Transition Noise                      |                                         |           | 0.8        |            | LSB              |

| Full-Scale Error                      | T <sub>MIN</sub> to T <sub>MAX</sub>    |           | ±0.25      | ±0.5       | % of FSR         |

| Full-Scale Error Drift                |                                         |           | ±2         |            | ppm/°C           |

| Unipolar Zero Error                   | T <sub>MIN</sub> to T <sub>MAX</sub>    |           |            | ±0.25      | % of FSR         |

| Unipolar Zero Error Drift             |                                         |           | ±0.8       |            | ppm/°C           |

| Power Supply Sensitivity              | $AVDD = 5 V \pm 5\%$                    |           | ±0.8       |            | LSB              |

| AC ACCURACY                           |                                         |           |            |            |                  |

| Signal-to-Noise                       | f <sub>IN</sub> = 100 kHz               |           | 86         |            | dB <sup>3</sup>  |

| Spurious-Free Dynamic Range           | $f_{IN} = 100 \text{ kHz}$              |           | 98         |            | dB               |

| Total Harmonic Distortion             | f <sub>IN</sub> = 100 kHz               |           | <b>-96</b> |            | dB               |

| Signal-to-Noise and Distortion        | $f_{IN} = 100 \text{ kHz}$              |           | 86         |            | dB               |

| 3                                     | f <sub>IN</sub> = 100 kHz, -60 dB input |           | 30         |            | dB               |

| Channel-to-Channel Isolation          | f <sub>IN</sub> = 100 kHz               |           | <b>-92</b> |            | dB               |

| –3 dB Input Bandwidth                 |                                         |           | 10         |            | MHz              |

| SAMPLING DYNAMICS                     |                                         |           |            |            |                  |

| Aperture Delay                        |                                         |           | 2          |            | ns               |

| Aperture Delay Matching               |                                         |           | 30         |            | ps               |

| Aperture Jitter                       |                                         |           | 5          |            | ps rms           |

| Transient Response                    | Full-scale step                         |           |            | 250        | ns               |

| REFERENCE                             | ·                                       |           |            |            |                  |

| External Reference Voltage Range      |                                         | 2.3       | 2.5        | AVDD/2     | V                |

| External Reference Current Drain      | 1 MSPS throughput                       |           | 180        |            | μΑ               |

| DIGITAL INPUTS                        | 3 '                                     |           |            |            | '                |

| Logic Levels                          |                                         |           |            |            |                  |

| V <sub>IL</sub>                       |                                         | -0.3      |            | +0.8       | V                |

| $V_{IH}$                              |                                         | +2.0      |            | DVDD + 0.3 | V                |

| I <sub>IL</sub>                       |                                         | -1        |            | +1         | μΑ               |

| I <sub>IH</sub>                       |                                         | -1        |            | +1         | μΑ               |

| DIGITAL OUTPUTS                       |                                         |           |            |            | +                |

| Data Format <sup>4</sup>              |                                         |           |            |            |                  |

| Pipeline Delay <sup>5</sup>           |                                         |           |            |            |                  |

| VoL                                   | I <sub>SINK</sub> = 1.6 mA              |           |            | 0.4        | V                |

| Vон                                   | $I_{\text{SOURCE}} = -500  \mu\text{A}$ | OVDD – 0. | 2          |            | V                |

| Parameter                      | Conditions                           | Min  | Тур  | Max               | Unit |

|--------------------------------|--------------------------------------|------|------|-------------------|------|

| POWER SUPPLIES                 |                                      |      |      |                   |      |

| Specified Performance          |                                      |      |      |                   |      |

| AVDD                           |                                      | 4.75 | 5    | 5.25              | V    |

| DVDD                           |                                      | 4.75 | 5    | 5.25              | V    |

| OVDD                           |                                      | 2.7  |      | 5.25 <sup>6</sup> | V    |

| Operating Current <sup>7</sup> | 1 MSPS throughput                    |      |      |                   |      |

| AVDD                           |                                      |      | 15.5 |                   | mA   |

| DVDD                           |                                      |      | 8.5  |                   | mA   |

| OVDD                           |                                      |      | 100  |                   | μΑ   |

| Power Dissipation              | 1 MSPS throughput <sup>7</sup>       |      | 120  | 135               | mW   |

|                                | 20 kSPS throughput <sup>8</sup>      |      | 2.6  |                   | mW   |

|                                | 888 kSPS throughput <sup>8</sup>     |      | 114  | 125               | mW   |

| TEMPERATURE RANGE <sup>9</sup> |                                      |      |      |                   |      |

| Specified Performance          | T <sub>MIN</sub> to T <sub>MAX</sub> | -55  |      | +125              | °C   |

$<sup>^1</sup>$  Linearity is tested using endpoints, not best fit.  $^2$  LSB means least significant bit. With the 0 V to 5 V input range, 1 LSB is 76.294  $\mu$ V.  $^3$  All specifications in dB are referred to as full-scale input, FS. Tested with an input signal at 0.5 dB below full scale unless otherwise specified.

<sup>&</sup>lt;sup>4</sup> Parallel or serial 16 bit.

<sup>&</sup>lt;sup>5</sup> Conversion results are available immediately after completed conversion. <sup>6</sup> The maximum should be the minimum of 5.25 V and DVDD + 0.3 V.

<sup>7</sup> In normal mode; tested in parallel reading mode.

8 In impulse mode; tested in parallel reading mode.

9 Consult sales for extended temperature range.

#### **TIMING SPECIFICATIONS**

$AVDD = DVDD = 5 \ V, OVDD = 2.7 \ V \ to \ 5.25 \ V; V_{REF} = 2.5 \ V; all \ specifications \ T_{MIN} \ to \ T_{MAX}, unless \ otherwise \ noted.$

Table 3.

| Parameter                                                           | Symbol                | Min    | Тур         | Max    | Unit |

|---------------------------------------------------------------------|-----------------------|--------|-------------|--------|------|

| CONVERSION AND RESET                                                |                       |        |             |        |      |

| Convert Pulse Width                                                 | t <sub>1</sub>        | 5      |             |        | ns   |

| Time Between Conversions                                            |                       |        |             |        |      |

| (Normal Mode/Impulse Mode)                                          | t <sub>2</sub>        | 2/2.25 |             |        | μs   |

| CNVST Low to BUSY High Delay                                        | t <sub>3</sub>        |        |             | 32     | ns   |

| BUSY High All Modes Except in Master Serial Read After Convert Mode |                       |        |             |        |      |

| (Normal Mode/Impulse Mode)                                          | t <sub>4</sub>        |        |             | 1.75/2 | μs   |

| Aperture Delay                                                      | <b>t</b> <sub>5</sub> |        | 2           |        | ns   |

| End of Conversions to BUSY Low Delay                                | <b>t</b> <sub>6</sub> | 10     |             |        | ns   |

| Conversion Time                                                     |                       |        |             |        |      |

| (Normal Mode/Impulse Mode)                                          | t <sub>7</sub>        |        |             | 1.75/2 | μs   |

| Acquisition Time                                                    | t <sub>8</sub>        | 250    |             |        | ns   |

| RESET Pulse Width                                                   | t <sub>9</sub>        | 10     |             |        | ns   |

| CNVST Low to EOC High Delay                                         | t <sub>10</sub>       |        |             | 30     | ns   |

| EOC High for Channel A Conversion                                   |                       |        |             |        |      |

| (Normal Mode/Impulse Mode)                                          | t <sub>11</sub>       |        |             | 1/1.25 | μs   |

| EOC Low after Channel A Conversion                                  | t <sub>12</sub>       | 45     |             |        | ns   |

| EOC High for Channel B Conversion                                   | t <sub>13</sub>       |        |             | 0.75   | μs   |

| Channel Selection Setup Time                                        | t <sub>14</sub>       | 250    |             |        | ns   |

| Channel Selection Hold Time                                         | <b>t</b> 15           |        |             | 30     | ns   |

| PARALLEL INTERFACE MODES                                            |                       |        |             |        |      |

| CNVST Low to DATA Valid Delay                                       | t <sub>16</sub>       |        |             | 1.75/2 | μs   |

| DATA Valid to BUSY Low Delay                                        | t <sub>17</sub>       | 14     |             | 5, =   | ns   |

| Bus Access Request to DATA Valid                                    | t <sub>18</sub>       | ' '    |             | 40     | ns   |

| Bus Relinquish Time                                                 | t <sub>19</sub>       | 5      |             | 15     | ns   |

| A/B Low to Data Valid Delay                                         | t <sub>20</sub>       |        |             | 40     | ns   |

| MASTER SERIAL INTERFACE MODES                                       |                       |        |             |        | 1    |

| CS Low to SYNC Valid Delay                                          | t <sub>21</sub>       |        |             | 10     | ns   |

| CS Low to Internal SCLK Valid Delay <sup>1</sup>                    | t <sub>22</sub>       |        |             | 10     | ns   |

| CS Low to SDOUT Delay                                               |                       |        |             | 10     |      |

| •                                                                   | t <sub>23</sub>       |        |             | 10     | ns   |

| CNVST Low to SYNC Delay, Read During Convert                        |                       |        | 250/500     |        |      |

| (Normal Mode/Impulse Mode)                                          | t <sub>24</sub>       |        | 250/500     |        | ns   |

| SYNC Asserted to SCLK First Edge Delay                              | t <sub>25</sub>       | 3      |             | 40     | ns   |

| Internal SCK Period <sup>2</sup>                                    | t <sub>26</sub>       | 23     |             | 40     | ns   |

| Internal SCLK High <sup>2</sup>                                     | t <sub>27</sub>       | 12     |             |        | ns   |

| Internal SCLK Low <sup>2</sup>                                      | t <sub>28</sub>       | 7      |             |        | ns   |

| SDOUT Valid Setup Time <sup>2</sup>                                 | t <sub>29</sub>       | 4      |             |        | ns   |

| SDOUT Valid Hold Time <sup>2</sup>                                  | t <sub>30</sub>       | 2      |             |        | ns   |

| SCLK Last Edge to SYNC Delay <sup>2</sup>                           | t <sub>31</sub>       | 1      |             |        | ns   |

| CS High to SYNC High-Z                                              | t <sub>32</sub>       |        |             | 10     | ns   |

| CS High to Internal SCLK High-Z                                     | t <sub>33</sub>       |        |             | 10     | ns   |

| CS High to SDOUT High-Z                                             | t <sub>34</sub>       |        |             | 10     | ns   |

| BUSY High in Master Serial Read after Convert <sup>2</sup>          | t <sub>35</sub>       |        | See Table 4 |        |      |

| CNVST Low to SYNC Asserted Delay                                    |                       |        |             |        |      |

| (Normal Mode/Impulse Mode)                                          | t <sub>36</sub>       |        | 0.75/1      |        | μs   |

| SYNC Deasserted to BUSY Low Delay                                   | t <sub>37</sub>       |        | 25          |        | ns   |

| Parameter                                | Symbol          | Min | Тур | Max | Unit |

|------------------------------------------|-----------------|-----|-----|-----|------|

| SLAVE SERIAL INTERFACE MODES             |                 |     |     |     |      |

| External SCLK Setup Time                 | t <sub>38</sub> | 5   |     |     | ns   |

| External SCLK Active Edge to SDOUT Delay | t <sub>39</sub> | 3   |     | 18  | ns   |

| SDIN Setup Time                          | t <sub>40</sub> | 5   |     |     | ns   |

| SDIN Hold Time                           | t <sub>41</sub> | 5   |     |     | ns   |

| External SCLK Period                     | t <sub>42</sub> | 25  |     |     | ns   |

| External SCLK High                       | t <sub>43</sub> | 10  |     |     | ns   |

| External SCLK Low                        | t <sub>44</sub> | 10  |     |     | ns   |

$<sup>^1</sup>$  In serial interface modes, the SYNC, SCLK, and SDOUT timings are defined with a maximum load  $C_L$  of 10 pF; otherwise  $C_L$  is 60 pF maximum.  $^2$  In serial master read during convert mode. See Table 4 for serial master read after convert mode.

Table 4. Serial Clock Timings in Master Read After Convert

| DIVSCLK[1]                            |                                                            | 0    | 0    | 1    | 1     |      |

|---------------------------------------|------------------------------------------------------------|------|------|------|-------|------|

| DIVSCLK[0]                            | Symbol                                                     | 0    | 1    | 0    | 1     | Unit |

| SYNC to SCLK First Edge Delay Minimum | SYNC to SCLK First Edge Delay Minimum t <sub>25</sub> 3 17 |      |      |      | 17    | ns   |

| Internal SCLK Period Minimum          | t <sub>26</sub>                                            | 25   | 50   | 100  | 200   | ns   |

| Internal SCLK Period Typical          | t <sub>26</sub>                                            | 40   | 70   | 140  | 280   | ns   |

| Internal SCLK High Minimum            | t <sub>27</sub>                                            | 12   | 22   | 50   | 100   | ns   |

| Internal SCLK Low Minimum             | t <sub>28</sub>                                            | 7    | 21   | 49   | 99    | ns   |

| SDOUT Valid Setup Time Minimum        | t <sub>29</sub>                                            | 4    | 18   | 18   | 18    | ns   |

| SDOUT Valid Hold Time Minimum         | t <sub>30</sub>                                            | 2    | 4    | 30   | 80    | ns   |

| SCLK Last Edge to SYNC Delay Minimum  | <b>t</b> <sub>31</sub>                                     | 1    | 3    | 30   | 80    | ns   |

| Busy High Width Maximum (Normal)      | t <sub>35</sub>                                            | 3.25 | 4.25 | 6.25 | 10.75 | μs   |

| Busy High Width Maximum (Impulse)     | t <sub>35</sub>                                            | 3.5  | 4.5  | 6.5  | 11    | μs   |

### **ABSOLUTE MAXIMUM RATINGS**

Table 5.

| Table 3.                               |                                 |

|----------------------------------------|---------------------------------|

| Parameter                              | Values                          |

| Analog Input                           |                                 |

| INAx, INBx, REFx, INxN, REFGND         | AVDD + 0.3 V to<br>AGND – 0.3 V |

| Ground Voltage Differences             |                                 |

| AGND, DGND, OGND                       | ±0.3 V                          |

| Supply Voltages                        |                                 |

| AVDD, DVDD, OVDD                       | −0.3 V to +7 V                  |

| AVDD to DVDD, AVDD to OVDD             | ±7 V                            |

| DVDD to OVDD                           | −0.3 V to +7 V                  |

| Digital Inputs                         | −0.3 V to DVDD + 0.3 V          |

| Internal Power Dissipation             | 2.5 W                           |

| Junction Temperature                   | 150°C                           |

| Storage Temperature Range <sup>1</sup> | −65°C to +150°C                 |

| Lead Temperature Range                 |                                 |

| (Soldering 10 sec)                     | 300°C                           |

<sup>&</sup>lt;sup>1</sup> Specification is for device in free air: 48-lead LFCSP,  $\theta_{JA} = 26^{\circ}$ C/W.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

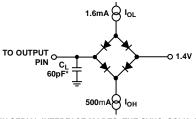

\*IN SERIAL INTERFACE MODES, THE SYNC, SCLK, AND SDOUT TIMINGS ARE DEFINED WITH A MAXIMUM LOAD  $C_L$  OF 10pF; OTHERWISE, THE LOAD IS 60pF MAXIMUM.

Figure 2. Load Circuit for Digital Interface Timing

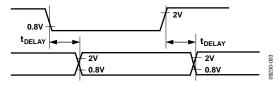

Figure 3. Voltage Reference Levels for Timing

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

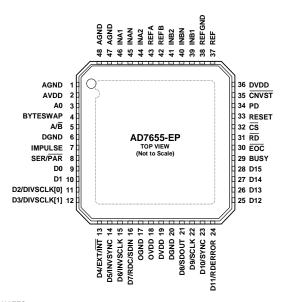

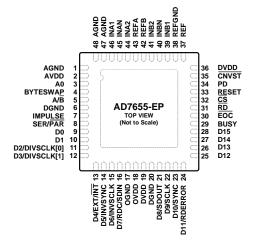

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

NOTES

1. EXPOSED PAD. THE EPAD IS CONNECTED TO GROUND; HOWEVER, THIS CONNECTION IS NOT REQUIRED TO MEET SPECIFIED PERFORMANCE.

Figure 4. 48-Lead LFCSP (CP-48-1)

NOTES

1. EXPOSED PAD. THE EPAD IS CONNECTED TO GROUND; HOWEVER, THIS CONNECTION IS NOT REQUIRED TO MEET SPECIFIED PERFORMANCE.

Figure 5. 48-Lead LFCSP (CP-48-4)

**Table 6. Pin Function Descriptions**

| Pin No.   | Mnemonic     | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|--------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 47, 48 | AGND         | Р                 | Analog Power Ground Pin.                                                                                                                                                                                                                                                                                                                                                                   |

| 2         | AVDD         | Р                 | Input Analog Power Pin. Nominally 5 V.                                                                                                                                                                                                                                                                                                                                                     |

| 3         | A0           | DI                | Multiplexer Select. When LOW, the analog inputs INA1 and INB1 are sampled simultaneously, then converted. When HIGH, the analog inputs INA2 and INB2 are sampled simultaneously, then converted.                                                                                                                                                                                           |

| 4         | BYTESWAP     | DI                | Parallel Mode Selection (8 Bit, 16 Bit). When LOW, the LSB is output on D[7:0] and the MSB is output on D[15:8]. When HIGH, the LSB is output on D[15:8] and the MSB is output on D[7:0].                                                                                                                                                                                                  |

| 5         | A/B          | DI                | Data Channel Selection. In parallel mode, when LOW, the data from Channel B is read. When HIGH, the data from Channel A is read. In serial mode, when HIGH, Channel A is output first followed by Channel B. When LOW, Channel B is output first followed by Channel A.                                                                                                                    |

| 6, 20     | DGND         | Р                 | Digital Power Ground.                                                                                                                                                                                                                                                                                                                                                                      |

| 7         | IMPULSE      | DI                | Mode Selection. When HIGH, this input selects a reduced power mode. In this mode, the power dissipation is approximately proportional to the sampling rate.                                                                                                                                                                                                                                |

| 8         | SER/PAR      | DI                | Serial/Parallel Selection Input. When LOW, the parallel port is selected; when HIGH, the serial interface mode is selected and some bits of the DATA bus are used as a serial port.                                                                                                                                                                                                        |

| 9, 10     | D[0:1]       | DO                | Bit 0 and Bit 1 of the Parallel Port Data Output Bus. When SER/PAR is HIGH, these outputs are in high impedance.                                                                                                                                                                                                                                                                           |

| 11, 12    | D[2:3] or    | DI/O              | When SER/PAR is LOW, these outputs are used as Bit 2 and Bit 3 of the Parallel Port Data Output Bus.                                                                                                                                                                                                                                                                                       |

|           | DIVSCLK[0:1] |                   | When SER/PAR is HIGH, EXT/INT is LOW, and RDC/SDIN is LOW, which is the serial master read after convert mode. These inputs, part of the serial port, are used to slow down the internal serial clock that clocks the data output. In the other serial modes, these inputs are not used.                                                                                                   |

| 13        | D[4]         | DI/O              | When SER/PAR is LOW, this output is used as Bit 4 of the Parallel Port Data Output Bus.                                                                                                                                                                                                                                                                                                    |

|           | or EXT/INT   |                   | When SER/PAR is HIGH, this input, part of the serial port, is used as a digital select input for choosing the internal or an external data clock called, respectively, master and slave mode. With EXT/INT tied LOW, the internal clock is selected on SCLK output. With EXT/INT set to a logic HIGH, output data is synchronized to an external clock signal connected to the SCLK input. |

| Pin No.      | Mnemonic     | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                       |  |

|--------------|--------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 14           | D[5]         | DI/O              | When SER/PAR is LOW, this output is used as Bit 5 of the Parallel Port Data Output Bus.                                                                                                                                                                                                                                           |  |

|              | or INVSYNC   |                   | When SER/PAR is HIGH, this input, part of the serial port, is used to select the active state of the SYNC signal in Master modes. When LOW, SYNC is active HIGH. When HIGH, SYNC is active LOW.                                                                                                                                   |  |

| 15           | D[6]         | DI/O              | When SER/PAR is LOW, this output is used as Bit 6 of the parallel port data output bus.                                                                                                                                                                                                                                           |  |

|              | or INVSCLK   |                   | When SER/PAR is HIGH, this input, part of the serial port, is used to invert the SCLK signal. It is active in both master and slave modes.                                                                                                                                                                                        |  |

| 16           | D[7]         | DI/O              | When SER/PAR is LOW, this output is used as Bit 7 of the Parallel Port Data Output Bus.                                                                                                                                                                                                                                           |  |

|              | or RDC/SDIN  |                   | When SER/PAR is HIGH, this input, part of the serial port, is used as either an external data input or a read mode selection input, depending on the state of EXT/INT.                                                                                                                                                            |  |

|              |              |                   | When EXT/INT is HIGH, RDC/SDIN can be used as a data input to daisy-chain the conversion results from two or more ADCs onto a single SDOUT line. The digital data level on SDIN is output on SDOUT with a delay of 32 SCLK periods after the initiation of the read sequence.                                                     |  |

|              |              |                   | When EXT/INT is LOW, RDC/SDIN is used to select the read mode. When RDC/SDIN is HIGH, the previous data is output on SDOUT during conversion. When RDC/SDIN is LOW, the data can be output on SDOUT only when the conversion is complete.                                                                                         |  |

| 17           | OGND         | Р                 | Input/Output Interface Digital Power Ground.                                                                                                                                                                                                                                                                                      |  |

| 18           | OVDD         | P                 | Input/Output Interface Digital Power. Nominally at the same supply as the supply of the host inter(5 V or 3 V).                                                                                                                                                                                                                   |  |

| 19, 36<br>21 | DVDD<br>D[8] | P<br>DO           | Digital Power. Nominally at 5 V. When SER/PAR is LOW, this output is used as Bit 8 of the Parallel Port Data Output Bus.                                                                                                                                                                                                          |  |

| 21           | or SDOUT     |                   | When SER/PAR is HIGH, this output, part of the serial port, is used as a serial data output synchronized                                                                                                                                                                                                                          |  |

|              | 01 30001     |                   | to SCLK. Conversion results are stored in a 32-bit on-chip register. The AD7655-EP provides the two conversion results, MSB first, from its internal shift register. The order of channel outputs is controlled by A/B. In serial mode, when EXT/INT is LOW, SDOUT is valid on both edges of SCLK.                                |  |

|              |              |                   | In serial mode, when EXT/INT is HIGH:                                                                                                                                                                                                                                                                                             |  |

|              |              |                   | If INVSCLK is LOW, SDOUT is updated on the SCLK rising edge and valid on the next falling edge.                                                                                                                                                                                                                                   |  |

|              |              |                   | If INVSCLK is HIGH, SDOUT is updated on the SCLK falling edge and valid on the next rising edge.                                                                                                                                                                                                                                  |  |

| 22           | D[9]         | DI/O              | When SER/PAR is LOW, this output is used as Bit 9 of the Parallel Port Data Output Bus.                                                                                                                                                                                                                                           |  |

|              | or SCLK      |                   | When SER/PAR is HIGH, this pin, part of the serial port, is used as a serial data clock input or output, depends upon the logic state of the EXT/INT pin. The active edge where the data SDOUT is updated                                                                                                                         |  |

| 23           | D[10]        | DO                | depends on the logic state of the INVSCLK pin.  When SER/PAR is LOW, this output is used as Bit 10 of the Parallel Port Data Output Bus.                                                                                                                                                                                          |  |

| 23           | or SYNC      |                   | When SER/PAR is HIGH, this output, part of the serial port, is used as a digital output frame                                                                                                                                                                                                                                     |  |

|              | OI STINE     |                   | synchronization for use with the internal data clock (EXT/INT = Logic LOW).                                                                                                                                                                                                                                                       |  |

|              |              |                   | When a read sequence is initiated and INVSYNC is LOW, SYNC is driven HIGH and frames SDOUT. After the first channel is output, SYNC is pulsed LOW. When a read sequence is initiated and INVSYNC is HIGH, SYNC is driven LOW and remains LOW while SDOUT output is valid. After the first channel is output, SYNC is pulsed HIGH. |  |

| 24           | D[11]        | DO                | When SER/PAR is LOW, this output is used as Bit 11 of the Parallel Port Data Output Bus.                                                                                                                                                                                                                                          |  |

|              | or RDERROR   |                   | When SER/PAR is HIGH and EXT/INT is HIGH, this output, part of the serial port, is used as an                                                                                                                                                                                                                                     |  |

|              |              |                   | incomplete read error flag. In slave mode, when a data read is started but not complete when the                                                                                                                                                                                                                                  |  |

| 25. 20       | D[12.15]     | 200               | following conversion is complete, the current data is lost and RDERROR is pulsed HIGH.                                                                                                                                                                                                                                            |  |

| 25 to 28     | D[12:15]     | DO                | Bit 12 to Bit 15 of the parallel port data output bus. When SER/PAR is HIGH, these outputs are in high impedance.                                                                                                                                                                                                                 |  |

| 29           | BUSY         | DO                | Busy Output. Transitions HIGH when a conversion is started and remains HIGH until the two conversions are complete and the data is latched into the on-chip shift register. The falling edge of BUSY can be used as a data ready clock signal.                                                                                    |  |

| 30           | EOC          | DO                | End of Convert Output. Goes LOW at each channel conversion.                                                                                                                                                                                                                                                                       |  |

| 31           | RD           | DI                | Read Data. When $\overline{\text{CS}}$ and $\overline{\text{RD}}$ are both LOW, the interface parallel or serial output bus is enabled.                                                                                                                                                                                           |  |

| 32           | <u>cs</u>    | DI                | Chip Select. When $\overline{CS}$ and $\overline{RD}$ are both LOW, the interface parallel or serial output bus is enabled. $\overline{CS}$ is also used to gate the external serial clock.                                                                                                                                       |  |

| 33           | RESET        | DI                | Reset Input. When set to a logic HIGH, reset the AD7655-EP. Current conversion, if any, is aborted. If not used, this pin could be tied to DGND.                                                                                                                                                                                  |  |

| 34           | PD           | DI                | Power-Down Input. When set to a logic HIGH, power consumption is reduced and conversions are inhibited after the current conversion is completed.                                                                                                                                                                                 |  |

| Pin No. | Mnemonic                  | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                 |  |  |

|---------|---------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 35      | CNVST                     | DI                | Start Conversion. A falling edge on CNVST puts the internal sample-and-hold into the hold state a initiates a conversion. In impulse mode (IMPULSE = HIGH), if CNVST is held LOW when the acquisit phase (ta) is complete, the internal sample-and-hold is put into the hold state and a conversion is immediately started. |  |  |

| 37      | REF                       | Al                | This input pin is used to provide a reference to the converter.                                                                                                                                                                                                                                                             |  |  |

| 38      | REFGND                    | Al                | Reference Input Analog Ground.                                                                                                                                                                                                                                                                                              |  |  |

| 39, 41  | INB1, INB2                | Al                | Channel B Analog Inputs.                                                                                                                                                                                                                                                                                                    |  |  |

| 40, 45  | INBN, INAN                | Al                | Analog Inputs Ground Senses. Allow to sense each channel ground independently.                                                                                                                                                                                                                                              |  |  |

| 42, 43  | REFB, REFA                | Al                | These inputs are the references applied to Channel A and Channel B, respectively.                                                                                                                                                                                                                                           |  |  |

| 44, 46  | , 46 INA2, INA1 AI Channe |                   | Channel A Analog Inputs.                                                                                                                                                                                                                                                                                                    |  |  |

|         | EPAD                      |                   | Exposed Pad. The exposed pad is connected to ground; however, this connection is not required to meet specified performance.                                                                                                                                                                                                |  |  |

$<sup>^{1}</sup>$  Al = input; DI = digital input; DO = digital output; DI/O = bidirectional digital; P = power.

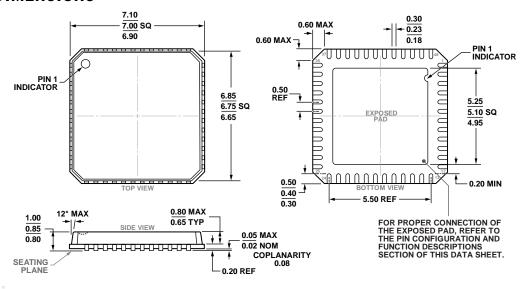

## **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MO-220-VKKD-2

Figure 6. 48-Lead Lead Frame Chip Scale Package [LFCSP] 7 mm × 7 mm Body and 0.85 mm Package Height (CP-48-1) Dimensions shown in millimeters

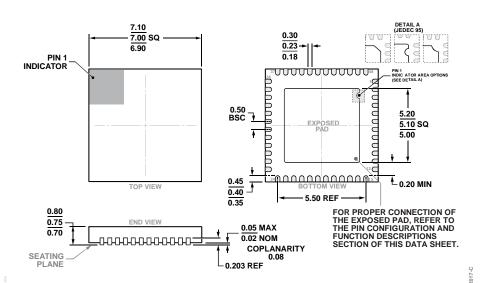

COMPLIANT TO JEDEC STANDARDS MO-220-WKKD-4

Figure 7. 48-Lead Lead Frame Chip Scale Package [LFCSP] 7 mm × 7 mm Body and 0.75 mm Package Height (CP-48-4) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                           | Package Option |

|--------------------|-------------------|-----------------------------------------------|----------------|

| AD7655SCP-EP-RL    | −55°C to +125°C   | 48-Lead Lead Frame Chip Scale Package [LFCSP] | CP-48-1        |

| AD7655SCPZ-EP-RL   | −55°C to +125°C   | 48-Lead Lead Frame Chip Scale Package [LFCSP] | CP-48-4        |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Data Conversion IC Development Tools category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below:

EVAL-AD5063EBZ EVAL-AD5422LFEBZ EVAL-AD7265EDZ EVAL-AD7641EDZ EVAL-AD7674EDZ EVAL-AD7719EBZ EVAL-AD7767-1EDZ EVAL-AD7995EBZ AD9114-DPG2-EBZ AD9211-200EBZ AD9251-20EBZ AD9251-65EBZ AD9255-125EBZ AD9284-250EBZ AD9613-170EBZ AD9627-125EBZ AD9629-20EBZ AD9709-EBZ AD9716-DPG2-EBZ AD9737A-EBZ AD9787-DPG2-EBZ AD9993-EBZ DAC8555EVM ADS5482EVM ADS8372EVM EVAL-AD5061EBZ EVAL-AD5062EBZ EVAL-AD5443-DBRDZ EVAL-AD5570SDZ EVAL-AD7450ASDZ EVAL-AD7677EDZ EVAL-AD7992EBZ EVAL-AD7994EBZ AD9119-MIX-EBZ AD9148-M5375-EBZ AD9204-80EBZ AD9233-125EBZ AD9265-105EBZ AD9265-80EBZ AD9608-125EBZ AD9629-80EBZ AD9648-125EBZ AD9649-20EBZ AD9650-80EBZ AD9765-EBZ AD9767-EBZ AD9778A-DPG2-EBZ ADS8322EVM LM96080EB/NOPB EVAL-AD5445SDZ