µModule data acquisition system

**Includes critical passive components**

16-bit resolution with no missing codes

INL: ±8 ppm typical and 20 ppm maximum

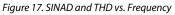

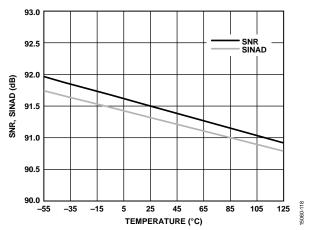

SNR: 91.5 dB typical at 10 kHz (unity gain)

Zero error: ±0.06 mV typical (unity gain)

21 mW typical at 1 MSPS (ADAQ7980)

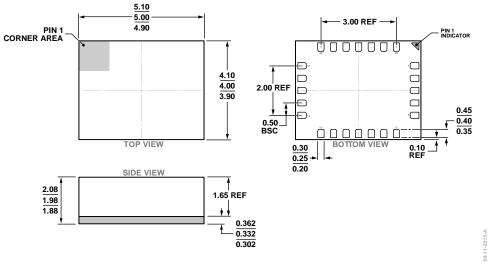

Small, 24-lead, 5 mm × 4 mm LGA package

3500 V human body model (HBM)

Flexible power-down modes

Automated test equipment (ATE)

**Battery powered instrumentation**

16.5 mW typical at 500 kSPS (ADAQ7988)

Zero error temperature drift: 1.3 µV/°C maximum

1250 V field-induced charged device model (FICDM)

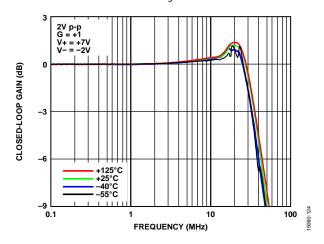

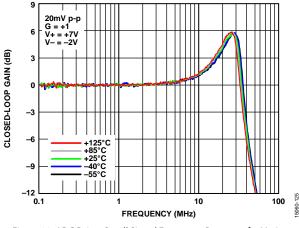

Wide operating temperature range: -55°C to +125°C

50% PCB area savings

logic interface

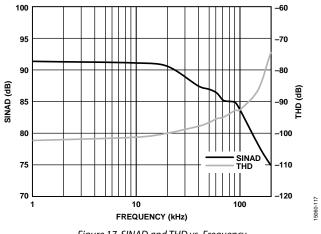

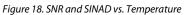

THD: -105 dB at 10 kHz

Low power dissipation

**Excellent ESD ratings**

**APPLICATIONS**

Communications

**Data acquisition**

**Process control**

**Medical instruments**

**GENERAL DESCRIPTION**

**High performance**

All active components designed by Analog Devices, Inc.

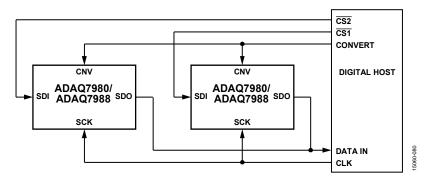

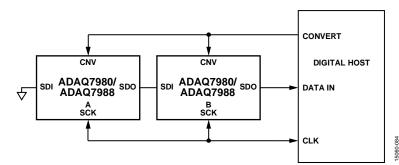

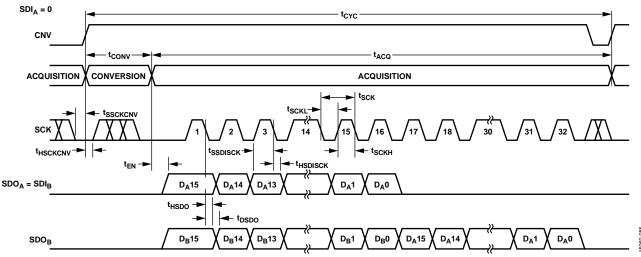

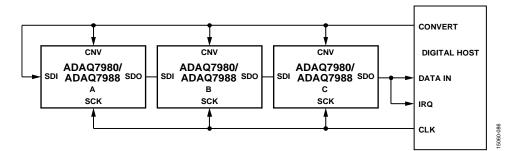

SPI-/QSPI-/MICROWIRE<sup>™</sup>-/DSP-compatible serial interface Daisy-chain multiple ADAQ7980/ADAQ7988 devices

Throughput: 1 MSPS (ADAQ7980) and 500 kSPS (ADAQ7988)

Versatile supply configuration with 1.8 V/2.5 V/3 V/5 V

## 16-Bit, 1 MSPS µModule Data Acquisition System

## **Data Sheet**

FEATURES Easy to use

## ADAQ7980/ADAQ7988

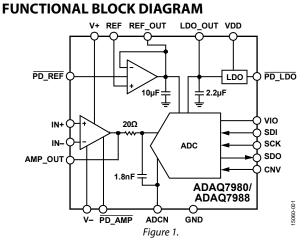

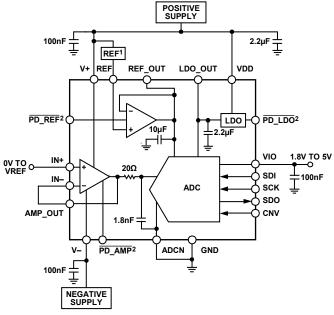

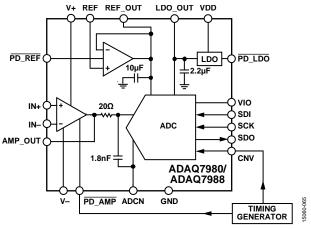

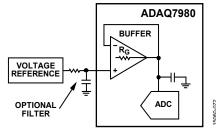

The ADAQ7980/ADAQ7988 contain a high accuracy, low power, 16-bit SAR ADC, a low power, high bandwidth, high input impedance ADC driver, a low power, stable reference buffer, and an efficient power management block. Housed within a tiny, 5 mm × 4 mm LGA package, these products simplify the design process for data acquisition systems. The level of system integration of the ADAQ7980/ADAQ7988 solves many design challenges, while the devices still provide the flexibility of a configurable ADC driver feedback loop to allow gain and/or common-mode adjustments. A set of four device supplies provides optimal system performance; however, single-supply operation is possible with minimal impact on device operating specifications.

The ADAQ7980/ADAQ7988 integrate within a compact, integrated circuit (IC)-like form factor key components commonly used in data acquisition signal chain designs. The  $\mu$ Module family transfers the design burden of component selection, optimization, and layout from designer to device, shortening overall design time, system troubleshooting, and ultimately improving time to market.

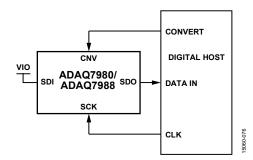

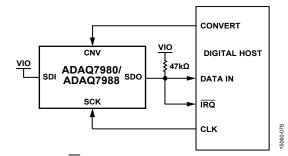

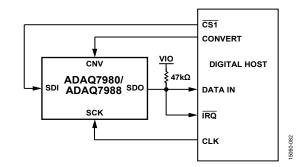

The serial peripheral interface (SPI)-compatible serial interface features the ability to daisy-chain multiple devices on a single, 3-wire bus and provides an optional busy indicator. The user interface is compatible with 1.8 V, 2.5 V, 3 V, or 5 V logic.

Specified operation of these devices is from -55°C to +125°C.

#### Table 1. Integrated SAR ADC µModules

| Туре   | 500 kSPS | 1000 kSPS |

|--------|----------|-----------|

| 16-Bit | ADAQ7988 | ADAQ7980  |

Rev. A

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

The ADAQ7980/ADAQ7988 are 16-bit analog-to-digital converter

common signal processing and conditioning blocks into a system

in package (SiP) design that supports a variety of applications. These devices contain the most critical passive components,

eliminating many of the design challenges associated with traditional signal chains that use successive approximation register (SAR) ADCs. These passive components are crucial to

achieving the specified device performance.

(ADC) µModule<sup>®</sup> data acquisition systems that integrate four

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2017 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

\_\_\_\_

## TABLE OF CONTENTS

| Features                                      |

|-----------------------------------------------|

| Applications1                                 |

| General Description1                          |

| Functional Block Diagram1                     |

| Revision History 2                            |

| Specifications                                |

| Dual-Supply Configuration                     |

| Single-Supply Configuration7                  |

| Timing Specifications11                       |

| Absolute Maximum Ratings                      |

| Thermal Data                                  |

| Thermal Resistance                            |

| ESD Caution13                                 |

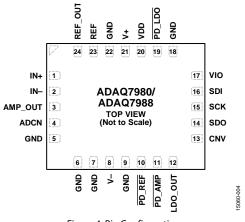

| Pin Configuration and Function Descriptions15 |

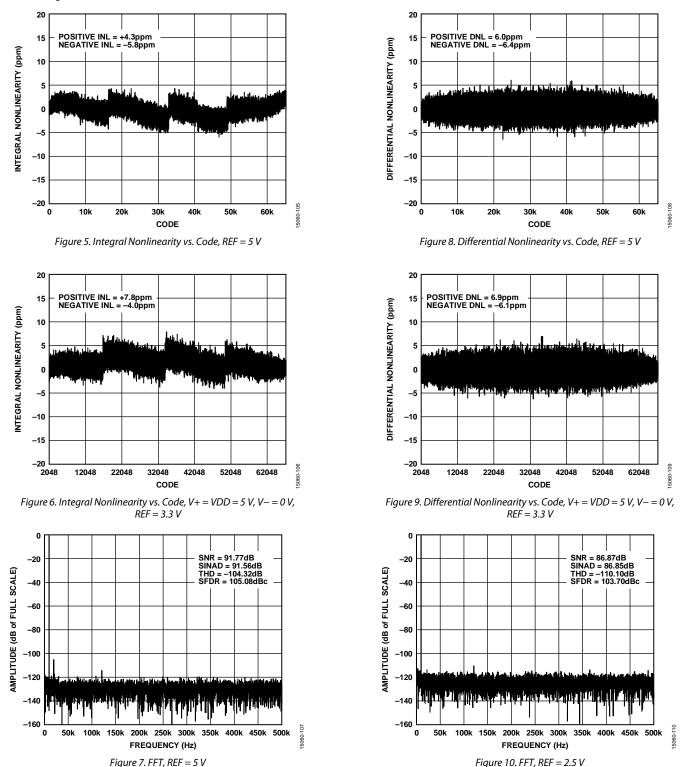

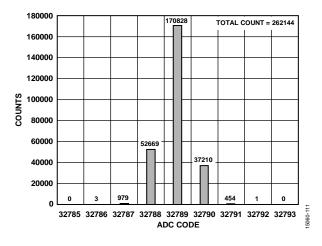

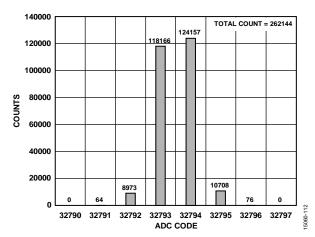

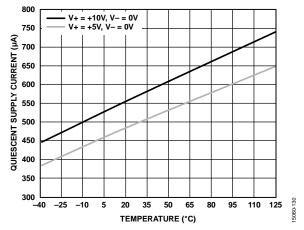

| Typical Performance Characteristics17         |

| Terminology                                   |

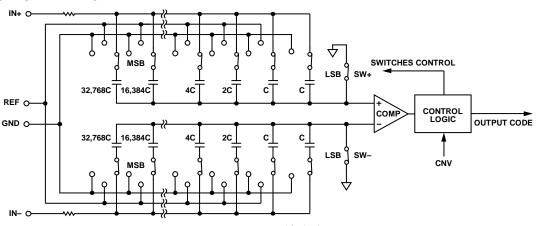

| Theory of Operation                           |

| Circuit Information                           |

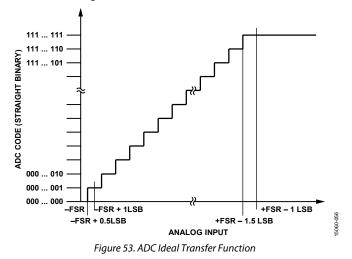

| Converter Operation                           |

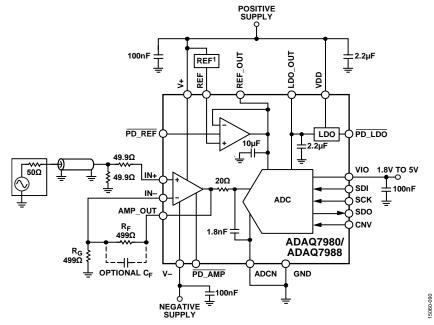

| Typical Connection Diagram27                  |

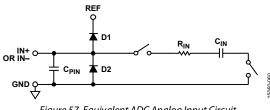

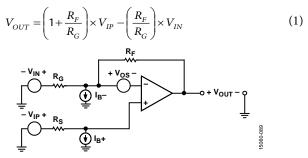

| ADC Driver Input                              |

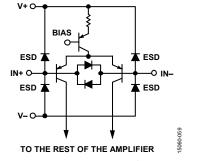

| Input Protection                              |

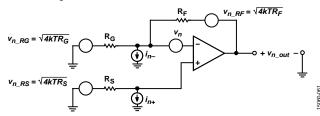

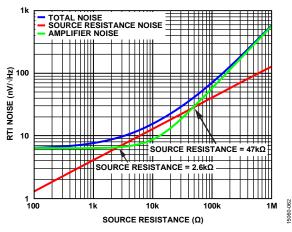

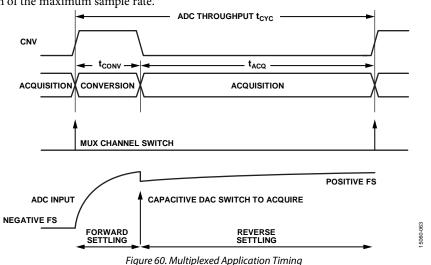

| Noise Considerations And Signal Settling      |

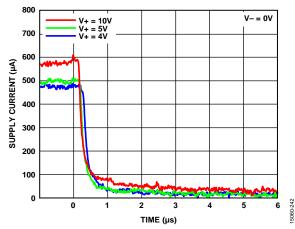

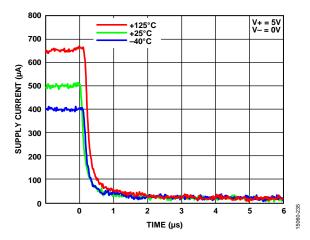

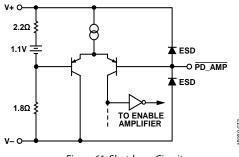

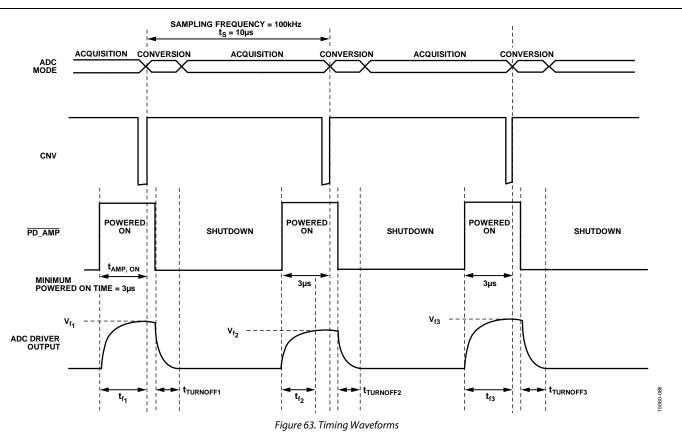

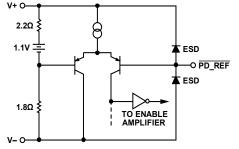

| PD_AMP Operation                              |

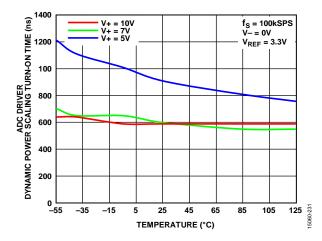

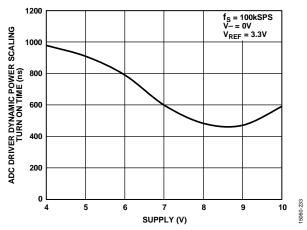

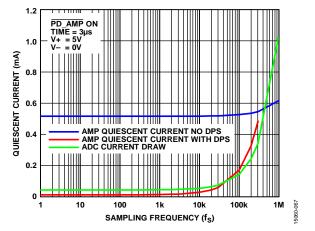

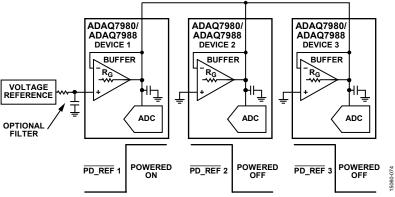

| Dynamic Power Scaling (DPS)                   |

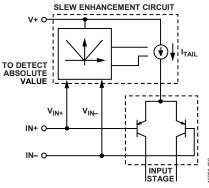

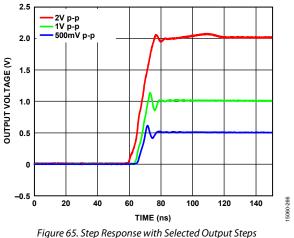

| Slew Enhancement                                               | 33 |

|----------------------------------------------------------------|----|

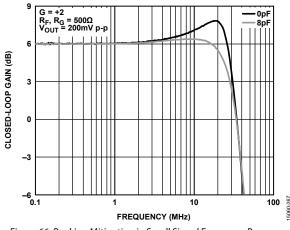

| Effect of Feedback Resistor on Frequency Response              | 33 |

| Voltage Reference Input                                        | 33 |

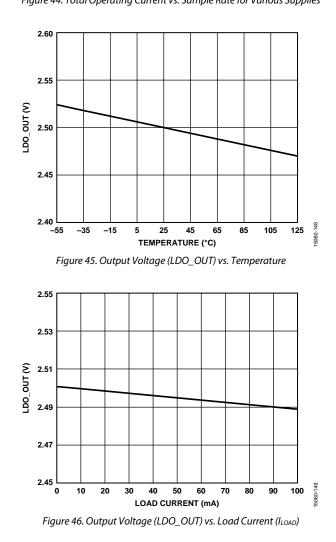

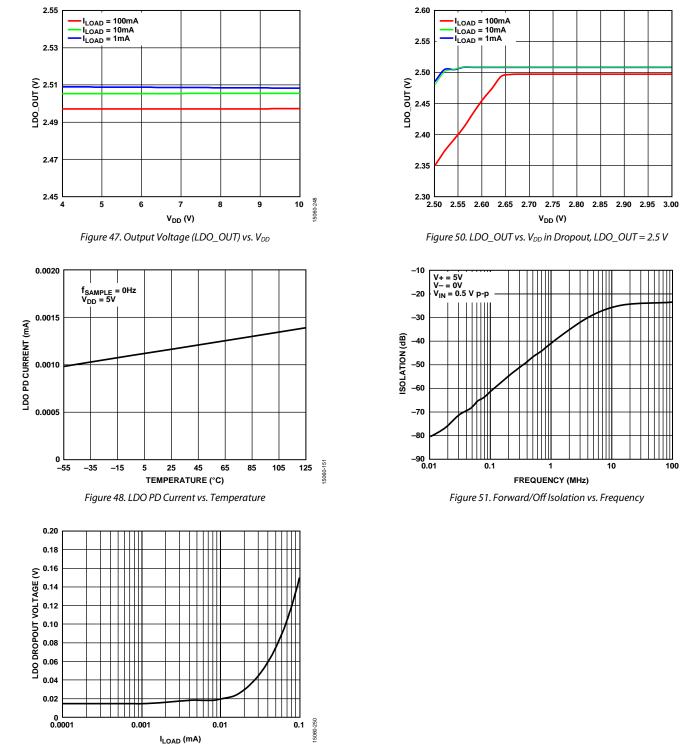

| Power Supply                                                   | 35 |

| LDO Regulator Current-Limit and Thermal Overload<br>Protection | 36 |

| LDO Regulator Thermal Considerations                           | 36 |

| Digital Interface                                              | 37 |

| 3-Wire $\overline{\text{CS}}$ Mode Without the Busy Indicator  | 38 |

| 3-Wire $\overline{\text{CS}}$ Mode with the Busy Indicator     | 39 |

| 4-Wire $\overline{\text{CS}}$ Mode Without the Busy Indicator  | 40 |

| 4-Wire $\overline{\text{CS}}$ Mode with the Busy Indicator     | 41 |

| Chain Mode Without the Busy Indicator                          | 42 |

| Chain Mode with the Busy Indicator                             | 43 |

| Application Circuits                                           | 44 |

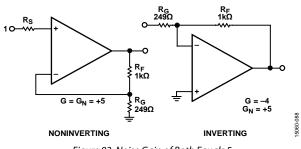

| Nonunity Gain Configurations                                   | 45 |

| Inverting Configuration with Level Shift                       | 46 |

| Using the ADAQ7980/ADAQ7988 With Active Filters                | 47 |

| Applications Information                                       | 48 |

| Layout                                                         | 48 |

| Evaluating the Performance of the ADAQ7980/ADAQ7988            | 48 |

| Outline Dimensions                                             | 49 |

| Ordering Guide                                                 | 49 |

|                                                                |    |

#### **REVISION HISTORY**

#### 8/2017—Rev. 0 to Rev. A

| Changed Integrated Data Acquisition System to µModule,      |

|-------------------------------------------------------------|

| Subsystem to µModule Data Acquisition System, Subsystems to |

| $\mu$ Module Data Acquisition Systems, and DAQ Subsystem to |

| µModule Data Acquisition System Throughout                  |

| Changes to Features Section and Table 1 Title 1             |

| Moved General Description Section                           |

| Changes to General Description Section                      |

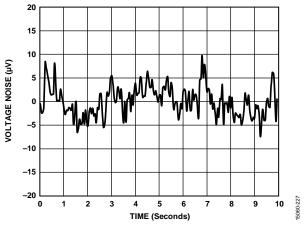

| Change to 0.1 Hz to 10 Hz Voltage Noise Parameter Heading,  |

| Table 2                                                     |

| Change to 0.1 Hz to 10 Hz Voltage Noise Parameter Heading, | ,  |

|------------------------------------------------------------|----|

| Table 4                                                    | 8  |

| Changes to Human Body Model (HBM) Parameter and            |    |

| Endnote 4, Table 7                                         | 14 |

| Change to Figure 27 Caption                                | 21 |

| Changes to Circuit Information Section                     | 27 |

| Change to Table 15 Title                                   | 45 |

| -                                                          |    |

3/2017—Revision 0: Initial Version

## **SPECIFICATIONS**

#### **DUAL-SUPPLY CONFIGURATION**

VDD = 3.5 V to 10 V, V + = 6.3 V to 7.7 V, V - = -2.5 V to -0.2 V, VIO = 1.7 V to 5.5 V,  $V_{REF} = 5 V$ ,  $T_A = -55^{\circ}C$  to  $+125^{\circ}C$ , ADC driver in a unity-gain buffer configuration,  $f_{SAMPLE} = 1$  MSPS (ADAQ7980), and  $f_{SAMPLE} = 500$  kSPS (ADAQ7988), unless otherwise noted.

| Parameter                             | Test Conditions/Comments                                 | Min   | Тур    | Max   | Unit                 |

|---------------------------------------|----------------------------------------------------------|-------|--------|-------|----------------------|

| RESOLUTION                            |                                                          | 16    |        |       | Bits                 |

| SYSTEM ACCURACY                       |                                                          |       |        |       |                      |

| No Missing Codes                      |                                                          | 16    |        |       | Bits                 |

| Differential Nonlinearity Error (DNL) |                                                          | -14   | ±7     | +14   | ppm <sup>1</sup>     |

| Integral Nonlinearity Error (INL)     |                                                          | -20   | ±8     | +20   | ppm <sup>1</sup>     |

| Transition Noise                      |                                                          |       | 0.6    |       | LSB <sup>1</sup> rms |

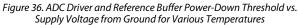

| Gain Error                            | $T_A = 25^{\circ}C$                                      | -0.01 | ±0.002 | +0.01 | %FS                  |

| Gain Error Temperature Drift          |                                                          |       | 0.1    | 0.4   | ppm/°C               |

| Zero Error                            | $T_A = 25^{\circ}C$                                      | -0.5  | ±0.06  | +0.5  | mV                   |

| Zero Error Temperature Drift          |                                                          |       | 0.3    | 1.3   | μV/°C                |

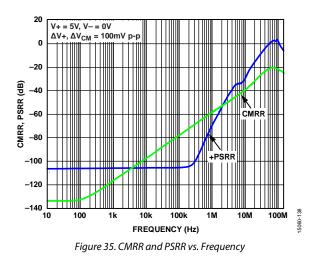

| Common-Mode Rejection Ratio           | ADC driver configured as difference amplifier            | 103   | 130    |       | dB                   |

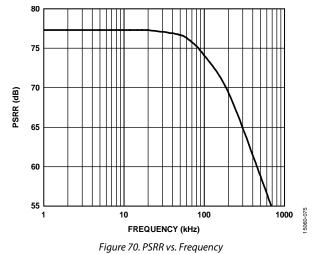

| Power Supply Rejection Ratio          |                                                          |       |        |       |                      |

| Positive                              | V + = +6.3 V to $+8 V$ , $V - = -2 V$                    | 75    | 105    |       | dB                   |

| Negative                              | V + = +7 V, V - = -1.0 V to -2.5 V                       | 80    | 110    |       | dB                   |

| SYSTEM AC PERFORMANCE                 |                                                          |       |        |       |                      |

| Dynamic Range                         |                                                          |       | 92     |       | dB <sup>2</sup>      |

| , 5                                   | $V_{REF} = 2.5 V$                                        |       | 87     |       | dB <sup>2</sup>      |

| Total RMS Noise                       |                                                          |       | 44.4   |       | μV rms               |

| Oversampled Dynamic Range             | Oversample dynamic range frequency $(f_{ODR}) = 10$ kSPS |       | 111    |       | dB <sup>2</sup>      |

| Signal-to-Noise Ratio (SNR)           | Input frequency $(f_{IN}) = 10 \text{ kHz}$              | 90.5  | 91.5   |       | dB <sup>2</sup>      |

| <b>J</b>                              | $f_{IN} = 10 \text{ kHz}, V_{REF} = 2.5 \text{ V}$       | 84.5  | 86.5   |       | dB <sup>2</sup>      |

| Spurious-Free Dynamic Range           | $f_{IN} = 10 \text{ kHz}$                                |       | 106    |       | dB <sup>2</sup>      |

| Total Harmonic Distortion (THD)       | $f_{IN} = 10 \text{ kHz}$                                |       | -105   | -100  | dB <sup>2</sup>      |

| Signal-to-Noise-and-Distortion Ratio  | $f_{IN} = 10 \text{ kHz}$                                | 90    | 91     |       | dB <sup>2</sup>      |

| -                                     | $f_{IN} = 10 \text{ kHz}, V_{REF} = 2.5 \text{ V}$       | 84    | 86     |       | dB <sup>2</sup>      |

| Effective Number of Bits              | $f_{IN} = 10 \text{ kHz}$                                | 14.65 | 14.8   |       | Bits                 |

| Noise Free Code Resolution            |                                                          |       | 14.1   |       | Bits                 |

| SYSTEM SAMPLING DYNAMICS              |                                                          |       |        |       |                      |

| Conversion Rate                       |                                                          |       |        |       |                      |

| ADAQ7980                              | $VIO \ge 3.0 V$                                          | 0     |        | 1     | MSPS                 |

|                                       | $VIO \ge 1.7 V$                                          | 0     |        | 833   | kSPS                 |

| ADAQ7988                              | $VIO \ge 1.7 V$                                          | 0     |        | 500   | kSPS                 |

| Transient Response                    | Full-scale step                                          |       | 430    | 500   | ns                   |

| –3 dB Input Bandwidth                 | ADC driver RC filter                                     |       | 4.42   |       | MHz                  |

| –1 dB Frequency                       | ADC driver RC filter                                     |       | 2.2    |       | MHz                  |

| –0.1 dB Frequency                     | ADC driver RC filter                                     |       | 0.67   |       | MHz                  |

| 0.1 Hz to 10 Hz Voltage Noise         |                                                          |       | 17     |       | μV p-p               |

| Aperture Delay                        |                                                          |       | 2.0    |       | ns                   |

| Aperture Jitter                       |                                                          |       | 2.0    |       | ns                   |

<sup>1</sup> LSB means least significant bit. With the 5 V input range, 1 LSB is 76.3 μV and 1 LSB = 15.26 ppm. <sup>2</sup> All specifications in dB are referred to a full-scale input, FSR. Tested with an input signal at 0.5 dB below full scale, unless otherwise specified.

VDD = 3.5 V to 10 V, V + = 6.3 V to 7.7 V, V - = -2.5 V to -0.2 V, VIO = 1.7 V to 5.5 V,  $V_{REF} = 5 V$ ,  $T_A = -55^{\circ}C$  to  $+125^{\circ}C$ , ADC driver in a unity-gain buffer configuration, and  $f_{SAMPLE} = 1 MSPS$  (ADAQ7980) and  $f_{SAMPLE} = 500 kSPS$  (ADAQ7988), unless otherwise noted.

| Parameter                          | Test Conditions/Comments                      | Min       | Тур   | Max                      | Unit   |

|------------------------------------|-----------------------------------------------|-----------|-------|--------------------------|--------|

| REFERENCE                          |                                               |           |       |                          |        |

| Input Voltage Range                | Voltage at REF pin                            | 2.4       |       | 5.1                      | V      |

| Load Current                       | REFOUT                                        |           | 330   |                          | μA     |

| Buffer Input                       |                                               |           |       |                          |        |

| Resistance                         | REF                                           |           | 50    |                          | MΩ     |

| Capacitance                        | REF                                           |           | 1     |                          | pF     |

| Bias Current                       |                                               |           | 550   | 800                      | nA     |

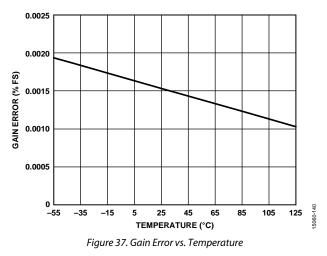

| Offset Voltage                     | $T_A = 25^{\circ}C$                           |           | 13    | 125                      | μV     |

| Offset Voltage Drift               |                                               |           | 0.2   | 1.3                      | μV/°C  |

| Voltage Noise                      | $f_{IN} = 100 \text{ kHz}$                    |           | 5.2   |                          | nV/√H  |

| Voltage Noise 1/f Corner Frequency |                                               |           | 8     |                          | Hz     |

| Current Noise                      | $f_{IN} = 100 \text{ kHz}$                    |           | 0.7   |                          | pA/√H  |

| 0.1 Hz to 10 Hz Voltage Noise      |                                               |           | 44    |                          | nV rms |

| Linear Output Current              | REFOUT                                        |           | ±40   |                          | mA     |

| Short-Circuit Current              | REFOUT sinking/sourcing                       |           | 85/73 |                          | mA     |

| ADC DRIVER CHARACTERISTICS         | KEI OOT sinking/sourcing                      |           | 0,75  |                          |        |

| Voltage Range                      | IN+, IN–, AMP_OUT                             | 0         |       | V <sub>REF</sub>         | v      |

| Absolute Input Voltage             |                                               | -0.1      |       | V REF<br>+5.1            | V      |

| Absolute input voltage             | IN+, IN–, AMP_OUT<br>ADCN                     |           |       |                          | v      |

|                                    |                                               | -0.1      | 27    | +0.1                     | -      |

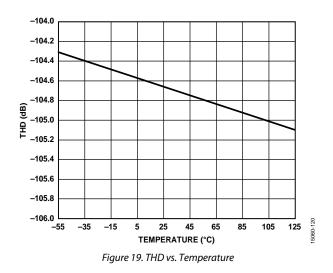

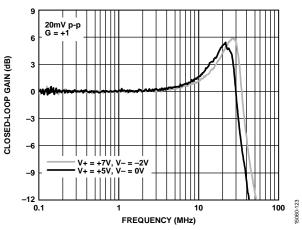

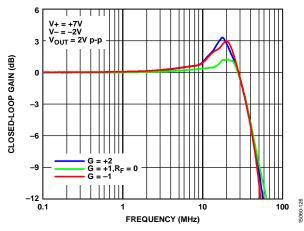

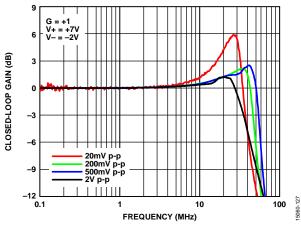

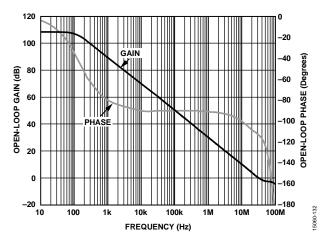

| –3 dB Bandwidth                    | $G = +1, V_{AMP_{OUT}} = 0.02 V p - p$        |           | 37    |                          | MHz    |

|                                    | $G = +1, V_{AMP_OUT} = 2 V p_p$               |           | 35    |                          | MHz    |

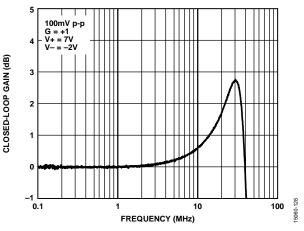

| Bandwidth for 0.1 dB Flatness      | $G = +1, V_{AMP_{OUT}} = 0.1 V p - p$         |           | 4     |                          | MHz    |

| Slew Rate                          | $G = +1, V_{AMP_OUT} = 2V step$               |           | 110   |                          | V/µs   |

|                                    | $G = +1, V_{AMP_{OUT}} = 5 V step$            |           | 40    |                          | V/µs   |

| Input Voltage Noise                | f = 100 kHz                                   |           | 5.2   |                          | nV/√H  |

| 1/f Corner Frequency               |                                               |           | 8     |                          | Hz     |

| 0.1 Hz to 10 Hz Voltage Noise      |                                               |           | 44    |                          | nV rms |

| Input Current                      |                                               |           |       |                          |        |

| Noise                              | f = 100 kHz                                   |           | 0.7   |                          | pA/√H  |

| Bias                               | IN+, IN–                                      |           | 550   | 800                      | nA     |

| Offset                             |                                               |           | 2.1   |                          | nA     |

| Input Offset Voltage               | $T_A = 25^{\circ}C$                           |           | 13    | 125                      | μV     |

| Drift                              |                                               |           | 0.2   | 1.3                      | μV/°C  |

| Open-Loop Gain                     |                                               |           | 111   |                          | dB     |

| Input Resistance                   | IN+, IN–                                      |           |       |                          |        |

| Common Mode                        |                                               |           | 50    |                          | MΩ     |

| Differential Mode                  |                                               |           | 260   |                          | kΩ     |

| Input Capacitance                  | IN+, IN–                                      |           | 1     |                          | рF     |

| Input Common-Mode Voltage Range    | Specified performance                         | -0.1      |       | V+ – 1.3V                | V      |

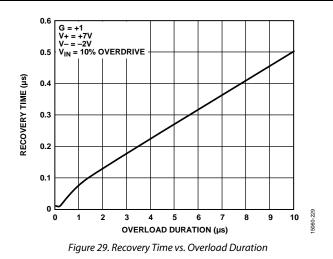

| Output Overdrive Recovery Time     | $V_{IN+} = 10\%$ overdrive, $f_{IN} = 10$ kHz |           | 500   |                          | ns     |

| Linear Output Current              |                                               |           | ±40   |                          | mA     |

| Short-Circuit Current              | Sinking/sourcing                              |           | 85/73 |                          | mA     |

| DIGITAL INPUTS                     |                                               |           |       |                          |        |

| Logic Levels                       |                                               |           |       |                          |        |

| Input Voltage                      |                                               |           |       |                          |        |

| Low (Vil)                          | VIO > 3.0 V                                   | -0.3      |       | +0.3 × VIO               | v      |

|                                    | VIO > 3.0 V<br>$VIO \le 3.0 V$                | -0.3      |       | +0.3 × VIO<br>+0.1 × VIO | v      |

| High (V⊮)                          | VIO ≤ 3.0 V<br>VIO > 3.0 V                    | 0.7 × VIO |       | +0.1 × 010<br>VIO + 0.3  | V      |

|                                    |                                               |           |       | VIC + 0.5                | v      |

**Data Sheet**

## ADAQ7980/ADAQ7988

| Parameter                             | Test Conditions/Comments                                        | Min            | Тур           | Max            | Unit |

|---------------------------------------|-----------------------------------------------------------------|----------------|---------------|----------------|------|

| Input Current                         |                                                                 |                |               |                |      |

| Low (IIL)                             |                                                                 | -1             |               | +1             | μΑ   |

| High (I⊮)                             |                                                                 | -1             |               | +1             | μA   |

| DIGITAL OUTPUTS                       |                                                                 |                |               |                |      |

| Data Format                           |                                                                 | Serial         | 16 hits stra  | ight binary    |      |

| Pipeline Delay                        |                                                                 |                | ersion result |                |      |

| i ipeline belay                       |                                                                 |                |               | completed      |      |

|                                       |                                                                 |                | conversi      |                |      |

| V <sub>OL</sub>                       | I <sub>SINK</sub> = 500 μA                                      |                |               | 0.4            | V    |

| VoH                                   | $I_{\text{SOURCE}} = -500 \mu\text{A}$                          | VIO – 0.3      |               |                | v    |

| POWER-DOWN SIGNALING                  |                                                                 |                |               |                | -    |

| ADC Driver/REF Buffer                 |                                                                 |                |               |                |      |

| PD_AMP, PD_REF Voltage                |                                                                 |                |               |                |      |

| -                                     |                                                                 |                |               |                |      |

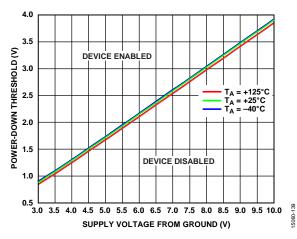

| Low                                   | Powered down                                                    |                | <2.2          |                | V    |

| High                                  | Enabled                                                         |                | >2.6          |                | V    |

| Turn-Off Time                         | 50% of PD_AMP, PD_REF to <10% of                                |                | 1.25          | 2.75           | μs   |

|                                       | enabled quiescent current                                       |                |               |                |      |

| Turn-On Time                          | Specified performance                                           |                | 2             | 7.25           | μs   |

| Dynamic Power Scaling Period          | Specified performance                                           | 10             |               |                | μs   |

| Low Dropout (LDO) Regulator           |                                                                 |                |               |                |      |

| PD_LDO Voltage                        |                                                                 |                |               |                |      |

| Low                                   | Powered down                                                    | 1.06           | 1.12          | 1.18           | v    |

| High                                  | Enabled                                                         | 1.15           | 1.22          | 1.30           | v    |

| PD_LDO Logic Hysteresis               |                                                                 |                | 100           |                | mV   |

| Turn-Off Time                         | 2.2 μF capacitive load                                          |                | 460           | 650            |      |

|                                       |                                                                 |                |               |                | μs   |

| Turn-On Time                          |                                                                 |                | 370           | 425            | μs   |

| POWER REQUIREMENTS                    |                                                                 |                | _             |                |      |

| VDD                                   |                                                                 | 3.5            | 5             | 10             | V    |

| LDO Voltage Accuracy                  | $I_{LDO_OUT} = 10 \text{ mA}, T_A = 25^{\circ}\text{C}$         | -0.8           |               | +0.8           | %    |

|                                       | $100 \ \mu A < I_{LDO_OUT} < 100 \ mA$ ,<br>VDD = 3.5 V to 10 V | -1.8           |               | +1.8           | %    |

| LDO Line Regulation                   | VDD = 3.5 V to 10 V                                             | -0.015         |               | +0.015         | %/V  |

| LDO Load Regulation                   | $I_{LDO_OUT} = 100 \mu A \text{ to } 100 \text{mA}$             |                | 0.002         | 0.004          | %/m/ |

| LDO Start-Up Time                     | $V_{LDO_OUT} = 2.5 V$                                           |                | 380           |                | μs   |

| LDO Current-Limit Threshold           |                                                                 | 250            | 360           | 460            | mA   |

| LDO Thermal Shutdown                  |                                                                 |                |               |                |      |

| Threshold                             | T, rising                                                       |                | 150           |                | °C   |

| Hysteresis                            |                                                                 |                | 15            |                | °C   |

| LDO Dropout Voltage                   | $I_{LDO_OUT} = 10 \text{ mA}$                                   |                | 30            | 60             | mV   |

| o Bropout Voltage                     | $I_{LDO_OUT} = 100 \text{ mA}$                                  |                | 200           | 420            | mV   |

| V+                                    |                                                                 | 3.7            | 200<br>7      | 420<br>V– + 10 | V    |

| V+<br>V-                              |                                                                 | 3.7<br>V+ - 10 |               |                | v    |

|                                       |                                                                 | -              | -2            | +0.1           |      |

| VIO                                   |                                                                 | 1.7            |               | 5.5            | V.   |

| Total Standby Current <sup>1, 2</sup> | Static, all devices enabled                                     |                | 1.2           | 1.7            | mA   |

|                                       | ADC driver, REF buffer disable                                  |                | 56            | 103            | μΑ   |

|                                       | ADC driver, REF buffer, LDO disable                             |                | 14            | 23             | μΑ   |

| ADAQ7980 Current Draw                 | 1 MSPS                                                          |                |               |                |      |

| VIO                                   |                                                                 |                | 0.3           | 0.34           | mA   |

| V+/V-                                 |                                                                 |                | 1.5           | 2.0            | mA   |

| VDD                                   |                                                                 |                | 1.45          | 1.6            | mA   |

| Parameter                  | Test Conditions/Comments                           | Min | Тур  | Max               | Unit |

|----------------------------|----------------------------------------------------|-----|------|-------------------|------|

| ADAQ7980 Power Dissipation | 1 MSPS                                             |     |      |                   |      |

| V+/V-/VDD                  |                                                    |     | 20   | 36                | mW   |

|                            | 1 kSPS, dynamic power scaling enabled <sup>3</sup> |     | 5.8  | 9                 | mW   |

| VIO                        |                                                    |     | 1.0  | 1.9               | mW   |

| Total                      |                                                    |     | 21   | 37.9 <sup>4</sup> | mW   |

| ADAQ7988 Current Draw      |                                                    |     |      |                   |      |

| VIO                        |                                                    |     | 0.15 | 0.17              | mA   |

| V+/V-                      |                                                    |     | 1.35 | 1.85              | mA   |

| VDD                        |                                                    |     | 0.73 | 0.8               | mA   |

| ADAQ7988 Power Dissipation | 500 kSPS                                           |     |      |                   |      |

| V+/V-/VDD                  |                                                    |     | 16   | 26.5              | mW   |

|                            | 1 kSPS, dynamic power scaling enabled <sup>3</sup> |     | 5.8  | 9                 | mW   |

| VIO                        |                                                    |     | 0.5  | 0.95              | mW   |

| Total                      |                                                    |     | 16.5 | 27.5 <sup>4</sup> | mW   |

| TEMPERATURE RANGE          |                                                    |     |      |                   |      |

| Specified Performance      | T <sub>MIN</sub> to T <sub>MAX</sub>               | -55 |      | +125              | °C   |

<sup>1</sup> With all digital inputs forced to VIO or GND as required.

<sup>2</sup> During the acquisition phase.

<sup>3</sup> Dynamic power scaling duty cycle is 10%.

<sup>4</sup> Calculated with the maximum supply differential and not the typical supply values.

#### SINGLE-SUPPLY CONFIGURATION

VDD = V + = 5.0 V, V - = 0 V, VIO = 1.7 V to 5.5 V,  $V_{REF} = 3.3 V$ ,  $T_A = -55^{\circ}C$  to  $+125^{\circ}C$ , the ADC driver in a unity-gain buffer configuration, and f<sub>SAMPLE</sub> = 1 MSPS (ADAQ7980) and f<sub>SAMPLE</sub> = 500 kSPS (ADAQ7988), unless otherwise noted.

| Parameter                                    | <b>Test Conditions/Comments</b>             | Min    | Тур    | Max    | Unit                 |

|----------------------------------------------|---------------------------------------------|--------|--------|--------|----------------------|

| RESOLUTION                                   |                                             | 16     |        |        | Bits                 |

| SYSTEM ACCURACY                              |                                             |        |        |        |                      |

| Differential Nonlinearity Error <sup>1</sup> |                                             | -14    | ±7     | +14    | ppm <sup>2</sup>     |

| Integral Nonlinearity Error <sup>1</sup>     |                                             | -20    | ±8     | +20    | ppm <sup>2</sup>     |

| Transition Noise                             |                                             |        | 0.8    |        | LSB <sup>2</sup> rms |

| Gain Error                                   | $T_A = 25^{\circ}C$                         | -0.013 | ±0.002 | +0.013 | %FS                  |

| Gain Error Temperature Drift                 |                                             |        | 0.1    | 0.4    | ppm/°C               |

| Zero Error                                   | $T_A = 25^{\circ}C$                         | -0.5   | ±0.06  | +0.5   | mV                   |

| Zero Error Temperature Drift                 |                                             |        | 0.35   | 1.75   | μV/°C                |

| Common-Mode Rejection Ratio                  |                                             | 103    | 133    |        | dB                   |

| Power Supply Rejection Ratio                 |                                             |        |        |        |                      |

| Positive                                     | V + = 4.5 V to 5.5 V, $V - = 0 V$           | 75     | 92     |        | dB                   |

| SYSTEM AC PERFORMANCE                        |                                             |        |        |        |                      |

| Dynamic Range                                |                                             |        | 89     |        | dB <sup>3</sup>      |

| Total RMS Noise                              |                                             |        | 41.4   |        | μV rms               |

| Oversampled Dynamic Range                    | $f_{ODR} = 10 \text{ kSPS}$                 |        | 109    |        | dB <sup>3</sup>      |

| Signal-to-Noise Ratio                        | Input frequency $(f_{IN}) = 10 \text{ kHz}$ | 87.3   | 88.7   |        | dB <sup>3</sup>      |

| Spurious-Free Dynamic Range                  | $f_{IN} = 10 \text{ kHz}$                   |        | 103    |        | dB <sup>3</sup>      |

| Total Harmonic Distortion                    | $f_{IN} = 10 \text{ kHz}$                   |        | -113   | -100   | dB <sup>3</sup>      |

| Signal-to-Noise-and-Distortion Ratio         | $f_{IN} = 10 \text{ kHz}$                   | 87     | 88.4   |        | dB <sup>3</sup>      |

| Effective Number of Bits                     | $f_{IN} = 10 \text{ kHz}$                   | 14.1   | 14.4   |        | Bits                 |

| Noise Free Code Resolution                   |                                             |        | 13.5   |        | Bits                 |

| SYSTEM SAMPLING DYNAMICS                     |                                             |        |        |        |                      |

| Conversion Rate                              |                                             |        |        |        |                      |

| ADAQ7980                                     | $VIO \ge 3.0 V$                             | 0      |        | 1      | MSPS                 |

|                                              | $VIO \ge 1.7 V$                             | 0      |        | 833    | kSPS                 |

| ADAQ7988                                     | $VIO \ge 1.7 V$                             | 0      |        | 500    | kSPS                 |

| Transient Response                           | Full-scale step                             |        | 430    | 500    | ns                   |

| –3 dB Input Bandwidth                        | ADC driver RC filter                        |        | 4.42   |        | MHz                  |

| –1 dB Frequency                              | ADC driver RC filter                        |        | 2.2    |        | MHz                  |

| –0.1 dB Frequency                            | ADC driver RC filter                        |        | 0.67   |        | MHz                  |

| 0.1 Hz to 10 Hz Voltage Noise                |                                             |        | 17     |        | μV p-p               |

| Aperture Delay                               |                                             |        | 2.0    |        | ns                   |

| Aperture Jitter                              |                                             |        | 2.0    |        | ns                   |

<sup>1</sup> Nonlinearity guaranteed over input voltage range. Codes below 150 mV are not represented with a unipolar supply configuration. <sup>2</sup> LSB means least significant bit. With the 3.3 V input range, 1 LSB = 50.4  $\mu$ V, and 1 LSB = 15.26 ppm.

<sup>3</sup> All specifications in dB are referred to a full-scale input, FSR. Tested with an input signal at 0.5 dB below full scale, unless otherwise specified.

VDD = V + = 5.0 V, V - = 0 V, VIO = 1.7 V to 5.5 V,  $V_{REF} = 3.3 V$ ,  $T_A = -55^{\circ}C$  to  $+125^{\circ}C$ , the ADC driver in a unity-gain buffer configuration, and  $f_{SAMPLE} = 1 MSPS$  (ADAQ7980) and  $f_{SAMPLE} = 500 kSPS$  (ADAQ7988), unless otherwise noted.

Table 5.

| Parameter                          | Test Conditions/Comments                              | Min       | Тур   | Max              | Unit   |

|------------------------------------|-------------------------------------------------------|-----------|-------|------------------|--------|

| REFERENCE                          |                                                       |           |       |                  |        |

| Input Voltage Range                | Voltage at REF pin                                    | 2.4       |       | V+ – 1.3         | V      |

| Load Current                       | REFOUT                                                |           | 330   |                  | μA     |

| Buffer Input                       |                                                       |           |       |                  |        |

| Resistance                         | REF                                                   |           | 50    |                  | MΩ     |

| Capacitance                        | REF                                                   |           | 1     |                  | рF     |

| Bias Current                       |                                                       |           | 470   | 720              | nA     |

| Offset Voltage                     | $T_A = 25^{\circ}C$                                   |           | 9     | 125              | μV     |

| Offset Voltage Drift               |                                                       |           | 0.2   | 1.5              | μV/°C  |

| Voltage Noise                      | $f_{IN} = 100 \text{kHz}$                             |           | 5.9   |                  | nV/√H  |

| Voltage Noise 1/f Corner Frequency |                                                       |           | 8     |                  | Hz     |

| Current Noise                      | $f_{IN} = 100 \text{kHz}$                             |           | 0.6   |                  | pA/√H  |

| 0.1 Hz to 10 Hz Voltage Noise      |                                                       |           | 54    |                  | nV rms |

| Linear Output Current              | REFOUT                                                |           | ±40   |                  | mA     |

| Short-Circuit Current              | REFOUT sinking/sourcing                               |           | 73/63 |                  | mA     |

| ADC DRIVER CHARACTERISTICS         | here of ranking/sourcing                              |           |       |                  |        |

| Specified Voltage Range            | IN+, IN–, AMP_OUT                                     | 0.15      |       | VREF             | v      |

|                                    |                                                       | -0.1      |       | VREF<br>V+ - 1.3 | v      |

| Absolute Input Voltage             | IN+, IN-, AMP_OUT                                     |           |       |                  | -      |

|                                    | ADCN                                                  | -0.1      | 21    | +0.1             | V      |

| –3 dB Bandwidth                    | $G = +1, V_{AMP_{OUT}} = 0.02 V p - p$                |           | 31    |                  | MHz    |

|                                    | $G = +1, V_{AMP_{OUT}} = 2 V p - p$                   |           | 30    |                  | MHz    |

| Bandwidth for 0.1 dB Flatness      | $G = +1, V_{AMP_OUT} = 0.1 V p-p$                     |           | 4     |                  | MHz    |

| Slew Rate                          | $G = +1, V_{AMP_OUT} = 2 V step$                      |           | 31    |                  | V/µs   |

|                                    | $G = +1$ , $V_{AMP_OUT} = 3.15$ V step                |           | 20    |                  | V/µs   |

| Input Voltage Noise                | f = 100 kHz                                           |           | 5.9   |                  | nV/√H: |

| 1/f Corner Frequency               |                                                       |           | 8     |                  | Hz     |

| 0.1 Hz to 10 Hz Voltage Noise      |                                                       |           | 54    |                  | nV rms |

| Input Current                      |                                                       |           |       |                  |        |

| Noise                              | f = 100 kHz                                           |           | 0.6   |                  | pA/√H  |

| Bias                               | IN+, IN–                                              |           | 470   | 720              | nA     |

| Offset                             |                                                       |           | 0.4   |                  | nA     |

| Input Offset Voltage               | $T_A = 25^{\circ}C$                                   |           | 9     | 125              | μV     |

| Open-Loop Gain                     |                                                       |           | 109   |                  | dB     |

| Input Resistance                   | IN+, IN–                                              |           |       |                  |        |

| Common Mode                        |                                                       |           | 50    |                  | MΩ     |

| Differential Mode                  |                                                       |           | 260   |                  | kΩ     |

| Input Capacitance                  | IN+, IN–                                              |           | 1     |                  | рF     |

| Input Common-Mode Voltage Range    | Specified performance                                 | -0.1      |       | V+ – 1.3         | V      |

| Output Overdrive Recovery Time     | $V_{IN+} = 10\%$ overdrive, $f_{IN} = 10 \text{ kHz}$ |           | 800   |                  | ns     |

| Linear Output Current              |                                                       |           | ±40   |                  | mA     |

| Short-Circuit Current              | Sinking/sourcing                                      |           | 73/63 |                  | mA     |

| DIGITAL INPUTS                     |                                                       |           |       |                  |        |

| Logic Levels                       |                                                       |           |       |                  |        |

| Input Voltage                      |                                                       |           |       |                  |        |

|                                    | VIO > 3.0 V                                           | -0.3      |       | +0.3×VIO         | v      |

|                                    | $VIO \leq 3.0 V$                                      | -0.3      |       | +0.1 × VIO       | v      |

| High (V <sub>IH</sub> )            | VIO > 3.0 V                                           | 0.7 × VIO |       | VIO + 0.3        | v      |

|                                    | $VIO \leq 3.0 V$                                      | 0.9 × VIO |       | VIO + 0.3        | v      |

**Data Sheet**

## ADAQ7980/ADAQ7988

| Parameter                             | Test Conditions/Comments                                         | Min       | Тур           | Max        | Unit       |

|---------------------------------------|------------------------------------------------------------------|-----------|---------------|------------|------------|

| Input Current                         |                                                                  |           |               |            |            |

| Low (I <sub>IL</sub> )                |                                                                  | -1        |               | +1         | μΑ         |

| High (I⊮)                             |                                                                  | -1        |               | +1         | μΑ         |

| DIGITAL OUTPUTS                       |                                                                  |           |               |            | -          |

| Data Format                           |                                                                  | Serial    | 16 bits strai | ght binary |            |

| Pipeline Delay                        |                                                                  |           | rsion result  |            |            |

|                                       |                                                                  |           |               | completed  |            |

|                                       |                                                                  |           | conversio     | on         |            |

| V <sub>OL</sub>                       | $I_{SINK} = 500 \ \mu A$                                         |           |               | 0.4        | V          |

| V <sub>он</sub>                       | $I_{SOURCE} = -500 \mu A$                                        | VIO – 0.3 |               |            | V          |

| OWER-DOWN SIGNALING                   |                                                                  |           |               |            |            |

| ADC Driver/Reference Buffer           |                                                                  |           |               |            |            |

| PD_AMP, PD_REF Voltage                |                                                                  |           |               |            |            |

| Low                                   | Powered down                                                     |           | <1.5          |            | v          |

| High                                  | Enabled                                                          |           | >1.9          |            | v          |

| Turn-Off Time                         | 50% of PD_AMP, PD_REF to <10% of enabled                         |           | 0.9           | 1.25       | μs         |

|                                       | quiescent current                                                |           | 0.2           | 1.20       | ۳ <u>م</u> |

| Turn-On Time                          | Specified performance                                            |           | 2             | 7.25       | μs         |

| Dynamic Power Scaling Period          | Specified performance                                            | 10        | Z             | 7.25       | μs         |

| LDO                                   | specifica performance                                            | 10        |               |            | μ          |

| PD_LDO Voltage                        |                                                                  |           |               |            |            |

|                                       |                                                                  | 1.00      | 1 1 2         | 1.10       |            |

| Low                                   | Powered down                                                     | 1.06      | 1.12          | 1.18       | V          |

| High                                  | Enabled                                                          | 1.15      | 1.22          | 1.30       | V          |

| PD_LDO Logic Hysteresis               |                                                                  |           | 100           |            | mV         |

| Turn-Off Time                         | 2.2 μF capacitive load                                           |           | 460           | 650        | μs         |

| Turn-On Time                          |                                                                  |           | 370           | 425        | μs         |

| POWER REQUIREMENTS                    |                                                                  |           |               |            |            |

| VDD                                   |                                                                  | 3.5       | 5             | 10         | V          |

| LDO Voltage Accuracy                  | $I_{LDO_OUT} = 10 \text{ mA}, T_A = 25^{\circ}\text{C}$          | -0.8      |               | +0.8       | %          |

|                                       | 100 $\mu$ A < I <sub>LDO_OUT</sub> < 100 mA, VDD = 3.5 V to 10 V | -1.8      |               | +1.8       | %          |

| LDO Line Regulation                   | VDD = 3.5 V to 10 V                                              | -0.015    |               | +0.015     | %/V        |

| LDO Load Regulation                   | $I_{LDO_OUT} = 100 \mu A \text{ to } 100 \text{mA}$              |           | 0.002         | 0.004      | %/m/       |

| LDO Start-Up Time                     | $V_{LDO_OUT} = 2.5 V$                                            |           | 380           |            | μs         |

| LDO Current-Limit Threshold           |                                                                  | 250       | 360           | 460        | mA         |

| LDO Thermal Shutdown                  |                                                                  |           |               |            |            |

| Threshold                             | T <sub>2</sub> rising                                            |           | 150           |            | °C         |

| Hysteresis                            |                                                                  |           | 15            |            | °C         |

| LDO Dropout Voltage                   | $I_{LDO OUT} = 10 \text{ mA}$                                    |           | 30            | 60         | mV         |

|                                       | $I_{\text{LDO}_{\text{OUT}}} = 100 \text{ mA}$                   |           | 200           | 420        | mV         |

| V+                                    |                                                                  | 3.7       | 5             | V-+10      | v          |

| V–                                    |                                                                  | V+ - 10   | 0             | +0.1       | v          |

| VIO                                   |                                                                  | 1.7       | v             | 5.5        | v          |

| Total Standby Current <sup>1, 2</sup> | Static, all devices enabled                                      | 1.7       | 1.1           | 3.3<br>1.7 | mA         |

|                                       | ADC driver, REF buffer disabled                                  |           | 50            |            |            |

|                                       |                                                                  |           |               | 103<br>22  | μΑ         |

|                                       | ADC driver, REF buffer, LDO disabled                             |           | 7             | 23         | μA         |

| ADAQ7980 Current Draw                 | 1 MSPS                                                           |           | 0.7           | 0.24       |            |

| VIO                                   |                                                                  |           | 0.3           | 0.34       | mA         |

| V+/V-                                 |                                                                  |           | 1.3           | 2.0        | mA         |

| VDD                                   |                                                                  |           | 1.45          | 1.6        | mA         |

| Parameter                  | Test Conditions/Comments                                      | Min | Тур   | Max               | Unit |

|----------------------------|---------------------------------------------------------------|-----|-------|-------------------|------|

| ADAQ7980 Power Dissipation | 1MSPS                                                         |     |       |                   |      |

| V+/V-/VDD                  |                                                               |     | 13.75 | 36                | mW   |

|                            | 1 kSPS, ADC driver dynamic power scaling enabled <sup>3</sup> |     | 2.9   | 9                 | mW   |

| VIO                        |                                                               |     | 1.0   | 1.9               | mW   |

| Total                      |                                                               |     | 14.75 | 37.9 <sup>4</sup> | mW   |

| ADAQ7988 Current Draw      |                                                               |     |       |                   |      |

| VIO                        |                                                               |     | 0.15  | 0.17              | mA   |

| V+/V-                      |                                                               |     | 1.15  | 1.85              | mA   |

| VDD                        |                                                               |     | 0.73  | 0.8               | mA   |

| ADAQ7988 Power Dissipation | 500 kSPS                                                      |     |       |                   |      |

| V+/V-/VDD                  |                                                               |     | 9.4   | 26.5              | mW   |

|                            | 1 kSPS, ADC driver dynamic power scaling enabled <sup>3</sup> |     | 2.9   | 9                 | mW   |

| VIO                        |                                                               |     | 0.5   | 0.95              | mW   |

| Total                      |                                                               |     | 9.9   | 27.5 <sup>4</sup> | mW   |

| TEMPERATURE RANGE          |                                                               |     |       |                   |      |

| Specified Performance      | T <sub>MIN</sub> to T <sub>MAX</sub>                          | -55 |       | +125              | °C   |

<sup>1</sup> With all digital inputs forced to VIO or GND as required.

<sup>2</sup> During the acquisition phase.

<sup>3</sup> Dynamic power scaling duty cycle is 10%.

<sup>4</sup> Calculated with the maximum supply differential and not the typical supply values.

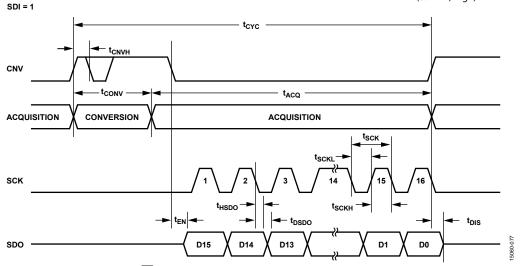

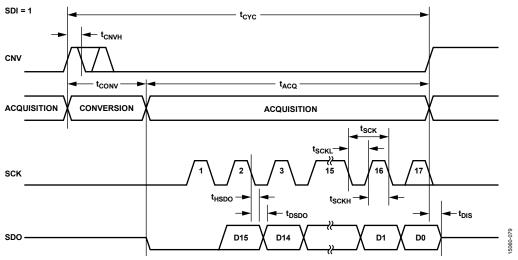

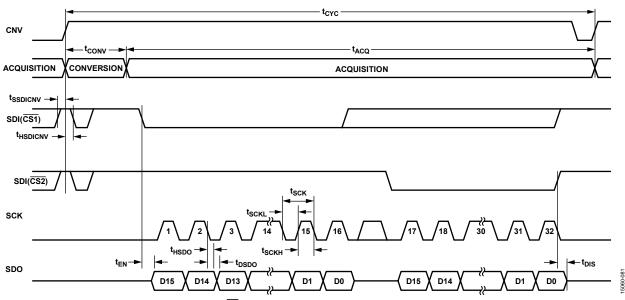

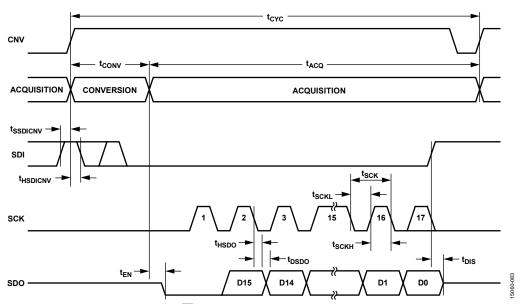

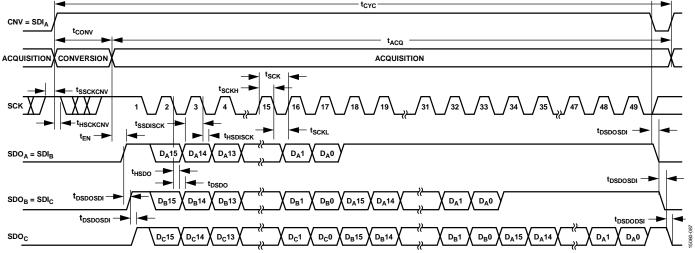

#### TIMING SPECIFICATIONS

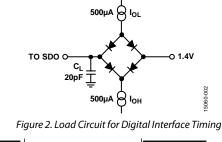

VDD = 3.5 V to 10 V, VIO = 1.7 V to 5.5 V, and  $T_A = -55^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted In addition to Figure 2 and Figure 3, see Figure 72, Figure 74, Figure 76, Figure 78, Figure 80, and Figure 82 for the additional timing diagrams detailed in Table 6.

| Table 6.                                                       |                      |      |     |      |      |  |  |

|----------------------------------------------------------------|----------------------|------|-----|------|------|--|--|

| Parameter                                                      | Symbol               | Min  | Тур | Max  | Unit |  |  |

| CONVERSION TIME: CNV RISING EDGE TO DATA AVAILABLE             | t <sub>conv</sub>    |      |     |      |      |  |  |

| VIO Above 3.0 V (ADAQ7980)                                     |                      | 500  |     | 710  | ns   |  |  |

| VIO Above 1.7 V (ADAQ7980)                                     |                      | 500  |     | 800  | ns   |  |  |

| ADAQ7988                                                       |                      | 500  |     | 1200 | ns   |  |  |

| ACQUISITION PHASE <sup>1</sup>                                 | t <sub>ACQ</sub>     |      |     |      | ns   |  |  |

| ADAQ7980                                                       |                      | 290  |     |      | ns   |  |  |

| ADAQ7988                                                       |                      | 800  |     |      | ns   |  |  |

| TIME BETWEEN CONVERSIONS                                       | t <sub>cyc</sub>     |      |     |      |      |  |  |

| VIO Above 3.0 V (ADAQ7980)                                     |                      | 1000 |     |      | ns   |  |  |

| VIO Above 1.7 V (ADAQ7980)                                     |                      | 1200 |     |      | ns   |  |  |

| VIO Above 1.7 V (ADAQ7988)                                     |                      | 2000 |     |      | ns   |  |  |

| CS MODE                                                        |                      |      |     |      |      |  |  |

| CNV Pulse Width                                                | t <sub>CNVH</sub>    | 10   |     |      | ns   |  |  |

| SCK Period                                                     | t <sub>scк</sub>     |      |     |      |      |  |  |

| VIO Above 4.5 V                                                |                      | 10.5 |     |      | ns   |  |  |

| VIO Above 3.0 V                                                |                      | 12   |     |      | ns   |  |  |

| VIO Above 1.7 V                                                |                      | 22   |     |      | ns   |  |  |

| CNV or SDI Low to SDO D15 MSB Valid                            | t <sub>en</sub>      |      |     |      |      |  |  |

| VIO Above 3.0 V                                                | -214                 |      |     | 10   | ns   |  |  |

| VIO Above 1.7 V                                                |                      |      |     | 40   | ns   |  |  |

| CNV or SDI High or Last SCK Falling Edge to SDO High Impedance | t <sub>DIS</sub>     |      |     | 20   | ns   |  |  |

| SDI Valid Hold Time from CNV Rising Edge                       |                      |      |     | 20   | 115  |  |  |

| VIO Above 3.0 V                                                | CHSDICINV            | 2    |     |      | ns   |  |  |

| VIO Above 1.7 V                                                |                      | 10   |     |      | ns   |  |  |

| CHAIN MODE                                                     |                      | 10   |     |      | 115  |  |  |

| SCK Period                                                     | t <sub>sck</sub>     |      |     |      |      |  |  |

| VIO Above 4.5 V                                                | USCK                 | 11.5 |     |      | ns   |  |  |

| VIO Above 4.5 V<br>VIO Above 3.0 V                             |                      | 13   |     |      | ns   |  |  |

| VIO Above 1.7 V                                                |                      | 23   |     |      |      |  |  |

| SDI Valid Hold Time from CNV Rising Edge                       | +                    | 0    |     |      | ns   |  |  |

|                                                                |                      |      |     |      | ns   |  |  |

| SCK Valid Setup Time from CNV Rising Edge                      | tssckcnv             | 5    |     |      | ns   |  |  |

| SCK Valid Hold Time from CNV Rising Edge                       | t <sub>HSCKCNV</sub> | 5    |     |      | ns   |  |  |

| SDI Valid Setup Time from SCK Falling Edge                     | <b>t</b> ssdisck     | 2    |     |      | ns   |  |  |

| SDI Valid Hold Time from SCK Falling Edge                      | t <sub>HSDISCK</sub> | 3    |     |      | ns   |  |  |

| SDI High to SDO High (with Busy Indicator)                     | tdsdosdi             |      |     | 45   |      |  |  |

| VIO Above 3.0 V                                                |                      |      |     | 15   | ns   |  |  |

| VIO Above 1.7 V                                                |                      | _    |     | 22   | ns   |  |  |

| SCK                                                            |                      |      |     |      |      |  |  |

| Low Time                                                       | tscĸ∟                |      |     |      | 1    |  |  |

| VIO Above 3.0 V                                                |                      | 4.5  |     |      | ns   |  |  |

| VIO Above 1.7 V                                                |                      | 6    |     |      | ns   |  |  |

| High Time                                                      | t <sub>scкн</sub>    |      |     |      | 1    |  |  |

| VIO Above 3.0 V                                                |                      | 4.5  |     |      | ns   |  |  |

| VIO Above 1.7 V                                                |                      | 6    |     |      | ns   |  |  |

| Parameter                                 | Symbol            | Min | Тур | Max | Unit |

|-------------------------------------------|-------------------|-----|-----|-----|------|

| Falling Edge to Data Remains Valid        | t <sub>HSDO</sub> | 3   |     |     | ns   |

| Falling Edge to Data Valid Delay          | t <sub>DSDO</sub> |     |     |     |      |

| VIO Above 4.5 V                           |                   |     |     | 9.5 | ns   |

| VIO Above 3.0 V                           |                   |     |     | 11  | ns   |

| VIO Above 1.7 V                           |                   |     |     | 21  | ns   |

| SDI VALID SETUP TIME From CNV RISING EDGE | tssdicnv          | 5   |     |     | ns   |

<sup>1</sup> The acquisition phase is the time available for the ADC sampling capacitors to acquire a new input with the ADC running at a throughput rate of 1 MSPS.

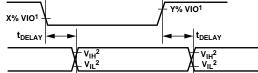

$^{1}$  FOR VIO  $\leq$  3.0V, X = 90, AND Y = 10; FOR VIO > 3.0V, X = 70, AND Y = 30.  $^{2}$  MINIMUM  $v_{IH}$  AND MAXIMUM  $v_{IL}$  USED. SEE DIGITAL INPUTS SPECIFICATIONS IN TABLE 3 OR TABLE 5.

Figure 3. Voltage Levels for Timing

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 7.

| Parameter                                               | Rating                              |

|---------------------------------------------------------|-------------------------------------|

| V+ to V–                                                | 11 V                                |

| V+ to GND                                               | –0.3 V to +11 V                     |

| V– to GND                                               | -11 V to +0.3 V                     |

| VDD to GND                                              | –0.3 V to +24 V                     |

| REF_OUT/VIO to GND                                      | –0.3 V to +6 V                      |

| IN+/IN–/REF to GND                                      | V0.7 V to $V + +0.7 V$              |

| AMP_OUT/ADCN to GND                                     | $-0.3V$ to $V_{\text{REF}}+0.3V$ or |

|                                                         | ±130 mA                             |

| Differential Analog Input Voltage                       | ±1 V                                |

| (IN+ - IN-)                                             |                                     |

| Digital Input <sup>1</sup> Voltage to GND               | –0.3 V to VIO + 0.3 V               |

| Digital Output <sup>2</sup> Voltage to GND              | -0.3 V to VIO + 0.3 V               |

| Input Current to Any Pin Except Supplies <sup>3,4</sup> | ±10 mA                              |

| Operating Temperature Range                             | -55°C to +125°C                     |

| Storage Temperature Range                               | –65°C to +150°C                     |

| Junction Temperature                                    | 150°C                               |

| ESD                                                     |                                     |

| Human Body Model (HBM)                                  | 3500 V                              |

| Field Induced Charged Device Model<br>(FICDM)           | 1250 V                              |

<sup>1</sup> The digital input pins include the following: CNV, SDI, and SCK.

<sup>2</sup> The digital output pin is SDO.

<sup>3</sup> Transient currents of up to 100 mA do not cause SCR latch-up. <sup>4</sup> Condition applies when power is provided to the device.

Condition applies when power is provided to the device.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL DATA

Absolute maximum ratings apply individually only, not in combination. The ADAQ7980/ADAQ7988 can be damaged when the junction temperature ( $T_1$ ) limits are exceeded. Monitoring ambient temperature does not guarantee that  $T_1$  is within the specified temperature limits. In applications with high power dissipation and poor thermal resistance, the maximum ambient temperature ( $T_A$ ) may have to be derated.

In applications with moderate power dissipation and low printed circuit board (PCB) thermal resistance, the maximum  $T_A$  can exceed the maximum limit as long as the junction temperature is within specification limits. The  $\theta_{JA}$  of the package is based on modeling and calculation using a 4-layer board. The  $\theta_{JA}$  is highly dependent on the application and board layout. In applications where high maximum power dissipation exists, close attention to thermal board design is required. The  $\theta_{JA}$  value may vary depending on PCB material, layout, and environmental conditions.

#### THERMAL RESISTANCE

Thermal resistance values specified in Table 8 were calculated based on JEDEC specifications and must be used in compliance with JESD51-12. Because the product contains more than one silicon device, only the worst case junction temperature is reported.

#### Table 8. Thermal Resistance

| Package Type <sup>1, 2</sup> | θ」 | $\theta_{\text{JCTOP}^2}$ | Ψл   | Unit |

|------------------------------|----|---------------------------|------|------|

| CC-24-2                      | 65 | 103                       | 12.6 | °C/W |

<sup>1</sup> These values represent the worst case die junction in the package.

<sup>2</sup> Table 8 values were calculated based on the standard JEDEC test conditions defined in Table 9, unless otherwise specified.

$^3$  For  $\theta_{Jc}$  test, 100  $\mu m$  thermal interface material (TIM) was used. TIM is assumed to be 3.6 W/mK.

Only use  $\theta_{IA}$  and  $\theta_{IC TOP}$  to compare thermal performance of the package of the device with other semiconductor packages when all test conditions listed are similar. One common mistake is to use  $\theta_{IA}$  and  $\theta_{IC}$  to estimate the junction temperature in the system environment. Instead, using  $\Psi_{JT}$  is a more appropriate way to estimate the worst case junction temperature of the device in the system environment. First, take an accurate thermal measurement of the top center of the device (on the mold compound in this case) while the device operates in the system environment. This measurement is known in the following equation as  $T_{TOP}$ . This equation can then be used to solve for the worst case  $T_J$  in that given environment as follows:

$T_J = \Psi_{JT} \times P + T_{TOP}$

#### where:

$\Psi_{IT}$  is the junction to top thermal characterization number as specified in data sheet.

*P* refers to total power dissipation in the chip (W).

$T_{TOP}$  refers to the package top temperature (°C) and is measured at the top center of the package in the environment of the user.

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

#### Table 9. Standard JEDEC Test Conditions

| Test Conditions          | θ <sub>JA</sub>                                                                                                                                                                                            | θ」                                                                                                                                                                                                         | θյ <sub>B</sub>                                                                                                                                                                                            |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Main Heat Transfer Mode  | Convection                                                                                                                                                                                                 | Conduction                                                                                                                                                                                                 | Conduction                                                                                                                                                                                                 |

| Board Type               | 2S2P                                                                                                                                                                                                       | 1S0P                                                                                                                                                                                                       | 2S2P                                                                                                                                                                                                       |

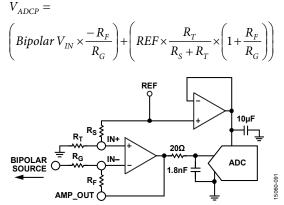

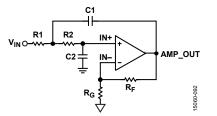

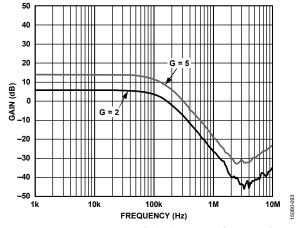

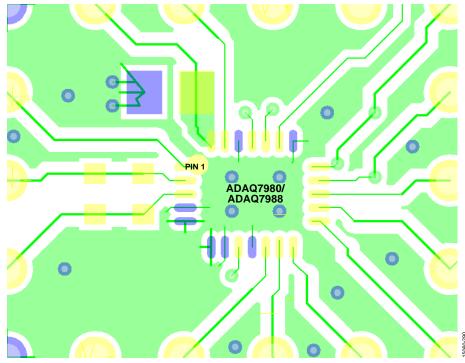

| Board Thickness          | 1.6 mm                                                                                                                                                                                                     | 1.6 mm                                                                                                                                                                                                     | 1.6 mm                                                                                                                                                                                                     |