# 4-Channel, 16-Bit, Continuous Time Data Acquisition ADC

### **Data Sheet**

## **ADAR7251**

#### **FEATURES**

Low noise: 2.4 nV/ $\sqrt{Hz}$  input referred voltage noise at maximum gain setting Wide input signal bandwidth: 500 kHz at 1.2 MSPS sample rate, 16-bit resolution Additional sample rates supported: 300 kSPS, 450 kSPS, 600 kSPS, 900 kSPS, and 1.8 MSPS 4 differential simultaneous sampling channels No active antialiasing filter required LNA and PGA with 45 dB gain range in 6 dB steps Selectable equalizer Flexible data port supports serial or parallel mode Supports FSK mode for FMCW radar systems **On-chip 1.5 V reference** Internal oscillator/PLL input: 16 MHz to 54 MHz High speed serial data interface SPI control 2 general-purpose inputs/outputs 48-lead LFCSP\_SS package Temperature range: -40°C to +125°C Single supply operation of 3.3 V **Qualified for automotive applications**

#### APPLICATIONS

Automotive LSR systems Data acquisition systems

#### **GENERAL DESCRIPTION**

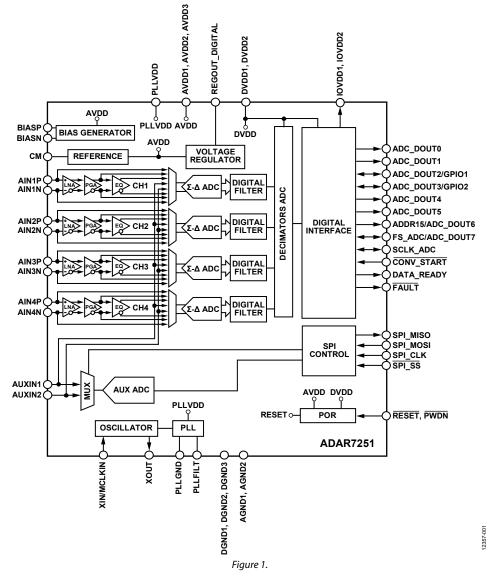

The ADAR7251 is a 16-bit, 4-channel, simultaneous sampling analog-to-digital converter (ADC) designed especially for applications such as automotive LSR-FMCW or FSK-FMCW radar systems. Each of the four channels contains a low noise amplifier (LNA), a programmable gain amplifier (PGA), an equalizer, a multibit  $\Sigma$ - $\Delta$  ADC, and a decimation filter.

The front-end circuitry is designed to allow direct connection to an MMIC output with few external passive components. The ADAR7251 eliminates the need for a high order antialiasing filter, driver op amps, and external bipolar supplies. The ADAR7251 also offers precise channel-to-channel drift matching.

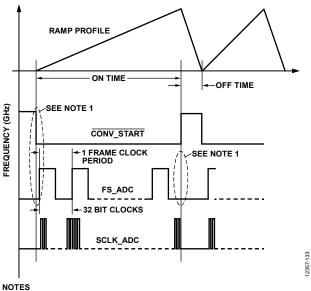

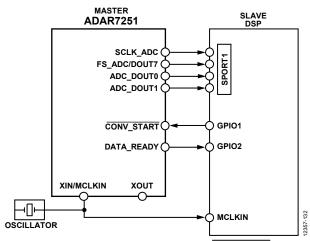

The ADAR7251 features an on-chip phase-locked loop (PLL) that allows a range of clock frequencies for flexibility in the system. The CONV\_START input and DATA\_READY output signals synchronize the ADC with an external ramp for applications such as FSK-FMCW radar.

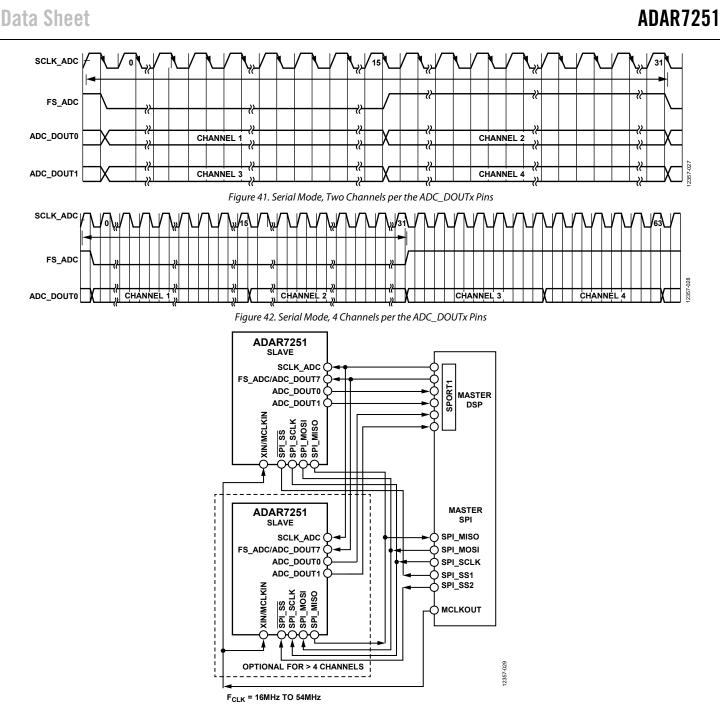

The ADAR7251 supports serial and parallel interfaces at programmable sample rates from 300 kSPS to 1.8 MSPS, as well as easy connections to digital signal processors (DSPs) and microcontroller units (MCUs) in the system.

Rev. 0

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# TABLE OF CONTENTS

| Features                                                |

|---------------------------------------------------------|

| Applications                                            |

| General Description                                     |

| Revision History                                        |

| Functional Block Diagram 4                              |

| Specifications                                          |

| Analog Channel 5                                        |

| Digital Input/Output6                                   |

| Power Supply7                                           |

| Digital Filter                                          |

| SPI Port Timing                                         |

| Serial/Peripheral Parallel Interface (PPI) Port Timing  |

| Absolute Maximum Ratings11                              |

| Thermal Resistance11                                    |

| ESD Caution11                                           |

| Pin Configuration and Function Descriptions12           |

| Typical Performance Characteristics14                   |

| Terminology 17                                          |

| Theory of Operation                                     |

| Low Speed Ramp Radar Analog Front End18                 |

| Main Channel Overview18                                 |

| $\Sigma\text{-}\Delta$ Modulation and Digital Filtering |

| Differential Input Configuration19                      |

| Equalizer (EQ)19                                        |

| Using LNA/PGA, EQ, or the Input Capacitor               |

| Reference                                               |

| Auxiliary ADC20                                         |

| Power Supply21                                          |

| LDO21                                                   |

| Clock Requirements21                                    |

| Crystal Oscillator                                      |

| PLL                                                     |

| GPIO                                                    |

| ADC Data Port                                           |

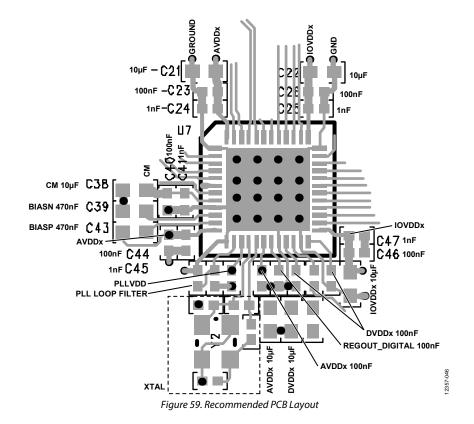

| PCB Layout Guidelines                                   |

| Register Summary                                        |

| Register Details                                        |

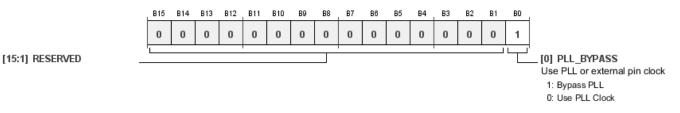

| Clock Control Register                                  |

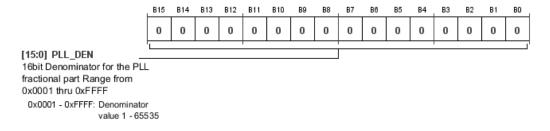

| PLL Denominator Register                                |

| PLL Numerator Register                                  |

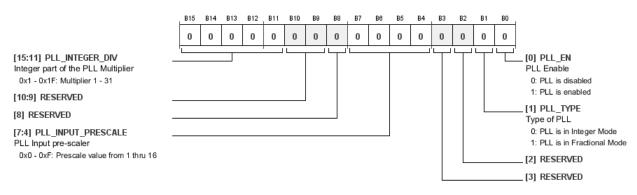

| PLL Control Register                                                    |

|-------------------------------------------------------------------------|

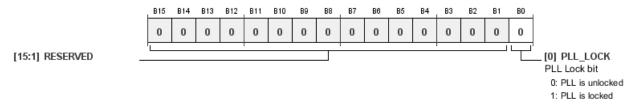

| PLL Status Register                                                     |

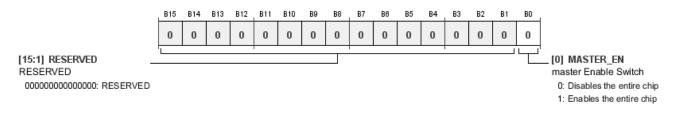

| Master Enable Switch Register 39                                        |

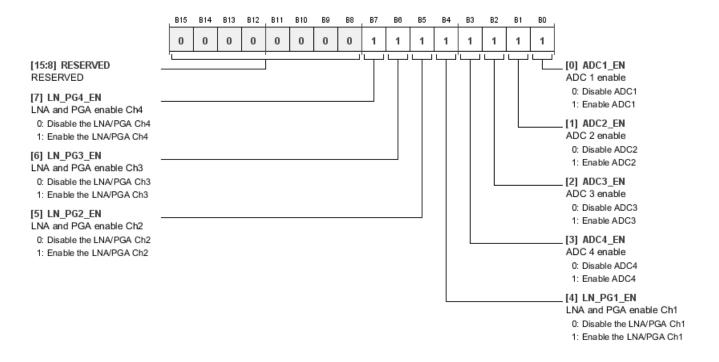

| ADC Enable Register                                                     |

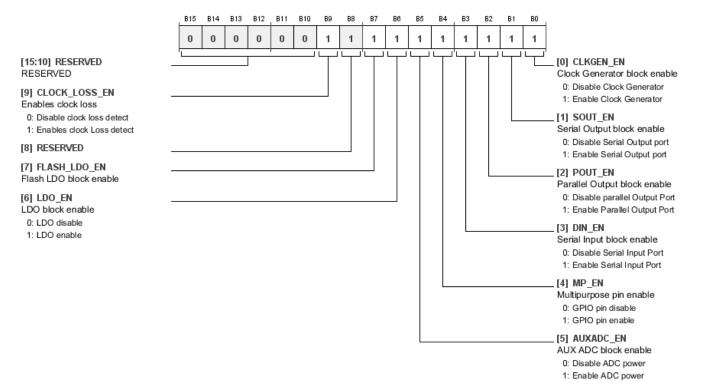

| Power Enable Register 40                                                |

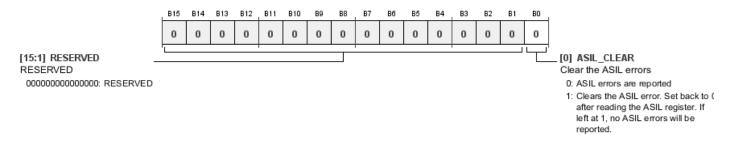

| Clear the ASIL errors Register                                          |

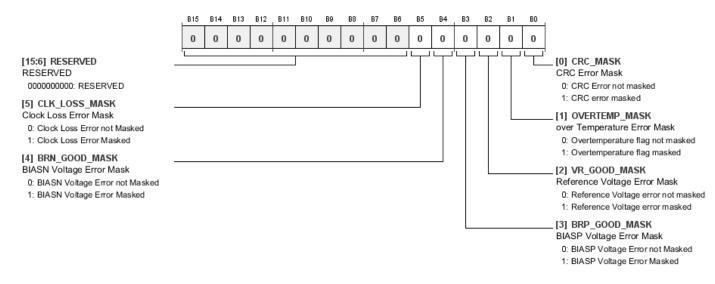

| Selects Which Errors to Mask Register 42                                |

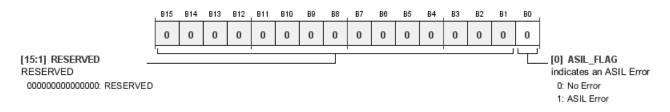

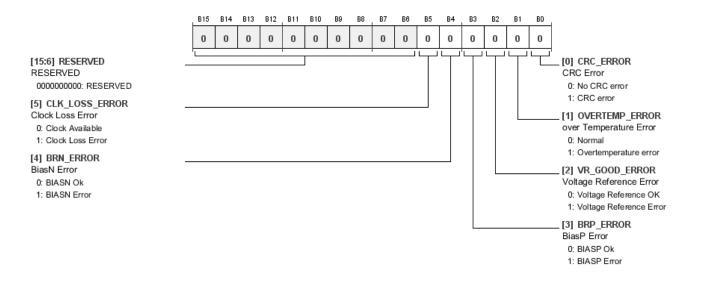

| ASIL Error Flag Register 43                                             |

| ASIL Error Code Register 43                                             |

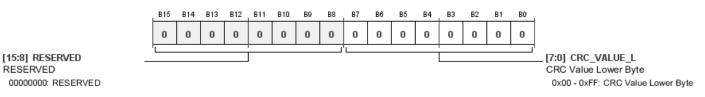

| CRC Value, Bits[7:0] Register                                           |

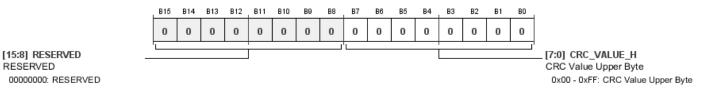

| CRC Value Register                                                      |

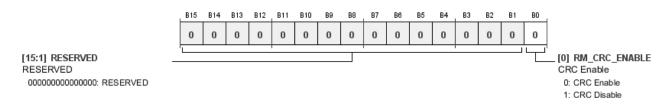

| Start Calculating the CRC Value of the Register Map Content<br>Register |

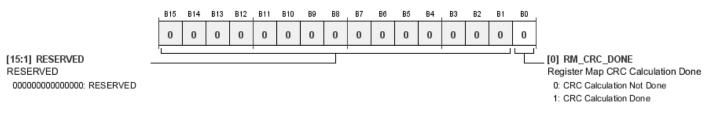

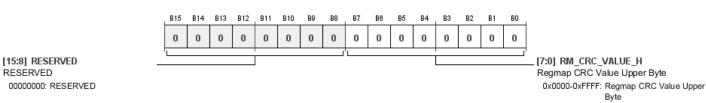

| Register Map CRC Calculation Done Register                              |

| Register Map CRC Value, Bits[7:0] Register                              |

| Register Map CRC Value, Bits[15:8] Register                             |

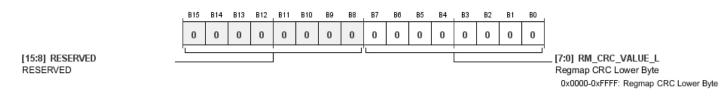

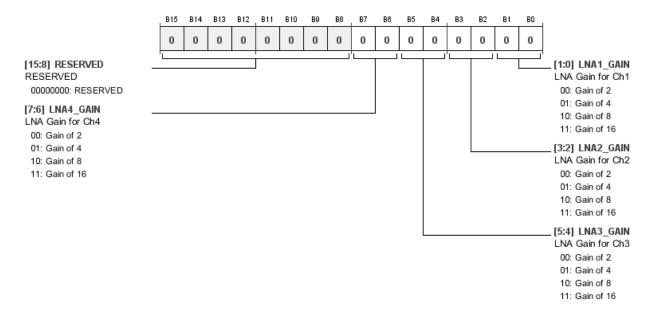

| Low Noise Amplifier Gain Control Register                               |

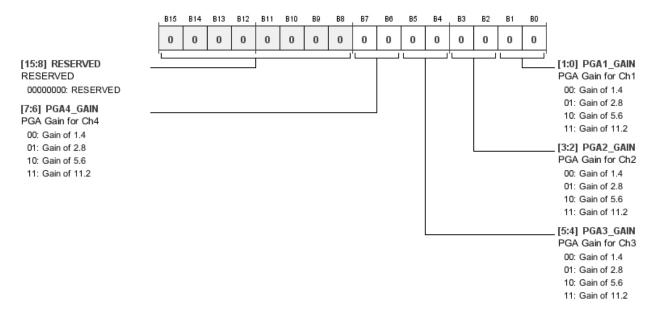

| Programmable Gain Amplifier Gain Control Register 47                    |

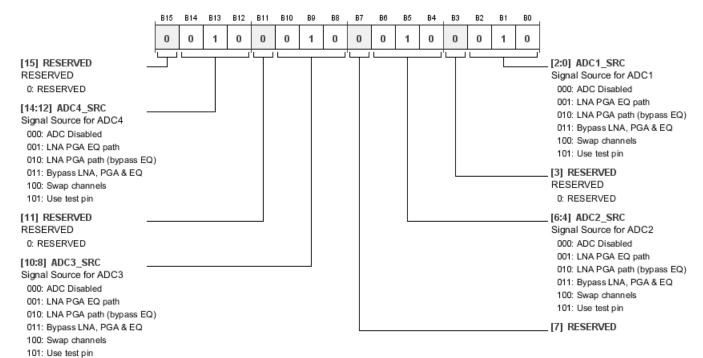

| Signal Path for ADC 1 Through ADC 4 Register 48                         |

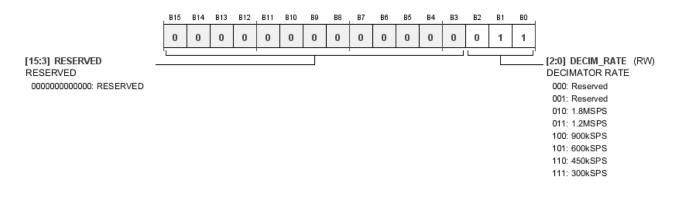

| Decimator Rate Control Register                                         |

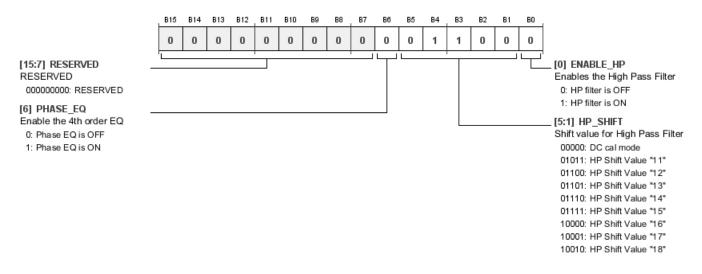

| High Pass Filter Control Register                                       |

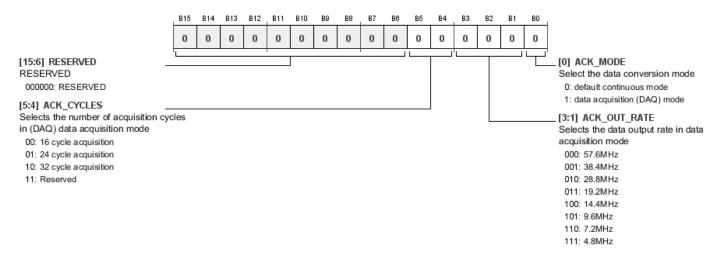

| DAQ Mode Control Register 51                                            |

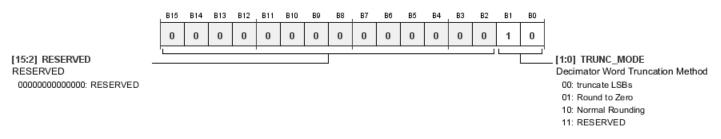

| Decimator Truncate Control Register                                     |

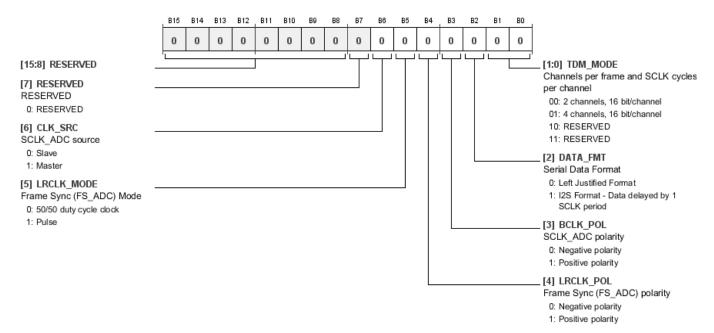

| Serial Output Port Control Register                                     |

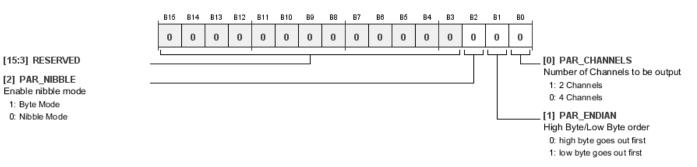

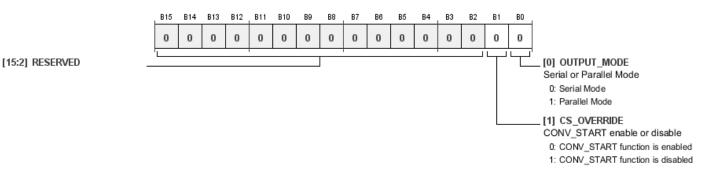

| Parallel Port Control Register                                          |

| ADC Digital Output Mode Register                                        |

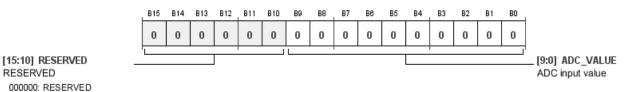

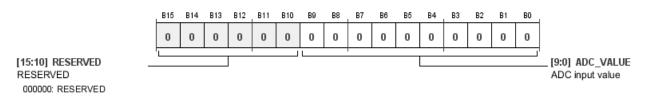

| Auxiliary ADC Read Value Registers                                      |

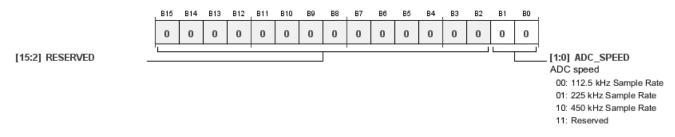

| Auxiliary ADC Sample Rate Selection Register                            |

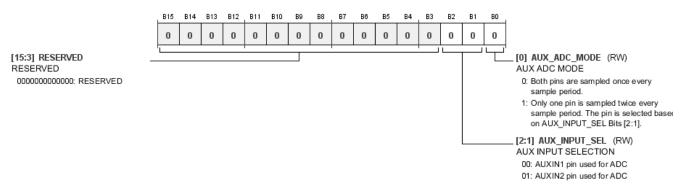

| Auxiliary ADC Mode Register                                             |

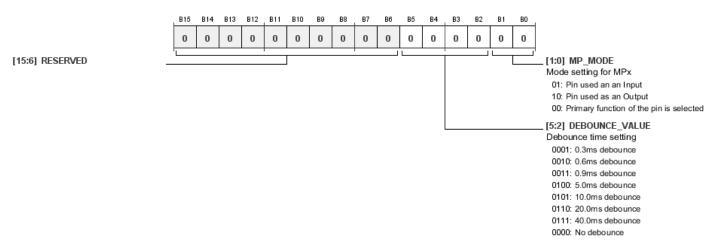

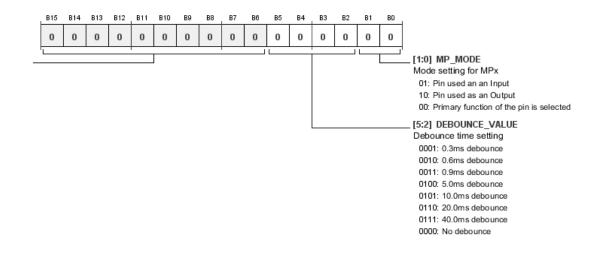

| MPx Pin Modes Registers                                                 |

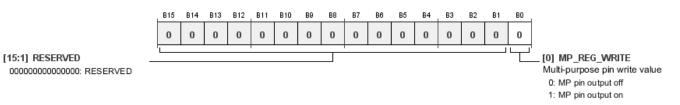

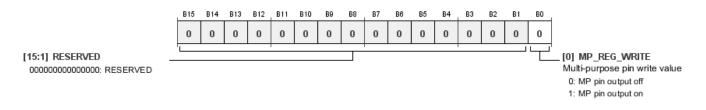

| MP Write Value Registers                                                |

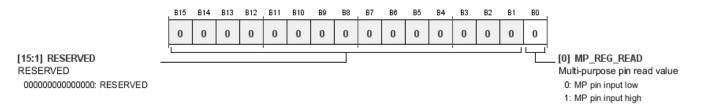

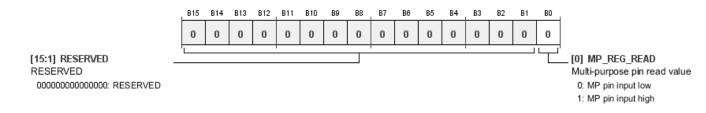

| MP Read Value Registers                                                 |

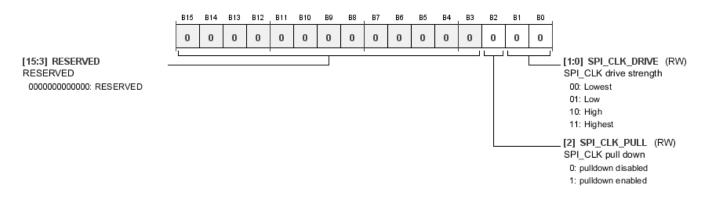

| SPI_CLK Pin Drive Strength and Slew Rate Register                       |

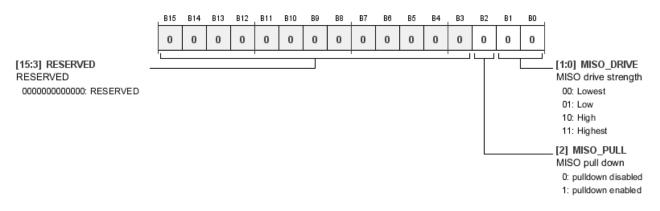

| SPI_MISO Pin Drive Strength and Slew Rate Register 60                   |

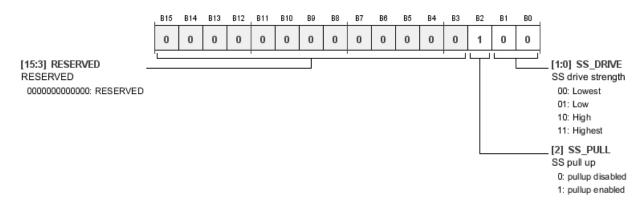

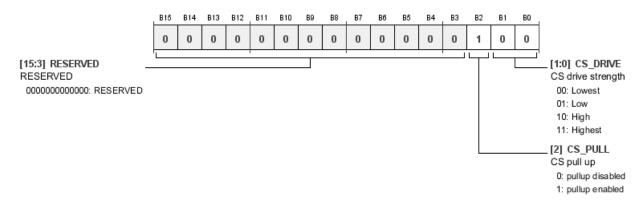

| SPI_SS Pin Drive Strength and Slew Rate Register                        |

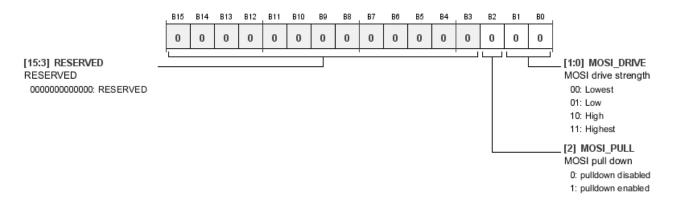

| SPI_MOSI Pin Drive Strength and Slew Rate Register 61                   |

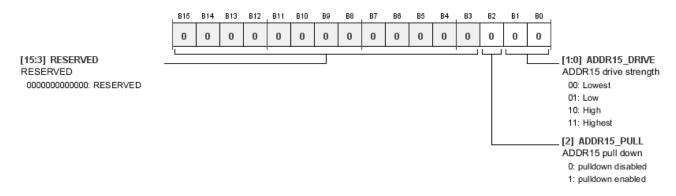

| ADDR15 Pin Drive Strength and Slew Rate Register                        |

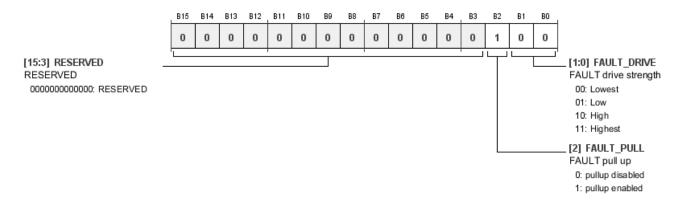

| FAULT Pin Drive Strength and Slew Rate Register                         |

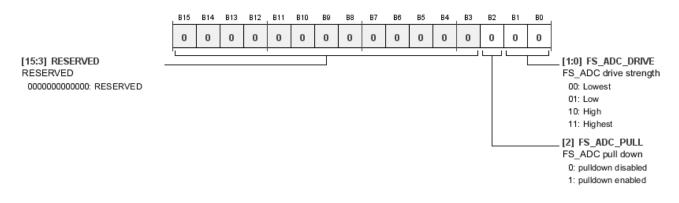

| FS_ADC Pin Drive Strength and Slew Rate Register                        |

| CONV_START Pin Drive Strength and Slew Rate Register 64                 |

| 0 0 0                                                                   |

### **Data Sheet**

## ADAR7251

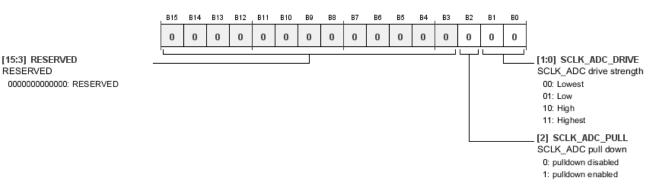

| SCLK_ADC Pin Drive Strength and Slew Rate Register64    |

|---------------------------------------------------------|

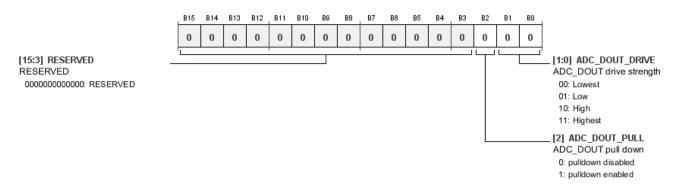

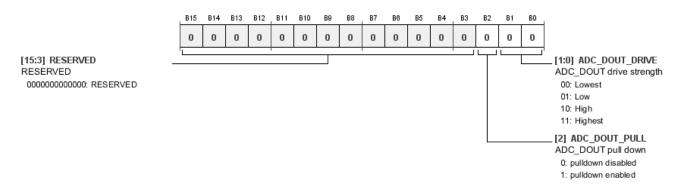

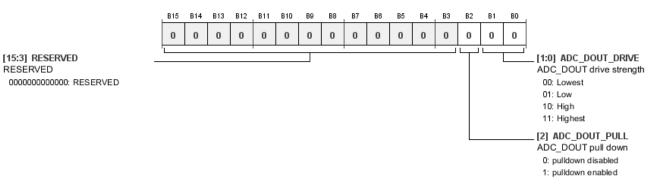

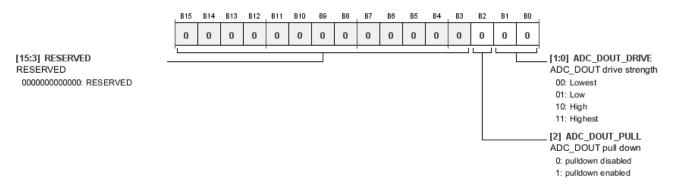

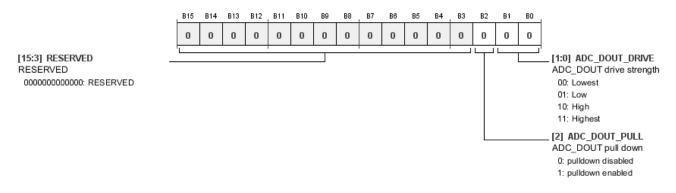

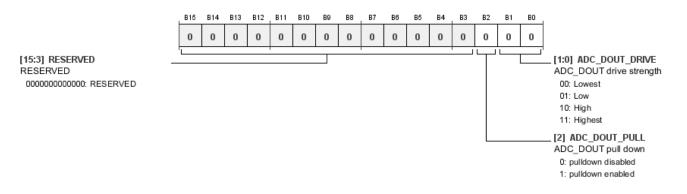

| ADC_DOUTx Pins Drive Strength and Slew Rate Registers65 |

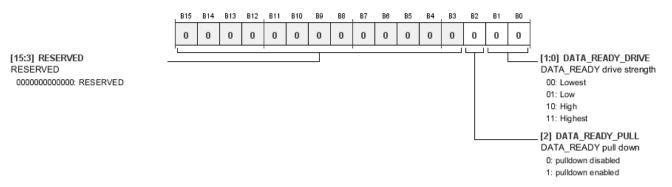

| DATA_READY Pin Drive Strength and Slew Rate Register68  |

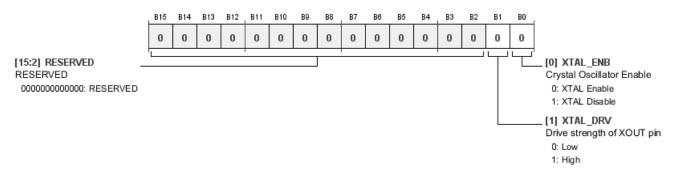

| XTAL Enable and Drive Register68                        |

| ADC Test Register69                                     |

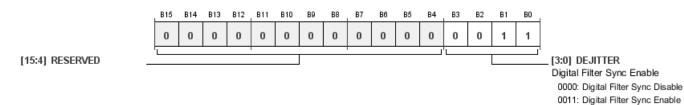

| Digital Filter Sync Enable Register70                   |

###

#### **REVISION HISTORY**

11/14—Revision 0: Initial Version

### FUNCTIONAL BLOCK DIAGRAM

### **SPECIFICATIONS**

### ANALOG CHANNEL

AVDDx = 3.3 V, DVDDx = 1.8 V, IOVDDx = 3.3 V,  $V_{REF} = 1.5 V$  internal/external reference,  $f_{SAMPLE} = 1.2 MSPS$ ,  $T_{AMB} = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted.

#### Table 1.

| Parameter                                      | Test Conditions/Comments                 | Min  | Тур  | Мах  | Unit   |

|------------------------------------------------|------------------------------------------|------|------|------|--------|

| DYNAMIC PERFORMANCE                            |                                          |      |      |      |        |

| Input Referred Noise Spectral Density          |                                          |      |      |      |        |

| Frequency = 100 Hz                             |                                          |      |      |      |        |

|                                                | Gain = 9 dB                              |      | 44.7 |      | nV/√Hz |

|                                                | Gain = 15 dB                             |      | 23.6 |      | nV/√Hz |

|                                                | Gain = 21 dB                             |      | 15   |      | nV/√Hz |

|                                                | Gain = 27 dB                             |      | 12   |      | nV/√Hz |

|                                                | Gain = 33 dB                             |      | 11.3 |      | nV/√Hz |

|                                                | Gain = 39 dB                             |      | 10.9 |      | nV/√Hz |

|                                                | Gain = 45 dB                             |      | 10.8 |      | nV/√Hz |

| Frequency = 1 kHz                              |                                          |      |      |      |        |

|                                                | Gain = 9 dB                              |      | 16   |      | nV/√Hz |

|                                                | Gain = 15 dB                             |      | 8.7  |      | nV/√Hz |

|                                                | Gain = 21 dB                             |      | 5.4  |      | nV/√Hz |

|                                                | Gain = 27 dB                             |      | 4.3  |      | nV/√Hz |

|                                                | Gain = 33 dB                             |      | 4    |      | nV/√Hz |

|                                                | Gain = 39 dB                             |      | 3.86 |      | nV/√Hz |

|                                                | Gain = 45 dB                             |      | 3.83 |      | nV/√Hz |

| Frequency = 100 kHz                            |                                          |      |      |      |        |

|                                                | Gain = 9 dB                              |      | 9.7  |      | nV/√Hz |

|                                                | Gain = 15 dB                             |      | 5.2  |      | nV/√Hz |

|                                                | Gain = 21 dB                             |      | 3.3  |      | nV/√Hz |

|                                                | Gain = 27 dB                             |      | 2.67 |      | nV/√Hz |

|                                                | Gain = 33 dB                             |      | 2.5  |      | nV/√Hz |

|                                                | Gain = 39 dB                             |      | 2.44 |      | nV/√Hz |

|                                                | Gain = 45 dB                             |      | 2.4  |      | nV/√Hz |

| Equalizer Corner Frequency                     | Setting 1 EQ00                           |      | 54   |      | kHz    |

|                                                | Setting 2 EQ01                           |      | 45   |      | kHz    |

|                                                | Setting 3 EQ10                           |      | 37   |      | kHz    |

|                                                | Setting 4 EQ11                           |      | 32   |      | kHz    |

| Signal to Noise Ratio (SNR)                    | No input signal and reference to 0 dBFS  | 88   | 94   |      | dB     |

| Spurious-Free Dynamic Range (SFDR)             | At –3 dBFS input, 100 kHz                | 68   | 82   |      | dB     |

| Total Harmonic Distortion Plus Noise (THD + N) | At –3 dBFS input, 100 kHz                |      | -80  | -66  | dB     |

|                                                | At –1 dBFS input, 100 kHz                |      | -77  | -62  | dB     |

| Channel to Channel Crosstalk                   | At 50 kHz, –3 dBFS input                 |      | -94  | -89  | dB     |

| Interchannel Gain Mismatch                     |                                          | -0.5 | 0    | +0.5 | dB     |

| Interchannel Phase Mismatch                    |                                          | 0.0  | 0.04 |      | Degree |

| DC Offset                                      |                                          |      | -72  |      | dBFS   |

| Power Supply Rejection                         | Ripple = 100 mV rms on AVDDx at<br>1 kHz |      | 65   |      | dB     |

| Parameter                          | Test Conditions/Comments                                       | Min   | Тур   | Max  | Unit   |

|------------------------------------|----------------------------------------------------------------|-------|-------|------|--------|

| ANALOG INPUT                       |                                                                |       |       |      |        |

| Full-Scale Differential Voltage    | Gain = $0 \text{ dB}$ (LNA and PGA bypass)                     |       | 5.6   |      | V p-p  |

|                                    | Gain = 9 dB                                                    |       | 1.987 |      | V p-p  |

|                                    | Gain = 15 dB                                                   |       | 0.995 |      | V p-p  |

|                                    | Gain = 21 dB                                                   |       | 0.498 |      | V p-р  |

|                                    | Gain = 27 dB                                                   |       | 249   |      | mV p-p |

|                                    | Gain = 33 dB                                                   |       | 124   |      | mV p-p |

|                                    | Gain = 39 dB                                                   |       | 62    |      | mV p-p |

|                                    | Gain = 45 dB                                                   |       | 31    |      | mV p-p |

| Common-Mode Rejection Ratio (CMRR) | At 1 kHz                                                       |       | 68    |      | dB     |

| Gain Error                         |                                                                | -0.8  |       | +0.8 | dB     |

| Input Resistance                   | Single-ended                                                   |       | 2860  |      | Ω      |

|                                    | Differential                                                   |       | 5720  |      | Ω      |

| VOLTAGE REFERENCE IN/OUT (VREF)    | At the CM pin                                                  |       | 1.5   |      | V      |

| CONVERSION SAMPLE RATE             |                                                                |       |       |      |        |

| Sample Rate                        |                                                                | 0.3   | 1.2   | 1.8  | MSPS   |

| Input Signal Bandwidth             |                                                                | 150   | 600   | 900  | kHz    |

| PLL                                |                                                                |       |       |      |        |

| Input Frequency                    |                                                                | 16    |       | 54   | MHz    |

| Output Frequency (Internal)        |                                                                |       | 115.2 |      | MHz    |

| Lock Time                          |                                                                |       | 1     |      | ms     |

| LDO                                |                                                                |       |       |      |        |

| REGOUT_DIGITAL Output Voltage      | Used for internal digital core only                            |       | 1.8   |      | V      |

| Line Regulation                    | AVDDx as an input                                              | 2.97  | 3.3   | 3.63 | V      |

| Load Regulation                    | Used for internal digital core only                            |       | 1     |      | %      |

| AUXILIARY ADC                      |                                                                |       |       |      |        |

| Full-Scale Input                   |                                                                |       | 3.3   |      | V p-p  |

| Sample Rate                        |                                                                | 112.5 |       | 450  | kHz    |

| Resolution                         |                                                                |       | 8     |      | bits   |

| INL                                |                                                                |       | 0.5   |      | LSB    |

| DNL                                |                                                                |       | 1     |      | LSB    |

| Input Resistance <sup>1</sup>      | Switched capacitor input at a switching frequency of 112.5 kHz |       | 1.2   |      | MΩ     |

<sup>1</sup> From simulation.

### **DIGITAL INPUT/OUTPUT**

DVDDx = 1.8 V, IOVDDx = 3.3 V,  $C_{\mbox{\scriptsize LOAD}}$  = 22 pF.

Table 2.

| Parameter             | Symbol          | Test Conditions/Comments | Min                 | Тур | Max                 | Unit |

|-----------------------|-----------------|--------------------------|---------------------|-----|---------------------|------|

| INPUT VOLTAGE         |                 |                          |                     |     |                     |      |

| High Level            | VIH             |                          | $0.7 \times IOVDDx$ |     |                     | V    |

| Low Level             | VIL             |                          |                     |     | $0.3 \times IOVDDx$ | V    |

| OUTPUT VOLTAGE        |                 |                          |                     |     |                     |      |

| High Level            | Vон             | I <sub>он</sub> = 1 mA   | IOVDDx – 0.60       |     |                     | V    |

| Low Level             | V <sub>OL</sub> | $I_{OL} = 1 \text{ mA}$  |                     |     | 0.4                 | V    |

| INPUT CAPACITANCE     |                 |                          |                     |     | 5                   | pF   |

| INPUT LEAKAGE CURRENT |                 |                          |                     |     | ±10                 | μΑ   |

#### **POWER SUPPLY**

AVDDx = 3.3 V, DVDDx = 1.8 V, IOVDDx = 3.3 V,  $f_s = 1.2 MHz$  (master mode), PLL enabled with 19.2 MHz master clock input, -3 dBFS, 100 kHz input on all channels, unless otherwise noted.

#### Table 3.

| Parameter                | Test Conditions/Comments                                 | Min  | Тур | Max  | Uni |

|--------------------------|----------------------------------------------------------|------|-----|------|-----|

| DVDD                     | On-chip LDO                                              | 1.62 | 1.8 | 1.98 | V   |

| Current                  |                                                          |      |     |      |     |

| Normal Operation         | DVDDx external at $f_s = 1.2 \text{ MHz}$                |      | 32  |      | mA  |

| Power-Down               | Standby without master clock                             |      | 80  |      | μΑ  |

| AVDD                     |                                                          | 2.97 | 3.3 | 3.6  | V   |

| Current                  |                                                          |      |     |      |     |

| Normal Operation         | 4-channel ADC, DVDDx internal, $f_s = 1.2 \text{ MHz}$   |      | 115 |      | mA  |

|                          | Power save mode                                          |      | 87  |      | mA  |

| Power-Down               | RESET/PWDN pin held low without master clock             |      | 1.1 |      | mA  |

|                          | RESET/PWDN pin held low with master clock                |      | 1.1 |      | mA  |

| IOVDD                    |                                                          | 2.97 | 3.3 | 3.6  | V   |

| Current                  | Input master clock = 19.2 MHz                            |      |     |      |     |

| Normal Operation         | 4-channel ADC; serial mode, 2 channels per data line     |      |     |      |     |

|                          | $f_s = 1.2 \text{ MHz}$                                  |      | 4   |      | mA  |

|                          | f <sub>s</sub> = 900 kHz                                 |      | 3.4 |      | mA  |

|                          | $f_s = 600 \text{ kHz}$                                  |      | 2.7 |      | mA  |

|                          | fs = 300 kHz                                             |      | 2   |      | mA  |

|                          | 4-channel ADC; parallel mode, byte wide format           |      |     |      |     |

|                          | fs = 1.8 MHz                                             |      | 2.8 |      | mA  |

|                          | $f_S = 1.2 \text{ MHz}$                                  |      | 2.3 |      | mA  |

|                          | fs = 900 kHz                                             |      | 2   |      | mA  |

|                          | $f_s = 600 \text{ kHz}$                                  |      | 1.7 |      | mA  |

|                          | $f_s = 300 \text{ kHz}$                                  |      | 1.3 |      | mA  |

| Power-Down               | RESET/PWDN pin held low without master clock             |      | 335 |      | μΑ  |

|                          | RESET/PWDN pin held low with master clock                |      | 360 |      | μA  |

| POWER DISSIPATION        |                                                          |      |     |      |     |

| Normal Operation         | Input master clock = 19.2 MHz                            |      |     |      |     |

|                          | DVDDx internal, 4-channel ADC at $f_s = 1.2 \text{ MHz}$ |      | 400 |      | m٧  |

|                          | DVDDx external, 4-channel ADC at $f_s = 1.2 \text{ MHz}$ |      | 294 |      | m٧  |

| Power-Down, All Supplies | RESET/PWDN pin held low with master clock                |      | 5   |      | m٧  |

#### **DIGITAL FILTER**

#### Table 4.

| Parameter                                             | Mode                                                                | Factor             | Min   | Тур  | Мах  | Unit |

|-------------------------------------------------------|---------------------------------------------------------------------|--------------------|-------|------|------|------|

| ADC DECIMATION FILTER                                 | At $f_s = 1.2$ MHz, decimation ratio = 48                           |                    |       |      |      |      |

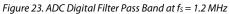

| At f <sub>s</sub> = 1.2 MHz, Decimation<br>Ratio = 48 |                                                                     |                    |       |      |      |      |

| Pass Band                                             | –0.1 dB corner                                                      | $0.166 \times f_s$ |       | 200  |      | kHz  |

| Pass-Band Droop                                       | At 600 kHz                                                          |                    |       | -1.4 |      | dB   |

| Stop Band                                             |                                                                     | $0.666 \times f_s$ |       | 800  |      | kHz  |

| Stop-Band Attenuation                                 |                                                                     |                    |       | 70   |      | dB   |

| Group Delay                                           |                                                                     |                    |       | 95   |      | μs   |

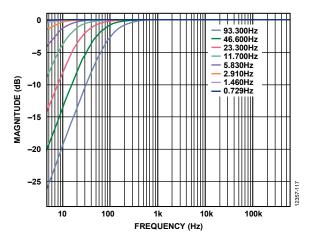

| High-Pass Filter                                      |                                                                     |                    |       |      |      |      |

| Corner Frequency                                      | -3 dB, programmable in eight steps                                  |                    | 0.729 |      | 93.3 | Hz   |

| Attenuation                                           | See Figure 24 in the Typical<br>Performance Characteristics section |                    |       |      |      |      |

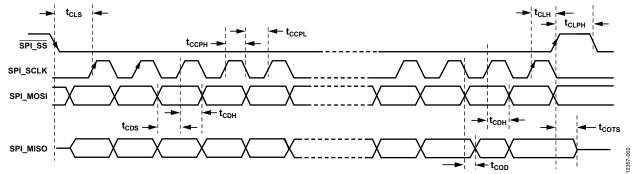

#### **SPI PORT TIMING**

DVDDx = 1.8 V, IOVDDx = 3.3 V, C  $_{\text{LOAD}}$  = 22 pF,  $I_{\text{OUT}}$  = ±1 mA.

#### Table 5.

|                   |                                      |     | Limit a | t   |      |

|-------------------|--------------------------------------|-----|---------|-----|------|

| Parameter         | Description                          | Min | Тур     | Max | Unit |

| SPI PORT          | See Figure 2                         |     |         |     |      |

| <b>t</b> ссрн     | SPI_SCLK high                        | 50  |         |     | ns   |

| t <sub>CCPL</sub> | SPI_SCLK low                         | 50  |         |     | ns   |

| <b>f</b> spi_clk  | SPI_SCLK frequency                   |     |         | 10  | MHz  |

| t <sub>CDS</sub>  | SPI_MOSI setup to SPI_SCLK rising    | 10  |         |     | ns   |

| t <sub>cdh</sub>  | SPI_MOSI hold from SPI_SCLK rising   | 10  |         |     | ns   |

| t <sub>CLS</sub>  | SPI_SS setup to SPI_SCLK rising      | 10  |         |     | ns   |

| t <sub>CLH</sub>  | SPI_SS hold from SPI_SCLK rising     | 40  |         |     | ns   |

| <b>t</b> clph     | SPI_SS high                          | 10  |         |     | ns   |

| t <sub>cdh</sub>  | SPI_MISO hold from SPI_SCLK rising   |     |         | 30  | ns   |

| t <sub>COD</sub>  | SPI_MISO delay from SPI_SCLK falling |     |         | 30  | ns   |

| <b>t</b> cots     | SPI_MISO tristate from SPI_SS rising |     |         | 30  | ns   |

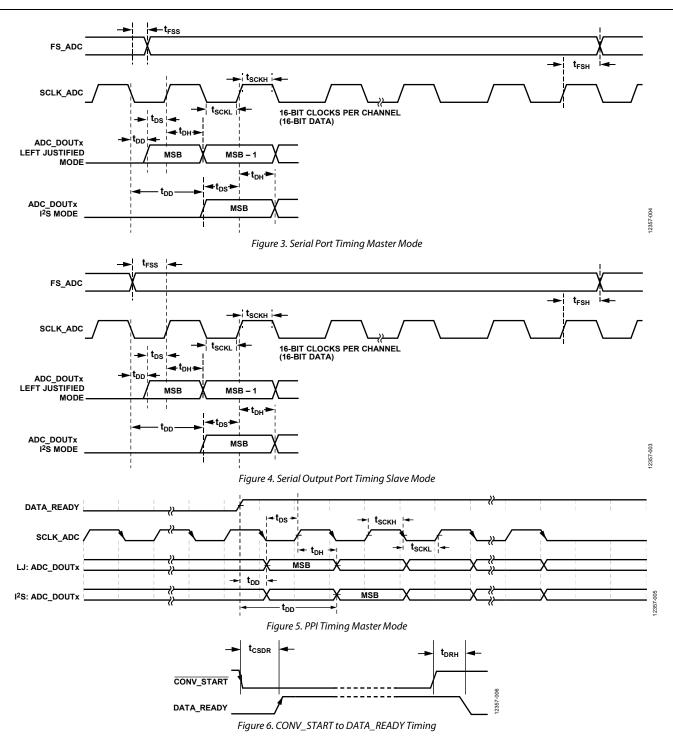

#### SERIAL/PERIPHERAL PARALLEL INTERFACE (PPI) PORT TIMING

DVDDx = 1.8 V, IOVDDx = 3.3 V,  $C_{LOAD} = 22 pF$ ,  $I_{OUT} = \pm 1 mA$ .

Table 6.

|                             |                                                                                                     |     | Limit at |     |      |

|-----------------------------|-----------------------------------------------------------------------------------------------------|-----|----------|-----|------|

| Parameter                   | Description                                                                                         | Min | Тур      | Max | Unit |

| INPUT MASTER CLOCK (MCLKIN) |                                                                                                     |     |          |     |      |

| Duty Cycle                  | MCLKIN duty cycle; MCLKIN at 256 $\times$ fs, 384 $\times$ fs, 512 $\times$ fs, and 768 $\times$ fs | 40  |          | 60  | %    |

| fmclkin                     | MCLKIN frequency, PLL in MCLK mode                                                                  | 16  |          | 54  | MHz  |

| RESET                       |                                                                                                     |     |          |     |      |

| Reset Pulse, tRESET         | RESET/PWDN held low                                                                                 | 15  |          |     | ns   |

| PLL                         |                                                                                                     |     |          |     |      |

| Lock Time                   |                                                                                                     |     |          | 1   | ms   |

### **Data Sheet**

## ADAR7251

|                                    |                                                                                                 |     | Limit a | t     |      |

|------------------------------------|-------------------------------------------------------------------------------------------------|-----|---------|-------|------|

| Parameter                          | Description                                                                                     | Min | Тур     | Max   | Unit |

| ADC SERIAL PORT MASTER<br>MODE     | See Figure 3                                                                                    |     |         |       |      |

| tscкн                              | SCLK_ADC high, slave mode                                                                       | 10  |         |       | ns   |

| <b>t</b> scкL                      | SCLK_ADC low, slave mode                                                                        | 10  |         |       | ns   |

| t <sub>Ds</sub>                    | ADC_DOUTx setup to SCLK_ADC rising, slave mode                                                  | 10  |         |       | ns   |

| t <sub>DH</sub>                    | ADC_DOUTx hold from SCLK_ADC rising, slave mode                                                 | 5   |         |       | ns   |

| t <sub>DD</sub>                    | ADC_DOUTx delay from SCLK_ADC falling                                                           |     |         | 18    | ns   |

| t <sub>FSH</sub>                   | FS_ADC hold from SCLK_ADC rising                                                                |     |         | 18    | ns   |

| t <sub>FSS</sub>                   | FS_ADC setup from SCLK_ADC falling                                                              |     |         | 1     | ns   |

| ADC SERIAL PORT SLAVE MODE         | See Figure 4                                                                                    |     |         |       |      |

| tscкн                              | SCLK_ADC high, slave mode                                                                       | 7   |         |       | ns   |

| <b>t</b> sckl                      | SCLK_ADC low, slave mode                                                                        | 7   |         |       | ns   |

| t <sub>DS</sub>                    | ADC_DOUTx valid to SCLK_ADC rising, slave mode                                                  | 11  |         |       | ns   |

| t <sub>DH</sub>                    | ADC_DOUTx hold from SCLK_ADC rising, slave mode                                                 | 11  |         |       | ns   |

| t <sub>DD</sub>                    | ADC_DOUTx delay from SCLK_ADC falling                                                           |     |         | 2     | ns   |

| t <sub>FSH</sub>                   | FS_ADC hold from SCLK_ADC rising                                                                |     |         | 1     | ns   |

| t <sub>FSS</sub>                   | FS_ADC setup from SCLK_ADC falling                                                              |     |         | 1     | ns   |

| PARALLEL MODE, BYTE WIDE<br>FORMAT | See Figure 5; if usingCONV_START, see Figure 6 for the CONV_START to DATA_READY timing relation |     |         |       |      |

| t <sub>scкн</sub>                  | SCLK_ADC high, master mode                                                                      | 28  |         |       | ns   |

| t <sub>sckl</sub>                  | SCLK_ADC low, master mode                                                                       | 28  |         |       | ns   |

| t <sub>DS</sub>                    | ADC_DOUTx setup to SCLK_ADC rising, master mode                                                 | 7   |         |       | ns   |

| t <sub>DH</sub>                    | ADC_DOUTx hold from SCLK_ADC rising, master mode                                                | 5   |         |       | ns   |

| t <sub>DD</sub>                    | ADC_DOUTx delay from SCLK_ADC falling for left justified (LJ) mode                              |     |         | 6     | ns   |

|                                    | For I <sup>2</sup> S mode, add one SCLK_ADC period to the t <sub>DD</sub> of LJ mode            |     |         |       |      |

| tcsdr                              | CONV_START falling to DATA_READY rising                                                         |     |         | 1.215 | μs   |

| DATA ACQUISITION (DAQ)<br>MODE     | CONV_START falling to DATA_READY rising, see Figure 6                                           |     |         |       |      |

| t <sub>DRH</sub>                   | CONV_START rising to DATA_READY falling                                                         |     |         | 0.44  | μs   |

| t <sub>csdr</sub>                  | DAQ16 mode (16 acquisition clock cycles)                                                        |     |         | 1.215 | μs   |

|                                    | DAQ24 mode (24 acquisition clock cycles)                                                        |     |         | 1.8   | μs   |

|                                    | DAQ32 mode (32 acquisition clock cycles)                                                        |     |         | 2.43  | μs   |

#### Timing Diagrams

Figure 2. SPI Port Timing

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 7.

| Parameter                                      | Rating            |

|------------------------------------------------|-------------------|

| AVDDx to AGNDx, DGNDx                          | –0.3 V to +3.63 V |

| DVDDx to AGNDx, DGNDx                          | –0.3 V to +1.98 V |

| IOVDDx to AGNDx, DGNDx                         | –0.3 V to +3.63 V |

| AGNDx to DGNDx                                 | –0.3 V to +0.3 V  |

| Analog Input Voltage to AGNDx                  | –0.3 V to +3.63 V |

| Digital Input Voltage to DGNDx                 | –0.3 V to +3.63 V |

| Digital Output Voltage to DGNDx                | –0.3 V to +3.63 V |

| Input Current to Any Pin Except Supplies       | ±10 mA            |

| Operating Temperature Range (Ambient)          | -40°C to +125°C   |

| Junction Temperature Range                     | -40°C to + 150°C  |

| Storage Temperature Range                      | −65°C to +150°C   |

| RoHS-Compliant Temperature Soldering<br>Reflow | 260°C             |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

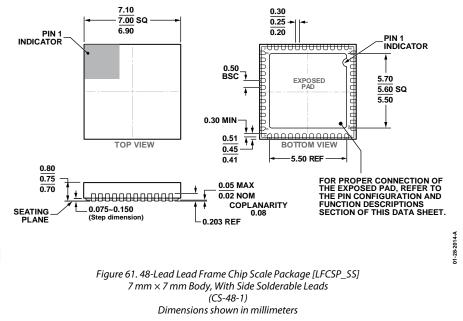

#### THERMAL RESISTANCE

$\theta_{JA}$  represents junction-to-ambient thermal resistance, and  $\theta_{JC}$  represents the junction-to-case thermal resistance. All characteristics are for a standard JEDEC board per JESD51.

#### Table 8. Thermal Resistance

| Package Type     | $\theta_{JA}^{1}$ | θ <sub>JC</sub> 1 | Unit |

|------------------|-------------------|-------------------|------|

| 48-Lead LFCSP_SS | 25                | 1                 | °C/W |

<sup>1</sup>JEDEC 2S2P standard board.

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

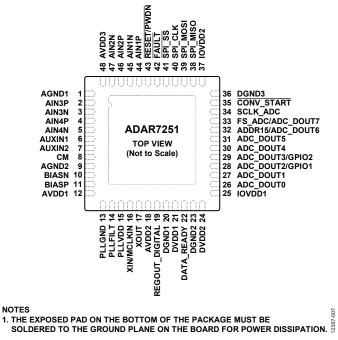

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 7. Pin Configuration

#### **Table 9. Pin Function Descriptions**

| Pin No. | Mnemonic           | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                          |  |

|---------|--------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|         | EPAD               |                   | Exposed Pad. The exposed pad on the bottom of the package must be soldered to the ground plane on the board for power dissipation.                                                                                                                                   |  |

| 1       | AGND1 <sup>2</sup> | PWR               | Analog Ground. This pin is the ground reference point for all analog blocks in the ADAR7251.                                                                                                                                                                         |  |

| 2       | AIN3P              | AIN               | Noninverting Input to Differential Analog Channel 3.                                                                                                                                                                                                                 |  |

| 3       | AIN3N              | AIN               | Inverting Input to Differential Analog Channel 3.                                                                                                                                                                                                                    |  |

| 4       | AIN4P              | AIN               | Noninverting Input to Differential Analog Channel 4.                                                                                                                                                                                                                 |  |

| 5       | AIN4N              | AIN               | Inverting Input to Differential Analog Channel 4.                                                                                                                                                                                                                    |  |

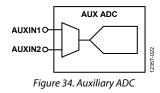

| 6       | AUXIN1             | AIN               | Auxiliary ADC Analog Input 1. Single-ended analog input channel.                                                                                                                                                                                                     |  |

| 7       | AUXIN2             | AIN               | Auxiliary ADC Analog Input 2. Single-ended analog input channel.                                                                                                                                                                                                     |  |

| 8       | СМ                 | AIO               | ADC Reference Output. Connect a 10 $\mu$ F capacitor in parallel with a 100 nF capacitor from this pin to AGNDx.                                                                                                                                                     |  |

| 9       | AGND2 <sup>2</sup> | PWR               | Analog Ground. This pin is the ground reference point for all analog blocks in the ADAR7251.                                                                                                                                                                         |  |

| 10      | BIASN              | AOUT              | Internal Bias Generator. Decouple to AGNDx using a 0.47 µF capacitor.                                                                                                                                                                                                |  |

| 11      | BIASP              | AOUT              | Internal Bias Generator. Decouple to AVDDx using a 0.47 µF capacitor.                                                                                                                                                                                                |  |

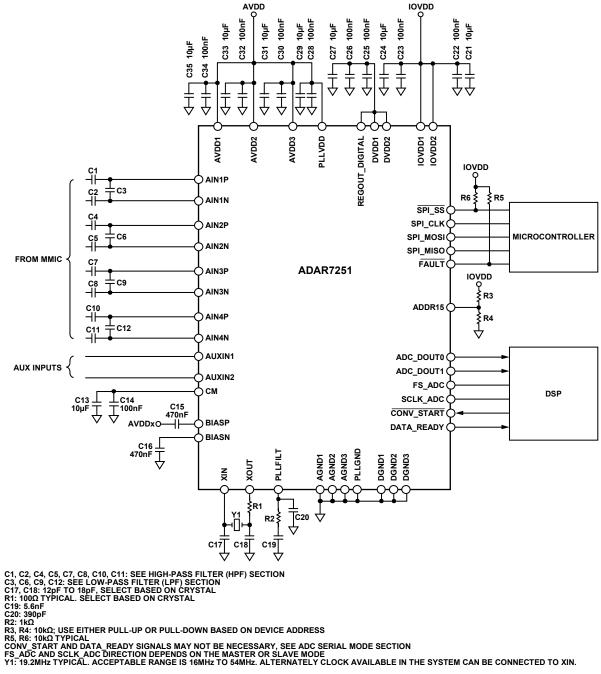

| 12      | AVDD1              | PWR               | Analog Supply Voltage, 3.3 V. Decouple this supply pin to AGNDx. See Figure 60.                                                                                                                                                                                      |  |

| 13      | PLLGND             | PWR               | Analog Ground for PLL. Connect to a ground plane directly on the board.                                                                                                                                                                                              |  |

| 14      | PLLFILT            | AIN               | Filter Components Connection for PLL. See Figure 60.                                                                                                                                                                                                                 |  |

| 15      | PLLVDD             | PWR               | Analog Supply for Analog PLL, 3.3 V. Decouple to the PLLGND pin (Pin13) using a 0.1 µF multilayer ceramic capacitor (MLCC). Connect to AVDDx or an external 3.3 V source. It is recommended to add the filter for a clean 3.3 V source and for good PLL performance. |  |

| 16      | XIN/MCLKIN         | AIN               | Internal Oscillator Input/Clock Input. If using an external crystal, connect it between the XIN and XOUT pins. If not using a crystal, a single-ended clock must be provided at the MCLKIN pin. The ADAR7251 accepts a clock frequency range of 16 MHz to 54 MHz.    |  |

| 17      | XOUT               | AOUT              | Internal Oscillator Output Connection for External Crystal.                                                                                                                                                                                                          |  |

| 18      | AVDD2              | PWR               | Analog Supply Voltage, 3.3 V. Decouple this supply pin to AGNDx. See Figure 60.                                                                                                                                                                                      |  |

| 19      | REGOUT_DIGITAL     | PWR               | LDO Regulator Output for Internal Digital Core (1.8 V, Typical). Decouple to DGNDx. See Figure 60. Connect REGOUT_DIGITAL to the DVDDx pins if using the internal regulator to supply the 1.8 V to the digital core.                                                 |  |

| 20      | DGND1 <sup>3</sup> | PWR               | Digital Ground. This pin is the ground reference point for the digital circuitry on the ADAR7251.                                                                                                                                                                    |  |

| Pin No. | Mnemonic             | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                          |  |

|---------|----------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 21      | DVDD1                | PWR               | Digital Core Power Supply Input. Connect decoupling capacitors between the DVDDx and DGNDx pins. See Figure 60. The voltage on this pin is 1.8 V. This pin can be connected to REGOUT_DIGITAL (Pin 19), or to the external 1.8 V source if the internal LDO is not used.                                                             |  |

| 22      | DATA_READY           | DOUT              | ADC Conversion Data Ready Output. Connect to the DSP general-purpose input/output (GPIO) in the system.                                                                                                                                                                                                                              |  |

| 23      | DGND2 <sup>3</sup>   | PWR               | Digital Ground. This pin is the ground reference point for digital circuitry on the ADAR7251.                                                                                                                                                                                                                                        |  |

| 24      | DVDD2                | PWR               | Digital Core Power Supply Input. Connect decoupling capacitors between the DVDDx and DGNDx pins. See Figure 60. The voltage on this pin is 1.8 V. This pin can be connected to REGOUT_DIGITAL (Pin 19), or to the external 1.8 V source if the internal LDO is not used.                                                             |  |

| 25      | IOVDD1               | PWR               | Logic Power Supply Input. The voltage supplied at this pin determines at what voltage the interface operates. Connect decoupling capacitors between the IOVDDx and DGNDx pins. See Figure 60.                                                                                                                                        |  |

| 26      | ADC_DOUT0            | DOUT              | ADC Data Output (Serial Mode) or ADC Data Output Bit 0 and Bit 8 (PPI Mode). Refer to the ADC Serial Mode and ADC PPI (Byte Wide Mode) sections for function information.                                                                                                                                                            |  |

| 27      | ADC_DOUT1            | DOUT              | ADC Data Output (Serial Mode) or ADC Data Output Bit 1/9 (PPI Mode). Refer to the ADC Serial Mode and ADC PPI (Byte Wide Mode) sections for function information.                                                                                                                                                                    |  |

| 28      | ADC_DOUT2/GPIO1      | DOUT              | ADC Data Output Bit 2 and Bit 10 (PPI Mode)/General-Purpose Input/Output 1. Refer to the ADC Serial Mode section for function information.                                                                                                                                                                                           |  |

| 29      | ADC_DOUT3/GPIO2      | DOUT              | ADC Data Output Bit 3 and Bit 11 (PPI Mode)/General-Purpose Input/Output 2. Refer to the ADC PPI (Byte Wide Mode) section for function information.                                                                                                                                                                                  |  |

| 30      | ADC_DOUT4            | DIO               | ADC Data Output Bit 4 and Bit 12 (PPI Mode). Refer to the ADC PPI (Byte Wide Mode) section for function information.                                                                                                                                                                                                                 |  |

| 31      | ADC_DOUT5            | DIO               | ADC Data Output Bit 5 and Bit 13 (PPI Mode). Refer to the ADC PPI (Byte Wide Mode) section for function information.                                                                                                                                                                                                                 |  |

| 32      | ADDR15/<br>ADC_DOUT6 | DIO               | Device Address Setting for the SPI Control Interface/ADC Data Output Bit 6 and Bit 14 in PPI mode.<br>This pin sets Bit 1 of the SPI device address. Connect to either DGNDx or IOVDDx as desired using a<br>10 k $\Omega$ pull-down or pull-up resistor. Refer to the ADC PPI (Byte Wide Mode) section for function<br>information. |  |

| 33      | FS_ADC/<br>ADC_DOUT7 | DIO               | Active Low Frame Synchronization Signal for Default ADC Data (Serial Mode)/ADC Data Output Bit 7 and Bit 15 (PPI Mode). Refer to the ADC PPI (Byte Wide Mode) section for function information.                                                                                                                                      |  |

| 34      | SCLK_ADC             | DIO               | Serial Bit Clock for the ADC Data Output (Serial Mode and PPI Mode). This pin is an input in slave mode or is an output in master mode.                                                                                                                                                                                              |  |

| 35      | CONV_START           | DIN               | ADC Conversion Start in DAQ/PPI/Serial Mode (Active Low). An active low signal initiates an ADC conversion. See the Theory of Operation section for further details.                                                                                                                                                                 |  |

| 36      | DGND3 <sup>3</sup>   | PWR               | Digital Ground. This pin is the ground reference point for digital circuitry on the ADAR7251.                                                                                                                                                                                                                                        |  |

| 37      | IOVDD2               | PWR               | Logic Power Supply Input. The voltage supplied at this pin determines at what voltage the interface operates. Connect decoupling capacitors between the IOVDDx and DGNDx pins. See Figure 60.                                                                                                                                        |  |

| 38      | SPI_MISO             | DOUT              | SPI Control Interface Slave Data Output.                                                                                                                                                                                                                                                                                             |  |

| 39      | SPI_MOSI             | DIN               | SPI Control Interface Slave Data Input.                                                                                                                                                                                                                                                                                              |  |

| 40      | SPI_CLK              | DIN               | SPI Control Interface Serial clock Input.                                                                                                                                                                                                                                                                                            |  |

| 41      | SPI_SS               | DIN               | SPI Control Interface Slave Select (Active Low Input). Connect an external 10 $k\Omega$ pull-up resistor to IOVDDx.                                                                                                                                                                                                                  |  |

| 42      | FAULT                | DOUT              | Digital Output. This pin becomes active under fault condition. Connect an external 10 k $\Omega$ pull-up resistor to IOVDDx. This pin can be used as an interrupt input to the microcontroller or DSP in case o faults.                                                                                                              |  |

| 43      | RESET/PWDN           | DIN               | Active Low Reset Input/Power-Down. The ADAR7251 requires an external reset signal to hold the RESET input low until AVDDx is within the specified operating range. When held low, this pin places the ADAR7251 into power-down mode.                                                                                                 |  |

| 44      | AIN1P                | AIN               | Noninverting Input to Differential Analog Channel 1.                                                                                                                                                                                                                                                                                 |  |

| 45      | AIN1N                | AIN               | Inverting Input to Differential Analog Channel 1.                                                                                                                                                                                                                                                                                    |  |

| 46      | AIN2P                | AIN               | Noninverting Input to Differential Analog Channel 2.                                                                                                                                                                                                                                                                                 |  |

| 47      | AIN2N                | AIN               | Inverting Input to Differential Analog Channel 2.                                                                                                                                                                                                                                                                                    |  |

| 48      | AVDD3                | PWR               | Analog Supply Voltage. Decouple this supply pin to AGNDx.                                                                                                                                                                                                                                                                            |  |

<sup>1</sup> PWR is power supply or ground pin, AIN is analog input, AIO is analog input/output, AOUT is analog output, DIN is digital input, DOUT is digital output, and DIO is

<sup>2</sup> All the AGNDx pins (AGND1 and AGND2) are shorted internally and recommended to be connected to a single ground plane on the board. Refer to the PCB Layout Guidelines section for details.

<sup>3</sup> All the DGNDx pins (DGND1, DGND2, and DGND3) are shorted internally and recommended to be connected to a single ground plane on the board. Refer to the PCB Layout Guidelines section for details.

Layout Guidelines section for details.

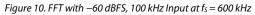

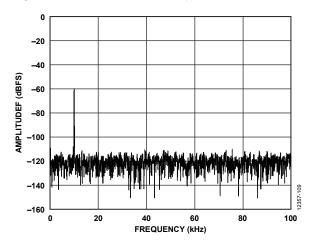

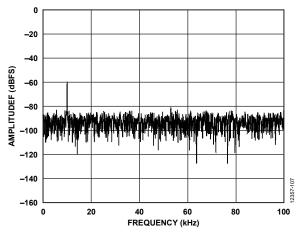

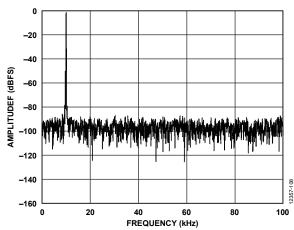

#### **TYPICAL PERFORMANCE CHARACTERISTICS** -20 -40 AMPLITUDEF (dBFS) -60 -80 -100 -120 -140 -160 30 60 90 120 150 0 FREQUENCY (kHz) Figure 8. FFT with -60 dBFS, 100 kHz Input at $f_s = 300$ kHz 0 -20 -40 AMPLITUDEF (dBFS) -60 -80 -100 -120 -140 2357--160 0 45 90 135 180 225 FREQUENCY (kHz) Figure 9. FFT with -60 dBFS, 100 kHz Input at $f_s = 450$ kHz 0 -20 -40 AMPLITUDEF (dBFS) -60 -80 -100 -120 -140 8 2357 -160 0 60 120 180 240 300 FREQUENCY (kHz)

Figure 13. FFT with -60 dBFS, 100 kHz Input at  $f_s = 1.8 \text{ MHz}$

### **Data Sheet**

ADAR7251

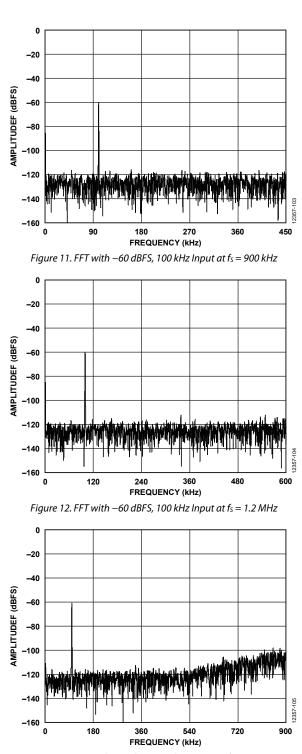

Figure 14. FFT with -60 dBFS, 100 kHz Input, DAQ16, at  $f_s = 758 \text{ kHz}$

Figure 15. FFT with -60 dBFS, 100 kHz Input, DAQ24, at  $f_s = 380 \text{ kHz}$

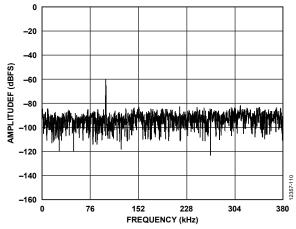

Figure 16. FFT with -60 dBFS, 10 kHz Input, DAQ32, at  $f_s = 200 \text{ kHz}$

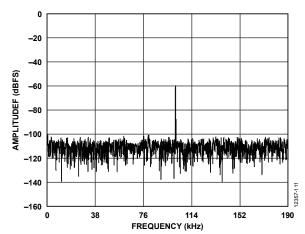

Figure 17. FFT with  $-60 \, dBFS$ , 10 kHz Input, DAQ16, at  $f_s = 200 \, kHz$

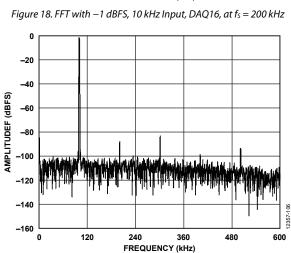

Figure 19. FFT with -1 dBFS, 100 kHz Input, at  $f_s = 1.2$  MHz

Figure 22. Frequency Response, ADC Digital Filter at  $f_s = 1.2$  MHz

Figure 24. ADC High-Pass Filter Frequency Response

### TERMINOLOGY

#### Integral Nonlinearity (INL)

INL is the maximum deviation from a straight line passing through the endpoints of the ADC transfer function. For the ADAR7251, the endpoints of the transfer function are zero scale, a point ½ LSB below the first code transition, and full scale, a point ½ LSB above the last code transition.

#### Differential Nonlinearity (DNL)

DNL is the difference between the measured and the ideal 1 LSB change between any two adjacent codes in the ADC.

#### **Offset Error**

Offset error is the deviation of the first code transition (00...000) to (00...001) from the ideal (such as ground + 0.5 LSB).

#### **Gain Error**

For the ADAR7251, gain error is the deviation of the last code transition (111...110) to (111...111) from the ideal (such as  $V_{REF}$  – 1.5 LSB) after the offset error is adjusted out.

#### Signal-to-Noise Ratio (SNR)

SNR is the ratio of the rms value of the actual input signal to the rms sum of all other spectral components below the Nyquist frequency, excluding harmonics and dc. The value for SNR is expressed in decibels (dB).

#### **Total Harmonic Distortion (THD)**

THD is the ratio of the rms sum of harmonics to the fundamental. For the ADAR7251, THD is defined as

THD (dB) = 20 log

$$\frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2}}{V_1}$$

where:

$V_1$  is the rms amplitude of the fundamental.

$V_2$ ,  $V_3$ ,  $V_4$ ,  $V_5$ , and  $V_6$  are the rms amplitudes of the second through the sixth harmonics.

#### Dynamic Range (DNR)

THD + N is measured in dB with an input level of -60 dBFS (-60 dB relative to the full-scale input). Then, 60 dB is added to the measured THD + N value and is expressed in decibels. For example, when measuring 36 dB THD + N with a -60 dBFS input, DNR is 60 + 36 = 96 dB.

#### Peak Harmonic or Spurious Noise

Peak harmonic or spurious noise is defined as the ratio of the rms value of the next largest component in the ADC output spectrum (up to  $f_s/2$  and excluding dc) to the rms value of the fundamental. Normally, the value of this specification is determined by the largest harmonic in the spectrum, but for ADCs where the harmonics are buried in the noise floor, it is a noise peak.

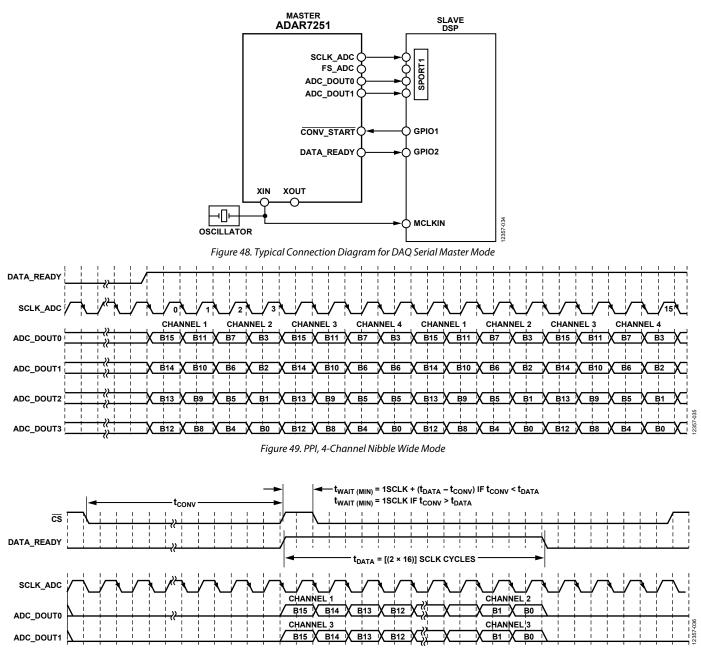

### THEORY OF OPERATION LOW SPEED RAMP RADAR ANALOG FRONT END

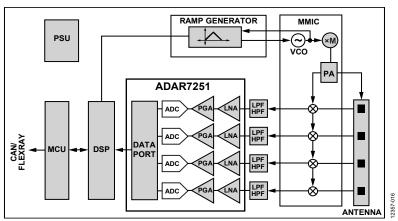

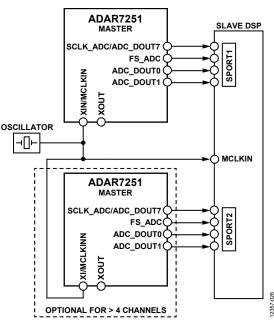

The most common application for the ADAR7251 is low speed ramp, frequency modulated, continuous wave, or frequency shift keying radar (LSR-FMCW or FSK-FMCW). Figure 28 shows a typical block diagram of an LSR/FSK radar system for a 4-channel application. The signal chain may require up to eight channels, each including an LNA, a PGA, and a  $\Sigma$ - $\Delta$  ADC. All input channels on the ADAR7251 sample the input signals simultaneously. The ADAR7251 also delivers secondary features required by an LSR radar system: a 2-channel, auxiliary 8-bit ADC and two GPIOs.

#### MAIN CHANNEL OVERVIEW

The ADAR7251 features an on-chip, fully differential LNA and PGA to feed the  $\Sigma$ - $\Delta$  input pins, as well as a digital filter block to perform the required filtering on the  $\Sigma$ - $\Delta$  modulator output. Using this  $\Sigma$ - $\Delta$  conversion technique with added digital filtering, the analog input converts to an equivalent digital word. The ADAR7251 uses an internal 1.5 V reference voltage.

#### $\Sigma\text{-}\Delta$ MODULATION AND DIGITAL FILTERING

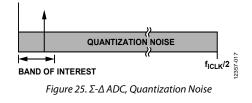

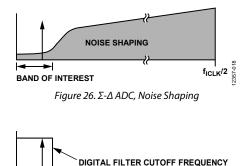

The input waveform applied to the modulator is sampled, and an equivalent digital word is output to the digital filter at a rate equal to the modulator clock. The modulator is clocked by  $48 \times f_S$  (57.6 MHz clock signal,  $f_{ICLK}$ , for  $f_S = 1.2$  MHz). By employing oversampling, the quantization noise spreads across a wide bandwidth (see Figure 25). This means that the noise energy contained in the bandwidth of interest is reduced. To further reduce the quantization noise, a third-order modulator is employed to shape the noise spectrum so that most of the noise energy is shifted out of the signal band (see Figure 26).

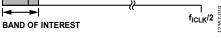

The digital filtering that follows the modulator removes the large out-of-band quantization noise (see Figure 27) while also reducing the data rate at the input of the filter to 1.2 MHz or less at the output of the filter, depending on the decimation rate used.

The total channel noise of the ADAR7251 depends on the bandwidth specification and the selected analog input range. The data rate at the output of the ADAR7251 can be reduced further to meet specific application requirements. The continuous time modulator removes the need for a high order antialias filter at the input to the ADAR7251. The continuous time  $\Sigma$ - $\Delta$  modulator used within the ADAR7251 has inherent antialiasing due to oversampling. The device uses 48× oversampling. This relaxes the requirement of filtering required at the input of the ADC. Typically, a single pole passive resistor capacitor (RC) filter is sufficient.

Figure 27.  $\Sigma$ - $\Delta$  ADC, Digital Filter Cutoff Frequency

Figure 28. Radar System Overview

#### DIFFERENTIAL INPUT CONFIGURATION

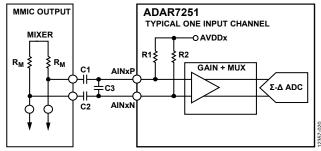

The ADAR7251 main ADC input channel consists of an LNA, a PGA, a continuous time  $\Sigma$ - $\Delta$  ADC, and internal bias resistors that set the common-mode voltage on the input of the LNA. The PGA includes an equalizer (EQ) function that gains up low amplitude, high frequency signals. Typically, in an automotive radar application, the analog inputs of the ADAR7251 connect directly to the mixer output (See Figure 29). If additional external filtering is required, the external C1, C2, and C3 capacitors can be used. These capacitors, together with the R1, R2, and the mixer output impedance, create an external filter that removes dc components and high frequency noise from the ADC inputs.

Figure 29. Typical Differential Input Channel Configuration

A monolithic microwave integrated circuit (MMIC) mixer output impedance,  $R_M$ , with Capacitor C3, forms a single-pole, low-pass filter that reduces high frequency spurs from the ADAR7251 inputs. Two capacitors, C1 and C2, with the ADAR7251 internal resistance of R1 and R2, produce a high-pass filter that removes dc components from the input signal.

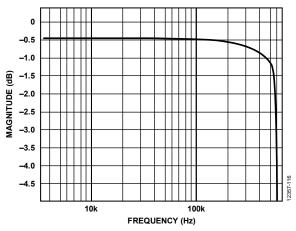

Each  $\Sigma$ - $\Delta$  ADC input is preceded by its own LNA and PGA gain stage. The variable gain settings ensure that the device is able to amplify signals from a variety of sources. The ADAR7251 offers the flexibility to choose the most appropriate gain setting to utilize the wide dynamic range of the device. The LNA stage gain can be set using Register 0x100 in 6 dB steps. The default gain is 6 dB. The PGA gain can be set independently using Register 0x101and has a default gain of 2.92 dB. The total LNA + PGA gain range is 36 dB. The gain settings, along with the ADAR7251 analog input range and channel noise specifications, are shown in the Specifications section (see Table 1). The default gain with LNA + PGA is 9 dB (2.8×), so that the full-scale differential input signal is 0.7 V rms. However, if a direct path is chosen and LNA + PGA is bypassed, the full-scale input signal to the ADC is 2 V rms differential.

#### High-Pass Filter (HPF)

The external input coupling capacitors form the passive first order, high-pass filter with the input impedance of the ADAR7251. This filter can also be used as a passive equalizer to boost the high frequency if desired. The corner frequency can be set to the desired frequency using the equation

$f_{3dB} = 1/(2 \times \pi \times R1 \times C1)$

where R1 = R2 (typical) is 2.86 k $\Omega$  and C2 = C1 (see Figure 29).

#### Low-Pass Filter (LPF)

The low-pass filter is formed by adding the capacitor across the differential input pins. The value of the source resistance driving the ADC dictates the corner frequency of the filter. Use the following equation to set the corner frequency to the desired frequency:

$f_{3dB} = 1/(4 \times \pi \times R_M \times C3)$

where  $R_M$  (typical) is the source resistance of the MMIC output.

#### Input Routing

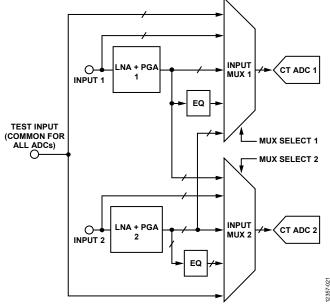

Figure 30 shows the typical 2-channel input block with multiplexers and input signal routing inside the ADAR7251. For simplicity, the connections in Figure 30 are shown as single-ended, although they are differential.

The input signal can be routed through LNA + PGA, LNA + PGA + EQ, or direct to the ADC. Register 0x102 is used to select the multiplexer at the input of the ADC. The inputs to the ADC can be swapped between adjacent channels, for example, Channel 1 can be sent to ADC2 and the Channel 2 input can be sent to ADC1. In addition, the auxiliary Input 1 and Input 2 can be sent directly to the ADC. In this case, AUXIN1 becomes a noninverting input, and AUXIN2 becomes an inverting input to form a differential pair. The default path is LNA + PGA + ADC.

Figure 30. Typical 2-Channel Input Block

#### **EQUALIZER (EQ)**

The output of LNA + PGA can be routed to an equalizer block. In LSR-FMCW radar systems, the distance between the radar and the object affects signal amplitude and frequency. Distant objects have a higher frequency and smaller amplitude. The EQ provides frequency dependent gain to boost these signals. This provides easier detection of distant objects in a system. Excellent noise performance relies on an ultralow noise LNA at the beginning of the signal chain and a high precision ADC architecture. Enable the EQ path in Register 0x102. The EQ is a first order, high-pass

### **Data Sheet**

## ADAR7251

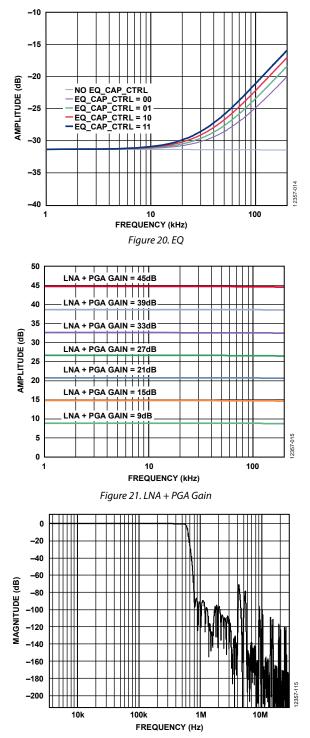

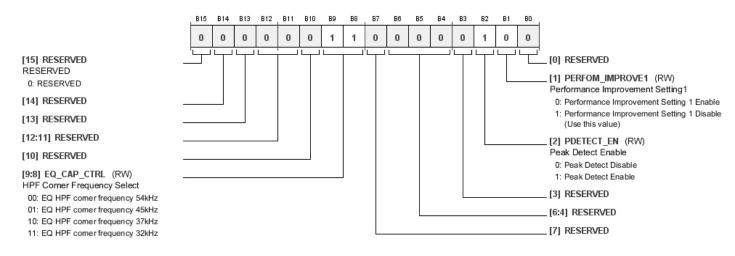

type. The cutoff frequency can be either 32 kHz (default), 37 kHz, 45 kHz, or 54 kHz. Select the EQ cutoff frequency in EQ\_CAP\_CTRL, Bits[1:0] in Register 0x301 (see Figure 20 in the Typical Performance Characteristics section).

#### USING LNA/PGA, EQ, OR THE INPUT CAPACITOR

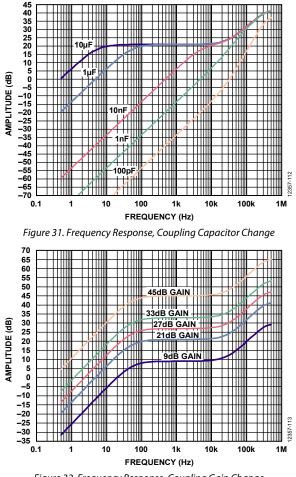

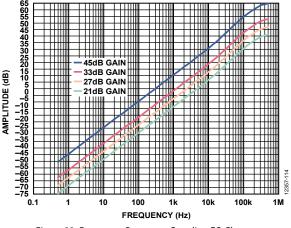

The input passive filter, along with LNA + PGA and EQ, can be used to achieve the desired frequency response in the system. See Figure 31, Figure 32, and Figure 33 for typical examples.

Figure 31 shows the frequency response plot by varying the input coupling capacitor value, with the LNA + PGA gain and EQ fixed.

Figure 32 shows the frequency response plot by varying the LNA + PGA gain, with the input coupling capacitor and EQ fixed. Figure 33 shows the frequency response plot by varying the EQ setting, with the input coupling capacitor and LNA + PGA gain fixed.

Figure 32. Frequency Response, Coupling Gain Change

#### Figure 33. Frequency Response, Coupling EQ Change

#### REFERENCE

The internal reference of the ADAR7251 is set to 1.5 V. This 1.5 V reference is available at the CM pin. Decouple the CM pin to the AGNDx pin using a 10  $\mu$ F MLCC in parallel with a 100 nF MLCC. The 1.5 V reference is current-limited and not designed to drive an external load. Employ an external buffer circuit if this reference is required for use with external circuits. The internal reference voltage can be overdriven externally if required.

#### **AUXILIARY ADC**

The ADAR7251 includes a 2-channel, auxiliary successive approximation register (SAR) ADC for low frequency housekeeping functions in the system. These functions include dc voltage monitoring and temperature monitoring. The auxiliary ADC uses AVDDx as the power supply; therefore, the input range is limited from 0 V to AVDDx. The ADC uses a time multiplexing technique to sample the two auxiliary inputs. The multiplexer in the front of the ADC selects the input for the conversion. The sample rate of the ADC is selectable between 112.5 kHz and 450 kHz. The default sample rate is 112.5 kHz. When 2-channel operation is selected, the set sample rate is the effective sample rate. If only one channel is selected, the effective sample rate is double the set value. The resolution of the ADC is eight bits, and the ADC output is straight binary. The ADC output is stored in the internal registers, which are read via the SPI port. Register 0x200 stores the current conversion value for Input 1 and Input 2. In addition, Register 0x201 stores the last sample value.

The ADC sample rate can be selected using Register 0x210, and Register 0x211 is used for selecting the input to the ADC. By default, the AUXINx pins are sampled. If the AUX\_ADC\_MODE bit (Bit 0 of Register 0x211) is set to 1, only one input is sampled at twice the sample rate. Because the auxiliary ADC is not continuous, care must be taken to ensure that the input signals are band limited and time multiplexed to prevent aliases.

The auxiliary ADC inputs are switched capacitor type; therefore, the input impedance is capacitive during the sampling phase. The typical source impedance must be less than 1 k $\Omega$  to ensure that the input settles before the sample value is held internally. The

### **Data Sheet**

## ADAR7251

source driving the ADC inputs must be able to drive at least 20 pF, excluding the parasitic capacitance on the board.

#### **POWER SUPPLY**

The ADAR7251 uses three supplies: 3.3 V for AVDDx, 1.8 V for DVDDx, and 3.3 V for IOVDDx. AVDDx and IOVDDx must be supplied to the device, but the supply to the DVDDx pins can be either generated by an internal LDO, or provided externally by turning off the LDO.

The AVDDx pins supply the analog core of the ADC, and the DVDDx pins supply the digital core of the ADC. The IOVDDx pins supply the digital input/output pins of the ADAR7251.

Decouple all power supplies to ground with a 0.1  $\mu$ F and a 10  $\mu$ F X7R MLCC for best ADC performance. The device provides the exposed pad underneath, which must be connected to the ground plane with thermal vias. All the ground pins must be connected to the single ground plane on the PCB with the shortest possible path close to the respective pins.

#### LDO

The internal LDO generates the DVDDx voltage (1.8 V) required for the digital core. The LDO takes the AVDDx (3.3 V) supply and regulates down to 1.8 V. External decoupling capacitors are required to ensure clean power to the digital core. If using the internal 1.8 V supply for the digital core, the REGOUT\_DIGITAL pin must be externally connected to the DVDDx pins. The 1 nF MLCC, in parallel with 0.1  $\mu$ F and 10  $\mu$ F capacitors, are recommended at the DVDDx pins to decouple the high frequency noise.

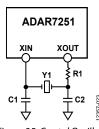

#### **CLOCK REQUIREMENTS**

To achieve the specified dynamic performance, use an external crystal at the XIN/MCLKIN and XOUT pins. Alternatively, provide the single-ended clock at the MCLKIN input via an MCU/DSP controller. The ADAR7251 features an internal PLL block that accepts the clock frequency in a range of 16 MHz to 54 MHz, via either the clock available in the system, or an external crystal. An external clock must be connected to the XIN/MCLKIN pin and must be within the 0 V to 3.3 V p-p.

#### **CRYSTAL OSCILLATOR**

The external quartz crystal can be connected across the XIN and XOUT pins. When using the crystal, use Register 0x292 to enable the crystal oscillator block. The output of the crystal oscillator is an input to the PLL. The typical supported frequency range is 16 MHz to 54 MHz. Select load capacitors C1 and C2 for the crystal based on the recommendation of the crystal manufacturer. Determine the value of R1 based on the crystal current rating.

Figure 35. Crystal Oscillator

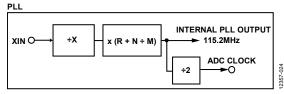

#### PLL

The PLL provides the stable clock for the internal blocks. It uses the clock input at the XIN/MCLKIN pin as a reference to generate the core clock. Set the PLL for either integer or fractional mode. The PLL multipliers and dividers (X, R, M, and N) are programmed using Register 0x000 to Register 0x003. The PLL can accept input frequencies in the range of 16 MHz to 54 MHz, either directly from an external source, or using the crystal connected at the XIN/MCLKIN and XOUT pins. The PLL output frequency is fixed at 115.2 MHz.

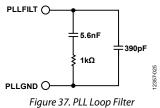

Figure 36. PLL Block Diagram

The PLL requires an external loop filter, which is fixed (see Figure 37). For temperature sensitive applications, the loop filter components must be appropriate. The PLL loop filter capacitors must be NPO type for best temperature performance.

Place the PLL loop filter close to the PLLFILT pin to prevent crosstalk from other sources on the board. In addition, take care to decouple the PLLVDD supply to the PLL. It is recommended that X7R MLCC or better dielectric MLCCs of 1 nF be added in parallel with 0.1  $\mu$ F and 10  $\mu$ F capacitors close to the PLLVDD pin. See the PCB Layout Guidelines section for details.

Table 10 describes the registers used to set the PLL.

#### Table 10. Registers Used to Set the PLL

| Register | Name     | Description                                                                                      |  |

|----------|----------|--------------------------------------------------------------------------------------------------|--|

| 0x000    | CLK_CTRL | Uses the PLL output for the internal<br>master clock, or bypasses the PLL                        |  |

| 0x001    | PLL_DEN  | Sets the 16-bit denominator of the fractional part (M)                                           |  |

| 0x002    | PLL_NUM  | Sets the 16-bit numerator of the fractional part (N)                                             |  |

| 0x003    | PLL_CTRL | Sets the PLL mode, PLL enable, 4-bit<br>integer multiplier (R), and 4-bit integer<br>divider (X) |  |

| 0x005    | PLL_LOCK | Checks the PLL lock status                                                                       |  |

The PLL can be used in either integer mode or fractional mode.

#### Integer Mode

Use integer mode when the input clock frequency is an integer multiple of the PLL output frequency, governed by the following equation:

$f_{PLL} = (R/X) \times f_{IN}$

where  $f_{PLL} = 115.2$  MHz.

For example, if  $f_{IN} = 19.2$  MHz, then

$(R/X) = f_{PLL} (PLL Required Output)/f_{IN} = 6$

Therefore, R and X are set as follows: R = 6, and X = 1 (default).

To route the clock through the PLL, first set Register 0x000 to 0x0001.

In integer mode, the values set for N and M are ignored; leave Register 0x001 and Register 0x002 at default.

Table 11 shows the name, function, and required settings for the bits in Register 0x003.

**Data Sheet**

| Bits    | Name               | Function                             | Required<br>Setting |

|---------|--------------------|--------------------------------------|---------------------|

| [15:11] | PLL_INTEGER_DIV    | Sets the R value                     | 00110               |

| [7:4]   | PLL_INPUT_PRESCALE | Sets the X value                     | 0001                |

| 1       | PLL_TYPE           | Sets the integer<br>mode for the PLL | 0                   |

| 0       | PLL_EN             | Enables the PLL                      | 1                   |

| Table 11. Re | equired Writes | for Register | 0x0003, Integer Mode |

|--------------|----------------|--------------|----------------------|

|--------------|----------------|--------------|----------------------|

Set Register 0x003 to 001100000000001, that is, 0x3011. To check the status of the PLL, read Register 0x0005.

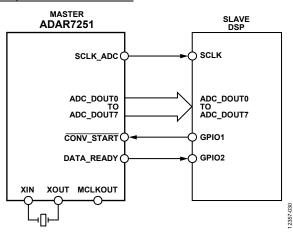

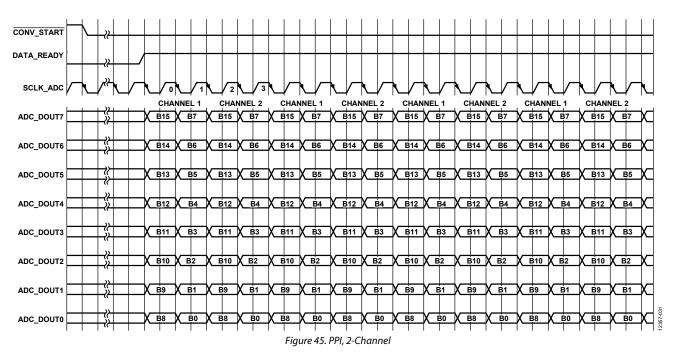

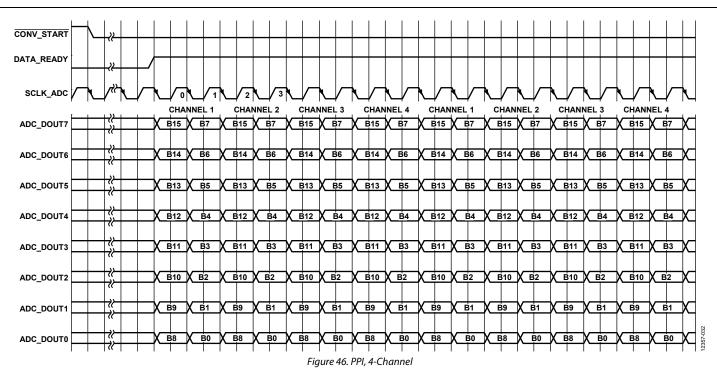

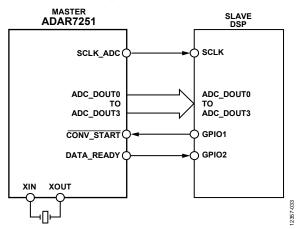

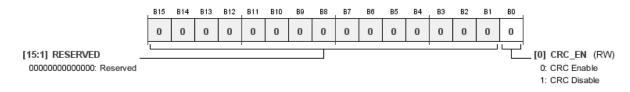

#### Fractional Mode