# Dual Channel, Configurable, Isolated Digital Input

**Data Sheet**

# ADE1202

## FEATURES

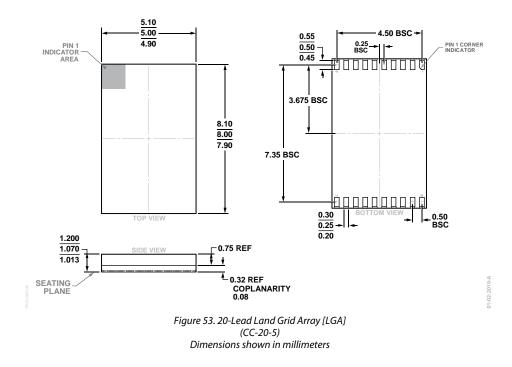

Dual channel, configurable, isolated digital input **Programmable trip threshold On-chip debounce filter On-chip data and power Isolation** Application circuit monitors wide voltage range 10 V dc to 300 V dc 8 V rms to 240 V rms ac (with 10 ms + pickup) **Negative dc protected** Programmable wetting current Pulse up to 50 mA Constant current up to 6.3 mA Safety and regulatory approvals **UL** recognition 3750 V rms for 1 minute per UL 1577 CSA Component Acceptance Notice #5A (pending) CSA 61010-1: 300 V rms VDE certificate of conformity (pending) DIN V VDE V 0884-11 (VDE V 0884-11):2017-1  $V_{IORM} = 565 V peak$ EMC robust solution supports relay protection system level requirements ADC samples available for system diagnostics Internal SAR ADC with PGA Single 3.3 V Supply Integrated isoPower, isolated dc-to-dc converter Interfaces SPI DOUTx output reflects state of digital input **IRQ** interrupt pin Operating temperature: -40°C to +125°C 20-lead, LGA package with 6.8 mm creepage

## APPLICATIONS

Energy transmission and distribution Multifunction relay protection Substation battery monitoring Bay or substation interlocking Merge unit Circuit breaker status indication Remote terminal unit Building automation

## **GENERAL DESCRIPTION**

The ADE1202<sup>1</sup> is a dual channel, configurable, isolated digital input monitoring solution for energy transmission and distribution applications. The ADE1202 is configured through the serial port interface (SPI) to perform an isolated measurement of the digital input that is also called binary input or contact input. The ADE1202 digital output signal on the DOUTx pins reflects the state of the input signal after user configurable signal conditioning. The SPI protocol supports addressing to allow up to eight devices sharing one 4-wire SPI port.

The ADE1202 application circuit accepts a wide range of input voltages from 10 V dc to 300 V, or 8 V rms to 240 V rms. The programmable wetting current and robust application circuit enable the device to meet stringent, system level electromagnetic capability (EMC) requirements.

The ADE1202 includes an *iso*Power<sup>®</sup> integrated, isolated dc-to-dc converter that eliminates the need for an external isolated power supply. The *i*Coupler<sup>®</sup> chip scale transformer technology is used to isolate the logic signals between the high voltage, isolated side and the low voltage, nonisolated side of the digital input monitor. This technology creates a small form factor design that includes data and power isolation.

An integrated successive approximation register (SAR) analog-to-digital converter (ADC) and a programmable gain amplifier (PGA) from  $1 \times$  to  $10 \times$  measure the analog inputs. The ADC waveforms are available through the SPI port to allow system level diagnostics.

Note that throughout this data sheet, multifunction pins, such as DOUT2/IRQ, are referred to either by the entire pin name or by a single function of the pin, for example, DOUT2, when only that function is relevant.

## **PRODUCT HIGHLIGHTS**

- 1. Dual channel, configurable, isolated digital input.

- 2. Single hardware design supports 24 V to 300 V systems.

- 3. Robust architecture.

- 4. Enables system level diagnostics.

<sup>1</sup> Protected by U.S. Patent Number 2017/0250043. Other patents pending.

Rev. 0

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

## TABLE OF CONTENTS

| Features 1                                                        |

|-------------------------------------------------------------------|

| Applications1                                                     |

| General Description                                               |

| Product Highlights 1                                              |

| Revision History 2                                                |

| Functional Block Diagram                                          |

| Specifications                                                    |

| Electrical Characteristics                                        |

| Timing Characteristics                                            |

| Insulation and Safety Related Specifications7                     |

| Package Characteristics7                                          |

| Regulatory Information 8                                          |

| DIN V VDE V 0884-11 (VDE V 0884-11) Insulation<br>Characteristics |

| Absolute Maximum Ratings                                          |

| Thermal Resistance                                                |

| ESD Caution10                                                     |

| Pin Configuration and Function Descriptions                       |

| Typical Performance Characteristics                               |

| Test Circuit                                                      |

| Theory of Operation                                               |

| Power Supply and Conditioning16                                   |

| Digital Inputs Signal Path17                                      |

| Invalid Mode                                                      |

| Programmable Load Current                                         |

| External FET Protection                                           |

| Gate Drive                                                        |

| Thermal Shutdown24                                                |

| Interrupt24                                                       |

| SPI Protocol Overview                                             |

| Protecting the Integrity of Configuration Registers               |

| Version                                                           |

| Insulation Wear Out27                                             |

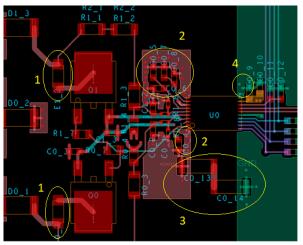

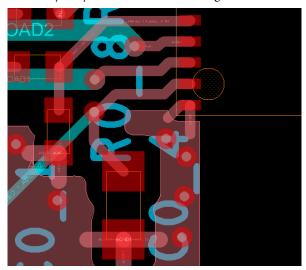

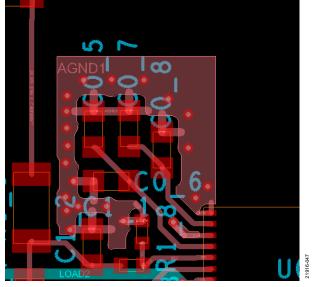

| Layout Guidelines                                                 |

| Ferrite Bead                                                      |

## Decoupling and Ground Plane Connection ...... 29 Binary Channel Threshold Level Register ...... 35 WARNAx Channel Threshold Level Register ...... 35 WARNCx Channel Threshold Level Register ...... 35 Programmable Load High Code Register ...... 40 Programmable Load High Current Period Register...... 40 Energy Meter Control Register ...... 40 Energy Meter Maximum Threshold Register...... 40 Energy Meter Channel 1 Accumulator Register ...... 41 Energy Meter Channel 2 Accumulator Register ...... 41 Programmable Load Enable Register ...... 41 Ordering Guide ...... 42

## **REVISION HISTORY**

12/2019—Revision 0: Initial Version

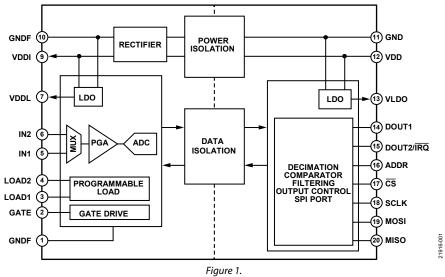

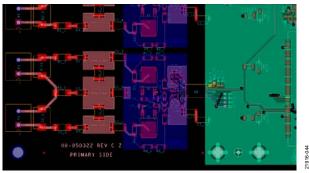

## FUNCTIONAL BLOCK DIAGRAM

## **SPECIFICATIONS**

## **ELECTRICAL CHARACTERISTICS**

$VDD = 3.3 V \pm 10\%$ , GND = 0 V, on-chip reference, and all specifications at  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted.

### Table 1. Static Characteristics

| Parameter                                          | Symbol            | Min  | Тур  | Мах      | Unit   | Test Conditions/Comments                              |

|----------------------------------------------------|-------------------|------|------|----------|--------|-------------------------------------------------------|

| ANALOG INPUTS (IN1, IN2)                           |                   |      |      |          |        |                                                       |

| Input Voltage Range                                | VIN               | 0    |      | 1.25/PGA | V      | PGA = 1, 2, 5, and 10                                 |

| Input Sampling Current                             | l <sub>INx</sub>  | -50  |      | +50      | nA     | PGA = 1, 2, 5, and 10                                 |

| GATE DRIVE (GATE)                                  |                   |      |      |          |        |                                                       |

| Output Voltage                                     | VGATENOM          |      | 6.9  |          | V      |                                                       |

| Output Current                                     | I <sub>GATE</sub> |      |      | 3.5      | μΑ     | $V_{GATENOM} = 6.6 V$                                 |

| PROGRAMABLE LOAD (LOADx)                           |                   |      |      |          |        |                                                       |

| Leakage Resistance                                 |                   |      | 58   |          | kΩ     | Programmable load is disabled                         |

| Constant Current                                   |                   |      |      |          |        |                                                       |

| Resolution                                         |                   |      | 6    |          | bits   |                                                       |

| Range                                              |                   | 0.11 |      | 6.3      | mA     | Typical programmable range                            |

| Total Unadjusted Error (TUE) <sup>1</sup>          |                   | -4.5 |      | +4.5     | %FSR   |                                                       |

| TUE at 25°C <sup>1</sup>                           |                   | -2   |      | +3.5     | %FSR   |                                                       |

| Integral Nonlinearity (INL)                        |                   | -1   |      | +1       | LSB    |                                                       |

| Differential Nonlinearity (DNL)                    |                   | -0.5 |      | +0.5     | LSB    |                                                       |

| Offset                                             |                   | 8    | 10   | 15       | μA     |                                                       |

| Gain Error                                         |                   | -7   | +0.1 | +5.7     | %FSR   | Measured at Code 63 compared to ideal value of 6.3 mA |

| Code 22 <sup>1</sup>                               |                   | 2    |      | 2.5      | mA     |                                                       |

| Code 63 <sup>1</sup>                               |                   | 5.8  |      | 6.7      | mA     |                                                       |

| Pulsed Current                                     |                   |      |      |          |        |                                                       |

| Resolution                                         |                   |      | 8    |          | bits   |                                                       |

| Range                                              |                   | 0.21 |      | 51       | mA     | Typical programmable range                            |

| TUE <sup>1</sup>                                   |                   | -4.5 |      | +4.5     | %FSR   |                                                       |

| TUE at 25°C <sup>1</sup>                           |                   | -2   |      | +3.5     | %FSR   |                                                       |

| INL                                                |                   | -0.8 |      | +2.1     | LSB    |                                                       |

| DNL                                                |                   | -1.2 |      | +1.4     | LSB    |                                                       |

| Offset                                             |                   | 9    | 10   | 14.5     | μA     |                                                       |

| Gain Error                                         |                   | -7   | +0.2 | +6       | %FSR   | Measured at Code 255 compared to ideal value of 51 mA |

| Code 255 <sup>1</sup>                              |                   | 47   |      | 54       | mA     |                                                       |

| THERMAL SHUTDOWN                                   |                   |      |      |          |        | See Thermal Shutdown section                          |

| Threshold <sup>1</sup>                             | T <sub>SD</sub>   |      | 170  |          | °C     | Junction temperature                                  |

| Hysteresis <sup>1</sup>                            |                   |      | 25   |          | °C     |                                                       |

| ISOLATION COMMON-MODE TRANSIENT IMMUNITY<br>(CMTI) |                   |      |      |          |        | Common-mode voltage $( V_{CM} ) = 2 \text{ kV}$       |

| Static                                             |                   |      | 50   |          | kV/ μS |                                                       |

| ADDR PIN INPUT                                     |                   |      |      |          |        |                                                       |

| Input Current                                      | I <sub>INH</sub>  |      |      | 1        | μA     |                                                       |

| Input Current                                      | I <sub>INL</sub>  |      |      | 1        | μA     |                                                       |

| LOGIC INPUTS (MOSI, SCLK, CS)                      |                   |      |      |          | ·      |                                                       |

| Input High Voltage                                 | VINH              | 2.4  |      |          | v      |                                                       |

| Input Low Voltage                                  | VINL              |      |      | 0.8      | v      |                                                       |

| Input High Current                                 | INH               |      |      | 1        | μA     |                                                       |

| Input Low Current                                  |                   |      |      | 10       | μΑ     |                                                       |

| Input Capacitance <sup>1</sup>                     |                   |      |      | 10       | рF     |                                                       |

| Parameter                              | Symbol          | Min  | Тур | Max  | Unit | <b>Test Conditions/Comments</b>                        |

|----------------------------------------|-----------------|------|-----|------|------|--------------------------------------------------------|

| LOGIC OUTPUTS (MISO, DOUT1, DOUT2/IRQ) |                 |      |     |      |      | The DOUT2/IRQ pin is open-drain when configured as IRQ |

| Output High Voltage                    | V <sub>OH</sub> | 2.4  |     |      | V    | Source current (I <sub>SOURCE</sub> ) = 3.5 mA         |

| Output Low Voltage                     | Vol             |      |     | 0.4  | V    | Sink current ( $I_{SINK}$ ) = 3.5 mA                   |

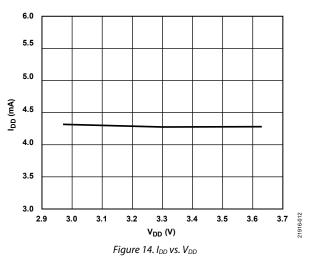

| POWER SUPPLY                           |                 |      |     |      |      |                                                        |

| Operating Voltage Range                | V <sub>DD</sub> | 2.97 |     | 3.63 | V    |                                                        |

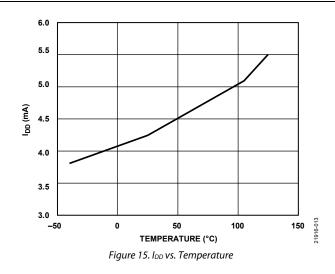

| Supply Current                         | IDD             | 3.3  | 4.3 | 6.7  | mA   |                                                        |

$^{\scriptscriptstyle 1}$  Guaranteed by design and characterization.

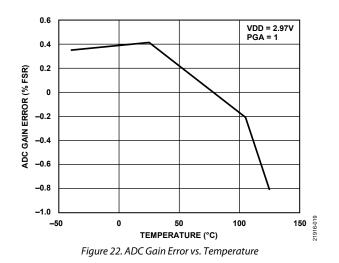

## Table 2. SAR, ADC, and PGA Characteristics

| Parameter                   | Min  | Тур   | Max  | Unit | <b>Test Conditions/Comments</b> |

|-----------------------------|------|-------|------|------|---------------------------------|

| SPEED AND PERFORMANCE       |      |       |      |      |                                 |

| ADC Resolution              |      | 8     |      | bits | No missing codes                |

| Throughput <sup>1</sup>     |      | 100   |      | kSPS |                                 |

| SIGNAL-TO-NOISE RATIO (SNR) |      |       |      |      |                                 |

| PGA = 1, 2, 5               |      | 48    |      | dB   |                                 |

| PGA = 10                    |      | 46    |      | dB   |                                 |

| DC ACCURACY                 |      |       |      |      |                                 |

| INL                         |      | ±0.25 |      | LSB  |                                 |

| DNL                         |      | ±0.25 |      | LSB  |                                 |

| Gain Error                  | -2.5 |       | +2.5 | %FSR | PGA = 1, 2, 5, 10               |

| Offset Error                | -3   |       | +3   | LSB  | PGA = 1, 2, 5, 10               |

$^{\rm 1}$  The ADC is multiplexed between sampling IN1 and IN2, resulting in 50 kSPS per channel.

## TIMING CHARACTERISTICS

### Table 3. Input Signal Timing Characteristics

| Parameter                                                         | Min | Тур | Max | Unit | Test Conditions/Comments                                        |

|-------------------------------------------------------------------|-----|-----|-----|------|-----------------------------------------------------------------|

| Input Signal Filter Resolution <sup>1</sup>                       |     | 20  |     | μs   |                                                                 |

| Time Delay from Step Change on INx Input to DOUTx<br>Change State | 60  | 86  | 110 | μs   | BIN_FILTER_VAL = 3, with step on INx from 0 V to 0.8 V          |

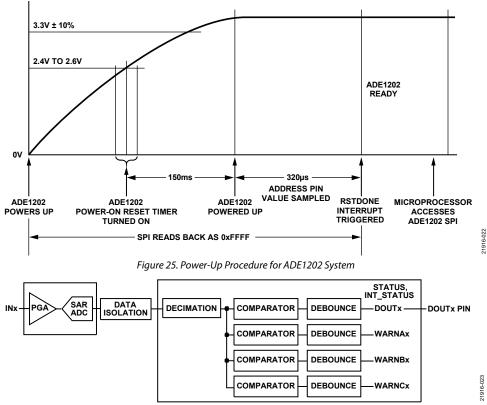

| Power-Up Time                                                     |     | 110 |     | ms   | With initial VDDI = 0 V, using recommended circuit in Figure 23 |

| ADDR Pin Load Time <sup>1</sup>                                   |     | 320 |     | μs   | After power-on (see Figure 25)                                  |

<sup>1</sup> Guaranteed by design.

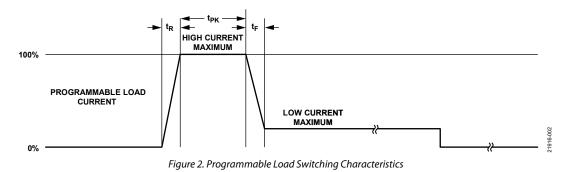

### Table 4. Programmable Load Switching Characteristics

| Parameter              | Symbol         | Min | Тур | Max   | Unit | Test Conditions/Comments             |

|------------------------|----------------|-----|-----|-------|------|--------------------------------------|

| Turn On Rise Time      | t <sub>R</sub> | 2   |     | 9     | μs   | In high idle mode with a 50 mA pulse |

| Pulsed Current On Time | tрк            | 4   | 4.1 | 4.3   | ms   | HIGH_TIME = 400                      |

| Turn Off Fall Time     | t <sub>F</sub> |     |     | 0.025 | μs   |                                      |

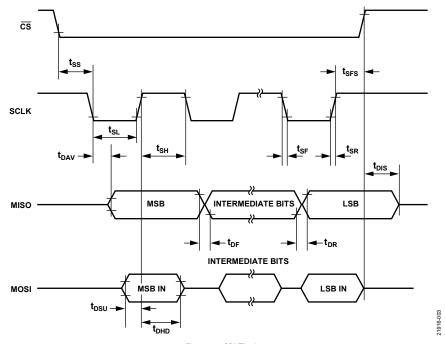

### **Table 5. SPI Timing Parameters**

| Parameter                              | Symbol            | Min     | Тур | Мах | Unit |

|----------------------------------------|-------------------|---------|-----|-----|------|

| CS to SCLK Negative Edge               | t <sub>ss</sub>   | 10      |     |     | ns   |

| SCLK Frequency <sup>1</sup>            | f <sub>SCLK</sub> | 0.00025 |     | 10  | MHz  |

| SCLK Low Pulse Width                   | tsL               | 40      |     |     | ns   |

| SCLK High Pulse Width                  | t <sub>sH</sub>   | 40      |     |     | ns   |

| Data Output Valid After SCLK Edge      | t <sub>DAV</sub>  |         |     | 40  | ns   |

| Data Input Setup Time Before SCLK Edge | t <sub>DSU</sub>  | 10      |     |     | ns   |

| Data Input Hold Time After SCLK Edge   | t <sub>DHD</sub>  | 10      |     |     | ns   |

| Data Output Fall Time                  | t <sub>DF</sub>   |         |     | 10  | ns   |

| Data Output Rise Time                  | t <sub>DR</sub>   |         |     | 10  | ns   |

| SCLK Rise Time                         | t <sub>sr</sub>   |         |     | 10  | ns   |

| SCLK Fall Time                         | t <sub>sF</sub>   |         |     | 10  | ns   |

| MISO Disable After CS Rising Edge      | t <sub>DIS</sub>  |         |     | 100 | ns   |

| CS High After SCLK Edge                | t <sub>SFS</sub>  | 0       |     |     | ns   |

<sup>1</sup> Guaranteed by design and characterization.

#### Figure 3. SPI Timing

## INSULATION AND SAFETY RELATED SPECIFICATIONS

For additional information, see www.analog.com/icouplersafety.

| Parameter                                                         | Symbol  | Value | Unit   | Test Conditions/Comments                                                                                                   |

|-------------------------------------------------------------------|---------|-------|--------|----------------------------------------------------------------------------------------------------------------------------|

| Rated Dielectric Insulation Voltage                               | -       | 3750  | V rms  | 1-minute duration                                                                                                          |

| Minimum External Air Gap<br>(Clearance)                           | L (I01) | 6.8   | mm min | Measured from input terminals to output terminals, shortest distance through air                                           |

| Minimum External Tracking<br>(Creepage)                           | L (I02) | 6.8   | mm min | Measured from input terminals to output terminals, shortest distance path along body                                       |

| Minimum Clearance in the Plane of the Printed Circuit Board (PCB) | L (PCB) | 6.8   | mm min | Measured from input terminals to output terminals, shortest distance through air, line of sight, in the PCB mounting plane |

| Minimum Internal Gap (Internal<br>Clearance)                      |         | 21    | µm min | Minimum distance through insulation                                                                                        |

| Tracking Resistance (Comparative<br>Tracking Index)               | СТІ     | >400  | V      | DIN IEC 112/VDE 0303 Part 1                                                                                                |

| Material Group                                                    |         | 11    |        | Material Group (DIN VDE 0110, 1/89, Table 1)                                                                               |

## **PACKAGE CHARACTERISTICS**

| Table 7.                                   |        |     |                  |     |      |                          |  |

|--------------------------------------------|--------|-----|------------------|-----|------|--------------------------|--|

| Parameter                                  | Symbol | Min | Тур              | Max | Unit | Test Conditions/Comments |  |

| Resistance (Input to Output) <sup>1</sup>  | RI-O   |     | 10 <sup>12</sup> |     | Ω    |                          |  |

| Capacitance (Input to Output) <sup>1</sup> | CI-O   |     | 1.25             |     | pF   | f = 1 MHz                |  |

<sup>1</sup> The device is considered a 2-terminal device. Pin 1 through Pin 10 are shorted together, and Pin 11 through Pin 20 are shorted together.

## **REGULATORY INFORMATION**

The ADE1202 is pending approval by the organizations listed in Table 8.

### Table 8. Approvals

| UL                                                                     | CSA (Pending)                                                          | VDE (Pending)                                                                                                             |

|------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Recognized Under UL 1577 Component<br>Recognition Program <sup>1</sup> | Approved under CSA Component Acceptance<br>Notice 5A                   | Certified according to DIN V VDE V 0884-11<br>(VDE V 0884-11):2017-1 <sup>2</sup>                                         |

| Single Protection, 3750 V rms Isolation<br>Voltage                     | CSA 60950-1-07+A1+A2 and IEC 60950-1, second edition, +A1+A2:          | Reinforced insulation, V <sub>IORM</sub> = 565 V peak, V <sub>IOTM</sub> =<br>8 kV peak, V <sub>IMPULSE</sub> = 8 kV peak |

|                                                                        | Basic insulation at 640 V rms (904 V peak)                             |                                                                                                                           |

|                                                                        | Reinforced insulation at 320 V rms (452 V peak)                        |                                                                                                                           |

|                                                                        | IEC 60601-1 Edition 3.1: 1 means of patient protection (MOPP),         |                                                                                                                           |

|                                                                        | 250 V rms (354 V peak)                                                 |                                                                                                                           |

|                                                                        | CSA 61010-1-12 and IEC 61010-1 third edition                           |                                                                                                                           |

|                                                                        | Basic insulation at 300 V rms Mains, 640 V rms<br>(904 V peak)         |                                                                                                                           |

|                                                                        | Reinforced insulation at 300 V rms Mains, 320 V secondary (452 V peak) |                                                                                                                           |

| File E214100                                                           | File 205078                                                            | File 2471900-4880-0001                                                                                                    |

<sup>1</sup> In accordance with UL 1577, each product is proof tested by applying an insulation test voltage of ≥4500 V rms for 1 sec.

<sup>2</sup> In accordance with DIN V VDE V 0884-11, each product is proof tested by applying an insulation test voltage of ≥1059 V peak for 1 sec.

## DIN V VDE V 0884-11 (VDE V 0884-11) INSULATION CHARACTERISTICS

This isolator is suitable for electrical isolation only within the safety limit data. Maintenance of the safety data must be ensured by means of protective circuits.

An asterisk (\*) on a package denotes VDE 0884 approval for a 707 V peak working voltage.

| Table 9.                                                    |                  |                                                                                                                                  |                |                  |

|-------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|

| Description                                                 | Symbol           | Test Conditions/Comments                                                                                                         | Characteristic | Unit             |

| Installation Classification per IEC 60664-1                 |                  |                                                                                                                                  |                |                  |

| For Rated Mains Voltage ≤ 150 V rms                         |                  |                                                                                                                                  | I to IV        |                  |

| For Rated Mains Voltage ≤ 300 V rms                         |                  |                                                                                                                                  | I to IV        |                  |

| For Rated Mains Voltage $\leq$ 600 V rms                    |                  |                                                                                                                                  | l to III       |                  |

| Climatic Classification                                     |                  |                                                                                                                                  | 40/125/21      |                  |

| Pollution Degree per DIN VDE 0110, Table 1                  |                  |                                                                                                                                  | 2              |                  |

| Maximum Working Insulation Voltage                          | VIORM            |                                                                                                                                  | 565            | V peak           |

| Input to Output Test Voltage, Method b1                     | $V_{pd(m)}$      | $V_{IORM} \times 1.875 = V_{pd(m)}$ , 100% production test, $t_{ini} = t_m = 1$ sec, partial discharge < 5 pC                    | 1060           | V peak           |

| Input to Output Test Voltage, Method a                      |                  |                                                                                                                                  |                |                  |

| After Environmental Tests Subgroup 1                        | $V_{pd(m)}$      | $V_{\text{IORM}} \times 1.5 = V_{\text{pd(m)}}, t_{\text{ini}} = 60 \text{ sec}, t_m = 10 \text{ sec}, partial discharge < 5 pC$ | 848            | V peak           |

| After Input and/or Safety Test Subgroup 2<br>and Subgroup 3 | $V_{pd(m)}$      | $V_{\text{IORM}} \times 1.2 = V_{\text{pd(m)}}, t_{\text{ini}} = 60$ sec, $t_m = 10$ sec, partial discharge $< 5 \text{ pC}$     | 678            | V peak           |

| Highest Allowable Overvoltage                               | VIOTM            |                                                                                                                                  | 8000           | V peak           |

| Impulse                                                     | VIMPULSE         | 1.2 μs rise time, 50 μs, 50% fall time in air, to the preferred sequence                                                         | 8000           | V peak           |

| Withstand Isolation Voltage                                 | V <sub>ISO</sub> | 1 minute withstand rating                                                                                                        | 3750           | V <sub>RMS</sub> |

| Surge Isolation Voltage Reinforced                          | VIOSM            | V peak = $1.3 \times V_{IMPULSE}$ , 1.2 µs rise time, 50 µs, 50% fall time                                                       | 10400          | V peak           |

| Safety Limiting Values                                      |                  | Maximum value allowed in the event of a failure                                                                                  |                |                  |

|                                                             |                  | (see Figure 4)                                                                                                                   |                |                  |

| Maximum Ambient Temperature                                 | Ts               |                                                                                                                                  | 125            | °C               |

| Total Power Dissipation <sup>1</sup> at 25°C                | I <sub>S1</sub>  |                                                                                                                                  | 0.75           | W                |

| Insulation Resistance at Ts                                 | Rs               | $V_{IO} = 500 V$                                                                                                                 | >109           | Ω                |

<sup>1</sup> This is the maximum power dissipation to guarantee insulation integrity.

Figure 4. Thermal Derating Curve, Dependence of Safety Limiting Values with Ambient Temperature, per DIN V VDE V 0884-11

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 10.

| Parameter                                                  | Rating                               |

|------------------------------------------------------------|--------------------------------------|

| VDD to GND                                                 | –0.3 V to +3.7 V                     |

| IN1, IN2 to GNDF                                           | –0.2 V to +2 V                       |

| LOAD1, LOAD2 to GNDF                                       | –0.3 V to +7.7 V                     |

| GATE to GNDF                                               | –0.3 V to +7.7 V                     |

| Digital Input Voltage to GND                               | -0.3 V to V <sub>DD</sub> + 0.3<br>V |

| Digital Output Voltage to GND                              | -0.3 V to V <sub>DD</sub> + 0.3 V    |

| Operating Temperature                                      |                                      |

| Industrial Range                                           | -40°C to +125°C                      |

| Storage Temperature Range                                  | –65°C to +150°C                      |

| Lead Temperature (Soldering, 10 sec) <sup>1</sup>          | 300°C                                |

| Electrostatic Discharge (ESD)                              |                                      |

| Human Body Model <sup>2</sup>                              | ±5 kV                                |

| Field Induced Charged Device Model<br>(FICDM) <sup>3</sup> | ±1.5 kV                              |

<sup>1</sup>Analog Devices, Inc., recommends that reflow profiles used in soldering RoHS compliant devices conform to J-STD-020D.1 from JEDEC. Refer to JEDEC for the latest revision of this standard.

<sup>2</sup> Applicable standard: ANSI/ESDA/JEDEC JS-001-2014.

<sup>3</sup> Applicable standard: JESD22-C101F (ESD FICDM standard of JEDEC).

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

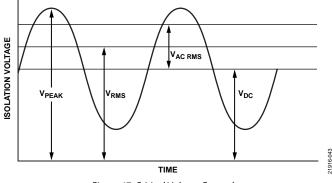

#### Parameter Max Unit **Reference Standard<sup>2</sup>** AC Voltage **Bipolar Waveform Basic Insulation** 636 V peak Lifetime limited by insulation lifetime per VDE-0884-11 **Reinforced Insulation** 537 V peak Lifetime limited by package creepage per IEC 60664-1 Unipolar Waveform **Basic Insulation** 1242 V peak Lifetime limited by package creepage per IEC 60664-1 **Reinforced Insulation** 621 V peak Lifetime limited by package creepage per IEC 60664-1 DC Voltage 760 **Basic Insulation** V peak Lifetime limited by package creepage per IEC 60664-1 **Reinforced Insulation** 380 V peak Lifetime limited by package creepage per IEC 60664-1

<sup>1</sup> The maximum continuous working voltage refers to the continuous voltage magnitude imposed across the isolation barrier. See the Insulation Wear Out section for more details. <sup>2</sup> Insulation lifetime for the specified test condition is greater than 50 years.

### THERMAL RESISTANCE

Thermal performance is directly linked to PCB design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the junction to ambient thermal resistance.  $\theta_{JC}$  is the junction to case thermal resistance.  $\Psi_{JT}$  is the junction to top characterization parameter.

#### Table 11. Thermal Resistance<sup>1</sup>

| Tuble 11. Thermai Resistance |     |     |    |      |

|------------------------------|-----|-----|----|------|

| Package Type                 | Αιθ | θıc | Ψл | Unit |

| CC-20-5                      | 168 | 76  | 12 | °C/W |

<sup>1</sup> Based on simulated data using a JEDEC 2s2p thermal test board in a JEDEC natural convection environment. See JEDEC specification JESD-51 for details.

#### ESD CAUTION

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

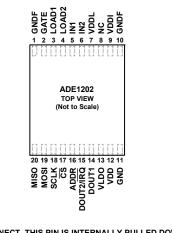

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

NOTES 1. NC = NO CONNECT. THIS PIN IS INTERNALLY PULLED DOWN TO GNDF. IT IS RECOMMENDED TO TIE THIS PIN TO GNDF EXTERNALLY.

Figure 5. Pin Configuration

### **Table 13. Pin Function Descriptions**

| Pin No. | Mnemonic        | Description                                                                                                                                                                                                                                                                                                                                   |

|---------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | GNDF            | The GNDF pin located at Pin 1 is used to provide a return path for current from the internal programmable load.<br>Both Pin 1 and Pin 10 must be connected to ground externally. See the Layout Guidelines section for<br>recommendations on how to connect this pin.                                                                         |

| 2       | GATE            | Use this pin to drive the gate pins of two enhancement mode field effect transistors (FETs), one for each channel of the ADE1202.                                                                                                                                                                                                             |

| 3, 4    | LOAD1,<br>LOAD2 | Programmable Loads. Use these pins to command a preset current required for loading the relay contacts.                                                                                                                                                                                                                                       |

| 5, 6    | IN1, IN2        | Digital Input Pins. The scaled input signals are applied at these pins.                                                                                                                                                                                                                                                                       |

| 7       | VDDL            | 1.8 V Output of the Analog Low Dropout (LDO) Regulator. Do not connect external load circuitry to this pin.<br>Decouple this pin to GNDF with the recommended capacitors shown in Table 16, and see the Layout Guidelines<br>section for recommendations on how to connect this pin.                                                          |

| 8       | NC              | No Connect. This pin is internally pulled down to GNDF. It is recommended to tie this pin to GNDF externally.                                                                                                                                                                                                                                 |

| 9       | VDDI            | Isolated Secondary Side Power Supply Output Pin. This pin provides access to the 2.0 V, on-chip isolated power supply. Decouple this pin to GNDF with the recommended capacitors shown in Table 16, and see the Layout Guidelines section for recommendations on how to connect this pin. Do not connect external load circuitry to this pin. |

| 10      | GNDF            | The GNDF pin located at Pin 10 is used as a reference for the internal, isolated power supply and the LDO regulator.<br>Both Pin 1 and Pin 10 must be connected to ground externally. See the Layout Guidelines section for<br>recommendations on how to connect this pin.                                                                    |

| 11      | GND             | GND Pin. This pin is the system controller side ground pin.                                                                                                                                                                                                                                                                                   |

| 12      | VDD             | Primary Supply Voltage. This pin provides the supply voltage for the ADE1202. Maintain the supply voltage at $3.3  V \pm 10\%$ for specified operation. Decouple this pin to the GND pin with the recommended capacitors shown in Table 16, and see the Layout Guidelines section for recommendations on how to connect this pin.             |

| 13      | VLDO            | 1.8 V Output of the LDO Regulator. Decouple this pin to the GND pin with the recommended capacitors shown in Table 16, and see the Layout Guidelines section for recommendations on how to connect this pin. Do not connect external load circuitry to this pin.                                                                              |

| 14      | DOUT1           | Digital Data Output Pin. This pin operates in a push/pull mode. This pin transitions to logic high, V <sub>INH</sub> , or logic low, V <sub>INL</sub> , replicating the digital input signal at the IN1 pin.                                                                                                                                  |

| 15      | DOUT2/IRQ       | Digital Data Output Pin. When configured as DOUT2, this pin operates in a push/pull mode and transitions to $V_{INH}$ or $V_{INL}$ replicating the digital input signal at the IN2 pin. When configured as an interrupt, IRQ, the pin is open-drain and a 10 k $\Omega$ pull-up resistor to the VDD voltage is recommended.                   |

| 16      | ADDR            | Address Mode Pin. This pin is used for multichip addressing. If multichip addressing is not used, connect this pin to ground. The address divider requires 1% resistors, as described in the SPI ADE1202 Addressing section.                                                                                                                  |

| 17      | CS              | Chip Select for SPI Port.                                                                                                                                                                                                                                                                                                                     |

| 18      | SCLK            | Serial Clock Input for SPI Port. All serial data transfers are synchronized to this clock.                                                                                                                                                                                                                                                    |

| 19      | MOSI            | Data Input for SPI Port.                                                                                                                                                                                                                                                                                                                      |

| 20      | MISO            | Data Output for SPI Port.                                                                                                                                                                                                                                                                                                                     |

## **TYPICAL PERFORMANCE CHARACTERISTICS**

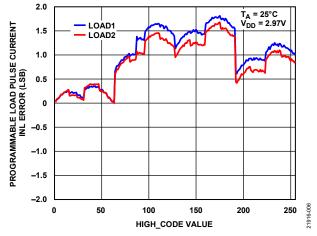

Figure 6. Programmable Load Pulse Current INL Error vs. HIGH\_CODE Value

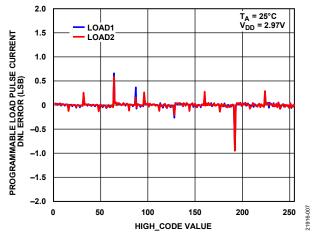

Figure 7. Programmable Load Pulse Current DNL Error vs. HIGH\_CODE Value

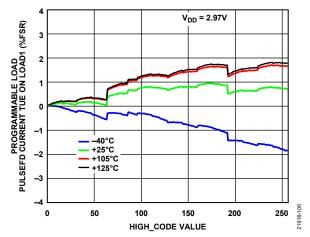

Figure 8. Programmable Load Pulsed Current TUE on LOAD1 vs. HIGH\_CODE Value over Temperature

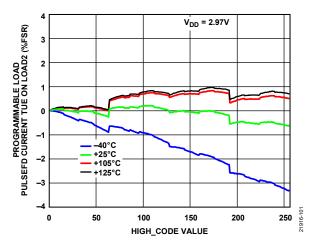

Figure 9. Programmable Load Pulse Current TUE on LOAD2 vs. HIGH\_CODE Value over Temperature

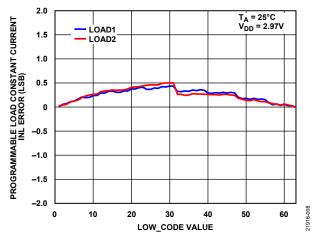

Figure 10. Programmable Load Constant Current INL Error vs. LOW\_CODE Value

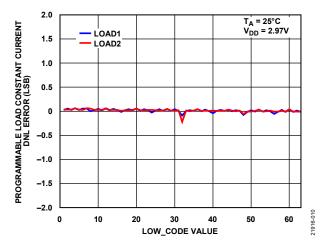

Figure 11. Programmable Load Constant Current DNL Error vs. LOW\_CODE Value

## **Data Sheet**

4 V<sub>DD</sub> = 2.97V PROGRAMMABLE LOAD CONSTANT CURRENT TUE ON LOAD1 (%FSR) 3 2 1 0 -1 -40<sup>°</sup>C +25°C -2 +105°C +125°C -3 21916-102 0 10 20 30 40 50 60 LOW\_CODE VALUE

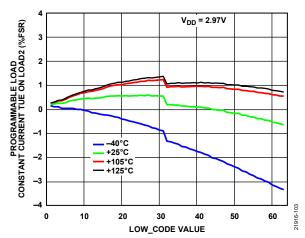

Figure 12. Programmable Load Constant Current TUE on LOAD1 vs. LOW\_CODE Value over Temperature

Figure 13. Programmable Load Constant Current TUE on LOAD2 vs. LOW\_CODE Value over Temperature

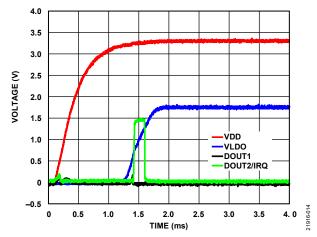

Figure 16. Power-Up of Nonisolated Side (VDD, VLDO, DOUT1, and DOUT2/IRQ Pins)

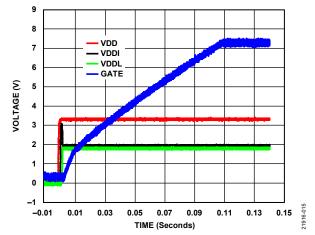

Figure 17. Power-Up of Isolated Side (VDDI, VDDL, and GATE Pins) when VDD Pin is Supplied on Nonisolated Side

## ADE1202

## ADE1202

Figure 19. Typical Input, Gate, LOAD1, and LOAD2 Signals when Both External FETs Conducting (IN1 = IN2, Gate, LOAD1, LOAD2)

Figure 20. Typical Input, Gate, LOAD1, and LOAD2 Signals when the External FET on Channel 1-Conducting and Channel 2 Input Floating (IN1, Gate, LOAD1, LOAD2)

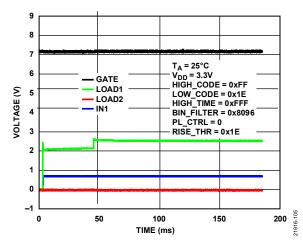

Figure 21. Decoded SPI Address (CHIP\_ADDR) Value vs. ADDR Pin Voltage

## **TEST CIRCUIT**

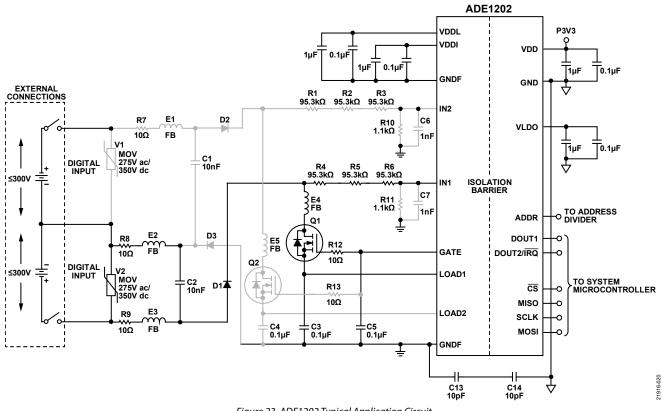

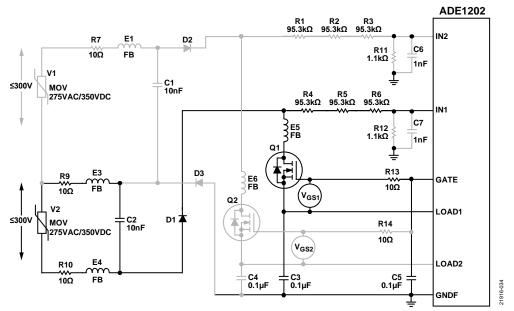

The typical ADE1202 application circuit is shown in Figure 23.

Figure 23. ADE1202 Typical Application Circuit

## THEORY OF OPERATION

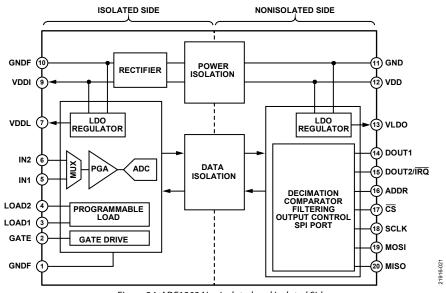

The ADE1202 is a dual channel, configurable, isolated digital input monitor designed for energy transmission and distribution applications. The ADE1202 contains an isolated and a nonisolated side (see Figure 24).

Only a single 3.3 V supply is required to power the ADE1202. The isolated side (the VDDI pin and GNDF pin) is supplied from an internal, isolated dc-to-dc converter, which is generated from the VDD pin and GND pin on the nonisolated side. The *iso*Power technology eliminates the need for an external, isolated power supply.

The isolated side of the device contains a PGA, an SAR ADC, a programmable load, and a gate drive.

Digital isolators allow the isolated side to communicate with the nonisolated side.

The nonisolated side signal conditions the ADC data coming from the isolated side and creates the DOUT1 and DOUT2 digital outputs. The digital outputs reflect the status of the IN1 and IN2 digital inputs from the isolated side.

The SPI is used to initialize the ADE1202 and can be used to monitor status and ADC waveforms during operation.

## POWER SUPPLY AND CONDITIONING VDD, VLDO, and GND Pins

Connect the VDD pin to a 3.3 V logic level supply. Decouple these pins to the GND pin with the recommended capacitors shown in Table 16, and see the Layout Guidelines section for recommendations on how to make these connections.

### **GNDF** Pins

The GNDF pins are used to reference the high voltage side circuits after the isolation barrier. The GNDF pin located at Pin 1 is used to

provide a return path for current from the internal programmable load. The GNDF pin located at Pin 10 is used as a reference for internal, isolated power supply and the LDO regulator. Both Pin 1 and Pin 10 are required to be connected to the high voltage ground plane on the PCB. The detailed grounding method is described in the Layout Guidelines section.

## **VDDI and VDDL Supplies**

The VDDI pin is the 2.0 V, isolated side power supply output, and the VDDL pin is the 1.8 V output of the analog LDO regulator. Decouple these pins to GNDF (Pin 10) with the recommended capacitors shown in Table 16, and see the Layout Guidelines section for recommendations.

Note that no external component can be supplied from the VDDI and GNDF isolated power supply outputs.

### Power-Up

At power-up, the following steps must be taken by the host controller managing a system formed by one or multiple ADE1202 devices:

- Supply 3.3 V to the VDD pin. The dc-to-dc converter powers up and supplies the isolated side of the ADE1202. The full device becomes functional. See Table 3 for the power-up time.

- 2. To determine when the ADE1202 devices are ready to accept commands, read the INT\_STATUS register of each device until Bit 14 (RSTDONE) is set to 1.

- 3. Use the SPI to initialize the configuration registers (BIN\_FILTER, PL\_EN, and PGA\_GAIN) of each ADE1202.

- 4. Write 0xADE1 to the LOCK register to complete the configuration process.

Figure 24. ADE1202 Nonisolated and Isolated Sides

## Data Sheet

Figure 26. Digital Input Signal Path

### **DIGITAL INPUTS SIGNAL PATH**

A typical ADE1202 application circuit is shown in Figure 23, which includes external scaling using a voltage divider. The acceptable input voltage between the INx and GNDF pins is given in Table 1.

Using the application circuit shown in Figure 23, ac input signals are half wave rectified, as shown in Figure 23, and require 10 ms + pickup time.

Figure 26 shows a detailed view of the digital signal conditioning done within the ADE1202 IC to generate a DOUTx digital output signal based on the input measured on the INx pins.

The following sections describe the functionality of each circuit in detail.

### PGA

The PGA stage allows four scaling factors, as shown in Table 14. The input voltage range is the same as the INx input voltage range ( $V_{IN}$  in Table 1 and Table 14). To configure the gain over the SPI, write to the PGA\_GAIN register (Address 0x201), Bits[1:0] (PGA\_GAIN). It is recommended to choose the gain that maximizes the range of the internal ADC, as shown in Table 14, without setting the system thresholds outside the range of the PGA.

By default, the PGA\_GAIN bits are cleared to 00, which means the PGA is set to 1.

Table 14. PGA Gain Settings

| Tuble I |     | in strings                   |

|---------|-----|------------------------------|

| VIN     | PGA | PGA_GAIN Register, Bits[1:0] |

| 1.25    | 1×  | 00                           |

| 0.625   | 2×  | 01                           |

| 0.25    | 5×  | 10                           |

| 0.125   | 10× | 11                           |

### SAR ADC

After the PGA stage, the ADE1202 SAR ADC produces 8-bit outputs, as shown in Figure 26. The ADE1202 has two multiplexed channels that share one ADC. The ADC samples at 100 kSPS and each INx channels is sampled at 50 kSPS. The digitized data is then passed through the isolation barrier.

To get an indication of when new ADC samples are ready, configure the DOUT2/IRQ pin as an interrupt by setting the IRQ\_PIN\_MODE bit in the CTRL register, and write 0x8000 to the MASK register. The DOUT2/IRQ pin goes high for 1  $\mu$ s and then low for 9  $\mu$ s at a rate of 100 kSPS, indicating when new ADC samples are ready. When reading ADC samples, Bit 15 in the MASK register, DREADY, must be the only interrupt enabled so that MASK = 0x8000.

## ADE1202

## Decimation

The data from the ADC is passed through a decimator. The decimation filter averages N samples and then decimates by N, where N is 2, 4, or 8, as configured in the DECRATE bits (Bits[2:1]) in the BIN\_CTRL register (see Table 15). The decimation filter topology is shown in Figure 27. To enable the decimation, set Bit 0 (DECIMATE) to 1 in the BIN\_CTRL register. By default, the decimator is disabled and the data from the ADC bypasses the decimator.

### Table 15. Decimation Settings

| DECRATE Bit Setting | Number of Samples    |

|---------------------|----------------------|

| 00                  | Bypass the decimator |

| 01                  | 2                    |

| 10                  | 4                    |

| 11                  | 8                    |

## Digital Datapaths

Four datapaths process the data coming out of the decimator, including comparators and debounce filtering.

One datapath, DOUTx, is capable of driving the DOUTx output, as shown in Figure 26. The output can also be read over the SPI.

Three additional datapaths, WARNAx, WARNBx, and WARNCx are provided for the user to configure warnings. The output of the warning datapaths can be read over the SPI.

Both digital input channels, IN1 and IN2, share the same digital datapath settings.

Set Bit 15 of the BIN\_FILTER, WARNA\_FILTER, WARNB\_ FILTER, and WARNC\_FILTER registers to enable the comparator and debounce filters.

### **Comparator Function**

Each comparator includes a high threshold level and a low threshold level. The thresholds are programmable between 0x00 and 0xFF. An INx pin voltage of 1.25 V/PGA translates to 0xFF. To calculate the threshold register value based on the desired threshold voltage and input signal level, use the following equation:

$$THR = (THRESHOLD/(1.25/PGA)) \times 255$$

(1)

where:

*THR* is the value that is written in the BIN\_THR, WARNA\_THR, WARNB\_THR, and WARNC\_THR control registers. *THRESHOLD* is the desired threshold level expressed in V. *PGA* is the PGA gain selected by the PGA\_GAIN register.

The BIN\_THR register contains the configuration used for the DOUT1 and DOUT2 datapaths, which can be output on the DOUT1 pin and DOUT2 pin.

The WARNA\_THR, WARNB\_THR, and WARNC\_THR registers contain the configuration for the warning channels.

Each comparator has four configurable modes: hysteretic mode, midrange mode, greater than (GT) mode, and lesser than (LT) mode. They are selected by the BIN\_MODE, WARNA\_ MODE, WARNB\_MODE, and WARNC\_MODE bits in the BIN\_CTRL register. After reset, the DOUT1 and DOUT2 channels are in hysteretic mode, the WARNAx channel is in GT mode, the WARNBx channel is in midrange mode, and the WARNCx channel is in LT mode.

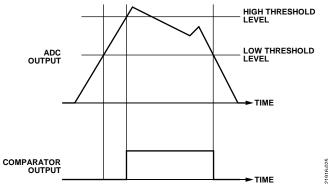

## Comparator in Hysteretic Output Mode

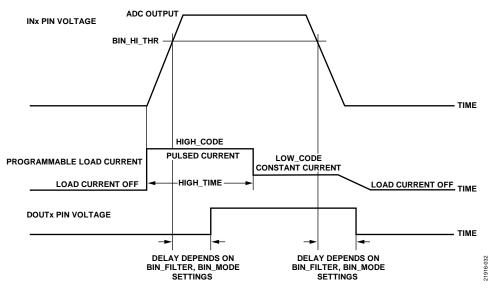

In hysteretic output mode, when the ADC output is greater than the high threshold level of the comparator, the output is set high. The output is set low when the ADC output drops below the low threshold level. The behavior of the comparator in the hysteretic output mode is shown in Figure 28.

Figure 28. Comparator Behavior in Hysteretic Output Mode

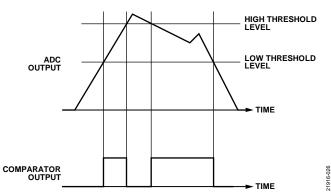

## Comparator in Midrange Output Mode

In midrange output mode, when the ADC output is less than the high threshold level and greater than the low threshold level, the comparator output is set high. The output is set low when the ADC output drops below the low threshold level or goes above the high threshold level. The behavior of the comparator in the midrange output mode is shown in Figure 29.

Figure 29. Comparator Behavior in Midrange Output Mode

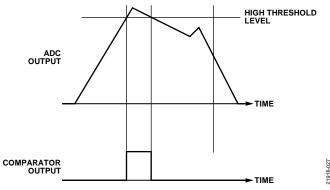

### **Comparator in GT Mode**

In GT mode, when the ADC output is greater than the high threshold level, the comparator output is set high. The comparator output is set low when the ADC output drops below the high threshold level. The behavior of the comparator in GT output mode is shown in Figure 30.

Figure 30. Comparator Behavior in GT Output Mode

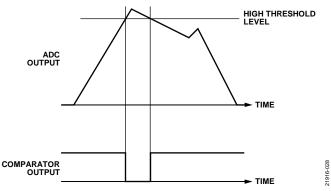

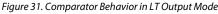

### **Comparator in LT Mode**

In LT mode, when the ADC output is lower than or equal to the high threshold level, the comparator output is set high. The comparator output is set low when the ADC output is greater than the high threshold level. The behavior of the comparator in LT output mode is shown in Figure 31.

### **Debounce Function**

A debounce filter follows the comparator in each datapath.

Each debounce filter consists of a counter that increments every 20  $\mu$ s. The maximum debounce time is 163.82 ms. A filter length of 0 means the debounce filter is bypassed. To calculate the filter length, use the following equation:

#### where:

*Filter Length* is the value that is written in the BIN\_FILTER\_VAL, WARNA\_FILTER\_VAL, WARNB\_FILTER\_VAL, and WARNC\_FILTER\_VAL bit fields. *Debounce Time* is the desired length of the filter expressed in μs. *Channel Update* is 20 μs. The debounce filter can function in two modes, managed by Bit 14 of the BIN\_FILTER, WARNA\_FILTER, WARNB\_FILTER, and WARNC\_FILTER registers. If Bit 14 is 0 (the default value) the filter is in up/clear mode. If Bit 14 is 1, the filter is in up/down mode.

### Debounce Function Up/Clear Mode

In up/clear mode, the filter counter increments while the comparator output is high until the counter reaches the filter length. If the comparator output goes low before the filter length has been reached, the counter is cleared.

When the filter length has been reached, the filter output goes high. The counter stops incrementing when the comparator output is high. The counter is decremented when the comparator output goes low. When the counter decrements to 0, the filter output goes low. If the comparator output goes from low to high before the counter decrements to 0, the counter is reset to the filter length.

### Debounce Function Up/Down Mode

In up/down mode, the filter counter increments while the comparator output is high until the counter reaches the filter length. If the comparator output is low, the counter is decremented.

When the filter length has been reached, the filter output goes high. The counter stops incrementing when the comparator output is high. When the comparator output is low, the counter is decremented. When the counter decrements to 0, the filter output goes low.

See Figure 32 for an example of the debounce filter working in up/down mode and up/clear mode.

The output of the debounce filter can be read through the SPI in the corresponding DOUTx, WARNAx, WARNBx, and WARNCx bits in the STATUS register, and the DOUT1 filter output represents the status for the IN1 filter output, and the DOUT2 filter output represents the status of the DOUT2 debounce filter output.

The status of the DOUT1 and DOUT2 filter outputs is reflected on the DOUT1 pin and the DOUT2/IRQ pin based on the setting of the IRQ\_PIN\_MODE bit (Bit 2) in the CTRL register. The debounce filter outputs can be configured to trigger an interrupt on the DOUT2/IRQ pin (see the Interrupt section).

Figure 32. Debounce Filter Function Example

## **INVALID MODE**

The register protection feature must be disabled when configuring the ADE1202 (see the Protecting the Integrity of Configuration Registers section). During this time, the state of the DOUT1 pin and DOUT2 pin does not reflect the state of the inputs on the IN1 pin and IN2 pin, and the IC is in invalid mode. The IC remains in this mode until the register protection is enabled.

During invalid mode, the ADE1202 output on the DOUT1 pin and DOUT2 pin is set based on Bits[5:4] (INVALID\_MODE) and Bit 3 (FORCEVAL) of the BIN\_CTRL register.

If the INVALID\_MODE bits are equal to 00, the DOUT1 and DOUT2 filter outputs are set to the value configured in the FORCEVAL bit in the BIN\_CTRL register. If the bits are equal to 01, the DOUT1 and DOUT2 filter outputs are set to the DOUTx output from the digital datapath. If the bits are equal to 10, the DOUT1 and DOUT2 filter outputs toggle the value they had upon entering invalid mode. If the bits are equal to 11, the DOUT1 and DOUT2 filter outputs hold the current value.

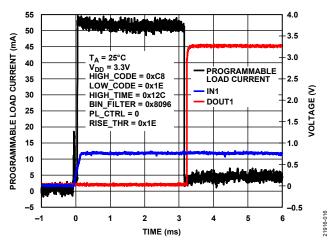

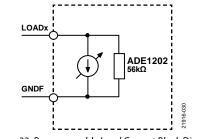

### **PROGRAMMABLE LOAD CURRENT**

The ADE1202 programmable load current block diagram is shown in Figure 33. The input impedance of the programmable load is given in Table 1. When the programmable load is disabled with the PL\_EN register, Bit 15 and Bit 14 = 00, and the external FET is conducting, the load sinks ~100  $\mu$ A.

Figure 33. Programmable Load Current Block Diagram

A high voltage digital input is presented to the ADE1202 application circuit, as shown in Figure 23. When the digital input switches on to a high voltage state, the ADE1202 injects a pulsed current load for a user defined period of time based on the PL\_HIGH\_TIME register, and then switches to a constant current. The pulsed current is sometimes called a wetting current and removes oxidation from the digital input contacts, as well as minimizes the effects of surge and electrical fast transients.

To calculate the value to write to the HIGH\_CODE bits (Bits[7:0]) of the PL\_HIGH\_CODE register to configure the pulsed current, use the following equation:

$$HIGH\_CODE = Pulsed Current/0.2$$

(2)

where *Pulsed Current* is the desired current level expressed in mA. The resolution of the pulsed current is 0.2 mA per LSB. The maximum current is  $(2^8 - 1) \times 0.2 = 51$  mA.

The recommended range of the pulsed current is between 20 mA and 50 mA, and HIGH\_CODE = 100 decimal to 250 decimal. The minimum current is 0.2 mA and HIGH\_CODE = 1.

The pulsed current is applied for a time period set in Bits[11:0] (HIGH\_TIME) in the PL\_HIGH\_TIME register.

To determine the value to write to the HIGH\_TIME bit field based on the desired period of the pulse, use the following equation:

(3)

where *Pulsed Current Period* is the desired time period expressed in  $\mu$ s. The resolution of the pulsed current period is 10  $\mu$ s. The maximum period is  $(2^{12} - 1) \times 10 \ (\mu s) = 40.95 \ ms.$

After the pulsed current period, the programmable load switches to a constant current level set in the LOW\_CODE bits (PL\_LOW\_CODE register, Bits[5:0]). To determine the value to write to the LOW\_CODE bit field, use the following equation:

$$LOW\_CODE = Constant Current/0.1$$

(4)

where:

*Constant Current* is the desired current level expressed in mA. The resolution of the constant current is 0.1 mA per LSB.

The maximum current that can be set is  $(2^6 - 1) \times 0.1 = 6.3$  mA.

## Data Sheet

The user can select between low idle mode and high idle mode to determine when the programmable pulse current is activated.

### Low Idle Mode

The user can select the ADC input code where the programmable load pulse current turns on in low idle mode, where PL\_MODE = 0 in the PL\_CTRL register. This is the default mode of operation.

Figure 34 shows the programmable load current behavior in low idle mode. When the digital input changes from low to high, the pulsed current is generated after the ADC output reaches a rising edge threshold set in the RISE\_THR bits of the PL\_RISE\_THR register, Bits[7:0].

Note that the DOUTx pins must be low for the programmable load pulsed current to be generated. To ensure that a pulsed current is generated, BIN\_FILTER\_VAL must be  $\geq$ 3 and RISE\_THR must be <BIN\_HI\_THR.

## High Idle Mode

To enable high idle mode, set the PL\_MODE bit to 1 in the PL\_CTRL register so the programmable load pulse current conducts as soon as the input voltage over the FET is sufficient (a few hundred mV). Figure 35 shows the programmable load current behavior in high idle mode.

Note that the DOUTx pins must be low for the programmable load pulsed current to be generated. To ensure that a pulsed current is generated, BIN\_FILTER\_VAL must be  $\geq 3$ .

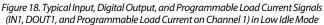

Figure 34. Programmable Load Current Waveform in Low Idle Mode

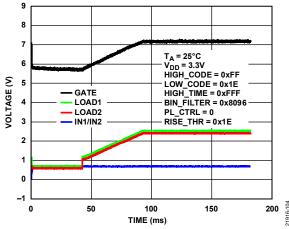

Figure 35. Programmable Load Current Waveform in High Idle Mode

## **Data Sheet**

## **EXTERNAL FET PROTECTION**

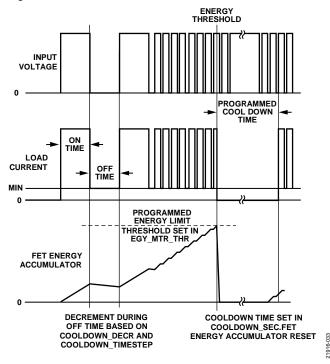

The external FET protection function monitors the approximate FET energy based on the programmed load current and measured digital input voltage over time. When the accumulation reaches a user programmed limit threshold that is a function of the programmed current load, the pulsed current is turned off for a cool down period.

#### **Threshold Calculation**

Calculate the expected ADC code for a given input, ADCx, with the following equation and round to the nearest whole number:

$$ADCx = ((Voltage \times Gain \times Full Scale ADC Codes)) (Voltage Divider \times Reference))$$

(5)

where:

*Voltage* is the input voltage to the ADE1202 application circuit measured in V.

*Gain* is 1, 2, 5, or 10 according to the setting in the PGA\_GAIN register.

*Full Scale ADC Codes* is the maximum code output by the ADC, which is 255.

*Voltage Divide*r is the application circuit voltage divider ratio. *Reference* is the voltage reference value, typically 1.25 V, expressed in V.

Using the safe operating area for the external FET, a threshold, EGY\_MTR\_THR, can be calculated to prevent energy from the pulsed current from exceeding this threshold. To calculate the threshold, use the following equation:

$$EGY\_MTR\_THR = (SOA \times ADCx)/(Voltage \times Pulsed Current \times Rate \times 2^{7})$$

(6)

where:

SOA is the energy that can be safely dissipated by the FET, expressed in J.

Pulsed Current is the pulsed current setting in the

programmable load expressed in A.

*Rate* is the accumulation rate,  $1/100 \text{ kHz} = 10 \text{ }\mu\text{s}$ , expressed in seconds (s).

The expected increase for each pulse is given by the following equation:

Single Pulse Increase =

$$(ADCx \times Pulse Current Time)/$$

(Rate  $\times 2^7$ ) (7)

When the ADC code is equal to 0xFF in a pulsed current state, the IN1 or IN2 input voltages may be greater than the ADC input voltage range, which can cause the external FET to reach the limit of the safe operating area more quickly. To model this effect, configure the OV\_SCALE bits in the EGY\_MTR\_CTRL register to set an overvoltage scaling factor to speed up the FET energy monitoring accumulation. In this condition, the value of each pulse can be calculated with the following equation:

(Overvoltage Factor × Full Scale ADC Codes × Pulse Current Time)/(Rate × 2<sup>7</sup>) where *Overvoltage Factor* is configured in the OV\_SCALE bits in the EGY\_MTR\_CTRL register to allow a 1, 4, 8, or 16 scaling factor.

### **Cool Down Configuration**

When the monitored FET energy reaches the user programmed energy limit threshold, the pulsed current is turned off for a cool down period. The cool down period, expressed in seconds, is set in Bits[3:0] (COOLDOWN\_SEC) in the EGY\_MTR\_CTRL register (Address 0x015). If the COOLDOWN\_SEC bits are cleared to 0, the cool down functionality is disabled, the load current is not turned off, and the accumulator is forced to 0.

The external FET energy accumulator is decremented outside of the pulsed current period by a quantity set in the COOLDOWN\_DECR bits (EGY\_MTR\_CTRL register, Bits[15:8]). The decrement frequency is set in the COOLDOWN\_TIMESTEP bits (EGY\_MTR\_CTRL register, Bits[5:4]). The frequency can be 10 µs (Bits[5:4] = 00), 20 µs (Bits[5:4] = 01), 40 µs (Bits[5:4] = 10), or 80 µs (Bits[5:4] = 11).

When the ADE1202 is in the cool down period, the accumulator resets to 0. Each channel has a corresponding accumulator, EGY\_MTR1 or EGY\_MTR2, which allows cool down to be evaluated on each channel individually.

The external FET protection function mechanism is shown in Figure 36.

Figure 36. FET Protection Cool Down Feature

(8)

## **GATE DRIVE**

The GATE pin is used to drive two external high voltage enhancement mode FETs, Q1 and Q2. After power-up, the GATE pin is biased at  $V_{GATENOM}$  to allow Q1 and Q2 to conduct the constant current while protecting the LOADx pins, as shown in Figure 37. Two 10  $\Omega$ , external, gate current limiting resistors (R13 and R14), and a 0.1  $\mu$ F gate capacitor (C5) are required for stability. Table 1 shows the nominal  $V_{GATENOM}$  voltage (see Figure 37).

During a pulsed current,  $V_{GATENOM}$  is regulated to reduce the voltage on the LOADx pins to minimize on-chip power consumption.

When two FETs are conducting, the corresponding LOADx pin for the FET with the larger gate source voltage ( $V_{GS}$ ) is at 0.6 V and the other LOADx pin is at a higher voltage, as determined by FET mismatch.

When one FET is conducting, the corresponding LOADx pin is at 2.8 V, or as close as possible based on FET  $V_{GS}$ . The LOADx pin voltage is higher with one FET conducting to allow a fast response in case the other FET must turn on.

After a pulsed current period, the GATE voltage is regulated back to  $V_{GATENOM}$ . The ADE1202 is compatible with FETs with a maximum  $V_{GS}$  of 6 V. It is recommended to use the same FET for both channels, and FET to FET mismatch of up to 2 V is supported.

Figure 37. FET Gate Control

## THERMAL SHUTDOWN

If the junction temperature of the isolated side exceeds the thermal shutdown value given in Table 1, the programmable load current is disabled. The TSD bit in the INT\_STATUS register indicates if the device is in thermal shutdown condition. When the device cools down by the hysteresis value given in Table 1, the programmable load current is reenabled.

## INTERRUPT

The interrupt pin,  $\overline{IRQ}$ , is multiplexed with the DOUT2/ $\overline{IRQ}$  pin. Use Bit 2 (IRQ\_PIN\_MODE) in the CTRL register to select the functionality for this pin. If the IRQ\_PIN\_MODE bit is cleared to 0 (the default) the pin functionality is DOUT2. If the bit is set to 1, the pin functionality is  $\overline{IRQ}$ .

When the interrupt pin function,  $\overline{IRQ}$ , is selected, the DOUT2/ $\overline{IRQ}$  output switches from being a push/pull output to an open-drain output.

The  $\overline{IRQ}$  pin is managed by a 16-bit interrupt mask register, MASK. To enable an interrupt, the corresponding bit in the MASK register must be set to 1. To disable an interrupt, the bit must be cleared to 0.

## INT\_STATUS Register

When an interrupt is triggered, the  $\overline{IRQ}$  pin goes low. To determine the source of the interrupt, read the INT\_STATUS register to identify which bit(s) are set to 1. To clear the flag(s) in the INT\_STATUS register, write to the INT\_STATUS register with the corresponding bits set to 1. The  $\overline{IRQ}$  pin remains low until the corresponding INT\_STATUS flag is cleared.

By default, all interrupts are disabled with the exception of the RSTDONE interrupt. This interrupt cannot be disabled (masked).

During power-up or software reset, the DOUT2/IRQ pin defaults to DOUT2 functionality. When the power-up or software reset ends, Bit 14 (RSTDONE) in the INT\_STATUS register is set to 1.

Note that Bit 15 (DREADY) in the MASK register functions differently than Bits[14:0]. See the SAR ADC section more information on the DREADY function.

### STATUS Register

The STATUS register contains status flags that are updated in real time. When the condition related to a flag is triggered, the flag is set to 1. When the condition disappears, the flag is automatically cleared to 0.

The bits in the STATUS register are identical to the bits in the INT\_STATUS register with one exception. Bit 14 is RSTBUSY in the STATUS register and RSTDONE in the INT\_STATUS register. The RSTBUSY bit is 1 during reset and power-on and becomes 0 when the IC is ready to accept commands.

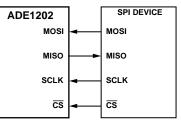

## SPI PROTOCOL OVERVIEW

The compatible SPI consists of four pins: SCLK, MOSI, MISO, and  $\overline{\text{CS}}$ . The ADE1202 is always an SPI slave. The SPI is compatible with 16-bit read/write operations. The maximum serial clock frequency supported by this interface is 10 MHz.

The  $\overline{CS}$  input pin is the chip select input. Drive the  $\overline{CS}$  pin low for the entire data transfer operation. Bring the  $\overline{CS}$  pin high during a data transfer operation to abort the transfer and place the serial bus in a high impedance state. A new transfer can be initiated by returning the  $\overline{CS}$  pin to low.

Data shifts into the device at the MOSI pin on the falling edge of SCLK, and the ADE1202 samples the data on the rising edge of SCLK. Data shifts out of the ADE1202 at the MISO pin on the falling edge of SCLK, and the host controller samples the data on the rising edge of SCLK. The MSB of the word is shifted in and out first. MISO stays in high impedance when no data is transmitted from the ADE1202.

Figure 38 shows the connection between the ADE1202 SPI and a host controller with a master SPI.

Figure 38. Connecting the SPI to an SPI Device

### SPI ADE1202 Addressing

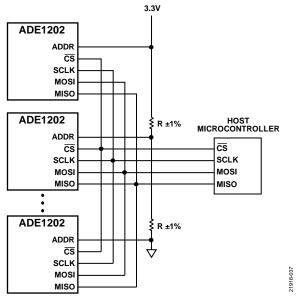

Up to eight ADE1202 devices can be accessed on the same SPI bus. A voltage ladder of up to seven equal resistors ranging from 1 k $\Omega$  to 10 k $\Omega$  values with 1% tolerance can be used (see Figure 40). With the ADDR pin connected to 3.3 V, the ADE1202 has the chip address of 7. With the ADDR pin connected to ground, the ADE1202 has the chip address of 0. The remaining six ADE1202 devices have the chip addresses in sequence based on the applied voltage of the potential divider. If multichip addressing is not used, connect the ADDR pin to ground.

The chip address is indicated in Bits[2:0] of the 16-bit command header.

## **Data Sheet**

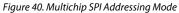

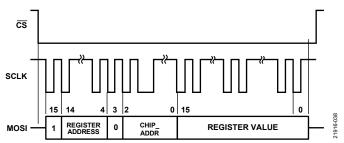

### SPI Write Operation

A write operation is initiated when the host controller sets the  $\overline{\text{CS}}$  pin low and begins sending a 16-bit command word with the register address in Bits[14:4] and Bit 3 of the command header cleared to 0 (see Figure 41).

Figure 43. SPI Read Operation with Appended Cyclic Redundancy Check (CRC)

Each time a register is written, the register value must be verified by reading it back.

If multiple ADE1202 devices share the same SPI bus (as shown in Figure 38) and the same register in multiple chips must be initialized with an identical value, the broadcast write functionality is available. Set Bit 15 in the SPI header word to 1 to enable a broadcast write, as shown in Figure 44. Bits[2:0] (CHIP\_ADDR) of the header word that indicate the chip address on the SPI bus are ignored during a broadcast write.

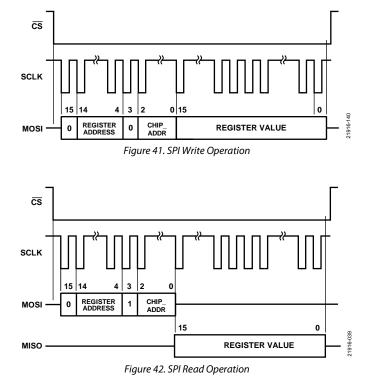

### **SPI Read Operation**

The registers of the ADE1202 can be read one at a time following the protocol shown in Figure 42.

A read operation is initiated when the host controller sets the  $\overline{CS}$  pin low and begins sending a 16-bit command word (see Figure 39). When the ADE1202 receives the last bit of the header word, the device begins to transmit the register contents on the MISO line when the next SCLK high to low transition occurs. The host controller samples the data on the low to high SCLK transition.

For an SPI read operation, Bit 3 of the command header must be set to 1 (see Figure 39).

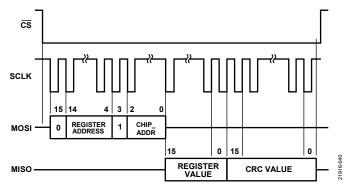

To ensure the integrity of the SPI read operation, a 16-bit CRC (CRC-16) of the register value sent out on the MOSI pin can be included in the transaction. If enabled, the ADE1202 appends the CRC-16 value during the SPI read operation after the register value (see Figure 43).

If Bit 0 (SPI\_CRC\_APPEND\_EN) in the CTRL register is cleared to 0 (the default value), no CRC value is appended during an SPI read operation. If the bit is set to 1, the CRC-16

value is appended to the register value read during the SPI read operation.

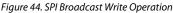

The CRC algorithm is based on the standard CRC-16-CCITT polynomial. The registers are introduced into a linear feedback shift register (LFSR)-based generator one byte at a time, most significant byte first, as shown in Figure 45. Each byte is then used with the MSB first.

Figure 46 shows how the LFSR is used for CRC calculation. The ADE1202 register forms  $Bits[a_{15}:a_0]$  used by the LFSR. Bit  $a_0$  is Bit 15 of the register. Bit  $a_{15}$  is Bit 0 of the register.

Figure 46. LFSR Generator Used for CRC Calculation

Bits  $b_i(0) = 1$ , where i = 0, 1, 2, ... 15, the initial state of the bits that form the CRC. Bit  $b_0$  is the LSB, and Bit  $b_{15}$  is the MSB.

The coefficients  $g_i$ , where i = 0, 1, 2, ... 15, are the coefficients of the generating polynomial defined by the CRC-16-CCITT algorithm as follows:

$$G(x) = x^{16} + x^{12} + x^5 + 1$$

(9)

$$g_0 = g_5 = g_{12} = 1 \tag{10}$$

All other g<sub>i</sub> coefficients are equal to 0.

$FB(j) = a_{j-1} \operatorname{XOR} b_{15}(j-1)$  (11)

$b_0(j) = FB(j) \text{ AND } g_0 \tag{12}$

$$b_i(j) = FB(j)$$

AND  $g_i$  XOR  $b_{i-1}(j-1), i = 1, 2, 3, ... 15$  (13)

Equation 11, Equation 12, and Equation 13 must be repeated for j = 1, 2, ... 16. The value written into the SPI communication CRC contains Bit  $b_i(16)$ , where i = 0, 1, ... 15.