# Multimodal Sensor Front End

#### **FEATURES**

- Multimodal analog front end

- ▶ 4 input channels with multiple operation modes to accommodate the following measurements: PPG, ECG, EDA, impedance, and temperature

- Dual-channel processing with simultaneous sampling

- ▶ 12 programmable time slots for synchronized sensor measurements

- Flexible input multiplexing to support differential and singleended sensor measurements

- ▶ 4 LED drivers, which can be driven simultaneously

- Flexible sampling rate from 0.004 Hz to 9 kHz using internal oscillators

- On-chip digital filtering

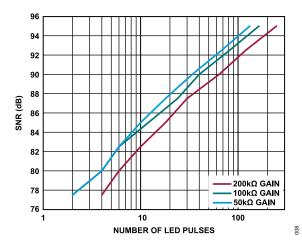

- SNR: 105 dB (100 k $\Omega$  TIA gain, 100 Hz ODR, 80 pulses, C<sub>PD</sub> = 70 pF, 0.5 Hz to 10 Hz bandwidth)

- AC ambient light rejection: 60 dB up to 1 kHz

- ▶ 400 mA total LED peak drive current

- Total system power dissipation: 30 μW (combined LED and AFE power), continuous PPG measurement at 75 dB SNR, 25 Hz ODR, 100 nA/mA CTR

- SPI communications supported

- ▶ 512-byte FIFO size

# **APPLICATIONS**

- Wearable health and fitness monitors: heart rate monitors (HRMs), heart rate variability (HRV), stress, blood pressure estimation, SpO<sub>2</sub>, hydration, and body composition

- ▶ Industrial monitoring: CO, CO<sub>2</sub>, smoke, and aerosol detection

- Home patient monitoring

## **GENERAL DESCRIPTION**

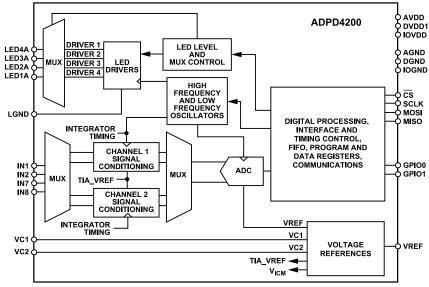

The ADPD4200 operates as a complete multimodal sensor front end, stimulating up to four light emitting diodes (LEDs) and measuring the return signal on up to four separate current inputs. Twelve time slots are available, enabling 12 separate measurements per sampling period.

The data output and functional configuration utilize a serial port interface (SPI) on the ADPD4200. The control circuitry includes flexible LED signaling and synchronous detection. The device uses a 1.8 V analog core and 1.8 V or 3.3 V compatible digital input/output (I/O).

The analog front end (AFE) rejects signal offsets and corruption from asynchronous modulated interference, typically from ambient light, eliminating the need for optical filters or externally controlled dc cancellation circuitry. Multiple operating modes are provided, enabling the ADPD4200 to be a sensor hub for synchronous measurements of photodiodes, biopotential electrodes, resistance, capacitance, and temperature sensors.

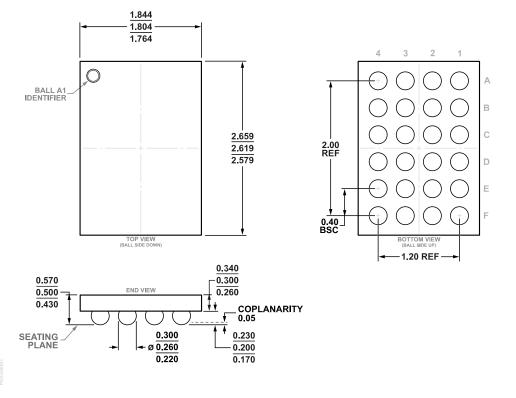

The ADPD4200 is available in a 2.619 mm × 1.804 mm, 0.40 mm pitch, 24-ball WLCSP.

Analog Devices is in the process of updating documentation to provide terminology and language that is culturally appropriate. This is a process with a wide scope and will be phased in as quickly as possible. Thank you for your patience.

# **TABLE OF CONTENTS**

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| General Description                         | 1  |

| Functional Block Diagram                    |    |

| Specifications                              |    |

| Temperature and Power Specifications        |    |

| Performance Specifications                  |    |

| Digital Specifications                      |    |

| Timing Specifications                       | 8  |

| Absolute Maximum Ratings                    |    |

| Thermal Resistance                          |    |

| Recommended Soldering Profile               | 9  |

| Electrostatic Discharge (ESD) Ratings       | 9  |

| ESD Caution                                 | 9  |

| Pin Configuration and Function Descriptions | 10 |

| Typical Performance Characteristics         | 11 |

| Theory of Operation                         | 13 |

| Introduction                                | 13 |

| Analog Signal Path                          | 13 |

| LED Drivers                                 |    |

| Determining C <sub>VLED</sub>               | 15 |

| Datapath, Decimation, Subsampling, and      |    |

| FIFO                                        | 16 |

| Clocking                                    | 19 |

| Time Stamp Operation                        | 19 |

| Low Frequency Oscillator Calibration        | 20 |

| High Frequency Oscillator Calibration       | 20 |

| Time Slot Operation                         | 21 |

| Execution Modes                        | 22 |

|----------------------------------------|----|

| Host Interface                         | 22 |

| Applications Information               | 25 |

| Operating Mode Overview                |    |

| Single Integration Mode                | 25 |

| Multiple Integration Mode              |    |

| Digital Integration Mode               |    |

| TIA ADC Mode                           |    |

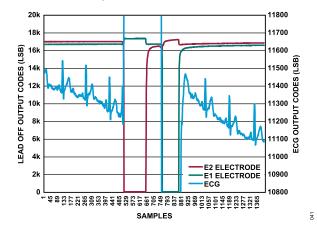

| ECG Measurement with the ADPD4200      |    |

| Register Map                           | 43 |

| Register Details                       |    |

| Global Configuration Registers         | 69 |

| Interrupt Status and Control Registers | 71 |

| Threshold Setup and Control Registers  | 77 |

| Clock and Timestamp Setup and Control  |    |

| Registers                              | 79 |

| System Registers                       | 79 |

| Input and Output Setup and Control     |    |

| Registers                              | 80 |

| Time Slot Configuration Registers      | 83 |

| AFE Timing Setup Registers             | 87 |

| LED Control and Timing Registers       | 89 |

| ADC Offset Registers                   |    |

| Output Data Registers                  | 90 |

| Outline Dimensions                     | 93 |

| Ordering Guide                         |    |

| Evaluation Boards                      | 93 |

# **REVISION HISTORY**

3/2022—Revision 0: Initial Version

analog.com Rev. 0 | 2 of 93

## **FUNCTIONAL BLOCK DIAGRAM**

NOTES

1. TIA\_VREF IS THE INTERNAL VOLTAGE REFERENCE SIGNAL FOR THE TRANSIMPEDANCE AMPLIFIER.

2. CS, SCLK, MOSI, AND MISO ARE SPI INTERFACE PINS.

Figure 1.

00

Rev. 0 | 3 of 93 analog.com

# **SPECIFICATIONS**

# **TEMPERATURE AND POWER SPECIFICATIONS**

**Table 1. Operating Conditions**

| Parameter                                | Test Conditions/Comments           | Min | Тур | Max  | Unit |  |

|------------------------------------------|------------------------------------|-----|-----|------|------|--|

| TEMPERATURE RANGE                        |                                    |     |     |      |      |  |

| Operating Range                          |                                    | -40 |     | +85  | °C   |  |

| Storage Range                            |                                    | -65 |     | +150 | °C   |  |

| POWER SUPPLY VOLTAGE                     |                                    |     |     |      |      |  |

| Supply Voltage, V <sub>DD</sub>          | Applied at the AVDD and DVDD1 pins | 1.7 | 1.8 | 1.9  | V    |  |

| Input and Output Driver Supply, $IOV_DD$ | Applied at the IOVDD pin           | 1.7 | 1.8 | 3.6  | V    |  |

AVDD = DVDD1 = IOVDD = 1.8 V and  $T_A$  = 25°C, unless otherwise noted.

**Table 2. Current Consumption**

| Parameter                                   | Symbol                   | Test Conditions/Comments                                                                                                                      | Min | Тур   | Max | Unit |

|---------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

| POWER SUPPLY (V <sub>DD</sub> ) CURRENT     |                          |                                                                                                                                               |     |       |     |      |

| V <sub>DD</sub> Supply Current <sup>1</sup> |                          | Signal-to-noise ratio (SNR) = 75 dB, 25 Hz output data rate (ODR), single time slot                                                           |     | 10    |     | μA   |

| Total System Power Dissipation              |                          | Combined LED and AFE power, continuous photoplethysmography (PPG) measurement at 75 dB SNR, 25 Hz ODR, 100 nA/mA current transfer ratio (CTR) |     | 30    |     | μW   |

| Peak V <sub>DD</sub> Supply Current (1.8 V) |                          |                                                                                                                                               |     |       |     |      |

| 1-Channel Operation                         | I <sub>VDD_PEAK</sub>    | Peak V <sub>DD</sub> current during time slot sampling                                                                                        |     | 4.5   |     | mA   |

| Standby Mode Current                        | I <sub>VDD_STANDBY</sub> |                                                                                                                                               |     | 0.250 |     | μA   |

$<sup>^{1}~~\</sup>mbox{V}_{\mbox{\scriptsize DD}}$  is the voltage applied at the AVDD and DVDD1 pins.

analog.com Rev. 0 | 4 of 93

# **SPECIFICATIONS**

# PERFORMANCE SPECIFICATIONS

AVDD = DVDD1 = IOVDD = 1.8 V, and  $T_A$  = full operating temperature range, unless otherwise noted.

Table 3.

| Parameter                       | Test Conditions/Comments                                  | Min   | Тур   | Max   | Unit  |

|---------------------------------|-----------------------------------------------------------|-------|-------|-------|-------|

| DATA ACQUISITION                |                                                           |       |       |       |       |

| Datapath Width                  |                                                           |       |       | 32    | Bits  |

| FIRST IN, FIRST OUT (FIFO) SIZE |                                                           |       |       | 512   | Bytes |

| LED DRIVER                      |                                                           |       |       |       |       |

| LED Peak Current per Driver     | LED pulse enabled                                         | 2     |       | 200   | mA    |

| LED Peak Current, Total         | Using multiple LED drivers simultaneously                 |       |       | 400   | mA    |

| Driver Compliance Voltage       | For any LED driver output at ILED = 40 mA                 |       |       | 200   | mV    |

| .ED PERIOD                      | AFE width = $4 \mu s^1$                                   | 10    |       |       | μs    |

|                                 | AFE width = 3 µs                                          | 8     |       |       | μs    |

| SAMPLING RATE <sup>2</sup>      | Single time slot, four data bytes to FIFO, 2 µs LED pulse | 0.004 |       | 9000  | Hz    |

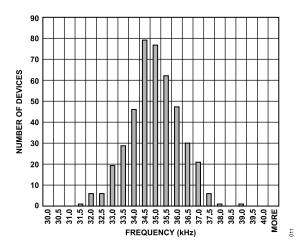

| OSCILLATOR DRIFT                |                                                           |       |       |       |       |

| 32 kHz Oscillator               | Percent variation from 25°C to 85°C                       |       | 3.00  | 5.00  | %     |

|                                 | Percent variation from +25°C to -40°C                     |       | -3.00 | -7.00 | %     |

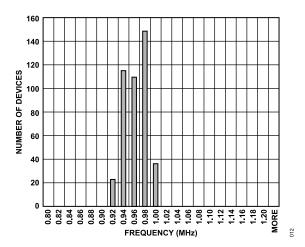

| 1 MHz Oscillator                | Percent variation from 25°C to 85°C                       |       | 1.00  | 2.00  | %     |

|                                 | Percent variation from +25°C to -40°C                     |       | -1.00 | -3.00 | %     |

| 32 MHz Oscillator               | Percent variation from 25°C to 85°C                       |       | 1.00  | 2.00  | %     |

|                                 | Percent variation from +25°C to -40°C                     |       | -2.00 | -4.00 | %     |

<sup>&</sup>lt;sup>1</sup> Minimum LED period =  $(2 \times AFE \text{ width}) + 2 \mu s$ .

Table 4.

| Parameter                                 | Test Conditions/Comments                        | Min  | Тур  | Max | Unit   |

|-------------------------------------------|-------------------------------------------------|------|------|-----|--------|

| TRANSIMPEDANCE AMPLIFIER (TIA) GAIN       |                                                 | 12.5 |      | 200 | kΩ     |

| PULSED SIGNAL CONVERSIONS, 3 µs LED PULSE | 4 μs integration width, signal integration mode |      |      |     |        |

| ADC Resolution <sup>1</sup>               | TIA feedback resistor                           |      |      |     |        |

|                                           | 12.5 kΩ                                         |      | 6.2  |     | nA/LSB |

|                                           | 25 kΩ                                           |      | 3.1  |     | nA/LSB |

|                                           | 50 kΩ                                           |      | 1.5  |     | nA/LSB |

|                                           | 100 kΩ                                          |      | 0.77 |     | nA/LSB |

|                                           | 200 kΩ                                          |      | 0.38 |     | nA/LSB |

| ADC Saturation Level <sup>2</sup>         | TIA feedback resistor                           |      |      |     |        |

|                                           | 12.5 kΩ                                         |      | 50   |     | μA     |

|                                           | 25 kΩ                                           |      | 25   |     | μA     |

|                                           | 50 kΩ                                           |      | 12.5 |     | μA     |

|                                           | 100 kΩ                                          |      | 6.22 |     | μA     |

|                                           | 200 kΩ                                          |      | 3.11 |     | μA     |

| PULSED SIGNAL CONVERSIONS, 2 µs LED PULSE | 3 μs integration width, single integration mode |      |      |     |        |

| ADC Resolution <sup>1</sup>               | TIA feedback resistor                           |      |      |     |        |

|                                           | 12.5 kΩ                                         |      | 8.2  |     | nA/LSB |

|                                           | 25 kΩ                                           |      | 4.1  |     | nA/LSB |

|                                           | 50 kΩ                                           |      | 2.04 |     | nA/LSB |

|                                           | 100 kΩ                                          |      | 1.02 |     | nA/LSB |

|                                           | 200 kΩ                                          |      | 0.51 |     | nA/LSB |

analog.com Rev. 0 | 5 of 93

<sup>&</sup>lt;sup>2</sup> The maximum value in this specification is the internal analog-to-digital converter (ADC) sampling rate using the internal 1 MHz state machine clock. The communication interface like SPI read rates in some configurations may limit the ODR.

# **SPECIFICATIONS**

Table 4.

| Parameter                                 | Test Conditions/Comments                                                                                                                                                     | Min Typ | Max Unit |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|

| ADC Saturation Level <sup>2</sup>         | TIA feedback resistor                                                                                                                                                        |         |          |

|                                           | 12.5 kΩ                                                                                                                                                                      | 67      | μA       |

|                                           | 25 kΩ                                                                                                                                                                        | 33      | μA       |

|                                           | 50 kΩ                                                                                                                                                                        | 16.7    | μA       |

|                                           | 100 kΩ                                                                                                                                                                       | 8.37    | μA       |

|                                           | 200 kΩ                                                                                                                                                                       | 4.19    | μA       |

| ULL SIGNAL CONVERSIONS                    |                                                                                                                                                                              |         |          |

| TIA Linear Dynamic Range (per Channel)    | Total input current, 1% compression point, TIA VREF = 1.265 V                                                                                                                |         |          |

| ,                                         | 12.5 kΩ                                                                                                                                                                      | 72      | μA       |

|                                           | 25 kΩ                                                                                                                                                                        | 38      | μA       |

|                                           | 50 kΩ                                                                                                                                                                        | 18.7    | μA       |

|                                           | 100 kΩ                                                                                                                                                                       | 9.3     | μA       |

|                                           | 200 kΩ                                                                                                                                                                       | 4.6     | μA       |

| YSTEM PERFORMANCE                         |                                                                                                                                                                              |         | <u> </u> |

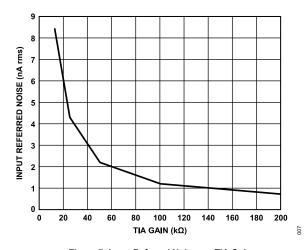

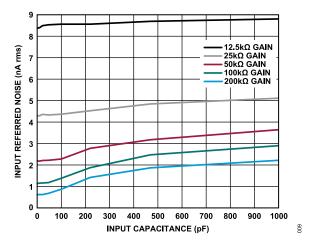

| Referred to Input Noise                   | Single integration mode, single pulse, single channel, floating input, TIA_VREF = 1.265 V, 3 µs integration time                                                             |         |          |

|                                           | 12.5 kΩ TIA gain                                                                                                                                                             | 8.2     | nA rm    |

|                                           | 25 kΩ TIA gain                                                                                                                                                               | 4.1     | nA rm    |

|                                           | 50 kΩ TIA gain                                                                                                                                                               | 2.2     | nA rm    |

|                                           | 100 kΩ TIA gain                                                                                                                                                              | 1.2     | nA rm    |

|                                           | 200 kΩ TIA gain                                                                                                                                                              | 0.61    | nA rm    |

| Referred to Input Noise                   | Single integration mode, single pulse, single channel, 90% full-scale input                                                                                                  | 0.01    | 10 (1111 |

| Tololiou d'Impartiolo                     | signal, no ambient light, TIA_VREF = 1.265 V, VCx = TIA_VREF + 250 mV, 2 $\mu$ s LED pulse, photodiode capacitance (C <sub>PD</sub> ) = 70 pF, input resistor = 500 $\Omega$ |         |          |

|                                           | 12.5 kΩ TIA gain                                                                                                                                                             | 10.3    | nA rm    |

|                                           | 25 kΩ TIA gain                                                                                                                                                               | 5.3     | nA rm    |

|                                           | 50 kΩ TIA gain                                                                                                                                                               | 2.7     | nA rm    |

|                                           | 100 kΩ TIA gain                                                                                                                                                              | 1.5     | nA rm    |

|                                           | 200 kΩ TIA gain                                                                                                                                                              | 0.97    | nA rm    |

| SNR                                       | 12.5 kΩ TIA gain, single pulse                                                                                                                                               | 76      | dB       |

|                                           | 25 kΩ TIA gain, single pulse                                                                                                                                                 | 76      | dB       |

|                                           | 50 kΩ TIA gain, single pulse                                                                                                                                                 | 75      | dB       |

|                                           | 100 kΩ TIA gain, single pulse                                                                                                                                                | 74      | dB       |

|                                           | 200 kΩ TIA gain, single pulse                                                                                                                                                | 72      | dB       |

|                                           | 100 kΩ TIA gain, 100 Hz ODR, 80 pulses, $C_{PD}$ = 70 pF, 0.5 Hz to 10 Hz bandwidth                                                                                          | 105     | dB       |

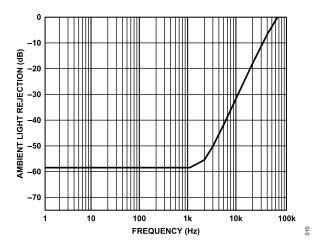

| AC Ambient Light Rejection                | DC to 1 kHz, linear range of TIA                                                                                                                                             | 60      | dB       |

| DC Power Supply Rejection Ratio (DC PSRR) | At 75% full-scale input                                                                                                                                                      | 50      | dB       |

<sup>&</sup>lt;sup>1</sup> ADC resolution is listed per pulse. If using multiple pulses, divide by the number of pulses.

analog.com Rev. 0 | 6 of 93

<sup>&</sup>lt;sup>2</sup> ADC saturation level applies to pulsed signal only, because ambient signal is rejected prior to ADC conversion.

# **SPECIFICATIONS**

# **DIGITAL SPECIFICATIONS**

IOVDD = 1.7 V to 3.6 V, unless otherwise noted.

Table 5. Digital Specifications

| Parameter                   | Symbol          | Test Conditions/Comments       | Min         | Тур Мах      | Unit |

|-----------------------------|-----------------|--------------------------------|-------------|--------------|------|

| LOGIC INPUTS                |                 |                                |             |              |      |

| Input Voltage Level         |                 |                                |             |              |      |

| GPIOx, MISO, MOSI, SCLK, CS |                 |                                |             |              |      |

| High                        | V <sub>IH</sub> |                                | 0.7 × IOVDD | IOVDD + 0.3  | V    |

| Low                         | V <sub>IL</sub> |                                | -0.3        | +0.3 × IOVDD | V    |

| Input Current Level         |                 | All logic inputs               |             |              |      |

| High                        | I <sub>IH</sub> |                                |             | 10           | μA   |

| Low                         | I <sub>IL</sub> |                                | <b>-10</b>  |              | μA   |

| Input Capacitance           | C <sub>IN</sub> |                                |             | 2            | pF   |

| LOGIC OUTPUTS               |                 |                                |             |              |      |

| Output Voltage Level        |                 |                                |             |              |      |

| GPIOx, MISO                 |                 |                                |             |              |      |

| High                        | V <sub>OH</sub> | 2 mA high level output current | IOVDD - 0.5 |              | V    |

| Low                         | V <sub>OL</sub> | 2 mA low level output current  |             | 0.5          | V    |

| Output Current Level        |                 | SDA                            |             |              |      |

| Low                         | I <sub>OL</sub> | V <sub>OL1</sub> = 0.4 V       | 20          |              | mA   |

analog.com Rev. 0 | 7 of 93

# **SPECIFICATIONS**

# **TIMING SPECIFICATIONS**

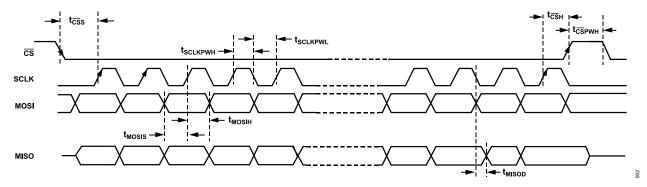

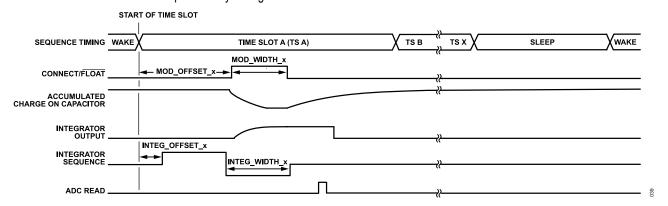

Table 6. SPI Timing Specifications

| Parameter           | Symbol               | Test Conditions/Comments                                                     | Min | Тур | Max  | Unit |

|---------------------|----------------------|------------------------------------------------------------------------------|-----|-----|------|------|

| SPI PORT            |                      |                                                                              |     |     |      |      |

| SCLK                |                      |                                                                              |     |     |      |      |

| Frequency           | f <sub>SCLK</sub>    |                                                                              |     |     | 24   | MHz  |

| Minimum Pulse Width |                      |                                                                              |     |     |      |      |

| High                | t <sub>SCLKPWH</sub> |                                                                              | 15  |     |      | ns   |

| Low                 | t <sub>SCLKPWL</sub> |                                                                              | 15  |     |      | ns   |

| CS                  |                      |                                                                              |     |     |      |      |

| Setup Time          | tcss                 | CS setup to SCLK rising edge                                                 | 11  |     |      | ns   |

| Hold Time           | t <sub>CSH</sub>     | CS hold from SCLK rising edge                                                | 5   |     |      | ns   |

| Pulse Width High    | t <sub>CSPWH</sub>   | CS pulse width high                                                          | 15  |     |      | ns   |

| MOSI                |                      |                                                                              |     |     |      |      |

| Setup Time          | t <sub>MOSIS</sub>   | MOSI setup to SCLK rising edge                                               | 5   |     |      | ns   |

| Hold Time           | t <sub>MOSIH</sub>   | MOSI hold from SCLK rising edge                                              | 5   |     |      | ns   |

| MISO Output Delay   | t <sub>MISOD</sub>   | MISO valid output delay from SCLK falling edge                               |     |     |      |      |

|                     |                      | Register 0x00B4 = 0x0050 (default)                                           |     |     | 28.1 | ns   |

|                     |                      | Register 0x00B4 = 0x005F (maximum slew rate, maximum drive strength for SPI) |     |     | 21.2 | ns   |

Table 7. Timing Specifications for Provision of External Low Frequency Oscillator

| Parameter                       | Min | Тур | Max  | Unit |

|---------------------------------|-----|-----|------|------|

| FREQUENCY                       |     |     |      |      |

| 1 MHz Low Frequency Oscillator  | 500 |     | 2000 | kHz  |

| 32 kHz Low Frequency Oscillator | 10  |     | 100  | kHz  |

| DUTY CYCLE                      |     |     |      |      |

| 1 MHz Low Frequency Oscillator  | 10  |     | 90   | %    |

| 32 kHz Low Frequency Oscillator | 10  |     | 90   | %    |

# **Timing Diagram**

Figure 2. SPI Timing Diagram

analog.com Rev. 0 | 8 of 93

# **ABSOLUTE MAXIMUM RATINGS**

Table 8.

| _ 1 1 1 1                                       |                  |

|-------------------------------------------------|------------------|

| Parameter                                       | Rating           |

| AVDD to AGND                                    | -0.3 V to +2.2 V |

| DVDD1 to DGND                                   | -0.3 V to +2.2 V |

| IOVDD to DGND                                   | -0.3 V to +3.9 V |

| GPIOx, MOSI, MISO, SCLK, $\overline{\text{CS}}$ | -0.3 V to +3.9 V |

| LEDxx to LGND                                   | -0.3 V to +3.9 V |

| Junction Temperature                            | 150°C            |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Close attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance.

Table 9. Thermal Resistance

| Package Type <sup>1</sup> | $\theta_{JA}$ | θ <sub>JC</sub> | Unit |

|---------------------------|---------------|-----------------|------|

| CB-24-5                   | 46            | 1.154           | °C/W |

<sup>&</sup>lt;sup>1</sup> The thermal resistance values are defined as per the JESD51-12 standard.

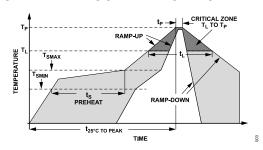

#### RECOMMENDED SOLDERING PROFILE

Figure 3. Recommended Soldering Profile

Table 10.

| 14010 101                                                                                                                                                                                                                                                                          |                                                        |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--|

| Profile Feature                                                                                                                                                                                                                                                                    | Condition (Pb-Free)                                    |  |

| Average Ramp Rate ( $T_L$ to $T_P$ ) Preheat                                                                                                                                                                                                                                       | 3°C/sec maximum                                        |  |

| $\begin{array}{c} \text{Minimum Temperature ($T_{SMIN}$)} \\ \text{Maximum Temperature ($T_{SMAX}$)} \\ \text{Time ($T_{SMIN}$ to $T_{SMAX}$) ($t_{S}$)} \\ \text{$T_{SMAX}$ to $T_{L}$ Ramp-Up Rate} \\ \text{Time Maintained Above Liquidous} \\ \text{Temperature} \end{array}$ | 150°C<br>200°C<br>60 sec to 180 sec<br>3°C/sec maximum |  |

Table 10.

| Profile Feature                                                 | Condition (Pb-Free) |

|-----------------------------------------------------------------|---------------------|

| Liquidous Temperature (T <sub>L</sub> )                         | 217°C               |

| Time (t <sub>L</sub> )                                          | 60 sec to 150 sec   |

| Peak Temperature (T <sub>P</sub> )                              | +260 (+0/-5)°C      |

| Time Within 5°C of Actual Peak<br>Temperature (t <sub>P</sub> ) | <30 sec             |

| Ramp-Down Rate                                                  | 6°C/sec maximum     |

| Time from 25°C to Peak Temperature                              | 8 minutes maximum   |

# **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001 and charged device model (CDM) per ANSI/ESDA/JEDEC JS-002.

# **ESD Ratings for ADPD4200**

Table 11. ADPD4200, 24-Ball WLCSP

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| HBM       | 2500                    | 2     |

| CDM       | 1250                    | C3    |

## **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. 0 | 9 of 93

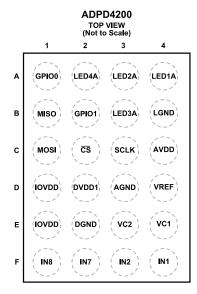

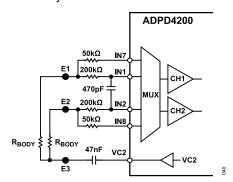

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. Pin Configuration

Table 12. Pin Function Descriptions

| Pin No. | Mnemonic | Type <sup>1</sup> | Description                                                                                            |

|---------|----------|-------------------|--------------------------------------------------------------------------------------------------------|

| A1      | GPIO0    | DIO               | General-Purpose Input and Output 0. The GPIO0 pin is used for interrupts and various clocking options. |

| A2      | LED4A    | AO                | LED Driver 4A Current Sink. If not in use, leave the LED4A pin floating.                               |

| A3      | LED2A    | AO                | LED Driver 2A Current Sink. If not in use, leave the LED2A pin floating.                               |

| A4      | LED1A    | AO                | LED Driver 1A Current Sink. If not in use, leave the LED1A pin floating.                               |

| B1      | MISO     | DO                | SPI Master Input/Slave Output.                                                                         |

| B2      | GPIO1    | DIO               | General-Purpose Input and Output 1. The GPIO1 pin is used for interrupts and various clocking options. |

| B3      | LED3A    | AO                | LED Driver 3A Current Sink. If not in use, leave the LED3A pin floating.                               |

| B4      | LGND     | AO                | LED Driver Ground.                                                                                     |

| C1      | MOSI     | DIO               | SPI Master Output/Slave Input.                                                                         |

| C2      | CS       | DIO               | SPI Chip Select Input.                                                                                 |

| C3      | SCLK     | DIO               | SPI Clock Input.                                                                                       |

| C4      | AVDD     | S                 | 1.8 V Analog Supply.                                                                                   |

| D1      | IOVDD    | S                 | Input and Output Driver Ground.                                                                        |

| D2      | DVDD1    | S                 | 1.8 V Digital Supply.                                                                                  |

| D3      | AGND     | S                 | Analog Ground.                                                                                         |

| D4      | VREF     | REF               | Internally Generated ADC Voltage Reference. Buffer the VREF pin with a 1 µF capacitor to AGND.         |

| E1      | IOVDD    | S                 | 1.8 V or 3.3 V Input and Output Driver Supply.                                                         |

| E2      | DGND     | S                 | Digital Ground.                                                                                        |

| E3      | VC2      | AO                | Output Voltage Source 2 for Photodiode Common Cathode Bias or Other Sensor Stimulus.                   |

| E4      | VC1      | AO                | Output Voltage Source 1 for Photodiode Common Cathode Bias or Other Sensor Stimulus.                   |

| F1      | IN8      | Al                | Current Input 8. If not in use, leave the IN8 pin floating.                                            |

| F2      | IN7      | Al                | Current Input 7. If not in use, leave the IN7 pin floating.                                            |

| F3      | IN2      | Al                | Current Input 2. If not in use, leave the IN2 pin floating.                                            |

| F4      | IN1      | Al                | Current Input 1. If not in use, leave the IN1 pin floating.                                            |

<sup>&</sup>lt;sup>1</sup> DIO means digital input and output, AO means analog output, DO means digital output, S means supply, REF means voltage reference, and AI means analog input.

analog.com Rev. 0 | 10 of 93

## **TYPICAL PERFORMANCE CHARACTERISTICS**

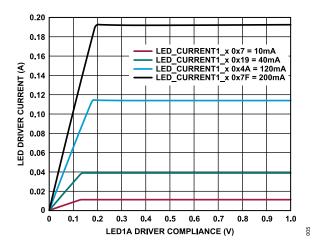

Figure 5. LED Driver Current vs. LED1A Driver Compliance at 10 mA, 40mA, 120 mA, and 200 mA

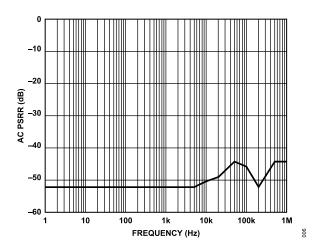

Figure 6. AC PSRR vs. Frequency

Figure 7. Input Referred Noise vs. TIA Gain

Figure 8. SNR vs. Number of Pulses,  $C_{PD}$  = 70 pF

Figure 9. Referred to Input Noise vs. Input Capacitance

Figure 10. Ambient Light Rejection vs. Frequency

analog.com Rev. 0 | 11 of 93

# **TYPICAL PERFORMANCE CHARACTERISTICS**

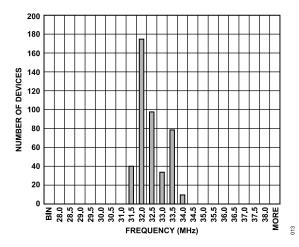

Figure 11. 32 kHz Clock Frequency Distribution, Untrimmed

Figure 12. 1 MHz Clock Frequency Distribution, Untrimmed

Figure 13. 32 MHz Clock Frequency Distribution, Untrimmed

analog.com Rev. 0 | 12 of 93

#### THEORY OF OPERATION

#### INTRODUCTION

The ADPD4200 operates as a complete multimodal sensor front end, stimulating up to four LEDs and measuring the return signal on up to four separate current inputs. Twelve time slots are available, enabling 12 separate measurements per sampling period. The analog inputs can be driven single-ended or in differential pairs. The four analog inputs are multiplexed into a single channel or two independent channels, enabling simultaneous sampling of two sensors.

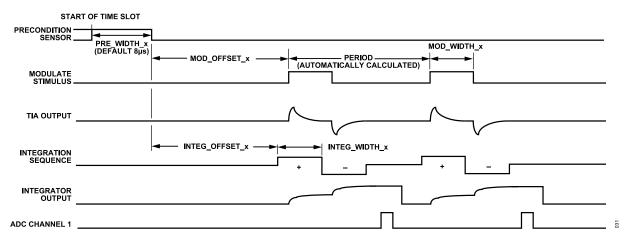

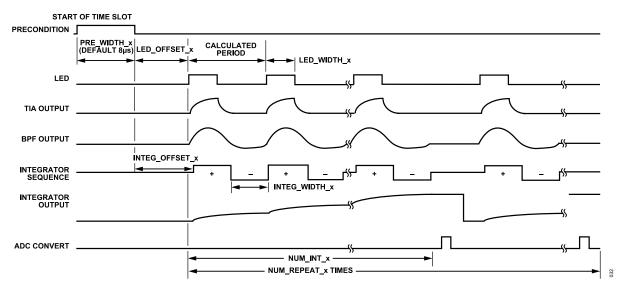

The analog front end (AFE) consists of a TIA, band-pass filter (BPF), integrator, and ADC. The digital block provides multiple operating modes, programmable timing, two GPIOx pins, block averaging, and a selectable second-order through fourth-order cascaded integrator comb (CIC) filter. Four independent LED drivers are provided that can each drive up to 200 mA. Four LED drivers can be enabled in any time slot and can be programmed from 2 mA to 200 mA monotonically, with a 7-bit register setting. The LED drivers enabled in any time slot can provide a total combined maximum of 400 mA of LED current.

The core circuitry provides stimulus to the sensors connected to the inputs of the device and measures the response, storing the results in discrete data locations. The four inputs can drive two simultaneous input channels, either in a single-ended or differential configuration. Data is read directly by a register or through a FIFO method. This highly integrated system includes an analog signal processing block, digital signal processing block, an SPI communication interface, programmable pulsed LED current sources, and pulsed voltage sources for sensors that require voltage excitation.

When making optical measurements, the ADPD4200 provides 60 dB of ambient light rejection using a synchronous modulation scheme with pulses as short as 1  $\mu$ s combined with a BPF. Ambient light rejection is automatic without the need of external control loops, dc current subtraction, or digital algorithms.

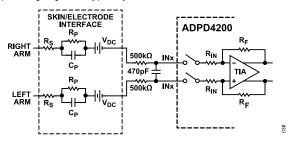

The LED driver is a current sink and is independent from the LED supply voltage and the LED type. The inputs can be connected to any sensor that provides currents up to  $200~\mu A$ . The ADPD4200 can also interface with voltage output sensors with a series resistor placed between the sensor output and the ADPD4200 inputs to convert the voltage to a current. The ADPD4200 produces a high SNR for relatively low LED power while greatly reducing the effect of ambient light on the measured signal.

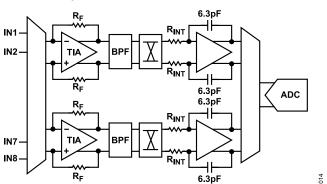

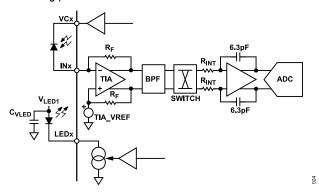

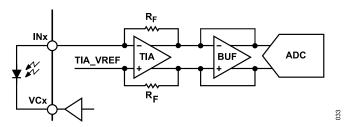

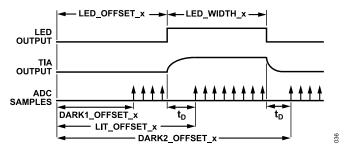

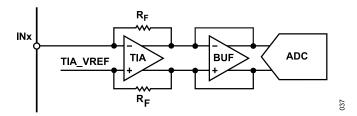

#### ANALOG SIGNAL PATH

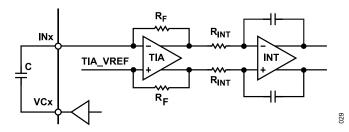

The ADPD4200 analog signal path consists of four current inputs that can be configured as single-ended or differential pairs into one of two independent channels. The two channels can be sampled simultaneously for applications that require instantaneous sampling of two sensors. Each channel contains a TIA with programmable gain, a BPF with a high-pass corner at 100 kHz and a low-pass cutoff frequency of 390 kHz, and an integrator capable of integrating  $\pm 7.5$  pC per sample. Each channel is time multiplexed into a 14-bit ADC. In Figure 14,  $R_{\rm F}$  is the TIA feedback resistor, and  $R_{\rm INT}$  is the series resistor to the input of the integrator.

Figure 14. Analog Signal Path Block Diagram

analog.com Rev. 0 | 13 of 93

#### THEORY OF OPERATION

# **Analog Input Multiplexer**

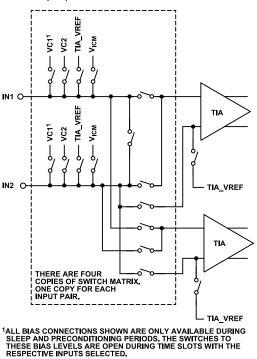

The ADPD4200 supports four analog input pins. Each input can be used as a single-ended input or as part of a differential pair. Figure 15 shows a single representation of the input switch matrix. which allows programmable connection to the two AFE channels. Each pair of inputs has an exact duplicate of this multiplexer: IN1 and IN2, and IN7 and IN8. The connections are programmable per time slot.

The PAIR12 and PAIR78 bits select whether the matching input pair is used as two single-ended inputs or as a differential pair. This selection is valid for all active time slots. The INP12 x and INP78 x bits specify whether the input pair is enabled during the corresponding time slot and, if enabled, which input is connected to which AFE channel.

The sleep conditions are used for any inputs that are not enabled. Sleep conditions are determined by the INP SLEEP 12 and INP SLEEP 78 bits, which specify the state for the input pairs

during sleep and when the inputs are not active. Inputs are only considered active during the precondition and pulse regions for time slots where they are enabled.

Preconditioning of the sensor connected to the input is provided to set the operating point at the input just before sampling. There are several different options for preconditioning determined by the PRECON x bits. The PRECON x bits are provided for each time slot to specify the precondition for enabled inputs or input pairs during the corresponding time slot. Preconditioning options include: float the input(s), VC1, VC2, input common-mode voltage (V<sub>ICM</sub>), TIA VREF, TIA input, and short the input pair. The preconditioning time at the start of each time slot is programmable using the PRE WIDTH x bits. The default preconditioning period is 8 µs.

The block diagram in Figure 15 shows all the bias levels that can be switched into the input connections during sleep and preconditioning. These connections are not available during the sampling phase of a time slot in which the input is selected.

Figure 15. Analog Input Multiplexer

analog.com Rev. 0 | 14 of 93

#### THEORY OF OPERATION

#### Second AFE Channel

The second AFE channel is disabled by default. When disabled, the three amplifiers (TIA, BPF, and integrator) are automatically powered down, and no ADC cycles occur for the second channel. Digital integration and impulse response mode do not use the second channel.

The second AFE channel can be enabled with the CH2\_EN\_x bits on a per time slot basis. When the second channel is enabled, ADC conversions and the datapath bits of the second channel operate. When data is being written to the FIFO, the Channel 2 data is written after the Channel 1 data.

The Channel 2 TIA gain, integrator resistor, and buffer gain (when in digital integrate or TIA ADC mode) are set separately from Channel 1.

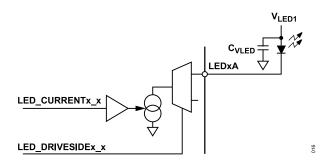

#### **LED DRIVERS**

The ADPD4200 has four LED drivers, which can drive up to four LEDs simultaneously. The LED output driver is a current sink. Figure 16 shows an example of a single LED driver output pair. The ADPD4200 supports only one side of each LED driver, unlike the ADPD4100/ADPD4101 devices. Therefore, there is no LEDxB pin in the ADPD4200 device, but there is still a register to configure the relative LED.

Figure 16. Block Diagram of LED Driver Output Pair

The LED driver output pins, LED1A, LED2A, LED3A, and LED4A, have an absolute maximum voltage rating of 3.9 V. Any voltage exposure over this rating affects the reliability of the device operation and, in certain circumstances, causes the device to cease proper operation. The voltage of the LED driver output pins must not be confused with the supply voltages for the LED themselves. V<sub>LEDx</sub> is the voltage applied to the anode of the external LED, whereas the LED output driver pin is connected to the cathode of the external LED. The compliance voltage is the amount of headroom voltage at the LED driver pin, measured with respect to ground, required to maintain the programmed LED current level and is a function of the current required. Figure 5 shows the typical compliance voltages required at various LED current settings.

Either side of each LED driver output pair, but not both, can be driven in any of the 12 available time slots. Up to four LED driver outputs can be enabled in any time slot using the LED\_

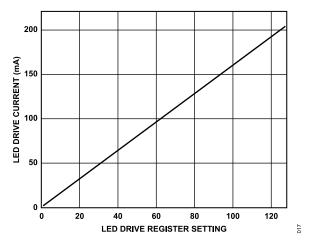

DRIVESIDE1\_x, LED\_DRIVESIDE2\_x, LED\_DRIVESIDE3\_x, and LED\_DRIVESIDE4\_x bit fields. The current is set on a per driver, per time slot basis using the LED\_CURRENT1\_x, LED\_CURRENT2\_x, LED\_CURRENT3\_x, and LED\_CURRENT4\_x bit fields. Each driver can be programmed from 1.5 mA to 200 mA with a monotonic 7-bit setting, as shown in Figure 17. Each setting from 1 to 127 increases the LED drive current by ~1.6 mA. Setting LED\_CURRENTX\_x = 0 disables that particular driver.

Although each driver can be programmed to 200 mA and up to four LED drivers can be enabled in any time slot, there is a 400 mA limit of combined LED driver current that can be provided in any time slot. It is up to the user to program the LED drivers such that this 400 mA limit is not exceeded. If the 400 mA limit is exceeded by the user settings, priority is given, in the following order, to LED1x, LED2x, LED3x, and LED4x. For example, if the user settings have LED1A set to 150 mA, LED2A set to 150 mA, and LED3A set to 150 mA in a single time slot, LED1A and LED2A both provide 150 mA. However, LED3A is limited to 100 mA to maintain the 400 mA total LED drive current limit for the device.

Figure 17. LED Driver Current vs. LED Drive Register Setting

# DETERMINING CVLED

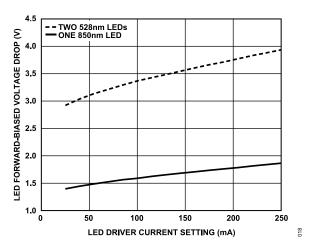

To determine the bypass capacitor ( $C_{VLED}$ ) value, determine the maximum forward-biased voltage,  $V_{FB\_LED\_MAX}$ , of the LED in operation. The maximum LED current,  $I_{LED\_MAX}$ , converts to  $V_{FB\_LED\_MAX}$  as shown in Figure 18. In this example, 125 mA of current through two green LEDs in parallel yields  $V_{FB\_LED\_MAX}$  = 3.5 V. Any series resistance in the LED path must also be included in this voltage. When designing the LED path, keep in mind that small resistances can add up to large voltage drops due to the LED peak current being large. In addition, these resistances can be unnecessary constraints on the  $V_{LEDx}$  supply.

analog.com Rev. 0 | 15 of 93

#### THEORY OF OPERATION

Figure 18. Example of the Average LED Forward-Biased Voltage Drop as a Function of the LED Driver Current Setting

To correctly size the  $C_{VLED}$  capacitor, do not deplete it during the pulse of the LED to the point where the voltage on the capacitor is less than the forward bias on the LED. Calculate the minimum value for  $C_{VLED}$  as follows:

$$C_{VLED} = (t_{LED\_PW} \times I_{LED\_MAX}) / (V_{LED\_MIN} - (V_{FB\_LED\_MAX} + V_{COMP}))$$

(1)

## where:

$t_{LED\ PW}$  is the LED pulse width.

$I_{LED\_MAX}$  is the maximum forward-biased current on the LED used in operating the devices.

$V_{LED\_MIN}$  is the lowest voltage from the  $V_{LED_X}$  supply with no load.  $V_{FB\_LED\_MAX}$  is the maximum forward-biased voltage required on the LED to achieve  $I_{LED\_MAX}$ .

$V_{COMP}$  is the compliance voltage of the LED driver at the programmed LED drive level.

The numerator of Equation 1 sets up the total discharge amount in coulombs from the bypass capacitor to satisfy a single programmed LED pulse of the maximum current. The denominator represents the difference between the lowest voltage from the  $V_{LEDx}$  supply and the LED required voltage. The LED required voltage is the voltage of the anode of the LED such that the compliance of the LED driver and the forward-biased voltage of the LED operating at the maximum current is satisfied. At a 125 mA drive current, the compliance voltage of the driver is  $\sim$ 0.4 V. For a typical ADPD4200

example, assume that the lowest value for the  $V_{LEDx}$  supply is 4.5 V, and that the peak current is 125 mA for two 528 nm LEDs in parallel. The minimum value for  $C_{VI\;ED}$  is then equal to 1  $\mu F$ .

$$C_{VLED} = (3 \times 10^{-6} \times 0.125) / (4.5 - (3.5 + 0.4)) = 0.625 \ \mu F$$

(2)

As shown in Equation 2, as the minimum supply voltage drops close to the maximum anode voltage, the demands on  $C_{VLED}$  become more stringent, forcing the capacitor value higher. It is important to insert the correct values into Equation 2. For example, using an average value for  $V_{LED\_MIN}$  instead of the worst case value for  $V_{LED\_MIN}$  can cause a serious design deficiency, resulting in a  $C_{VLED}$  value that is too small, causing insufficient optical power in the application.

Additionally, multiple pulses can cause further droop on the  $V_{LEDx}$  supply if the  $C_{VLED}$  capacitor is not fully recharged between pulses. Therefore, adding a sufficient margin on  $C_{VLED}$  is strongly recommended. Add additional margin to  $C_{VLED}$  to account for multiple pulses and derating of the capacitor value over voltage, bias, temperature, and other factors over the life of the component.

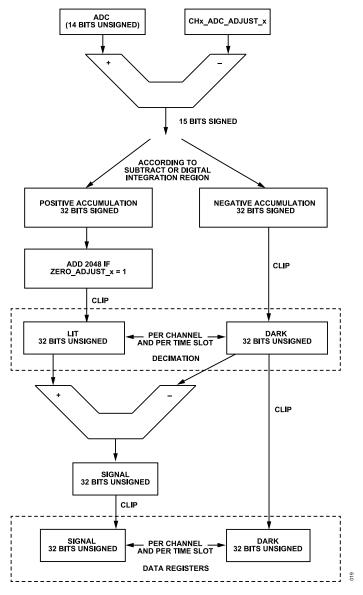

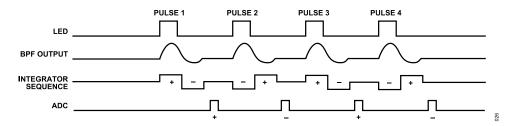

# DATAPATH, DECIMATION, SUBSAMPLING, AND FIFO

ADC samples are gathered for each pulse in each time slot and combine to create a running positive and negative sum for each time slot. These sums are each kept as a 32-bit unsigned value register and saturate if the values overflow 32 bits. Each ADC sample is added to either the positive or negative sum based on the SUBTRACT\_x bits for the current pulse in standard sampling mode, or in the lit or dark acquisition regions for digital integration mode. In impulse mode, the positive sum is used to add two values and the result is written directly to the FIFO. Figure 19 shows the datapath structure.

At the end of the pulse operations in each time slot, the signal value is calculated by subtracting the negative accumulator from the positive accumulator. The signal and dark values are then clipped to positive numbers and are processed by the decimation unit. If the decimated value is ready, the data registers update, and the selected values are written to the FIFO. The data interrupt for that time slot is also set at this time.

analog.com Rev. 0 | 16 of 93

# THEORY OF OPERATION

Figure 19. Datapath Block Diagram

analog.com Rev. 0 | 17 of 93

#### THEORY OF OPERATION

#### Decimation

The DECIMATE\_FACTOR\_x bits determine the number of time slot values used to create a 32-bit final sample value at a rate of

Sample Rate =  $(1/TIMESLOT\_PERIOD\_x)/(DECIMATE\_FACTOR\_x + 1)$

If DECIMATE FACTOR x is 0, the output sample rate equals the time slot rate. The final value is the sum of the decimated samples. There is no divide by (DECIMATE FACTOR x + 1) operation performed on the decimated data, but final data values can be bit shifted to the right before being written to the FIFO, creating a direct average when the number of samples is a power of 2. DECIMATE TYPE x selects the method of decimation used. A setting of 0 selects a simple block sum with other settings allowing higher order CIC filters up to fourth order. If using higher order CIC filters for the signal data, the dark data still uses the simple block sum at the same decimation rate. Each time slot maintains its own block sum or CIC filter state. The entire decimation path uses a 32-bit datapath. When using the CIC filter, the number of bits required for the result is dependent on the number of pulses, the decimation rate, and the order of the CIC filter according to the following equation:

$N_{BITS} = 14 + \log_2(Number \ of \ Pulses) + (\log_2(Decimation \ Rate))(CIC \ Order)$

It is up to the user to ensure that there is no undesired overflow.

Final data results can be read from data registers or a 512-byte data FIFO. Data written to the FIFO is configurable to allow the different data registers, formats, and data sizes as required. Each time slot can use its own decimation rate. Data from each time slot is written to the FIFO at its respective ODR.

## Subsampling

The ADPD4200 supports a subsampling mode that allows selected time slots to run at slower sampling rates than the programmed sampling rate. For example, in a multiparameter application where most of the measurements must be taken at a sampling rate of 300 Hz but one of the measurements must only be taken at 25 Hz, the subsampling mode can be used on the time slot that only needs to operate at 25 Hz. To enable subsampling mode for a specific time slot, set the SUBSAMPLE x bit to 1 and set the DECIMATE FACTOR x bits to the desired subsampling rate. The subsampled time slot then samples only once every (DECI-MATE FACTOR x + 1) cycle, instead of operating every time slot sequence. If other time slots are decimating at the same rate, the subsampled cycles occur at the same time the decimated data is presented to the FIFO. For example, if Time Slot A is operating at 300 Hz but decimating to 25 Hz, and Time Slot B is set to subsample by 12, both time slots write the FIFO during the same time slot sequence and at the same rate.

More complicated patterns can be made if the decimate and subsample rates for the enabled time slots are different. The user must manage the varying packet sizes by reading the data in multiples of the repeating packet size. For example, if Time Slot A is not decimating or subsampling, Time Slot B is subsampling every second cycle, and Time Slot C is subsampling every fourth cycle, the data pattern written to the FIFO is A, AB, A, ABC, and so on, as the repeating packet.

Decimation and subsampling have the same effect on the output data rate. The only difference is that the decimated time slots operate every input cycle but produce data at the slower rate using the on-chip decimating filter. The subsampling time slots only occur at the slower rate.

Status bytes are written to the FIFO every wake-up period, regardless of which time slots execute. Using the same example as the different decimate and subsample rates scenario, but with a status byte enabled, the pattern is AS, ABS, AS, ABCS, and so on, where S is a status byte.

### **FIFO**

Data is written to the FIFO at the end of each sampling period. This packet can include 0, 8-, 16-, 24-, or 32-bit data for each of the dark data and signal data values. The bit alignment of the data written to the FIFO is selectable with a shift of 0 bits to 31 bits, with saturation provided. Lower bits are ignored. The DARK\_SHIFT\_x and SIGNAL\_SHIFT\_x bit fields select the number of bits to shift the output data to the right before writing to the FIFO. The DARK\_SIZE\_x and SIGNAL\_SIZE\_x bit fields select the number of bytes of each field to be written from 0 bytes to 4 bytes. When set to 0, no data is written for that data type. If there are any nonzero bits at more significant bit positions than those selected, the data written to the FIFO is saturated. If both channels are enabled, all selected Channel 1 data values are written to the FIFO first, followed by the Channel 2 data.

For example, in modes that utilize dark data, the eight upper bits of the dark data can be stored with 24 appropriately selected bits from the signal data for each time slot to allow detection of whether the ambient light is becoming large, while limiting the size of the amount of data transferred.

Data is written to the FIFO at the end of the sampling period only if there is enough FIFO space left to write data for each active timeslot. For example, if one active timeslot is running at an ODR of 100 Hz and a second timeslot is decimating by 4 or subsampling at 1/4<sup>th</sup> the rate of the first timeslot for an ODR of 25 Hz, data is only going to be written to the FIFO at the end of the sampling period if there is enough room for both active timeslots to write data, regardless of whether or not the timeslot that is decimating or subsampling is supposed to write data during that sampling period. It is up to the user to manage the data appropriately at the microprocessor end when using timeslots with different decimation and/or subsampling rates.

analog.com Rev. 0 | 18 of 93

#### THEORY OF OPERATION

The FIFO is never written with partial packets of data. If there is not enough room for all of the data to be written to the FIFO for all enabled time slots and any selected status bytes, no data is written from any of the time slots during that period, and the INT\_FIFO\_OFLOW status bit is set.

The order of samples written to the FIFO (if selected) is dark data followed by signal data. The byte order for multibyte words is shown in Table 13.

Table 13. Byte Order for FIFO Writes

| Size | Byte Order (After Shift)        |

|------|---------------------------------|

| 8    | [7:0]                           |

| 16   | [15:8], [7:0]                   |

| 24   | [15:8], [7:0], [23:16]          |

| 32   | [15:8], [7:0], [31:24], [23:16] |

The FIFO size is 512 bytes. When the FIFO is empty, a read operation returns 0xFF, and the INT\_FIFO\_UFLOW status bit is set.

In addition to the FIFO, the signal and dark 32-bit registers can be directly read. These registers are effectively two-stage registers where there is an internal data register that updates with every sample and a latched output data register that is accessed by the host. The data interrupts can be used to align the access of these registers to just after the registers are written. If using the interrupt timing is troublesome, use the HOLD\_REGS\_x bit field to prevent update of the output registers during access not aligned to the interrupt. Setting the HOLD\_REGS\_x bit field blocks the update of the latched output data register and ensures that the dark and signal values read by the host are from the same sample point. If additional samples occur while the HOLD\_REGS\_x bit field is set, the samples are written to the internal data register but not latched into the output data register that is accessed by the host. Setting the HOLD\_REGS\_x bit field to 0 reenables the pass through of new data.

After all time slots have completed, the optional status bytes are written to the FIFO. See the Optional Status Bytes section for more information.

#### **CLOCKING**

# Low Frequency Oscillator

A low frequency oscillator clocks the low speed state machine, which sets the time base used to control the sample timing, wake-up states, and overall operation. There are three options for low frequency oscillator generation. The first option is an internal, selectable 32 kHz or 1 MHz oscillator. The second option is for the host to provide a low frequency oscillator externally. Finally, the low frequency oscillator can be generated by a divide by 32 or divide by 1000 of an external high frequency clock source at 32 MHz. When powering up the device, it is expected that the low frequency oscillator is enabled and left running continuously.

To operate with the on-chip low frequency oscillator, use the following writes. Set the LFOSC\_SEL bit to 0 to select the 32 kHz clock or 1 if the 1 MHz clock is desired. Then, set either the OSC\_1M\_EN or OSC\_32K\_EN bit to 1 to turn on the desired internal oscillator. The internal 32 kHz clock frequency is set using the 6-bit OSC\_32K\_ADJUST bit field. The internal 1 MHz clock frequency is set using the 10-bit OSC\_1M\_FREQ\_ADJ bit field.

If higher timing precision is required than can be provided by the on-chip low frequency oscillator, this oscillator can be driven directly from an external source provided on a GPIOx input. To enable an external low frequency clock, use the following writes. Enable one of the GPIOx inputs using the GPIO\_PIN\_CFGx bit fields. Next, use the ALT\_CLK\_GPIO bit field to choose the enabled GPIOx input to be used for the external low frequency oscillator. Set the ALT\_CLOCKS bit field to 0x1 to select an external low frequency oscillator. Finally, use the LFOSC\_SEL bit to match whether a 32 kHz or 1 MHz clock is being provided.

In a third method, an external 32 MHz clock is used for both the high frequency clock and to be divided down to generate the low frequency clock. To use this method, follow the previous instructions for an external low frequency clock but set the ALT\_CLOCKS bit field to 0x3, and use the LFOSC\_SEL bit to determine if a divide by 32 or 1000 is used to generate the low frequency clock so that either a 32 kHz or 1 MHz clock is generated from the external 32 MHz clock.

# **High Frequency Oscillator**

A 32 MHz high frequency oscillator is generated internally or can be provided externally. This high frequency clock clocks the high speed state machine, which controls the AFE operations during the time slots, such as LED timing and integration times.

The high frequency oscillator can be internally generated by setting the ALT\_CLOCKS bits to 0x0 or 0x1. When selected, the internal 32 MHz oscillator is enabled automatically by the low speed state machine during the appropriate wake-up time or during the 32 MHz oscillator calibration routine.

The high frequency oscillator can also be driven from an external source. To provide an external 32 MHz high frequency oscillator, enable one of the GPIOx inputs using the GPIO\_PIN\_CFGx bits. Then, use the ALT\_CLK\_GPIO bits to choose the enabled GPIOx input for the external high frequency oscillator. Finally, write 0x2 or 0x3 to the ALT\_CLOCKS bits to select an external high frequency oscillator. Writing 0x2 provides only the high frequency oscillator from the external source, whereas writing 0x3 generates both the low frequency oscillator and high frequency oscillator from the external 32 MHz source. When using an external 32 MHz oscillator, it must be kept running continuously for proper device operation.

### TIME STAMP OPERATION

The time stamp feature is useful for calibration of the low frequency oscillator as well as providing the host with timing information

analog.com Rev. 0 | 19 of 93

#### THEORY OF OPERATION

during time slot operation. Time stamping is supported by the use of any GPIOx as a time stamp request input, the CAPTURE\_TIME-STAMP bit to enable capture of the time stamp trigger, a time counter running in the low frequency oscillator domain, and two output registers. The output bits include TIMESTAMP\_COUNT\_x, which holds the number of low frequency oscillator cycles between time stamp triggers, and TIMESTAMP\_SLOT\_DELTA, which holds the number of low frequency oscillator cycles remaining to the next time slot start.

The setup for using the time stamp operation is as follows:

- Set CLK\_CAL\_ENA = 1 to enable the oscillator calibration circuitry.

- Configure a GPIOx to support the time stamp input using the appropriate GPIO\_PIN\_CFGx bits. Select the matching GPIOx to provide the time stamp using the TIMESTAMP GPIOx bits.

- **3.** Configure the ADPD4200 for operation and enable the low frequency oscillator.

- 4. If the TIMESTAMP\_SLOT\_DELTA function is desired, start the time slot operation by placing the device in go mode using the OP\_MODE bit (see Table 14). For low frequency oscillator calibration, it is only required that the low frequency oscillator be enabled. The device does not have to be in go mode for low frequency oscillator calibration.

Use the following procedure to capture the time stamp:

- 1. Set the CAPTURE\_TIMESTAMP bit to 1 to enable the capture of the time stamp on the next rising edge of the selected GPIOx input.

- **2.** The host provides the initial time stamp trigger on the selected GPIOx at an appropriate time.

- The CAPTURE\_TIMESTAMP bit is cleared when the time stamp signal is captured unless the TIMESTAMP\_AL-WAYS\_EN bit is set, in which case, the capture of the time stamp is always enabled. Reenable the capture if necessary.

- **4.** The host provides a subsequent time stamp trigger on the selected GPIOx at an appropriate time.

- The number of low frequency oscillator cycles that occurred between time stamp triggers can be read from the TIME-STAMP\_COUNT\_x bits.

The host must continue to handle the FIFO and/or data register data normally during time stamp processing.

If using a dedicated pin for a time stamp that does not have transitions other than the time stamp, set the TIMESTAMP\_ALWAYS\_EN bit to avoid automatic clearing of the CAPTURE\_TIMESTAMP bit. This setting removes the need to enable the time stamp capture each time.

The time stamp can calibrate the low frequency oscillator as described in the Low Frequency Oscillator Calibration section. The host can also use TIMESTAMP\_SLOT\_DELTA to determine when the next time slot occurs. TIMESTAMP\_SLOT\_DELTA can

determine the arrival time of the samples currently in the FIFO. TIMESTAMP\_SLOT\_DELTA does not account for the decimation factor.

The time stamp trigger is edge sensitive and can be set to either trigger on the rising edge (default) or falling edge using TIMESTAMP INV.

# LOW FREQUENCY OSCILLATOR CALIBRATION

The time stamp circuitry can be used to calibrate either the 32 kHz or 1 MHz low frequency oscillator circuit by adjusting the frequency to match the timing of the time stamp triggers. Simply compare the TIMESTAMP\_COUNT\_x value in low frequency oscillator cycles to the actual time stamp trigger period and adjust the OSC\_32K\_ADJUST or OSC\_1M\_FREQ\_ ADJ value accordingly.

# HIGH FREQUENCY OSCILLATOR CALIBRATION

The high frequency oscillator is calibrated by comparing multiples of its cycles with multiple cycles of the low frequency oscillator, which is calibrated to the system time. Calibration of the low frequency oscillator precedes calibration of the high frequency oscillator. The method for calibrating the high frequency oscillator is as follows:

- 1. Write 1 to the OSC 32M CAL START bit.

- The ADPD4200 automatically powers up the high frequency oscillator.

- The device automatically waits for the high frequency oscillator to be stable.

- 4. An internal counter automatically counts the number of 32 MHz high frequency oscillations that occur during 128 cycles of the 1 MHz low frequency oscillator or 4 cycles of the 32 kHz low frequency oscillator, depending on which low frequency oscillator is enabled based on the setting of the LFOSC\_SEL bit.

- The OSC\_32M\_CAL\_COUNT bits are updated with the final count.

- **6.** The 32 MHz oscillator automatically powers down following calibration unless time slots are active.

- 7. The device resets the OSC\_32M\_CAL\_START bit indicating the count has been updated.

The OSC\_32M\_FREQ\_ADJ bits adjust the frequency of the 32 MHz oscillator to the desired frequency. When using an external low frequency oscillator, the 32 MHz oscillator calibration is performed with respect to the externally provided low frequency oscillator.

When low frequency oscillator and high frequency oscillator calibrations are complete, set the CLK\_CAL\_ENA bit = 0 to disable the clocking of the oscillator calibration circuitry to reduce power. The CLK\_CAL\_ENA bit defaults to 0 so that the calibration circuitry is disabled by default.

analog.com Rev. 0 | 20 of 93

#### THEORY OF OPERATION

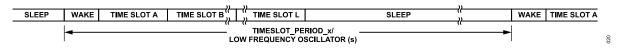

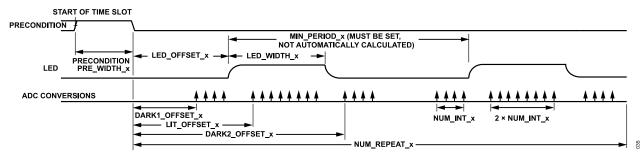

#### TIME SLOT OPERATION

Operation of the ADPD4200 is controlled by an internal configurable controller that generates all the timing needed to generate sampling regions and sleep periods. Measurements of multiple sensors and control of synchronous stimulus sources are handled by multiple time slots. The device provides up to 12 time slots for multisensor applications. The enabled time slots are repeated at the sampling rate, which is configured by the 23-bit TIMESLOT\_PE-RIOD\_x bit field in the TS\_FREQ register. The sampling rate is determined by the following formula:

Sampling Rate = Low Frequency Oscillator Frequency (Hz)  $\div$  TIME-SLOT PERIOD x

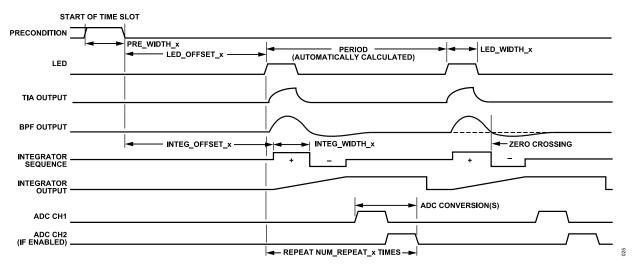

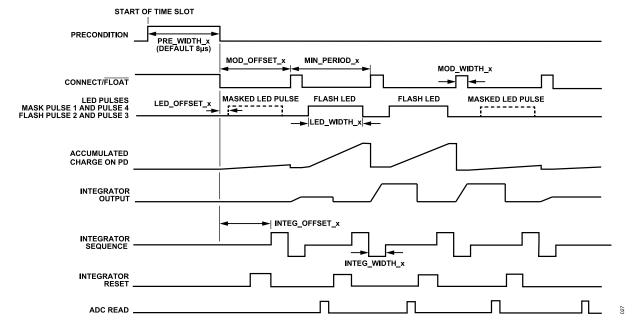

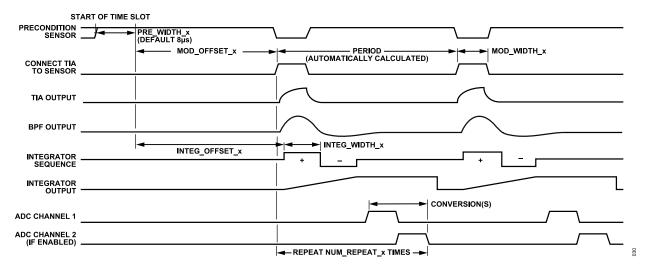

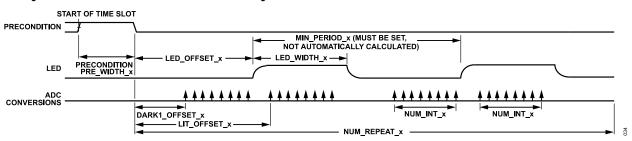

Each time slot allows the creation of one or more LED and/or modulation pulses, and the acquisition of the photodiode or other sensor current based on that stimulus. The operating parameters for each time slot are highly configurable.

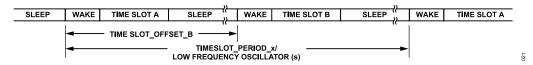

Figure 20 shows the basic time slot operation sequence. Each time slot is repeated at the sampling rate, followed by an ultra low power sleep period. By default, subsequent time slots are initiated immediately following the end of the previous time slot. In addition, there is an option to add an offset to the start of the subsequent time slots using the TIMESLOT\_OFFSET\_x bit field as shown in Figure 21, which shows the TIMESLOT\_OFFSET\_B bit field being used to offset the start of Time Slot B. In this case, each time slot still operates at the sampling rate, but there is a sleep period between Time Slot A and Time Slot B. The wake period shown in Figure 20 and Figure 21 is used to power up and stabilize the analog circuitry before data acquisition begins. If the TIMESLOT\_OFFSET\_B bit field is set to 0, the time slot starts as soon as the previous time slot finishes.

The time slot offset is always applied to the Time Slot A start time. For example, TIMESLOT\_OFFSET\_D is an offset added to the beginning of Time Slot A, not Time Slot C, which immediately precedes Time Slot D.

The amount of offset applied is dependent on the low frequency oscillator used. If using the 1 MHz low frequency oscillator,

Offset = 64 × (Number of 1 MHz Low Frequency Oscillator Cycles) × TIMESLOT OFFSET x

If using the 32 kHz low frequency oscillator,

Offset = 2 × (Number of 32 kHz Low Frequency Oscillator Cycles) × TIMESLOT\_OFFSET\_x

For example, if TIMESLOT\_OFFSET\_C is set to 0x040 and the 1 MHz low frequency oscillator is being used, the offset from the start of Time Slot A to the start of Time Slot C is

Offset =

$$(64 \times 1 \mu s \times 64) = 4.096 ms$$

The sampling rate is controlled by the low frequency oscillator. The low frequency oscillator is driven by one of three sources as described in the Clocking section.

If the sampling period is set too short to allow the enabled time slots to complete, a full cycle of enabled time slot samples is skipped, effectively reducing the overall sample rate. For example, if the sampling rate is set to 100 Hz (10 ms period) and the total amount of time required to complete all enabled time slots is 11 ms, the next cycle of time slots does not begin until t = 20 ms, effectively reducing the sampling rate to 50 Hz.

If TIMESLOT\_OFFSET\_x is set too short to allow the previous time slot to finish, the time slot occurs immediately after the previous time slot. Time slots always occur in A through L order.

# **Using External Synchronization for Sampling**

An external signal driven to a configured GPIOx pin can be used to wake the device from sleep instead of the TIMESLOT\_PERIOD\_x counter, which allows external control of the sample rate and time. This mode of operation is enabled using the EXT\_SYNC\_EN bit and uses the GPIOx pin selected by the EXT\_SYNC\_GPIO bits. If using this feature, be sure to enable the selected GPIOx pin as an input using the appropriate GPIO\_PIN\_CFGx bits.

When operating with external synchronization and set in go mode, the device enters sleep first and waits for the next external synchronization signal before waking up. This external synchronization signal is then synchronized to the low frequency oscillator and then starts the wake-up sequence. If an additional external synchronization is provided prior to completing time slot operations, it is ignored.

Figure 20. Basic Time Slot Operation Sequence

Figure 21. Time Slot Operation with Offset Using TIMESLOT\_OFFSET\_B

analog.com Rev. 0 | 21 of 93

#### THEORY OF OPERATION

## **EXECUTION MODES**

A state machine in the low frequency oscillator clock domain controls sleep times, wake-up cycles, and the start of time slot operations. The low frequency oscillator serves as the time base for all time slot operations, controls the sample rates, and clocks the low frequency state machine. This state machine controls all operations and is controlled by the OP\_MODE bit.

Table 14. OP MODE Bit Setting Descriptions

| OP_MODE Setting | Mode    | Description                                                               |

|-----------------|---------|---------------------------------------------------------------------------|

| 0               | Standby | All operations stopped. Time slot actions reset. Low power standby state. |

| 1               | Go      | Transitioning to this state from standby mode starts time slot operation. |

At power-up and following any subsequent reset operations, the ADPD4200 is in standby mode. The user can write 0 to the OP\_MODE bit to immediately stop operations and return to standby mode.

Register writes that affect operating modes cannot occur during go mode. The user must enter standby mode before changing the control registers. Standby mode resets the digital portion of the ADC, all of the pulse generators, and the state machine.

When OP\_MODE is set to 1, the device immediately starts the first wake-up sequence and time slot operations unless using an external synchronization trigger. If using an external synchronization trigger, the device enters the sleep state before the first wake-up and time slot regions begin.

### **HOST INTERFACE**

The ADPD4200 provides a SPI to communicate with the host. The device also provides numerous FIFO, data register, error, and threshold status bits, each of which can be provided by an interrupt function from a GPIOx, read from status registers, or appended as optional status bytes at the end of a FIFO packet.

# **Interrupt Status Bits**

## **Data Register Interrupts**

The data interrupt status bits, INT\_DATA\_x for each time slot, are set every time that the data registers for each time slot are updated. The state of the HOLD\_REGS\_x bit has no effect on the interrupt logic.

#### **FIFO Threshold Interrupt**