## Multimodal Sensor Front End

#### **FEATURES**

- Optical channel

- 4 input channels with multiple operation modes for various sensor measurements

- Dual channel processing with simultaneous sampling

- 12 programmable time slots for synchronized sensor measurements

- ▶ Flexible input multiplexing to support single-ended sensor measurements

- ▶ 4 LED drivers, 2 of which can be driven simultaneously

- ► Flexible sampling rate from 0.004 Hz to 9 kHz using internal oscillators

- SNR of transmit and receive signal chain: 117 dB (with off-chip filtering)

- ▶ AC ambient light rejection: 78 dB up to 100 Hz

- ▶ 400 mA total LED peak drive current

- ▶ Individual ambient light rejection DAC at TIA input with 9-bit control up to 300 µA

- Individual LED dc cancellation DAC at TIA input with 7-bit control up to 190 μA

- ▶ ECG channel

- ▶ 0.75 µV rms RTI noise at diagnostic filter bandwidth (150 Hz)

- High input impedance: 3 GΩ

- ► Accepts up to 1.2 V of dc differential input range

- ► Common-mode rejection ratio: 116 dB

- ▶ Two-electrode and three-electrode configurations

- ▶ AC lead off detection and dc lead off detection

- ▶ BIA channel

- ▶ Low power, high accuracy excitation path

- Configurable output frequency up to 250 kHz

- Sine wave excitation with a 12-bit DAC

- High accuracy with large imbalance contact impedance

- ► Configurable receive filters with low noise design

- Complex impedance measurement engine

- Supports both external calibration and internal calibration

- SPI communications supported

- ▶ 640-byte FIFO

#### **APPLICATIONS**

- Wearable health and fitness monitors: heart rate, heart rate variability, SpO2, body impedance analysis, hydration, cuffless noninvasive blood pressure

- Home patient monitoring

- Industrial monitoring: particle and aerosol, gas, and conductivity detection

#### **GENERAL DESCRIPTION**

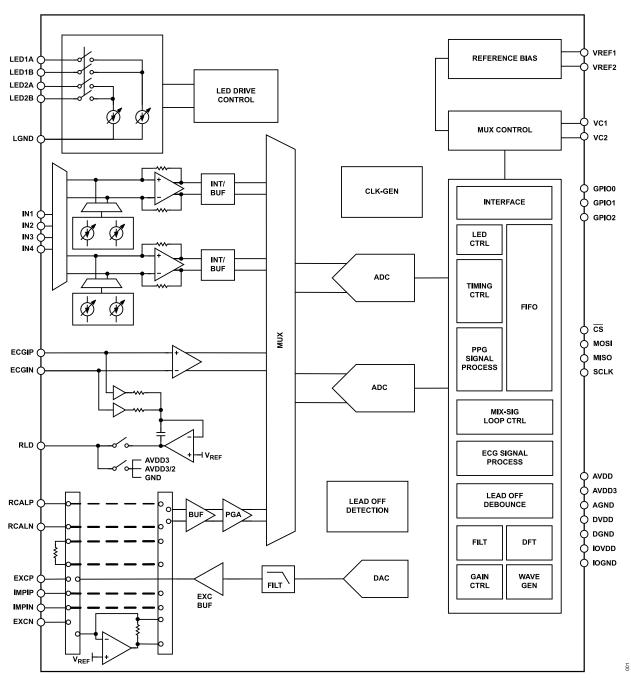

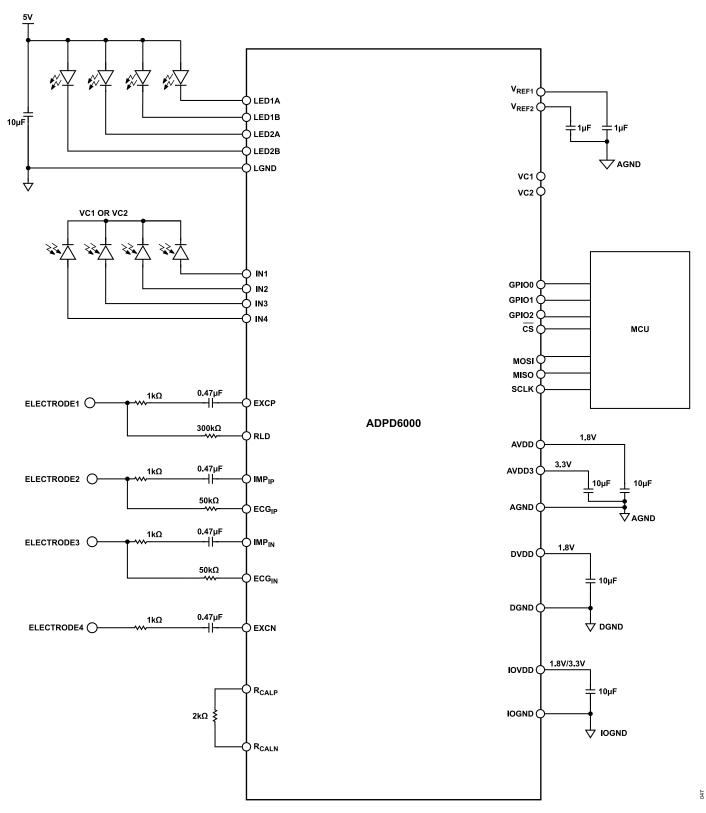

The ADPD6000 is a highly integrated analog front end (AFE) designed for measuring various vital signals.

The optical channel is designed as an optical transceiver, stimulating up to four light emitting diodes (LEDs) and measuring the return signal on up to four separate current inputs. The signal chain rejects signal offsets and corruption from asynchronous modulated interference, typically from ambient light, eliminating the need for optical filters or externally controlled dc cancellation circuitry.

The electrocardiography (ECG) signal acquisition is designed to support low noise, diagnostic level measurement in the presence of a variety of interferers. The ECG signal chain has a number of complementary features supporting ECG measurement, such as driven reference for common-mode rejection and lead off detection to identify a fallen electrode.

The body impedance analysis (BIA) signal chain is designed for body impedance measurement with a configurable excitation path and measurement path. A 12-bit digital-to-analog (DAC) is used in the excitation path to generate the sinusoid wave and high precision measurement, with configurable filters used to measure the body response of the stimulus.

The data output and functional configuration use a serial port interface (SPI) on the ADPD6000. The control circuitry includes flexible LED signaling and synchronous detection, digital filters, digital wave generators, and configurable filters.

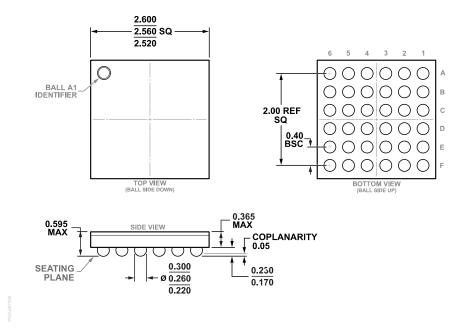

The ADPD6000 is available in a 2.6 mm × 2.6 mm, 0.4 mm pitch, 36-ball wafer level chip scale package (WLCSP).

with a wide scope and will be phased in as quickly as possible. Thank you for your patience.

Analog Devices is in the process of updating documentation to provide terminology and language that is culturally appropriate. This is a process

## **TABLE OF CONTENTS**

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| General Description                         | 1  |

| Functional Block Diagram                    | 3  |

| Specifications                              | 4  |

| Temperature and Power Specifications        | 4  |

| Performance Specifications                  | 4  |

| Digital Specifications                      | 7  |

| Timing Specifications                       | 7  |

| Absolute Maximum Ratings                    |    |

| Thermal Resistance                          |    |

| Electrostatic Discharge (ESD) Ratings       | 9  |

| ESD Caution                                 | 9  |

| Pin Configuration and Function Descriptions | 10 |

| Typical Performance Characteristics         | 12 |

| Theory of Operation                         | 16 |

| Introduction                                |    |

| Time Slot Operation                         | 16 |

| Optical Signal Chain                        | 17 |

| •                                           |    |

| ECG Signal Chain         | 18 |

|--------------------------|----|

| BIA Signal Chain         |    |

| FIFO                     |    |

| Clocking                 | 23 |

| Time Stamp Operation     |    |

| Execution Modes          |    |

| Host Interface           |    |

| Applications Information | 27 |

| Optical Path             | 27 |

| ECG Path                 |    |

| BIA Path                 | 32 |

| Multimodal               | 32 |

| Design Guide             | 35 |

| Register Summary         | 36 |

| Register Details         | 65 |

| Outline Dimensions       |    |

| Ordering Guide           | 89 |

| Evaluation Boards        |    |

# **REVISION HISTORY**

4/2022—Revision 0: Initial Version

analog.com Rev. 0 | 2 of 89

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

analog.com Rev. 0 | 3 of 89

## **SPECIFICATIONS**

## **TEMPERATURE AND POWER SPECIFICATIONS**

Table 1. Temperature and Power Specifications

| Parameter             | Min | Тур | Max  | Unit |

|-----------------------|-----|-----|------|------|

| TEMPERATURE RANGE     |     |     |      |      |

| Operating Range       | -40 |     | +85  | °C   |

| Storage Range         | -65 |     | +150 | °C   |

| POWER SUPPLY VOLTAGES |     |     |      |      |

| AVDD                  | 1.7 | 1.8 | 1.9  | V    |

| AVDD3                 | 2.7 | 3.3 | 3.6  | V    |

| DVDD                  | 1.7 | 1.8 | 1.9  | V    |

| IOVDD                 | 1.7 | 1.8 | 3.6  | V    |

## PERFORMANCE SPECIFICATIONS

AVDD = DVDD = IOVDD = 1.8 V, AVDD3 = 3.3V, and  $T_A$  = 25°C, unless otherwise noted.

**Table 2. Performance Specifications**

| Parameter                                    | Test Condition/Comments                 | Min  | Тур   | Max | Unit   |

|----------------------------------------------|-----------------------------------------|------|-------|-----|--------|

| DATA ACQUISTION                              |                                         |      |       |     |        |

| Datapath Width                               |                                         |      |       | 32  | Bits   |

| FIRST IN, FIRST OUT (FIFO) SIZE              |                                         |      |       | 640 | Bytes  |

| PHOTOPLETHYSMOGRAPHY (PPG)<br>CHANNEL        |                                         |      |       |     |        |

| Transimpedance Amplifier (TIA) Gain          |                                         | 12.5 |       | 400 | kΩ     |

| DIGITAL INTEGRATION MODE                     |                                         |      |       |     |        |

| Analog-to-Digital Converter (ADC) Resolution | TIA feedback resistor (R <sub>F</sub> ) |      | 5.84  |     | nA/LSB |

|                                              | 25 kΩ                                   |      | 2.92  |     | nA/LSB |

|                                              | 50 kΩ                                   |      | 1.46  |     | nA/LSB |

|                                              | 100 kΩ                                  |      | 0.73  |     | nA/LSB |

|                                              | 200 kΩ                                  |      | 0.365 |     | nA/LSB |

|                                              | 400 kΩ                                  |      | 0.183 |     | nA/LSB |

| ADC Saturation Level                         | TIA feedback resistor                   |      |       |     |        |

|                                              | 12.5 kΩ                                 |      | 48    |     | μA     |

|                                              | 25 kΩ                                   |      | 24    |     | μA     |

|                                              | 50 kΩ                                   |      | 12    |     | μA     |

|                                              | 100 kΩ                                  |      | 6     |     | μA     |

|                                              | 200 kΩ                                  |      | 3     |     | μA     |

|                                              | 400 kΩ                                  |      | 1.5   |     | μA     |

| DC Ambient Light Rejection (ALR)             |                                         |      |       |     |        |

| ALR Range                                    |                                         | 0    |       | 300 | μA     |

| ALR Resolution                               |                                         |      | 0.59  |     | μA     |

| LED DC Cancellation                          |                                         |      |       |     |        |

| Range                                        |                                         | 0    |       | 190 | μA     |

| Resolution                                   |                                         |      | 1.48  |     | μA     |

| Dark Noise                                   | Pulse = 1, ADC sample = 20              |      |       |     |        |

|                                              | TIA gain = 12.5 kΩ                      |      | 1490  |     | pA rms |

|                                              | TIA gain = 25 kΩ                        |      | 775   |     | pA rms |

|                                              | TIA gain = 50 kΩ                        |      | 401.5 |     | pA rms |

|                                              | TIA gain = 100 kΩ                       |      | 204.5 |     | pA rms |

analog.com Rev. 0 | 4 of 89

# **SPECIFICATIONS**

**Table 2. Performance Specifications**

| Parameter                                                                                          | Test Condition/Comments                                                     | Min   | Тур  | Max            | Unit   |

|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------|------|----------------|--------|

|                                                                                                    | TIA gain = 200 kΩ                                                           |       | 120  |                | pA rms |

|                                                                                                    | TIA gain = 400 kΩ                                                           |       | 100  |                | pA rms |

| Signal-to-Noise Ratio (SNR)                                                                        | White card reflection, pulse = 1, ADC sample = 20                           |       |      |                |        |

|                                                                                                    | TIA gain = 12.5 kΩ                                                          |       | 90   |                | dB     |

|                                                                                                    | TIA gain = 25 kΩ                                                            |       | 90   |                | dB     |

|                                                                                                    | TIA gain = 50 kΩ                                                            |       | 88   |                | dB     |

|                                                                                                    | TIA gain = 100 kΩ                                                           |       | 87   |                | dB     |

|                                                                                                    | TIA gain = 200 kΩ                                                           |       | 85   |                | dB     |

|                                                                                                    | TIA gain = $400 \text{ k}\Omega$                                            |       | 82   |                | dB     |

| AC ALR                                                                                             | Up to 100 Hz                                                                |       | 78   |                | dB     |

| DC Power Supply Rejection Ratio (PSRR)                                                             | At 75% full scale (FS) input, optimal settings, all gains <sup>1</sup>      |       | 60   |                | dB     |

| ED DRIVER                                                                                          |                                                                             |       |      |                |        |

| Peak Current per Driver                                                                            | LED pulse enabled                                                           |       | 200  |                | mA     |

| Peak Current, Total                                                                                | Using multiple LED drivers simultaneously                                   |       | 400  |                | mA     |

| Current Step                                                                                       | High SNR mode                                                               |       | 1.57 |                | mA     |

| •                                                                                                  | Low compliance mode                                                         |       | 0.52 |                | mA     |

| Compliance Voltage                                                                                 | High SNR mode                                                               |       | 400  |                | mV     |

| - ·                                                                                                | Low compliance mode                                                         |       | 200  |                | mV     |

| Power                                                                                              | AFE current only, 70% FS output data rate (ODR) = 25 Hz                     |       |      |                |        |

| Standby                                                                                            | DVDD + AVDD                                                                 |       | 0.2  |                | μA     |

| Typical Heart Rate Monitor (HRM)                                                                   | DVDD + AVDD                                                                 |       | 28.5 |                | μA     |

| Application  AMPLING RATE                                                                          | TOTAL TABLE                                                                 | 0.004 | 20.0 | 0000           | ļ .    |

|                                                                                                    | D 16 : 000 W 1                                                              | 0.004 |      | 9000           | Hz     |

| CG CHANNEL                                                                                         | Resolution is 286 nV, unless otherwise noted                                |       | 000  |                |        |

| Input Bias Current                                                                                 | ECG input pins, room temperature, lead off detection is off, measured at dc |       | 300  |                | pA     |

| Input Impedance                                                                                    | ECG input pins, measured at dc                                              |       | 3    |                | GΩ     |

| Differential Input Range                                                                           |                                                                             | -1.2  |      | +1.2           | V      |

| Electrode Single-Ended Input Voltage Range                                                         |                                                                             | 0.2   |      | AVDD3 -<br>0.2 | V      |

| Input Common Mode Range                                                                            |                                                                             | 0.4   |      | AVDD3 -<br>0.4 | V      |

| −3 dB Monitor Bandwidth                                                                            | Data rate = 250 SPS                                                         | 40    |      |                | Hz     |

| −3 dB Diagnostic Bandwidth                                                                         | Data rate = 500 SPS                                                         | 150   |      |                | Hz     |

| Gain Flatness                                                                                      | DC to 5.3 Hz (data rate = 250 SPS)                                          |       | ±1   |                | %      |

|                                                                                                    | DC to 19 Hz (data rate = 500 SPS)                                           |       | ±1.5 |                | %      |

| Gain Error                                                                                         |                                                                             | -2    |      | +2             | %      |

| Resolution                                                                                         |                                                                             |       | 286  |                | nV/LSB |

|                                                                                                    |                                                                             |       | 572  |                | nV/LSB |

| Input Referred Noise                                                                               |                                                                             |       |      |                |        |

| 10 Sec Measurement Using Internal<br>Shorted Mode, Measured at Room<br>Temperature                 | Data rate = 250 SPS, monitoring filter bandwidth (40 Hz)                    |       | 0.37 |                | μV rms |

| ·                                                                                                  | Data rate = 500 SPS, diagnostic filter bandwidth (150 Hz)                   |       | 0.75 |                | μV rms |

| 10 Sec System Level Measurement with Proper Electrode Model and All Functions Enabled (DCLO, ACLO) | Data rate = 250 SPS, monitoring filter bandwidth (40 Hz)                    |       | 0.65 |                | μV rms |

| , ,                                                                                                | Data rate = 500 SPS, diagnostic filter bandwidth (150 Hz)                   |       | 0.95 |                | μV rms |

| Common-Mode Rejection Ratio (CMRR)                                                                 | Measured at 60 Hz                                                           |       | 116  |                | dB     |

analog.com Rev. 0 | 5 of 89

## **SPECIFICATIONS**

**Table 2. Performance Specifications**

| Parameter                                 | Test Condition/Comments                                                                                                                                                                                                                                                          | Min     | Тур     | Max     | Unit    |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|---------|

| Output Date Rate                          | Aligned with filter design                                                                                                                                                                                                                                                       | 250     |         | 4000    | Hz      |

| Enable Time                               | Data rate of 500 SPS                                                                                                                                                                                                                                                             |         | 15      |         | ms      |

| Overload Recovery Time                    |                                                                                                                                                                                                                                                                                  |         | 10      |         | ms      |

| Power                                     |                                                                                                                                                                                                                                                                                  |         | 1.7     |         | mW      |

| DC LEAD OFF (DCLO) DETECTION              |                                                                                                                                                                                                                                                                                  |         |         |         |         |

| Drive Circuit                             |                                                                                                                                                                                                                                                                                  |         |         |         |         |

| Lead Off Current Range                    | Lead fail current is programmable over the specified range, programmed current magnitude setting applies across all electrode pins, current polarity is programmable on individual electrode basis                                                                               |         | ±16     |         | nA      |

| Lead Off Current Step Size                |                                                                                                                                                                                                                                                                                  |         | 2       |         | nA      |

| Measure Circuit                           |                                                                                                                                                                                                                                                                                  |         |         |         |         |

| RLD Lead Off Thresholds                   |                                                                                                                                                                                                                                                                                  |         |         |         |         |

| High                                      |                                                                                                                                                                                                                                                                                  | AVDD3 - |         | AVDD3 - | V       |

|                                           |                                                                                                                                                                                                                                                                                  | 0.4     |         | 0.1     |         |

| Low                                       |                                                                                                                                                                                                                                                                                  | 0.1     |         | 0.4     | V       |

| AC LEAD OFF (ACLO) THRESHOLD              |                                                                                                                                                                                                                                                                                  |         |         |         |         |

| Drive Circuit                             |                                                                                                                                                                                                                                                                                  |         |         |         |         |

| Excitation Frequency                      |                                                                                                                                                                                                                                                                                  |         | 4       |         | kHz     |

| Current                                   |                                                                                                                                                                                                                                                                                  | 10      |         | 70      | nA      |

| Measure Circuit                           |                                                                                                                                                                                                                                                                                  |         |         |         |         |

| Threshold                                 |                                                                                                                                                                                                                                                                                  | 0.04    |         | 2.33    | nF      |

| RIGHT LEG DRIVER (RLD)                    |                                                                                                                                                                                                                                                                                  |         |         |         |         |

| Output Voltage                            |                                                                                                                                                                                                                                                                                  | GND     | AVDD3/2 | AVDD3   | V       |

| Stable Load Capacitance                   |                                                                                                                                                                                                                                                                                  |         |         | 2.2     | nF      |

| BIA CHANNEL                               | For Z = 1 k $\Omega$ (0.1% tolerant resistor), excitation frequency = 50 kHz, sine amplitude = 0.6 V p-p, TIA resistor ( $R_{TIA}$ ) = 2 k $\Omega$ , TIA capacitor ( $R_{TIA}$ ) = 7 pF, isolation capacitor = 470 nF, current-limiting resistor ( $R_{LIMIT}$ ) = 1 k $\Omega$ |         |         |         |         |

| SYSTEM PERFORMANCE                        |                                                                                                                                                                                                                                                                                  |         |         |         |         |

| Total System Accuracy                     |                                                                                                                                                                                                                                                                                  |         |         |         |         |

| Magnitude                                 |                                                                                                                                                                                                                                                                                  |         | 0.26    |         | %       |

| Phase                                     |                                                                                                                                                                                                                                                                                  |         | 1       |         | Degrees |

| Body Impedance Magnitude Error            | Contact resistor <1 kΩ                                                                                                                                                                                                                                                           |         | 0.26    |         | %       |

|                                           | Contact resistor <10 kΩ                                                                                                                                                                                                                                                          |         | 5       |         | %       |

| Body Impedance Magnitude<br>Repeatability | Room temperature, test 10 times, contact resistor <1 k $\Omega$                                                                                                                                                                                                                  |         | 0.1     |         | %       |

| Body Phase Angle Error                    |                                                                                                                                                                                                                                                                                  |         | 1       |         | Degrees |

| FRANSMIT STAGE                            |                                                                                                                                                                                                                                                                                  |         | 1       |         | Degrees |

| Output Frequency Range                    |                                                                                                                                                                                                                                                                                  |         | 50      | 250     | kHz     |

| Output Frequency Resolution               |                                                                                                                                                                                                                                                                                  |         | 0.48    | 200     | Hz      |

| Output Voltage Range                      |                                                                                                                                                                                                                                                                                  |         | 5.10    | 800     | mV      |

| Output Voltage Resolution                 |                                                                                                                                                                                                                                                                                  |         | 0.39    | •••     | mV      |

| RECEIVE STAGE                             |                                                                                                                                                                                                                                                                                  |         |         |         |         |

| Input Leakage Current                     |                                                                                                                                                                                                                                                                                  |         |         |         |         |

| Input Capacitance                         | Toward ground for current sensing                                                                                                                                                                                                                                                |         | 10      |         | pF      |

| 1 * 1                                     | Toward ground for voltage sensing                                                                                                                                                                                                                                                |         | 10      |         | pF      |

| ADC Saturation Level                      | Voltage                                                                                                                                                                                                                                                                          |         | ±0.8    |         | V       |

|                                           | Current (TIA = $2 k\Omega$ )                                                                                                                                                                                                                                                     |         | ±400    |         | μA      |

analog.com Rev. 0 | 6 of 89

## **SPECIFICATIONS**

**Table 2. Performance Specifications**

| Parameter            | Test Condition/Comments | Min | Тур  | Max | Unit |

|----------------------|-------------------------|-----|------|-----|------|

| CALIBRATION RESISTOR |                         |     |      |     |      |

| External             |                         |     | 2    |     | kΩ   |

| Internal             |                         |     | 2    |     | kΩ   |

| Power Consumption    |                         |     | 1.24 |     | mW   |

$<sup>^{1} \ \ \</sup>mathsf{DC} \ \mathsf{PSRR} = 20 \times \log((\mathsf{Signal}(\mathsf{LSB})/\mathsf{NUM\_INT\_x}/\mathsf{NUM\_REPEAT\_x} \times 0.146 \ \mathsf{mV/LSB})/\mathsf{V_{IN}} \ (\mathsf{mV}))$

## **DIGITAL SPECIFICATIONS**

IOVDD = 1.7 V to 3.6 V, unless otherwise noted.

Table 3. Digital Specifications

| Parameter                                       | Test Condition/Comments        | Min         | Тур | Max          | Unit |

|-------------------------------------------------|--------------------------------|-------------|-----|--------------|------|

| LOGIC INPUTS                                    |                                |             |     |              |      |

| Input Voltage Level                             |                                |             |     |              |      |

| GPIOx, MISO, MOSI, SCLK, $\overline{\text{CS}}$ |                                |             |     |              |      |

| High                                            |                                | 0.7 × IOVDD |     | IOVDD + 0.3  | V    |

| Low                                             |                                | -0.3        |     | +0.3 × IOVDD | V    |

| Input Current Level                             | All logic inputs               |             |     |              |      |

| High                                            |                                |             |     | 10           | μA   |

| Low                                             |                                | -10         |     |              | μA   |

| Input Capacitance                               |                                |             | 2   |              | pF   |

| LOGIC OUTPUTS                                   |                                |             |     |              |      |

| Output Voltage Level                            |                                |             |     |              |      |

| GPIOx, MISO                                     |                                |             |     |              |      |

| High                                            | 2 mA high level output current | IOVDD - 0.5 |     |              | V    |

| Low                                             | 2 mA low level output current  |             |     | 0.5          | V    |

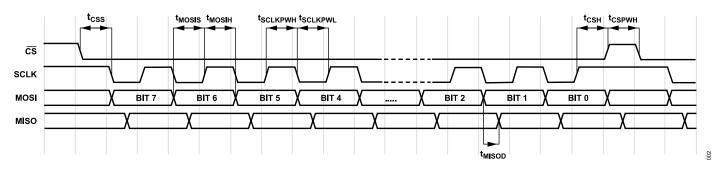

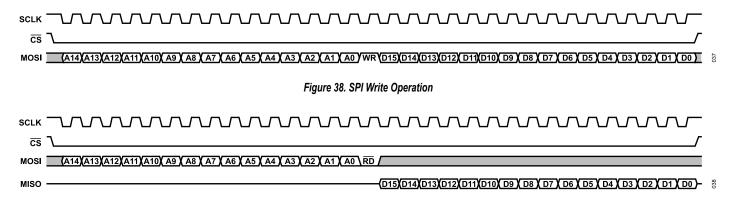

## **TIMING SPECIFICATIONS**

**Table 4. Timing Specifications**

| Parameter                 | Symbol               | Test Condition/Comments                                                      | Min | Тур | Max  | Unit |

|---------------------------|----------------------|------------------------------------------------------------------------------|-----|-----|------|------|

| SPI PORT                  |                      |                                                                              |     |     |      |      |

| SCLK                      |                      |                                                                              |     |     |      |      |

| Frequency                 | f <sub>SCLK</sub>    |                                                                              |     |     | 10   | MHz  |

| Minimum Pulse Width       |                      |                                                                              |     |     |      |      |

| High                      | t <sub>SCLKPWH</sub> |                                                                              | 15  |     |      | ns   |

| Low                       | t <sub>SCLKPWL</sub> |                                                                              | 15  |     |      | ns   |

| CS                        |                      |                                                                              |     |     |      |      |

| Setup Time                | t <sub>CSS</sub>     | CS setup to SCLK rising edge                                                 | 11  |     |      | ns   |

| Hold Time                 | t <sub>CSH</sub>     | CS hold from SCLK rising edge                                                | 5   |     |      | ns   |

| Pulse Width High          | t <sub>CSPWH</sub>   | CS pulse width high                                                          | 15  |     |      | ns   |

| MOSI                      |                      |                                                                              |     |     |      |      |

| Setup Time                | t <sub>MOSIS</sub>   | MOSI setup to SCLK rising edge                                               | 5   |     |      | ns   |

| Hold Time                 | t <sub>MOSIH</sub>   | MOSI hold from SCLK rising edge                                              | 5   |     |      | ns   |

| SWITCHING CHARACTERISTICS |                      |                                                                              |     |     |      |      |

| MISO Output Delay         | t <sub>MISOD</sub>   | MISO valid output delay from SCLK falling edge                               |     |     |      |      |

|                           |                      | Register 0x0057 = 0x0050 (default)                                           |     |     | 21.5 | ns   |

|                           |                      | Register 0x0057 = 0x005F (maximum slew rate, maximum drive strength for SPI) |     |     | 14   | ns   |

analog.com Rev. 0 | 7 of 89

## **SPECIFICATIONS**

# **Timing Diagram**

Figure 2. SPI Timing Diagram

analog.com Rev. 0 | 8 of 89

## **ABSOLUTE MAXIMUM RATINGS**

Table 5. Absolute Maximum Ratings

| Parameter                                               | Rating           |

|---------------------------------------------------------|------------------|

| AVDD to AGND                                            | -0.3 V to +2.2 V |

| AVDD3 to AGND                                           | -0.3 V to +3.9 V |

| DVDD to DGND                                            | -0.3 V to +2.2 V |

| IOVDD to IOGND                                          | -0.3 V to +3.9 V |

| GPIOx, MOSI, MISO, SCLK, $\overline{\text{CS}}$ to DGND | -0.3 V to +3.9 V |

| LEDxx to LGND                                           | -0.3 V to +3.9 V |

| Junction Temperature                                    | 150°C            |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Close attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance.

Table 6. Thermal Resistance

| Package Type          | $\theta_{JA}$ | $\theta_{JC}$ | Unit |

|-----------------------|---------------|---------------|------|

| CB-36-10 <sup>1</sup> | 42.15         | 0.98          | °C/W |

<sup>&</sup>lt;sup>1</sup> The thermal resistance values are defined as per the JESD51-12 standard.

## **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

Charged device model (CDM) per ANSI/ESDA/JEDEC JS-002.

Machine model (MM) per ANSI/ESD STM5.2. MM voltage values are for characterization only.

## **ESD Ratings for ADPD6000**

Table 7. ADPD6000, 36-Ball WLCSP

| ESD Model | Withstand Threshold (V) | Class          |

|-----------|-------------------------|----------------|

| HBM       | 2000                    | 2              |

| CDM       | 750                     | C2B            |

| MM        | 100                     | Not applicable |

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. 0 | 9 of 89

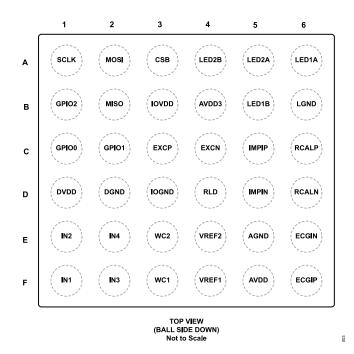

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 8. Pin Function Descriptions**

| Pin No. | Mnemonic | Туре   | Description                                                                          |

|---------|----------|--------|--------------------------------------------------------------------------------------|

| F5      | AVDD     | Power  | 1.8 V Analog Power Supply.                                                           |

| B4      | AVDD3    | Power  | 3.3 V Analog Power Supply.                                                           |

| E5      | AGND     | Power  | Analog Ground.                                                                       |

| D1      | DVDD     | Power  | 1.8 V Digital Power Supply.                                                          |

| D2      | DGND     | Power  | Digital Ground.                                                                      |

| B3      | IOVDD    | Power  | I/O Power Supply.                                                                    |

| D3      | IOGND    | Power  | I/O Ground.                                                                          |

| B6      | LGND     | Power  | LED Ground.                                                                          |

| F4      | VREF1    | Analog | ADC 1 Reference.                                                                     |

| E4      | VREF2    | Analog | ADC 2 Reference.                                                                     |

| F3      | VC1      | Analog | Output Voltage Source 1 for Photodiode Common Cathode Bias or Other Sensor Stimulus. |

| E3      | VC2      | Analog | Output Voltage Source 2 for Photodiode Common Cathode Bias or Other Sensor Stimulus. |

| F1      | IN1      | Analog | Current Input 1.                                                                     |

| E1      | IN2      | Analog | Current Input 2.                                                                     |

| F2      | IN3      | Analog | Current Input 3.                                                                     |

| E2      | IN4      | Analog | Current Input 4.                                                                     |

| A6      | LED1A    | Analog | LED Driver 1A.                                                                       |

| B5      | LED1B    | Analog | LED Driver 1B.                                                                       |

| A5      | LED2A    | Analog | LED Driver 2A.                                                                       |

| A4      | LED2B    | Analog | LED Driver 2B.                                                                       |

| F6      | ECGIP    | Analog | ECG Positive Input.                                                                  |

| E6      | ECGIN    | Analog | ECG Negative Input.                                                                  |

| D4      | RLD      | Analog | Right LED Driver.                                                                    |

| C5      | IMPIP    | Analog | BIA Positive Input.                                                                  |

| D5      | IMPIN    | Analog | BIA Negative Input.                                                                  |

| C3      | EXCP     | Analog | BIA Excitation Positive Output.                                                      |

| C4      | EXCN     | Analog | BIA Excitation Negative Output.                                                      |

analog.com Rev. 0 | 10 of 89

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 8. Pin Function Descriptions

| Pin No. | Mnemonic | Туре    | Description                         |

|---------|----------|---------|-------------------------------------|

| C6      | RCALP    | Analog  | Calibration Resistor Positive Side. |

| D6      | RCALN    | Analog  | Calibration Resistor Negative Side. |

| A3      | CS       | Digital | SPI Chip Select Input.              |

| A1      | SCLK     | Digital | SPI Clock Input.                    |

| B2      | MISO     | Digital | SPI Master Input/Slave Output.      |

| A2      | MOSI     | Digital | SPI Master Output/Slave Input.      |

| C1      | GPIO0    | Digital | General-Purpose Input/Output 0.     |

| C2      | GPIO1    | Digital | General-Purpose Input/Output 1.     |

| B1      | GPIO2    | Digital | General-Purpose Input/Output 2.     |

analog.com Rev. 0 | 11 of 89

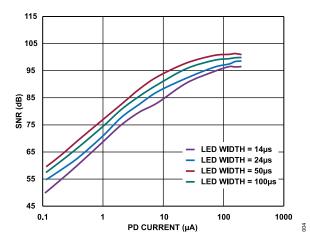

## **TYPICAL PERFORMANCE CHARACTERISTICS**

DVDD = AVDD = 1.8 V, AVDD3 = 3.3 V, LGND = DGND = AGND = IOGND = 0 V, and  $T_A$  = 25°C, unless otherwise noted.

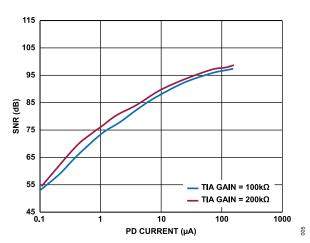

Figure 4. SNR vs. Photodiode (PD) Current, Number of Sequence Repeats = 1, TIA Gain = 100 k $\Omega$

Figure 5. SNR vs. PD Current, LED Width = 24 µs, Number of Sequence Repeats = 1

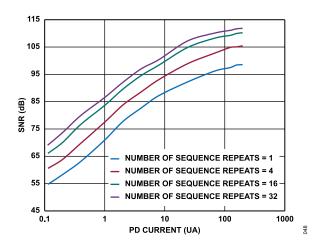

Figure 6. SNR vs. PD Current, LED Width = 24  $\mu$ s, TIA Gain = 100  $k\Omega$

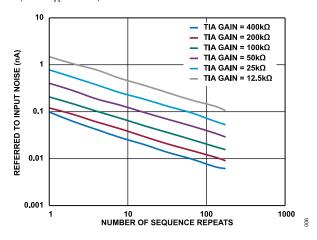

Figure 7. Referred to Input Noise vs. Number of Sequence Repeats

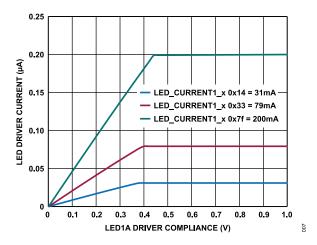

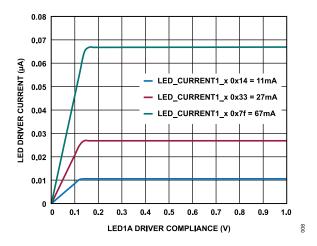

Figure 8. LED Driver Current vs. LED1A Driver Compliance, High SNR Mode

Figure 9. LED Driver Current vs. LED1A Driver Compliance, Low Compliance

Mode

analog.com Rev. 0 | 12 of 89

## TYPICAL PERFORMANCE CHARACTERISTICS

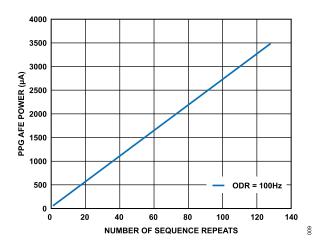

Figure 10. PPG AFE Power vs. Number of Sequence Repeats

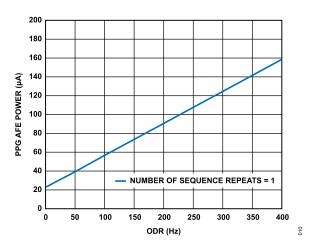

Figure 11. PPG AFE Power vs. ODR

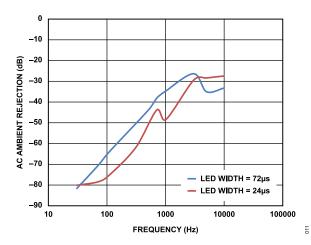

Figure 12. AC Ambient Rejection vs. Frequency

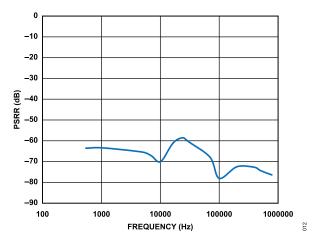

Figure 13. PSRR vs. Frequency, PD Current = 8 μA

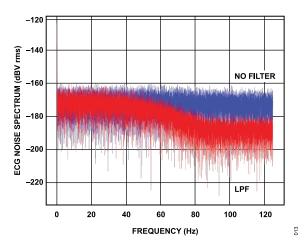

Figure 14. ECG Noise Spectrum vs. Frequency, Input Shorted to Common-Mode Voltage ( $V_{\rm CM}$ ), Resolution = 286 nV/LSB, Sample Rate = 250 Hz (LPF Is Low Pass Filter)

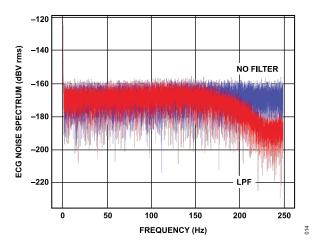

Figure 15. ECG Noise Spectrum vs. Frequency, Input Shorted to V<sub>CM</sub>, Resolution = 286 nV/LSB, Sample Rate = 500 Hz

analog.com Rev. 0 | 13 of 89

## TYPICAL PERFORMANCE CHARACTERISTICS

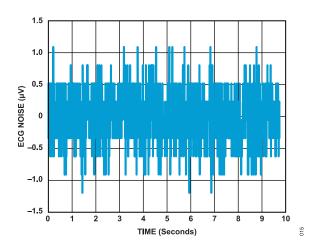

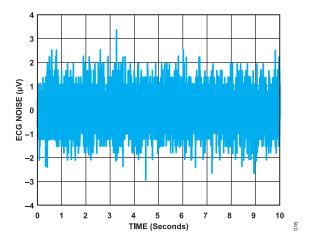

Figure 16. ECG Noise vs. Time, Input Shorted to  $V_{CM}$ , Resolution = 286 nV/LSB, Sample Rate = 250 Hz

Figure 17. ECG Noise vs. Time, Input Shorted to  $V_{CM}$ , Resolution = 286 nV/LSB, Sample Rate = 500 Hz

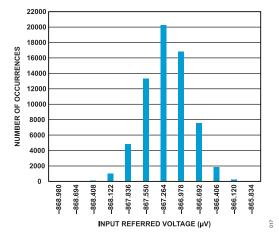

Figure 18. ECG Noise Histogram, Input Shorted to  $V_{CM}$ , Resolution = 286 nV/LSB, Sample Rate = 250 Hz

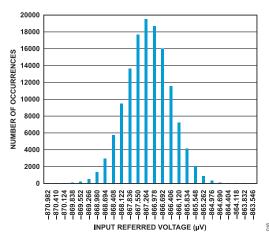

Figure 19. ECG Noise Histogram, Input Shorted to  $V_{\rm CM}$ , Resolution = 286 nV/LSB, Sample Rate = 500 Hz

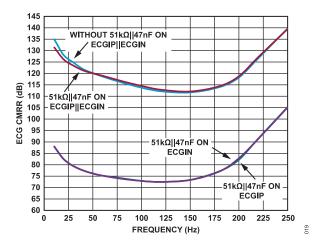

Figure 20. ECG CMRR vs. Frequency, Resolution = 286 nV/LSB, Sample Rate = 500 Hz

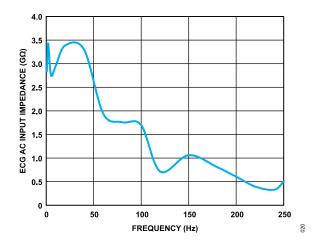

Figure 21. ECG AC Input Impedance vs. Frequency, Resolution = 286 nV/LSB, Sample Rate = 500 Hz

analog.com Rev. 0 | 14 of 89

## **TYPICAL PERFORMANCE CHARACTERISTICS**

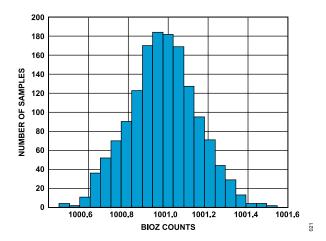

Figure 22. Bioimpedance (BIOZ) Noise Histogram

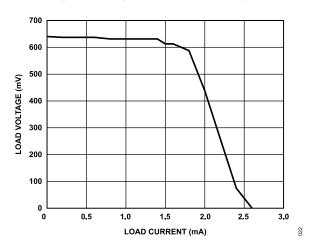

Figure 23. BIOZ Drive Capability

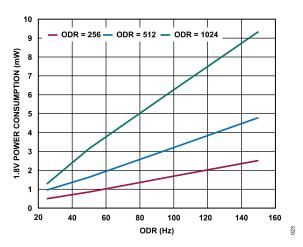

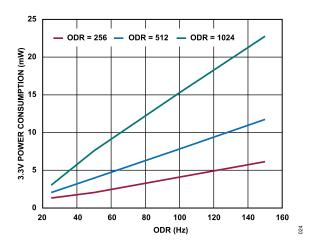

Figure 24. 1.8 V Power Consumption vs. ODR

Figure 25. 3.3 V Power Consumption vs. ODR

analog.com Rev. 0 | 15 of 89

#### THEORY OF OPERATION

#### INTRODUCTION

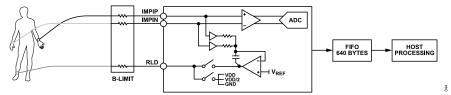

The ADPD6000 is a multimodal, vital signal monitoring AFE that comprises three high performance signal chains: an optical measurement path (PPG), ECG measurement path, and BIA measurement path.

The PPG measurement path works as a transceiver that supports up to four LEDs and four photodiode inputs. The current on the LEDs is programmable from two 7-bit LED drivers. The receiver path provides two high performance readout channels that can sample simultaneously and can be configured separately. Two high performance current DACs (IDACs) are implemented in each channel to provide first class ambient light suppression and large dynamic range in different application scenarios.

The ECG measurement path offers a high input impedance, low noise, high dynamic range solution to allow high quality ECG signal acquisition in wearable devices. Both DCLO detection and ACLO detection are integrated to guarantee proper detectability.

The stimulus in the BIA path offers a sine wave with various options for frequency, amplitude, and phase to make the ADPD6000 suitable for measurement in different scenarios. A low noise TIA, programmable gain amplifier (PGA), filter, and ADC are integrated in the receiver channel to provide high performance impedance measurement. Direct digital synthesis (DDS) and discrete Fourier transform (DFT) engines are also integrated in this path.

An internal state machine allows flexible control of these three measurement paths. The acquisition data can be stored in a 640-byte FIFO.

#### **TIME SLOT OPERATION**

An internal configurable controller handles the operation of the ADPD6000. This controller generates the timing needed to generate sampling regions comprising combinations of the three measurement paths and sleep periods. To facilitate the use of multiple signal chains, multiple time slots handle the access to different transmitters or receivers.

The system is characterized by the ODR, which determines the repetition periodicity of each enabled time slot. The enabled time

slots are repeated at the time slot rate configured by the TIME-SLOT PERIOD x bits.

There are 19 time slots in the ADPD6000, as shown in Figure 26.

Each enabled PPG and BIA time slot is repeated at the time slot rate, followed by an ultra low power sleep period.

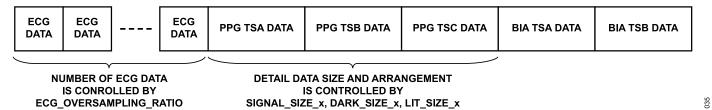

ECG\_TS is the ECG time slot. The operation of the ECG signal chain is not in time slot fashion. After the ECG time slot turns on, the ECG signal chain runs until the system stops. However, the ECG signal chain output data is synchronized to the FIFO with this time slot rate.

Following the ECG time slot, there are 12 PPG time slots (PPG\_TSA to PPG\_TSL). Each PPG time slot allows the creation of one or more LED pulses and modulate pulses, as well as the acquisition of the photodiode or other device current based on that stimulus. The operating parameters for each time slot are highly configurable.

The last six time slots are the BIA time slots (BIA\_TSA to BIA\_TSF). Each BIA time slot allows the excitation voltages, frequencies, and receiver configurations to facilitate accurate body impedance measurement.

Equation 1 determines the sampling rate (time slot rate), as follows:

Sampling Rate = Timer Clock Frequency  $(Hz)/TIMESLOT\_PERIOD\_x$  (1)

Table 9. Sources of Low Frequency Clock (LFCLK) and Timer Clock<sup>1</sup>

| LFCLK                                      | Timer Clock                                | ALT_CLOCKS | TM_CLK_GPIO_SEL |

|--------------------------------------------|--------------------------------------------|------------|-----------------|

| 960 kHz internal                           | 960 kHz internal                           | 0          | N/A             |

| 960 kHz external                           | 960 kHz external                           | 1          | N/A             |

| 960 kHz internal                           | 960 kHz internal                           | 2          | N/A             |

| 1 MHz external<br>(divided from 32<br>MHz) | 1 MHz external<br>(divided from 32<br>MHz) | 3          | N/A             |

| 960 kHz internal                           | 960 kHz external                           | 4          | 1               |

| 960 kHz internal                           | 32 kHz external                            | 4          | 0               |

025

<sup>&</sup>lt;sup>1</sup> N/A means not applicable.

|   | 0      | 1       | 2       | 3       | 4       | 5       | 6       | 7       | 8       | 9       | 10      | 11      | 12      | 13      | 14      | 15      | 16      | 17      | 18      |

|---|--------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| I | ECG_TS | PPG_TSA | PPG_TSB | PPG_TSC | PPG_TSD | PPG_TSE | PPG_TSF | PPG_TSG | PPG_TSH | PPG_TSI | PPG_TSJ | PPG_TSK | PPG_TSL | BIA_TSA | BIA_TSB | BIA_TSC | BIA_TSD | BIA_TSE | BIA_TSF |

Figure 26. Time Slot Allocation

analog.com Rev. 0 | 16 of 89

#### THEORY OF OPERATION

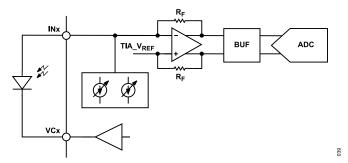

#### **OPTICAL SIGNAL CHAIN**

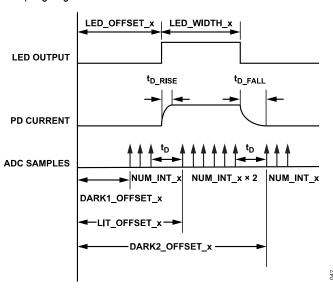

The optical signal path stimulates up to four LEDs and measures the return signal on up to four separate current inputs. Twelve optical time slots enable 12 separate optical measurements per sampling period.

The analog inputs can be driven single-ended or in differential pairs. The four analog inputs can be multiplexed into a single channel or two independent channels, enabling simultaneous sampling of two sensors.

The optical signal chain consists of a TIA, an integrator that can also be configured as a buffer depending on the register setting, and an ADC. The digital block provides multiple operating modes, programmable timing, and block averaging.

Four independent LED drivers are provided that can each drive up to 200 mA. Two LED drivers can be enabled in any time slot and can be programmed from 1.5 mA to 200 mA monotonically, with a 7-bit register setting. The LED drivers enabled in any time slot can provide a combined maximum LED current of 400 mA.

When making optical measurements, the ADPD6000 provides 100 dB of ac ambient light rejection using a synchronous modulation scheme with pulses as short as 1  $\mu$ s. Ambient light rejection is automatic without the need of external control loops, dc current subtraction, or digital algorithms.

The LED driver is a current sink and is independent from the LED supply voltage and the LED type. The optical measurement path produces a high SNR for relatively low LED power, while greatly reducing the effect of ambient light on the measured signal.

## **Analog Signal Path**

The analog signal path of the optical signal chain consists of four current inputs that can be configured as single-ended or differential pairs into one of two independent channels. The two channels can be sampled simultaneously for applications that require instantaneous sampling of two sensors.

#### **Analog Input Multiplexer**

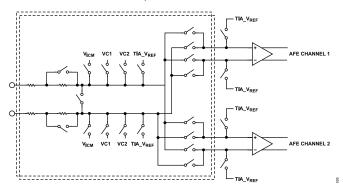

The optical signal chain supports four analog input pins. Each input can be used as a single-ended input or as part of a differential pair. Figure 27 shows a single representation of the input switch matrix, which allows a programmable connection to the two optical channels. Each pair of inputs has a duplicate of this multiplexer: IN1 and IN2, and IN3 and IN4. The connections are programmable per time slot.

The PAIR12 and PAIR34 bits select whether the matching input pair is used as two single-ended inputs or as a differential pair. This selection is valid for all active time slots. The INP12\_x and INP34\_x bits specify whether the input pair is enabled during the corresponding time slot and, if enabled, which input is connected to which optical channel.

The sleep conditions are used for any inputs that are not enabled. Sleep conditions are determined by the INP\_SLEEP\_12 and INP\_SLEEP\_34 bits, which specify the state for the input pairs during sleep and when the inputs are not active. Inputs are only considered active during the precondition and pulse regions for time slots where they are enabled.

Preconditioning of the sensor connected to the input is provided to set the operating point at the input before sampling. There are several different options for preconditioning determined by the PRECON\_x bits. The PRECON\_x bits are provided for each time slot to specify the precondition for enabled inputs or input pairs during the corresponding time slot. Preconditioning options include floating the inputs, VC1, VC2, input common-mode voltage (V<sub>ICM</sub>), internal voltage reference signal for the TIA (TIA\_V<sub>REF</sub>), TIA input, and shorting the input pair. The preconditioning time at the start of each time slot is programmable using the PRE\_WIDTH\_x bits. The default preconditioning period is 8  $\mu$ s.

The block diagram in Figure 27 shows the bias levels that can be switched into the input connections during sleep and preconditioning. These connections are not available during the sampling phase of a time slot in which the input is selected.

Figure 27. Switch Matrix Block Diagram

## **Ambient Light Cancellation**

The ADPD6000 has three modes to perform ambient light cancellation, as follows:

- Coarse tuning only

- ▶ Coarse and fine tuning loop

- ► External microcontroller unit (MCU) control

Coarse tuning only mode and coarse and fine tuning loop mode are automatically controlled by the ADPD6000 without any software assistance. External MCU control mode allows tuning the ambient light rejection through an external algorithm.

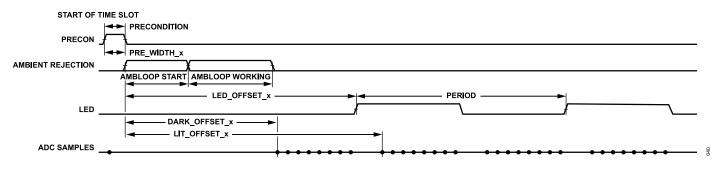

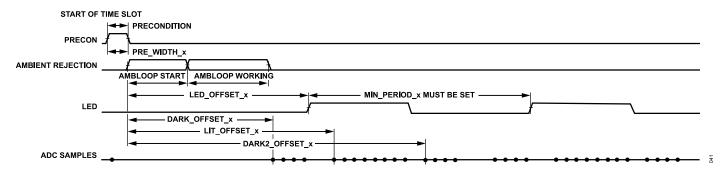

Use the AMBIENT CANCELLATION x bits to choose the mode.

Coarse tuning mode works at the beginning of each PPG time slot. This mode measures the ambient light level and sets the ambient DAC code. This circuitry needs 48  $\mu$ s to complete these activities and determine the baseline of the ambient DAC. Afterward, the

analog.com Rev. 0 | 17 of 89

#### THEORY OF OPERATION

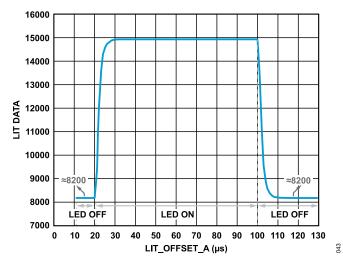

PPG channel can start normal operation—for example, if in digital integration mode, the PPG receiver channel can start to take dark samples. This ambient baseline is used in the time slot if coarse tuning only mode is enabled.

If coarse and fine tuning loop mode is enabled, the coarse tuning circuit works the same way as in coarse tuning mode. However, the ambient DAC code updates after each dark sample measurement.

Select these two modes with the AMBIENT\_CANCELLATION\_x bits for system level design flexibility.

Coarse loop mode makes the measurement to find the accurate value of the ambient current. Then, the ambient DAC subtracts the ambient current at the beginning of the signal chain so that it does not corrupt the PPG signal measurement.

Both analog integration mode and digital integration mode can perform coarse loop ambient rejection.

The fine tuning loop updates the ambient information after each dark sample measurement. This feature is available only in digital integration mode.

The MCU mode allows the user to subtract the ambient current. The DAC\_AMBIENT\_CH1\_x and DAC\_AMBIENT\_CH2\_x bits are designed to allow the user to fill in the current ambient value, and the AFE then subtracts that value from the signal chain. DAC\_AMBIENT\_CH1\_x and DAC\_AMBIENT\_CH2\_x are 9-bit fields, with each LSB representing a 0.6  $\mu$ A step in a 0  $\mu$ A to 300  $\mu$ A range.

#### **LED DC Cancellation**

Besides the ambient DAC, there is another IDAC at the input of each signal chain. This IDAC is used to subtract the unwanted dc component in the reflected LED to increase the dynamic range of the receiver channel.

These two IDACs are controlled by the MCU only. The DAC\_LED\_DC\_CH1\_x and DAC\_LED\_DC\_CH2\_x bits control the LED dc canceling, 7-bit IDAC with full scale.

The LED dc subtraction feature is available only for digital integration mode.

A certain amount of dc current can be subtracted from the AFE based on the top level optical and system design. DAC\_LED\_DC\_CH1\_x and DAC\_LED\_DC\_CH2\_x are 7-bit fields, with each LSB representing a 1.5  $\mu A$  step in a 0  $\mu A$  to 190  $\mu A$  range.

#### **LED Drivers**

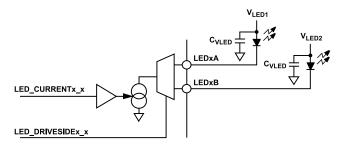

The optical path has two LED drivers, each of which is brought out to two LED driver outputs, providing a total of four LED output drivers. The device can drive up to two LEDs simultaneously, one from each driver pair. The LED output driver is a current sink.

Figure 28 shows an example of a single LED driver output pair.

NOTES C<sub>VLED</sub> IS THE BYPASS CAPACITOR.

Figure 28. LED Driver Output Pair

327

The LED driver output pins (LED1A, LED1B, LED2A, and LED2B) have a maximum allowable pin voltage of 3.6 V. Any voltage exposure over this rating affects the reliability of the device operation and, in certain circumstances, causes the device to cease proper operation. The voltage of the LED driver output pins must not be confused with the supply voltages of the LEDs.  $V_{\text{LEDx}}$  is the voltage applied to the anode of the external LED, whereas the LED output driver pin is connected to the cathode of the external LED. The compliance voltage is the amount of headroom voltage at the LED driver pin, measured with respect to ground, required to maintain the programmed LED current level. The compliance voltage is a function of the current required.

## **ECG SIGNAL CHAIN**

The ECG channel measures the differential voltage across two electrodes to create a lead measurement. The output of this channel is a 24-bit digital word representing the measured ECG voltage. The maximum input differential signal is ±1.2 V, and the LSB size is 286 nV. The output data rate can be 250 SPS, 500 SPS, 1 kSPS, 2 kSPS, or 4 kSPS. This filter selection affects the digital processing but not the analog processing. Additionally, a 4 kHz ac lead off signal is converted by the analog ECG path and extracted in the digital domain.

The ECG channel has a dedicated ADC path with feedback arrangement to remove the dc offset presented by the ECG electrodes. The ECG channel is designed to provide a high quality ECG signal process while suppressing the large dc offset that is caused by the complex system design.

Both DCLO detection and ACLO detection are integrated to accommodate different complex lead contact conditions to provide reliable lead information.

The RLD pin is designed to better bias the human body potential to avoid interference.

ECGIP and ECGIN are the signal inputs for the ECG channel, and they must be connected to the input leads. The RLD pin must be connected to the reference lead.

analog.com Rev. 0 | 18 of 89

#### THEORY OF OPERATION

## **ECG Main Signal Chain**

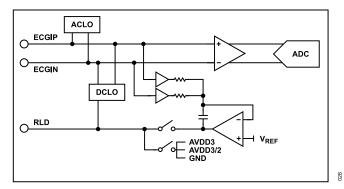

Figure 29 shows the ECG main signal chain diagram.

Figure 29. ECG Main Signal Chain Diagram

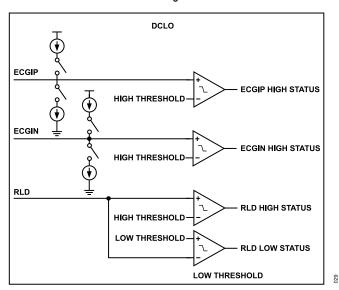

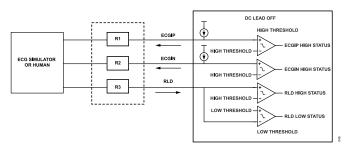

#### **DCLO Detection**

The DCLO circuit injects a small programmable dc current into each input electrode and monitors the resulting electrode voltage. Figure 30 shows the DCLO detection diagram.

Figure 30. DCLO Detection Diagram

When both ECGIP and ECGIN, are properly connected, the current flow from one of the ECG inputs through the patient and into the other ECG input produces a minimal voltage shift. The fail current magnitude is common across all the ECG electrodes and programmable with a step size of 2 nA over a ±16 nA range using the ECG\_DCLO\_MAG bit field to change the magnitude.

The polarity of the fail current is independent for each electrode and programmed using ECG\_DCLO\_POLARITY\_IN and ECG\_DCLO\_POLARITY\_IP. When an electrode connection degrades or falls off, the pin voltage of that electrode is pulled high or low depending on the programmed fail current polarity.

The DCLO detection circuit is based on each individual electrode input (ECGIP and ECGIN). The detection circuit is comparator based with independent programmable threshold levels for ECG inputs.

For each input lead (ECGIP and ECGIN), there is only one comparator with a high-side threshold. For the RLD pin, there are two comparators with a high-side threshold and low-side threshold.

These threshold limits are chosen such that all the threshold voltages cover the expected signal range. The window comparator compares the electrode input voltage with the corresponding threshold voltages. Where the voltage change on a particular electrode exceeds one of the programmed threshold voltages for that fail current, the dc resistance of the electrode contact can be determined to flag a lead off.

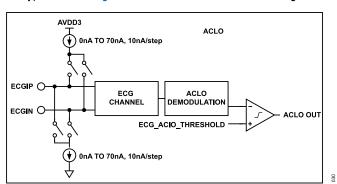

#### **ACLO Detection**

The ECG path has an ACLO detection circuit that can be used for lead off detection with the DCLO detection circuit to deal with different types of lead. Figure 31 shows the ACLO detection diagram.

Figure 31. ACLO Detection Diagram

The ACLO method of sensing if the electrodes are connected to the patient is based on injecting ac currents into each ECG electrode and measuring the amplitudes of the resulting voltages through the ECG channel. The ECG channel must be enabled to use the ACLO function.

The magnitude of the ACLO current is programmable through the ECG\_ACLO\_MAG bit field. The ac current is driven out onto the ECG input paths and establishes a voltage between the ECG channel inputs where it is measured. The measured voltage is synchronously demodulated and sent through a comparator. The user can set the threshold though the ECG\_ACLO\_THRESHOLD bit field.

ACLO detection functions only on the ECG input pins (ECGIP and ECGIN) and is not supported for the RLD pin. A properly connected electrode has a small signal because the drive current flows into the right leg (RL). An improperly connected or dried out electrode has a larger signal as determined by a capacitive voltage divider.

analog.com Rev. 0 | 19 of 89

#### THEORY OF OPERATION

## **Right Leg Driver**

The use of a driven reference benefits overall performance by improving common-mode rejection of noise and interference from external sources, such as power line interference (50 Hz/60 Hz) or other patient connected instruments. The drive stage also acts to absorb lead fail currents injected into the ECG electrodes.

The reference electrode drive circuit senses the patient common-mode voltage and drives an inverted version back to the body, creating a negative feedback loop around the patient. The RLD amplifier uses  $V_{CM}$  = AVDD3/2, which centers the electrode voltages in the middle of the ADC input range. Each electrode input is buffered and fed to the RLD amplifier through a switch.

The amount of capacitance on the RLD pin affects the RLD amplifier. For best performance, the capacitance on this node must be less than 2.2 nF. In normal operation, the RLD amplifier output is applied to the RL electrode via the RLD pin and associated protection network.

The RLD amplifier can be turned off and the user can drive the RLD pin by selecting a voltage in the ECG RLD OUT SEL bit field.

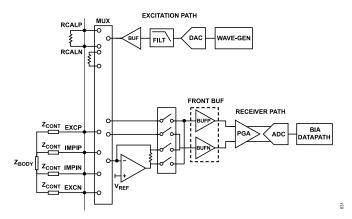

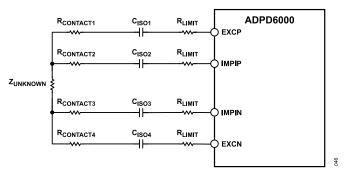

#### **BIA SIGNAL CHAIN**

The BIA signal chain is designed for body impedance measurement. The signal chain consists of a high frequency precision excitation loop and a measurement channel, which enables a wide capability of measurement of the different bioimpedance configurations.

The excitation loop consists of a 12-bit DAC, referred to as the high speed DAC. This DAC is capable of generating high frequency excitation signals up to 250 kHz.

The measurement channel features an ADC with input buffers, a built in antialias filter, and a PGA.

An ultralow leakage, programmable switch matrix connects the sensor to the internal analog excitation and measurement blocks. This matrix provides an interface for connecting external bioimpedance and calibration resistors. Figure 32 shows the block diagram of this BIA signal chain.

Figure 32. BIA Channel Block Diagram ( $Z_{CONT}$  Is Contact Impedance and  $Z_{BODY}$  Is Human Body Impedance)

The input multiplexer (mux) of the excitation loop is controlled by the BIOZ\_TSW\_x, BIOZ\_TRSW\_x, BIOZ\_DSW\_x, BIOZ\_DRSW\_x. The input mux for the measurement path is controlled by the BIOZ\_NCHAN\_x and BIOZ\_PCHAN\_x. Table 10 shows the connections of the input mux with the related bit setting. The flexible design of the BIA channel allows different configurations of the measurement.

Table 10. TIA Connections in the BIA Channel

| Bit Name              | Setting | Connection            |

|-----------------------|---------|-----------------------|

| BIOZ_TSW_x            | 0001    | IMPIP                 |

|                       | 0010    | IMPIN                 |

|                       | 0100    | EXCP                  |

|                       | 1000    | EXCN                  |

| BIOZ_TRSW_x           | 1       | RCALN                 |

| BIOZ_RINT_SW_x, Bit 1 | 1       | R <sub>INT SN</sub> 1 |

| BIOZ_DSW_x            | 0001    | IMPIP                 |

|                       | 0010    | IMPIN                 |

|                       | 0100    | EXCP                  |

|                       | 1000    | EXCN                  |

| BIOZ_DRSW_x           | 1       | RCALP                 |

| BIOZ_RINT_SW_x, Bit 0 | 1       | R <sub>INT SP</sub> 1 |

| BIOZ_PCHAN_x and      | 00      | TIA                   |

| BIOZ_NCHAN_x          | 01      | IMPIP and IMPIN       |

|                       | 10      | RCALN and RCALP       |

|                       | 11      | R <sub>INT</sub>      |

<sup>&</sup>lt;sup>1</sup> R<sub>INT SN</sub> and R<sub>INT SP</sub> refer to the two terminals of the internal resistor (R<sub>INT</sub>).

The frequency of the generated sine wave is controlled by BI-OZ\_SINEFCW\_x\_x, whereas the amplitude of the sine wave is controlled by BIOZ\_SINEAMPLITUDE\_x. BIOZ\_SINE\_PHASE\_OFF-SET\_x is used to control the sine wave phase.

Equation 2 and Equation 3 show how to set the voltage output (V<sub>OUT</sub>) amplitude and sine wave frequency with these bits, respectively, as follows:

analog.com Rev. 0 | 20 of 89

#### THEORY OF OPERATION

$$V_{OUT} = 0.8 \times \frac{BIOZ\_SINEAMPLITUDE\_x}{2^{11}} Vp - p$$

(2)

$$Frequency = \frac{32M \times BIOZ\_SINEFCW\_x\_x}{2^{26}}Hz$$

(3)

BIOZ\_DAC\_GAIN\_x and BIOZ\_DAC\_OFFSET\_x are used to give more flexible control of the generated sine wave for different applications.

The TIA gain can be accessed through BIOZ\_TIA\_RGAIN\_x.

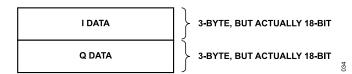

After digitizing the measurement, the ADC output is sent to the datapath of the BIA channel, which includes filters, gain controls, and the DFT path (see the Datapath section for more information). The DFT result is I data and Q data of the received sine wave, and the data format is 18 bits.

When the chain turns on, the DFT path can wait before performing the DFT. The waiting time is controlled by BI-OZ ADC CONV DLY x.

For accurate measurement, the chip must perform ratio measurement. That is, the chip needs to measure the known external resistor at the RCALP and RCALN pins, and then measure the unknown resistor. Use the ratio method to calculate the resistor under test.

#### **FIFO**

The FIFO is never written with partial packets of data. If there is not enough room for the data that is written to the FIFO for all enabled time slots and any selected status bytes, no data is written from any of the time slots during that period and the INT\_FIFO\_OFLOW status bit is set.

The order of samples written to the FIFO (if selected) is dark followed by lit data. Table 11 shows the byte order for multibyte words.

Table 11. Byte Order for FIFO Writes

|      | 7                               |

|------|---------------------------------|

| Size | Byte Order (After Shift)        |

| 8    | [7:0]                           |

| 16   | [15:8], [7:0]                   |

| 24   | [23:16], [15:8], [7:0]          |

| 32   | [31:24], [23:16], [15:8], [7:0] |

The FIFO size is 640 bytes. When the FIFO is empty, a read operation returns 0xFF and the INT FIFO UFLOW status bit is set.

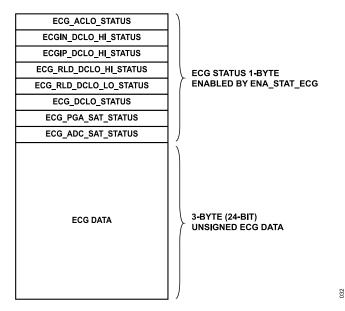

#### **ECG Data Format**

The data in the ECG is channel is 24-bit unsigned data with a status byte as a header. Figure 33 shows the data in the ECG channel.

Figure 33. ECG Data Format

If ENA\_STAT\_ECG is set to 1, the ECG output data is a 4-byte structure, where the highest byte is the ECG related status information. If ENA\_STAT\_ECG is set to 0, the ECG output data is a 3-byte structure with only ECG channel output data.

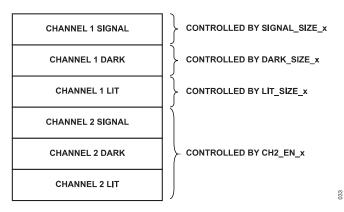

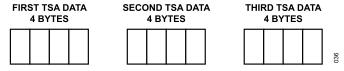

## **PPG Data Format**