### Circuit Note CN-0243

# **Circuits** from the **Lab**™ Reference Circuits

Circuits from the Lab™ reference circuits are engineered and tested for quick and easy system integration to help solve today's analog, mixed-signal, and RF design challenges. For more information and/or support, visit www.analog.com/CN0243.

| Devices Connected/Referenced                         |                                                                                                               |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| ADRF6702                                             | 1200 MHz to 2400 MHz Quadrature<br>Modulator with 1550 MHz to 2150 MHz<br>Fractional-N PLL and Integrated VCO |

| AD9122                                               | Dual, 16-Bit, 1230 MSPS, TxDAC®                                                                               |

| AD9516-0/AD9516-1/<br>AD9516-2/AD9516-3/<br>AD9516-4 | Clock Generator with Integrated VCO<br>with Various Frequency Range Options<br>from 1.45 GHz to 2.95 GHz      |

# High Dynamic Range RF Transmitter Signal Chain Using Single External Frequency Reference for DAC Sample Clock and IQ Modulator LO Generation

#### **EVALUATION AND DESIGN SUPPORT**

**Circuit Evaluation Boards**

**CN-0243 Circuit Evaluation Board (EVAL-CN0243-EB1Z)**

**Design and Integration Files**

**Schematics, Layout Files, Bill of Materials**

#### CIRCUIT FUNCTION AND BENEFITS

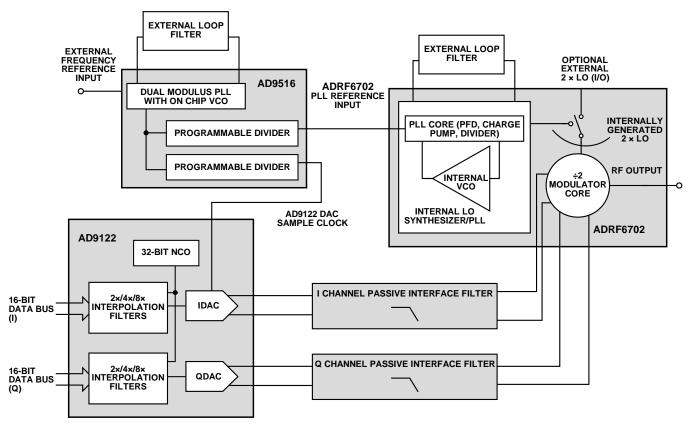

The combination of the ADRF6702 IQ modulator and the AD9122 16-bit dual 1.2 GSPS TxDAC has the dynamic range necessary for a modern high level QAM or OFDM based wireless transmitter as shown in Figure 1. The dynamic range

Figure 1. AD9122, ADRF6702, and AD9516 Used in a High Dynamic Range Transmitter

#### Rev.0

Circuits from the Lab™ circuits from Analog Devices have been designed and built by Analog Devices engineers. Standard engineering practices have been employed in the design and construction of each circuit, and their function and performance have been tested and verified in a lab environment at room temperature. However, you are solely responsible for testing the circuit and determining its suitability and applicability for your use and application. Accordingly, in no event shall Analog Devices be liable for direct, indirect, special, incidental, consequential or punitive damages due to any cause whatsoever connected to the use of any Circuits from the Lab circuits. (Continued on last page)

of this circuit is good enough to enable both ZIF (zero IF/baseband) and CIF (complex IF up to 200 MHz to 300 MHz). The AD9122 has the option of up to  $8\times$  interpolation, as well as a 32-bit NCO for very fine IF frequency selectivity.

Overall performance of a transmitter is highly dependent on the dynamic range of the components directly in the signal chain. In a mixed-signal transmitter using a DAC and IQ modulator, the noise floor and distortion characteristics of these components define the overall dynamic range of the signal chain. However, the noise floor of the DAC can also be degraded by sample clock jitter, and the IQ modulator performance is dependent on the noise and spur characteristics of its local oscillator (LO). Using high performance components for sample clock and LO generation is, therefore, key to a high performance transmitter.

In addition, generating these signals physically close to the DAC and modulator on the PCB and using a single external reference can make the design much simpler. Generating the sample clock and LO (LO is very often a multi-GHz signal) separately and at some distance from the DAC and IQ modulator requires great care in the PCB layout. Subtle layout errors can cause coupling to and from these critical signals and degrade overall signal chain performance.

The signal chain performance is also heavily dependent on the DAC/ IQ modulator interface filter. For optimal performance, this passive filter should be designed after careful analysis of the required system specifications.

The ADRF6702 includes an on-board fractional PLL for LO generation so that a low frequency reference (typically less than 100 MHz) is all that is necessary to synthesize the IQ modulator LO. Using the PLL in the AD9516 clock generator allows a single reference to generate both the DAC sample clock and the PLL reference for the ADRF6702.

The circuit in Figure 1 was built using the AD9516-0, but other members of the AD9516 family could be used depending on the desired internal VCO frequency.

#### CIRCUIT DESCRIPTION

## ADRF6702 IQ Modulator with Internal LO Synthesizer, Synthesizer IQ Modulator Interface

The ADRF6702 IQ modulator is a unique device in several respects. In addition to its exceptional dynamic range, it also includes a fractional-N PLL, which allows programming of discrete LO frequency steps of less than 25 kHz while at the same time keeping the overall frequency multiplication small enough to avoid a large increase in phase noise from the reference to the synthesizer output.

Another aspect of the ADRF6702 is the divide-by-2 architecture of the IQ modulator. Traditional IQ modulators accept an LO input frequency at 1× the desired LO. Internally, a distributed RC network creates the desired in-phase and quadrature LO signals from the single LO frequency input. Because this is a passive RC network, the bandwidth over which quadrature modulation accuracy is achieved is limited. Also, for good quadrature accuracy, the external LO should be spectrally pure. Harmonics on the LO with this traditional IQ modulator architecture can degrade the overall modulation accuracy. For this reason, when using a PLL synthesizer to generate an LO signal for an IQ modulator, a sharp band-pass or low-pass filter is often required at the IQ modulator LO input.

In the divide-by-2 LO architecture of the ADRF6702, a simple digital divider is used internally to create nearly perfect quadrature over a wide band. The PLL synthesizer generates the  $2\times$  LO internally, so that it does not have to be distributed around the PCB, and no filter is required between the synthesizer and IQ modulator LO because the  $2\times$  LO architecture is only sensitive to the edges of the LO signal, not the frequency content. For a detailed descripton of the effects of LO harmonics on a  $1\times$  IQ modulator and the design of the LO filter, see Circuit Note CN-0134.

#### Sampled Signal to RF, Overall Spur Floor

A baseband signal goes through a number of steps on the way to the RF transmit frequency. The signal begins in the discrete

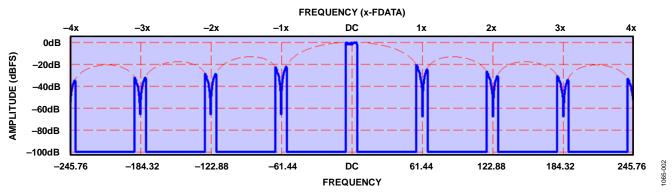

Figure 2. DAC Output Spectrum, Solid Blue Line Represents Baseband Signal and Images, Dotted Red Line Represents DAC Sinc Function

Circuit Note CN-0243

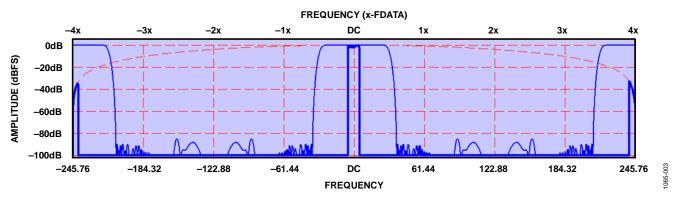

Figure 3. DAC Output Spectrum Using  $4 \times$  Interpolation, the Thin Blue Line Represents the DAC Interpolation Transfer Function

(sampled) domain and is synthesized by the DAC into the analog domain. The results of this step are images and distortion products generated by the DAC. As shown in Figure 2, an ideal DAC with no distortion will generate images of a baseband signal that must be filtered before being modulated. The use of interpolation filters such as those in the AD9122 can suppress most of the image energy, but an analog interface filter between DAC and modulator will still be necessary. There is a trade-off, however, between the order of the DAC interpolation and the order of the analog filter. Higher DAC interpolation rates mean lower required analog filter order and vice versa. Figure 3 shows what the DAC output spectrum looks like when using 4× interpolation, as an example.

#### A Multitude of Spurious Components at RF

The signal chain can add significant spurious components to the spectrum, due both to modulation products, distortion products, and integer multiples of the LO frequency. It we take into account all of the possibilities for spurious which we have discussed, the spurious content can consist of

$$(j \times LO\_freq) + (k \times DAC\_sample\_rate) + (l \times DAC\_NCO\_freq) + (m \times DAC\_input\_IF)$$

Where j, k, l, and m are integers over the range of negative infinity to positive infinity.

#### **DAC/Modulator Passive Interface Filter**

The key to reducing the overall spurious spectrum is the analog interface filter between the DAC and the IQ modulator. The design of the interface filter between the DAC and IQ modulator must take into account multiple aspects of performance:

- 1. Filter topology, order, and 3 dB cutoff frequency

- 2. At dc, the DAC sees a load impedance equal to the DAC termination resistors (typically a 100  $\Omega$  differential impedance) in parallel with the input impedance of the IQ modulator. The IQ modulator impedance is often >1k $\Omega$ , so a shunt resistor is often used across the IQ modulator inputs to create a similar load impedance to the source. Unequal filter source

- and load impedances, as well as parasitics in the signal traces, may add unwanted ripple in the filter pass band.

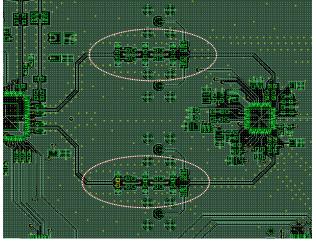

- 3. PCB layout. As shown in Figure 4, the I and Q baseband inputs on the ADRF6702 IQ modulator are located on opposite edges of the device. Note the filter layout area within the dotted circles. To route the DAC output signals to these pins, the traces must travel up and then back down to get to the baseband pins on the ADRF6702. These differential signal traces should be of equal length, and any changes in direction of the trace should be done by using 45° bends. If these recommendations are not implemented, in-band ripple, phase, or amplitude response may be degraded in the filter response. Note that with this filter topology, the capacitors can be used differentially (across the signal path) or they can be used in a common-mode connection by placing the filter caps from the signal path pads to ground pads. There are conditions (discussed later in this circuit note) where common-mode capacitors improve performance vs. differential-mode capacitors.

Figure 4. PCB Layout for Transmitter, DAC/Mod Interface Filter Section

10165-004

4. To achieve optimal performance from the filter, these traces should be 100  $\Omega$  differential, or 50  $\Omega$  per line. Note that with typical FR4 material, a 50  $\Omega$  line results from a T/W ratio of 2:1.

If higher impedance lines are desired it should be understood that the impedance of the line is a nonlinear function of T/W (T = board layer thickness, W = width of trace). A thinner line results in a higher impedance line. With typical FR4 layer thicknesses, a 100  $\Omega$  line can get very thin, often close to minimum design constraints. One solution to this is to void the ground layer underneath the trace and put another ground layer on the third layer of the PCB. This effectively doubles T and allows for a wider trace.

#### DAC\_MOD Interface Filter Topology

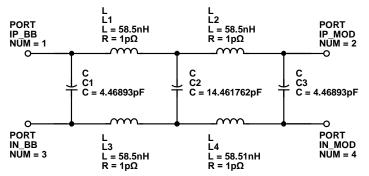

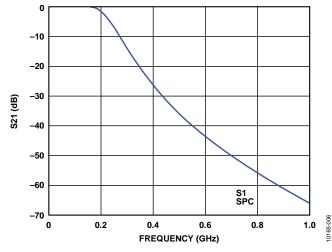

Figure 5 shows a typical topology which gives a 5<sup>th</sup> order maximally flat Butterworth response for a differential input and output impedance of 100  $\Omega$ .. The actual response is given in Figure 6. This filter uses 4.6 pF capacitors at the source and load.

This magnitude of capacitor value (<20 pF) is typical of filters with high cutoff frequencies. Parasitics may have a significant effect on response when using these small capacitor values.

Figure 5. DAC/Mod Interface Filter Topology, 5th Order Butterworth, 3 dB BW = 220 MHz,  $100 \Omega$  Differential Input and Output Impedance

Figure 6. Frequency Response of Filter Topology Given in Figure 5

#### **DAC and Distortion Related Spurious Components**

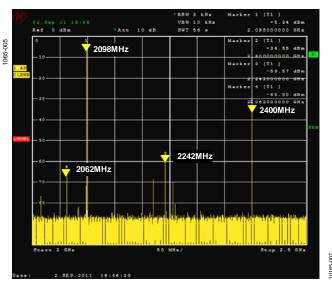

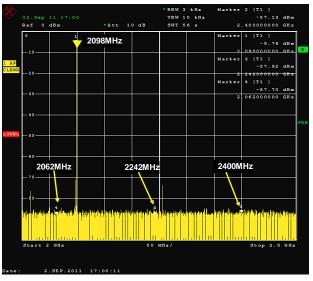

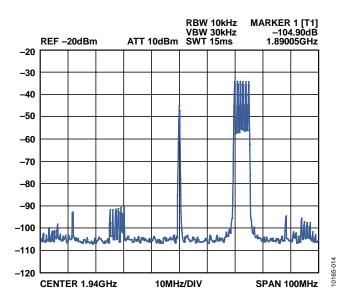

The use of DAC interpolation filters by themselves can reduce the spurious content at the modulator input and, therefore, the spurious content at RF. However, there may still be significant spurious content. Figure 7 shows the RF output spectrum of the IQ modulator under the following conditions;

FLO = 1940 MHz

DAC input data rate = 300 MSPS

*DAC interpolation* =  $4 \times$

$DAC\ NCO\ frequency = 150\ MHz$

DAC input IF frequency = 8 MHz

Note that the strongest spurious component (aside from the fundamental at 2098 MHz) is the 2× component of the DAC clock at 2400 MHz. This is likely a result of common and differential mode components of the DAC output containing some spectrum from the DAC clock. The common-mode rejection of the IQ modulator input rejects much of this signal, but it is still contains significant energy. The next two highest spurs, at 2062 MHz and at 2242 MHz, also seem to be related to DAC clock spurs. The spur at 2242 MHz is easily recognized as  $2 \times (\text{DAC clock} - \text{DAC fundamental}) = 2400 - 158$ . The spur at 2062 MHz is not so obvious, but looks like  $(3 \times \text{LO}) - (3 \times \text{DAC clock}) - 158 = 5820 - 3600 - 158$ . If the analysis is correct, then we should be able to see significant spur reduction if we can suppress the common-mode component of the DAC clock at the IQ modulator inputs.

Figure 7. IQ Modulator RF Output with DAC/IQ Mod Filter Absent, LO = 1940 MHz, DAC Input IF = 8 MHz, DAC NCO = 150 MHz, RF = 2098 MHz

Circuit Note CN-0243

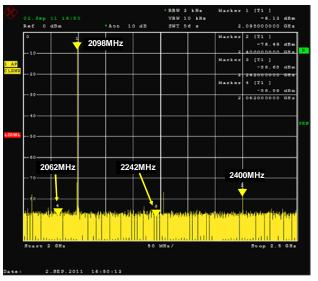

Applying the differential Butterworth filter gives significant spur level reduction, as shown in Figure 8. The strongest spurs are still at 2062 MHz, 2242 MHz, and the  $2\times$  DAC clock spur at 2400 MHz. All three spurious components have been reduced significantly.

Figure 8. RF Spectrum Using 5th Order Butterworth Filter, Differential

Capacitors

The common-mode rejection of the DAC/IQ modulator interface can often be improved by changing the topology of the interface filter. In Figure 9, the input and output 4.7 pF caps are replaced by common-mode capacitors (9.0 pF) from both sides of the filter input and both sides of the filter output to ground. This does not change the overall differential filter mode response but does have an effect on this board on the overall spurious content at RF. The harmonics mentioned earlier at

Figure 9. RF Spectrum Using 5th Order Butterworth Filter, Combination of Differential and Common-Mode Capacitors Used in the DAC\_Mod Filter

2062 MHz and 2242 MHz are down a few dB more, and there has been about a 15 dB reduction in the  $2\times$  DAC clock component, nearly to the noise floor.

The topology and results shown here may vary from layout to layout, so it is always to the advantage of the designer to experiment with the layout of the filter, specifically which mix of differential and common-mode capacitors results in the lowest overall spur floor.

#### Synthesizer Path and PLL Phase Noise

As shown in Figure 1, this circuit uses a single external reference to generate the AD9122 DAC sample clock and the reference clock for the PLL in the ADRF6702. The AD9516 is fundamental in providing the flexibility to do this. The AD9516 contains a PLL and integrated VCO. It also contains a number of outputs that can be programmed for differential LVPECL, LVDS, or single-ended CMOS, with independent divider settings for each output path. In this circuit, one of these output paths is used for the DAC clock and another output is used for the reference input of the fractional-N PLL in the ADRF6702.

The advantage of using a fractional PLL in the ADRF6702 is twofold. First, the fractional PLL allows very fine tuning of the output LO. As an example, with an input frequency of 38.4 MHz and a programmed MOD value in the ADRF6702 of 1536, the LO can be programmed in increments of 25 kHz. The second advantage is that the reference frequency does not have to be equal to LO freq/divider ratio, but can be much higher, leading to a lower divider ratio. Because the output phase noise is a function of the reference phase noise multiplied by the divider ratio, this means inherently lower phase noise at RF.

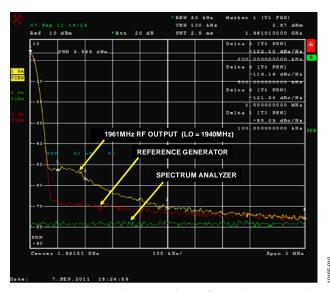

One of the key metrics in a synthesizer system is the amount of phase noise added by the individual PLL and dividers. Figure 10 shows the noise floor of the spectrum analyzer doing the measurement (green trace), the phase noise of the reference generator (red), and the phase noise of an output tone at an RF frequency of 1961 MHz with an LO of 1940 MHz (yellow). The combination of the PLL in the AD9516 and the ADRF6702 does generate noticeably high close-in phase noise (less than 500 kHz offset from carrier) but does not contribute significant wideband noise to the system. The loop filters for the VCOs in both the AD9516 and ADRF6702 are set to bandwidths of ~100 kHz in the measurement circuit. Close-in phase noise may be reduced by lowering the bandwidth of these loop filters. System specifications should be reviewed to determine how much close-in phase noise can be tolerated for a given system.

Figure 10. Spectrum Analyzer Noise Floor, Reference Phase Noise, and RF Output Phase Noise

#### **COMMON VARIATIONS**

As described in the last section, PLL performance can be adjusted by varying the bandwidth of the loop filters. There is a trade-off between loop filter bandwidth and frequency settling time that must be taken into account. If a DAC such as the AD9122 is used, the DAC NCO can also be used for fine frequency hopping, although there is a limit to the hopping speed since the NCO requires programming via an SPI port. Newer clock synthesis and distribution devices such as the AD9520 and AD9523 may provide improvements in phase noise.

#### **CIRCUIT EVALUATION AND TEST**

The EVAL-CN0243-EB1Z evaluation board requires the following equipment and software for signal generation and basic measurement:

#### **Equipment Needed**

- 5 V power supply

- Low phase noise reference source (10 MHz to 200 MHz range @ +3 dBm), Rohde & Schwarz SMA100, low noise option, or equivalent

- DPG2 Digital Pattern Generator from Analog Devices

- High dynamic range spectrum analyzer, Agilent E4440A or equivalent

- Analog Devices EVAL-ADF4XXXZ USB Adapter

#### Software

- DPG2 Software (included with DPG)

- ADRF6702 software available at www.analog.com/ADRF6702

Figure 11. EVAL-CN0243-EB1Z Evaluation Board

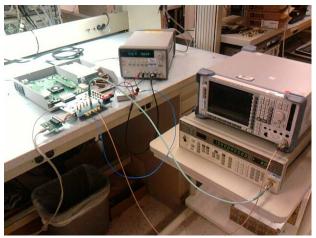

Figure 12. Bench Test Setup

#### Setup and Test

The following steps are required to properly run the EVAL-CN0243-EB1Z evaluation board:

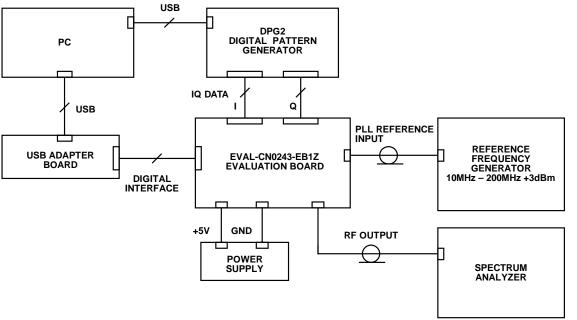

- 1. Before powering up, connect all instruments, USB adapters, and cables, as shown in Figure 13.

- There is only a single 5 V power supply required. This should be connected to the female banana plugs on the EVAL-CN0243-EB1Z board. Make sure this supply is connected, then turn on the +5 V supply. The total current at this point should be 850 mA to 900 mA.

- 3. The DPG2 software contains a GUI to program the AD9122. Program the AD9122 for the correct interpolations rate and NCO (if desired).

- 4. Turn on the DPG2 software itself. If all cables and software are working correctly, the software should recognize the DAC input data rate and display it in the lower right hand corner of the DPG GUI. Note that this

Circuit Note CN-0243

Figure 13. Test Setup Functional Block Diagram

data rate should be equal to the DAC sample rate (614.4 MSPS) in Figure 13 divided by the programmed interpolation rate of the AD9122.

- 5. Note that as the various devices are activated and programmed, the current will increase. At the end of this exercise, the current should be between 1.4 A and 1.5 A, depending on DAC sample rate.

- 6. Use the DPG2 software to create a waveform (single, multi tone, or comms standard signals are available). A digital back-off of -8 dB should be used initially to optimize linearity of the DAC/ADRF6702 combination. Complex signal generation should also be selected in the DPG2 GUI. When the waveform is created, use the "load" and "play" buttons in the GUI to load the digital pattern into the DPG memory itself.

- 7. Start the ADRF6702 GUI. To begin with, the only options in the ADRF6702 GUI which need to be selected are the input reference frequency and LO output frequency. To program these values, click the reference input frequency or the LO output values in the top center of the ADRF6702 GUI. Another window will appear which will allow you to enter these values. Important: After entering these values, the user must finish with a carriage return to make sure that the values are entered into the GUI.

- 8. Programming the ADRF6702 is the last step in setting up the EVAL-CN0243-EB1Z evaluation board. As an example, if the DPG2 generates a series of tones (20 MHz

to 25 MHz with 1 MHz spacing) @-8 dB back-off, and the LO of the ADRF6702 is programmed to 1940 MHz, the spectrum should look very similar to that shown in Figure 14.

Figure 14. Spectrum of Complex Multitone Signal at LO Frequency of 1940 MHz at ADRF6702 RF Output, Desired Sideband Offset: +20 MHz, Undesired Sideband Offset: -20 MHz

#### **LEARN MORE**

CN-0243 Design Support Package: www.analog.com/CN0243-DesignSupport

DPG2 Digital Pattern Generator: www.analog.com/DPG\_DAC\_Eval\_Platfform

ADIsimPLL Design Tool

ADIsimRF Design Tool

#### **Data Sheets and Evaluation Boards**

ADRF6702 Data Sheet

ADRF6702 Evaluation Board

AD9122 Data Sheet

AD9122 Evaluation Board

AD9516-0 Data Sheet

AD9516-0 Evaluation Board

AD9516-1 Data Sheet

AD9516-1 Evaluation Board

AD9516-2 Data Sheet

AD9516-2 Evaluation Board

AD9516-3 Data Sheet

AD9516-3 Evaluation Board

AD9516-4 Data Sheet

AD9516-4 Evaluation Board

#### **REVISION HISTORY**

10/11—Revision 0: Initial Version

(Continued from first page) Circuits from the Lab circuits are intended only for use with Analog Devices products and are the intellectual property of Analog Devices or its licensors. While you may use the Circuits from the Lab circuits in the design of your product, no other license is granted by implication or otherwise under any patents or other intellectual property by application or use of the Circuits from the Lab circuits. Information furnished by Analog Devices is believed to be accurate and reliable. However, "Circuits from the Lab" are supplied "as is" and without warranties of any kind, express, implied, or statutory including, but not limited to, any implied warranty of merchantability, noninfringement or fitness for a particular purpose and no responsibility is assumed by Analog Devices for their use, nor for any infringements of patents or other rights of third parties that may result from their use. Analog Devices reserves the right to change any Circuits from the Lab circuits at any time without notice but is under no obligation to do so.

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Audio DSPs category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below:

E-TDA7377A TDA7716N BR281W31A101V1G LC823425-12G1-LR-H TDA7419N R3910-CFAB-E1B HMC474MP86ETR

AMIS30660CANH6G B300W35A102XYG MAX9892ERT+T MAX9892ELTT SB3229-E1 NJW1157BFC2 ZL38060LDG1 SB3231-E1

HMC1022-SX SA3229-E1-T LC75056PE-H TDA7729 NJW1195AV WM5102ECS/R CI1103 WM5102ECS/R 100-CG1820 CS48L10-CNZ CS48L10-CNZR CS47024C-CQZ CS48L10-CWZR CS48L11-CNZ HMC618LP3ETR HMC604LP3ETR HMC5622LS7TR

HMC288MS8ETR HMC240A STA323W13TR BU9408KS2 DSPB56725AF TAS3204PAGR ADAU1467WBCPZ300

ADAU1463WBCPZ300 BD37514FS-E2 ADAU1463WBCPZ150 ADAU1466WBCPZ300 NJM2294V-TE1 LC823450TA-2H NJM2537V-TE1 TWL1103TPBSQ1 LC823450XDTBG HMC-AUH312-SX ADAV4622BSTZ