## LT4294

## IEEE 802.3bt PD Interface Controller

## FEATURES

- IEEE 802.3af/at/bt Powered Device (PD) Controller

- Supports Up to 71.3W PDs

- 5-Event Classification Sensing

- Superior Surge Protection (100V Absolute Maximum)

- Wide Junction Temperature Range (-40°C to 125°C)

- Overtemperature Protection

- Integrated Signature Resistor

- External Hot Swap N-Channel MOSFET for Lowest Power Dissipation and Highest System Efficiency

- Configurable Aux Power Support as Low as 9V

- Easy Migration Between LTPoE++® PDs and IEEE 802.3bt PDs

- Pin Compatible with LT4275A/B/C

- Available in 10-Lead MSOP and 3mm × 3mm DFN Packages

## **APPLICATIONS**

High Power Wireless Data Systems

TYPICAL APPLICATION

- Outdoor Security Camera Equipment

- Commercial and Public Information Displays

- High Temperature Industrial Applications

## DESCRIPTION

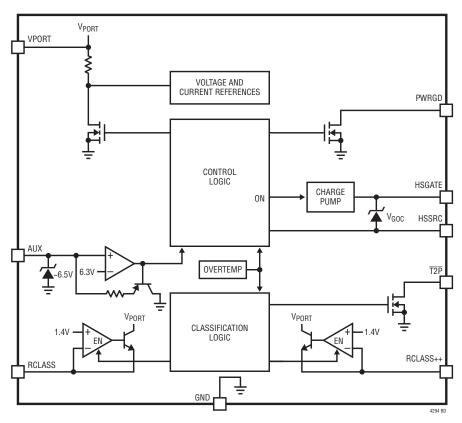

The LT®4294 is an IEEE 802.3af/at/bt-compliant powered device (PD) interface controller. The T2P output indicates the number of classification events received during IEEE 802.3bt-compliant mutual identification and negotiation of available power.

The LT4294 utilizes an external, low  $R_{DS(ON)}$  N-channel hot swap MOSFET and supports the LT4320/LT4321 ideal diode bridges, to extend the end-to-end power delivery efficiency and eliminate costly heat sinks. The LT4294 also includes a power good output, onboard signature resistor, undervoltage lockout, and thermal protection. Start-up inrush current is adjustable with an external capacitor. Auxiliary power override is supported as low as 9V with the AUX pin.

The LT4294 can be configured to support all possible 802.3bt, 802.3at and 802.3af power levels with external component changes. Pin-for-pin compatibility with the LT4275 family of PD Interface Controllers enables easy migration between LTPoE++ PDs and IEEE 802.3bt-compliant PDs.

All registered trademarks and trademarks are the property of their respective owners.

#### IEEE 802.3bt Single-Signature Powered Device Interface V<sub>AUX</sub> (9V TO 60V) CPORT PSMN040-100MSE DATA CPD l₹T VPORT PAIR 0.10 VIN ISOLATED + SPARE POWER VPORT HSGATE PAIR HSSRC Vout SUPPLY AUX **PWRGD** RUN LT4294 RCLASS RCLASS++ PSE TYPE OPTO T2P (TO uP) GND **₹**R<sub>CLS<sup>++</sup></sub> Rcls Ŧ

|             | SINGLE-SIGNATURE<br>POWER CLASSIFICATION<br>(AT PD INPUT) |  |  |  |  |  |  |

|-------------|-----------------------------------------------------------|--|--|--|--|--|--|

| CLASS POWER |                                                           |  |  |  |  |  |  |

| 0           | 13W                                                       |  |  |  |  |  |  |

| 1           | 3.84W                                                     |  |  |  |  |  |  |

| 2           | 6.49W                                                     |  |  |  |  |  |  |

| 3           | 13W                                                       |  |  |  |  |  |  |

| 4           | 25.5W                                                     |  |  |  |  |  |  |

| 5           | 40W                                                       |  |  |  |  |  |  |

| 6           | 51W                                                       |  |  |  |  |  |  |

| 7 62W       |                                                           |  |  |  |  |  |  |

| 8           | 71.3W                                                     |  |  |  |  |  |  |

## **ABSOLUTE MAXIMUM RATINGS**

| VPORT, HSSRC Voltages | –0.3V to 100V                    |

|-----------------------|----------------------------------|

| HSGATE Current        | ±20mA                            |

| RCLASS, RCLASS++      |                                  |

| Voltages              | $-0.3V$ to 8V (and $\leq$ VPORT) |

| AUX Current           | ±1.4mÅ                           |

| T2P, PWRGD Voltage    | –0.3V to 100V                    |

| T2P, PWRGD Current    | 5mA                              |

| Operating Junction Temperature Range (Note 4) |  |

|-----------------------------------------------|--|

| LT42941–40°C to 85°C                          |  |

| LT4294H –40°C to 125°C                        |  |

| Storage Temperature Range65°C to 150°C        |  |

| Lead Temperature (Soldering, 10 sec.)         |  |

|                                               |  |

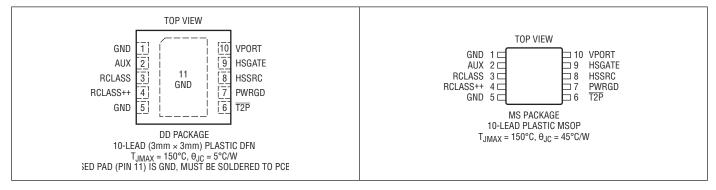

## PIN CONFIGURATION

## **ORDER INFORMATION**

| LEAD FREE FINISH | TAPE AND REEL   | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|-----------------|---------------|---------------------------------|-------------------|

| LT4294IDD#PBF    | LT4294IDD#TRPBF | LHBX          | 10-Lead (3mm × 3mm) Plastic DFN | –40°C to 85°C     |

| LT4294HDD#PBF    | LT4294HDD#TRPBF | LHBX          | 10-Lead (3mm × 3mm) Plastic DFN | -40°C to 125°C    |

| LT4294IMS#PBF    | LT4294IMS#TRPBF | LTHBW         | 10-Lead Plastic MSOP            | -40°C to 85°C     |

| LT4294HMS#PBF    | LT4294HMS#TRPBF | LTHBW         | 10-Lead Plastic MSOP            | -40°C to 125°C    |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

## **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 3)

| SYMBOL             | PARAMETER                     | CONDITIONS                                   |   | MIN  | ТҮР | MAX | UNITS |

|--------------------|-------------------------------|----------------------------------------------|---|------|-----|-----|-------|

|                    | VPORT Operating Input Voltage | At VPORT Pin                                 | ٠ |      |     | 60  | V     |

| V <sub>SIG</sub>   | VPORT Signature Range         | At VPORT Pin                                 | • | 1.5  |     | 10  | V     |

| V <sub>CLASS</sub> | VPORT Classification Range    | At VPORT Pin                                 | ٠ | 12.5 |     | 21  | V     |

| V <sub>MARK</sub>  | VPORT Mark Range              | At VPORT Pin, Preceded by V <sub>CLASS</sub> | ٠ | 5.6  |     | 10  | V     |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 3)

| SYMBOL             | PARAMETER                                                | CONDITIONS                                                                                     |   | MIN  | ТҮР      | MAX  | UNITS |

|--------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------|---|------|----------|------|-------|

|                    | VPORT Aux Mode Range                                     | At VPORT Pin, AUX > V <sub>AUXT</sub>                                                          | • | 8    |          | 60   | V     |

|                    | Signature/Class Hysteresis Window                        |                                                                                                | • | 1.0  |          |      | V     |

| V <sub>RESET</sub> | Reset Threshold                                          | At VPORT Pin, Preceded by V <sub>CLASS</sub>                                                   | • | 2.6  |          | 5.6  | V     |

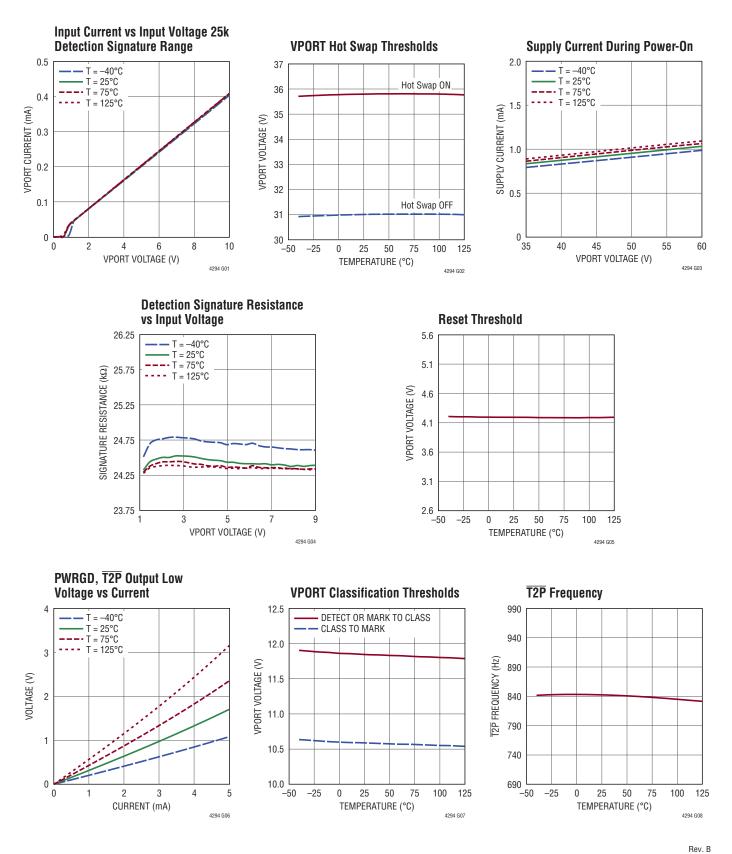

| V <sub>HSON</sub>  | Hot Swap Turn-On Voltage                                 |                                                                                                | • |      | 35       | 37   | V     |

| V <sub>HSOFF</sub> | Hot Swap Turn-Off Voltage                                |                                                                                                | ٠ | 30   | 31       |      | V     |

|                    | Hot Swap On/Off Hysteresis Window                        |                                                                                                | ٠ | 3    |          |      | V     |

| Supply Cu          | irrent                                                   |                                                                                                |   |      |          |      |       |

|                    | Supply Current                                           | V <sub>VPORT</sub> = V <sub>HSSRC</sub> = 57V                                                  | • |      |          | 2    | mA    |

|                    | Supply Current During Classification                     | V <sub>VPORT</sub> = 17.5V, RCLASS and RCLASS++ Open                                           | • | 0.4  | 0.7      | 0.9  | mA    |

|                    | Supply Current During Mark Event                         | V <sub>VPORT</sub> = V <sub>MARK</sub> After 1st Classification Event                          | ٠ | 0.5  |          | 2.2  | mA    |

| Detection          | and Classification Signature                             |                                                                                                |   |      |          |      |       |

|                    | Detection Signature Resistance                           | V <sub>SIG</sub> (Note 2)                                                                      | • | 23.7 | 24.4     | 25.2 | kΩ    |

|                    | Resistance During Mark Event                             | V <sub>MARK</sub> (Note 2)                                                                     | ٠ | 5.8  | 8.3      | 11   | kΩ    |

|                    | RCLASS/RCLASS++ Operating Voltage                        | $-10\text{mA} \ge I_{\text{RCLASS}} \ge -36\text{mA}, V_{\text{CLASS}}$                        | ٠ | 1.32 | 1.40     | 1.43 | V     |

|                    | Classification Signature Stability Time                  | V <sub>VPORT</sub> Step to 17.5V,<br>34.8Ω from RCLASS or RCLASS++ to GND                      | • |      |          | 2    | ms    |

| Analog/Di          | igital Interface                                         |                                                                                                |   |      |          |      |       |

| V <sub>AUXT</sub>  | AUX Threshold                                            |                                                                                                | • | 6.1  | 6.3      | 6.5  | V     |

| I <sub>AUXH</sub>  | AUX Pin Hysteresis Current                               | V <sub>AUX</sub> = 6.1V                                                                        | • | 3.2  | 5        | 7    | μA    |

|                    | T2P Output Low                                           | 1mA Load                                                                                       | • |      |          | 0.8  | V     |

|                    | PWRGD Output Low                                         | 1mA Load                                                                                       | ٠ |      |          | 0.8  | V     |

|                    | PWRGD Leakage Current                                    | V <sub>PWRGD</sub> = 60V                                                                       | • |      |          | 5    | μA    |

|                    | T2P Leakage Current                                      | T2P = 60V                                                                                      | ٠ |      |          | 5    | μA    |

| Hot Swap           | Control                                                  |                                                                                                |   |      |          |      |       |

| I <sub>GPU</sub>   | HSGATE Pull-Up Current                                   | V <sub>HSGATE</sub> – V <sub>HSSRC</sub> = 5V (Note 6)                                         | • | -27  | -22      | -18  | μA    |

| V <sub>GOC</sub>   | HSGATE Open Circuit Voltage                              | –10µA Load, with Respect to HSSRC                                                              | ٠ | 10   |          | 18   | V     |

|                    | HSGATE Pull-Down Current                                 | V <sub>HSGATE</sub> – V <sub>HSSRC</sub> = 5V                                                  | • | 200  |          |      | μA    |

| Timing             |                                                          |                                                                                                |   |      |          |      |       |

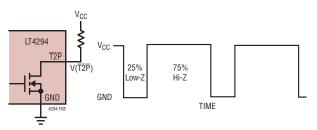

| f <sub>T2P</sub>   | T2P Frequency                                            | After PWRGD Valid, if IEEE802.3bt PSE Is Mutually Identified                                   | • | 690  | 840      | 990  | Hz    |

|                    | T2P Duty Cycle in PoE Operation (Note 5)                 | After 4-Event Classification<br>After 5-Event Classification<br>(RCLASS++ Has Resistor to GND) |   |      | 50<br>25 |      | %     |

|                    | T2P Duty Cycle in Auxiliary<br>Supply Operation (Note 5) | $V_{AUX} > V_{AUXT}$ , and RCLASS++ Has Resistor to GND                                        |   |      | 25       | -    | %     |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: Signature resistance specifications do not include resistance added by the external diode bridge which can add as much as 1.1k to the port resistance.

Note 3: All voltages with respect to GND unless otherwise noted. Positive currents are into pins; negative currents are out of pins unless otherwise noted.

Note 4: This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 150°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

Note 5: Specified as the percentage of the period which  $\overline{\text{T2P}}$  is low impedance with respect to GND.

Note 6: IGPU available in PoE powered operation. That is, available after  $V_{VPORT} > V_{HSON}$  and  $V_{AUX} < V_{AUXT}$ , over the range where  $V_{VPORT}$  is between V<sub>HSOFF</sub> and 60V.

## **TYPICAL PERFORMANCE CHARACTERISTICS**

## PIN FUNCTIONS

**GND (Pins 1, 5, DFN Exposed Pad Pin 11):** Device Ground. Exposed Pad must be electrically and thermally connected to pin 5 and PCB GND.

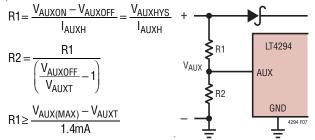

**AUX (Pin 2):** Auxiliary Sense. A resistive divider from the auxiliary power input to AUX sets the voltage at which the auxiliary supply takes over. In auxiliary power operation, HSGATE pulls down, the signature resistor disconnects, classification is disabled, the PWRGD pin is high impedance and T2P indicates max available power. The AUX pin sinks  $I_{AUXH}$  when below its threshold voltage of  $V_{AUXT}$  to provide hysteresis. Connect to GND when not used.

**RCLASS (Pin 3):** Configurable PoE Classification Resistor. See Table 2.

**RCLASS++ (Pin 4):** Configurable PoE Classification Resistor. See Table 2.

**T2P** (Pin 6): PSE Type Indicator, Open-Drain Output. See the T2P Output section for pin behavior.

**PWRGD (Pin 7):** Power Good Indicator, Open-Drain Output. Pulls to GND during  $V_{CLASS}$  and inrush.

**HSSRC (Pin 8):** External Hot Swap MOSFET Source. Connect to source of the external MOSFET.

**HSGATE (Pin 9):** External Hot Swap MOSFET Gate Control, Output. Connect to gate of the external MOSFET.

**VPORT (Pin 10):** PD interface upper power rail and external Hot Swap MOSFET drain connection.

## **BLOCK DIAGRAM**

#### **OVERVIEW**

Power over Ethernet (PoE) continues to gain popularity as products take advantage of DC power and high speed data available from a single RJ45 connector. Powered device (PD) equipment vendors are running into the 25.5W power limit established by the IEEE 802.3at standard.

The LT4294 is an IEEE 802.3bt-compliant PD interface controller, and allows up to 71.3W operation while maintaining backwards compatibility with existing PSE systems. The T2P output indicates the number of classification events received during IEEE 802.3bt-compliant mutual identification and negotiation of available power. The LT4294 controls a low  $R_{DS(ON)}$  N-channel MOSFET to maximize efficiency and delivered power.

Analog Devices also provides the LT4295, an IEEE 802.3btcompliant PD with an integrated switching regulator to service applications that require a more compact and integrated solution.

#### IEEE 802.3bt vs LTPoE++ Available Power

The LT4294 supports IEEE 802.3bt PD power levels up to 71.3W.

The LT4275 and LT4276 are available to support PD power levels up to 90W under the LTPoE++ standard. See the Related Parts section for a list of LTPoE++ products.

#### **MODES OF OPERATION**

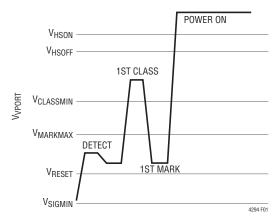

#### **Detection Signature**

During detection, the PSE looks for a 25k signature resistor which identifies the device as a PD. The PSE will apply two voltages in the range of 2.7V to 10.1V and measure the corresponding currents. Figure 1 shows the detection voltages. The PSE calculates the signature resistance using a  $\Delta V/\Delta I$  measurement technique.

The LT4294 presents its precision, temperature-compensated 24.4k resistor between the VPORT and GND pins, allowing the PSE to recognize a PD is present and requesting power to be applied. The LT4294 signature resistor is

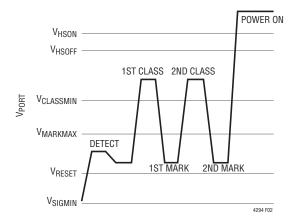

Figure 1. Type 3 or 4 PSE, 1-Event Class Sequence

smaller than 25k to compensate for the additional series resistance introduced by the IEEE required bridge or the LT4321-based ideal diode bridge.

#### IEEE 802.3bt Single-Signature vs Dual-Signature PDs

IEEE 802.3bt defines two PD topologies: single-signature and dual-signature. The LT4294 primarily targets singlesignature PD topologies, eliminating the need for a second PD controller. All PD descriptions and IEEE 802.3 standard references in this data sheet are limited in scope to singlesignature PDs.

The LT4294 may be deployed in dual-signature PD applications. For more information, contact Analog Devices Applications.

#### **Classification Signature and Mark**

The classification/mark process varies depending on the PSE type. A PSE, after a successful detection, may apply a classification probe voltage of 14.5V to 20.5V and measure the PD classification signature current. Once the PSE applies a classification probe voltage, the PSE returns the PD voltage to the mark voltage range before applying another classification probe voltage, or powering up the PD.

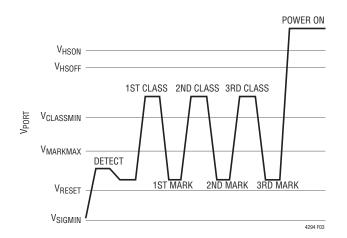

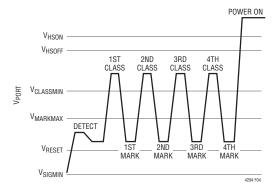

An example of 1-Event classification is shown in Figure 1. In 2-Event classification, a PSE probes for power classification twice as shown in Figure 2. An IEEE 802.3bt PSE may apply as many as 5 events before powering up the PD.

Figure 2. Type 2 PSE, 2-Event Class Sequence

Figure 3. Type 3 or 4 PSE, 3-Event Class Sequence

#### IEEE 802.3bt Physical Classification and Demotion

IEEE 802.3bt defines physical classification to allow a PD to request a power allocation from the connected PSE and to allow the PSE to inform the PD of the PSE's available power. Demotion is provided if the PD Requested Power level is not available at the PSE. If demoted, the PD must operate in a lower power state.

The number of class/mark events issued by the PSE directly indicates the power allocated to the PD and is summarized in Table 1.

IEEE 802.3bt provides nine PD classes and four PD types, as shown in Table 2. The LT4294 class is configured by setting the  $R_{CLS}$  and  $R_{CLS++}$  resistor values.

#### Table 1. PSE Allocated Power

| PD REQUESTED | NUMBER OF PSE CLASS/MARK EVENTS |       |       |     |       |  |  |  |

|--------------|---------------------------------|-------|-------|-----|-------|--|--|--|

| CLASS        | 1                               | 2     | 3     | 4   | 5     |  |  |  |

| 0            |                                 |       | 13W   |     |       |  |  |  |

| 1            |                                 |       | 3.84W |     |       |  |  |  |

| 2            |                                 | 6.49W |       |     |       |  |  |  |

| 3            |                                 |       | 13W   |     |       |  |  |  |

| 4            | 13W                             |       | 25.   | 5W  |       |  |  |  |

| 5            | 13W                             | 25.   | 5W    | 40  | W     |  |  |  |

| 6            | 13W                             | 25.   | 5W    | 51  | W     |  |  |  |

| 7            | 13W                             | 25.   | 5W    | 51W | 62W   |  |  |  |

| 8            | 13W                             | 25.   | 5W    | 51W | 71.3W |  |  |  |

Note: Bold indicates the PD has been demoted.

Table 2. Single-Signature Classification, Power Levels and Resistor Selection

| PD REQUESTED |                    |             |                       | RESISTOR (1%)    |                     |  |

|--------------|--------------------|-------------|-----------------------|------------------|---------------------|--|

| CLASS        | PD REQUESTED POWER | PD TYPE     | NOMINAL CLASS CURRENT | R <sub>CLS</sub> | R <sub>CLS</sub> ++ |  |

| 0            | 13W                | Type 1      | 2.5mA                 | 1.00kΩ           | Open                |  |

| 1            | 3.84W              | Type 1 or 3 | 10.5mA                | 140Ω             | Open                |  |

| 2            | 6.49W              | Type 1 or 3 | 18.5mA                | 76.8Ω            | Open                |  |

| 3            | 13W                | Type 1 or 3 | 28mA                  | 49.9Ω            | Open                |  |

| 4            | 25.5W              | Type 2 or 3 | 40mA                  | 34.8Ω            | Open                |  |

| 5            | 40W                | Туре З      | 40mA/2.5mA            | 1.00kΩ           | 37.4Ω               |  |

| 6            | 51W                | Туре З      | 40mA/10.5mA           | 140Ω             | 46.4Ω               |  |

| 7            | 62W                | Type 4      | 40mA/18.5mA           | 76.8Ω            | 64.9Ω               |  |

| 8            | 71.3W              | Type 4      | 40mA/28mA             | 49.9Ω            | 118Ω                |  |

IEEE 802.3bt PSEs present a single classification event (see Figure 1) to Class 0 through 3 PDs. A Class 0 through 3 PD presents its class signature to the PSE and is then powered on if sufficient power is available. Power limited IEEE 802.3bt PSEs may issue a single event to Class 4 and higher PDs in order to demote those PDs to Class 3 (13W).

IEEE 802.3bt PSEs present up to three classification events, depending on PSE Type, to Class 4 PDs (see Figure 3). Class 4 PDs present a class signature 4 on all events. The third event differentiates a Class 4 PD from a higher Class PD. Power-limited IEEE 802.3bt PSEs may issue three events to Class 5 and higher PDs in order to demote those PDs to Class 4 (25.5W).

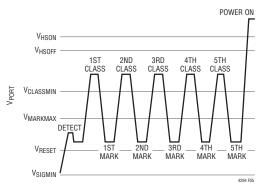

IEEE 802.3bt PSEs present four classification events (see Figure 4) to Class 5 and 6 PDs. Class 5 and 6 PDs present a class signature 4 on the first two events, then present a class signature 0 or 1, respectively, on the remaining events. Power limited IEEE 802.3bt PSEs may issue four events to Class 7 and higher PDs in order to demote those PDs to Class 6 (51W).

Figure 4. Type 3 or 4 PSE, 4-Event Class Sequence

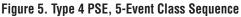

IEEE 802.3bt PSEs present five classification events (see Figure 5) to Class 7 and 8 PDs. Class 7 and 8 PDs present a class signature 4 on the first two events, then present a class signature 2 or 3, respectively, on the remaining events.

The number of class/mark events is communicated through the LT4294  $\overline{\text{T2P}}$  pin. See  $\overline{\text{T2P}}$  Output section for more details.

#### Classification Resistors (R<sub>CLS</sub> and R<sub>CLS++</sub>)

The R<sub>CLS</sub> and R<sub>CLS++</sub> resistors set the classification currents corresponding to the PD power classification. Select the value of R<sub>CLS</sub> and R<sub>CLS++</sub> from Table 2 and connect each 1% resistor between the RCLASS, RCLASS++ pins and GND.

#### **Detection Signature Corrupt During Mark Event**

During the mark event, the LT4294 presents <11 k  $\Omega$  to the port as required by the IEEE 802.3 specification.

#### **Inrush and Power On**

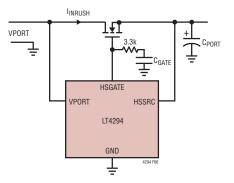

Once the PSE detects and classifies the PD, the PSE then powers on the PD. When the port voltage rises above the  $V_{\rm HSON}$  threshold, it begins to source  $I_{\rm GPU}$  out of the HSGATE pin. This current flows into an external capacitor,  $C_{\rm GATE}$  in Figure 6, that causes a voltage to ramp up the gate of the external MOSFET. The external MOSFET acts as a source follower and ramps the voltage up on the output bulk capacitor,  $C_{\rm PORT}$ , thereby determining the inrush current,  $I_{\rm INRUSH}$ . Design  $I_{\rm INRUSH}$  to be approximately ~100mA. See equation below:

$$I_{\text{INRUSH}} = I_{\text{GPU}} \bullet \frac{C_{\text{PORT}}}{C_{\text{GATE}}}$$

Figure 6. Configuring I<sub>INRUSH</sub>

The LT4294 internal charge pump provides an N-channel MOSFET solution, eliminating a larger and more costly P-channel MOSFET. The low  $R_{DS(ON)}$  MOSFET also maximizes power delivery and efficiency, reduces power and heat dissipation, and eases thermal design.

#### **Power Good**

The PWRGD pin is held low by its open drain output until HSGATE charges up to approximately 7V above HSSRC. The PWRGD pin is used to hold off the downstream circuitry until inrush is complete and the external MOSFET is fully enhanced. The HSGATE pin remains high and the PWRGD pin remains open-drain until the port voltage falls below  $V_{\rm HSOFE}$

#### **Delay Start**

When the PSE powers up the port, the PD application should not draw more than 350mA for 80ms to comply with the IEEE 802.3 standard.

### Auxiliary Supply Override

If the AUX pin is held above  $V_{AUXT}$ , the LT4294 enters auxiliary power supply override mode. In this mode the signature resistor disconnects, classification is disabled, HSGATE pulls down, the PWRGD pin is open drain and T2P pin indicates max available power.

The AUX pin allows for setting the auxiliary supply turn on and turn off voltage thresholds,  $V_{AUXON}$ , and  $V_{AUXOFF}$ respectively. The auxiliary supply hysteresis voltage,  $V_{AUXHYS}$ , is generated with sinking current,  $I_{AUXH}$ , and is active only when the AUX pin voltage is less than  $V_{AUXT}$ . Use the following equations to set  $V_{AUXON}$  and  $V_{AUXOFF}$ via R1 and R2 in Figure 7. Note that an internal 6.5V Zener limits the voltage on the AUX pin.

A capacitor up to 1000pF may be placed between the AUX pin and GND to improve noise immunity.  $V_{AUXON}$  must be lower than  $V_{HSOFE}$

#### **T2P** Output

The LT4294 communicates the PSE allocated power to the PD application via the T2P pin. The T2P pin state is determined by the AUX pin, the RCLASS<sup>++</sup> pin, and the number of classification events. The LT4294 uses a 4-state encoding for the T2P output. T2P state and the associated PSE allocated power are shown in Table 3.

| Table 3. T2P Response to Determine PSE Allocated P | ower |

|----------------------------------------------------|------|

|----------------------------------------------------|------|

| STATE     | PD<br>REQUESTED<br>CLASS | NUMBER<br>OF CLAS-<br>SIFICATION<br>EVENTS | T2P*                                | PSE<br>ALLOCATED<br>POWER             |

|-----------|--------------------------|--------------------------------------------|-------------------------------------|---------------------------------------|

| Auviliany | 0-4                      | N/A                                        | Low-Z                               | AUX Power                             |

| Auxiliary | 5-8                      | N/A                                        | 25%                                 | AUX Power                             |

|           | 0-4                      | 1                                          | Hi-Z                                | Min (PD<br>Requested<br>Power, 13W)   |

|           |                          | ≥ 2                                        | Low-Z                               | 25.5W                                 |

|           |                          | 1                                          | Hi-Z                                | 13W                                   |

| PoE       |                          | 2 or 3                                     | Low-Z                               | 25.5W                                 |

| 5-8       | 4                        | 50%                                        | Min (PD<br>Requested<br>Power, 51W) |                                       |

|           |                          | 5                                          | 25%                                 | Min (PD<br>Requested<br>Power, 71.3W) |

\*Specified as the percentage of the period which  $\overline{\text{T2P}}$  is low impedance with respect to GND.

The highest priority input is the AUX pin. AUX is asserted to enter the auxiliary power state and deasserted to enter the PoE state. In the auxiliary power state, the  $\overline{T2P}$  pin indicates the highest available power, based on

Figure 8. Response Example for 25% Low-Z, 75% Hi-Z

Rev. B

PD Requested Class. The auxiliary power supply must be sized to provide at least the PD Requested Power.

Second, PD Requested Class and PD Requested Power are configured using the RCLASS and RCLASS++ pins. The RCLASS++ pin alone can be used to determine if the PD Class is 0-4 or 5-8, as shown in Table 2.

Last, the number of classification events determines the amount of power allocated by the PSE as described in Table 1.

## Interoperability Across Various PSEs and Auxiliary Power Source

Table 4 summarizes the expected  $\overline{T2P}$  response, the PSE allocated power, and the number of classification events. The result is a function of PD Requested Class and power source—Auxiliary or PoE.

#### **Overtemperature Protection**

The IEEE 802.3 specification requires a PD to withstand any applied voltage from 0V to 57V indefinitely. During classification, however, the power dissipation in the LT4294 may be as high as 1.5W. The LT4294 can easily tolerate this power for the maximum IEEE classification timing but overheats if this condition persists abnormally.

The LT4294 includes an overtemperature protection feature which is intended to protect the device during momentary overload conditions. If the junction temperature exceeds the overtemperature threshold, the LT4294 pulls down HSGATE pin, and disables classification.

#### EXTERNAL INTERFACE AND COMPONENT SELECTION

#### **PoE Input Bridge**

A PD is required to polarity-correct its input voltage. There are several different options available for bridge rectifiers;

| abie 4. L14294 lille                       |                              |                                        | -                            | E TYPE, CLASS (POW           |                              |                              | /                            |                            |

|--------------------------------------------|------------------------------|----------------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|----------------------------|

|                                            | IEEE 802.3<br>TYPE 1         | IEEE 802.3 IEEE 802.3<br>TYPE 2 TYPE 3 |                              |                              |                              | IEEE<br>TYF                  | AUXILIARY                    |                            |

| PD REQUESTED CLASS<br>(PD REQUESTED POWER) | CLASS 3<br>(13W)             | CLASS 4<br>(25.5W)                     | CLASS 4<br>(25.5W)           | CLASS 5<br>(40W)             | CLASS 6<br>(51W)             | CLASS 7<br>(62W)             | CLASS 8<br>(71.3W)           | POWER<br>Source**          |

| CLASS 0-3<br>(Up to 13W)                   | Hi-Z<br>Up to 13W<br>1-Event | Hi-Z<br>Up to 13W<br>1-Event           | Hi-Z<br>Up to 13W<br>1-Event | Hi-Z<br>Up to 13W<br>1-Event | Hi-Z<br>Up to 13W<br>1-Event | Hi-Z<br>Up to 13W<br>1-Event | Hi-Z<br>Up to 13W<br>1-Event | Low-Z<br>Aux. Power<br>N/A |

| CLASS 4<br>(25.5W)                         | Hi-Z<br>13W<br>1-Event       | Low-Z<br>25.5W<br>2-Event              | Low-Z<br>25.5W<br>3-Event    | Low-Z<br>25.5W<br>3-Event    | Low-Z<br>25.5W<br>3-Event    | Low-Z<br>25.5W<br>3-Event    | Low-Z<br>25.5W<br>3-Event    | Low-Z<br>Aux. Power<br>N/A |

| CLASS 5<br>(40W)                           | Hi-Z<br>13W<br>1-Event       | Low-Z<br>25.5W<br>2-Event              | Low-Z<br>25.5W<br>3-Event    | 50%<br>40W<br>4-Event        | 50%<br>40W<br>4-Event        | 50%<br>40W<br>4-Event        | 50%<br>40W<br>4-Event        | 25%<br>Aux. Power<br>N/A   |

| CLASS 6<br>(51W)                           | Hi-Z<br>13W<br>1-Event       | Low-Z<br>25.5W<br>2-Event              | Low-Z<br>25.5W<br>3-Event    | Low-Z<br>25.5W<br>3-Event    | 50%<br>51W<br>4-Event        | 50%<br>51W<br>4-Event        | 50%<br>51W<br>4-Event        | 25%<br>Aux. Power<br>N/A   |

| CLASS 7<br>(62W)                           | Hi-Z<br>13W<br>1-Event       | Low-Z<br>25.5W<br>2-Event              | Low-Z<br>25.5W<br>3-Event    | Low-Z<br>25.5W<br>3-Event    | 50%<br>51W<br>4-Event        | 25%<br>62W<br>5-Event        | 25%<br>62W<br>5-Event        | 25%<br>Aux. Power<br>N/A   |

| CLASS 8<br>(71.3W)                         | Hi-Z<br>13W<br>1-Event       | Low-Z<br>25.5W<br>2-Event              | Low-Z<br>25.5W<br>3-Event    | Low-Z<br>25.5W<br>3-Event    | 50%<br>51W<br>4-Event        | 50%<br>51W<br>4-Event        | 25%<br>71.3W<br>5-Event      | 25%<br>Aux. Power<br>N/A   |

#### Table 4. LT4294 Interoperability (T2P Response\*, PSE Allocated Power, Number of Classification Events)

$\begin{array}{c|c} & \downarrow \\ \hline \hline 12P \mbox{ Response}^* \rightarrow & 25\% \\ PSE \mbox{ Allocated Power} \rightarrow & 71.3W \\ Number \mbox{ of Classification Events} \rightarrow & 5-Event \\ \end{array}$

Note 1. Shade of blue indicates the PD has been demoted or denied power.

$^{\ast}$  Specified as the percentage of the period which  $\overline{\text{T2P}}$  is low impedance with respect to GND.

\*\* Auxiliary Power Supply must be sized to provide PD Requested Power.

silicon diodes, Schottky diodes, and ideal diodes. When silicon or Schottky diode bridges are used, the diode forward voltage drops affect the voltage at the VPORT pin. The LT4294 is designed to tolerate these voltage drops. Note, the voltage parameters shown in the Electrical Characteristics are specified at the LT4294 package pins.

A silicon diode bridge consumes up to 4% of the available power. In addition, silicon diode bridges exhibit poor pairset-to-pairset unbalance performance. Each branch of a silicon diode bridge shares source/return current, and thermal runaway can cause large, non-compliant current unbalances between pairsets.

While using Schottky diodes can help reduce the power loss with a lower forward voltage, the Schottky bridge may not be suitable for high temperature PD applications. Schottky diode bridges exhibit temperature induced leakage currents. The leakage current has a voltage dependency that can invalidate the measured detection signature. In addition, these leakage currents can back-feed through the unpowered branch and the unused bridge, violating IEEE 802.3 specifications.

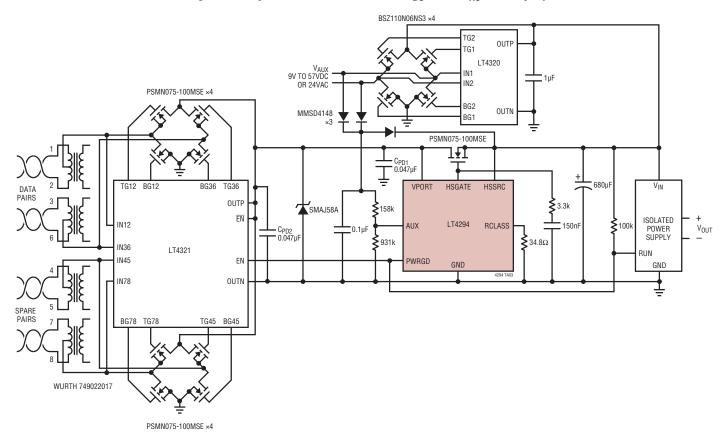

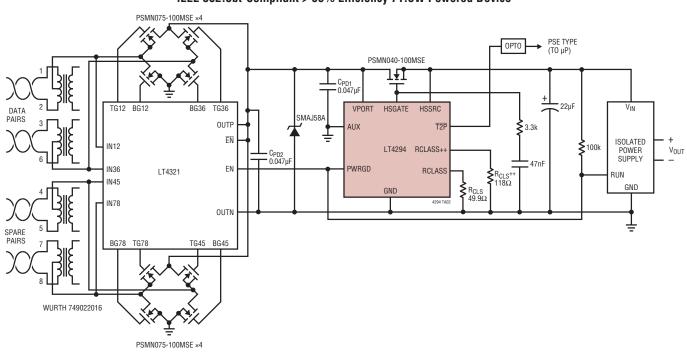

For high efficiency applications, the LT4294 supports an LT4321-based PoE ideal diode bridge that reduces the forward voltage drop from 0.7V to 20mV per diode while maintaining IEEE 802.3 compliance. The LT4321 simplifies thermal design, eliminates costly heatsinks, and can operate in space-constrained applications.

#### **Auxiliary Input Diode Bridge**

Some PDs are required to receive AC or DC power from an auxiliary power source. A diode bridge is typically required to handle the voltage rectification and polarity correction.

In high efficiency applications, or in low auxiliary input voltage applications, the voltage drop across the rectifier cannot be tolerated. The LT4294 can be configured with an LT4320-based ideal diode bridge to recover the diode voltage drop and ease thermal design.

For applications with auxiliary input voltages below 10V, the LT4294 must be configured with an LT4320-based ideal diode bridge to recover the voltage drop and guarantee the

minimum VPORT voltage is within the VPORT AUX Mode Range as specified in the Electrical Characteristics table.

An example of a high efficiency typical application circuit is show in the Typical Application section.

#### **Input Capacitor**

A 0.1 $\mu$ F capacitor is needed from V<sub>PORT</sub> to GND to meet the input impedance requirement in IEEE 802.3 and to properly bypass the LT4294. When operating with the LT4321, locally bypass each with a 0.047 $\mu$ F capacitor, thus keeping the total port capacitance within specification.

#### **Transient Voltage Suppressor**

The LT4294 specifies an absolute maximum voltage of 100V and is designed to tolerate brief overvoltage events due to Ethernet cable surges. To protect the LT4294 from an overvoltage event, install a unidirectional transient voltage suppressor (TVS) such as an SMAJ58A between the  $V_{PORT}$  and GND pins. For PD applications that require an auxiliary power input, install a TVS between  $V_{IN}$  and GND. See Layout Considerations for TVS placement.

For extremely high cable discharge and surge protection, contact Analog Devices Applications.

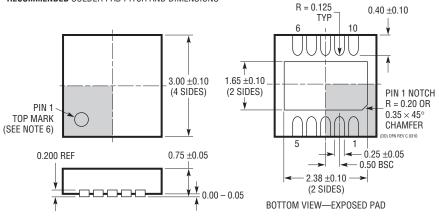

#### **Exposed Pad**

The LT4294 DFN package has an exposed pad that is internally electrically connected to GND. The exposed pad may only be connected to GND on the printed circuit board.

#### LAYOUT CONSIDERATIONS

Avoid excessive parasitic capacitance on the RCLASS and RCLASS++ pins and place resistors  $R_{CLS}$  and  $R_{CLS++}$  close to the LT4294.

It is strictly required for maximum protection to place the 0.1 $\mu$ F input capacitor, C<sub>PD</sub>, and transient voltage suppressor as close to the LT4294 as possible. When operating the LT4294 with the LT4321, place a 0.047 $\mu$ F capacitor, C<sub>PD1</sub>, as close as possible to the LT4294 VPORT and GND pins (pin 10 and pin 5, respectively), and a 0.047 $\mu$ F capacitor, C<sub>PD2</sub>, as close as possible to the LT4321 OUTP and OUTN pins.

## TYPICAL APPLICATIONS

High Efficiency 25.5W PD Solution with  $12V_{DC}$  and  $24V_{AC}$  Auxiliary Input

## PACKAGE DESCRIPTION

**DD Package** 10-Lead Plastic DFN (3mm × 3mm) (Reference LTC DWG # 05-08-1699 Rev C)

**RECOMMENDED** SOLDER PAD PITCH AND DIMENSIONS

NOTE:

1. DRAWING TO BE MADE A JEDEC PACKAGE OUTLINE M0-229 VARIATION OF (WEED-2). CHECK THE LTC WEBSITE DATA SHEET FOR CURRENT STATUS OF VARIATION ASSIGNMENT

2. DRAWING NOT TO SCALE

ALL DIMENSIONS ARE IN MILLIMETERS

AL DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE

MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE 5. EXPOSED PAD SHALL BE SOLDER PLATED

6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE

TOP AND BOTTOM OF PACKAGE

Rev. B

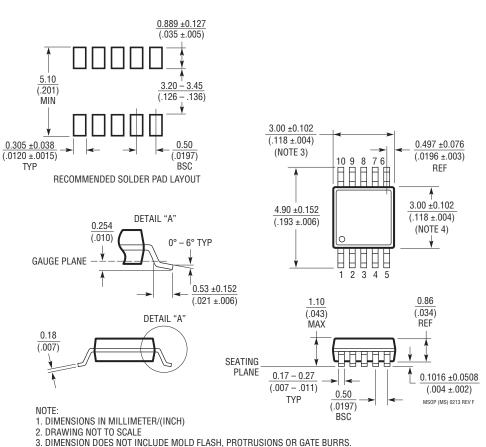

## PACKAGE DESCRIPTION

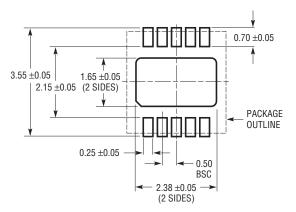

**MS Package 10-Lead Plastic MSOP** (Reference LTC DWG # 05-08-1661 Rev F)

MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

A DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006') PER SIDE 5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004') MAX

## **REVISION HISTORY**

| REV | DATE  | DESCRIPTION                                                                                                                                                             | PAGE NUMBER              |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| A   | 09/18 | Updated to IEEE 802.3af/at/bt (Draft 3.5)<br>Revised T2P Output Applications Information<br>Revised External Interface and Component Selection Applications Information | 1-16<br>10, 11<br>11, 12 |

| В   | 04/19 | Removed Draft Number<br>Added Table 4 – Interoperability                                                                                                                | 1-16<br>11               |

## TYPICAL APPLICATION

#### IEEE 802.3bt-Compliant > 99% Efficiency 71.3W Powered Device

## **RELATED PARTS**

| PART NUMBER                                                                             | DESCRIPTION                                                              | COMMENTS                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LT4293                                                                                  | LTPoE++/IEEE 802.3bt PD Interface                                        | Mutually Identified with LTPoE++ and IEEE 802.3bt PSEs                                                                                                                                                                    |

| LT4295 IEEE 802.3bt PD with Forward/Flyback<br>Switching Regulator Controller           |                                                                          | External Switch, IEEE 802.3bt Support, Configurable Class, Forward or No-Opto Flyback<br>Operation, Frequency, PG/SG Delays, Soft-Start, and Aux Support as Low as 9V,<br>Including Housekeeping Buck, Slope Compensation |

| LT4321                                                                                  | PoE Ideal Diode Bridge Controller                                        | Controls 8-NMOSFETs for IEEE-Required PD Voltage Rectification without Diode Drops                                                                                                                                        |

| LT4320/LT4320-1                                                                         | Ideal Diode Bridge Controller                                            | 9V – 72V, DC to 600Hz Input. Controls 4-NMOSFETs, Voltage Rectification without Diode Drops                                                                                                                               |

| LTC4292/LTC4291-1                                                                       | 4-Port IEEE 802.3bt PSE Controller                                       | Transformer Isolation, Supports IEEE 802.3bt PDs                                                                                                                                                                          |

| LTC4279                                                                                 | Single PoE/PoE+/LTPoE++ PSE Controller                                   | Supports IEEE 802.3af, IEEE 802.3at, LTPoE++ and Proprietary PDs                                                                                                                                                          |

| LTC4290/LTC4271                                                                         | 8-Port PoE/PoE+/LTPoE++ PSE Controller                                   | Transformer Isolation, Supports IEEE 802.3af, IEEE 802.3at and LTPoE++ PDs                                                                                                                                                |

| LT4276A/B/C LTPoE++/PoE+/PoE PD with Forward/<br>Flyback Switching Regulator Controller |                                                                          | External Switch, LTPoE++ Support, User-Configurable Class, Forward or No-Opto<br>Flyback Operation, Frequency, PG/SG Delays, Soft-Start, and Aux Support as Low as 9V<br>Including Housekeeping Buck, Slope Compensation  |

| LT4275A/B/C                                                                             | LTPoE++/PoE+/PoE PD Controller                                           | External Switch, LTPoE++ Support                                                                                                                                                                                          |

| LTC4269-1                                                                               | IEEE 802.3at PD Interface with Integrated<br>Flyback Switching Regulator | 2-Event Classification, Programmable Class, Synchronous No-Opto Flyback Controller,<br>50kHz to 250kHz, Aux Support                                                                                                       |

| LTC4269-2                                                                               | IEEE 802.3at PD Interface with Integrated Forward Switching Regulator    | 2-Event Classification, Programmable Class, Synchronous Forward Controller, 100kHz to 500kHz, Aux Support                                                                                                                 |

| LTC4278                                                                                 | IEEE 802.3at PD Interface with Integrated<br>Flyback Switching Regulator | 2-Event Classification, Programmable Class, Synchronous No-Opto Flyback Controller,<br>50kHz to 250kHz, 12V Aux Support                                                                                                   |

| LTC4267/LTC4267-1/<br>LTC4267-3                                                         | IEEE 802.3af PD Interface with Integrated Switching Regulator            | Internal 100V, 400mA Switch, Programmable Class, 200/300kHz Constant<br>Frequency PWM                                                                                                                                     |

|                                                                                         | 1                                                                        | Rev. E                                                                                                                                                                                                                    |

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Hot Swap Voltage Controllers category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below :

LTC4227CUFD-4#PBF LTC4212IMS MAX16141ADF/V+ ADM1075-2ARUZ-RL7 LM5067MW-1/NOPB MAX5969BETB+T MIC22700YML-TR LT1640LIS8#PBF LTC4217CDHC-12#PBF LT4294HDD#PBF LTC4253CGN#PBF LTC4260IGN#PBF LTC4211CMS8#PBF LTC4230CGN#PBF LTC4214MS-1#PBF LTC4216IMS#PBF LTC4212IMS#PBF LTC4260CGN#PBF LTC4227CGN-2#PBF LTC4244IGN#PBF LTC4212CMS#PBF LT4250HCN8#PBF ADM1276-3ACPZ-RL LTC4260IUD-1#PBF ADM1075-2ACPZ ADM1075-1ACPZ ADM1073ARUZ ADM1073ARUZ-REEL7 ADM1075-1ARUZ ADM1075-2ARUZ ADM1170-1AUJZ-RL7 ADM1171-2AUJZ-RL7 ADM1172-1AUJZ-RL7 ADM1172-2AUJZ-RL7 ADM1177-1ARMZ-R7 ADM1177-2ARMZ-R7 ADM1275-3ARQZ ADM1275-1ARQZ ADM1275-3ARQZ-R7 ADM1276-3ACPZ ADM4210-1AUJZ-RL7 ADM1275-2ARQZ ADM1070ARTZ-REEL7 LTC1645IS#PBF LTC1645CS#PBF LTC4251BIS6-1#TRMPBF LTC1422IS8#PBF LT1641CS8#PBF LT1640HCS8#PBF LT1640HIS8#PBF