# Precision, Funneling Instrumentation Amplifier with Level Shift and Output Clamping

## **FEATURES**

- Single Gain Set Resistor: G = 0.2 to >200

- Excellent DC Precision

- Input Offset Voltage: 60µV Max

- Input Offset Voltage Drift: 0.6µV/°C Max

- Low Gain Error: 0.012% Max (G = 0.2)

- Low Gain Drift: 35ppm/°C Max (G > 0.2)

- High DC CMRR: 80dB Min (G = 0.2)

- Integrated Output Clamps

- Integrated Output Level Shift

- Input Bias Current: 800pA Max

- 4MHz –3dB Bandwidth (G = 0.2)

- Low Noise:

- 0.1Hz to 10Hz Noise: 0.2μV<sub>P-P</sub>

- 1kHz Voltage Noise: 7nV/√Hz

- Integrated Input RFI Filter

- Wide Supply Range 4.75V to 35V

- Temperature Ranges: -40°C to 85°C and -40°C to 125°C

- MS16E and 20-Lead 3mm × 4mm QFN Packages

# **APPLICATIONS**

- Bridge Amplifier

- Data Acquisition

- Thermocouple Amplifier

- Strain Gauge Amplifier

- Medical Instrumentation

- Transducer Interfaces

- Differential to Single-Ended Conversion

#### DESCRIPTION

The LT®6372-0.2 is a gain programmable, high precision funneling instrumentation amplifier that delivers industry leading DC precision. This high precision enables smaller signals to be sensed and eases calibration requirements, particularly over temperature. The LT6372-0.2 incorporates features into the LT6370 which further improve accuracy and simplify interfacing to an ADC.

The LT6372-0.2 uses a proprietary high performance bipolar process which enables industry leading accuracy coupled with exceptional long-term stability. The LT6372-0.2 is laser trimmed for very low input offset voltage ( $60\mu V$ ) and high CMRR (80dB, G = 0.2). Proprietary on-chip test capability allows the gain drift ( $35ppm/^{\circ}C$ ) to be guaranteed with automated testing.

The LT6372-0.2's difference amplifier uses a split reference configuration which simplifies level shifting the amplifier's output to the center of the ADC's input range. Output clamp pins are also provided to limit the voltage which can be applied to an ADC's input. EMI filtering is integrated on the LT6372-0.2's inputs to maintain accuracy in the presence of harsh RF interference.

The LT6372-0.2 is available in a compact MS16E or a 20-pin 3mm x 4mm QFN. The LT6372-0.2 is fully specified over the –40°C to 85°C and –40°C to 125°C temperature ranges.

All registered trademarks and trademarks are the property of their respective owners.

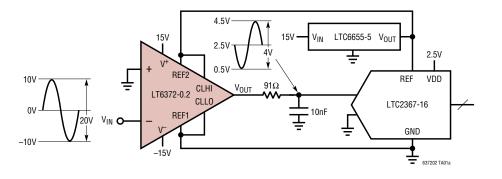

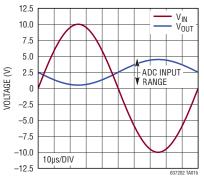

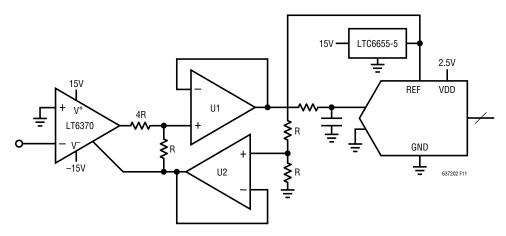

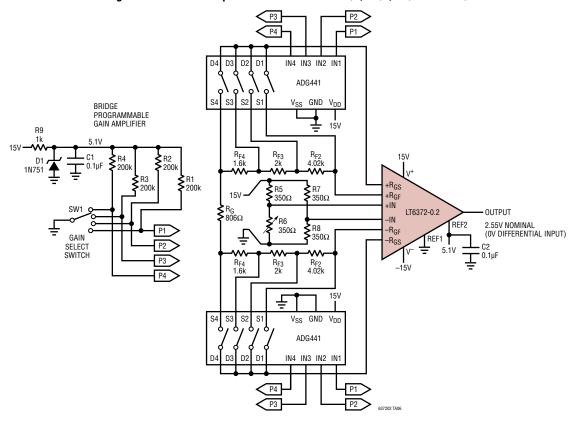

# TYPICAL APPLICATION

LT6372-0.2 Funnels and Level Shifts ±10V Inputs to 5V ADC Input Range

# **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| Total Supply Voltage (V+ to V <sup>-</sup> )3                                                            | 6V  |

|----------------------------------------------------------------------------------------------------------|-----|

| Input Voltage (+IN, -IN, +R <sub>G.S</sub> , +R <sub>G.F</sub> , -R <sub>G.S</sub> , -R <sub>G.F</sub> , |     |

| REF1, REF2, CLHI, CLLO) $(V^{-} - 0.3V)$ to $(V^{+} + 0.3V)$                                             | 3V) |

| Differential Input Voltage                                                                               |     |

| (+IN to -IN)±3                                                                                           | 6V  |

| (REF1 to REF2)±                                                                                          | 8V  |

| Input Current                                                                                            |     |

| (+R <sub>GS</sub> , +R <sub>GF</sub> , -R <sub>GS</sub> , -R <sub>GF</sub> )±2i                          | nΑ  |

| (+IN, -IN, CLLO)±10r                                                                                     | nΑ  |

| (REF1, REF2, CLHI)10r                                                                                    | nΑ  |

| Output Short-Circuit Duration        | Thermally Limited |

|--------------------------------------|-------------------|

| Output Current                       | 80mA              |

| Operating and Specified Temperature  | Range             |

| I-Grade                              | 40°C to 85°C      |

| H-Grade                              | 40°C to 125°C     |

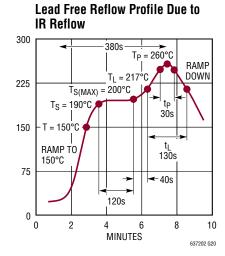

| Maximum Junction Temperature         | 150°C             |

| Storage Temperature Range            | 65°C to 150°C     |

| Lead Temperature (Soldering, 10 sec) | )300°C            |

|                                      |                   |

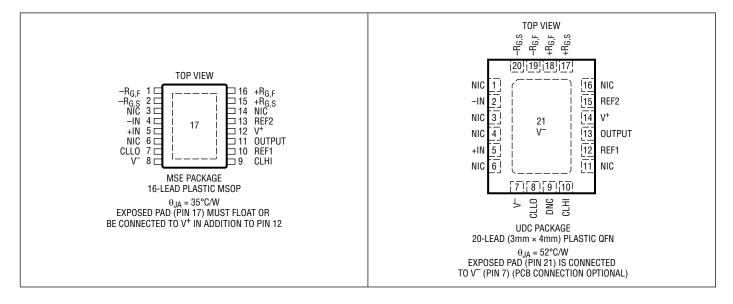

# PIN CONFIGURATION

# ORDER INFORMATION

| TUBE               | TAPE AND REEL        | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|--------------------|----------------------|---------------|---------------------------------|-------------------|

| LT6372IMSE-0.2#PBF | LT6372IMSE-0.2#TRPBF | 637202        | 16-Lead Plastic MSOP            | -40°C to 85°C     |

| LT6372HMSE-0.2#PBF | LT6372HMSE-0.2#TRPBF | 637202        | 16-Lead Plastic MSOP            | -40°C to 125°C    |

| LT6372IUDC-0.2#PBF | LT6372IUDC-0.2#TRPBF | LHHQ          | 20-Lead (3mm × 4mm) Plastic QFN | -40°C to 85°C     |

| LT6372HUDC-0.2#PBF | LT6372HUDC-0.2#TRPBF | LHHQ          | 20-Lead (3mm × 4mm) Plastic QFN | -40°C to 125°C    |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the specified temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>S</sub> = $\pm 15$ V, V<sub>CM</sub> = V<sub>REF1</sub> = V<sub>REF2</sub> = 0V, V<sub>CLL0</sub> = V<sup>-</sup>, V<sub>CLH1</sub> = V<sup>+</sup>, R<sub>L</sub> = 4k $\Omega$ .

| SYMBOL                  | PARAMETER                                            | CONDITIONS                                                                                                                                                                                                  |   | MIN                                  | TYP                          | MAX                          | UNITS                                  |

|-------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------------------------|------------------------------|------------------------------|----------------------------------------|

| G                       | Gain Range                                           | $G = 0.2 \cdot (1 + 24.2 \text{k/R}_{G}) \text{ (Note 2)}$                                                                                                                                                  |   | 0.2                                  |                              | 200                          | V/V                                    |

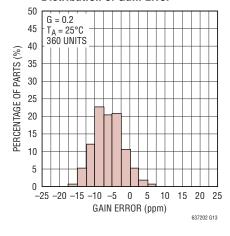

|                         | Gain Error (Notes 3, 4)                              | G = 0.2<br>G = 0.2<br>G = 1                                                                                                                                                                                 | • |                                      | 0.002<br>0.01                | 0.012<br>0.015<br>0.15       | %<br>%<br>%                            |

|                         |                                                      | G = 1<br>G = 10<br>G = 10<br>G = 100                                                                                                                                                                        | • |                                      | 0.02<br>0.02                 | 0.45<br>0.15<br>0.45<br>0.15 | %<br>%<br>%                            |

|                         |                                                      | G = 100<br>G = 200<br>G = 200                                                                                                                                                                               | • |                                      | 0.03                         | 0.45<br>0.15<br>0.53         | %<br>%<br>%                            |

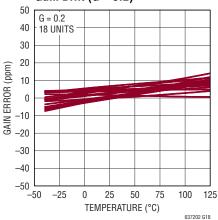

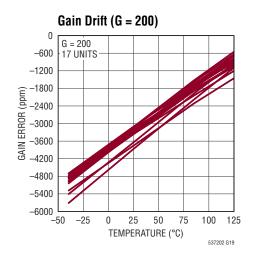

|                         | Gain vs Temperature (Notes 3, 4)                     | G = 0.2 (Note 5)<br>G > 0.2 (Note 6)                                                                                                                                                                        | • |                                      | 0.2<br>20                    | 0.5<br>35                    | ppm/°C<br>ppm/°C                       |

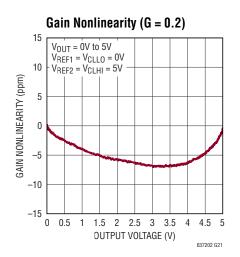

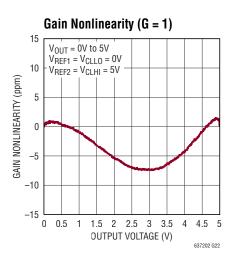

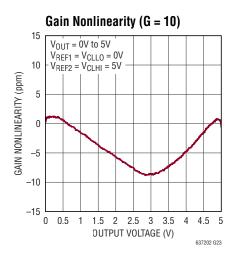

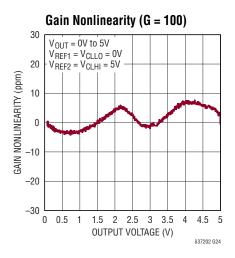

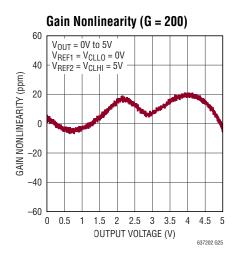

|                         | Gain Nonlinearity (Notes 3, 7)                       | $V_{OUT} = 0V$ to $4.096V$ , $G = 0.2$<br>$V_{OUT} = 0V$ to $4.096V$ , $G = 1$<br>$V_{OUT} = 0V$ to $4.096V$ , $G = 10$<br>$V_{OUT} = 0V$ to $4.096V$ , $G = 100$<br>$V_{OUT} = 0V$ to $4.096V$ , $G = 200$ |   |                                      | 3<br>4<br>5<br>6<br>12       | 5<br>60<br>80                | ppm<br>ppm<br>ppm<br>ppm<br>ppm        |

| V <sub>OST</sub> , Tota | al Input Referred Offset Voltage, $V_{OST} = V_{O}$  | <sub>SI</sub> + V <sub>0S0</sub> /G                                                                                                                                                                         |   |                                      |                              |                              |                                        |

| V <sub>OSI</sub>        | Input Offset Voltage<br>(Note 8)                     |                                                                                                                                                                                                             | • |                                      | ±15                          | ±60<br>±175                  | μV<br>μV                               |

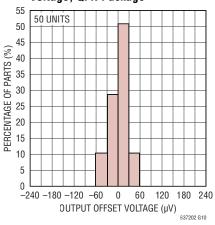

| V <sub>0S0</sub>        | Output Offset Voltage (Note 8)                       |                                                                                                                                                                                                             | • |                                      | ±30                          | ±175<br>±300                 | μV<br>μV                               |

| V <sub>OSI</sub> /T     | Input Offset Voltage Drift<br>(Notes 5, 8)           |                                                                                                                                                                                                             | • |                                      |                              | ±0.6                         | μV/°C                                  |

|                         | Input Offset Voltage<br>Hysteresis (Note 9)          | $T_A = -40$ °C to 125°C                                                                                                                                                                                     | • |                                      | ±3                           |                              | μV                                     |

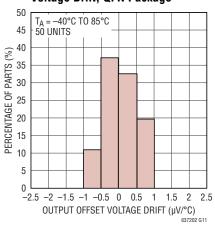

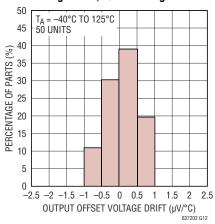

| V <sub>OSO</sub> /T     | Output Offset Voltage Drift<br>(Notes 5, 8)          |                                                                                                                                                                                                             | • |                                      |                              | ±2                           | μV/°C                                  |

|                         | Output Offset Voltage Hysteresis (Note 9)            | $T_A = -40$ °C to 125°C                                                                                                                                                                                     | • |                                      | ±10                          |                              | μV                                     |

| I <sub>B</sub>          | Input Bias Current                                   | $T_A = -40$ °C to 85°C<br>$T_A = -40$ °C to 125°C                                                                                                                                                           | • |                                      | ±0.1                         | ±0.8<br>±1.5<br>±3           | nA<br>nA<br>nA                         |

| I <sub>OS</sub>         | Input Offset Current                                 |                                                                                                                                                                                                             | • |                                      | ±0.2                         | ±1.4<br>±4                   | nA<br>nA                               |

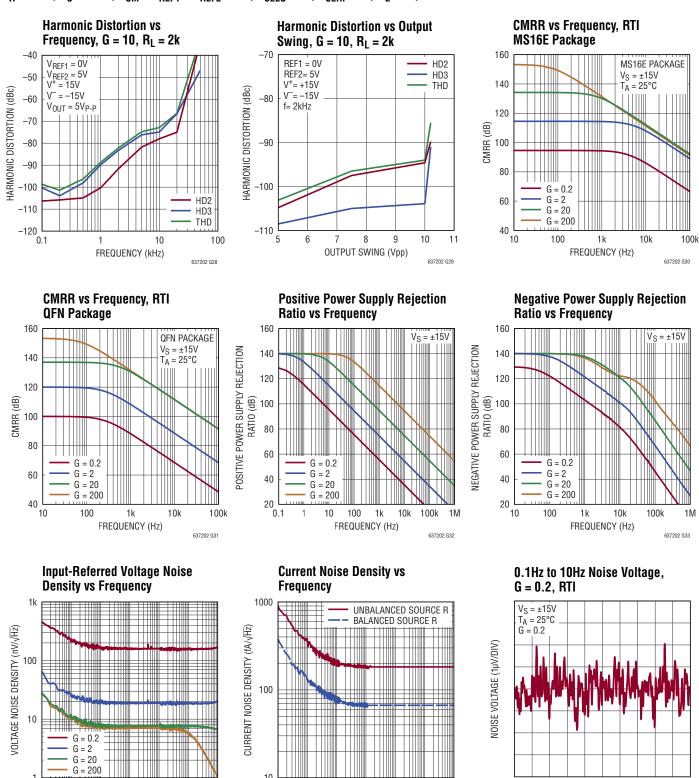

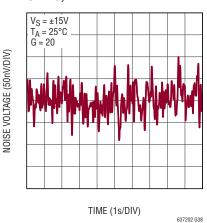

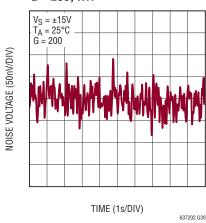

|                         | Input Noise Voltage (Note 10)                        | 0.1Hz to 10Hz, G = 0.2<br>0.1Hz to 10Hz, G = 200                                                                                                                                                            |   |                                      | 4<br>0.2                     |                              | μV <sub>P-P</sub><br>μV <sub>P-P</sub> |

| Total RTI               | Noise = $\sqrt{{e_{ni}}^2 + (e_{no}/G)^2}$ (Note 10) |                                                                                                                                                                                                             |   |                                      |                              |                              |                                        |

| e <sub>ni</sub>         | Input Noise Voltage Density                          | f = 1kHz                                                                                                                                                                                                    |   |                                      | 7                            |                              | nV/√Hz                                 |

| e <sub>no</sub>         | Output Noise Voltage Density                         | f = 1kHz                                                                                                                                                                                                    |   |                                      | 32                           |                              | nV/√Hz                                 |

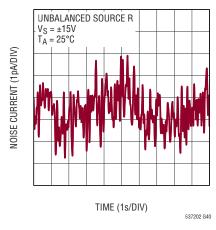

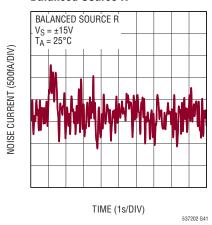

|                         | Input Noise Current                                  | 0.1Hz to 10Hz                                                                                                                                                                                               |   |                                      | 10                           |                              | pA <sub>P-P</sub>                      |

| i <sub>n</sub>          | Input Noise Current Density                          | f = 1kHz                                                                                                                                                                                                    |   |                                      | 200                          |                              | fA/√Hz                                 |

| R <sub>IN</sub>         | Input Resistance                                     | $V_{IN} = -12.6V \text{ to } 13V$                                                                                                                                                                           |   |                                      | 225                          |                              | GΩ                                     |

| C <sub>IN</sub>         | Differential<br>Common Mode                          | f = 100kHz<br>f = 100kHz                                                                                                                                                                                    |   |                                      | 0.9<br>15.9                  |                              | pF<br>pF                               |

| V <sub>CM</sub>         | Input Voltage Range                                  | Guaranteed by CMRR                                                                                                                                                                                          | • | V <sup>-</sup><br>V <sup>-</sup> + 2 | + 1.8/V <sup>+</sup> –<br>.4 | · 1.4<br>V+ – 2              | V<br>V                                 |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the specified temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>S</sub> = $\pm 15$ V, V<sub>CM</sub> = V<sub>REF1</sub> = V<sub>REF2</sub> = 0V, V<sub>CLL0</sub> = V<sup>-</sup>, V<sub>CLH1</sub> = V<sup>+</sup>, R<sub>L</sub> = 4k $\Omega$ .

| SYMBOL           | PARAMETER                      | CONDITIONS                                                                                                                                                       |   | MIN                                                  | TYP                             | MAX                 | UNITS                                  |

|------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------------------------------------------|---------------------------------|---------------------|----------------------------------------|

| CMRR             | Common Mode Rejection Ratio    | DC to 60Hz, 1k Source Imbalance,<br>V <sub>CM</sub> = -12.6V to 13V<br>G = 0.2<br>G = 0.2<br>G = 1<br>G = 1<br>G = 10<br>G = 10<br>G = 100<br>G = 200<br>G = 200 | • | 80<br>74<br>95<br>89<br>114<br>108                   | 96<br>110<br>130<br>146<br>146  |                     | dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB |

|                  | AC Common Mode Rejection Ratio | f = 20kHz, QFN20 Package<br>G = 0.2<br>G = 2<br>G = 20<br>G = 200                                                                                                |   |                                                      | 62<br>82<br>104<br>104          |                     | dB<br>dB<br>dB                         |

|                  |                                | f = 20kHz, MS16E Package<br>G = 0.2<br>G = 2<br>G = 20<br>G = 200                                                                                                |   |                                                      | 80<br>100<br>104<br>104         |                     | dB<br>dB<br>dB                         |

| PSRR             | Power Supply Rejection Ratio   | $V_S = \pm 2.375V \text{ to } \pm 17.5V$<br>G = 0.2<br>G = 0.2<br>G = 1<br>G = 1<br>G = 10<br>G = 100<br>G = 100<br>G = 200                                      | • | 106<br>104<br>120<br>117<br>128<br>122<br>128<br>122 | 121<br>135<br>140<br>142<br>146 |                     | dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB |

| $\overline{V_S}$ | Supply Voltage                 | Guaranteed by PSRR                                                                                                                                               | • | 4.75                                                 | ,                               | 35                  | V                                      |

| Is               | Supply Current                 | $V_S = \pm 15V$ $T_A = -40^{\circ}C \text{ to } 85^{\circ}C$ $T_A = -40^{\circ}C \text{ to } 125^{\circ}C$                                                       | • |                                                      | 2.75                            | 2.85<br>3<br>3.1    | mA<br>mA<br>mA                         |

|                  |                                | $V_S = \pm 2.375V$ $T_A = -40^{\circ}C$ to 85°C $T_A = -40^{\circ}C$ to 125°C                                                                                    | • |                                                      | 2.65                            | 2.7<br>2.85<br>2.95 | mA<br>mA<br>mA                         |

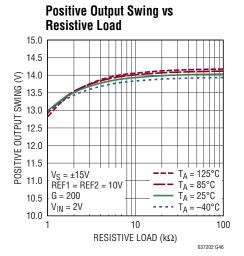

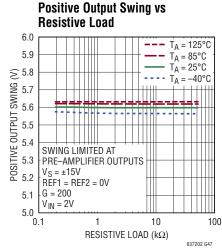

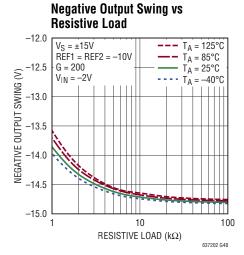

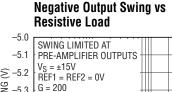

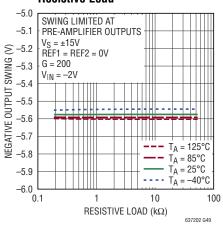

| V <sub>OUT</sub> | Output Voltage Swing           | $V_S = \pm 15V$ , $R_L = 10k\Omega$                                                                                                                              | • | -14.4<br>-14.2                                       | -14.7/14                        | 13.6<br>13.5        | V                                      |

|                  |                                | $V_S = \pm 2.375V, R_L = 10k\Omega$                                                                                                                              | • | -0.7<br>-0.5                                         | -1/1.6                          | 1.4<br>1.2          | V                                      |

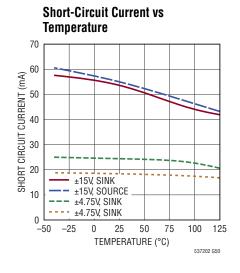

| I <sub>OUT</sub> | Output Short Circuit Current   |                                                                                                                                                                  | • | 35<br>30                                             | 55                              |                     | mA<br>mA                               |

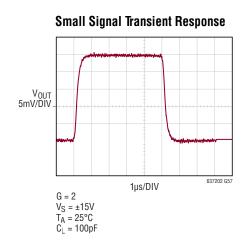

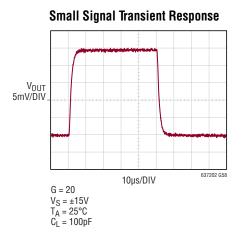

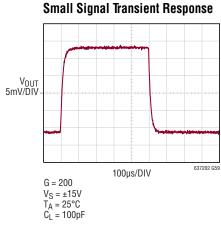

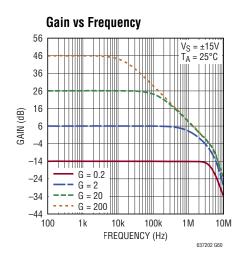

| BW               | -3dB Bandwidth                 | G = 0.2<br>G = 1<br>G = 10<br>G = 100<br>G = 200                                                                                                                 |   |                                                      | 4<br>2<br>1<br>140<br>15        |                     | MHz<br>MHz<br>MHz<br>kHz<br>kHz        |

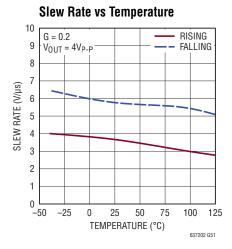

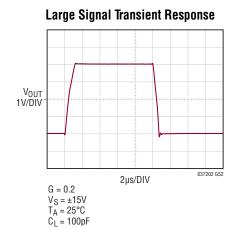

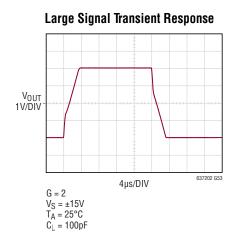

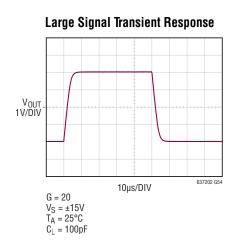

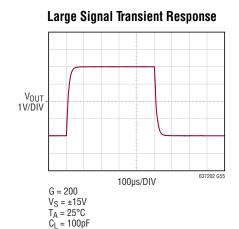

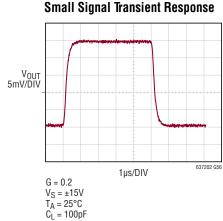

| SR               | Slew Rate                      | $G = 1, V_{OUT} = \pm 2.5V$                                                                                                                                      |   |                                                      | 3.5                             |                     | V/µs                                   |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the specified temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_S = \pm 15V$ , $V_{CM} = V_{REF1} = V_{REF2} = 0V$ , $V_{CLL0} = V^-$ , $V_{CLH1} = V^+$ , $R_L = 4k\Omega$ .

| SYMBOL               | PARAMETER                                                  | CONDITIONS                                                                        |   | MIN                | TYP                             | MAX           | UNITS                      |

|----------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------|---|--------------------|---------------------------------|---------------|----------------------------|

| t <sub>S</sub>       | Settling Time                                              | 4.096V Output Step to 0.0015%<br>G = 0.2<br>G = 1<br>G = 10<br>G = 100<br>G = 200 |   |                    | 1.8<br>2.5<br>12.4<br>68<br>135 |               | µs<br>µs<br>µs<br>µs<br>µs |

| R <sub>REFIN</sub>   | REF Input Resistance                                       | REF1 or REF2, Untested REF pin floating                                           |   |                    | 14                              |               | kΩ                         |

| I <sub>REFIN</sub>   | REF Input Current                                          | $V_{+IN} = V_{-IN} = V_{REF1} = V_{REF2} = 0V$ , REF1 or REF2                     | • | -36<br>-50         | -24                             | -12<br>0      | μA<br>μA                   |

| $\overline{V_{REF}}$ | REF Voltage Range                                          | REF1 or REF2                                                                      | • | V-                 |                                 | V+            | V                          |

| A <sub>VREF</sub>    | REF Gain to Output                                         | V <sub>REF1</sub> = 0V to 5V, V <sub>REF2</sub> = 0V                              |   |                    | 0.5                             |               | V/V                        |

|                      | REF Gain Error                                             | V <sub>REF1</sub> = 0V to 5V, V <sub>REF2</sub> = 0V                              | • | -250<br>-300       | ±75                             | 250<br>300    | ppm<br>ppm                 |

|                      | CLLO Input Current                                         | V <sub>CLLO</sub> = 0V                                                            | • |                    |                                 | 1             | μΑ                         |

|                      | CLHI Input Current                                         | V <sub>CLHI</sub> = 5V                                                            | • |                    |                                 | 1             | μA                         |

|                      | CLLO Input Operating Voltage Range                         | Outside this Range CLLO is Disabled                                               | • | V <sup>-</sup> + 3 |                                 | V+ - 2        | V                          |

|                      | CLHI Input Operating Voltage Range                         | Outside this Range CLHI is Disabled                                               | • | V <sup>-</sup> + 2 |                                 | V+ - 2.5      | V                          |

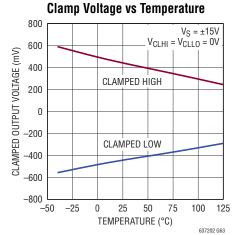

|                      | CLLO Clamp Voltage (V <sub>OUT</sub> – V <sub>CLLO</sub> ) |                                                                                   | • | -0.57<br>-0.74     | -0.45                           |               | V                          |

|                      | CLHI Clamp Voltage (V <sub>OUT</sub> – V <sub>CLHI</sub> ) |                                                                                   | • |                    | 0.45                            | 0.55<br>0.755 | V                          |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** Gains higher than 200 are possible but the resulting low  $R_{\rm G}$  values can make PCB and package lead resistance a significant error source.

**Note 3:** For gains greater than 0.2V/V, gain tests are performed with –IN at mid-supply and +IN driven. The gain of 0.2V/V testing is performed with –IN and +IN driven differentially.

**Note 4:** When the gain is greater than 0.2 the gain error and gain drift specifications do not include the effect of external gain set resistor R<sub>G</sub>.

Note 5: This specification is guaranteed by design.

Note 6: This specification is guaranteed with high-speed automated testing.

**Note 7:** This parameter is measured in a high speed automatic tester that does not measure the thermal effects with longer time constants. The

magnitude of these thermal effects are dependent on the package used, PCB layout, heat sinking and air flow conditions.

**Note 8:** For more information on how offsets relate to the amplifiers, see section "Input and Output Offset Voltage" in the Applications section.

**Note 9:** Hysteresis in output voltage is created by mechanical stress that differs depending on whether the IC was previously at a higher or lower temperature. Output voltage is always measured at 25°C, but the IC is cycled to the hot or cold temperature limit before successive measurements. Hysteresis is roughly proportional to the square of the temperature change. For instruments that are stored at well controlled temperatures (within 20 or 30 degrees of operational temperature), hysteresis is usually not a significant error source. Typical hysteresis is the worst case of 25°C to cold to 25°C or 25°C to hot to 25°C, preconditioned by one thermal cycle.

Note 10: Referred to the input.

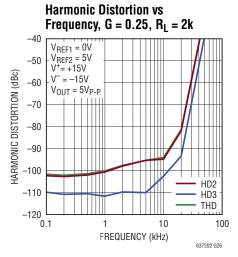

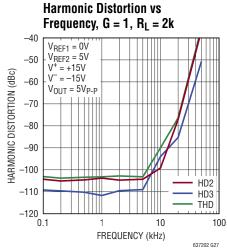

$T_A = 25^{\circ}C$ ,  $V_S = \pm 15V$ ,  $V_{CM} = V_{REF1} = V_{REF2} = 0V$ ,  $V_{CLL0} = V^-$ ,  $V_{CLH1} = V^+$ ,  $R_L = 4k$ , unless otherwise noted.

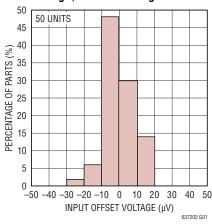

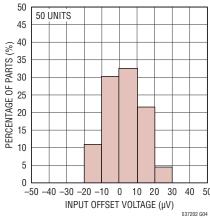

#### Distribution of Input Offset Voltage, MS16E Package

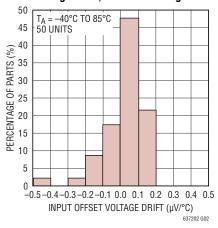

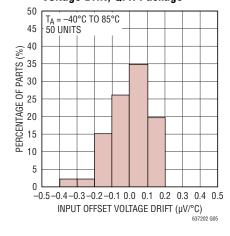

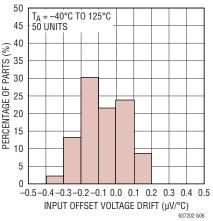

#### Distribution of Input Offset Voltage Drift, MS16E Package

#### Distribution of Input Offset Voltage Drift, MS16E Package

#### Distribution of Input Offset Voltage, QFN Package

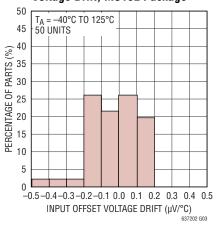

#### Distribution of Input Offset Voltage Drift, QFN Package

Distribution of Input Offset Voltage Drift, QFN Package

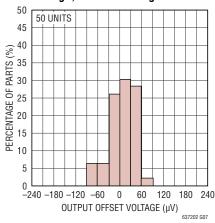

#### Distribution of Output Offset Voltage, MS16E Package

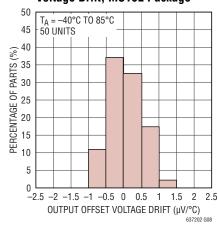

#### Distribution of Output Offset Voltage Drift, MS16E Package

#### Distribution Output Offset Voltage Drift, MS16E Package

$T_A = 25$ °C,  $V_S = \pm 15$ V,  $V_{CM} = V_{REF1} = V_{REF2} = 0$ V,  $V_{CLL0} = V^-$ ,  $V_{CLHI} = V^+$ ,  $R_L = 4$ k, unless otherwise noted.

#### Distribution of Output Offset Voltage, QFN Package

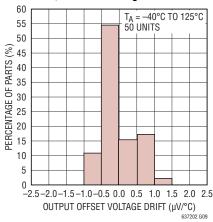

#### Distribution of Output Offset Voltage Drift, QFN Package

#### Distribution of Output Offset Voltage Drift, QFN Package

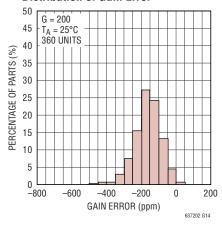

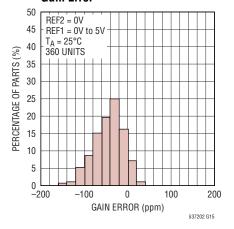

#### **Distribution of Gain Error**

#### **Distribution of Gain Error**

# Distribution of REF Divide Gain Error

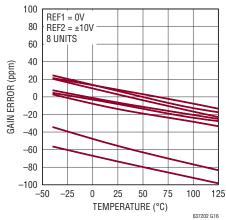

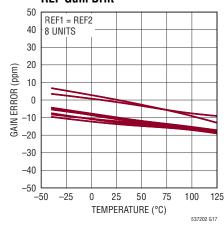

#### **REF Divider Gain Drift**

#### **REF Gain Drift**

#### Gain Drift (G = 0.2)

$T_A = 25$ °C,  $V_S = \pm 15$ V,  $V_{CM} = V_{REF1} = V_{REF2} = 0$ V,  $V_{CLL0} = V^-$ ,  $V_{CLH1} = V^+$ ,  $R_L = 4$ k, unless otherwise noted.

$T_A = 25$ °C,  $V_S = \pm 15$ V,  $V_{CM} = V_{REF1} = V_{REF2} = 0$ V,  $V_{CLL0} = V^-$ ,  $V_{CLH1} = V^+$ ,  $R_L = 4$ k, unless otherwise noted.

637202 G36

TIME (1s/DIV)

100

FREQUENCY (Hz)

1k

10k

100k

637202 G35

0.1

100

FREQUENCY (Hz)

1k

10k

100k

637202 G34

0.1

$T_A = 25^{\circ}C$ ,  $V_S = \pm 15V$ ,  $V_{CM} = V_{REF1} = V_{REF2} = 0V$ ,  $V_{CLL0} = V^-$ ,  $V_{CLH1} = V^+$ ,  $R_L = 4k$ , unless otherwise noted.

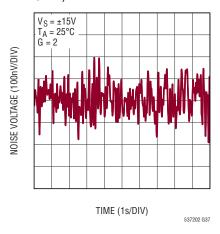

#### 0.1Hz to 10Hz Noise Voltage, G = 2, RTI

0.1Hz to 10Hz Noise Voltage, G = 20, RTI

0.1Hz to 10Hz Noise Voltage, G = 200, RTI

0.1Hz to 10Hz Noise Current, Unbalanced Source R

0.1Hz to 10Hz Noise Current, Balanced Source R

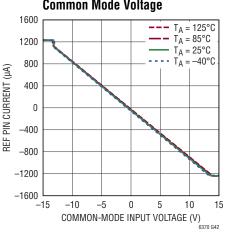

REF Pin Current vs Input Common Mode Voltage

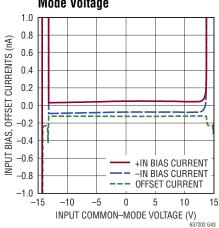

Input Bias Current vs Common Mode Voltage

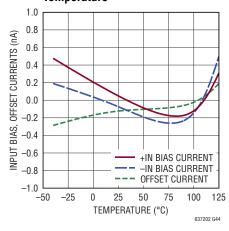

Input Bias and Offset Current vs Temperature

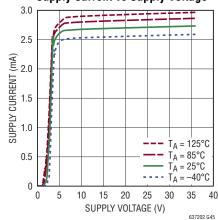

#### **Supply Current vs Supply Voltage**

$T_A = 25^{\circ}C$ ,  $V_S = \pm 15V$ ,  $V_{CM} = V_{REF1} = V_{REF2} = 0V$ ,  $V_{CLL0} = V^-$ ,  $V_{CLH1} = V^+$ ,  $R_L = 4k$ , unless otherwise noted.

$T_A = 25^{\circ}C$ ,  $V_S = \pm 15V$ ,  $V_{CM} = V_{REF1} = V_{REF2} = 0V$ ,  $V_{CLL0} = V^-$ ,  $V_{CLH1} = V^+$ ,  $R_L = 4k$ , unless otherwise noted.

# PIN FUNCTIONS (MS16E/QFN20)

- $-R_{G,F}$  (Pin 1/Pin 19): For use with an external gain setting resistor. This connection should be routed to the gain setting resistor separately from  $-R_{G,S}$  in order to minimize gain errors.

- $-R_{G,S}$  (Pin 2/Pin 20): For use with an external gain setting resistor. This connection should be routed to the gain setting resistor separately from  $-R_{G,F}$  in order to minimize gain errors.

- **-IN (Pin 4/Pin 2):** Negative Input Terminal. This input is high impedance.

- **+IN (Pin 5/Pin 5):** Positive Input Terminal. This input is high impedance.

- **CLLO (Pin 7/Pin 8):** Low Side Clamp Input. The voltage applied to the CLLO pin defines the lower voltage limit of the output. Typically, the output clamps 500mV below the voltage applied to the CLLO pin. Do not float CLLO.

- **V**<sup>-</sup> (**Pin 8/Pin 7**): Negative Power Supply. A bypass capacitor should be used between supply pins and ground.

- **CLHI (Pin 9/Pin 10):** High Side Clamp Input. The voltage applied to the CLHI pin defines the upper voltage limit of the output. Typically, the output clamps 500mV above the voltage applied to the CLHI pin. Do not float CLHI.

- **REF1 (Pin 10/Pin 12):** Reference for the output voltage. REF1 can be tied to REF2 and used as a reference for the output. REF1 can also be used with REF2 to form a voltage divider and level shift the output.

- **OUTPUT (Pin 11/Pin 13):** Output voltage referenced to the REF pins.

- V<sup>+</sup> (Pin 12/Pin 14): Positive Power Supply. A bypass capacitor should be used between supply pins and ground.

- **REF2 (Pin 13/Pin 15):** Reference for the output voltage. REF2 can be tied to REF1 and used as a reference for the output. REF2 can also be used with REF1 to form a voltage divider and level shift the output.

- $+R_{G,S}$  (Pin 15/Pin 17): For use with an external gain setting resistor. This connection should be routed to the gain setting resistor separately from  $+R_{G,F}$  in order to minimize gain errors.

- $+R_{G,F}$  (Pin 16/Pin 18): For use with an external gain setting resistor. This connection should be routed to the gain setting resistor separately from  $+R_{G,S}$  in order to minimize gain errors.

- NIC (Pins 3, 6, 14/Pins 1, 3, 4, 6, 11, 16): No Internal Connection.

- **DNC (QFN Pin 9):** Do Not Connect. This pin should float.

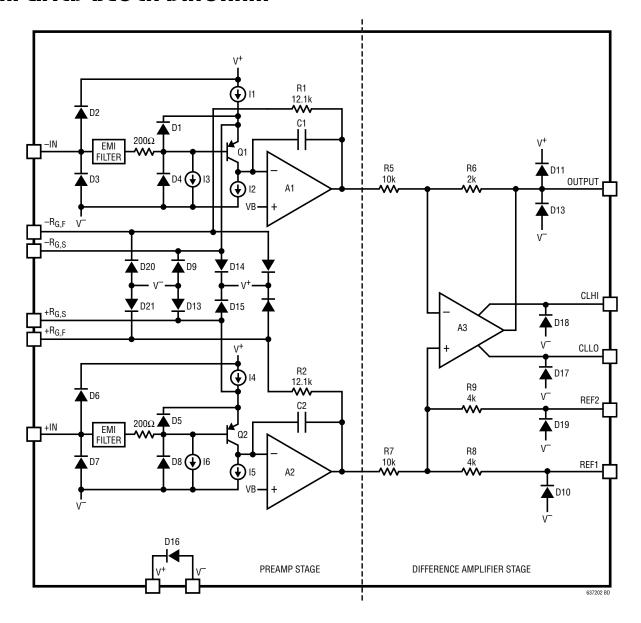

# SIMPLIFIED BLOCK DIAGRAM

## THEORY OF OPERATION

The LT6372-0.2 is an improved version of the classic three op amp instrumentation amplifier topology that incorporates features to improve accuracy and simplify interfacing to ADCs. Laser trimming and proprietary monolithic construction allow for tight matching and extremely low drift of circuit parameters over the specified temperature range. Refer to the Simplified Block Diagram to aid in understanding the following circuit description. The collector currents in Q1 and Q2 as well as I1 and I4 are trimmed to minimize input offset voltage drift, thus assuring a high level of performance. R1 and R2 are trimmed to an absolute value of 12.1k to assure that the gain can be set accurately (0.15% at G = 100) with only one external resistor,  $R_G$ . The value of R<sub>G</sub> determines the transconductance of the preamp stage. As R<sub>G</sub> is reduced to increase the programmed gain, the transconductance of the input preamp stage also increases to that of the input transistors Q1 and Q2. This causes the open-loop gain to increase when the programmed gain is increased, reducing the input related errors and noise. The input voltage noise at high gains is determined only by Q1 and Q2. At lower gains, noise of the difference amplifier and preamp gain setting resistors may increase the noise. The gain bandwidth product is determined by C1, C2 and the preamp transconductance, which increases with programmed gain. Therefore, the bandwidth is self-adjusting and does not drop directly proportional to gain.

The input transistors Q1 and Q2 offer excellent matching, drift and noise performance, which is due to using a proprietary high performance process, as well as low input bias current due to the high beta of these input devices. The input bias current is further reduced by trimming I3 and I6. The collector currents in Q1 and Q2 are held constant due to the feedback through the Q1-A1-R1 loop and Q2-A2-R2 loop. The action of the amplifier loops impresses the differential input voltage across the external gain set resistor  $R_{\rm G}$ . Since the current that flows through  $R_{\rm G}$  also flows through R1 and R2, the ratios provide a gained-up differential voltage,

$$G = 1 + \frac{R1 + R2}{R_G}$$

to the difference amplifier A3. The difference amplifier removes the common mode voltage and provides a single-ended output voltage referenced to the average of the voltages on REF1 and REF2. This split reference resistor configuration allows the output voltage to be easily level shifted to the center of an ADCs input range without external components. The offset voltage of the difference amplifier is trimmed to minimize output offset voltage drift, thus assuring a high level of performance, even in low gains. Resistors R5 to R9 are trimmed to maximize CMRR and minimize gain error. The resulting gain equation is:

$$G = 0.2 \left( 1 + \frac{24.2k}{R_G} \right)$$

Solving for the gain set resistor gives:

$$R_G = \frac{24.2k}{5G-1}$$

Table 1 shows appropriate 1% resistor values for a variety of gains.

Table 1. LT6372-0.2 Gain and  $R_{\rm G}$  Lookup.

| Resulting Gains for V | Resulting Gains for Various 1% Standard Resistor Values |  |  |  |  |  |

|-----------------------|---------------------------------------------------------|--|--|--|--|--|

| Gain                  | Standard 1% Resistor Value ( $\Omega$ )                 |  |  |  |  |  |

| 0.2                   | -                                                       |  |  |  |  |  |

| 0.399                 | 24.3k                                                   |  |  |  |  |  |

| 0.499                 | 16.2k                                                   |  |  |  |  |  |

| 0.8                   | 8.06k                                                   |  |  |  |  |  |

| 1.001                 | 6.04k                                                   |  |  |  |  |  |

| 2.013                 | 2.67k                                                   |  |  |  |  |  |

| 5.04                  | 1k                                                      |  |  |  |  |  |

| 9.9                   | 499                                                     |  |  |  |  |  |

| 20.12                 | 243                                                     |  |  |  |  |  |

| 49.79                 | 97.6                                                    |  |  |  |  |  |

| 99.58                 | 48.7                                                    |  |  |  |  |  |

| 199.4                 | 24.3                                                    |  |  |  |  |  |

| 496.1                 | 9.76                                                    |  |  |  |  |  |

| 994                   | 4.87                                                    |  |  |  |  |  |

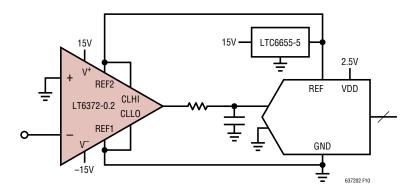

Additionally, The LT6372-0.2 has two integrated output voltage clamps which can be used to limit the voltage

applied to an ADCs input. Typically, CLHI is tied to the ADC's reference and CLLO is tied to the ADC's ground connection.

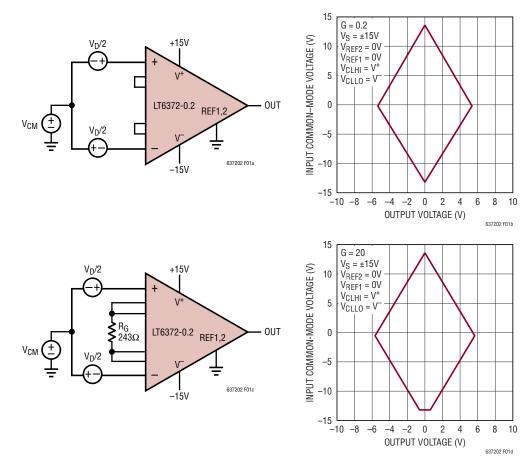

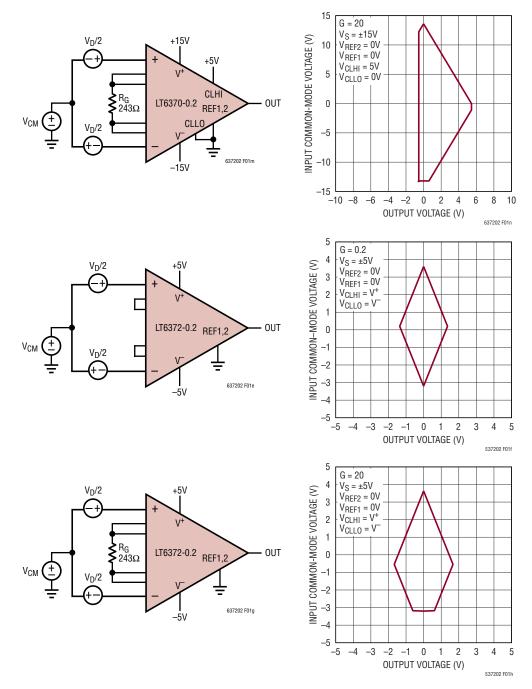

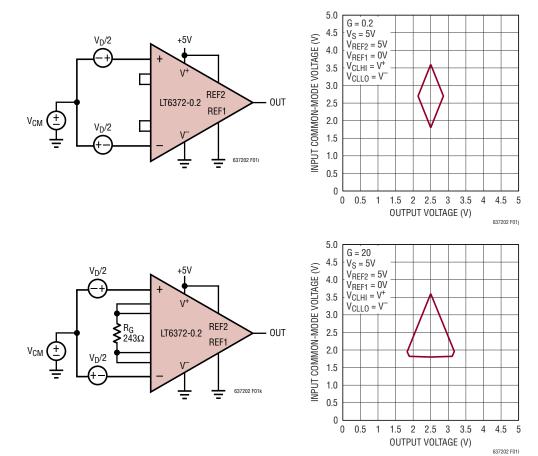

#### Valid Input and Output Range

Instrumentation amplifiers traditionally specify a valid input common mode range and an output swing range. This however often fails to identify limitations associated

with internal swing limits. Referring to the Simplified Block Diagram, the output swing of pre-amplifiers A1 and A2 as well as the common-mode input range of the difference amplifier A3 impose limitations on the valid operating range. Figure 1 shows the operating region where a valid output is produced for various configurations. Further valid input and output range plots can be generated using the Diamond Plot Tool.

Figure 1. Input Common Mode Range vs Output Voltage

Figure 1 (Continued). Input Common Mode Range vs Output Voltage

Figure 1 (Continued). Input Common Mode Range vs Output Voltage

#### **Output Level Shifting with Split Reference Pins**

The LT6372-0.2's difference amplifier features split reference pins, REF1 and REF2, which allow the output to be easily and accurately level shifted without the use of external circuitry. REF1 and REF2 are typically tied to an ADC ground and reference respectively. In this configuration the amplifier's output is conveniently level shifted to the center of the ADC input range.

If REF1 and REF2 are shorted to each other, they can function as the reference for the output voltage like a traditional instrumentation amplifier.

Parasitic resistance in series with REF1 and REF2 should be minimized to preserve CMRR and gain performance. It is also important to note that the drift in any circuitry used to drive REF1 or REF2 can result in an additional output drift term. Therefore, it may be important to consider the temperature accuracy of the circuitry used to drive the REF pin.

#### **Gain Setting Resistor Connections**

Each pre-amplifier gives a set of RG connection terminals which should be routed separately to the gain setting resistor. Doing this minimizes the impact which parasitic trace and lead resistance has on gain accuracy. When routing to the gain setting resistors, large loops should be avoided as they can couple noise into the amplifier.

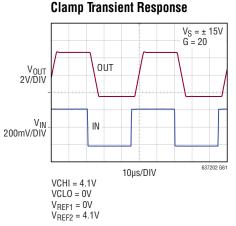

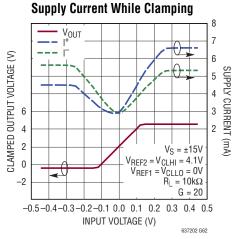

#### **Output Clamps**

The CLHI and CLLO clamp pins limit the output voltage swing of the LT6372-0.2. CLHI and CLLO are typically tied to the ADC supply/reference and ADC ground respectively. In this case the ADC input is protected from being overdriven by the LT6372-0.2 which is likely running off a higher supply voltage.

When the CLLO is tied to OV, attempts to drive the output below OV will be clamped at -0.45V typically. When CLHI is tied to 5V, attempts to drive the output above 5V will be clamped at 5.45V typically.

CLHI and CLLO are high impedance inputs and do not conduct significant current during clamping. Rather, internal amplifier nodes are controlled by CLHI and CLLO to limit the output voltage.

In applications where clamping is not desired, CLLO should be tied to V<sup>-</sup> and CLHI to V<sup>+</sup> to disable clamping.

#### **Input and Output Offset Voltage**

The offset voltage of the LT6372-0.2 has two main components: the input offset voltage due to the input amplifiers and the output offset due to the output amplifier. The total offset voltage referred to the input (RTI) is found by dividing the output offset by the programmed gain and adding it to the input offset voltage. At high gains the input offset voltage dominates, whereas at low gains the output offset voltage dominates. The total offset voltage is:

Total input offset voltage (RTI) =  $V_{OSI} + V_{OSO}/G$

Total output offset voltage (RTO) = V<sub>OSI</sub> • G + V<sub>OSO</sub>

The preceding equations can also be used to calculate offset drift in a similar manner.

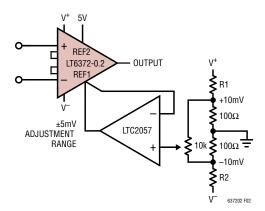

#### **Output Offset Trimming**

The LT6372-0.2 is laser trimmed for low offset voltage so that no external offset trimming is required for most applications. In the event that the offset voltage needs to be adjusted, the circuit in Figure 2 is an example of an optional offset adjustment circuit. The op amp buffer provides a low impedance signal to the REF pin in order to achieve the best CMRR and lowest gain error.

Figure 2. Optional Trimming of Output Offset Voltage

#### Thermocouple Effects

In order to achieve accuracy on the microvolt level, thermocouple effects must be considered. Any connection of dissimilar metals forms a thermoelectric junction and

Rev. C

generates a small temperature-dependent voltage. Also known as the Seebeck Effect, these thermal EMFs can be the dominant error source in low-drift circuits.

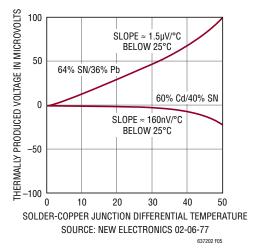

Connectors, switches, relay contacts, sockets, resistors, and solder are all candidates for significant thermal EMF generation. Even junctions of copper wire from different manufacturers can generate thermal EMFs of 200nV/°C, which is comparable to the maximum input offset voltage drift specification of the LT6372-0.2. Figure 3 and Figure 4 illustrate the potential magnitude of these voltages and their sensitivity to temperature.

In order to minimize thermocouple-induced errors, attention must be given to circuit board layout and component selection. It is good practice to minimize the number of junctions in the amplifier's input and  $R_{G}$  signal paths and avoid connectors, sockets, switches, and relays whenever possible. If such components are required, they should be selected for low thermal EMF characteristics. Furthermore, the number, type, and layout of junctions should be matched for both inputs with respect to thermal gradients on the circuit board. Doing so may involve deliberately introducing dummy junctions to offset unavoidable junctions.

Air currents can also lead to thermal gradients and cause significant noise in measurement systems. It is important to prevent airflow across sensitive circuits. Doing so will often reduce thermocouple noise substantially. Placing PCB input traces close together, and on an internal PCB layer, can help minimize temperature differentials resulting from air currents reacting with the input trace thermal surface area.

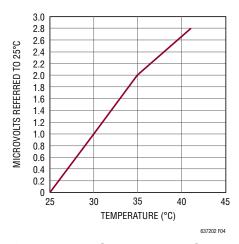

Figure 3. Thermal EMF Generated by Two Copper Wires From Different Manufacturers

Figure 4. Solder-Copper Thermal EMFs

#### Reducing Board-Related Leakage Effects

Leakage currents can have a significant impact on system accuracy, particularly in high temperature and high voltage applications. Quality insulation materials should be used, and insulating surfaces should be cleaned to remove fluxes and other residues. For humid environments, surface coating may be necessary to provide a moisture barrier.

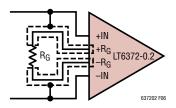

Leakage into the  $R_G$  pin conducts through the on-chip feedback resistor, creating an error at the output of the preamplifiers. This error is independent of gain and degrades accuracy the most at low gains. This leakage can be minimized by encircling the  $R_G$  connections with a guard-ring operated at a potential very close to that of the  $R_G$  pins. NIC pins adjacent to each  $R_G$  pin can be used to simplify the implementation of this guard-ring. These NIC pins do not provide any bias and have no internal connections. In some cases, the guard-ring can be connected to the input voltage which biases one diode drop below  $R_G$ .

Figure 5. Guard-Rings Can Be Used to Minimize Leakage into the  $\ensuremath{\text{R}}_{\ensuremath{\text{G}}}$  Pins

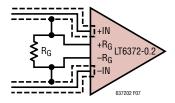

Leakage into the input pins reacts with the source resistance, creating an error directly at the input. This leakage can be minimized by encircling the input connections with a guard-rings operated at a potential very close to that of the input pins. In some cases, the guard-ring can be connected to  $R_{\mbox{\scriptsize G}}$  which biases one diode above the input.

Figure 5 and Figure 6 show the force and sense  $R_G$  connections as a single  $R_G$  connection for simplicity.

For the lowest leakage, amplifiers can be used to drive the guard ring. These buffers must have very low input bias current since that will now be a leakage.

Figure 6. Guard-Rings Can Be Used to Minimize Leakage into the Input Pins

#### **Input Bias Current Return Path**

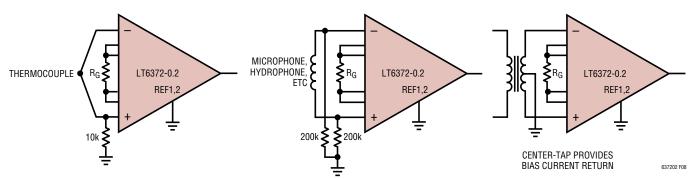

The low input bias current of the LT6372-0.2 (800pA max) and high input impedance (225G $\Omega$ ) allow the use of high impedance sources without introducing additional offset voltage errors, even when the full common mode range is required. However, a path must be provided for the input bias currents of both inputs when a purely differential signal is being amplified. Without this path, the inputs will float to either rail and exceed the input common mode range of the LT6372-0.2, resulting in a saturated input amplifier. Figure 7 shows three examples of an input bias current path. The first example is of a purely differential signal source with a  $10k\Omega$  input current path to ground. Since the impedance of the signal source is low, only one resistor is needed. Two matching resistors are needed for higher impedance signal sources as shown in the second example. Balancing the input impedance improves both AC and DC common mode rejection and DC offset. The need for input resistors is eliminated if a center tap is present as shown in the third example.

Figure 7. Providing an Input Common Mode Current Path

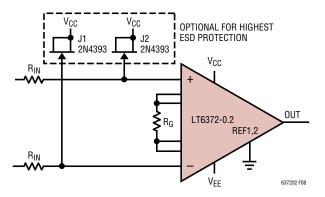

#### **Input Protection**

Additional input protection can be achieved by adding external resistors in series with each input. If low value resistors are needed, a clamp diode from the positive supply to each input will help improve robustness. A 2N4394 drain/source to gate is a good low leakage diode which can be used as shown in Figure 8. Robust input resistors should be chosen, such as carbon composite or bulk metal foil. Metal film and carbon film should not be used because of their poor performance.

Figure 8. Input Protection

#### **Maintaining AC CMRR**

To achieve optimum AC CMRR, it is important to balance the capacitance on the  $R_{\rm G}$  gain setting pins. Furthermore, if the source resistance on each input is not equal, adding an additional resistance to one input to improve input source resistance matching will improve AC CMRR.

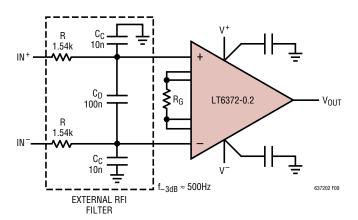

#### RFI Reduction/Internal RFI Filter

In many industrial and data acquisition applications, the LT6372-0.2 will be used to amplify small signals accurately in the presence of large common mode voltages or high levels of noise. Typically, the sources of these very small signals (on the order of microvolts or millivolts) are sensors that can be a significant distance from the signal conditioning circuit. Although these sensors may be connected to signal conditioning circuitry using shielded or unshielded twisted-pair cabling, the cabling may act as an antenna, conveying very high frequency interference directly into the input stage of the LT6372-0.2.

The amplitude and frequency of the interference can have an adverse effect on an instrumentation amplifier's input stage by causing any unwanted DC shift in the amplifier's input offset voltage. This well known effect is called RFI rectification and is produced when out-of-band interference is coupled (inductively, capacitively or via radiation) and rectified by the instrumentation amplifier's input transistors. These transistors act as high frequency signal detectors, in the same way diodes were used as RF envelope detectors in early radio designs. Regardless of the type of interference or the method by which it is coupled into the circuit, an out-of-band error signal appears in series with the instrumentation amplifier's inputs.

To help minimize this effect, the LT6372-0.2 has 50MHz on-chip RFI filters to help attenuate high frequencies before they can interact with its input transistors. These on-chip filters are well matched due to their monolithic construction, which helps minimize any degradation in AC CMRR. To reduce the effect of these out-of-band signals on the input offset voltage of the LT6372-0.2 further, an additional external low-pass filter can be used at the inputs. The filter should be located very close to the input pins of the circuit. An effective filter configuration is illustrated in Figure 9, where three capacitors have been added to the inputs of the LT6372-0.2.

The filter limits the input signal according to the following relationship:

$$FilterFreq_{DIFF} = \frac{1}{2\pi R(2C_D + C_C)}$$

$$FilterFreq_{CM} = \frac{1}{2\pi RC_C}$$

where  $C_D \ge 10C_C$ .

$C_D$  affects the difference signal.  $C_C$  affects the common-mode signal. Any mismatch in R  $\times$   $C_C$  degrades the LT6372-0.2 CMRR. To avoid inadvertently reducing CMRR-bandwidth performance, make sure that  $C_C$  is at least one magnitude smaller than  $C_D$ . The effect of mismatched  $C_C$ s is reduced with a larger  $C_D$ :  $C_C$  ratio.

Figure 9. Adding a Simple External RC Filter at the Inputs to an Instrumentation Amplifier Is Effective in Further Reducing Rectification of High Frequency Out-Of-Band Signals

To avoid any possibility of common mode to differential mode signal conversion, match the common mode low-pass filter on each input to 1% or better. Here are the steps to help determine appropriate values for the filter:

1. Pick R and  $C_D$  to have a low pass pole at least 10x higher than the highest signal of interest (e.g. 500Hz for a 50Hz signal) using:

FilterFreq<sub>DIFF</sub> =

$$\frac{1}{2\pi R(2C_D + C_C)}$$

=

$$\frac{1}{2\pi R(2C_D + 0.1C_D)}$$

=

$$\frac{1}{4.2\pi RC_D}$$

2. Select  $C_C = C_D/10$ .

If implemented this way, the common-mode pole frequency is placed about 20x higher than the differential pole frequency. Here are the differential and common-mode low pass pole frequencies for the values shown in Figure 9:

$FilterFreq_{DIFF} = 500Hz$

$FilterFreq_{CM} = 10kHz$

#### Benefits when using LT6372-0.2 as an ADC Driver

The LT6372-0.2 incorporates several features which enable better interface to ADCs compared to traditional instrumentation amplifiers. Often, larger signals need to be attenuated to match the input range of an ADC. Additionally, a level shift is often required to center the amplifier's output to the ADC's input range. Figure 10 shows the LT6372-0.2 performing both these functions while maintaining high input impedance and providing protective clamping to the ADC's input.

Consider the alternative circuit in Figure 11, which shows a traditional instrumentation amplifier with a handful of additional components to perform the attenuation and level shifting functions. The added resistive dividers to attenuate the output and the ADC reference must have excellent initial tolerance and temperature coefficient. The operational amplifiers use to buffer the divided down reference and amplifier output must also have precision specifications over temperature. In order to protect the ADC in this configuration, U1 should run off the same supplies as the ADC. This requires that the input and output of U1 be rail-to-rail, limiting choices and likely giving up some input range on the ADC. These additional components take up space, draw power, add noise, increase cost and add complexity when compared to the LT6372-0.2 solution.

Figure 10. LT6372-0.2 Integrated ADC Driving Solution

Figure 11. Alternative IA-ADC Interfacing Circuit

# TYPICAL APPLICATIONS

#### **Differential Output Instrumentation Amplifier**

# +IN +VS +OUT REF1,2 10k VBIAS -VS 10k LTC2057 -OUT

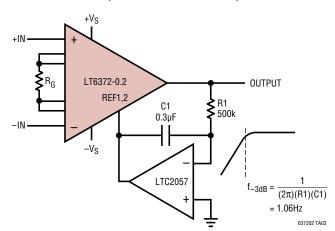

#### **AC Coupled Instrumentation Amplifier**

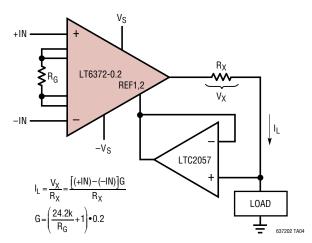

#### **Precision Voltage-to-Current Converter**

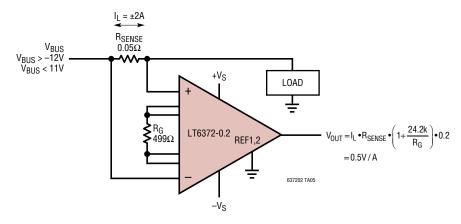

#### High Side, Bidirectional Current Sense

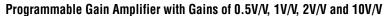

# PACKAGE DESCRIPTION

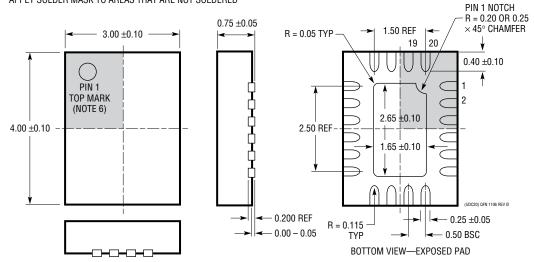

#### **UDC Package** 20-Lead Plastic QFN (3mm × 4mm)

(Reference LTC DWG # 05-08-1742 Rev Ø)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS APPLY SOLDER MASK TO AREAS THAT ARE NOT SOLDERED

#### NOTE:

- 1. DRAWING IS NOT A JEDEC PACKAGE OUTLINE

2. DRAWING NOT TO SCALE

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

# PACKAGE DESCRIPTION

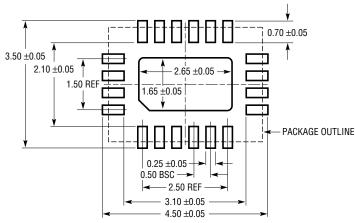

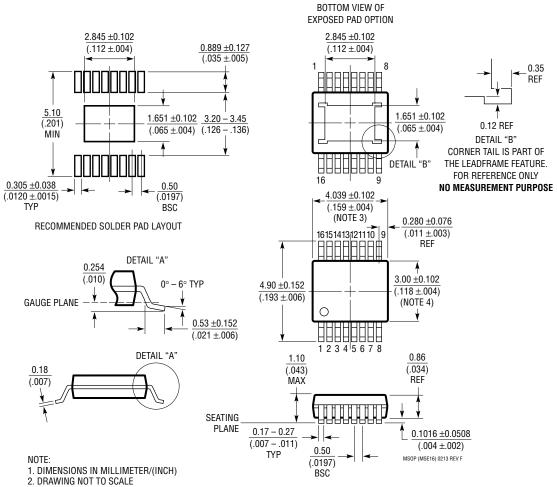

#### MSE Package 16-Lead Plastic MSOP, Exposed Die Pad

(Reference LTC DWG # 05-08-1667 Rev F)

- 2. DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

- 4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

- 5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX

- EXPOSED PAD DIMENSION DOES INCLUDE MOLD FLASH. MOLD FLASH ON E-PAD SHÁLL NOT EXCEED 0.254mm (.010") PER SIDE.

# TYPICAL APPLICATION

# **RELATED PARTS**

| PART NUMBER       | DESCRIPTION                          | COMMENTS                                                                                                                                                 |

|-------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instrumentation A | mplifiers                            |                                                                                                                                                          |

| AD8429            | Low Noise Instrumentation Amplifier  | $V_S = 36V$ , $I_S = 6.7$ mA, $V_{OS} = 50\mu V$ , BW = 15MHz, $e_{ni} = 1$ nV/ $\sqrt{Hz}$ , $e_{no} = 45$ nV/ $\sqrt{Hz}$                              |

| LT6372-1          | Low Drift Instrumentation Amplifier  | LT6372-0.2 with Min Gain = 1V/V                                                                                                                          |

| LT6370            | Low Drift Instrumentation Amplifier  | $V_S = 30V$ , $I_S = 2.65$ mA, $V_{OS} = 25\mu V$ , BW = 3.1MHz, $e_{ni} = 7$ nV/ $\sqrt{Hz}$ , $e_{no} = 65$ nV/ $\sqrt{Hz}$                            |

| LTC1100           | Zero-Drift Instrumentation Amplifier | $V_S = 18V$ , $I_S = 2.4$ mA, $V_{OS} = 10\mu V$ , BW = 19kHz, 1.9 $\mu V_{P-P}$ DC to 10Hz                                                              |

| AD8421            | Low Noise Instrumentation Amplifier  | $V_S = 36V, I_S = 2mA, V_{OS} = 25\mu V, BW = 10MHz, e_{ni} = 3nV/\sqrt{Hz}, e_{no} = 60nV/\sqrt{Hz}$                                                    |

| AD8221            | Low Power Instrumentation Amplifier  | $V_S = 36V$ , $I_S = 900\mu A$ , $V_{OS} = 25\mu V$ , $BW = 825kHz$ , $e_{ni} = 8nV/\sqrt{Hz}$ , $e_{no} = 75nV/\sqrt{Hz}$                               |

| LT1167            | Instrumentation Amplifier            | $V_S = 36V$ , $I_S = 900\mu A$ , $V_{OS} = 40\mu V$ , $BW = 1MHz$ , $e_{ni} = 7.5 \text{nV}/\sqrt{\text{Hz}}$ , $e_{no} = 67 \text{nV}/\sqrt{\text{Hz}}$ |

| AD620             | Low Power Instrumentation Amplifier  | $V_S = 36V, I_S = 900\mu A, V_{OS} = 50\mu V, BW = 1MHz, e_{ni} = 9nV/\sqrt{Hz}, e_{no} = 72nV/\sqrt{Hz}$                                                |

| LTC6800           | RRIO Instrumentation Amplifier       | $V_S = 5.5V$ , $I_S = 800\mu A$ , $V_{OS} = 100\mu V$ , $BW = 200kHz$ , $2.5\mu V_{P-P}$ DC to $10Hz$                                                    |

| LTC2053           | Zero-Drift Instrumentation Amplifier | $V_S = 11V$ , $I_S = 750\mu A$ , $V_{OS} = 10\mu V$ , BW = 200kHz, 2.5 $\mu V_{P-P}$ DC to 10Hz                                                          |

| LT1168            | Low Power Instrumentation Amplifier  | $V_S = 36V$ , $I_S = 350\mu A$ , $V_{OS} = 40\mu V$ , $BW = 400kHz$ , $e_{ni} = 10nV/\sqrt{Hz}$ , $e_{no} = 165nV/\sqrt{Hz}$                             |

| Operational Ampl  | ifiers                               |                                                                                                                                                          |

| LTC2057           | 40V Zero Drift Op Amp                | $V_{OS} = 4\mu V$ , Drift = 15nV/°C, $I_B = 200pA$ , $I_S = 900\mu A$                                                                                    |

| Analog to Digital | Converters                           |                                                                                                                                                          |

| LTC2389-16        | 16-Bit SAR ADC                       | 2.5Msps, 96dB SNR, 162.5mW                                                                                                                               |

| LTC2367-16        | 16-Bit SAR ADC                       | 500ksps, 94.7dB SNR, 6.8mW                                                                                                                               |

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Instrumentation Amplifiers category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below:

ADA4254RU-EBZ MCP6N16-001E/MF LT1102IN8#PBF AD694BRZ-REEL7 LT1101ISW AD521JDZ AD521KDZ AD521LDZ

AD524ADZ AD524BDZ AD524CDZ AD620ANZ AD621BNZ AD621BR AD622ANZ AD623ANZ AD623BNZ AD624ADZ

AD624CDZ AD624SD/883B AD625ADZ AD625BDZ AD625JNZ AD625KNZ AD625SD AD627BNZ AD693AD AD693AE AD693AQ

AD694AQ AD694ARZ-REEL AD694BRZ-REEL AD694JNZ AD8221ARMZ-R7 AD8224BCPZ-WP AD8224HBCPZ-WP

AD8226ARMZ-R7 AD8228ARMZ AD8228ARMZ-R7 AD8229HDZ AD8236ARMZ-R7 AD8237ARMZ-R7 AD8253ARMZ

AD8293G160BRJZ-R7 AD8293G80BRJZ-R2 AD8553ARMZ AD8553ARMZ AD8555ACPZ-REEL7 AD8556ACPZ-R2

AD8556ACPZ-REEL7