# 60V 2MHz Synchronous 4-Switch Buck-Boost Controller with Spread Spectrum

#### **FEATURES**

- 4-Switch Single Inductor Architecture Allows V<sub>IN</sub> Above, Below or Equal to V<sub>OUT</sub>

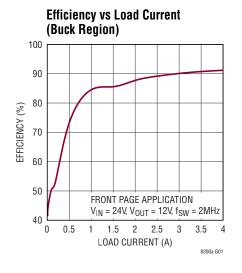

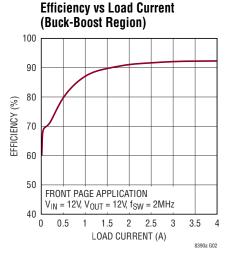

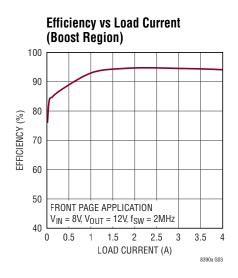

- Up to 95% Efficiency at 2MHz

- Proprietary Peak-Buck Peak-Boost Current Mode

- Wide V<sub>IN</sub> Range: 4V to 60V

- **±**1.5% Output Voltage Accuracy: 1V ≤ V<sub>OUT</sub> ≤ 60V

- ±3% Input or Output Current Accuracy with Monitor

- Spread Spectrum Frequency Modulation for Low EMI

- High Side PMOS Load Switch Driver

- No Top MOSFET Refresh Noise in Buck or Boost

- Adjustable and Synchronizable: 600kHz to 2MHz

- V<sub>OUT</sub> Disconnected from V<sub>IN</sub> During Shutdown

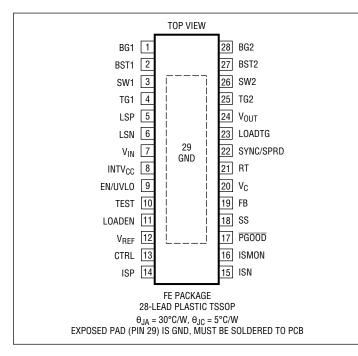

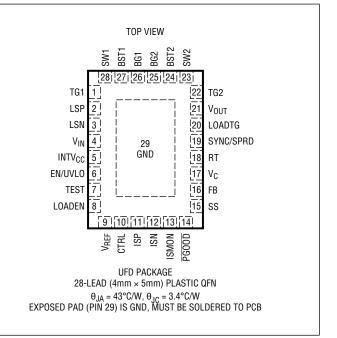

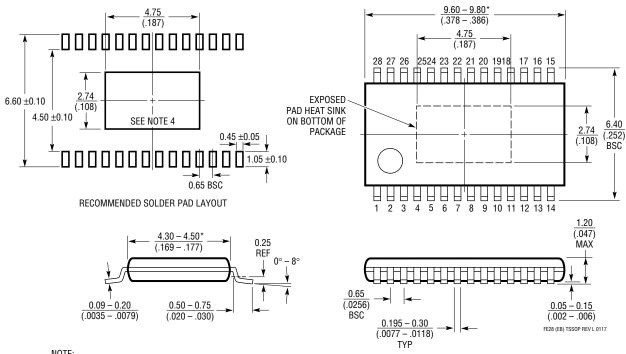

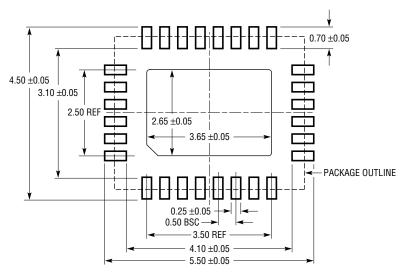

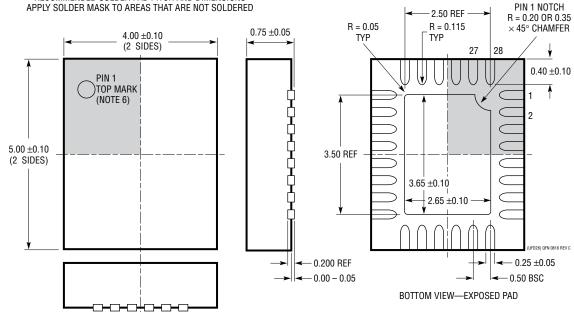

- Available in 28-Lead TSSOP with Exposed Pad and 28-Lead QFN (4mm × 5mm)

- AEC-Q100 Qualified for Automotive Applications

### **APPLICATIONS**

- Automotive, Industrial, Telecom Systems

- High Frequency Battery-Powered System

## DESCRIPTION

The LT®8390A is a synchronous 4-switch buck-boost DC/DC controller that regulates output voltage, input or output current from an input voltage above, below, or equal to the output voltage. The proprietary peak-buck peak-boost current mode control scheme allows adjustable and synchronizable 600kHz to 2MHz fixed frequency operation, or internal 25% triangle spread spectrum frequency modulation for low EMI. With a 4V to 60V input voltage range, 0V to 60V output voltage capability, and seamless low noise transitions between operation regions, the LT8390A is ideal for voltage regulator, battery and supercapacitor charger applications in automotive, industrial, telecom, and even battery-powered systems.

The LT8390A provides input or output current monitor and power good flag. Fault protection is also provided to detect output short-circuit condition, during which the LT8390A retries, latches off, or keeps running.

All registered trademarks and trademarks are the property of their respective owners.

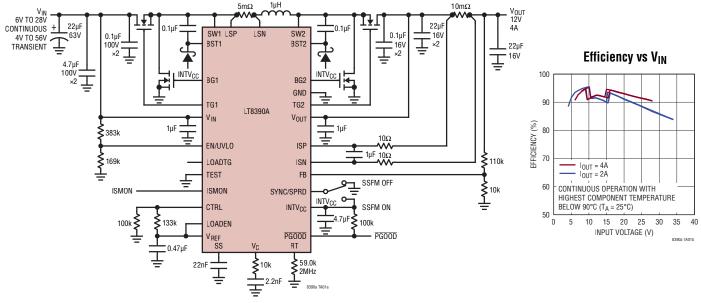

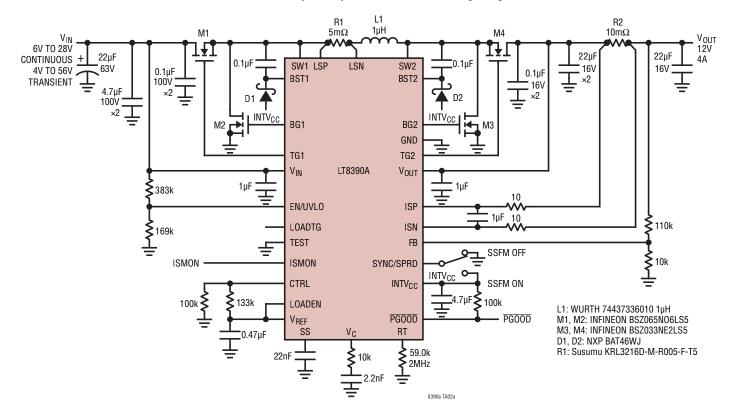

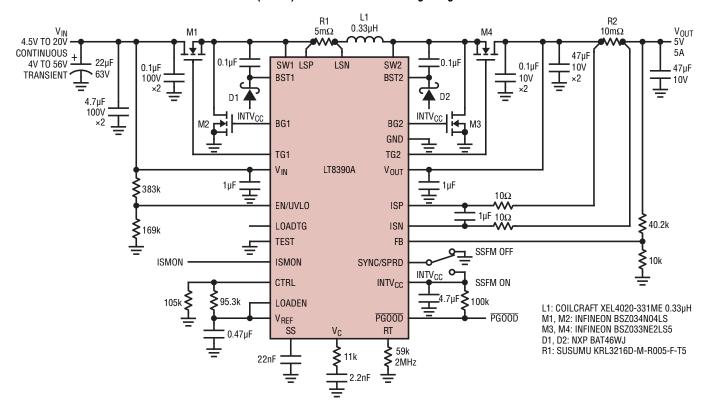

## TYPICAL APPLICATION

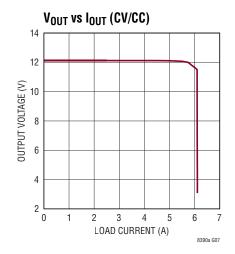

95% Efficient 48W (12V 4A) 2MHz Buck-Boost Voltage Regulator

# **ABSOLUTE MAXIMUM RATINGS** (Note 1)

| V <sub>IN</sub> , EN/UVLO, V <sub>OUT</sub> , ISP, ISN | 60V       |

|--------------------------------------------------------|-----------|

| (ISP-ISN)                                              | –1V to 1V |

| BST1, BST2                                             | 66V       |

| SW1, SW2, LSP, LSN                                     | 6V to 60V |

| INTV <sub>CC</sub> , (BST1-SW1), (BST2-SW2)            | 6V        |

| (BST1-LSP), (BST1-LSN)                                 | 6V        |

|                                                        |           |

| FB, LOADEN, SYNC/SPRD, CTRL, PGOOD                | .6V |

|---------------------------------------------------|-----|

| Operating Junction Temperature Range (Notes 2, 3) |     |

| LT8390AE40°C to 12                                | 5°C |

| LT8390AI                                          | 5°C |

| LT8390AH                                          | o°C |

| LT8390AJ40°C to 150                               | o°C |

| Storage Temperature Range65°C to 150              | 0°C |

# PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH     | TAPE AND REEL      | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|----------------------|--------------------|---------------|---------------------------------|-------------------|

| LT8390AEFE#PBF       | LT8390AEFE#TRPBF   | LT8390AFE     | 28-Lead Plastic TSSOP           | -40°C to 125°C    |

| LT8390AIFE#PBF       | LT8390AIFE#TRPBF   | LT8390AFE     | 28-Lead Plastic TSSOP           | -40°C to 125°C    |

| LT8390AHFE#PBF       | LT8390AHFE#TRPBF   | LT8390AFE     | 28-Lead Plastic TSSOP           | -40°C to 150°C    |

| LT8390AJFE#PBF       | LT8390AJFE#TRPBF   | LT8390AFE     | 28-Lead Plastic TSSOP           | -40°C to 150°C    |

| LT8390AEUFD#PBF      | LT8390AEUFD#TRPBF  | 8390A         | 28-Lead (4mm × 5mm) Plastic QFN | -40°C to 125°C    |

| LT8390AIUFD#PBF      | LT8390AIUFD#TRPBF  | 8390A         | 28-Lead (4mm × 5mm) Plastic QFN | -40°C to 125°C    |

| LT8390AJUFD#PBF      | LT8390AJUFD#TRPBF  | 8390A         | 28-Lead (4mm × 5mm) Plastic QFN | -40°C to 150°C    |

| LT8390AHUFD#PBF      | LT8390AHUFD#TRPBF  | 8390A         | 28-Lead (4mm × 5mm) Plastic QFN | -40°C to 150°C    |

| AUTOMOTIVE PRODUCTS* | *                  |               |                                 |                   |

| LT8390AJFE#WPBF      | LT8390AJFE#WTRPBF  | LT8390AFE     | 28-Lead Plastic TSSOP           | -40°C to 150°C    |

| LT8390AHFE#WPBF      | LT8390AHFE#WTRPBF  | LT8390AFE     | 28-Lead Plastic TSSOP           | -40°C to 150°C    |

| LT8390AJUFD#WPBF     | LT8390AJUFD#WTRPBF | 8390A         | 28-Lead (4mm × 5mm) Plastic QFN | -40°C to 150°C    |

| LT8390AHUFD#PBF      | LT8390AHUFD#WTRPBF | 8390A         | 28-Lead (4mm × 5mm) Plastic QFN | -40°C to 150°C    |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

<sup>\*\*</sup>Versions of this part are available with controlled manufacturing to support the quality and reliability requirements of automotive applications. These models are designated with a #W suffix. Only the automotive grade products shown are available for use in automotive applications. Contact your local Analog Devices account representative for specific product ordering information and to obtain the specific Automotive Reliability reports for these models.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25\,^{\circ}\text{C}$ (Note 2). $V_{IN} = 12\text{V}$ , $V_{EN/UVL0} = 1.5\text{V}$ unless otherwise noted.

| PARAMETER                                                                  | CONDITIONS                                                                 |   | MIN         | TYP      | MAX        | UNITS    |

|----------------------------------------------------------------------------|----------------------------------------------------------------------------|---|-------------|----------|------------|----------|

| Supply                                                                     |                                                                            |   |             |          |            |          |

| V <sub>IN</sub> Operating Voltage Range                                    |                                                                            | • | 4           |          | 60         | V        |

| V <sub>IN</sub> Quiescent Current                                          | V <sub>EN/UVLO</sub> = 0.3V                                                |   |             | 1        | 2          | μA       |

|                                                                            | V <sub>EN/UVLO</sub> = 1.1V                                                |   |             | 270      | 2.0        | μA       |

| V <sub>OUT</sub> Voltage Range                                             | Not Switching                                                              |   | 0           | 2.1      | 2.8        | MA<br>V  |

| V <sub>OUT</sub> Quiescent Current                                         | V <sub>EN/UVLO</sub> = 0.3V, V <sub>OUT</sub> = 12V                        | _ | U           | 0.1      | 0.5        |          |

| VOUT Quiescent outrent                                                     | $V_{EN/UVLO} = 0.3V, V_{OUT} = 12V$<br>$V_{EN/UVLO} = 1.1V, V_{OUT} = 12V$ |   |             | 0.1      | 0.5        | μΑ<br>μΑ |

|                                                                            | Not Switching, V <sub>OUT</sub> = 12V                                      |   | 20          | 40       | 60         | μA       |

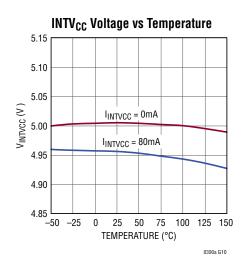

| Linear Regulators                                                          |                                                                            |   |             |          |            |          |

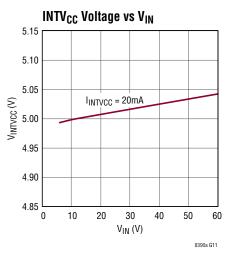

| INTV <sub>CC</sub> Regulation Voltage                                      | I <sub>INTVCC</sub> = 20mA                                                 |   | 4.85        | 5.0      | 5.15       | V        |

| INTV <sub>CC</sub> Load Regulation                                         | I <sub>INTVCC</sub> = 0mA to 80mA                                          |   |             | 1        | 4          | %        |

| INTV <sub>CC</sub> Line Regulation                                         | $I_{INTVCC}$ = 20mA, $V_{IN}$ = 6V to 60V                                  |   |             | 1        | 4          | %        |

| INTV <sub>CC</sub> Current Limit                                           | V <sub>INTVCC</sub> = 4.5V                                                 |   | 110         | 145      | 190        | mA       |

| INTV <sub>CC</sub> Dropout Voltage (V <sub>IN</sub> – INTV <sub>CC</sub> ) | $I_{INTVCC} = 20mA, V_{IN} = 4V$                                           |   |             | 160      |            | mV       |

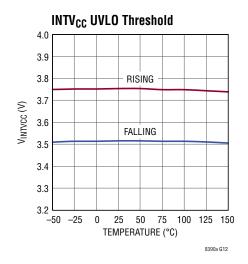

| INTV <sub>CC</sub> Undervoltage Lockout Threshold                          | Falling                                                                    |   | 3.44        | 3.54     | 3.64       | V        |

| INTV <sub>CC</sub> Undervoltage Lockout Hysteresis                         |                                                                            |   |             | 0.24     |            | V        |

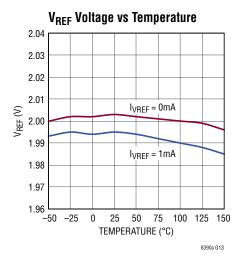

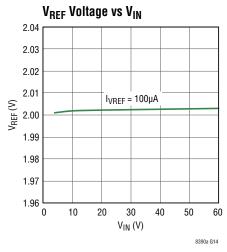

| V <sub>REF</sub> Regulation Voltage                                        | I <sub>VREF</sub> = 100μA                                                  | • | 1.97        | 2.00     | 2.03       | V        |

| V <sub>REF</sub> Load Regulation                                           | I <sub>VREF</sub> = 0mA to 1mA                                             |   |             | 0.4      | 1          | %        |

| V <sub>REF</sub> Line Regulation                                           | $I_{VREF} = 100 \mu A$ , $V_{IN} = 4V$ to $60V$                            |   |             | 0.1      | 0.2        | %        |

| V <sub>REF</sub> Current Limit                                             | V <sub>REF</sub> = 1.8V                                                    |   | 2           | 2.5      | 3.2        | mA       |

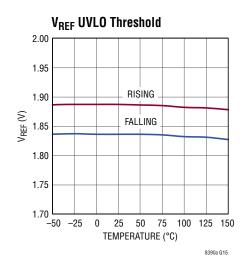

| V <sub>REF</sub> Undervoltage Lockout Threshold                            | Falling                                                                    |   | 1.78        | 1.84     | 1.90       | V        |

| V <sub>REF</sub> Undervoltage Lockout Hysteresis                           |                                                                            |   |             | 50       |            | mV       |

| Control Inputs/Outputs                                                     |                                                                            |   |             |          |            |          |

| EN/UVLO Shutdown Threshold                                                 |                                                                            | • | 0.3         | 0.6      | 1.0        | V        |

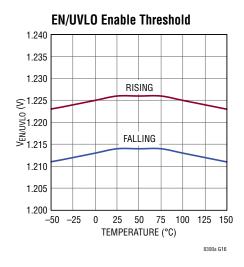

| EN/UVLO Enable Threshold                                                   | Falling                                                                    | • | 1.196       | 1.220    | 1.244      | V        |

| EN/UVLO Enable Hysteresis                                                  |                                                                            |   |             | 13       |            | mV       |

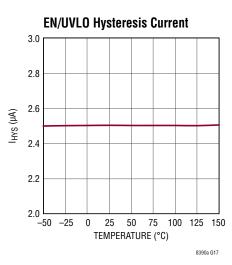

| EN/UVLO Hysteresis Current                                                 | $V_{EN/UVLO} = 0.3V$                                                       |   | -0.1        | 0_       | 0.1        | μA       |

|                                                                            | $V_{EN/UVLO} = 1.1V$<br>$V_{EN/UVLO} = 1.3V$                               |   | 2.1<br>-0.1 | 2.5<br>0 | 2.9<br>0.1 | μA<br>μA |

| CTRL Input Bias Current                                                    | V <sub>CTRL</sub> = 0.75V, Current Out of Pin                              |   | 0.1         | 20       | 50         | nA       |

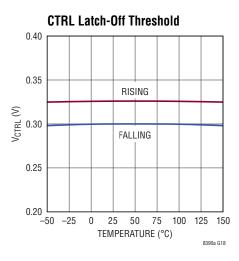

| CTRL Latch-Off Threshold                                                   | Falling                                                                    |   | 285         | 300      | 315        | mV       |

| CTRL Latch-Off Hysteresis                                                  | i uning                                                                    |   | 200         | 25       | 010        | mV       |

| Load Switch Driver                                                         |                                                                            |   |             |          |            | 1111     |

| LOADEN Threshold                                                           | Rising                                                                     | • | 1.3         | 1.4      | 1.5        | V        |

| LOADEN Hysteresis                                                          | ·······································                                    |   |             | 220      |            | mV       |

| Minimum V <sub>OUT</sub> for LOADTG to be On                               | V <sub>LOADEN</sub> = 5V                                                   |   |             | 2.4      | 3          | V        |

| LOADTG On Voltage V <sub>(VOUT-LOADTG)</sub>                               | $V_{OUT} = 12V$                                                            |   | 4.5         | 5        | 5.5        | V        |

| LOADTG Off Voltage V <sub>(VOUT-LOADTG)</sub>                              | V <sub>OUT</sub> = 12V                                                     |   | -0.1        | 0        | 0.1        | V        |

| LOADEN to LOADTG Turn On Propagation Delay                                 | C <sub>LOADTG</sub> = 3.3nF to V <sub>OUT</sub> , 50% to 50%               |   | 2           | 90       |            | ns       |

| LOADEN to LOADTG Turn Off Propagation Delay                                | $C_{LOADTG} = 3.3$ nF to $V_{OUT}$ , 50% to 50%                            |   |             | 40       |            | ns       |

| LOADTG Turn On Fall Time                                                   | C <sub>LOADTG</sub> = 3.3nF to V <sub>OUT</sub> , 10% to 90%               |   |             | 300      |            | ns       |

| LOADTG Turn Off Rise Time                                                  | $C_{LOADTG} = 3.3nF$ to $V_{OUT}$ , 90% to 10%                             |   |             | 10       |            | ns       |

# **ELECTRICAL CHARACTERISTICS** The ullet denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25 \,^{\circ}\text{C}$ (Note 2). $V_{IN} = 12 \,^{\circ}\text{V}$ , $V_{EN/UVL0} = 1.5 \,^{\circ}\text{V}$ unless otherwise noted.

| PARAMETER                                              | CONDITIONS                                                                                                                                                                          |   | MIN                  | ТҮР                  | MAX                  | UNITS          |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------|----------------------|----------------------|----------------|

| Error Amplifier                                        |                                                                                                                                                                                     |   |                      |                      |                      |                |

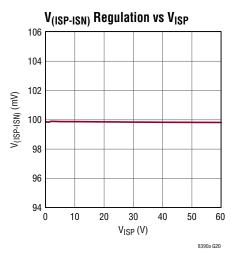

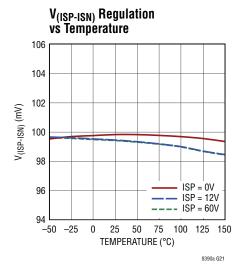

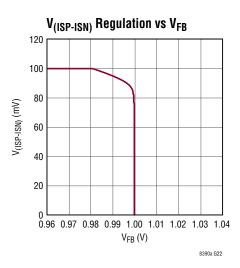

| Full Scale Current Regulation V <sub>(ISP-ISN)</sub>   | V <sub>CTRL</sub> = 2V, V <sub>ISP</sub> = 12V                                                                                                                                      | • | 97                   | 100                  | 103                  | mV             |

|                                                        | $V_{CTRL} = 2V, V_{ISP} = 0V$                                                                                                                                                       | • | 97                   | 100                  | 103                  | mV             |

| 1/10th Current Regulation V <sub>(ISP-ISN)</sub>       | $V_{CTRL} = 0.35V, V_{ISP} = 12V$<br>$V_{CTRL} = 0.35V, V_{ISP} = 0V$                                                                                                               | • | 8<br>8               | 10<br>10             | 12<br>12             | mV<br>mV       |

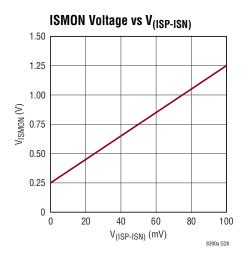

| ISMON Monitor Output V <sub>ISMON</sub>                | $V_{(ISP-ISN)} = 100mV, V_{ISP} = 12V/0V$<br>$V_{(ISP-ISN)} = 10mV, V_{ISP} = 12V/0V$<br>$V_{(ISP-ISN)} = 0mV, V_{ISP} = 12V/0V$                                                    | • | 1.20<br>0.30<br>0.20 | 1.25<br>0.35<br>0.25 | 1.30<br>0.40<br>0.30 | V<br>V<br>V    |

| ISP/ISN Input Common Mode Range                        |                                                                                                                                                                                     | • | 0                    |                      | 60                   | V              |

| ISP/ISN Low Side to High Side Switchover Voltage       | $V_{ISP} = V_{ISN}$                                                                                                                                                                 |   |                      | 1.8                  |                      | V              |

| ISP/ISN High Side to Low Side Switchover Voltage       | $V_{ISP} = V_{ISN}$                                                                                                                                                                 |   |                      | 1.7                  |                      | V              |

| ISP Input Bias Current                                 | $\begin{split} &V_{LOADEN} = 5V,  V_{ISP} = V_{ISN} = 12V \\ &V_{LOADEN} = 5V,  V_{ISP} = V_{ISN} = 0V \\ &V_{EN/UVLO} = 0V,  V_{ISP} = V_{ISN} = 12V   \text{or}   0V \end{split}$ |   |                      | 23<br>–10<br>0       |                      | μΑ<br>μΑ<br>μΑ |

| ISN Input Bias Current                                 | $\begin{split} &V_{LOADEN} = 5V,  V_{ISP} = V_{ISN} = 12V \\ &V_{LOADEN} = 5V,  V_{ISP} = V_{ISN} = 0V \\ &V_{EN/UVLO} = 0V,  V_{ISP} = V_{ISN} = 12V   \text{or}   0V \end{split}$ |   |                      | 23<br>–10<br>0       |                      | μΑ<br>μΑ<br>μΑ |

| ISP/ISN Current Regulation Amplifier g <sub>m</sub>    |                                                                                                                                                                                     |   |                      | 2000                 |                      | μs             |

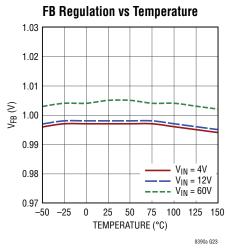

| FB Regulation Voltage                                  | $V_C = 1.2V$                                                                                                                                                                        | • | 0.985                | 1.00                 | 1.015                | V              |

| FB Line Regulation                                     | $V_{IN} = 4V$ to $60V$                                                                                                                                                              |   |                      | 0.2                  | 0.5                  | %              |

| FB Load Regulation                                     |                                                                                                                                                                                     |   |                      | 0.2                  | 8.0                  | %              |

| FB Voltage Regulation Amplifier g <sub>m</sub>         |                                                                                                                                                                                     |   |                      | 660                  |                      | μS             |

| FB Input Bias Current                                  | FB in Regulation, Current Out of Pin                                                                                                                                                |   |                      | 10                   | 40                   | nA             |

| V <sub>C</sub> Output Impedance                        |                                                                                                                                                                                     |   |                      | 10                   |                      | MΩ             |

| V <sub>C</sub> Standby Leakage Current                 | $V_C = 1.2V, V_{LOADEN} = 0V$                                                                                                                                                       |   | -10                  | 0                    | 10                   | nA             |

| Current Comparator                                     |                                                                                                                                                                                     |   |                      |                      |                      |                |

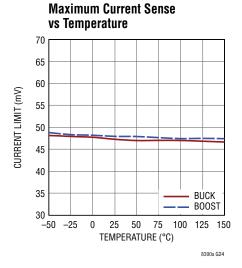

| Maximum Current Sense Threshold V <sub>(LSP-LSN)</sub> | Buck, V <sub>FB</sub> = 0.8V<br>Boost, V <sub>FB</sub> = 0.8V                                                                                                                       | • | 35<br>40             | 50<br>50             | 65<br>60             | mV<br>mV       |

| LSP Pin Bias Current                                   | $V_{LSP} = V_{LSN} = 12V$                                                                                                                                                           |   |                      | 60                   |                      | μΑ             |

| LSN Pin Bias Current                                   | $V_{LSP} = V_{LSN} = 12V$                                                                                                                                                           |   |                      | 60                   |                      | μΑ             |

| Fault                                                  |                                                                                                                                                                                     |   |                      |                      |                      |                |

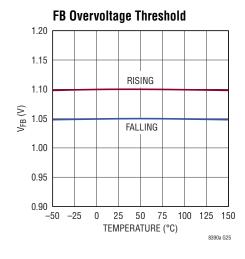

| FB Overvoltage Threshold (V <sub>FB</sub> )            | Rising                                                                                                                                                                              | • | 1.08                 | 1.1                  | 1.12                 | V              |

| FB Overvoltage Hysteresis                              |                                                                                                                                                                                     | • | 35                   | 50                   | 65                   | mV             |

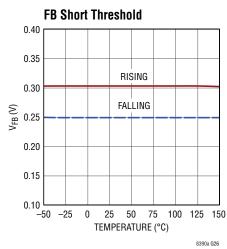

| FB Short Threshold (V <sub>FB</sub> )                  | Falling                                                                                                                                                                             | • | 0.24                 | 0.25                 | 0.26                 | V              |

| FB Short Hysteresis                                    | Hysteresis                                                                                                                                                                          | • | 35                   | 50                   | 65                   | mV             |

| ISP/ISN Over Current Threshold V <sub>(ISP-ISN)</sub>  | $V_{ISP} = 12V$                                                                                                                                                                     |   |                      | 750                  |                      | mV             |

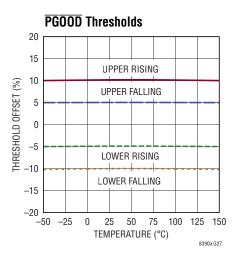

| PGOOD Upper Threshold Offset from V <sub>FB</sub>      | Rising                                                                                                                                                                              | • | 8                    | 10                   | 12                   | %              |

| PGOOD Lower Threshold Offset from V <sub>FB</sub>      | Falling                                                                                                                                                                             | • | -12                  | -10                  | -8                   | %              |

| PGOOD Pull-Down Resistance                             |                                                                                                                                                                                     |   |                      | 100                  | 200                  | Ω              |

| SS Hard Pull-Down Resistance                           | $V_{EN/UVLO} = 1.1V$                                                                                                                                                                |   |                      | 100                  | 200                  | Ω              |

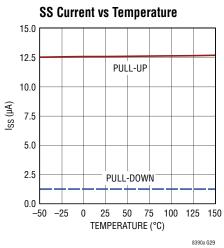

| SS Pull-Up Current                                     | $V_{FB} = 0.4V, V_{SS} = 0V$                                                                                                                                                        |   | 10                   | 12.5                 | 15                   | μA             |

| SS Pull-Down Current                                   | $V_{FB} = 0.1V, V_{SS} = 2V$                                                                                                                                                        |   | 1                    | 1.25                 | 1.5                  | μА             |

| SS Fault Latch-Off Threshold                           |                                                                                                                                                                                     |   |                      | 1.7                  |                      | V              |

| SS Fault Reset Threshold                               |                                                                                                                                                                                     |   |                      | 0.2                  |                      | V              |

# **ELECTRICAL CHARACTERISTICS** The ullet denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ (Note 2). $V_{IN} = 12V$ , $V_{EN/UVLO} = 1.5V$ unless otherwise noted.

| PARAMETER                                                            | CONDITIONS                                                                                                                                                     |    | MIN                 | TYP                 | MAX                 | UNITS             |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------------------|---------------------|---------------------|-------------------|

| Oscillator                                                           |                                                                                                                                                                |    |                     |                     |                     |                   |

| RT Pin Voltage                                                       | $R_T = 100k\Omega$                                                                                                                                             |    |                     | 1.00                |                     | V                 |

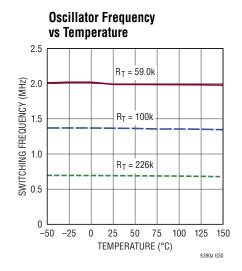

| Switching Frequency                                                  | $\begin{aligned} &V_{SYNC/SPRD} = 0V, \ R_T = 226k\Omega \\ &V_{SYNC/SPRD} = 0V, \ R_T = 100k\Omega \\ &V_{SYNC/SPRD} = 0V, \ R_T = 59.0k\Omega \end{aligned}$ | •  | 645<br>1290<br>1900 | 685<br>1360<br>2000 | 725<br>1430<br>2100 | kHz<br>kHz<br>kHz |

| SYNC Frequency                                                       |                                                                                                                                                                |    | 600                 |                     | 2100                | kHz               |

| SYNC/SPRD Input Bias Current                                         | V <sub>SYNC/SPRD</sub> = 5V                                                                                                                                    |    | -0.1                | 0                   | 0.1                 | μА                |

| SYNC/SPRD Threshold Voltage                                          |                                                                                                                                                                |    | 0.4                 |                     | 1.5                 | V                 |

| Highest Spread Spectrum Above Oscillator Frequency                   | V <sub>SYNC/SPRD</sub> = 5V                                                                                                                                    |    | 21                  | 23                  | 25                  | %                 |

| Region Transition                                                    |                                                                                                                                                                | Î  |                     |                     |                     |                   |

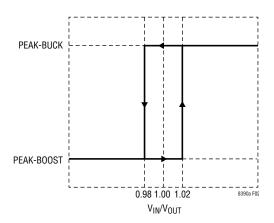

| Buck-Boost to Boost (V <sub>IN</sub> /V <sub>OUT</sub> )             |                                                                                                                                                                |    | 0.73                | 0.75                | 0.77                |                   |

| Boost to Buck-Boost (V <sub>IN</sub> /V <sub>OUT</sub> )             |                                                                                                                                                                |    | 0.83                | 0.85                | 0.87                |                   |

| Buck to Buck-Boost (V <sub>IN</sub> /V <sub>OUT</sub> )              |                                                                                                                                                                |    | 1.23                | 1.25                | 1.27                |                   |

| Buck-Boost to Buck (V <sub>IN</sub> /V <sub>OUT</sub> )              |                                                                                                                                                                |    | 1.31                | 1.33                | 1.35                |                   |

| Peak-Buck to Peak-Boost (V <sub>IN</sub> /V <sub>OUT</sub> )         |                                                                                                                                                                |    | 0.96                | 0.98                | 1.00                |                   |

| Peak-Boost to Peak-Buck (V <sub>IN</sub> /V <sub>OUT</sub> )         |                                                                                                                                                                |    | 1.00                | 1.02                | 1.04                |                   |

| NMOS Drivers                                                         |                                                                                                                                                                | •  |                     |                     |                     |                   |

| TG1, TG2 Gate Driver On-Resistance<br>Gate Pull-Up<br>Gate Pull-Down | V <sub>(BST-SW)</sub> = 5V                                                                                                                                     |    |                     | 2.6<br>1.4          |                     | Ω                 |

| BG1, BG2 Gate Driver On-Resistance<br>Gate Pull-Up<br>Gate Pull-Down | V <sub>INTVCC</sub> = 5V                                                                                                                                       |    |                     | 3.2<br>1.2          |                     | ΩΩ                |

| TG1, TG2 Rise Time<br>TG1, TG2 Fall Time                             | C <sub>L</sub> = 3.3nF, 10% to 90%<br>C <sub>L</sub> = 3.3nF, 90% to 10%                                                                                       |    | 25<br>20            |                     | ns<br>ns            |                   |

| BG1, BG2 Rise Time<br>BG1, BG2 Fall Time                             | C <sub>L</sub> = 3.3nF, 10% to 90%<br>C <sub>L</sub> = 3.3nF, 90% to 10%                                                                                       |    |                     | 25<br>20            |                     | ns<br>ns          |

| TG Off to BG On Delay                                                | C <sub>L</sub> = 3.3nF                                                                                                                                         |    | 25                  |                     | ns                  |                   |

| BG Off to TG On Delay                                                | C <sub>L</sub> = 3.3nF                                                                                                                                         |    | 25                  |                     | ns                  |                   |

| TG1 Minimum Duty Cycle in Buck Region                                | Peak-Buck Current Mode                                                                                                                                         |    | 10                  |                     | %                   |                   |

| TG1 Maximum Duty Cycle in Buck Region                                | Peak-Buck Current Mode                                                                                                                                         | 90 |                     | %                   |                     |                   |

| TG1 Fixed Duty Cycle in Buck-Boost Region                            | Peak-Boost Current Mode 80                                                                                                                                     |    |                     | %                   |                     |                   |

| BG2 Fixed Duty Cycle in Buck-Boost Region                            | Peak-Buck Current Mode                                                                                                                                         |    | 20                  |                     | %                   |                   |

| BG2 Minimum Duty Cycle in Boost Region                               | Peak-Boost Current Mode                                                                                                                                        |    |                     | 10                  |                     | %                 |

| BG2 Maximum Duty Cycle in Boost Region                               | Peak-Boost Current Mode                                                                                                                                        |    | 90                  |                     | %                   |                   |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LT8390AE is guaranteed to meet performance specifications from 0°C to 125°C operating junction temperature. Specifications over the –40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LT8390AI is guaranteed over the –40°C to 125°C operating junction

temperature range. The LT8390AJ and LT8390AH are guaranteed over the -40°C to 150°C operating junction temperature range. High junction temperatures degrade operating lifetimes. Operating lifetime is derated at junction temperatures greater than 125°C.

**Note 3:** The LT8390A includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 150°C when overtemperature protection is active. Continuous operation above the specified absolute maximum operating junction temperature may impair device reliability.

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

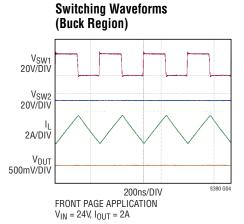

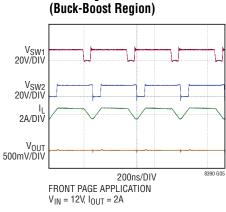

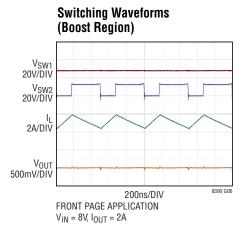

**Switching Waveforms**

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

## PIN FUNCTIONS

**BG1:** Buck Side Bottom Gate Drive. Drives the gate of buck side bottom N-channel MOSFET with a voltage swing from ground to  $INTV_{CC}$ .

**BST1:** Buck Side Bootstrap Floating Driver Supply. The BST1 pin has an integrated bootstrap Schottky diode from the INTV $_{CC}$  pin and requires an external bootstrap capacitor to the SW1 pin. The BST1 pin swings from a diode voltage drop below INTV $_{CC}$  to ( $V_{IN}$  + INTV $_{CC}$ ).

**SW1:** Buck Side Switch Node. The SW1 pin swings from a Schottky diode voltage drop below ground up to  $V_{IN}$ .

**TG1:** Buck Side Top Gate Drive. Drives the gate of buck side top N-channel MOSFET with a voltage swing from SW1 to BST1.

**LSP:** Positive Terminal of the Buck Side Inductor Current Sense Resistor (R<sub>SENSE</sub>). Ensure accurate current sense with Kelvin connection.

**LSN:** Negative Terminal of the Buck Side Inductor Current Sense Resistor (R<sub>SENSE</sub>). Ensure accurate current sense with Kelvin connection.

$V_{IN}$ : Input Supply. The  $V_{IN}$  pin must be tied to the power input to determine the buck, buck-boost, or boost operation regions. Locally bypass this pin to ground with a minimum  $1\mu F$  ceramic capacitor.

**INTV**<sub>CC</sub>: Internal 5V Linear Regulator Output. The INTV<sub>CC</sub> linear regulator is supplied from the  $V_{IN}$  pin, and powers the internal control circuitry and gate drivers. Locally bypass this pin to ground with a minimum 4.7µF ceramic capacitor.

**EN/UVLO:** Enable and Undervoltage Lockout. Force the pin below 0.3V to shut down the part and reduce  $V_{IN}$  quiescent current below  $2\mu A$ . Force the pin above 1.233V for normal operation. The accurate 1.220V falling threshold can be used to program an undervoltage lockout (UVLO) threshold with a resistor divider from  $V_{IN}$  to ground. An accurate 2.5 $\mu A$  pull-down current allows the programming

of  $V_{\text{IN}}$  UVLO hysteresis. If neither function is used, tie this pin directly to  $V_{\text{IN}}.$

**TEST:** Factory Test. This pin is used for testing purpose only and must be directly connected to ground for the part to operate properly.

**LOADEN:** Load Switch Enable Input. The LOADEN pin is used to control the ON/OFF of the high side PMOS load switch. If the load switch control is not used, tie this pin to  $V_{REF}$  or INTV<sub>CC</sub>. Forcing the pin low turns off TG1 and TG2, turns on BG1 and BG2, disconnects the  $V_{C}$  pin from all internal loads, and turns off LOADTG.

**V**<sub>REF</sub>: Voltage Reference Output. The V<sub>REF</sub> pin provides an accurate 2V reference capable of supplying 1mA current. Locally bypass this pin to ground with a  $0.47\mu F$  ceramic capacitor.

**CTRL:** Control Input for ISP/ISN Current Sense Threshold. The CTRL pin is used to program the ISP/ISN current limit:

$$I_{IS(MAX)} = \frac{Min(V_{CTRL} - 0.25V, 1V)}{10 \cdot R_{IS}}$$

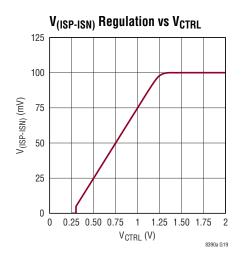

The  $V_{CTRL}$  can be set by an external voltage reference or a resistor divider from  $V_{REF}$  to ground. For  $0.3V \le V_{CTRL} \le 1.15V$ , the current sense threshold linearly goes up from 5mV to 90mV. For  $V_{CTRL} \ge 1.35V$ , the current sense threshold is constant at 100mV full scale value. For 1.15V  $\le V_{CTRL} \le 1.35V$ , the current sense threshold smoothly transitions from the linear function of  $V_{CTRL}$  to the 100mV constant value. Tie CTRL to  $V_{REF}$  for the 100mV full scale threshold. Force the pin below 0.3V to stop switching.

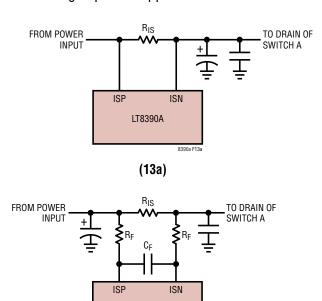

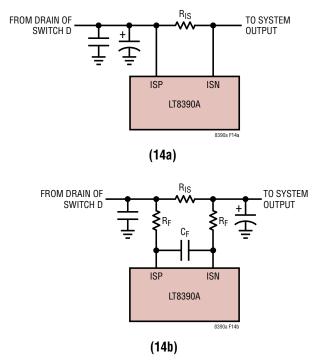

**ISP:** Positive Terminal of the ISP/ISN Current Sense Resistor ( $R_{IS}$ ). Ensure accurate current sense with Kelvin connection.

**ISN:** Negative Terminal of the ISP/ISN Current Sense Resistor (R<sub>IS</sub>). Ensure accurate current sense with Kelvin connection.

#### PIN FUNCTIONS

**ISMON:** ISP/ISN Current Sense Monitor Output. The ISMON pin generates a voltage that is equal to ten times  $V_{(ISP-ISN)}$  plus 0.25V offset voltage. For parallel applications, tie the master LT8390A ISMON pin to the slave LT8390A CTRL pin.

**PGOOD**: Power Good Open Drain Output. The PGOOD pin is pulled low when the FB pin is within ±10% of the final regulation voltage. To function, the pin requires an external pull-up resistor.

**SS:** Soft-Start Timer Setting. The SS pin is used to set soft-start timer by connecting a capacitor to ground. An internal 12.5µA pull-up current charging the external SS capacitor gradually ramps up FB regulation voltage. A 22nF capacitor is recommended on this pin. Any UVLO or thermal shutdown immediately pulls SS pin to ground and stops switching. Using a single resistor from SS to  $V_{REF}$ , the LT8390A can be set in three different fault protection modes during output short-circuit condition: hiccup (no resistor), latch-off (499k $\Omega$ ), and keep-running (100k $\Omega$ ). See more details in the Applications Information section.

**FB:** Voltage Loop Feedback Input. The FB pin is used for constant-voltage regulation and output fault protection. The internal error amplifier with its output  $V_C$  regulates  $V_{FB}$  to 1.00V through the DC/DC converter. During output short-circuit ( $V_{FB} < 0.25V$ ) condition, the part gets into one fault mode per customer setting. During an overvoltage ( $V_{FB} > 1.1V$ ) condition, the part turns off all TG1, BG1, TG2, BG2, and LOADTG.

$V_C$ : Error Amplifier Output to Set Inductor Current Comparator Threshold. The  $V_C$  pin is used to compensate the control loop with an external RC network. During LOADEN low state, the  $V_C$  pin is disconnected from all internal loads to store its voltage information.

RT: Switching Frequency Setting. Connect a resistor from this pin to ground to set the internal oscillator frequency from 600kHz to 2MHz.

**SYNC/SPRD:** Switching Frequency Synchronization or Spread Spectrum. Ground this pin for switching at internal oscillator frequency. Apply a clock signal for external frequency synchronization. Tie to  $INTV_{CC}$  for 25% triangle spread spectrum above internal oscillator frequency.

**LOADTG:** High Side PMOS Load Switch Top Gate Drive. A buffered and inverted version of the LOADEN input signal, the LOADTG pin drives an external high side PMOS load switch with a voltage swing from the higher voltage of  $(V_{OUT}$ -5V) and 1.2V to  $V_{OUT}$ . Leave this pin unconnected if not used.

$V_{OUT}$ : Output Supply. The  $V_{OUT}$  pin must be tied to the power output to determine the buck, buck-boost, or boost operation regions. The  $V_{OUT}$  pin also serves as positive rail for the LOADTG drive. Locally bypass this pin to ground with a minimum  $1\mu F$  ceramic capacitor.

**TG2:** Boost Side Top Gate Drive. Drives the gate of boost side top N-Channel MOSFET with a voltage swing from SW2 to BST2.

**SW2:** Boost Side Switch Node. The SW2 pin swings from a Schottky diode voltage drop below ground to  $V_{OLIT}$ .

**BST2:** Boost Side Bootstrap Floating Driver Supply. The BST2 pin has an integrated bootstrap Schottky diode from the INTV<sub>CC</sub> pin and requires an external bootstrap capacitor to the SW2 pin. The BST2 pin swings from a diode voltage drop below INTV<sub>CC</sub> to  $(V_{OUT} + INTV_{CC})$ .

**BG2:** Boost Side Bottom Gate Drive. Drives the gate of boost side bottom N-channel MOSFET with a voltage swing from ground to  $INTV_{CC}$ .

**GND (Exposed Pad):** Ground. Solder the exposed pad directly to the ground plane.

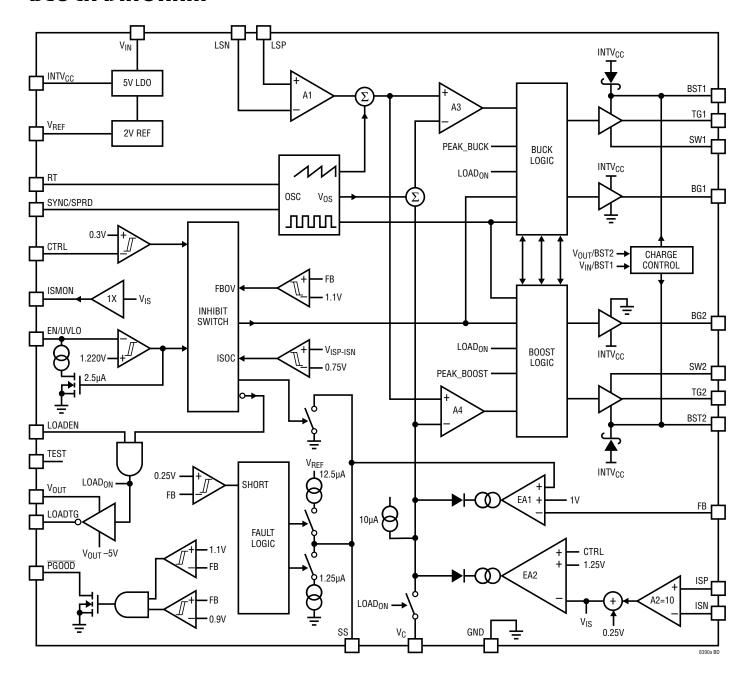

# **BLOCK DIAGRAM**

The LT8390A is a current mode DC/DC controller that can regulate output voltage, input or output current from input voltage above, below, or equal to the output voltage. The ADI proprietary peak-buck peak-boost current mode control scheme uses a single inductor current sense resistor and provides smooth transition between buck region, buck-boost region, and boost region. Its operation is best understood by referring to the Block Diagram.

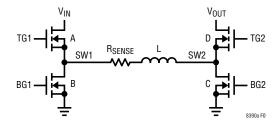

#### **Power Switch Control**

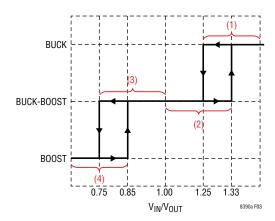

Figure 1 shows a simplified diagram of how the four power switches A, B, C, and D are connected to the inductor L, the current sense resistor  $R_{SENSE}$ , power input  $V_{IN}$ , power output  $V_{OUT}$ , and ground. The current sense resistor  $R_{SENSE}$  connected to the LSP and LSN pins provides inductor current information for both peak current mode control and reverse current detection in buck region, buck-boost region, and boost region. Figure 2 shows the current mode control as a function of  $V_{IN}/V_{OUT}$  ratio and Figure 3 shows the operation region as a function of  $V_{IN}/V_{OUT}$  ratio. The power switches are properly controlled to smoothly transition between modes and regions. Hysteresis is added to prevent chattering between modes and regions.

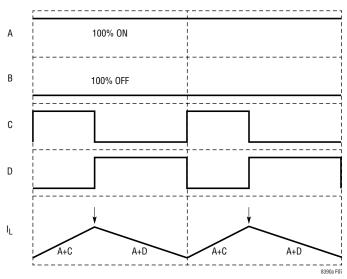

There are total four states: (1) peak-buck current mode control in buck region, (2) peak-buck current mode control in buck-boost region, (3) peak-boost current mode control in buck-boost region, and (4) peak-boost current mode control in boost region. The following sections give detailed description for each state with waveforms, in which the shoot-through protection dead time between switches A and B, between switches C and D are ignored for simplification.

Figure 1. Simplified Diagram of the Power Switches

Figure 2. Current Mode vs V<sub>IN</sub>/V<sub>OUT</sub> Ratio

Figure 3. Operation Region vs V<sub>IN</sub>/V<sub>OUT</sub> Ratio

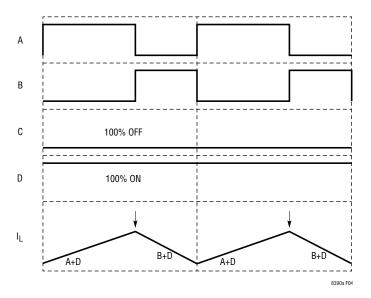

#### (1) Peak-Buck in Buck Region (V<sub>IN</sub> >> V<sub>OUT</sub>)

When  $V_{IN}$  is much higher than  $V_{OUT}$ , the LT8390A uses peak-buck current mode control in buck region (Figure 4). Switch C is always off and switch D is always on. At the beginning of every cycle, switch A is turned on and the inductor current ramps up. When the inductor current hits the peak buck current threshold commanded by  $V_{C}$  voltage at buck current comparator A3 during (A+D) phase, switch A is turned off and switch B is turned on for the rest of the cycle. Switches A and B will alternate, behaving like a typical synchronous buck regulator.

Figure 4. Peak-Buck in Buck Region (V<sub>IN</sub> >> V<sub>OUT</sub>)

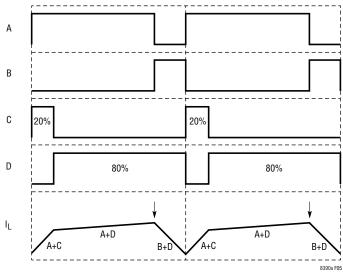

#### (2) Peak-Buck in Buck-Boost Region (V<sub>IN</sub> ~> V<sub>OUT</sub>)

When  $V_{IN}$  is slightly higher than  $V_{OUT}$ , the LT8390A uses peak-buck current mode control in buck-boost region (Figure 5). Switch C is always turned on for the beginning 20% cycle and switch D is always turned on for the remaining 80% cycle. At the beginning of every cycle, switches A and C are turned on and the inductor current ramps up. After 20% cycle, switch C is turned off and switch D is turned on, and the inductor keeps ramping up. When the inductor current hits the peak buck current threshold commanded by  $V_{C}$  voltage at buck current comparator A3 during (A+D) phase, switch A is turned off and switch B is turned on for the rest of the cycle.

Figure 5. Peak-Buck in Buck-Boost Region (VIN ~> VOLIT)

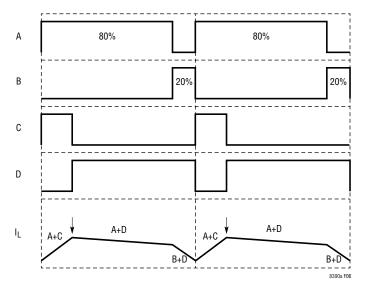

#### (3) Peak-Boost in Buck-Boost Region (V<sub>IN</sub> <~ V<sub>OUT</sub>)

When  $V_{IN}$  is slightly lower than  $V_{OUT}$ , the LT8390A uses peak-boost current mode control in buck-boost region (Figure 6). Switch A is always turned on for the beginning 80% cycle and switch B is always turned on for the remaining 20% cycle. At the beginning of every cycle, switches A and C are turned on and the inductor current ramps up. When the inductor current hits the peak boost current threshold commanded by  $V_{C}$  voltage at boost current comparator A4 during (A+C) phase, switch C is turned off and switch D is turned on for the rest of the cycle. After 80% cycle, switch A is turned off and switch B is turned on for the rest of the cycle.

#### (4) Peak-Boost in Boost Region (V<sub>IN</sub> << V<sub>OUT</sub>)

When  $V_{IN}$  is much lower than  $V_{OUT}$ , the LT8390A uses peak-boost current mode control in boost region (Figure 7). Switch A is always on and switch B is always off. At the beginning of every cycle, switch C is turned on and the inductor current ramps up. When the inductor current hits the peak boost current threshold commanded by  $V_{C}$  voltage at boost current comparator A4 during (A+C) phase, switch C is turned off and switch D is turned on for the rest of the cycle. Switches C and D will alternate, behaving like a typical synchronous boost regulator.

Figure 6. Peak-Boost in Buck-Boost Region (VIN <~ VOUT)

Figure 7. Peak-Boost in Boost Region ( $V_{IN} \ll V_{OUT}$ )

#### **Main Control Loop**

The LT8390A is a fixed frequency current mode controller. The inductor current is sensed through the inductor sense resistor between the LSP and LSN pins. The current sense voltage is gained up by amplifier A1 and added to a slope compensation ramp signal from the internal oscillator. The summing signal is then fed into the positive terminals of the buck current comparator A3 and boost current comparator A4. The negative terminals of A3 and A4 are controlled by the voltage on the  $V_{\rm C}$  pin, which is the diode-OR of error amplifiers EA1 and EA2.

Depending on the state of the peak-buck peak-boost current mode control, either the buck logic or the boost logic is controlling the four power switches so that either the FB voltage is regulated to 1V or the current sense voltage between the ISP and ISN pins is regulated by the CTRL pin during normal operation. The gains of EA1 and EA2 have been balanced to ensure smooth transition between constant-voltage and constant-current operation with the same compensation network.

#### **Light Load Current Operation**

At light load, the LT8390A runs either at full switching frequency discontinuous conduction mode or pulse-skipping mode, where the switches are held off for multiple cycles (i.e., skipping pulses) to maintain the regulation and improve the efficiency. Both the buck and boost reverse current sense thresholds are set to 1mV (typical) so that no reverse inductor current is allowed. Such no reverse inductor current from the output to the input is highly desired in certain applications.

In the buck region, switch B is turned off whenever the buck reverse current threshold is triggered during (B+D) phase. In the boost region, switch D is turned off whenever the boost reverse current threshold is triggered during (A+D) phase. In the buck-boost region, switch D is turned off whenever the boost reverse current threshold is triggered during (A+D) phase, and both switches B and D are turned off whenever the buck reverse current threshold is triggered during (B+D) phase.

#### **Internal Charge Path**

Each of the two top MOSFET drivers is biased from its floating bootstrap capacitor, which is normally re-charged by INTV<sub>CC</sub> through both the external and internal bootstrap diodes when the top MOSFET is turned off. When the LT8390A operates exclusively in the buck or boost regions, one of the top MOSFETs is constantly on. An internal charge path, from  $V_{OUT}$  and BST2 to BST1 or from  $V_{IN}$  and BST1 to BST2, charges the bootstrap capacitor to 4.6V so that the top MOSFET can be kept on.

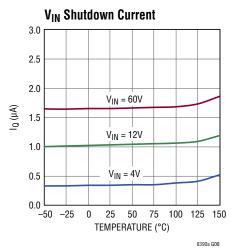

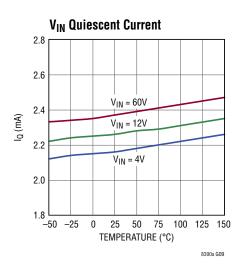

#### Shutdown and Power-On-Reset

The LT8390A enters shutdown mode and drains less than 2µA guiescent current when the EN/UVLO pin is below its shutdown threshold (0.3V minimum). Once the EN/UVLO pin is above its shutdown threshold (1V maximum), the LT8390A wakes up startup circuitry, generates bandgap reference, and powers up the internal INTV<sub>CC</sub> LDO. The INTV<sub>CC</sub> LDO supplies the internal control circuitry and gate drivers. Now the LT8390A enters undervoltage lockout (UVLO) mode with a hysteresis current (2.5µA typical) pulled into the EN/UVLO pin. When the INTV<sub>CC</sub> pin is charged above its rising UVLO threshold (3.78V typical), the EN/UVLO pin passes its rising enable threshold (1.233V typical), and the junction temperature is less than its thermal shutdown (165°C typical), the LT8390A enters enable mode, in which the EN/UVLO hysteresis current is turned off and the voltage reference V<sub>RFF</sub> is being charged up from ground. From the time of entering enable mode to the time of  $V_{RFF}$  passing its rising UVLO threshold (1.89V typical), the LT8390A is going through a power-on-reset (POR), waking up the entire internal control circuitry and settling to the right initial conditions. After the POR, the LT8390A is ready and waiting for the signals on the CTRL and LOADEN pins to start switching.

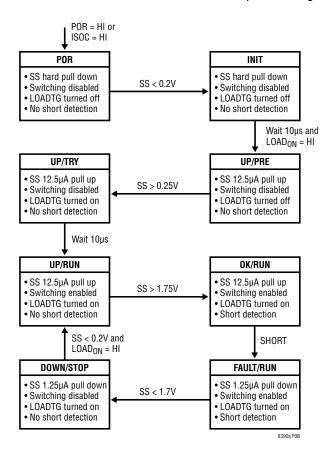

#### Start-Up and Fault Protection

Figure 8 shows the start-up and fault sequence for the LT8390A. During the POR state, the SS pin is hard pulled down with a  $100\Omega$  to ground. In a pre-biased condition, the SS pin has to be pulled below 0.2V to enter the INIT state, where the LT8390A wait 10µs so that the SS pin can be fully discharged to ground. After the 10µs, the LT8390A enters the UP/PRE state when the LOADON signal goes high. The LOADON high signal happens when CTRL pin is above its rising latch-off thresholds (0.325V typical) and the LOADEN is high.

During the UP/PRE state, the SS pin is charged up by a 12.5µA pull-up current while the switching is disabled and the LOADTG is turned off. Once the SS pin is charged

Figure 8. Start-Up and Fault Sequence

above 0.25V, the LT8390A enters the UP/TRY state, where the LOADTG is turned on first while the switching is still disabled. If an excessive current flowing through the current sense resistor triggers the ISP/ISN over current (ISOC) signal, it will reset the LT8390A back into the POR state. After 10µs in the UP/TRY state without triggering the ISOC signal, the LT8390A enters the UP/RUN state.

During the UP/RUN state, the switching is enabled and the start-up of the output voltage  $V_{OUT}$  is controlled by the voltage on the SS pin. When the SS pin voltage is less than 1V, the LT8390A regulates the FB pin voltage to the SS pin voltage instead of the 1V reference. This allows the SS pin to be used to program soft-start by connecting an external capacitor from the SS pin to GND. The internal 12.5 $\mu$ A pull-up current charges up the capacitor, creating a voltage ramp on the SS pin. As the SS pin voltage rises linearly from 0.25V to 1V (and beyond), the output voltage  $V_{OUT}$  rises smoothly to its final regulation voltage.

Once the SS pin is charged above 1.75V, the LT8390A enters the OK/RUN state, where the output short detection is activated. The output short means  $V_{FB} < 0.25V$ . When the output short happens, the LT8390A enters the FAULT/RUN state, where a 1.25 $\mu$ A pull-down current slowly discharges the SS pin with the other conditions the same as the OK/RUN state. Once the SS pin is discharged below 1.7V, the LT8390A enters the DOWN/STOP state, where the switching is disabled and the short detection is deactivated with the previous fault latched. Once the SS pin is discharged below 0.2V and the LOADON signal is still high, the LT8390A goes back to the UP/RUN state.

In an output short condition, the LT8390A can be set to hiccup, latch-off, or keep-running fault protection mode with a resistor between the SS and V<sub>REF</sub> pins. Without any resistor, the LT8390A will hiccup between 0.2V and 1.75V and go around the UP/RUN, OK/RUN, FAULT/RUN, and DOWN/STOP states until the fault condition is cleared. With a 499k $\Omega$  resistor, the LT8390A will latch off until the EN/UVLO is toggled. With a 100k $\Omega$  resistor, the LT8390A will keep running regardless of the fault.

The front page shows a typical LT8390A application circuit. This Applications Information section serves as a guideline of selecting external components for typical applications. The examples and equations in this section assume continuous conduction mode unless otherwise specified.

#### **Switching Frequency Selection**

The LT8390A uses a constant frequency control scheme between 600kHz and 2MHz. Selection of the switching frequency is a tradeoff between efficiency and component size. Low frequency operation improves efficiency by reducing MOSFET switching losses, but requires larger inductor and capacitor values. For high power applications, consider operating at lower frequencies to minimize MOSFET heating from switching losses. For low power applications, consider operating at higher frequencies to minimize the total solution size.

In addition, the specific application also plays an important role in switching frequency selection. In a noise-sensitive system, the switching frequency is usually selected to keep the switching noise out of a sensitive frequency band.

#### **Switching Frequency Setting**

The switching frequency of the LT8390A can be set by the internal oscillator. With the SYNC/SPRD pin pulled to ground, the switching frequency is set by a resistor from the RT pin to ground. Table 1 shows  $R_T$  resistor values for common switching frequencies.

Table 1. Switching Frequency vs R<sub>T</sub> Value (1% Resistor)

| f <sub>OSC</sub> (MHz) | R <sub>T</sub> (k) |

|------------------------|--------------------|

| 0.6                    | 267                |

| 0.8                    | 191                |

| 1.0                    | 147                |

| 1.2                    | 118                |

| 1.4                    | 97.6               |

| 1.6                    | 82.5               |

| 1.8                    | 66.5               |

| 2.0                    | 59.0               |

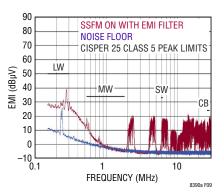

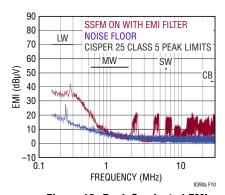

#### **Spread Spectrum Frequency Modulation**

Switching regulators can be particularly troublesome for applications where electromagnetic interference (EMI) is a concern. To improve the EMI performance, the LT8390A

implements a triangle spread spectrum frequency modulation scheme. With the SYNC/SPRD pin tied to INTV $_{\rm CC}$ , the LT8390A starts to spread its switching frequency 25% above the internal oscillator frequency. Figure 9 and Figure 10 show the noise spectrum of the front page application when spread spectrum enabled.

Figure 9. Average Conducted EMI

Figure 10. Peak Conducted EMI

#### **Frequency Synchronization**

The LT8390A switching frequency can be synchronized to an external clock using the SYNC/SPRD pin. Driving the SYNC/SPRD with a 50% duty cycle waveform is always a good choice, otherwise maintain the duty cycle between 10% and 90%. Due to the use of a phase-locked loop (PLL) inside, there is no restriction between the synchronization frequency and the internal oscillator frequency. The rising edge of the synchronization clock represents the beginning of a switching cycle, turning on switches A and C, or switches A and D.

#### **Inductor Selection**

The switching frequency and inductor selection are interrelated in that higher switching frequencies allow the use of smaller inductor and capacitor values. The inductor value has a direct effect on ripple current. The highest current ripple  $\Delta I_L\%$  happens in the buck region at  $V_{IN(MAX)}$ , and the lowest current ripple  $\Delta I_L\%$  happens in the boost region at  $V_{IN(MIN)}$ . For any given ripple allowance set by customers, the minimum inductance can be calculated as:

$$\begin{split} L_{BUCK} > & \frac{V_{OUT} \bullet \left(V_{IN(MAX)} - V_{OUT}\right)}{f \bullet I_{OUT(MAX)} \bullet \Delta I_L \% \bullet V_{IN(MAX)}} \\ L_{BOOST} > & \frac{V_{IN(MIN)}}{f \bullet I_{OUT(MAX)} \bullet \Delta I_L \% \bullet V_{OUT}} \end{aligned}$$

where:

$$\Delta I_L\% = \frac{\Delta I_L}{I_{L(AVG)}}$$

f is switching frequency

V<sub>IN(MIN)</sub> is minimum input voltage

V<sub>IN(MAX)</sub> is maximum input voltage

$V_{\text{OUT}}$  is output voltage

I<sub>OUT(MAX)</sub> is maximum output current

Slope compensation provides stability in constant frequency current mode control by preventing subharmonic oscillations at certain duty cycles. The minimum inductance required for stability when duty cycles are larger than 50% can be calculated as:

$$L > \frac{10 \bullet V_{OUT} \bullet R_{SENSE}}{f}$$

For high efficiency, choose an inductor with low core loss, such as ferrite. Also, the inductor should have low DC resistance to reduce the I<sup>2</sup>R losses, and must be able to handle the peak inductor current without saturating. To minimize radiated noise, use a shielded inductor.

#### **R<sub>SENSE</sub> Selection and Maximum Output Current**

R<sub>SENSE</sub> is chosen based on the required output current. The duty cycle independent maximum current sense thresholds (50mV in peak-buck and 50mV in peak-boost) set the maximum inductor peak current in buck region, buck-boost region, and boost region.

In boost region, the lowest maximum average load current happens at  $V_{\text{IN}(\text{MIN})}$  and can be calculated as:

$$I_{OUT(MAX\_BOOST)} = \left(\frac{50mV}{R_{SENSE}} - \frac{\Delta I_{L(BOOST)}}{2}\right) \bullet \frac{V_{IN(MIN)}}{V_{OUT}}$$

where  $\Delta I_{L(BOOST)}$  is peak-to-peak inductor ripple current in boost region and can be calculated as:

$$\Delta I_{L(BOOST)} = \frac{V_{IN(MIN)} \bullet (V_{OUT} - V_{IN(MIN)})}{f \bullet L \bullet V_{OUT}}$$

In buck region, the lowest maximum average load current happens at  $V_{\text{IN}(\text{MAX})}$  and can be calculated as:

$$I_{OUT(MAX\_BUCK)} = \left(\frac{50mV}{R_{SENSE}} - \frac{\Delta I_{L(BUCK)}}{2}\right)$$

where  $\Delta I_{L(BUCK)}$  is peak-to-peak inductor ripple current in buck region and can be calculated as:

$$\Delta I_{L(BUCK)} = \frac{V_{OUT} \cdot (V_{IN(MAX)} - V_{OUT})}{f \cdot L \cdot V_{IN(MAX)}}$$

The maximum current sense  $R_{\text{SENSE}}$  in boost region is:

$$R_{SENSE(BOOST)} = \frac{2 \bullet 50 \text{mV} \bullet V_{IN(MIN)}}{2 \bullet I_{OUT(MAX)} \bullet V_{OUT} + \Delta I_{L(BOOST)} \bullet V_{IN(MIN)}}$$

The maximum current sense R<sub>SENSE</sub> in buck region is

$$R_{SENSE(BUCK)} = \frac{2 \bullet 50mV}{2 \bullet I_{OUT(MAX)} + \Delta I_{L(BUCK)}}$$

The final  $R_{\text{SENSE}}$  value should be lower than the calculated  $R_{\text{SENSE}}$  in both buck and boost regions. A 20% to 30% margin is usually recommended. Always choose a low ESL current sense resistor.

#### **Power MOSFET Selection**

The LT8390A requires four external N-channel power MOSFETs, two for the top switches (switches A and D shown in Figure 1) and two for the bottom switches (switches B and C shown in Figure 1). Important parameters for the power MOSFETs are the breakdown voltage  $V_{BR(DSS)}$ , threshold voltage  $V_{GS(TH)}$ , on-resistance  $R_{DS(ON)}$ , reverse transfer capacitance  $C_{RSS}$  and maximum current  $I_{DS(MAX)}$ .

To achieve 2MHz operation, the power MOSFET selection is critical. With typical 25ns shoot-through protection deadtime, high performance power MOSFETs with low  $\mathbf{Q}_g$  and low  $\mathbf{R}_{DS(ON)}$  must be used.

Since the gate drive voltage is set by the 5V INTV $_{CC}$  supply, logic-level threshold MOSFETs must be used in LT8390A applications. Switching four MOSFETs at higher frequency like 2MHz, the substantial gate charge current from INTV $_{CC}$  can be estimated as:

$$I_{INTVCC} = f \bullet (Q_{gA} + Q_{gB} + Q_{gC} + Q_{gD})$$

where:

f is the switching frequency

$Q_{gA},\ Q_{gB},\ Q_{gC},\ Q_{gD}$  are the total gate charges of MOSFETs A, B, C, D

Make sure the total required INTV $_{CC}$  current not exceeding the INTV $_{CC}$  current limit in the data sheet. Typically, MOSFETs with less than 10nC  $Q_{\alpha}$  are recommended.

The LT8390A uses the  $V_{IN}/V_{OUT}$  ratio to transition between modes and regions. Bigger IR drop in the power path caused by improper MOSFET and inductor selection may prevent the LT8390A from smooth transition. To ensure smooth transitions between buck, buck-boost, and boost modes of operation, choose low  $R_{DS(ON)}$  MOSFETs and low DCR inductor to satisfy:

$$I_{OUT(MAX)} \leq \frac{0.025 \bullet V_{OUT}}{R_{A,B} + R_{C,D} + R_{SENSE} + R_{L}}$$

where:

$R_{A,B}$  is the maximum  $R_{DS(ON)}$  of MOSFETs A or B at 25°C  $R_{C,D}$  is the maximum  $R_{DS(ON)}$  of MOSFETs C or D at 25°C

R<sub>I</sub> is the maximum DCR resistor of inductor at 25°C

The  $R_{DS(ON)}$  and DCR increase at higher junction temperatures and the process variation have been included in the calculation above.

In order to select the power MOSFETs, the power dissipated by the device must be known. For switch A, the maximum power dissipation happens in boost region, when it remains on all the time. Its maximum power dissipation at maximum output current is given by:

$$P_{A(BOOST)} = \left(\frac{I_{OUT(MAX)} \bullet V_{OUT}}{V_{IN}}\right)^{2} \bullet \rho_{T} \bullet R_{DS(ON)}$$

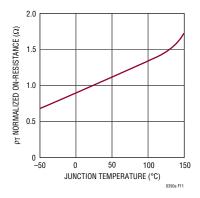

where  $\rho_T$  is a normalization factor (unity at 25°C) accounting for the significant variation in on-resistance with temperature, typically 0.4%/°C as shown in Figure 11. For a maximum junction temperature of 125°C, using a value of  $\rho_T$  = 1.5 is reasonable.

Switch B operates in buck region as the synchronous rectifier. Its power dissipation at maximum output current is given by:

$$P_{B(BUCK)} = \frac{V_{IN} - V_{OUT}}{V_{IN}} \bullet I_{OUT(MAX)}^{2} \bullet \rho_{T} \bullet R_{DS(ON)}$$

Switch C operates in boost region as the control switch. Its power dissipation at maximum current is given by:

$$\begin{split} P_{C(BOOST)} = & \frac{\left(V_{OUT} - V_{IN}\right) \bullet V_{OUT}}{V_{IN}^{2}} \bullet I_{OUT(MAX)}^{2} \bullet \rho_{T} \\ & \bullet R_{DS(ON)} + k \bullet V_{OUT} \quad {}^{3} \bullet \frac{I_{OUT(MAX)}}{V_{IN}} \bullet C_{RSS} \bullet f \end{split}$$

Figure 11. Normalized  $R_{DS(ON)}$  vs Temperature

Rev. I

where C<sub>RSS</sub> is usually specified by the MOSFET manufacturers. The constant k, which accounts for the loss caused by reverse recovery current, is inversely proportional to the gate drive current and has an empirical value of 1.7.

For switch D, the maximum power dissipation happens in boost region, when its duty cycle is higher than 50%. Its maximum power dissipation at maximum output current is given by:

$$P_{D(BOOST)} = \frac{V_{OUT}}{V_{IN}} \bullet I_{OUT(MAX)}^{2} \bullet \rho_{T} \bullet R_{DS(ON)}$$

For the same output voltage and current, switch A has the highest power dissipation and switch B has the lowest power dissipation unless a short occurs at the output.

From a known power dissipated in the power MOSFET, its junction temperature can be obtained using the following formula:

$$T_J = T_A + P \cdot R_{TH(JA)}$$

The junction-to-ambient thermal resistance  $R_{TH(JA)}$  includes the junction-to-case thermal resistance  $R_{TH(JC)}$  and the case-to-ambient thermal resistance  $R_{TH(CA)}$ . This value of  $T_J$  can then be compared to the original, assumed value used in the iterative calculation process.

## Optional Schottky Diode (DB, DD) Selection

The optional Schottky diodes  $D_B$  (in parallel with switch B) and  $D_D$  (in parallel with switch D) conduct during the dead time between the conduction of the power MOSFET switches. They are intended to prevent the body diode of synchronous switches B and D from turning on and storing charge during the dead time. In particular,  $D_B$  significantly reduces reverse recovery current between switch B turn-off and switch A turn-on, and  $D_D$  significantly reduces reverse recovery current between switch D turn-off and switch C turn-on. They improve converter efficiency and reduce switch voltage stress. In order for the diode to be effective, the inductance between it and the synchronous switch must be as small as possible, mandating that these components be placed adjacently.

#### CIN and COUT Selection

Input and output capacitance is necessary to suppress voltage ripple caused by discontinuous current moving in and out the regulator. A parallel combination of capacitors is typically used to achieve high capacitance and low equivalent series resistance (ESR). Dry tantalum, special polymer, aluminum electrolytic and ceramic capacitors are all available in surface mount packages. Capacitors with low ESR and high ripple current ratings, such as OS-CON and POSCAP are also available.

Ceramic capacitors should be placed near the regula-tor input and output to suppress high frequency switching spikes. Ceramic capacitors, of at least  $1\mu F$ , should also be placed from  $V_{IN}$  to GND and  $V_{OUT}$  to GND as close to the LT8390A pins as possible. Due to their excellent low ESR characteristics, ceramic capacitors can significantly reduce input ripple voltage and help reduce power loss in the higher ESR bulk capacitors. X5R or X7R dielectrics are preferred, as these materials retain their capacitance over wide voltage and temperature ranges. Many ceramic capacitors, particularly 0805 or 0603 case sizes, have greatly reduced capacitance at the desired operating voltage.

**Input Capacitance C**<sub>IN</sub>: Discontinuous input current is highest in the buck region due to the switch A toggling on and off. Make sure that the  $C_{IN}$  capacitor network has low enough ESR and is sized to handle the maximum RMS current. In buck region, the input RMS current is given by:

$$I_{RMS} \approx I_{OUT(MAX)} \bullet \frac{V_{OUT}}{V_{IN}} \bullet \sqrt{\frac{V_{IN}}{V_{OUT}}} - 1$$

The formula has a maximum at  $V_{IN} = 2V_{OUT}$ , where  $I_{RMS} = I_{OUT(MAX)}/2$ . This simple worst-case condition is commonly used for design because even significant deviations do not offer much relief.

**Output Capacitance C<sub>OUT</sub>:** Discontinuous current shifts from the input to the output in the boost region. Make sure that the  $C_{OUT}$  capacitor network is capable of reducing the output voltage ripple. The effects of ESR and the bulk capacitance must be considered when choosing the right capacitor for a given output ripple voltage. The maximum

steady state ripple due to charging and discharging the bulk capacitance is given by:

$$\Delta V_{CAP(BOOST)} = \frac{I_{OUT(MAX)} \bullet (V_{OUT} - V_{IN(MIN)})}{C_{OUT} \bullet V_{OUT} \bullet f}$$

$$\Delta V_{CAP(BUCK)} = \frac{V_{OUT} \bullet (1 - \frac{V_{OUT}}{V_{IN(MAX)}})}{8 \bullet L \bullet f^2 \bullet C_{OUT}}$$

The maximum steady ripple due to the voltage drop across the ESR is given by:

$$\Delta V_{\text{ESR(BOOST)}} = \frac{V_{\text{OUT}} \bullet I_{\text{OUT(MAX)}}}{V_{\text{IN(MIN)}}} \bullet \text{ESR}$$

$$\Delta V_{\text{ESR(BUCK)}} = \frac{V_{\text{OUT}} \bullet \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN(MAX)}}}\right)}{L \bullet f} \bullet \text{ESR}$$

#### INTV<sub>CC</sub> Regulator

An internal P-channel low dropout regulator produces 5V at the INTV<sub>CC</sub> pin from the V<sub>IN</sub> supply pin. The INTV<sub>CC</sub> powers internal circuitry and gate drivers in the LT8390A. The INTV<sub>CC</sub> regulator can supply a peak current of 145mA and must be bypassed to ground with a minimum of 4.7 $\mu$ F ceramic capacitor. Good local bypass is necessary to supply the high transient current required by MOSFET gate drivers.

Higher input voltage applications with large MOSFETs being driven at higher switching frequencies may cause the maximum junction temperature rating for the LT8390A to be exceeded. The system supply current is normally dominated by the gate charge current. Additional external loading of the INTV $_{\rm CC}$  also needs to be taken into account for the power dissipation calculation. The total LT8390A power dissipation in this case is  $V_{\rm IN}$  •  $I_{\rm INTVCC}$ , and overall efficiency is lowered. The junction temperature can be estimated by using the equation:

$$T_J = T_A + P_D \bullet \Theta_{JA}$$

where  $\theta_{\text{JA}}$  (in °C/W) is the package thermal resistance.

To prevent maximum junction temperature from being exceeded, the input supply current must be checked operating in continuous mode at maximum  $V_{\text{IN}}$ .

#### Top Gate MOSFET Driver Supply (C<sub>BST1</sub>, C<sub>BST2</sub>)

The top MOSFET drivers, TG1 and TG2, are driven between their respective SW and BST pin voltages. The boost voltages are biased from floating bootstrap capacitors  $C_{BST1}$  and  $C_{BST2}$ , which are normally recharged through both the external and internal bootstrap diodes when the respective top MOSFET is turned off. External bootstrap diodes are recommended because the internal bootstrap diodes are not always strong enough to refresh top MOSFETs at 2MHz. Both capacitors are charged to the same voltage as the INTV $_{CC}$  voltage. The bootstrap capacitors  $C_{BST1}$  and  $C_{BST2}$ , need to store about 100 times the gate charge required by the top switches A and D. In most applications, a 0.1 $\mu$ F to 0.47 $\mu$ F, X5R or X7R dielectric capacitor is adequate.

#### Programming V<sub>IN</sub> UVLO

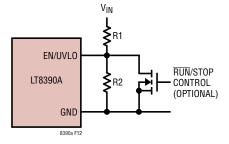

A resistor divider from  $V_{IN}$  to the EN/UVLO pin implements  $V_{IN}$  undervoltage lockout (UVLO). The EN/UVLO enable falling threshold is set at 1.220V with 13mV hysteresis. In addition, the EN/UVLO pin sinks 2.5 $\mu$ A when the voltage on the pin is below 1.220V. This current provides user programmable hysteresis based on the value of R1. The programmable UVLO thresholds are:

$$V_{IN(UVLO+)} = 1.233V \bullet \frac{R1 + R2}{R2} + 2.5\mu A \bullet R1$$

$$V_{IN(UVLO-)} = 1.220V \bullet \frac{R1 + R2}{R2}$$

Figure 12 shows the implementation of external shutdown control while still using the UVLO function. The NMOS grounds the EN/UVLO pin when turned on, and puts the LT8390A in shutdown with quiescent current less than  $2\mu A$ .

Figure 12. V<sub>IN</sub> Undervoltage Lockout (UVLO)

#### **Programming Input or Output Current Limit**

The input or output current limit can be programmed by placing an appropriate value current sense resistor,  $R_{IS}$ , in the input or output power path. The voltage drop across  $R_{IS}$  is (Kelvin) sensed by the ISP and ISN pins. The CTRL pin should be tied to a voltage higher than 1.35V to get the full-scale 100mV (typical) threshold across the sense resistor. The CTRL pin can be used to reduce the current threshold to zero, although relative accuracy decreases with the decreasing sense threshold. When the CTRL pin voltage is between 0.3V and 1.15V, the current limit is:

$$I_{IS(MAX)} = \frac{V_{CTRL} - 0.25V}{10 \bullet R_{IS}}$$

When  $V_{CTRL}$  is between 1.15V and 1.35V the current limit varies with  $V_{CTRL}$ , but departs from the equation above by an increasing amount as  $V_{CTRL}$  increases. Ultimately, when  $V_{CTRL}$  is larger than 1.35V, the current limit no longer varies. The typical  $V_{(ISP-ISN)}$  threshold vs  $V_{CTRL}$  is listed in Table 2.

Table 2. V(ISP-ISN) Threshold vs V<sub>CTRL</sub>

| V <sub>CTRL</sub> (V) | V <sub>(ISP-ISN)</sub> (mV) |

|-----------------------|-----------------------------|

| 1.15                  | 90                          |

| 1.20                  | 94.5                        |

| 1.25                  | 98                          |

| 1.30                  | 99.5                        |

| 1.35                  | 100                         |

|                       |                             |

When  $V_{\text{CTRL}}$  is larger than 1.35V, the current threshold is regulated to:

$$I_{IS(MAX)} = \frac{100mV}{R_{IS}}$$