Buck-Boost Battery Charge Controller with Maximum Power Point Tracking (MPPT)

#### **FEATURES**

- V<sub>IN</sub> Range: 6V to 80VV<sub>BAT</sub> Range: 1.3V to 80V

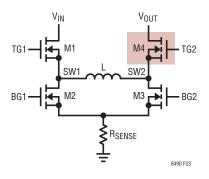

- Single Inductor Allows V<sub>IN</sub> Above, Below, or Equal to V<sub>RAT</sub>

- Automatic MPPT for Solar Powered Charging

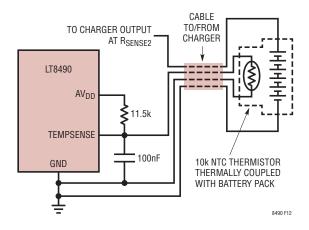

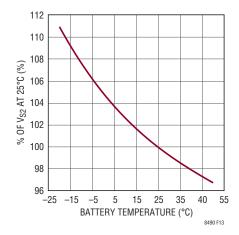

- Automatic Temperature Compensation

- No Software or Firmware Development Required

- Operation from Solar Panel or DC Supply

- Input and Output Current Monitor Pins

- Four Integrated Feedback Loops

- Synchronizable Fixed Frequency: 100kHz to 400kHz

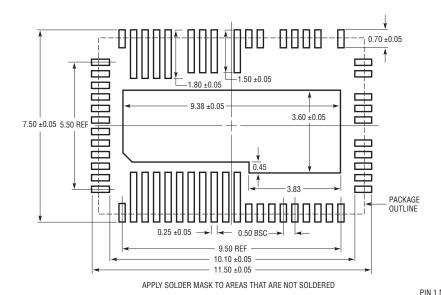

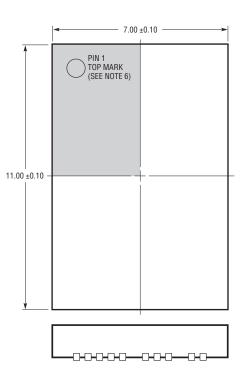

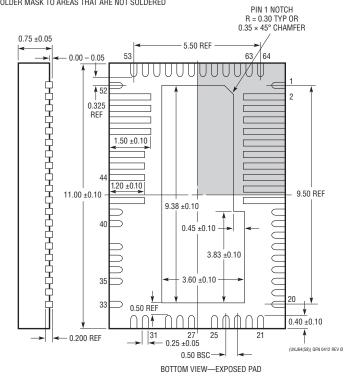

- 64-Lead (7mm × 11mm × 0.75mm) QFN Package

#### **APPLICATIONS**

- Solar Powered Battery Chargers

- Multiple Types of Lead-Acid Battery Charging

- Li-Ion Battery Charger

- Battery Equipped Industrial or Portable Military Equipment

## **DESCRIPTION**

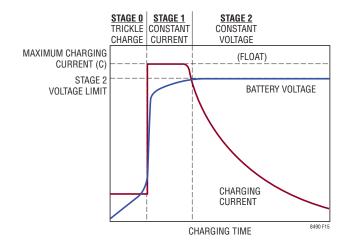

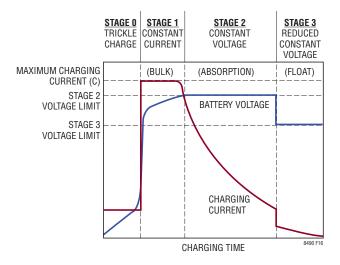

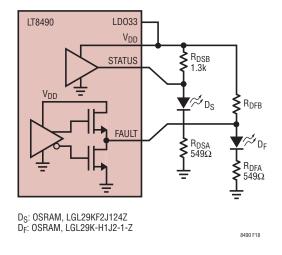

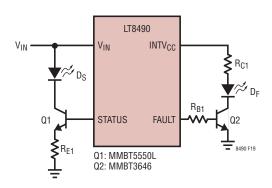

The LT®8490 is a buck-boost switching regulator battery charger that implements a constant-current constant-voltage (CCCV) charging profile used for most battery types, including sealed lead-acid (SLA), flooded, gel and lithium-ion. The device operates from input voltages above, below or equal to the output voltage and can be powered by a solar panel or a DC power supply. On-chip logic provides automatic maximum power point tracking (MPPT) for solar powered applications. The LT8490 can perform automatic temperature compensation by sensing an external thermistor thermally coupled to the battery. STATUS and FAULT pins containing charger information can be used to drive LED indicator lamps. The device is available in a low profile (0.75mm) 7mm × 11mm 64-lead QFN package.

$\mathcal{O}$ , LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

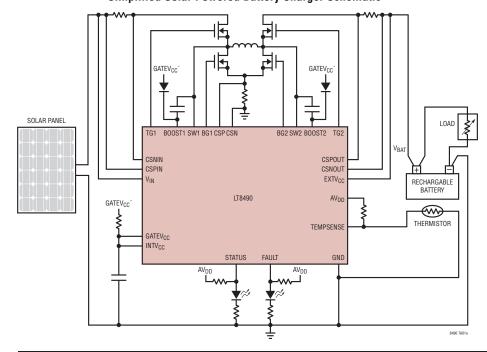

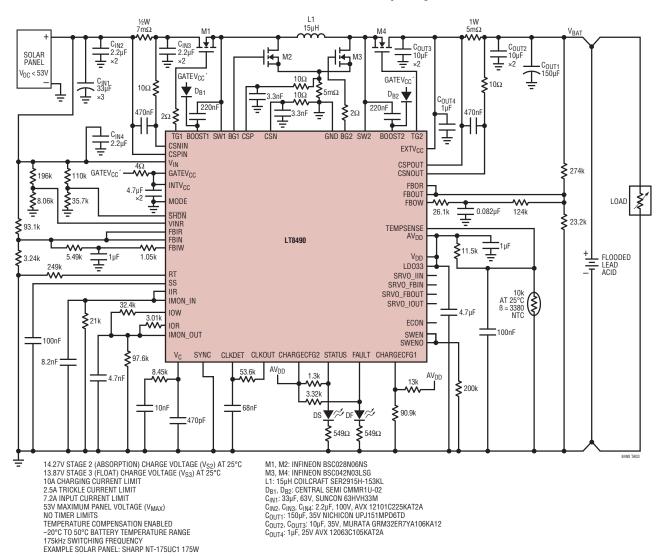

#### TYPICAL APPLICATION

Simplified Solar Powered Battery Charger Schematic

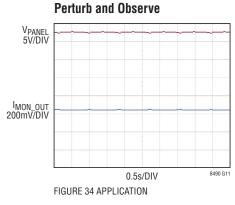

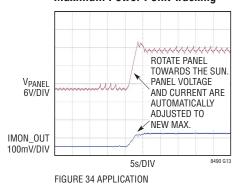

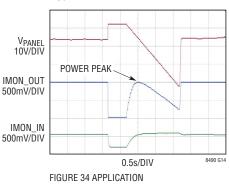

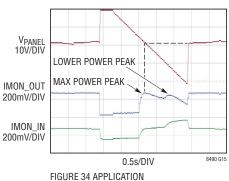

# Maximum Power Point Tracking FULL PANEL SCAN

VPANEL 6V/DIV

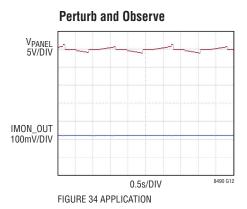

PERTURB & OBSERVE

1.36A/DIV

0.55/DIV

PERTURB & OBSERVE

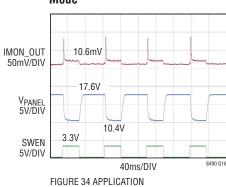

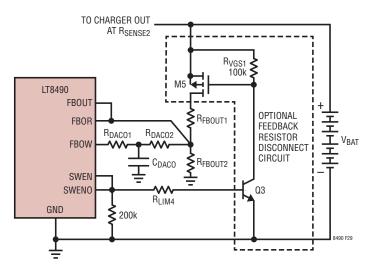

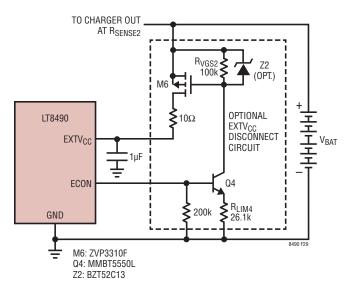

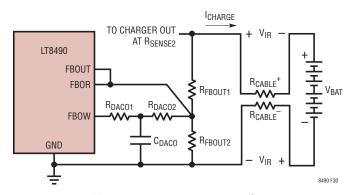

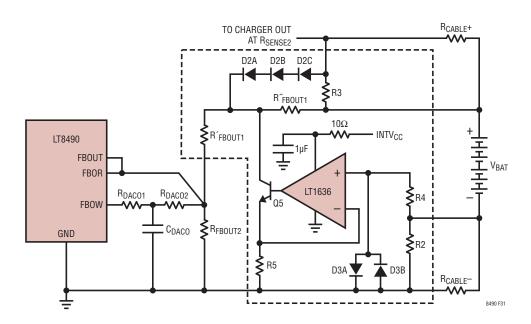

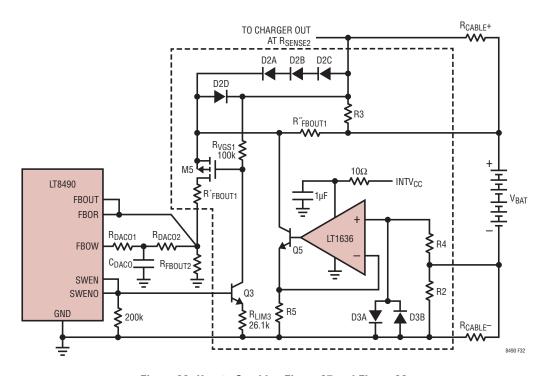

BACK PAGE APPLICATION

#### **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| V <sub>CSP</sub> - V <sub>CSN</sub> , V <sub>CSPIN</sub> - V <sub>CSNIN</sub> , |

|---------------------------------------------------------------------------------|

| V <sub>CSPOUT</sub> - V <sub>CSNOUT</sub> 0.3V to 0.3V                          |

| SS, CLKOUT, CSP, CSN Voltage0.3V to 3V                                          |

| V <sub>C</sub> Voltage (Note 2)0.3V to 2.2V                                     |

| LD033, V <sub>DD</sub> , AV <sub>DD</sub> Voltage0.3V to 5V                     |

| RT, FBOUT Voltage0.3V to 5V                                                     |

| IMON_IN, IMON_OUT Voltage0.3V to 5V                                             |

| SYNC Voltage0.3V to 5.5V                                                        |

| INTV <sub>CC</sub> , GATEV <sub>CC</sub> Voltage0.3V to 7V                      |

| $V_{B00ST1} - V_{SW1}$ , $V_{B00ST2} - V_{SW2}$ 0.3V to 7V                      |

| SWEN, MODE Voltage                                                              |

| SRVO_FBIN, SRVO_FBOUT Voltage0.3V to 30V                                        |

| SRVO_IIN, SRVO_IOUT Voltage                                                     |

| FBIN, SHDN Voltage                                                              |

| CSNIN, CSPIN, CSPOUT, CSNOUT Voltage0.3V to 80V                                 |

| V <sub>IN</sub> , EXTV <sub>CC</sub> Voltage                                    |

| SW1, SW2 Voltage                                                                |

| BOOST1, BOOST2 Voltage0.3V to 87V<br>BG1, BG2, TG1, TG2(Note 4)                 |

| IOW, ECON, CLKDET Voltage $-0.3V$ to $V_{DD} + 0.5V$                            |

| SWENO, STATUS Voltage                                                           |

| FBOW, FBIW, FAULT Voltage $-0.3V$ to $V_{DD} + 0.5V$                            |

| VINR, FBOR, IIR, IOR Voltage $-0.3V$ to $V_{DD} + 0.5V$                         |

| TEMPSENSE Voltage0.3V to V <sub>DD</sub> + 0.5V                                 |

| CHARGECFG2,                                                                     |

| CHARGECFG1 Voltage0.3V to V <sub>DD</sub> + 0.5V                                |

### **Operating Junction Temperature Range**

| LT8490E (Notes 1, 3)      | 40°C to 125°C |

|---------------------------|---------------|

| LT8490I (Notes 1, 3)      | 40°C to 125°C |

| Storage Temperature Range |               |

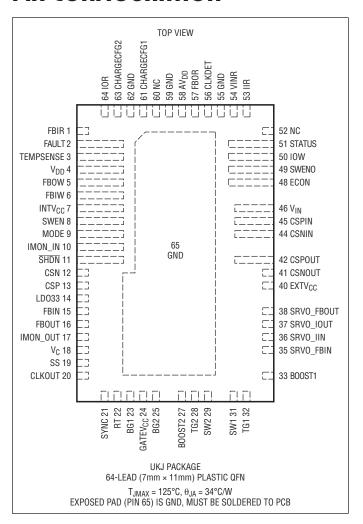

## PIN CONFIGURATION

#### ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL    | PART MARKING* | PACKAGE DESCRIPTION              | TEMPERATURE RANGE |

|------------------|------------------|---------------|----------------------------------|-------------------|

| LT8490EUKJ#PBF   | LT8490EUKJ#TRPBF | LT8490UKJ     | 64-Lead (7mm × 11mm) Plastic QFN | -40°C to 125°C    |

| LT8490IUKJ#PBF   | LT8490IUKJ#TRPBF | LT8490UKJ     | 64-Lead (7mm × 11mm) Plastic QFN | -40°C to 125°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

LINEAR TECHNOLOGY **ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25\,^{\circ}$ C.  $V_{IN} = 12V$ ,  $V_{DD} = AV_{DD} = 3.3V$ , SHDN = 3V unless otherwise noted. (Note 3)

| PARAMETER                                        | CONDITIONS                                                                                                                                                                                                                                                                                  |   | MIN                        | TYP                | MAX                        | UNITS                |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------------|--------------------|----------------------------|----------------------|

| Voltage Supply and Regulators                    |                                                                                                                                                                                                                                                                                             |   |                            |                    |                            |                      |

| V <sub>IN</sub> Operating Voltage Range (Note 7) |                                                                                                                                                                                                                                                                                             | • | 6                          |                    | 80                         | V                    |

| V <sub>IN</sub> Quiescent Current                | Not Switching, $V_{EXTVCC} = 0$ , $V_{DD} = AV_{DD} = Float$                                                                                                                                                                                                                                |   |                            | 2.65               | 4.2                        | mA                   |

| V <sub>IN</sub> Quiescent Current in Shutdown    | $V_{\overline{S}H\overline{D}\overline{N}} = 0V$                                                                                                                                                                                                                                            |   |                            | 0                  | 1                          | μA                   |

| V <sub>DD</sub> Quiescent Current                | $I_{AVDD} + I_{VDD}, V_{DD} = AV_{DD} = 3.3V$                                                                                                                                                                                                                                               | • | 2.5                        | 4                  | 6.5                        | mA                   |

| EXTV <sub>CC</sub> Switchover Voltage            | I <sub>INTVCC</sub> = 20mA, V <sub>EXTVCC</sub> Rising                                                                                                                                                                                                                                      | • | 6.15                       | 6.4                | 6.6                        | V                    |

| EXTV <sub>CC</sub> Switchover Hysteresis         |                                                                                                                                                                                                                                                                                             |   |                            | 0.18               |                            | V                    |

| LD033 Pin Voltage                                | 5mA from LDO33 Pin                                                                                                                                                                                                                                                                          | • | 3.23                       | 3.295              | 3.35                       | V                    |

| LD033 Pin Load Regulation                        | I <sub>LD033</sub> = 0.1mA to 5mA                                                                                                                                                                                                                                                           |   |                            | -0.25              | -1                         | %                    |

| LD033 Pin Current Limit                          |                                                                                                                                                                                                                                                                                             | • | 12                         | 17.25              | 22                         | mA                   |

| LD033 Pin Undervoltage Lockout                   | LD033 Falling                                                                                                                                                                                                                                                                               |   | 2.96                       | 3.04               | 3.12                       | V                    |

| LD033 Pin Undervoltage Lockout Hysteresis        |                                                                                                                                                                                                                                                                                             |   |                            | 35                 |                            | mV                   |

| Switching Regulator Control                      |                                                                                                                                                                                                                                                                                             |   |                            |                    |                            |                      |

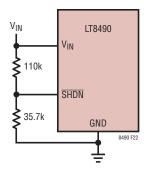

| SHDN Input Voltage High                          | SHDN Rising to Enable the Device                                                                                                                                                                                                                                                            | • | 1.184                      | 1.234              | 1.284                      | V                    |

| SHDN Input Voltage High Hysteresis               |                                                                                                                                                                                                                                                                                             |   |                            | 50                 |                            | mV                   |

| SHDN Input Voltage Low                           | Device Disabled, Low Quiescent Current                                                                                                                                                                                                                                                      | • |                            |                    | 0.35                       | V                    |

| SHDN Pin Bias Current                            | V <sub>SHDN</sub> = 3V<br>V <sub>SHDN</sub> = 12V                                                                                                                                                                                                                                           |   |                            | 0<br>11            | 1<br>22                    | μΑ<br>μΑ             |

| SWEN Rising Threshold Voltage                    |                                                                                                                                                                                                                                                                                             | • | 1.156                      | 1.206              | 1.256                      | V                    |

| SWEN Threshold Voltage Hysteresis                |                                                                                                                                                                                                                                                                                             |   |                            | 22                 |                            | mV                   |

| MODE Pin Thresholds                              | Discontinuous Mode<br>Forced Continuous Mode                                                                                                                                                                                                                                                | • | 0.4                        |                    | 2.3                        | V                    |

| IMON_OUT Rising threshold for CCM Operation      | MODE = 0V                                                                                                                                                                                                                                                                                   | • | 168                        | 195                | 224                        | mV                   |

| IMON_OUT Falling threshold for DCM               | MODE = 0V                                                                                                                                                                                                                                                                                   | • | 95                         | 122                | 150                        | mV                   |

| Voltage Regulation                               |                                                                                                                                                                                                                                                                                             |   |                            |                    |                            |                      |

| Regulation Voltage for FBOUT                     | $V_C = 1.2V$ , EXTV <sub>CC</sub> = 0V                                                                                                                                                                                                                                                      | • | 1.193                      | 1.207              | 1.222                      | V                    |

| Regulation Voltage for FBIN                      | $V_C = 1.2V$ , EXTV <sub>CC</sub> = 0V                                                                                                                                                                                                                                                      | • | 1.184                      | 1.205              | 1.226                      | V                    |

| FBOUT Pin Bias Current                           | Current Out of Pin                                                                                                                                                                                                                                                                          |   |                            | 15                 |                            | nA                   |

| FBIN Pin Bias Current                            | Current Out of Pin                                                                                                                                                                                                                                                                          |   |                            | 10                 |                            | nA                   |

| Current Regulation                               |                                                                                                                                                                                                                                                                                             |   |                            |                    |                            |                      |

| Regulation Voltage for IMON_IN and IMON_OUT      | $V_C = 1.2V$ , $EXTV_{CC} = 0V$                                                                                                                                                                                                                                                             | • | 1.187                      | 1.208              | 1.229                      | V                    |

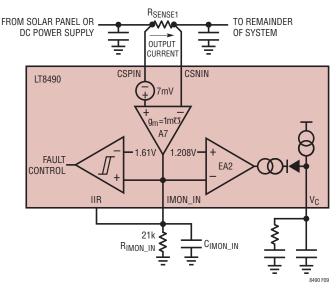

| IMON_IN Output Current                           | $V_{CSPIN} - V_{CSNIN} = 50 \text{mV}, V_{CSPIN} = 5.025 \text{V}$<br>$V_{CSPIN} - V_{CSNIN} = 50 \text{mV}, V_{CSPIN} = 5.025 \text{V}$<br>$V_{CSPIN} - V_{CSNIN} = 0 \text{mV}, V_{CSPIN} = 5 \text{V}$                                                                                   | • | 54<br>53<br>2.5            | 57<br>57<br>7      | 60<br>61<br>11.5           | μΑ<br>μΑ<br>μΑ       |

| IMON_IN Overvoltage Threshold                    |                                                                                                                                                                                                                                                                                             | • | 1.55                       | 1.61               | 1.67                       | V                    |

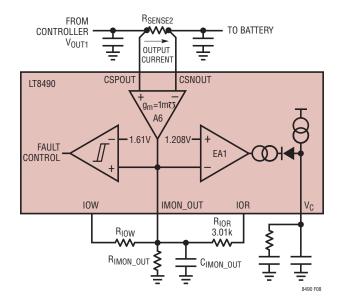

| IMON_OUT Output Current                          | $\begin{split} &V_{CSPOUT}-V_{CSNOUT}=50\text{mV}, V_{CSPOUT}=5.025\text{V} \\ &V_{CSPOUT}-V_{CSNOUT}=50\text{mV}, V_{CSPOUT}=5.025\text{V} \\ &V_{CSPOUT}-V_{CSNOUT}=5\text{mV}, V_{CSPOUT}=5.0025\text{V} \\ &V_{CSPOUT}-V_{CSNOUT}=5\text{mV}, V_{CSPOUT}=5.0025\text{V} \\ \end{split}$ | • | 47.5<br>47<br>3.25<br>2.75 | 50<br>50<br>5<br>5 | 52.5<br>54.25<br>6.75<br>8 | μΑ<br>μΑ<br>μΑ<br>μΑ |

| IMON_OUT Overvoltage Threshold                   |                                                                                                                                                                                                                                                                                             | • | 1.55                       | 1.61               | 1.67                       | V                    |

|                                                  |                                                                                                                                                                                                                                                                                             |   |                            |                    |                            |                      |

## **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25\,^{\circ}\text{C}$ . $V_{IN} = 12\text{V}$ , $V_{DD} = AV_{DD} = 3.3\text{V}$ , $\overline{SHDN} = 3\text{V}$ unless otherwise noted. (Note 3)

| Switch Frequency Range         Synding or Free Running         0         400         kHz           Switch Frequency, fogo         R₁ = 365k         • 102         120         142         kHz           Switching Frequency, fogo         R₁ = 365k         • 102         120         142         kHz           SYNC High Level for Synchronization         • 133         • 00         kHz           SYNC Low Level for Synchronization         • 13         • 0.5         V           SYNC Clock Pulse Duty Oycle         Vsvnc = 0V to 2V         20         80         %           80 Recommended Min SYNC Batio, fsync/fosc         Ima Out of CLKOUT Pin         2.3         2.45         2.55         V           CLKOUT Duty Voltage HIGH         Ima Out of CLKOUT Pin         2.23         2.45         2.55         V           CLKOUT Duty Oycle         Ima Out of CLKOUT Pin         2.27         3.0         2.7         %           CLKOUT Duty Oycle         Ima Out of CLKOUT Pin         2.27         3.0         2.7         %           CLKOUT Duty Oycle         Ima Out of CLKOUT Pin         2.27         3.0         V           CLKOUT Duty Oycle         Ima Out of CLKOUT Pin         2.27         3.0         V           STATUS, FROM, FBINK, SWENO, IOW. <th>PARAMETER</th> <th>CONDITIONS</th> <th></th> <th>MIN</th> <th>TYP</th> <th>MAX</th> <th>UNITS</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PARAMETER                                                                       | CONDITIONS                        |   | MIN  | TYP   | MAX  | UNITS |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------|---|------|-------|------|-------|

| Switching Frequency, f <sub>OSC</sub> R <sub>T</sub> = 365k<br>R <sub>T</sub> = 124k         0         102<br>102         120<br>22         125<br>235         440<br>417         441<br>412                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Switching Regulator Oscillator (OSC1)                                           |                                   |   |      |       |      |       |

| R <sub>T</sub> = 215k                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Switch Frequency Range                                                          | Syncing or Free Running           |   | 100  |       | 400  | kHz   |

| SYNC High Level for Synchronization         ■ 1.3         V           SYNC Clock Pulse Duty Cycle         V <sub>SYNC</sub> = 0V to 2V         20         80         %           Recommended Min SYNC Ratio, I <sub>SYNC</sub> /I <sub>OSC</sub> V <sub>SYNC</sub> = 0V to 2V         20         80         %           CLKOUT Output Voltage HIGH         1mA Out of CLKOUT Pin         2.3         2.45         2.55         V           CLKOUT Dutput Voltage LIGH         1mA into CLKOUT Pin         2.3         2.45         2.55         V           CLKOUT Dutput Voltage LOW         1mA into CLKOUT Pin         2.3         2.45         2.55         V           CLKOUT Duty Voltage LOW         1mA into CLKOUT Pin         2.27         30         10         10           Charging Control         1mA into CLKOUT Pin         2.27         44.1         %         %           Charging Control         1mA into CLKOUT Pin         2.2         2.7         30         V           Charging Control         1mA into CLKOUT Pin         2.2         2.7         30         V           Charging Control         1mA         2.2         2.7         3.0         V           Charging Control         1mA         2.2         2.7         3.0         V           STATUS, FBOW, FB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Switching Frequency, f <sub>OSC</sub>                                           | R <sub>T</sub> = 215k             | • | 170  | 202   | 235  | kHz   |

| SYNC Clock Pulse Duty Cycle         V <sub>SYNC</sub> = OV to 2V         20         80         %           Recommended Min SYNC Ratio, f <sub>SYNC</sub> /f <sub>OSC</sub> 1 mA Out of CLKOUT Pin         2.3 2.45 2.55         V           CLKOUT output Voltage LOW         1 mA into CLKOUT Pin         2.3 2.5 5.50         V           CLKOUT Duty Cycle         T <sub>J</sub> = -40°C<br>T <sub>J</sub> = 25°C<br>T <sub>J</sub> = 25°C         44.1 4 %         %           Charging Control         5 main         2.2.7 4.41 6 %         %           STATUS, FBOW, FBIW, SWENO, IOW, ECON Output Low Voltage         Io <sub>U</sub> = 5mA         • 0.22 0.5 V           STATUS, FBOW, FBIW, SWENO, IOW, ECON Output Voltage Low         Io <sub>U</sub> = 5mA         • 0.1 0.2 V         0.5 V           FAULT Output Voltage Low         Io <sub>U</sub> = 0.5mA         • 0.1 0.2 0.5 V         V           FAULT Output Voltage High         Io <sub>H</sub> = 0.1mA         • 1.7 2.2 V         V           Power Supply Mode Detection Threshold (Note 6)         VINR Pin Falling         • 155 174 mV         mV           Minimum VINR Voltage for Start-Up (Note 6)         VINR Pin Falling         • 155 174 mV         mV           Minimum VINR Voltage for Start-Up (Note 6)         Io R Rising → ECON Rising         • 168 195 224 mV         mV           High Charging Current Threshold on IOR (Note 6)         Io R Rising → ECON Rising         • 168 195 96 6 mV         % <td>SYNC High Level for Synchronization</td> <td>1</td> <td>•</td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SYNC High Level for Synchronization                                             | 1                                 | • |      |       |      |       |

| SYNC Clock Pulse Duty Cycle         V <sub>SYNC</sub> = 0V to 2V         20         80         %           Recommended Min SYNC Ratio, f <sub>SYNC</sub> /f <sub>OSC</sub> 1         3/4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                 |                                   | • |      |       | 0.5  | V     |

| Recommended Min SYNC Ratio, f <sub>SYNE</sub> /f <sub>oSC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                 | V <sub>SYNC</sub> = 0V to 2V      |   | 20   |       | 80   | %     |

| CLKOUT Output Voltage HIGH         1mA Out of CLKOUT Pin         2.3         2.45         2.55         V           CLKOUT Output Voltage LOW         1mA into CLKOUT Pin         25         100         mV           CLKOUT Duty Cycle         T <sub>J</sub> = -40°C<br>T <sub>J</sub> = 25°C<br>T <sub>J</sub> = 125°C         22.7         3.0         44.1         %           CEARGING Control         STATUS, FBOW, FBIW, SWENO, IOW, EDON Output Low Voltage         IoL = 5mA         •         0.22         0.5         V           STATUS, FBOW, FBIW, SWENO, IOW, EON Output High Voltage         IoL = 5mA         •         2.7         3.0         V           FAULT Output Voltage Low         IoL = 0.5mA         •         0.1         0.1         0.25         V           FAULT Output Voltage Low         IoL = 0.5mA         •         1.0         0.1         0.25         V           FAULT Output Voltage Low         IoL = 0.5mA         •         1.5         1.7         2.2         V           Power Supply Mode Detection Threshold (Note 6)         VINR Pin Falling         •         1.5         1.74         mV           Power Supply Mode Detection Threshold on IOR (Note 6)         VINR Pin         2.3         2.2         V           Minimum Charage Creat Batter Up (Note 6)         IoR Rising         •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Recommended Min SYNC Ratio, f <sub>SYNG</sub> /f <sub>OSC</sub>                 | 0.110                             |   |      | 3/4   |      |       |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                 | 1mA Out of CLKOUT Pin             |   | 2.3  | 2.45  | 2.55 | V     |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                 | 1mA into CLKOUT Pin               |   |      | 25    | 100  | mV    |

| STATUS, FBOW, FBIW, SWENO, 10W, ECON Output Low Voltage   10L = 5mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                 | $T_J = 25$ °C                     |   |      | 44.1  |      | %     |

| STATUS, FBOW, FBIW, SWENO, IOW, ECON Output Low Voltage   10H = -5mA   0   2.7   3.0   V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Charging Control                                                                |                                   |   |      |       |      |       |

| ECON Output High Voltage FAULT Output Voltage Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                 | $I_{OL} = 5mA$                    | • |      | 0.22  | 0.5  | V     |

| FAULT Output Voltage High $I_{DH} = -0.1 mA$ $0.1.7$ 2.2 $V$ Voltage High $I_{DH} = -0.1 mA$ $0.1.7$ 2.2 $V$ Power Supply Mode Detection Threshold (Note 6) VINR Pin Falling $0.155$ 174 $V$ mV Power Supply Mode Detection Threshold Hysteresis (Note 6) VINR Pin $V_{NR} = 0.0 m$ Minimum VINR Voltage for Start-Up (Note 6) $V_{NR} = 0.0 m$ Not in Power Supply Mode Low Power Mode Enabled Low Power Mode Disabled $V_{NR} = 0.0 m$ Not in Power Supply Mode Low Power Mode Enabled Low Power Mode Disabled $V_{NR} = 0.0 m$ Not in Power Supply Mode Low Power Mode Enabled $V_{NR} = 0.0 m$ Not in Power Supply Mode Low Power Mode Disabled $V_{NR} = 0.0 m$ Not in Power Supply Mode Low Power Mode Disabled $V_{NR} = 0.0 m$ Not in Power Supply Mode Low Power Mode Disabled $V_{NR} = 0.0 m$ Not in Power Supply Mode Low Power Mode Disabled $V_{NR} = 0.0 m$ Not in Power Supply Mode Low Power Mode Enabled $V_{NR} = 0.0 m$ Not in Power Supply Mode Low Power Mode Disabled $V_{NR} = 0.0 m$ Not in Power Supply Mode Low Power Mode Disabled $V_{NR} = 0.0 m$ Not in Power Supply Mode Low Power Mode Disabled $V_{NR} = 0.0 m$ Not in Power Supply Mode Low Power Mode Disabled $V_{NR} = 0.0 m$ Not in Power Supply Mode Low Power Mode Disabled $V_{NR} = 0.0 m$ Not in Power Supply Mode Low Power Mode Disabled $V_{NR} = 0.0 m$ Not in Power Supply Mode Low Power Mode Disabled $V_{NR} = 0.0 m$ Not in Power Supply Mode Low Power Mode Disable Dis |                                                                                 | I <sub>OH</sub> = -5mA            | • | 2.7  | 3.0   |      | V     |

| Power Supply Mode Detection Threshold (Note 6)   VINR Pin Falling   155   174   mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | FAULT Output Voltage Low                                                        | $I_{OL} = 0.5 \text{mA}$          | • |      | 0.1   | 0.25 | V     |

| Power Supply Mode Detection Threshold Hysteresis (Note 6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FAULT Output Voltage High                                                       | $I_{OH} = -0.1 \text{mA}$         | • | 1.7  | 2.2   |      | V     |

| Minimum VINR Voltage for Start-Up (Note 6)   Not in Power Supply Mode Low Power Mode Enabled Low Power Mode Disabled   380 395 225 237 mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Power Supply Mode Detection Threshold (Note 6)                                  | VINR Pin Falling                  | • | 155  | 174   |      | mV    |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Power Supply Mode Detection Threshold Hysteresis (Note 6)                       | VINR Pin                          |   |      | 29    |      | mV    |

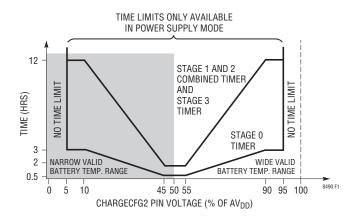

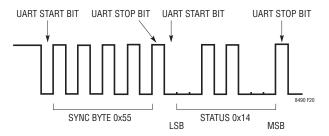

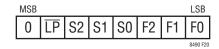

| Low Charging Current Threshold on IOR (Note 6)IOR Falling → ECON Falling95122150mVMinimum CHARGECFG1 % of AVDD to Disable Stage 3 (Note 6)Temperature Compensation Enabled949596%Maximum CHARGECFG1 % of AVDD to Disable Stage 3 (Note 6)Temperature Compensation Disabled456%Minimum CHARGECFG2 % of AVDD to Disable Time Limits (Note 6)Wide Valid Temperature Range949596%Maximum CHARGECFG2 % of AVDD to Disable Time Limits (Note 6)Narrow Valid Temperature Range456%Minimum TEMPSENSE % of AVDD to Detect Battery Disconnected (Note 6)VCSXOUT Common Mode = 5.0V, RTOTAL from IMON_OUT to Ground = 24.3kΩ9697.5%VCSPOUT − VCSNOUT Threshold for C/5 Detection (Note 6)VCSXOUT Common Mode = 5.0V, RTOTAL from IMON_OUT to Ground = 24.3kΩ4.2555.75mVFBIW, FBOW PWM Frequency (OSC2)31.25kHzFBIW, FBOW PWM Resolution8BitsSTATUS UART Bit Rate• 216024002640Baud                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Minimum VINR Voltage for Start-Up (Note 6)                                      | Low Power Mode Enabled            | • |      |       |      | 1     |

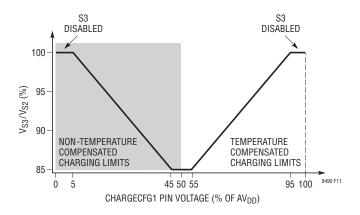

| Minimum CHARGECFG1 % of AVDD to Disable Stage 3<br>(Note 6)Temperature Compensation Enabled• 949596%Maximum CHARGECFG1 % of AVDD to Disable Stage 3<br>(Note 6)Temperature Compensation Disabled<br>Wide Valid Temperature Range• 456%Minimum CHARGECFG2 % of AVDD to Disable Time Limits<br>(Note 6)Wide Valid Temperature Range• 949596%Maximum CHARGECFG2 % of AVDD to Disable Time Limits<br>(Note 6)Narrow Valid Temperature Range• 456%Minimum TEMPSENSE % of AVDD to Detect Battery Disconnected<br>(Note 6)• 94.59697.5%VCSPOUT - VCSNOUT Threshold for C/5 Detection (Note 6)VCSXOUT Common Mode = 5.0V, RTOTAL from<br>IMON_OUT to Ground = 24.3kΩ91011mVVCSPOUT - VCSNOUT Threshold for C/10 Detection (Note 6)VCSXOUT Common Mode = 5.0V, IOR Falling,<br>RTOTAL from IMON_OUT to Ground = 24.3kΩ4.2555.75mVFBIW, FBOW PWM Frequency (OSC2)31.25kHzFBIW, FBOW PWM Resolution8BitsSTATUS UART Bit Rate• 216024002640Baud                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | High Charging Current Threshold on IOR (Note 6)                                 | IOR Rising → ECON Rising          | • | 168  | 195   | 224  | mV    |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Low Charging Current Threshold on IOR (Note 6)                                  | IOR Falling → ECON Falling        | • | 95   | 122   | 150  | mV    |

| Minimum CHARGECFG2 % of AV <sub>DD</sub> to Disable Time Limits (Note 6)   Wide Valid Temperature Range   94   95   96   % (Note 6)   Maximum CHARGECFG2 % of AV <sub>DD</sub> to Disable Time Limits (Note 6)   Maximum TEMPSENSE % of AV <sub>DD</sub> to Detect Battery Disconnected (Note 6)   94.5   96   97.5   % (Note 6)   V <sub>CSPOUT</sub> Common Mode = 5.0V, R <sub>TOTAL</sub> from IMON_OUT to Ground = 24.3kΩ   9   10   11   mV IMON_OUT Threshold for C/10 Detection (Note 6)   V <sub>CSPOUT</sub> Common Mode = 5.0V, IOR Falling, R <sub>TOTAL</sub> from IMON_OUT to Ground = 24.3kΩ   4.25   5   5.75   mV R <sub>TOTAL</sub> from IMON_OUT to Ground = 24.3kΩ   8   Bits STATUS UART Bit Rate   9   2160   2400   2640   Baud                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                 | Temperature Compensation Enabled  | • | 94   | 95    | 96   | %     |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                 | Temperature Compensation Disabled | • | 4    | 5     | 6    | %     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                 | Wide Valid Temperature Range      | • | 94   | 95    | 96   | %     |

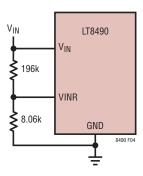

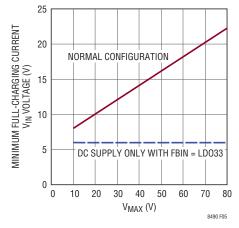

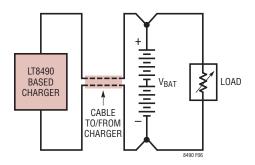

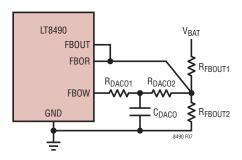

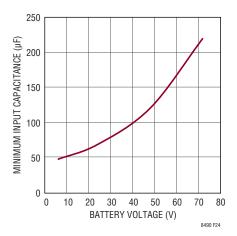

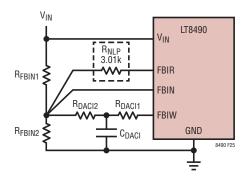

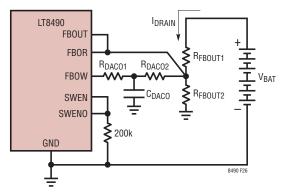

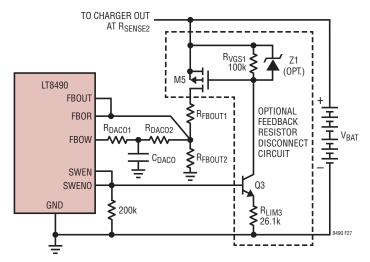

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                 | Narrow Valid Temperature Range    | • | 4    | 5     | 6    | %     |