# 5V 3A Output, 42V Input USB Charger with Cable Drop Compensation and Dataline Protection

## **FEATURES**

- Wide V<sub>IN</sub> Range Up to 42V

- Programmable Cable Drop Compensation Provides Accurate 5V Regulation to Remote USB Sockets

- High Speed USB 2.0 Compliant Dataline Switches

- Selectable Charger Profiles Including Major Vendors' and USB BC 1.2 Profiles

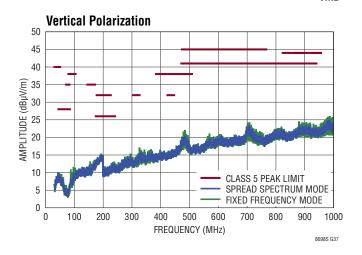

- Silent Switcher®2 Technology and Selectable Spread-Spectrum Modulation Provide Ultralow EMI

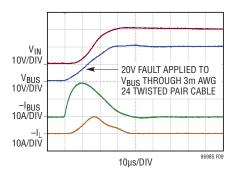

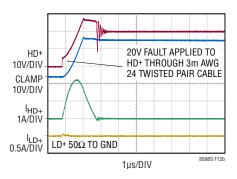

- Robust Dataline Protection

- Tolerant of Short Condition Up to 20V

- ESD Protected Up to IEC61000-4-2 8kV Contact Discharge and 15kV Air Discharge

- Available Status and Fault Output Pins

- Programmable and Synchronizable Switching Frequency 300kHz to 3MHz

- Selectable Forced Continuous or Pulse-Skipping Modes

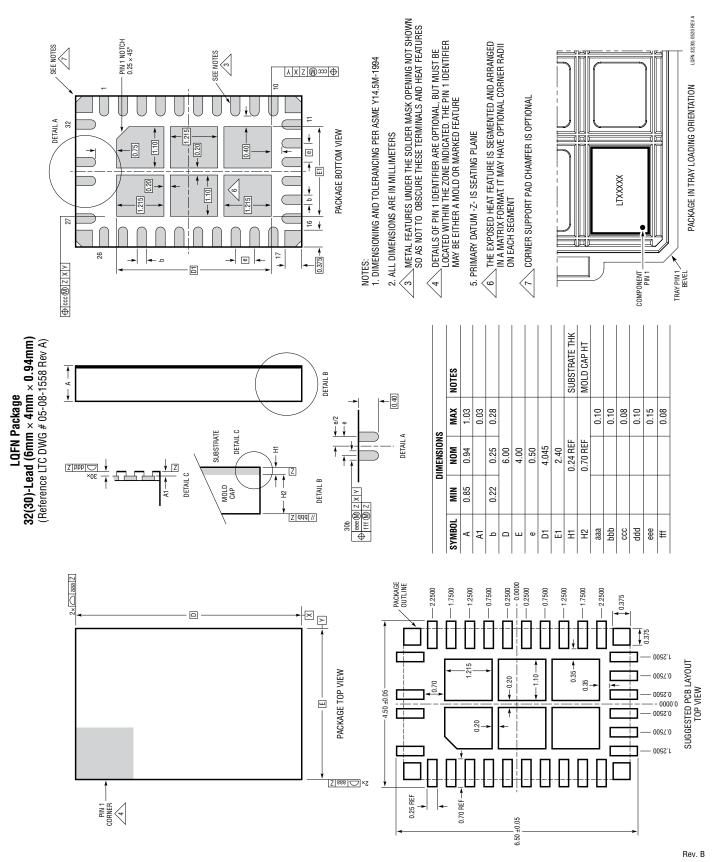

- Small 4mm × 6mm × 0.94mm LQFN Package with 0.75mm Spacing from V<sub>IN</sub> to GND Pins

- AEC-Q100 Qualified for Automotive Applications

## **APPLICATIONS**

- Automotive USB

- Industrial USB

### DESCRIPTION

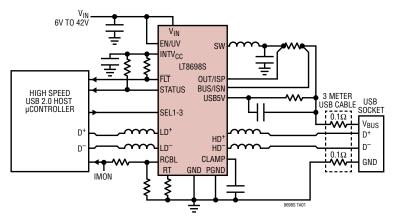

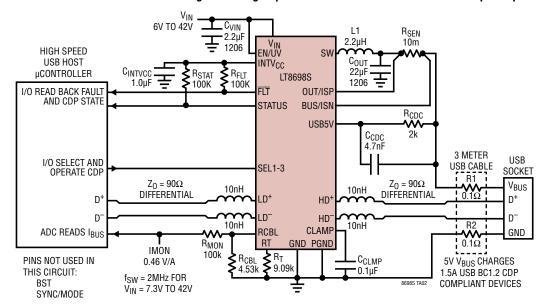

The LT®8698S is a compact, high efficiency, synchronous monolithic step-down switching regulator designed to power the 5V USB  $V_{BUS}$  rail with up to 3A from an input voltage as high as 42V. Programmable cable drop compensation maintains accurate 5V  $V_{BUS}$  regulation even for USB sockets separated from the LT8698S by a long cable such as an automobile wiring harness. Silent Switcher Technology and selectable spread-spectrum modulation provide ultralow EMI/EMC.

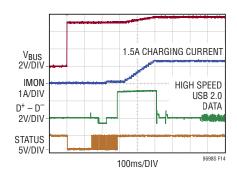

The LT8698S supports a wide variety of portable device charger profiles including USB BC 1.2 CDP, DCP, and SDP as well as common proprietary profiles. Integrated  $V_{BUS}$  reset and  $V_{BUS}$  regulator disable functions support USB OTG functionality.

The LT8698S's robust high speed USB 2.0 data line switches protect the upstream USB host  $\mu$ Controller from short-circuit conditions up to 20V and ESD events up to IEC61000-4-2 8kV contact discharge and 15kV air discharge levels. Further V<sub>BUS</sub> monitor and fault protection features eliminate the need for a USB power switch. The LT8698S includes two parallel 10nF capacitors from V<sub>IN</sub> to PGND for improved EMI/EMC performance. The LT8698S-1 does not include these capacitors.

All registered trademarks and trademarks are the property of their respective owners.

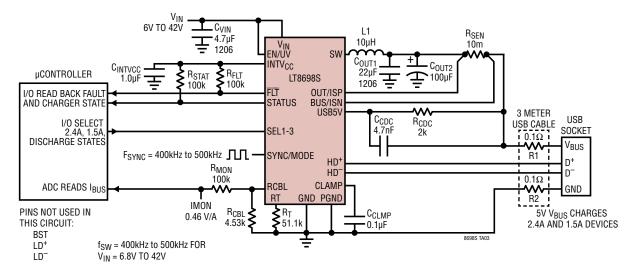

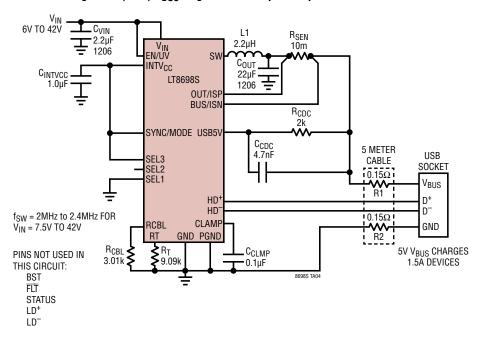

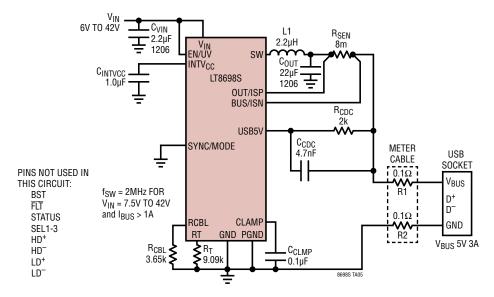

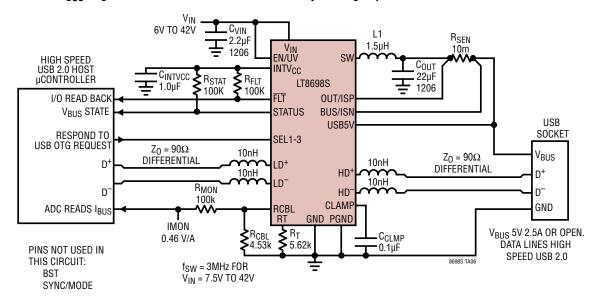

## TYPICAL APPLICATION

Automotive Charger with High Speed Dataline Protection and Cable Drop Compensation

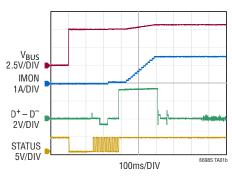

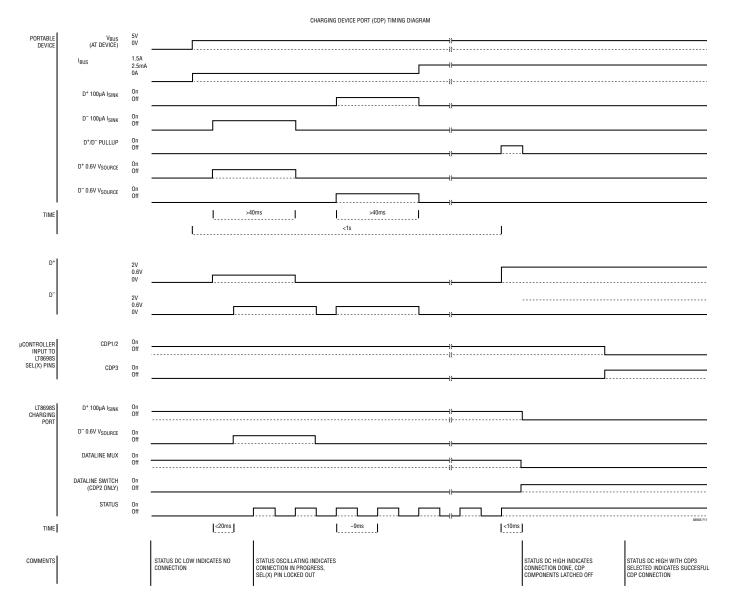

**USB BC1.2 CDP Session**

Rev. B

1

## **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| V <sub>IN</sub> , EN/UV, OUT/ISP, BUS/ISN, USB5V | l2V |

|--------------------------------------------------|-----|

| HD+, HD-, CLAMP2                                 | 20V |

| SYNC/MODE, FLT, STATUS,                          |     |

| SEL1, SEL2, SEL3, LD+, LD                        | .6V |

| RCBL, RT                                         | .2V |

| Operating Junction Temperature Range (Note 2)    |     |

| LT8698SE40°C to 125                              | 5°C |

| LT8698SJ40°C to 150                              | )°C |

| Storage Temperature Range65°C to 150             | )°C |

| Peak Package Body Reflow Temperature260          | )°C |

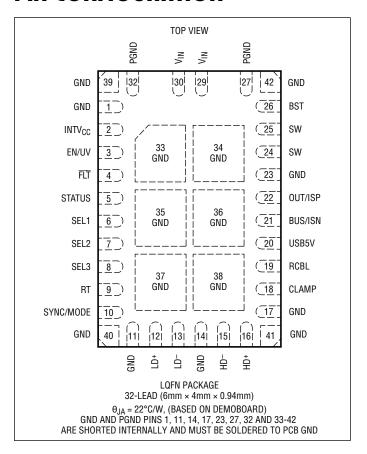

## PIN CONFIGURATION

## ORDER INFORMATION

|                    |                    | PAD OR BALL         | PART MARKING |             | PART MARKING           |                | PACKAGE        | MSL                                           | TEMPERATURE RANGE |                |            |             |            |     |        |    |                     |   |                |

|--------------------|--------------------|---------------------|--------------|-------------|------------------------|----------------|----------------|-----------------------------------------------|-------------------|----------------|------------|-------------|------------|-----|--------|----|---------------------|---|----------------|

| LEAD FREE FINISH   | TAPE AND REEL      | FINISH              | DEVICE       | FINISH CODE | TYPE                   | RATING         | (SEE NOTE 2)   |                                               |                   |                |            |             |            |     |        |    |                     |   |                |

| LT8698SEV#PBF      | LT8698SEV#TRPBF    |                     | 8698V        |             |                        |                | -40°C to 125°C |                                               |                   |                |            |             |            |     |        |    |                     |   |                |

| LT8698SJV#PBF      | LT8698SJV#TRPBF    | Au (Dalle)          | 00901        | e4          | LQFN (Laminate Package | 3              | -40°C to 150°C |                                               |                   |                |            |             |            |     |        |    |                     |   |                |

| LT8698SEV-1#PBF    | LT8698SEV-1#TRPBF  | with QFN Footprint) |              | Au (Norio)  | Au (Norio)             | Au (NUNS)      | Au (NUNS)      | Au (NUNS)                                     | Au (NUIIS)        | Au (NUNS)      | Au (Norio) | Au (110113) | Au (Horio) | , , | 8698S1 | 64 | with QFN Footprint) | J | -40°C to 125°C |

| LT8698SJV-1#PBF    | LT8698SJV-1#TRPBF  |                     | 009001       |             |                        |                | -40°C to 150°C |                                               |                   |                |            |             |            |     |        |    |                     |   |                |

| AUTOMOTIVE PRODUCT | S**                |                     |              |             |                        |                |                |                                               |                   |                |            |             |            |     |        |    |                     |   |                |

| LT8698SEV#WPBF     | LT8698SEV#WTRPBF   | 8698V               |              |             |                        | -40°C to 125°C |                |                                               |                   |                |            |             |            |     |        |    |                     |   |                |

| LT8698SJV#WPBF     | LT8698SJV#WTRPBF   |                     |              | Au (RoHS)   | (RoHS)                 | Au (RoHS)      |                | LQFN (Laminate Package<br>with QFN Footprint) | 3                 | -40°C to 150°C |            |             |            |     |        |    |                     |   |                |

| LT8698SEV-1#WPBF   | LT8698SEV-1#WTRPBF | Au (nuno)           |              |             |                        |                | e4             |                                               |                   | -40°C to 125°C |            |             |            |     |        |    |                     |   |                |

| LT8698SJV-1#WPBF   | LT8698SJV-1#WTRPBF |                     | 009031       |             |                        |                | -40°C to 150°C |                                               |                   |                |            |             |            |     |        |    |                     |   |                |

- · Device temperature grade is indicated by a label on the shipping container.

- Pad or ball finish code is per IPC/JEDEC J-STD-609.

- · Recommended PCB Assembly and Manufacturing Procedures.

- Package and Tray Drawings

- \*\*Versions of this part are available with controlled manufacturing to support the quality and reliability requirements of automotive applications. These models are designated with a #W suffix. Only the automotive grade products shown are available for use in automotive applications. Contact your local Analog Devices account representative for specific product ordering information and to obtain the specific Automotive Reliability reports for these models.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25\,^{\circ}\text{C}$ . (Note 2)

| SYMBOL                  | PARAMETER                                                 | MIN                                                                                                                                                                                  | TYP | MAX                   | UNITS                |                        |                   |

|-------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------|----------------------|------------------------|-------------------|

|                         | V <sub>IN</sub> Shutdown Current                          | V <sub>EN/UV</sub> = 0.25V, V <sub>IN</sub> = 12V                                                                                                                                    |     |                       | 0.1                  | 1                      | μА                |

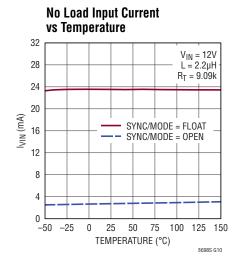

|                         | V <sub>IN</sub> Current in Regulation                     | I <sub>LOAD</sub> = 0A, V <sub>SYNC/MODE</sub> = 0V, V <sub>IN</sub> = 12V (Note 4)<br>I <sub>LOAD</sub> = 0A, V <sub>SYNC/MODE</sub> = Open, V <sub>IN</sub> = 12V (Note 4)         | •   |                       | 2.5<br>23            | 4<br>36                | mA<br>mA          |

| V <sub>CHG</sub>        | Regulator Output Voltage at BUS/ISN                       | I <sub>LOAD</sub> = 0A, R <sub>CBL</sub> = 3.57k (Note 4)<br>I <sub>LOAD</sub> = 2.4A, R <sub>CBL</sub> = 3.57k (Note 4)<br>I <sub>LOAD</sub> = 0A, V <sub>USB5V</sub> = 0V (Note 4) | •   | 4.925<br>5.52<br>5.93 | 5.00<br>5.61<br>6.05 | 5.063<br>5.680<br>6.13 | V<br>V<br>V       |

|                         | USB5V Voltage                                             | V <sub>IN</sub> = 5V to 42V                                                                                                                                                          | •   | 4.915                 | 4.99                 | 5.053                  | V                 |

|                         | Upper FLT Threshold Offset                                | Percentage of V <sub>USB5V</sub> , V <sub>USB5V</sub> Falling                                                                                                                        | •   | 4                     | 7                    | 10                     | %                 |

|                         | Lower FLT Threshold Offset                                | Percentage of V <sub>USB5V</sub> , V <sub>USB5V</sub> Rising                                                                                                                         | •   | 4                     | 7                    | 10                     | %                 |

|                         | FLT Threshold Hysteresis                                  | Percentage of V <sub>USB5V</sub>                                                                                                                                                     |     |                       | 3                    |                        | %                 |

| I <sub>CDP</sub>        | Regulator Output Current Limit                            | $V_{BUS/ISN} = 4.5V$ , $R_{SEN} = 10m\Omega$                                                                                                                                         |     | 2.55                  | 2.65                 | 2.75                   | А                 |

|                         | Latch-On Time in Current Limit                            | V <sub>BUS/ISN</sub> = 0.2V                                                                                                                                                          |     | 3.4                   | 4.2                  | 5                      | ms                |

| T <sub>SHTDWN_REC</sub> | Latch-Off Time in Current Limit                           | V <sub>BUS/ISN</sub> = 0.2V                                                                                                                                                          |     | 48                    | 59                   | 70                     | ms                |

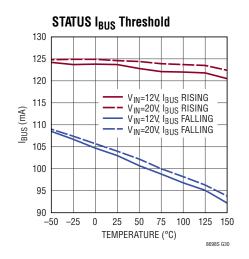

|                         | Regulator Output Current STATUS<br>Threshold              | $I_{BUS/ISN}$ Falling, $R_{SEN} = 10m\Omega$                                                                                                                                         |     | 20                    | 100                  | 180                    | mA                |

|                         | Regulator Output Current STATUS<br>Threshold Hysteresis   | $R_{SEN} = 10 m\Omega$                                                                                                                                                               |     |                       | 20                   |                        | mA                |

|                         | Regulator Output Sink Current                             | tor Output Sink Current $V_{BUS/ISN} = 6.3V$ (Note 4)                                                                                                                                |     |                       |                      | -1.7                   | A                 |

|                         | R <sub>CBL</sub> Monitor Voltage                          | $I_{LOAD}$ = 0A, $R_{SEN}$ = 10mΩ<br>$I_{LOAD}$ = 2.4A, $R_{SEN}$ = 10mΩ                                                                                                             | •   | 0<br>1.05             | 2<br>1.10            | 50<br>1.15             | mV<br>V           |

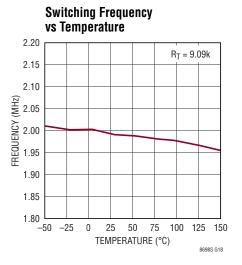

|                         | Oscillator Frequency                                      | R <sub>T</sub> = 9.09k<br>R <sub>T</sub> = 66.5k<br>R <sub>T</sub> = 5.76k                                                                                                           | •   | 1.8<br>255<br>2.7     | 2<br>300<br>3        | 2.2<br>345<br>3.3      | MHz<br>kHz<br>MHz |

|                         | SYNC/MODE Low Threshold for<br>Pulse-Skip Operation       | V <sub>SYNC/MODE</sub> Rising                                                                                                                                                        | •   | 0.3                   | 0.7                  | 1.1                    | V                 |

|                         | SYNC/MODE Input High for Synced Operation                 |                                                                                                                                                                                      | •   | 1.5                   |                      |                        | V                 |

|                         | SYNC/MODE Input Low for Synced Operation                  |                                                                                                                                                                                      | •   |                       |                      | 0.4                    | V                 |

|                         | SYNC/MODE High Threshold for<br>Spread Spectrum Operation | V <sub>SYNC/MODE</sub> Rising                                                                                                                                                        | •   | 2.7                   | 3.2                  | 3.7                    | V                 |

|                         | SYNC/MODE Pull Up Current for Forced Continuous Operation | V <sub>SYNC/MODE</sub> = 2V                                                                                                                                                          | •   | 2                     | 4.25                 | 6.5                    | μА                |

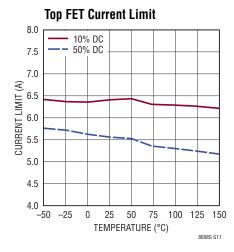

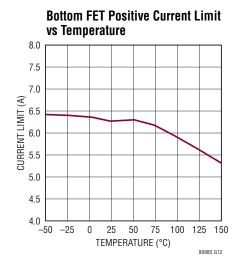

|                         | Top Switch Max Current Limit                              |                                                                                                                                                                                      |     | 5                     | 6                    | 7                      | А                 |

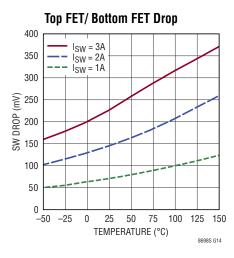

|                         | Top Switch On Resistance                                  | I <sub>SW</sub> = 1A                                                                                                                                                                 |     |                       | 75                   |                        | mΩ                |

|                         | Bottom Switch On Resistance                               | I <sub>SW</sub> = 1A                                                                                                                                                                 |     |                       | 75                   |                        | mΩ                |

|                         | SW Leakage Current                                        |                                                                                                                                                                                      |     | -1                    | 0                    | 1                      | μA                |

|                         | EN/UV Threshold                                           | V <sub>EN/UV</sub> Falling                                                                                                                                                           | •   | 1.17                  | 1.31                 | 1.45                   | ٧                 |

|                         | EN/UV Threshold Hysteresis                                |                                                                                                                                                                                      |     |                       | 150                  |                        | mV                |

|                         | EN/UV Current                                             | V <sub>EN/UV</sub> = 2V                                                                                                                                                              |     | -100                  |                      | 100                    | nA                |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 2)

| SYMBOL                        | PARAMETER                                        | CONDITIONS                                                                                                  |   | MIN      | TYP        | MAX    | UNITS    |

|-------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---|----------|------------|--------|----------|

|                               | FLT Pull Down Resistance                         | V <sub>FLT</sub> = 0.1V                                                                                     | • |          | 150        | 300    | Ω        |

|                               | FLT Leakage                                      | V <sub>FLT</sub> = 4V                                                                                       |   |          |            | 1      | μА       |

|                               | STATUS Pull Down Resistance                      | V <sub>STATUS</sub> = 0.1V                                                                                  | • |          | 150        | 300    | Ω        |

|                               | STATUS Leakage                                   | V <sub>STATUS</sub> = 4V                                                                                    |   |          |            | 1      | μА       |

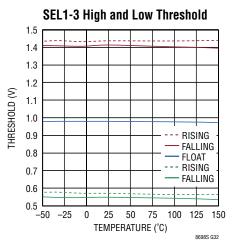

|                               | SEL1-3 Low Threshold                             | V <sub>SEL</sub> Rising                                                                                     | • | 0.48     | 0.58       | 0.68   | V        |

|                               | SEL1-3 Low Threshold Hysteresis                  |                                                                                                             |   |          | 35         |        | mV       |

|                               | SEL1-3 High Threshold                            | V <sub>SEL</sub> Falling                                                                                    | • | 1.31     | 1.41       | 1.51   | V        |

|                               | SEL1-3 High Threshold Hysteresis                 |                                                                                                             |   |          | 35         |        | mV       |

|                               | SEL1-3 Float Voltage                             |                                                                                                             | • | 0.9      | 1.0        | 1.1    | V        |

|                               | SEL1-3 Input Current                             | V <sub>SEL</sub> = 4V<br>V <sub>SEL</sub> = 0V                                                              |   |          | 45<br>–15  |        | μA<br>μA |

|                               | SEL1-3 De-bounce Time                            |                                                                                                             |   | 1.25     | 1.5        | 1.75   | ms       |

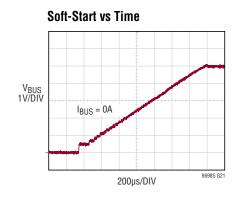

|                               | Soft Start Time                                  |                                                                                                             |   | 0.7      | 1.1        | 1.6    | ms       |

| DATALINE SV                   | VITCHES                                          |                                                                                                             | • |          |            |        |          |

| $V_{OL}$ , $V_{OH}$           | Signal Range                                     |                                                                                                             | • | 0        |            | 3.6    | V        |

|                               | Off HD+, HD <sup>-</sup> Current                 | $V_{HD}^+, V_{HD}^- = 3.6V, V_{LD}^+, V_{LD}^- = 0V$<br>$V_{HD}^+, V_{HD}^- = 20V, V_{LD}^+, V_{LD}^- = 0V$ |   | -1       | 0<br>0.75  | 1      | μA<br>mA |

|                               | Off LD+, LD <sup>-</sup> Current                 | $V_{HD}^+, V_{HD}^- = 0V, V_{LD}^+, V_{LD}^- = 3.6V$<br>$V_{HD}^+, V_{HD}^- = 20V, V_{LD}^+, V_{LD}^- = 0V$ |   | -1<br>-1 | 0<br>0     | 1<br>1 | μA<br>μA |

|                               | On Leakage Current                               | $V_{HD}^+, V_{HD}^- = 3.6V, 0V$                                                                             |   | -100     | 0          | 100    | nA       |

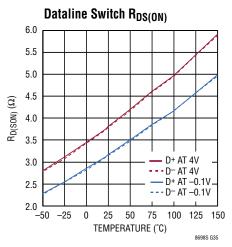

|                               | On Resistance                                    | $V_{HD}^+$ , $V_{HD}^- = 0V$ , 3.6V, $I_{LD}^+$ , $I_{LD}^- = 20mA$                                         |   |          | 3          |        | Ω        |

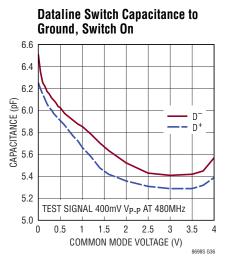

|                               | On Capacitance to Ground                         | $V_{HD}^+$ , $V_{HD}^- = 200 \text{mV}_{DC}$ , $400 \text{mV}_{P-P}$ , $480 \text{MHz}$ (Note 5)            |   |          | 6.1        |        | pF       |

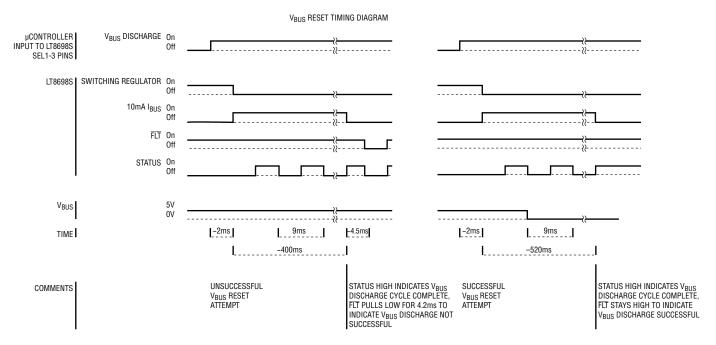

| V <sub>BUS</sub> DISCHA       | IRGE                                             |                                                                                                             |   |          |            |        |          |

|                               | BUS/ISN Discharge Current Sink                   | V <sub>BUS/ISN</sub> = 5V                                                                                   |   | 6        | 9          | 12     | mA       |

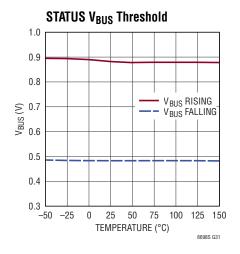

| V <sub>BUS_LKG</sub>          | BUS/ISN Discharge Status<br>Threshold            | V <sub>BUS/ISN</sub> Falling                                                                                |   |          | 0.5        | 0.7    | V        |

|                               | BUS/ISN Discharge Status<br>Threshold Hysteresis |                                                                                                             |   |          | 0.35       |        | V        |

| T <sub>VLD_VLKG</sub>         | Maximum BUS/ISN Discharge Time                   | V <sub>BUS/ISN</sub> = 1V                                                                                   |   |          | 400        | 500    | ms       |

| T <sub>VBUS_REAPP</sub>       | Minimum BUS/ISN Low Time                         | V <sub>BUS/ISN</sub> = 1V                                                                                   |   | 100      | 120        |        | ms       |

|                               | STATUS Oscillation Period                        |                                                                                                             |   | 7.5      | 9          | 10.5   | ms       |

| V <sub>BUS</sub> OFF          |                                                  |                                                                                                             |   |          |            |        |          |

| I <sub>VBUS_LKG_</sub><br>SRC | Regulator Output Leakage Current                 | V <sub>BUS/ISN</sub> = 0V<br>V <sub>BUS/ISN</sub> = 5V                                                      |   | -70      | -0.1<br>15 | 80     | μΑ<br>μΑ |

| R <sub>OTG_VBUS</sub>         | Regulator Output Resistance                      | V <sub>BUS/ISN</sub> = 0.75V                                                                                |   | 10       | 350        |        | kΩ       |

|                               | •                                                | ·                                                                                                           | • |          |            |        |          |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25\,^{\circ}\text{C}$ . (Note 2)

| SYMBOL                                       | PARAMETER                                                   | CONDITIONS                                |   | MIN   | TYP  | MAX  | UNITS |

|----------------------------------------------|-------------------------------------------------------------|-------------------------------------------|---|-------|------|------|-------|

| USB BCS 1.2                                  | CHARGING DOWNSTREAM PORT PRO                                | FILE                                      |   |       |      |      |       |

| V <sub>DAT_REF</sub>                         | HD <sup>+</sup> Data Detect Voltage                         | V <sub>HD</sub> <sup>+</sup> Rising       |   | 0.25  | 0.32 | 0.40 | V     |

|                                              | HD+ Data Detect Hysteresis                                  |                                           |   |       | 45   |      | mV    |

| $\overline{V_{IH}}$                          | HD+, HD <sup>-</sup> Logic High                             |                                           |   | 2.0   |      |      | V     |

| $V_{IL}$                                     | HD+, HD <sup>-</sup> Logic Low                              |                                           |   |       |      | 0.8  | V     |

| $V_{LGC}$                                    | HD+, HD <sup>-</sup> Logic Threshold                        |                                           |   | 0.8   | 1.4  | 2.0  | V     |

| $V_{DM\_SRC}$                                | HD <sup>-</sup> Voltage Source                              | $I_{HD}^- = -100 \mu A, V_{HD}^+ = 0.6 V$ |   | 0.5   | 0.6  | 0.7  | V     |

| I <sub>DP_SINK</sub>                         | HD+ Current Source                                          | $V_{HD}^{+} = 0.6V$                       |   | 25    | 100  | 175  | μА    |

| V <sub>DAT_SINK</sub>                        | HD <sup>+</sup> Data Sink Voltage                           | I <sub>HD</sub> <sup>+</sup> = 25μA       |   |       | 0.06 | 0.15 | V     |

| T <sub>VDMSRC_EN</sub>                       | HD <sup>-</sup> Voltage Source Enable Time                  | $V_{HD}^{+} = 0.6V$                       |   |       | 0.5  | 20   | ms    |

| T <sub>CON_IDPSNK_</sub>                     | HD+ Current Source Connect Disable<br>Time                  | $V_{HD}^+ = 2V$                           |   |       | 0.75 | 10   | ms    |

| T <sub>VDPSRC_ON</sub>                       | Minimum Accepted HD+ Voltage<br>Source On Time              | $V_{HD}^{+} = 0.6V$                       |   |       | 32   | 40   | ms    |

| T <sub>VDMSRC_DIS</sub>                      | HD <sup>-</sup> Voltage Source Disable Time                 | $V_{HD}^+ = 0V$                           |   |       | 0.5  | 20   | ms    |

|                                              | Minimum Accepted HD <sup>+</sup> Source<br>Voltage Off Time | $V_{HD}^+ = 0V$                           |   |       | 32   | 40   | ms    |

| T <sub>SVLD_CON_</sub><br>PWD                | Maximum Accepted USB Connect<br>Time                        | V <sub>HD</sub> +, <sub>HD</sub> -= 0V    |   | 1     | 1.15 |      | S     |

| USB BCS 1.2                                  | DEDICATED CHARGING PORT PROFIL                              | E                                         | ' |       |      |      |       |

| R <sub>DCP_DAT</sub>                         | Dataline Short Resistance                                   | $V_{HD}^{+} = 0.6V, I_{HD}^{-} = -2.5mA$  |   |       | 85   | 200  | Ω     |

| R <sub>DAT_LKG</sub>                         | Dataline Short Pull Down Resistance                         |                                           |   | 300   | 500  |      | kΩ    |

| USB BCS 1.2                                  | STANDARD DOWNSTREAM PORT PRO                                | )FILE                                     |   |       |      |      |       |

| R <sub>DP_DWN</sub> ,<br>R <sub>DM_DWN</sub> | Dataline Termination Resistor                               |                                           |   | 14.25 | 20   | 24.8 | kΩ    |

| 2.4A CHARGE                                  | R PROFILE                                                   |                                           |   |       |      |      |       |

|                                              | HD+ Voltage                                                 | V <sub>BUS/ISN</sub> = 5V                 |   | 2.60  | 2.68 | 2.76 | V     |

|                                              | HD+ Output Resistance                                       |                                           |   |       | 23   |      | kΩ    |

|                                              | HD <sup>-</sup> Voltage                                     | V <sub>BUS/ISN</sub> = 5V                 |   | 2.60  | 2.68 | 2.76 | V     |

|                                              | HD <sup>-</sup> Output Resistance                           |                                           |   |       | 23   |      | kΩ    |

| 2.1A CHARGE                                  | R PROFILE                                                   |                                           |   |       |      |      |       |

|                                              | HD+ Voltage                                                 | V <sub>BUS/ISN</sub> = 5V                 |   | 2.60  | 2.68 | 2.76 | V     |

|                                              | HD <sup>+</sup> Output Resistance                           |                                           |   |       | 23   |      | kΩ    |

|                                              | HD <sup>-</sup> Voltage                                     | V <sub>BUS/ISN</sub> = 5V                 |   | 1.94  | 2.00 | 2.06 | V     |

|                                              | HD <sup>-</sup> Output Resistance                           |                                           |   |       | 30   |      | kΩ    |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25$ °C. (Note 2)

| SYMBOL             | PARAMETER                              | CONDITIONS                |   | MIN  | TYP  | MAX  | UNITS |  |

|--------------------|----------------------------------------|---------------------------|---|------|------|------|-------|--|

| 1A CHARGER PROFILE |                                        |                           |   |      |      |      |       |  |

|                    | HD+ Voltage                            | V <sub>BUS/ISN</sub> = 5V |   | 1.94 | 2.00 | 2.06 | V     |  |

|                    | HD+ Output Resistance                  |                           |   |      | 30   |      | kΩ    |  |

|                    | HD <sup>-</sup> Voltage                | V <sub>BUS/ISN</sub> = 5V |   | 2.60 | 2.68 | 2.76 | V     |  |

|                    | HD <sup>-</sup> Output Resistance      |                           |   |      | 23   |      | kΩ    |  |

| 2A CHARGE          | R PROFILE                              |                           | · |      |      |      |       |  |

|                    | HD+, HD <sup>-</sup> Voltage           | V <sub>BUS/ISN</sub> = 5V |   | 1.2  | 1.25 | 1.35 | V     |  |

|                    | HD+, HD <sup>-</sup> Output Resistance |                           |   |      | 7.5  |      | kΩ    |  |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

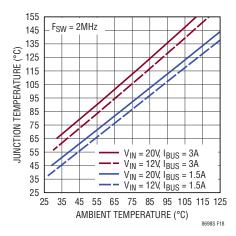

**Note 2:** The LT8698SE and LT8698SE-1 are guaranteed to meet performance specifications from 0°C to 125°C junction temperature. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LT8698SJ and LT8698SJ-1 are guaranteed over the full -40°C to 150°C operating temperature range. High junction temperatures degrade operating lifetime. Operating lifetime is de-rated at junction temperatures greater than 125°C. The junction

temperature ( $T_J$  in °C) is calculated from the ambient temperature ( $T_A$  in °C) and power dissipation (PD in Watts) according to the formula:

$$T_J = T_A + (P_D \bullet \theta_{JA})$$

where  $\theta_{JA}$  (in °C/W) is the package thermal impedance.

**Note 3:** This IC includes overtemperature protection that is intended to protect the device during overload conditions. Junction temperature will exceed 150°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature will reduce lifetime.

**Note 4:** DUT configured in closed loop test circuit similar to page 36 CDP charger application circuit.

**Note 5:** Parameter not tested in production.

**Note 6:**  $\theta$  values are determined by simulation per JESD51 conditions, except  $\theta_{JA}$  value is determined by simulation with demo board. See Applications Information section for more information on PCB layout considerations and example thermal data.

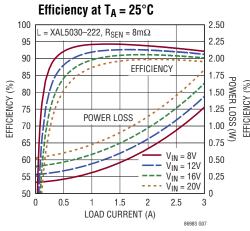

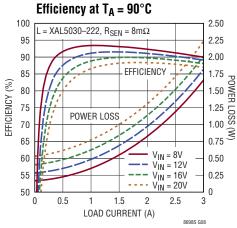

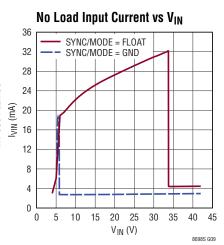

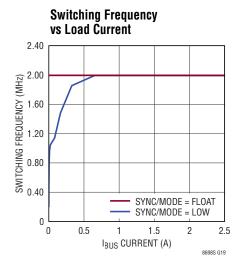

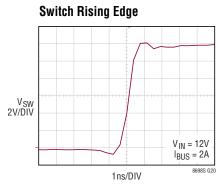

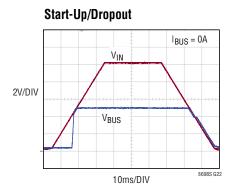

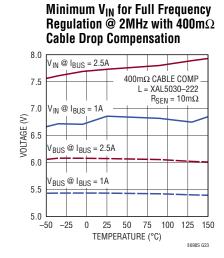

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, $V_{IN} = 12$ V unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , $V_{IN} = 12V$ unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = 25$ °C,  $V_{IN} = 12V$  unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , $V_{IN} = 12V$ unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, $V_{IN} = 12$ V unless otherwise noted.

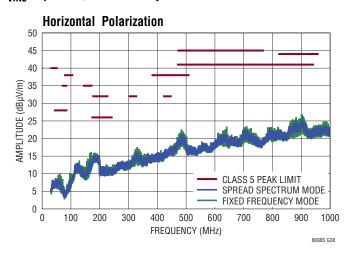

Radiated EMI Performance, (CISPR25 Radiated Emission with Peak Detector and Class 5 Peak Limit) DC2688A Demo Board with EMI Filter Installed,  $V_{IN} = 14V$ ,  $I_{VBUS} = 2.5A$ ,  $f_{SW} = 2MHz$ , L = XFL4020-222,  $C_{VIN2}$  and  $C_{VIN3}$  Populated, LT8698S Only

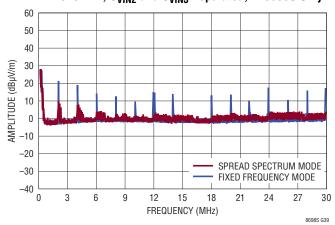

**Conducted EMI Performance** DC2688A Demo Board with EM Filter Installed,  $V_{IN}$  = 14V,  $I_{VBUS}$  = 2.5A,  $f_{SW}$  = 2MHz, L = XFL4020-222,  $C_{VIN2}$  and  $C_{VIN3}$  Populated, LT8698S Only

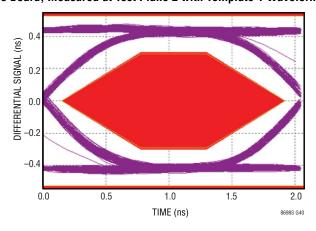

High Speed USB 2.0 Eye Diagram DC2688A Demo Board, Measured at Test Plane 2 with Template 1 Waveform Requirements

## PIN FUNCTIONS

**GND** (Pins 1, 11, 14, 17, 23): The GND pins are the return side of the internal control circuits and must be tied to ground. All GND and PGND pins are internally shorted together.

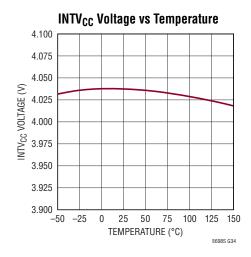

**INTV**<sub>CC</sub> (**Pin 2**): INTV<sub>CC</sub> is the bypass pin of the internal 4V linear regulator. This pin powers the internal power switch gate drivers and control circuits. INTV<sub>CC</sub> may be loaded by external termination resistors up to 1mA. For reliable operation, do not overload INTV<sub>CC</sub>. Bypass this pin to ground with a 1 $\mu$ F low ESR ceramic capacitor placed close to the LT8698S.

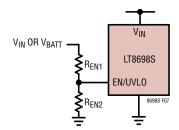

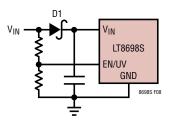

**EN/UV (Pin 3):** EN/UV is the enable and programmable undervoltage lockout pin. The LT8698S is shut down when the EN/UV pin is below its threshold and enabled when above. The threshold voltage is 1.46V with EN/UV rising and 1.31V with EN/UV falling. EN/UV below 0.25V reduces the  $V_{IN}$  current to <1 $\mu$ A. An external resistor divider from  $V_{IN}$  can be used to program an undervoltage lockout threshold below which the LT8698S will shut down. See the Applications Information section for additional information. Tie EN/UV to  $V_{IN}$  if not used.

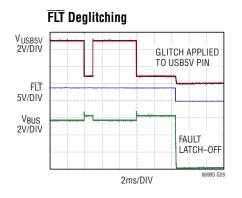

**FLT** (**Pin 4**): FLT is the open drain output of the internal fault logic. FLT pulls low after 4.2ms of a sustained fault condition in which the output voltage is not is regulation. FLT pulls low immediately if INTV<sub>CC</sub> < 3.6V or if the internal thermal shutdown feature activates. FLT transitions to high impedance after 4.2ms in the sustained absence of a fault condition. FLT is valid when  $V_{IN} > 4.5V$  and EN/UV > 1.46V. Float FLT if not used.

**STATUS (Pin 5):** STATUS is an open drain output indicator. The STATUS pin function depends on the state selected by the SEL1-3 pins. Refer to Table 6 for more information. STATUS is de-bounced for 4.2ms and is valid when  $V_{\text{IN}} > 4.5 \text{V}$  and EN/UV > 1.46 V. Float STATUS if not used.

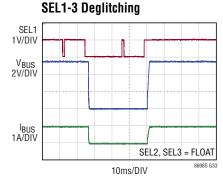

**SEL1, SEL2, SEL3 (Pins 6-8):** SEL1-3 are tristate input pins used to select the desired USB functionality of the LT8698S. Refer to Table 6 in the Applications Information section for detailed information. Tie below 0.58V for logic low, above 1.41V for logic high and float for tristate. Keep leakage currents under 1μA for robust tristate detection. The SEL1-3 pins are de-bounced for 1.5ms for robust transitions between USB states.

**RT (Pin 9):** RT is the switching frequency programming pin. Tie a resistor from RT to ground to select the switching frequency. See the Applications Information section for additional information.

**SYNC/MODE (Pin 10):** SYNC/MODE is the clock synchronization and mode selection input pin. Ground SYNC/MODE for pulse-skipping mode. Tie to a clock source for synchronization to an external frequency and forced continuous mode. Float for forced continuous mode with RT programing the switching frequency. Tie to INTV $_{\rm CC}$  for forced continuous mode with spread-spectrum modulation of the switching frequency for improved EMI/EMC performance.

**LD**<sup>+</sup> (**Pin 12**): LD<sup>+</sup> is the low voltage host side of the internal USB D<sup>+</sup> dataline switch. Float this pin if not used.

**LD**<sup>-</sup> (**Pin 13**): LD<sup>-</sup> is the low voltage host side of the internal USB D<sup>-</sup> dataline switch. Float this pin if not used.

**HD**<sup>-</sup> (**Pin 15**): HD<sup>-</sup> is the high voltage USB cable and device side of the internal USB D<sup>-</sup> dataline switch. Both dataline switches are disconnected if HD<sup>-</sup> > 4.5V. Float this pin if not used.

**HD**<sup>+</sup> (**Pin 16**): HD<sup>+</sup> is the high voltage USB cable and device side of the internal USB D<sup>+</sup> dataline switch. Both dataline switches are disconnected if HD<sup>+</sup> > 4.5V. Float this pin if not used.

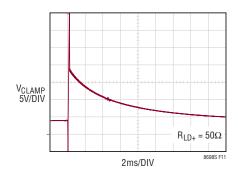

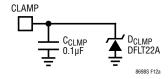

**CLAMP (Pin 18):** Bypass CLAMP with a  $0.1\mu F$  20V or greater low ESR capacitor to ground.

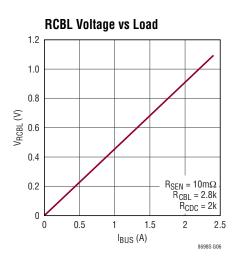

**RCBL** (**Pin 19**): RCBL is the cable drop compensation programming pin. A resistor R<sub>CBL</sub> tied from RCBL to ground programs the cable drop compensation by setting the USB5V input current. RCBL can source 2mA. Excessive capacitive loading on RCBL can degrade load transient response. Isolate load capacitance on this pin by tying a 100k resistor between RCBL and the capacitive load. The RCBL load monitor output is valid when the LT8698S is enabled; otherwise the output is low. See the Applications Information section for additional information.

## PIN FUNCTIONS

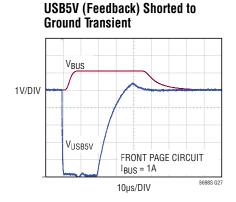

**USB5V** (**Pin 20**): USB5V is the 5V regulator feedback pin. For cable drop compensation, the USB5V pin input current is proportional to the sensed output current. Tie  $R_{CDC}$  from USB5V to the BUS/ISN output for 5V regulation plus cable drop compensation. Tie  $C_{CDC}$  from USB5V to BUS/ISN to limit the cable drop compensation loop bandwidth. Short USB5V to VBUS if no cable drop compensation is desired.

**BUS/ISN (Pin 21):** BUS/ISN is the USB VBUS output and negative current sense input pin. BUS/ISN provides an additional input to the error amplifier to ensure the maximum output regulation voltage does not exceed 6.05V. In addition, BUS/ISN provides the negative input to the internal current sense amplifier. BUS/ISN must be tied to the R<sub>SEN</sub> sense resistor for cable drop compensation and output current limit. Kelvin connect the BUS/ISN pin to the sense resistor to separate regulator output current from the BUS/ISN PCB trace. See the Applications Information section for additional operation and PCB layout information.

**OUT/ISP (Pin 22):** OUT/ISP is the switching regulator output. OUT/ISP must be tied to the inductor terminal opposite the SW and must be bypassed by the output capacitor. Also, the OUT/ISP pin is the noninverting input to the current sense amplifier and must be tied to the R<sub>SEN</sub> sense resistor for cable drop compensation and output current limit. Kelvin connect the OUT/ISP pin to the sense resistor to separate regulator output current from the OUT/ISP trace. See the Applications Information section for additional information.

**SW** (Pins 24, 25): SW is the output node of the internal top and bottom side power switches. Connect to the

switching regulator inductor. This node should be kept small on the PCB for good performance.

**BST (Pin 26):** BST provides a drive voltage, higher than the input voltage, to the top side power switch. Leave BST floating.

**PGND** (**Pins 27, 32**): The PGND pins are the return path of the internal bottom side power switch and must be tied together. Place negative terminal of the input capacitors as close as possible to the PGND pins. See Applications Information section for a sample layout. All GND and PGND pins are internally shorted together.

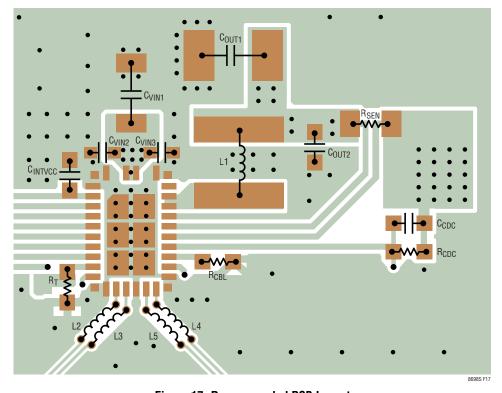

$V_{IN}$  (Pins 29, 30): The  $V_{IN}$  pins are the input path of the internal top side power switch and must be tied together. The LT8698S requires a minimum of 2μF local input bypass capacitance to PGND. A single 2.2μF capacitor may be placed between  $V_{IN}$  and PGND. Best practice for low EMI/EMC is to tie two additional 0.1μF input bypass capacitors to  $V_{IN}$ . One 0.1μF capacitor should be placed between  $V_{IN}$  and pin 27 PGND. A second 0.1μF capacitor of equal value should be placed between  $V_{IN}$  and pin 32 PGND. These capacitors should be placed as close as possible to the LT8698S. See Application Information section for a sample layout.

**Exposed Pads (Pins 33–38):** The exposed pads must be connected to ground. Keep the top layer PCB connection to these pins large to lower the thermal resistance from the LT8698S package to ambient. See the Applications Information section for detailed recommendations.

**Corner Support Pads (Pins 39–42):** The four pads at each corner of the package are support pads intended to improve board level mechanical reliability. These pads are tied to ground internally to the LT8698S. The pads must be tied to PCB ground.

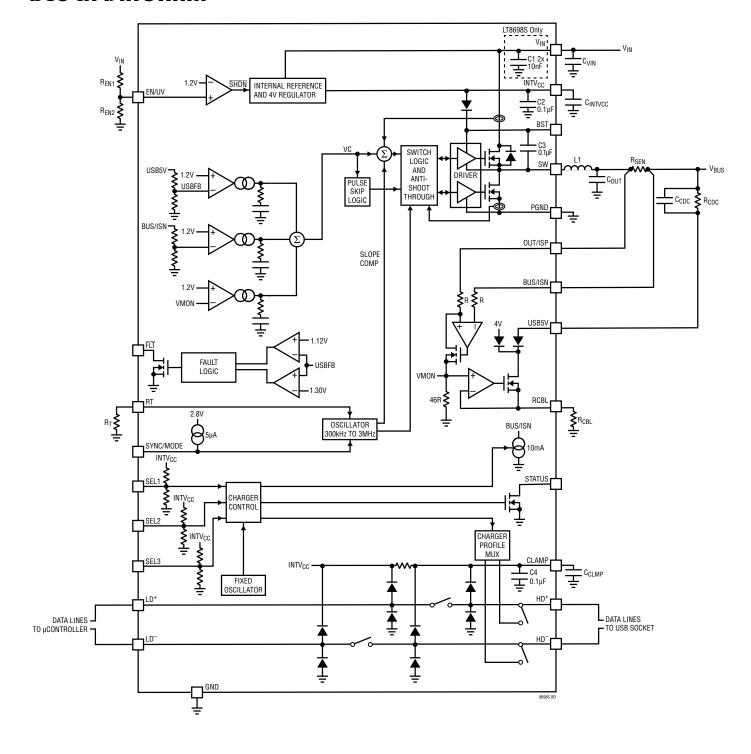

# **BLOCK DIAGRAM**

## **OPERATION**

The LT8698S is a highly efficient synchronous, monolithic USB charger with cable drop compensation and robust USB dataline protection. As such, the LT8698S includes a switching regulator optimized for powering the 5V USB  $V_{BUS}$  rail and two analog switches that tie to the high speed USB 2.0 datalines to provide fault and ESD protection to the upstream USB host IC. Finally, the LT8698S includes many USB charger profiles to allow high current charging of portable devices.

The LT8698S regulator is a monolithic, constant frequency, peak current mode step-down DC/DC converter. An oscillator, with frequency set using a resistor on the RT pin, turns on the internal top power switch at the beginning of each clock cycle. Current in the inductor then increases until the top switch current comparator trips and turns off the top power switch. The peak inductor current at which the top switch turns off is controlled by the voltage on the  $V_C$  node. The error amplifier compares the output voltage on the USB5V pin through an internal resistor divider to an internal reference and servos the  $V_{C}$  node to regulate the USB5V pin to 5V. When the load current increases it causes a reduction in the feedback voltage relative to the reference leading the error amplifier to raise the V<sub>C</sub> voltage until average inductor current matches the new load current. When the top power switch turns off, the synchronous bottom power switch turns on until the next clock cycle begins or inductor current falls to zero when not in forced continuous mode. If overload conditions result in a current higher than the bottom switch current limit flowing in the bottom switch, the next clock cycle will be delayed until switcher current returns to a safe level. In addition, during a fault condition in which USB5V is shorted to ground, the BUS/ISN voltage is regulated to 6.05V to limit the output voltage to a safe level for connected devices. Finally, during an output fault condition, the LT8698S provides an accurate, average output current limit using an external sense resistor connected across the OUT/ISP and BUS/ISN pins.

The LT8698S includes cable drop compensation to provide 5V regulation of the  $V_{BUS}$  rail at the end of a long, resistive cable even with high load current. To implement cable drop compensation, the LT8698S drives the RCBL pin to 46 • ( $V_{OUT/ISP}$  -  $V_{BUS/ISN}$ ). Current sourced from the RCBL pin through the  $R_{CBL}$  resistor is derived from the USB5V pin, creating an output offset across the  $R_{CDC}$  resistor above the 5V USB5V pin voltage that is proportional to the  $R_{CDC}/R_{CBL}$  resistor ratio.

The "S" in the LT8698S part name refers to the second generation Silent Switcher Technology. This technology allows fast switching edges for high switching regulator efficiency at high switching frequency, while simultaneously achieving good EMI performance. This technology includes the integration of ceramic capacitors into the package for the  $V_{IN}$ ,  $INTV_{CC}$  and BST (C1 to C4 in the Block Diagram). These capacitors keep all of the AC current loops small which improves EMI performance. The LT8698S-1 does not include integrated ceramic capacitors tied to  $V_{IN}$ .

An EN/UV pin voltage above 1.46V enables the switching regulator, dataline switches and associated circuitry. An EN/UV pin voltage below 1.31V stops switching and opens the dataline switches. EN/UV pin voltage below 0.25V reduces  $V_{IN}$  current to <1 $\mu$ A.

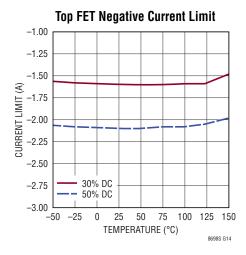

The LT8698S operates primarily in forced continuous mode (FCM) for fast transient response and full frequency operation over a wide load range. To improve regulator efficiency at light load, the LT8698S can operate in pulseskip mode (PSK). PSK reduces the switching frequency at light load current and reduces V<sub>IN</sub> quiescent current between pulses. Ground the SYNC/MODE pin for PSK operation, float it for FCM operation or apply a DC voltage higher than 3.2V to use FCM with spread spectrum modulation (SSM). If a clock is applied to the SYNC/MODE pin, the internal oscillator will synchronize to the external clock frequency and operate in FCM. While in FCM the oscillator operates continuously and rising SW transitions are aligned to the clock. During light loads, the inductor current is allowed to go negative to maintain the programmed switching frequency. The LT8698S can sink current from the output, improving the load step response. Minimum current limits for both power switches are enforced to prevent large negative inductor current from flowing back into the input. SSM dithers the switching frequency from the programmed value set by the RT pin up to 20% higher than the programmed value to spread out the switching energy in the frequency domain.

Comparators monitoring the USB5V pin voltage will pull the  $\overline{\text{FLT}}$  pin low if the output voltage varies more than  $\pm 7\%$  (typical) from the set point, or if a power supply fault condition is present.

## **OPERATION**

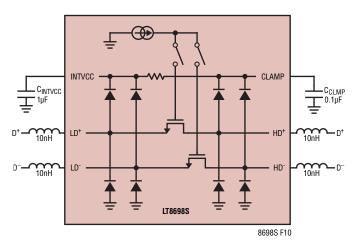

Dataline analog switches allow connection and disconnection between the HD<sup>+</sup> pin and the LD<sup>+</sup> pin and between the HD<sup>-</sup> pin and the LD<sup>-</sup> pin. When connected, the switches provide low resistance over the full 0V to 3.6V common mode range and can block 0V to 20V on the HD<sup>+</sup>/<sup>-</sup> side and 6V on the LD<sup>+</sup>/<sup>-</sup> side. High speed circuitry disconnects the switches in the event of a fault or ESD on the HD<sup>+</sup>/<sup>-</sup> side.

The LT8698S includes many charger profiles including USB BC 1.2 CDP, DCP, and SDP as well as common proprietary profiles. Each profile ties various components to the datalines. This could be resistive dividers, a short between the datalines, or voltage sources and current sources. These profiles might be passive or could react

to the device plugged into the USB socket in some active manner. The profile allows the device plugged into the USB socket to identify a high current charger and draw more current from  $V_{BUS}$  than the 0.5A that would usually be allowed from a standard USB 2.0 socket.

SEL1-3 pins are tristate inputs that allow the host  $\mu$ Controller to control the behavior of the LT8698S. Internal resistive dividers bias these pins to 1V when a high Z input is applied. The SEL1-3 pins are de-bounced for 1.5ms prior to allowing a state change to the LT8698S.

The STATUS pin is an open drain output whose function is determined by the state selected by the SEL1-3 pins. This pin can output high or low or oscillate with a 9ms period.

## APPLICATIONS INFORMATION

#### **Cable Drop Compensation**

The LT8698S includes the necessary circuitry to implement cable drop compensation. Cable drop compensation allows the regulator to maintain 5V regulation on the USB  $V_{BUS}$  rail despite high cable resistance. The LT8698S increases its local output voltage ( $V_{BUS/ISN}$ ) above 5V as the load increases to keep  $V_{BUS}$  regulated to 5V. This compensation does not require running an additional pair of Kelvin sense wires from the regulator to the load, but does require the system designer to know the cable resistance  $R_{CABLE}$  as the LT8698S does not sense this value.

Program the cable drop compensation using the ratio of Equation 1.

$$R_{CBL} = 46 \bullet \left( \frac{R_{SEN} \bullet R_{CDC}}{R_{CABLE}} \right)$$

(1)

where  $R_{CDC}$  is a resistor tied between the regulator output and the USB5V pin,  $R_{CBL}$  is a resistor tied between the RCBL pin and GND,  $R_{SEN}$  is the sense resistor tied between the OUT/ISP and BUS/ISN pins in series between the regulator output and the load, and  $R_{CABLE}$  is the cable resistance.  $R_{SEN}$  must be  $10m\Omega$  for 2.4A applications and  $8m\Omega$  for 3A applications for the LT8698S to function properly.

The current flowing into the USB5V pin through  $R_{CDC}$  is identical to the current flowing through  $R_{CBL}$ . While the ratio of these two resistors should be chosen per the equation above, choose the absolute values of these resistors to keep this current between  $30\mu A$  and  $1200\mu A$  at full load current. This restriction results in  $R_{CBL}$  and  $R_{CDC}$  values between 1k and 40.2k. If  $I_{USB5V}$  is too low, capacitive loading on the  $R_{CBL}$  pin will degrade the load step transient performance of the regulator. If  $I_{USB5V}$  is too high, the  $R_{CBL}$  pin will go into current limit and the cable drop compensation feature will not work.

Capacitance across the remote load to ground downstream of  $R_{SEN}$  forms a left half plane zero in the LT8698S device's feedback loop due to cable drop compensation.  $C_{BUS}$  and the input capacitance of a portable device tied to the USB socket typically form this zero.  $C_{CDC}$  reduces the cable drop compensation gain at high frequency. The 4.7nF  $C_{CDC}$  capacitor tied across the 2k  $R_{CDC}$  is required for stability of the LT8698S's output. If  $R_{CDC}$  is changed,  $C_{CDC}$  should also be changed to maintain roughly the same 10µs RC time constant. If the capacitance across the remote load is large compared to the LT8698S output capacitors  $C_{OUT}$  and  $C_{BUS}$ , a longer  $R_{CDC}$  •  $C_{CDC}$  time constant may be necessary for stability depending on the amount of cable drop compensation used. Output stability should always be verified in the end application circuit.

Short USB5V to the VBUS output if no cable drop compensation is desired.

The LT8698S limits the maximum voltage of  $V_{BUS}$  by limiting the voltage on the BUS/ISN pin to 6.05V. If the cable drop compensation is programmed to compensate for more than 1.05V of cable drop at the maximum  $I_{BUS}$ , this limit will prevent  $V_{BUS/ISN}$  from rising higher and the voltage at the point of load  $V_{BUS}$  will drop below 5V. Equation 2 shows how to derive the LT8698S output voltage.

$$V_{OUT} = 5V + \frac{46 \cdot I_{BUS} \cdot R_{SEN} \cdot R_{CDC}}{R_{CBL}}$$

(2)

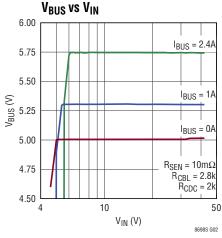

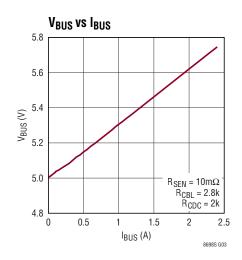

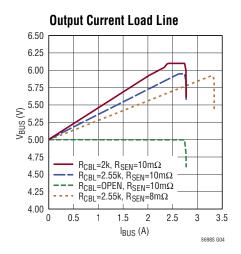

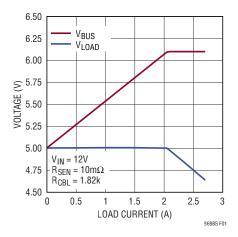

Refer to Figure 1 for load lines of  $V_{BUS/ISN}$  and  $V_{BUS}$  to see how cable drop compensation works.

Figure 1. Example Cable Drop Compensation Load Line

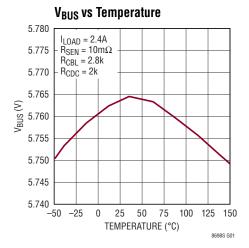

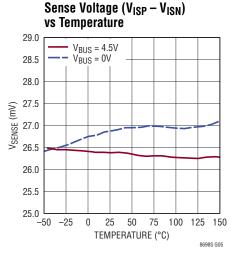

# Cable Drop Compensation Over a Wide Temperature Range

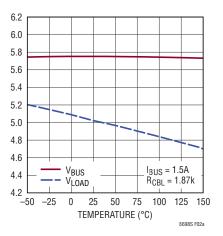

Cable drop compensation with zero temperature variation may be used in many applications (see Figure 2a,b,c). However, matching the cable drop compensation temperature variation to the cable resistance temperature variation may result in better overall output voltage accuracy over a wide operating temperature range. For example, in an application with  $0.49\Omega$  of wire resistance and a maximum output current of 1.5A, cable drop compensation adds 0.735V at  $25^{\circ}C$  to the output at max load for a fully compensated wire resistance. If the wire in this example is copper, the copper resistance temperature coefficient

(a) Cable Drop Compensation Through 3m of AWG 24 Twisted-Pair Cable (490m $\Omega$ ) without Temperature Compensation

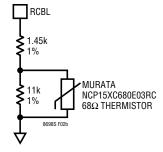

(b) R<sub>CBL</sub> Resistor Network for Matching Copper Wire Temperature Coefficient

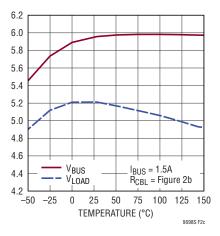

(c) Cable Drop Compensation Through 3m of AWG 24 Twisted-Pair Cable (490 $\Omega$ ) with Temperature Compensation Using NTC R<sub>CBL</sub>

Figure 2. Cable Drop Compensation Applications

of about 4000ppm/°C results in an output voltage error of 294mV at 125°C and 191mV at -40°C. Figure 2a shows this behavior.

See Table 1 for a list of copper wire resistances vs gauge.

Table 1. Copper Wire Resistance vs Wire Gauge

| AWG | RESISTANCE OF CU WIRE AT 20°C (mΩ/m) |

|-----|--------------------------------------|

| 15  | 10.4                                 |

| 16  | 13.2                                 |

| 17  | 16.6                                 |

| 18  | 21.0                                 |

| 19  | 26.4                                 |

| 20  | 33.3                                 |

| 21  | 42.0                                 |

| 22  | 53.0                                 |

| 23  | 66.8                                 |

| 24  | 84.2                                 |

| 25  | 106                                  |

| 26  | 134                                  |

| 27  | 169                                  |

| 28  | 213                                  |

| 29  | 268                                  |

| 30  | 339                                  |

| 31  | 427                                  |

| 32  | 538                                  |

| 33  | 679                                  |

| 34  | 856                                  |

| 35  | 1080                                 |

| 36  | 1360                                 |

| 37  | 1720                                 |

| 38  | 2160                                 |

| 39  | 2730                                 |

| 40  | 3440                                 |

Cable drop compensation can be made to vary positively versus temperature with the addition of a negative temperature coefficient (NTC) resistor as a part of the  $R_{CBL}$  resistance. This circuit idea assumes the NTC resistor is at the same temperature as the cable. Figure 2b shows an example resistor network for  $R_{CBL}$  that matches copper resistance variation over a wide  $-40\,^{\circ}\text{C}$  to 150°C temperature range. Figure 2c shows the resultant cable drop compensation output at several temperatures using  $R_{CBL}$  with negative temperature variation.

The NTC resistor does not give a perfectly linear transfer function versus temperature. Here, for typical component values, the worst case error is <20% of the cable compensation output, or <4% of the total output voltage accuracy. Better output voltage accuracy versus temperature can be achieved if  $R_{CBL}$  resistor values are optimized for a narrower temperature range.

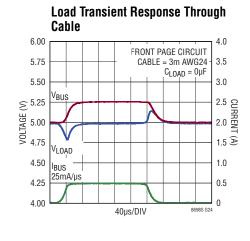

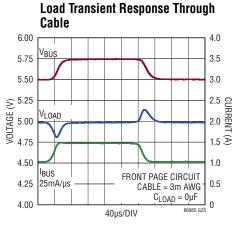

# Effect of Cable Inductance on Load Step Transient Response

The inductance of long cabling limits the peak-to-peak transient performance of a 2-wire sense regulator to fast load steps (see Figure 3). Since a 2-wire sense regulator like the LT8698S detects the output voltage at its local output and not at the point of load, the load step response degradation due to cable inductance is present even with cable resistance compensation. The local regulator output capacitor and the input capacitor of the remote load form a LC tank circuit through the inductive cabling between them. Fast load steps through long cabling show a large peak-to-peak transient response and ringing at the resonant frequency of the circuit. This ringing is a property of the LC tank circuit and does not indicate regulator instability.

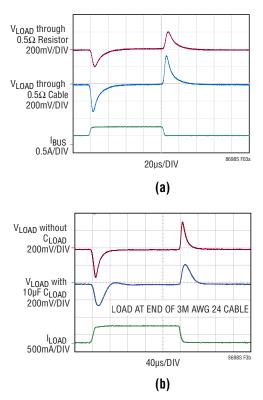

Figure 3a shows the LT8698S load step transient response to a 125mA/µs, 0.5A load step. Two cable impedances are compared: resistive only and then resistive plus inductive. First, a surface mount  $0.5\Omega$  resistor is tied between the LT8698S output and the load step generator. This resistor stands in for a purely resistive "cable". Second, AWG 24 twisted-pair cabling 3 meters long with  $0.5\Omega$  of total resistance and about 0.8µH of inductance is connected between the LT8698S output and the load step generator. Even though the resistance in these two circuits is the same, the transient load step response in the cable is worse due to the inductance. The degree that cable inductance degrades LT8698S load transient response performance depends on the inductance of the cable and on the load step rate. Long cables have higher inductance than short cables. Cables with less separation between supply and return conductor pairs show lower inductance per unit length than those with separated conductors. A faster load step rate exacerbates the effect of inductance on load step response.

Figure 3. Effect of Cable Inductance on Load Step Transient Response

Figure 3b shows the effect of remote capacitance at the load side of the cable on the LT8698S transient response. The load step is a 60mA/ $\mu$ s, 0.5A load step through a 0.5 $\Omega$ , 3 meter long cable. Without remote capacitance  $C_{LOAD}$  at the load step location, there is no LC tank and therefore no observed ringing. In this case, given 100% of the dl/dt of the load step occurs across the cable resistance R and inductance L, the peak to peak  $V_{LOAD}$  deviation is  $\pm 300$ mV. When  $10\mu F$  of remote  $C_{LOAD}$  is added at the load step location, the cable L and load capacitance form a tank circuit leading to modest ringing. In this case, given the effective dl/dt across the cable R and L is reduced, the peak to peak  $V_{LOAD}$  deviation is reduced to less than  $\pm 250$ mV.

#### **Probing a Remote Output Correctly**

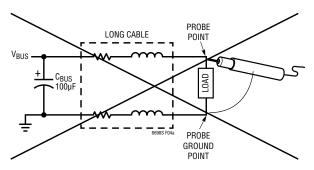

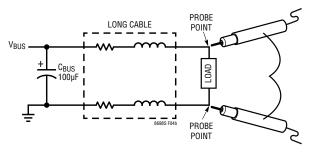

Take care when probing the LT8698S's remote output to obtain correct results. With cable drop compensation the local regulator output has a different voltage than the remote output at the end of a cable due to the cable resistance and high load current. The same is true for the ground return line which also has resistance and carries

the same current as the output. Since the local ground at the LT8698S is separated by a current carrying cable from the remote ground at the point of load, the ground reference points for these two locations are different.

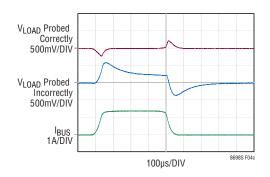

Use a differential probe across the remote output at the end of the cable to measure output voltage at that point, as shown in Figure 4b. Do not simultaneously tie an oscilloscope's probe ground leads to both the local LT8698S ground and the remote point of load ground, as shown in Figure 4a. Doing so will result in high current flow in the probe ground lines and a strange and incorrect measurement. Figure 4c shows this strange behavior. A 1.3A load step is applied to the LT8698S output through 3 meters of AWG 24 twisted-pair cable. On one curve, the resultant output voltage is measured correctly using a differential probe tied across the point of load. On the other curve, the oscilloscope ground lead is tied to the remote ground. This poor probing causes both a DC error due to the lower ground return resistance and an AC error showing increased overshoot. Do not add your oscilloscope. lab bench, and input power supply ground lines into your measurement of the LT8698S remote output.

#### **Reducing Output Overshoot**

A consequence of the use of cable drop compensation is that the local output voltage at the LT8698S BUS/ISN pin is regulated to a voltage that is higher than the remote output voltage at the point of load. Several hundred  $m\Omega$  of line resistance can separate these two outputs, so at 2A of load current,  $V_{BUS/ISN}$  may be up to 1.05V higher than the nominal 5V output at the point of load. Ensure that any components tied to the LT8698S output can withstand this increased voltage.

The LT8698S has several features designed to mitigate any effects of higher output voltage due to cable drop compensation. First, the LT8698S error amplifier, in addition to regulating the voltage on the USB5V pin to 5V for the primary output, also regulates the BUS/ISN pin voltage to less than 6.05V. This 6.05V upper limit on the maximum BUS/ISB voltage protects components tied to the LT8698S output such as a portable device from an overvoltage condition, but reduces the possible amount of cable drop compensation to 1.05V.

(a) Incorrect Remote Output Probing

(b) Correct Remote Output Probing

(c) Effect of Probing Remote Output Incorrectly

Figure 4. Probing a Remote Output Correctly

Additionally, the LT8698S can sink current from the output when in forced continuous mode (FCM). This feature improves the step response for a load step from high to low. Cable drop compensation adds voltage to the output to compensate for voltage drop across the cable resistance at high load. Since most DC/DC convertors can only source current, a load step from high to near zero current leaves the output voltage high and out of regulation. The LT8698S fixes this problem by allowing the regulator to

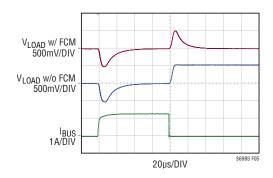

sink current from the output when USB5V is too high using FCM. Figure 5 shows the output voltage of the front page application circuit with both FCM and PSK modes in response to a fast, 1.3A load step through a 3m cable. The load step response from high current to zero in PSK mode is extremely slow and is limited by the OUT/ISP, BUS/ISN and USB5V pin bias currents. However, with FCM enabled, the output slews quickly back into regulation.

Figure 5. Load Step Response with and without Forced Continuous Mode

Lastly, the LT8698S positive switch peak current and negative valley current limits exceed the positive output current limit of 2.65A. This large current range allows the LT8698S to slew the output capacitor quickly for cable drop compensation during a transient load step.

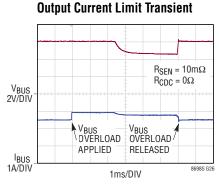

#### **Output Current Limit**

In addition to regulating the output voltage, the LT8698S limits the average output current with a current regulation loop. Output current regulation limits power dissipation in the case of a fault on the USB cable or of the device plugged into the socket. The LT8698S measures the voltage drop across the external sense resistor  $R_{SEN}$  using the OUT/ISP and BUS/ISN pins. This resistor should be connected on the load side of the output capacitor  $C_{OUT}$ , in series with the load. The LT8698S control loop modulates the cycle-by-cycle switch current limit such that the average voltage across the OUT/ISP to BUS/ISN pins does not exceed its regulation point. When load current exceeds the output current limit and current regulation is active, the output voltage will drop below its regulation point.

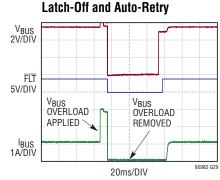

The LT8698S also includes latch-off and auto-retry functionality in the output current regulation loop. If the output

voltage is 7% below is regulation point for at least 4.2ms, the LT8698S will stop switching for 59ms. After 59ms, the LT8698S will start switching. If the output can return to its nominal regulation point within 4.2ms after starting to switch, then normal operation will resume. Otherwise, if the output still remains more than 7% below its regulation point, the LT8698S will again stop switching for 59ms and this sequence will repeat. This latch-off and auto-retry feature reduces the power dissipation in a fault condition to about an 7% duty cycle of what it otherwise would have been.

#### Using RCBL as an Output Current Monitor

The primary function of the RCBL pin is to set the cable drop compensation as discussed in the Cable Drop Compensation section. The secondary function of the RCBL pin is to produce an output voltage that is proportional to the output load current. The RCBL pin can therefore be used as an output load monitor. The voltage on the RCBL pin obeys Equation 3 relation to USB load current.

$$V_{BCRI} = I_{I OAD} \bullet R_{SFN} \bullet 46 \tag{3}$$

This formula is valid when the LT8698S is enabled.

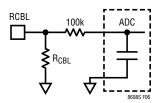

Since the RCBL pin current is part of the cable drop compensation control loop, excessive capacitive loading on the RCBL pin can cause USB output voltage overshoot during load steps. Keep the capacitive loading on the RCBL pin below 100pF or isolate the load capacitance with 100k $\Omega$  in series between the RCBL pin and the input it is driving as shown in Figure 6.

Figure 6. Using the RCBL Pin as Output Current Monitor

#### **Setting the Switching Frequency**

The LT8698S uses a constant frequency PWM architecture that can be programmed to switch from 300kHz to 3MHz by using a resistor tied from the RT pin to ground.

Table 2 shows the ideal R<sub>T</sub> value for a desired switching frequency.

Table 2. Switching Frequency vs R<sub>T</sub> Value

| Switching Frequency (MHz) | $R_T$ (k $\Omega$ ) |

|---------------------------|---------------------|

| 3                         | 5.76                |

| 2.8                       | 6.19                |

| 2.6                       | 6.81                |

| 2.4                       | 7.5                 |

| 2.2                       | 8.25                |

| 2                         | 9.09                |

| 1.8                       | 10.2                |

| 1.6                       | 11.5                |

| 1.5                       | 12.4                |

| 1.4                       | 13.3                |

| 1.3                       | 14.7                |

| 1.2                       | 15.8                |

| 1.1                       | 17.4                |

| 1                         | 19.1                |

| 0.9                       | 21.5                |

| 0.8                       | 24.3                |

| 0.7                       | 28                  |

| 0.6                       | 32.4                |

| 0.5                       | 39.2                |

| 0.4                       | 49.9                |

| 0.3                       | 66.5                |

R<sub>T</sub> can also be found for the desired switching frequency using Equation 4 where f is in MHz.

$$R_{T} = \frac{20.25}{f} - 1.013k \tag{4}$$

#### **Operating Frequency Selection and Trade-Offs**

Selection of the operating frequency is a trade-off between efficiency, component size and input voltage range. The advantage of high frequency operation is that smaller inductor and capacitor values may be used. The disadvantages are lower efficiency and a smaller input voltage range.

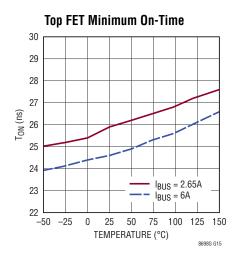

The highest switching frequency  $(f_{SW(MAX)})$  for a given application before min on-time limited can be calculated using Equation 5.

$$f_{SW(MAX)} = \frac{V_{OUT/ISP}}{t_{ON(MIN)} \cdot V_{IN(MAX)}} \cdot 1000$$

(5)

where  $V_{IN(MAX)}$  is the maximum input voltage without skipped cycles,  $V_{OUT/ISP}$  is the output voltage at OUT/ISP, and  $t_{ON(MIN)}$  is the minimum top switch on-time of about 30ns. This equation shows that a slower switching frequency is necessary to accommodate a high  $V_{IN}/V_{OUT/ISP}$  ratio.

For transient operation,  $V_{\text{IN}}$  may go as high as the absolute maximum rating of 42V regardless of the  $R_T$  value; however the LT8698S will reduce switching frequency as necessary to maintain control of inductor current to assure safe operation.

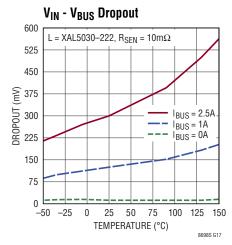

The LT8698S is capable of a maximum duty cycle of greater than 99%, and the  $V_{IN}$  to  $V_{BUS/ISN}$  dropout is limited by the  $R_{DS(ON)}$  of the top switch. Operating in this region results in lower switching frequency.

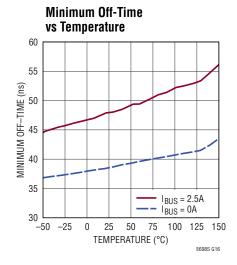

The highest switching frequency (f<sub>SW(MAX)</sub>) for a given application before min off-time limited can be calculated using Equation 6.

$$f_{SW(MAX)} = \left(\frac{1}{t_{OFF(MIN)}} - \frac{V_{OUT/ISP}}{t_{OFF(MIN)} \cdot V_{IN(MIN)}}\right) \cdot 1000$$

(6)

where  $V_{IN(MIN)}$  is the minimum input voltage without skipped cycles,  $V_{OUT/ISP}$  is the output voltage at OUT/ISP, and  $t_{OFF(MIN)}$  is the minimum switch off-time of 40ns. Note that higher switching frequency will increase the minimum input voltage for full frequency operation.

#### **Inductor Selection and Maximum Output Current**

The LT8698S is designed to minimize solution size by allowing the inductor to be chosen based on the output load requirements of the application. During overload or short-circuit conditions the LT8698S safely tolerates operation with a saturated inductor through the use of a high speed peak-current mode architecture.

Based on the desired switching frequency, pick an inductor for the LT8698S according to Table 3.

Table 3 lists nominal values for inductors. Inductors are typically de-rated versus current, versus temperature and have a tolerance spec. This table assumes the inductance in the application will not be 40% less than the nominal value at worst case operating conditions and tolerance.

For robust operation, use an inductor with value equal to or greater than the value on Table 3.

Table 3. Inductor Value by Switching Frequency

| SWITCHING FREQUENCY (MHz) | MINIMUM NOMINAL INDUCTOR VALUE (µH) |

|---------------------------|-------------------------------------|

| 2.4 - 3.0                 | 1.5                                 |

| 1.9 – 2.4                 | 2.2                                 |

| 1.3 – 1.9                 | 3.3                                 |

| 0.89 – 1.3                | 4.7                                 |

| 0.61 - 0.89               | 6.8                                 |

| 0.51 - 0.61               | 8.2                                 |

| 0.30 - 0.51               | 10                                  |

Table 4 lists inductor vendors and associated inductor product series names that are recommended for use with the LT8698S.

**Table 4. Inductor Manufacturers**

| VENDOR    | SERIES                 | WEBSITE           |

|-----------|------------------------|-------------------|

| TDK       | SLF, VLC, VLF          | www.tdk.com       |

| Sumida    | CRH, CDR, CDMC         | www.sumida.com    |

| Coilcraft | XAL, XFL, MSS          | www.coilcraft.com |

| NIC       | NPIM, NPIS             | www.niccomp.com   |

| Würth     | TPC, SPC, PD, PDF, PD3 | www.we-online.com |

#### **Input Capacitor**

Bypass the input of the LT8698S circuit with a ceramic capacitor with the appropriate temperature and voltage rating, placed as close as possible to the  $V_{IN}$  and PGND pins. Y5V types have poor performance over temperature and applied voltage, and should not be used. A 2.2 $\mu$ F to 4.7 $\mu$ F ceramic capacitor is adequate to bypass the LT8698S and will easily handle the ripple current. Note that larger input capacitance is required when a lower switching frequency is used. If the input power source has high impedance, or there is significant inductance due to long wires or cables, additional bulk capacitance may be necessary. This can be provided with a low performance electrolytic capacitor.

Step-down regulators draw current from the input supply in pulses with very fast rise and fall times. The input capacitor is required to reduce the resulting voltage ripple at the LT8698S and to force this very high frequency switching

current into a tight local loop, minimizing EMI. A second precaution regarding the ceramic input capacitor concerns the maximum input voltage rating of the LT8698S. A ceramic input capacitor combined with trace or cable inductance forms a high quality (under damped) tank circuit. If the LT8698S circuit is plugged into a live supply, the input voltage can ring to twice its nominal value, possibly exceeding the LT8698S's voltage rating. This situation is easily avoided (see ADI Application Note 88).

#### **Output Capacitor and Output Ripple**

The output capacitor  $C_{OUT}$  tied from the OUT/ISP pin to ground has two essential functions. Along with the inductor, it filters the square wave generated by the LT8698S to produce the DC output. In this role it determines the output ripple, thus low impedance at the switching frequency is important. The second function is to store energy in order to satisfy transient loads and stabilize the LT8698S's control loop. Ceramic capacitors have very low equivalent series resistance (ESR) and provide the best ripple performance. For good starting values, see the Typical Applications section.

On a switching regulator with fixed output voltage, transient performance can generally be improved with a higher value output capacitor. However, the LT8698S's cable drop compensation feature changes the local output voltage in response to a load step. Since transient load steps require the LT8698S to slew  $C_{OUT}$ , larger  $C_{OUT}$  in this case can degrade transient response. Only remote capacitance tied at the end of the cable near the USB socket can improve transient response. The minimum local output capacitance required for LT8698S loop stability and for output voltage ripple requirements is the best choice for  $C_{OUT}$ . See the Typical Applications section in this data sheet for suggested capacitor values.

The USB 2.0 specification document requires a minimum of 120µF low-ESR capacitor be tied from  $V_{BUS}$  to ground on a hub. Since the downstream device fixed  $V_{BUS}$  capacitance is limited to a maximum of 10µF, this minimum 120µF  $V_{BUS}$  capacitance prevents hot plugging of one downstream device from glitching the  $V_{BUS}$  and disrupting another connected device. If the LT8698S is powering  $V_{BUS}$  on a hub, then this requirement can be satisfied

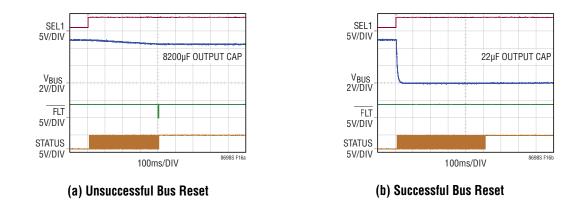

with extra  $C_{OUT}$  tied from either OUT/ISP to ground. There must always be a minimum of  $22\mu F$  capacitance tied from OUT/ISP to ground.