# LTC1477/LTC1478

Single and Dual Protected High Side Switches

## FEATURES

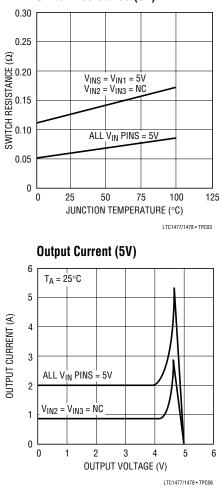

- Extremely Low  $R_{DS(ON)}$  Switch: 0.07 $\Omega$

- No Parasitic Body Diode

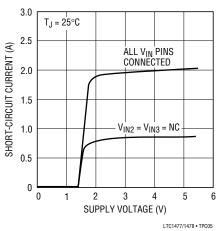

- Built-In Short-Circuit Protection: 2A

- Built-In Thermal Overload Protection

- Operates from 2.7V to 5.5V

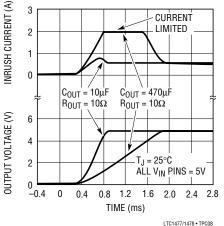

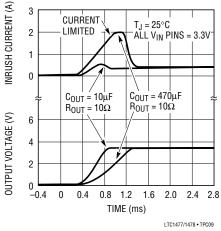

- Inrush Current Limited

- Ultralow Standby Current: 0.01µA

- Built-In Charge Pump

- Controlled Rise and Fall Times: t<sub>R</sub> = 1ms

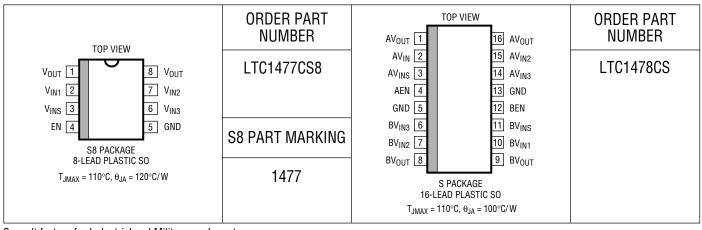

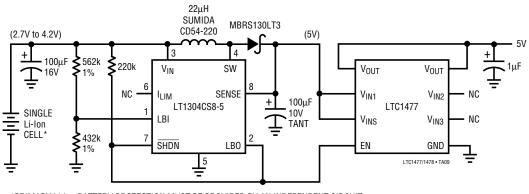

- Single Switch in 8-Pin SO Package

- Dual Switch in Narrow 16-Pin SO Package

## **APPLICATIONS**

Notebook Computer Power Management

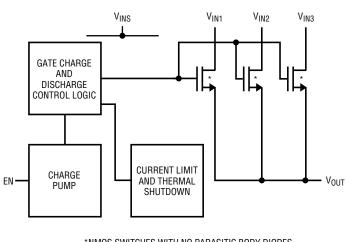

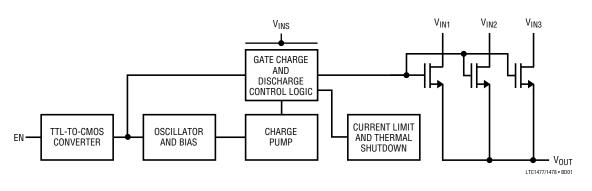

SIMPLIFIED BLOCK DIAGRAM

- Power Supply/Load Protection

- Supply/Battery Switch-Over Circuits

- Circuit Breaker Function

- "Hot Swap" Board Protection

- Peripheral Power Protection

## DESCRIPTION

The LTC<sup>®</sup>1477/LTC1478 protected high side switches provide extremely low  $R_{DS(ON)}$  switching with built-in protection against short-circuit and thermal overload conditions. A built-in charge pump generates gate drive higher than the supply voltage to fully enhance the internal NMOS switch. This switch has no parasitic body diode and therefore no current flows through the switch when it is turned off and the output is forced above the input supply voltage. (DMOS switches have parasitic body diodes that become forward biased under these conditions.)

Two levels of protection are provided by the LTC1477/LTC1478. The first level of protection is shortcircuit current limit which is set at 2A. The short-circuit current can be reduced to as low as 0.85A by disconnecting portions of the power device (see Applications Information). The second level of protection is provided by thermal overload protection which limits the die temperature to approximately 130°C.

The LTC1477 single is available in 8-lead SO packaging. The LTC1478 dual is available in 16-lead SO packaging.

T, LTC and LT are registered trademarks of Linear Technology Corporation.

<sup>\*</sup>NMOS SWITCHES WITH NO PARASITIC BODY DIODES

LTC1477/1478 • TAO

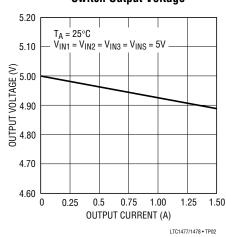

#### Switch Output Voltage

# ABSOLUTE MAXIMUM RATINGS

| Supply Voltage                               | 7V       |

|----------------------------------------------|----------|

| Enable Input Voltage (7V) to (GND            | -0.3V)   |

| Output Voltage (OFF) (Note 1) (7V) to (GND - | -0.3V)   |

| Output Short-Circuit Duration Inc            | definite |

| Junction Temperature                         | 110°C    |

| LTC1477C/LTC1478C                     | 0°C to 70°C    |

|---------------------------------------|----------------|

| Storage Temperature Range             | –65°C to 150°C |

| Lead Temperature (Soldering, 10 sec). | 300°C          |

## PACKAGE/ORDER INFORMATION

Consult factory for Industrial and Military grade parts.

# **ELECTRICAL CHARACTERISTICS**

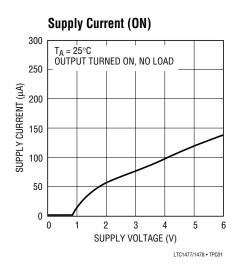

$V_{INS} = V_{IN1} = V_{IN2} = V_{IN3} = 5V$  (Note 2),  $T_A = 25^{\circ}C$ , unless otherwise noted. Each channel of the LTC1478 is tested separately (Note 3).

| SYMBOL           | PARAMETER                   | CONDITIONS                                                                |   | MIN  | ТҮР  | MAX  | UNITS |

|------------------|-----------------------------|---------------------------------------------------------------------------|---|------|------|------|-------|

| VIN              | Supply Voltage Range        |                                                                           |   | 2.7  |      | 5.5  | V     |

| IVIN             | Supply Current              | Switch OFF, Enable = 0V                                                   | • |      | 0.01 | 10   | μA    |

|                  |                             | Switch ON, Enable = 5V, $V_{IN}$ = 5V                                     |   |      | 120  | 180  | μA    |

|                  |                             | Switch ON, Enable = $3.3V$ , $V_{IN} = 3.3V$                              | • |      | 80   | 120  | μA    |

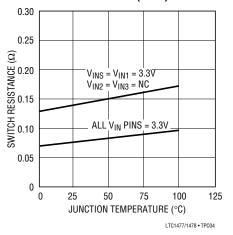

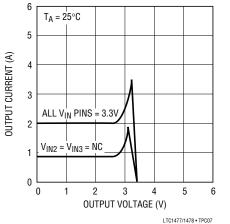

| R <sub>ON</sub>  | ON Resistance               | $V_{INS} = V_{IN1} = V_{IN2} = V_{IN3} = 5V$ , $I_{OUT} = 1A$             |   |      | 0.07 | 0.12 | Ω     |

|                  |                             | $V_{INS} = V_{IN1} = V_{IN2} = V_{IN3} = 3.3V$ , $I_{OUT} = 1A$           |   |      | 0.08 | 0.12 | Ω     |

|                  |                             | $V_{INS} = V_{IN1} = 5V, V_{IN2} = V_{IN3} = NC, I_{OUT} = 0.5A$          |   |      | 0.12 | 0.20 | Ω     |

|                  |                             | $V_{INS} = V_{IN1} = 3.3V$ , $V_{IN2} = V_{IN3} = NC$ , $I_{OUT} = 0.5A$  |   |      | 0.13 | 0.20 | Ω     |

| I <sub>LKG</sub> | Output Leakage Current OFF  | Switch OFF, Enable = 0V                                                   | • |      |      | ±20  | μA    |

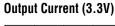

| I <sub>SC</sub>  | Short-Circuit Current Limit | $V_{INS} = V_{IN1} = V_{IN2} = V_{IN3} = 5V, V_{OUT} = 0V, (Note 4)$      |   | 1.60 | 2.00 | 2.40 | Α     |

|                  |                             | $V_{INS} = V_{IN1} = 5V, V_{IN2} = V_{IN3} = NC, V_{OUT} = 0V$ , (Note 4) |   | 0.68 | 0.85 | 1.02 | Α     |

| V <sub>ENH</sub> | Enable Input High Voltage   | $3.0V \le V_{INS} \le 5.5V$                                               | • | 2.0  |      |      | V     |

| V <sub>ENL</sub> | Enable Input Low Voltage    | $3.0V \le V_{INS} \le 5.5V$                                               | • |      |      | 0.8  | V     |

| I <sub>EN</sub>  | Enable Input Current        | $0V \le V_{EN} \le 5.5V$                                                  | • |      |      | ±1   | μA    |

| t <sub>D+R</sub> | Delay and Rise Time         | $R_{OUT} = 100\Omega$ , $C_{OUT} = 1\mu$ F, to 90% of Final Value         |   | 0.50 | 1.00 | 2.00 | ms    |

The  $\bullet$  denotes specifications which apply over the full operating temperature range.

**Note 1:** The V<sub>OUT</sub> pins must be connected together.

**Note 2:** The V<sub>INS</sub> and V<sub>IN1</sub> pins must be connected together. The V<sub>IN2</sub> and V<sub>IN3</sub> pins are typically connected to V<sub>INS</sub> and V<sub>IN1</sub> pins but can be selectively disconnected to reduce the short-circuit current limit and

increase the ON resistance of the switch. The LTC1478 GND pins must be connected together. (See Pin Functions and Block Diagram for more detail.)

Note 3: Other channel turned OFF, i.e. AEN and BEN = 0V.

**Note 4:** The output is protected with fold-back current limit which reduces the short-circuit (0V) currents below peak permissible current levels at higher output voltages. (See Typical Performance Characteristics for further detail on output current versus output voltage).

### **TYPICAL PERFORMANCE CHARACTERISTICS**

#### Switch Resistance (3.3V)

#### **Short-Circuit Current**

#### Inrush Current (5V) CURRENT LIMITED

3

2

Switch Resistance (5V)

Inrush Current (3.3V)

## PIN FUNCTIONS

### LTC1477

**EN (Pin 4):** The enable input is a high impedance CMOS gate with an ESD protection diode to ground and should not be forced below ground. This input has about 100mV of built-in hysteresis to ensure clean switching.

$V_{INS}$ ,  $V_{IN1}$  (Pins 3,2): The  $V_{INS}$  supply pin must always be connected to the  $V_{IN1}$  supply pin (see Block Diagram). The  $V_{INS}$  supply pin provides power for the input control logic, the current limit and thermal shutdown circuitry; plus provides a sense connection to the input power supply. The gate of the NMOS switch is powered by a charge pump from the  $V_{INS}$  supply pin (see Block Diagram). The  $V_{IN1}$ supply pin provides connection to the drain of 1/2 of the output power device.

**V**<sub>IN2</sub>, **V**<sub>IN3</sub> (**Pins 7,6**): The V<sub>IN2</sub> and V<sub>IN3</sub> supply pins are typically tied to the V<sub>INS</sub> and V<sub>IN1</sub> supply pins for lowest ON resistance; i.e., when all four V<sub>IN</sub> pins are connected together the entire power device is connected (see Block Diagram). Each auxiliary supply pin, V<sub>IN2</sub> and V<sub>IN3</sub>, is connected to the drain of 1/4 of the power device. The V<sub>IN2</sub> and V<sub>IN3</sub> pins can be selectively disconnected to reduce the short-circuit current limit at the expense of higher R<sub>DS(ON)</sub>. (See Applications Information section for more details.)

$V_{OUT}$  (Pins 1,8): The output pins of the LTC1477 must always be tied together. The output is protected against accidental short circuits to ground by a current limit circuit which protects the system power supply and load against damage. A second level of protection is provided by thermal shutdown circuitry which limits the die temperature to 130°C.

### LTC1478

**AEN, BEN (Pins 4,12):** The enable inputs are high impedance CMOS gates with ESD protection diodes to ground and should not be forced below ground. These inputs have about 100mV of built-in hysteresis to ensure clean switching.

$AV_{INS}$ ,  $AV_{IN1}$ ,  $BV_{INS}$ ,  $BV_{IN1}$  (Pins 3,2; 11,10): The  $AV_{INS}$ or  $BV_{INS}$  supply pin must always be connected to the  $AV_{IN1}$  or  $BV_{IN1}$  supply pin (see Block Diagram). The  $AV_{INS}$ and  $BV_{INS}$  supply pins provide power for the input control logic, the current limit and thermal shutdown circuitry; plus, provides a sense connection to the input power supply. The gate of the NMOS switch is powered by a charge pump from the  $AV_{INS}$  and  $BV_{INS}$  supply pins (see Block Diagram). The  $AV_{IN1}$  and  $BV_{IN1}$  supply pins provide connection to the drain of 1/2 of the output power device.

$AV_{IN2}$ ,  $AV_{IN3}$ ,  $BV_{IN2}$ ,  $BV_{IN3}$ , (Pins 15,14; 7,6): The  $AV_{IN2}$ ,  $AV_{IN3}$ ,  $BV_{IN2}$  and  $BV_{IN3}$  supply pins are typically tied to the  $AV_{INS}$ ,  $AV_{IN1}$ ,  $BV_{IN3}$  and  $BV_{IN1}$  supply pins for lowest ON resistance; i.e., when all four  $AV_{IN}$ ,  $BV_{IN}$  pins are connected together the entire power device is connected (see Block Diagram). Each auxiliary supply pin,  $AV_{IN2}$ ,  $AV_{IN3}$ ,  $BV_{IN2}$  and  $BV_{IN3}$ , is connected to the drain of approximately 1/4 of the corresponding power device. The  $AV_{IN2}$ ,  $AV_{IN3}$ ,  $BV_{IN2}$  and  $BV_{IN3}$  pins can be selectively disconnected to reduce the short-circuit current limit at the expense of higher  $R_{DS(ON)}$ . (See Applications Information section for more details.)

**AV<sub>OUT</sub>**, **BV<sub>OUT</sub>** (**Pins 1,16; 8,9**): The outputs of the LTC1478 are protected against accidental short circuits to ground by a current limit circuit which protects the system power supplies and loads against damage. A second level of protection is provided by thermal shutdown circuitry which limits the die temperature to approximately 130°C.

### **OPERATION** (LTC1477 or single channel of LTC1478)

#### Input TTL-CMOS Converter

The LTC1477 enable input is designed to accommodate a wide range of 3V and 5V logic families. The input threshold voltage is approximately 1.4V with 100mV of hysteresis. The input enables the bias generator, the gate charge pump and the protection circuitry. Therefore, when the enable input is turned off, the entire circuit is powered down and the supply current drops below 1µA.

### **Ramped Switch Control**

The LTC1477 gate charge pump includes circuitry which ramps the NMOS switch on slowly (1ms typical rise time) but turns it off much more quickly (typically 20µs).

#### Bias, Oscillator and Gate Charge Pump

When the switch is enabled, a bias current generator and high frequency oscillator are turned on. The on-chip capacitive charge pump generates approximately 12V of gate drive for the internal low R<sub>DS(ON)</sub> NMOS switch from the power supply. No external 12V supply is required to switch the output.

#### Switch Protection

Two levels of protection are designed into the power switch in the LTC1477. The switch is protected against accidental short circuits with a current limit circuit which limits the output current to typically 2A when the output is shorted to ground. The LTC1477 also has thermal shutdown set at approximately 130°C which limits the power dissipation to safe levels.

### LTC1478 Operation

The LTC1478 dual protected switch can be thought of as two independent LTC1477 single protected switches. The input supply voltages may be from separate power sources. The around connection, however, is common to both channels and must be connected to the same potential.

### **BLOCK DIAGRAM** (LTC1477 or single channel of LTC1478)

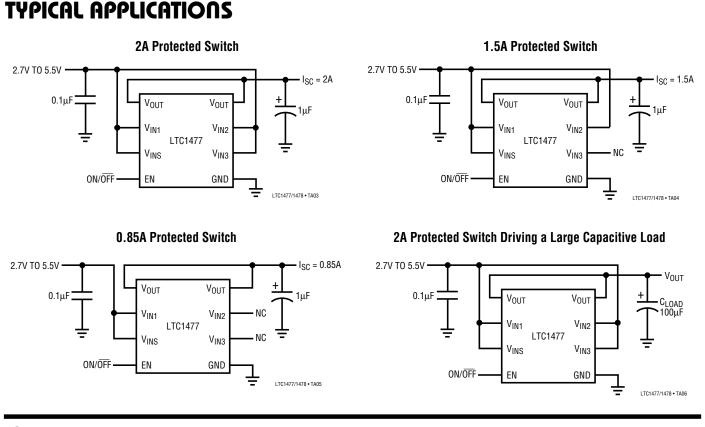

# APPLICATIONS INFORMATION

### Tailoring ILIMIT and RDS(ON) for Load Requirements

The LTC1477 is designed to current limit at approximately 2A during a short circuit with all the  $V_{IN}$  pins connected to the input power supply. It is possible however, to reduce this current by selectively disconnecting two of the four power supply pins ( $V_{IN2}$  and  $V_{IN3}$ ). Table 1 lists the effects of disconnecting these pins on R<sub>DS(ON)</sub> and short-circuit current limit

#### Table 1. Effects of Disconnecting V<sub>IN2</sub> and V<sub>IN3</sub>

|                     | ALL V <sub>IN</sub> PINS<br>Connected | V <sub>IN3</sub><br>DISCONNECTED | V <sub>IN2</sub> AND V <sub>IN3</sub><br>DISCONNECTED |

|---------------------|---------------------------------------|----------------------------------|-------------------------------------------------------|

| R <sub>DS(ON)</sub> | 0.07Ω                                 | 0.09Ω                            | 0.12Ω                                                 |

| LIMIT               | 2A                                    | 1.5A                             | 0.85A                                                 |

| Note: 5V Op         | eration                               |                                  | •                                                     |

Note: 5V Operation

Note that there is an inverse relationship between output current limit and switch resistance. This allows the tailor-

# **APPLICATIONS INFORMATION**

ing of the switch parameters to the expected load current and system current limit requirements.

A couple of examples are helpful:

- 1. If a nominal load of 1A was controlled by the switch configured to current limit at 2A (all  $V_{IN}$  pins connected together), the  $R_{DS(ON)}$  would be 0.07 $\Omega$  and the voltage drop across the switch would be 70mV. The power dissipated by the switch would only be 70mW.

- 2. If a nominal load of 0.5A was controlled by the switch configured to current limit at 0.85A ( $V_{IN2}$  and  $V_{IN3}$  disconnected), the  $R_{DS(ON)}$  would increase to 0.14 $\Omega$ . But the voltage drop would remain at 70mV and the switch power dissipation would drop to 35mW.

#### Supply Bypassing

For best results, bypass the supply input pins with a single  $1.0\mu$ F capacitor as close as possible to the LTC1477. Sometimes, much larger capacitors are already available at the output of the power supply. In this case, it is still good practice to use a  $0.1\mu$ F capacitor as close as possible

to the LTC1477, especially if the power supply output capacitor is more than 2 inches away on the printed circuit board.

#### **Output Capacitor**

The output pin is designed to ramp on slowly, typically 1ms rise time. Therefore, very large output capacitors can be driven without producing voltage spikes on the supply pins (see graphs in Typical Performance Characteristics). The output pin should have a  $1\mu$ F capacitor for noise reduction and smoothing.

#### Supply and Input Sequencing

The LTC1477 is designed to operate with continuous power (quiescent current drops to <  $1\mu$ A when disabled). If the power must be turned off, for example to enter a system "sleep" mode, the enable input must be turned off 100µs before the input supply is turned off to ensure that the gate of the NMOS switch is completely discharged before power is removed. However, the input control and power can be applied simultaneously during power up.

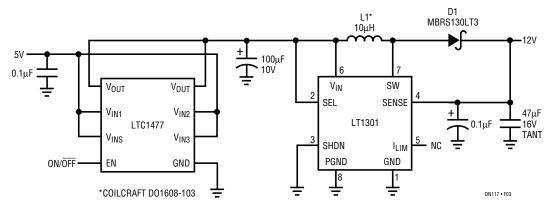

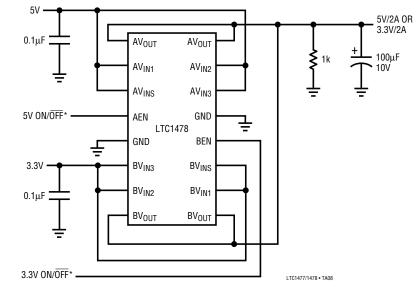

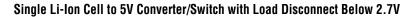

### **TYPICAL APPLICATIONS**

Adding Short-Circuit Protection to an LT1301 Step-Up Switching Regulator (0.01µA Standby Current)

5V to 3.3V Selector Switch with Slope Control and 0.01µA Standby Current

\*ALLOW AT LEAST 100ms BETWEEN 5V AND 3.3V SWITCHING FOR DISCHARGE OF 100µF OUTPUT CAPACITOR

\*PRIMARY Li-Ion BATTERY PROTECTION MUST BE PROVIDED BY AN INDEPENDENT CIRCUIT

# LTC1477/LTC1478

### PACKAGE DESCRIPTION Dimension in inches (millimeters) unless otherwise noted.

### **RELATED PARTS**

| PART NUMBER | DESCRIPTION                             | COMMENTS                                            |

|-------------|-----------------------------------------|-----------------------------------------------------|

| LTC1153     | Electronic Circuit Breaker              | MOSFET Driver with Adjustable Reset Time            |

| LTC1154     | Single High Side Driver                 | MOSFET Driver with Switch Status Output             |

| LTC1155     | Dual High Side Driver                   | Dual MOSFET Driver with Protection                  |

| LTC1470     | 5V and 3.3V V <sub>CC</sub> Switch      | SafeSlot <sup>™</sup> Protected Switch in 8-Lead SO |

| LTC1471     | Dual 5V and 3.3V V <sub>CC</sub> Switch | Dual Version of LTC1470 in 16-Lead SO               |

| LTC1472     | PCMCIA V <sub>CC</sub> and VPP Switches | Complete Single Channel SafeSlot Protection         |

SafeSlot is a trademark of Linear Technology Corporation.

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Gate Drivers category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below :

00028

00053P0231

8967380000

56956

CR7E-30DB-3.96E(72)

57.404.7355.5

LT4936

57.904.0755.0

5801-0903

5803-0901

5811-0902

5813-0901

58410

00576P0030

00581P0070

5882900001

00103P0020

00600P0005

00-9050-LRPP

00-9090-RDPP

5951900000

01

1003W-10/32-15

LTILA6E-1S-WH-RC-FN12VXCR1

0131700000

00-2240

LTP70N06

LVP640

0158-624-00

5J0-1000LG-SIL

020017-13

LY1D-2-5S-AC120

LY2-0-US-AC120

LY2-US-AC240

LY3-UA-DC24

00-5150

00576P0020

00600P0010

LZNQ2M-US-DC5

LZNQ2

US-DC12

LZP40N10

00-8196-RDPP

00-8274-RDPP

00-8275-RDNP

00-8609-RDPP

00-8722-RDPP

00-8728-WHPP

00-8869-RDPP

00

9051-RDPP

00-9091-LRPP

00-9291-RDPP

00-8722-RDPP

00-8728-WHPP

00-8869-RDPP

00