## LTC2947-65

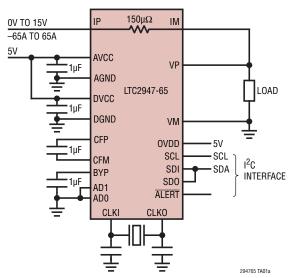

## 65A+ Power/Energy Monitor with Integrated Sense Resistor

## FEATURES

- Measures Current, Voltage, Power, Charge, Energy

- ±65A Current Range with Low 18mA Offset

- Integrated 150μΩ Sense Resistor

- OV to 15V Input Range Independent of Supply Voltage

- Instantaneous Multiplication of Voltage and Current

- 0.5% Voltage Accuracy

- 1% Current and Charge Accuracy

- 1.2% Power and Energy Accuracy

- Alerts When Thresholds Exceeded

- Stores Maximum and Minimum Values

- Shutdown Mode with I<sub>Q</sub> < 10µA</p>

- I<sup>2</sup>C/SPI Compatible Interface

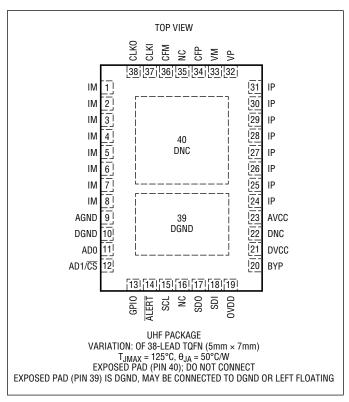

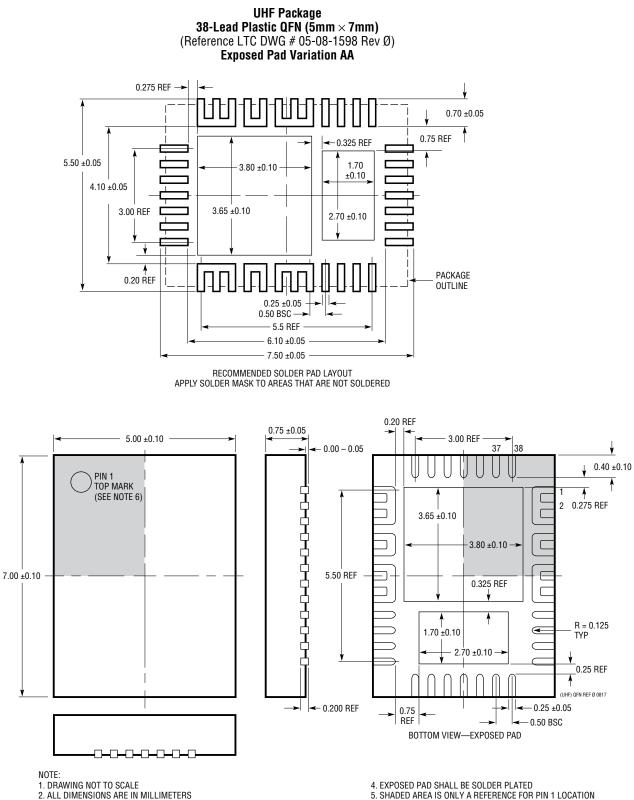

- Available in 38-Lead 5mm × 7mm QFN Package

### **APPLICATIONS**

- Servers

- Telecom Infrastructure

- Industrial

- Electric Vehicles

- Photovoltaics

## DESCRIPTION

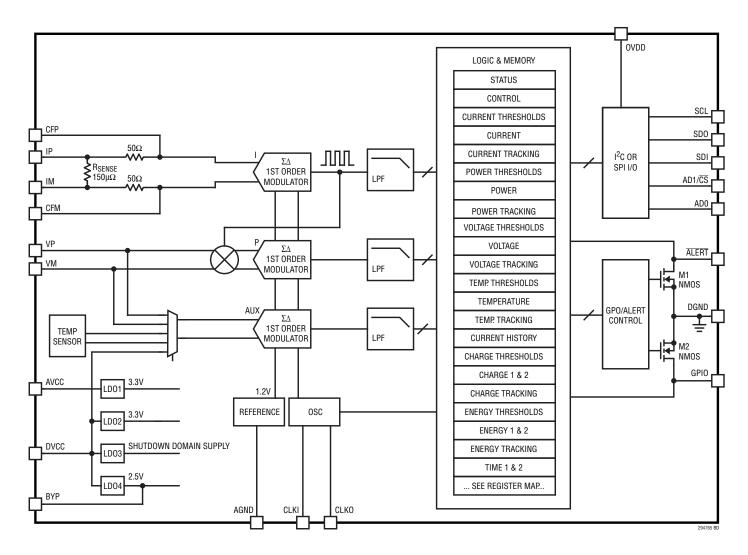

The LTC<sup>®</sup>2947-65 is a high precision power and energy monitor with an internal sense resistor supporting up to  $\pm 65A^*$ . Three internal No Latency  $\Delta\Sigma^{TM}$  ADCs ensure accurate measurement of voltage and current, while high-bandwidth analog multiplication of voltage and current provides accurate power measurement in a wide range of applications. Internal or external clocking options enable precise charge and energy measurements.

An internal  $150\mu\Omega$ , temperature-compensated sense resistor minimizes efficiency loss and external components, simplifying energy measurement applications while enabling high accuracy current measurement over the full temperature range.

All measured quantities are stored in internal registers accessible via the selectable  $I^2C/SPI$  interface. The LTC2947-65 features programmable high and low thresholds for all measured quantities to reduce digital traffic with the host.

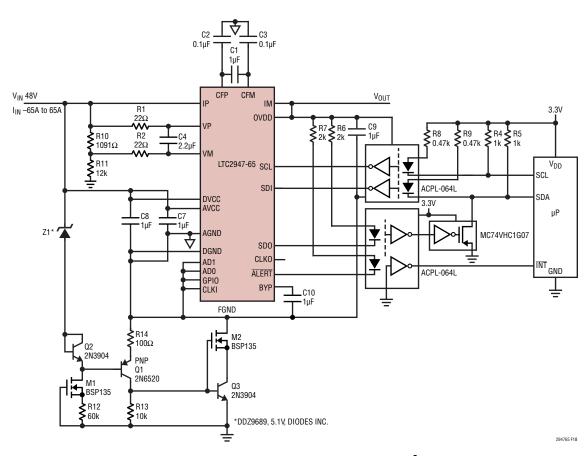

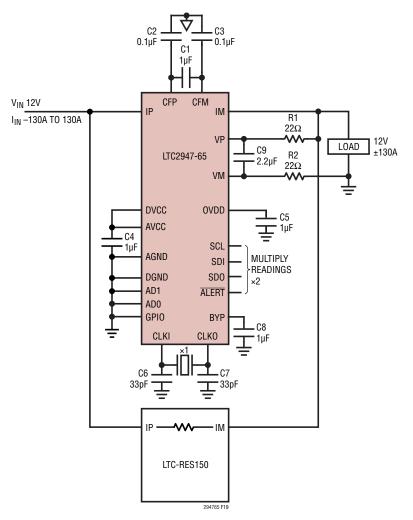

\*For applications greater than 65A, see Figure 19 or contact the factory.

All registered trademarks and trademarks are the property of their respective owners. Protected by U.S. Patents, including 8907703, 8841962.

## TABLE OF CONTENTS

| Description                                        | . 1 |

|----------------------------------------------------|-----|

| Absolute Maximum Ratings                           | . 3 |

| Order Information                                  | . 3 |

| Pin Configuration                                  | . 3 |

| Electrical Characteristics                         | . 4 |

| Timing Diagrams                                    | . 7 |

| Typical Performance Characteristics                | . 8 |

| Pin Functions                                      | 10  |

| Block Diagram                                      | .11 |

| Operation                                          | .12 |

| Overview                                           | 12  |

| Modes of Operation                                 |     |

| Current, Voltage and Temperature Measurement       | 14  |

| Power Measurement                                  | 14  |

| Charge, Energy Measurement and Accumulated Time    | 14  |

| Applications Information                           | 15  |

| Timebase: Internal/External Clock/Crystal          | 15  |

| Configuring the GPIO Pin                           | 15  |

| Internal Sense Resistor                            | 16  |

| Current and Voltage Input Filtering                | 16  |

| Layout Considerations                              | 17  |

| Digital Interface                                  |     |

| Selecting SPI or I <sup>2</sup> C Serial Interface |     |

| SPI Mode                                           |     |

| I <sup>2</sup> C Mode                              | 21  |

| Register Map                                       |     |

| Register Description                               |     |

| Register Naming Conventions                        |     |

| Paging Mechanism                                   |     |

| PAGE Control                                       |     |

| Operation Control                                  |     |

| Register Map PAGE0                                 |     |

| Register Map PAGE1                                 |     |

| Typical Applications                               |     |

| Package Description                                |     |

| Typical Application                                |     |

| Related Parts                                      | .42 |

## **ABSOLUTE MAXIMUM RATINGS**

#### (Notes 1, 2)

| Supply Pins                         |                |

|-------------------------------------|----------------|

| AVCC to AGND Voltage                | –0.3V to 20V   |

| DVCC to DGND Voltage                | –0.3V to 20V   |

| DGND to AGND Voltage                | –0.1V to 0.1V  |

| Digital Input/Output Pins           |                |

| OVDD to DGND Voltage                | –0.3V to 5.5V  |

| SCL, SDI, SDO, GPIO, ALERT, AD1,    |                |

| AD0 to DGND Voltage                 |                |

| CLKI to DGND Voltage                | –0.3V to 5.5V  |

| Analog Pins                         |                |

| VP, VM to AGND Voltage              |                |

| VP to VM Voltage                    |                |

| IP, IM Total Current (Note 6)       |                |

| IP, IM Current Per Pin (Note 6)     |                |

| CFP, CFM, BYP, CLKO                 | (Note 3)       |

| Operating Ambient Temperature Range |                |

| LTC2947-65I                         |                |

| Storage Temperature Range           | –65°C to 150°C |

|                                     |                |

## PIN CONFIGURATION

## **ORDER INFORMATION**

| TUBE               | TAPE AND REEL        | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|--------------------|----------------------|---------------|---------------------------------|-------------------|

| LTC2947IUHF-65#PBF | LTC2947IUHF-65#TRPBF | 294765        | 38-Lead (5mm × 7mm) Plastic QFN | –40°C to 85°C     |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

Rev. 0

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ .

| SYMBOL             | PARAMETER                                                               | CONDITIONS                                                               |   | MIN  | ТҮР                    | MAX                    | UNITS                        |

|--------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------|---|------|------------------------|------------------------|------------------------------|

| Power Sup          | ply                                                                     |                                                                          | I |      |                        |                        |                              |

| VAVCC, VDVC        | CC Supply Voltage                                                       |                                                                          | • | 4.75 |                        | 15                     | V                            |

| V <sub>OVDD</sub>  | Supply Voltage of Digital Interface                                     |                                                                          | • | 1.8  |                        | 5.5                    | V                            |

| V <sub>UVLO</sub>  | V <sub>AVCC</sub> , V <sub>DVCC</sub> Undervoltage Lockout<br>Threshold | V <sub>AVCC</sub> , V <sub>DVCC</sub> Falling                            | • |      |                        | 4.75                   | V                            |

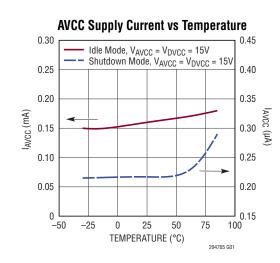

| IAVCC              | Supply Current Analog Section                                           | Continuous Mode<br>Idle Mode<br>Shutdown Mode<br>Shutdown Mode           | • |      | 3<br>0.2<br>0.3<br>0.3 | 3.5<br>0.3<br>0.5<br>1 | mA<br>mA<br>μA<br>μA         |

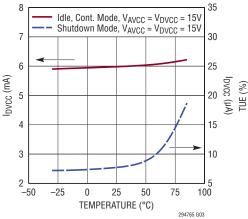

| IDVCC              | Supply Current Digital Section                                          | Continuous Mode<br>Idle Mode<br>Shutdown Mode<br>Shutdown Mode           | • |      | 6<br>6<br>7<br>7       | 8<br>8<br>9.5<br>90    | mA<br>mA<br>μA<br>μA         |

|                    | Delay of V <sub>AVCC,DVCC</sub> to V <sub>OVDD</sub> at Power-Up        | $V_{OVDD}, V_{AVCC}, V_{DVCC} \ge 0.9 \bullet V_{OVDDFINAL}$<br>(Note 8) | • | 0    |                        |                        | ns                           |

| Current Sei        | nse (IP, IM) ADC                                                        |                                                                          |   |      |                        |                        |                              |

|                    | Resolution (No Missing Codes)                                           | (Note 5)                                                                 | • | 15   |                        |                        | Bit                          |

| ISENSE             | Input Current Through IP and IM                                         | (Note 6)                                                                 | • |      |                        | ±65                    | A                            |

| R <sub>SENSE</sub> | Internal Sense Resistor                                                 | (Note 7)                                                                 | • | 93   | 150                    | 203                    | μΩ                           |

|                    | Sense Resistor Voltage                                                  | Current through IP and IM = 65A                                          |   |      | 9                      |                        | mV                           |

|                    | Common Mode Input Voltage Range                                         |                                                                          | • | -0.1 |                        | 15.5                   | V                            |

| LSBI               | Current Sense Quantization Step                                         |                                                                          |   |      | 6                      |                        | mA                           |

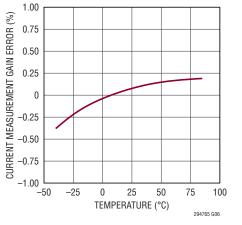

|                    | Current Gain Error                                                      |                                                                          | • |      |                        | ±0.75<br>±1            | % of Reading<br>% of Reading |

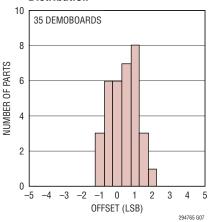

| I <sub>OS</sub>    | Current Offset                                                          |                                                                          | • |      |                        | ±3<br>±5               | LSB<br>LSB                   |

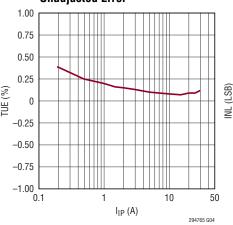

| INL                | Current Integral Nonlinearity                                           | (Note 6)                                                                 | • |      |                        | ±0.3                   | %                            |

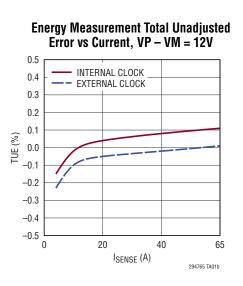

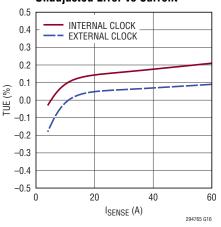

| TUE <sub>I</sub>   | Total Unadjusted Error                                                  | I  ≥ 12A (Note 6)                                                        | • |      |                        | ±1<br>±1.5             | % of Reading<br>% of Reading |

|                    | Input DC Common Mode Rejection                                          |                                                                          | • | 120  |                        |                        | dB                           |

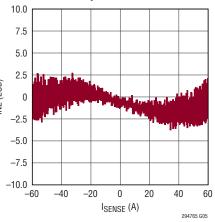

|                    | RMS Noise                                                               | (Note 5)                                                                 |   |      | 320                    |                        | nV                           |

|                    | Sampling Rate                                                           |                                                                          |   |      | 10.5                   |                        | MHz                          |

| Voltage Se         | nse (VP, VM) ADC                                                        |                                                                          |   |      |                        |                        |                              |

|                    | Resolution (No Missing Codes)                                           | (Note 5)                                                                 | • | 14   |                        |                        | Bit                          |

|                    | Common Mode Voltage                                                     |                                                                          | • | 0    |                        | 15.5                   | V                            |

| VD                 | Input Differential Voltage Range                                        | V <sub>VP</sub> – V <sub>VM</sub>                                        | • | -0.3 |                        | 15.5                   | V                            |

|                    | V <sub>D</sub> Quantization Step                                        |                                                                          |   |      | 2                      |                        | mV                           |

|                    | Voltage Gain Error                                                      |                                                                          | • |      |                        | ±0.4                   | % of Reading                 |

|                    | Voltage Offset                                                          |                                                                          | • |      |                        | ±2                     | LSB                          |

| INL <sub>V</sub>   | Voltage Integral Nonlinearity                                           |                                                                          | • |      |                        | ±2                     | LSB                          |

| TUE <sub>V</sub>   | Voltage Total Unadjusted Error                                          | $V_D \ge 4.0V$                                                           | • |      |                        | ±0.5                   | % of Reading                 |

|                    | Input DC Voltage Common Mode<br>Rejection                               |                                                                          | • | 70   |                        |                        | dB                           |

|                    | Sampling Rate                                                           |                                                                          |   |      | 5.25                   |                        | MHz                          |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C.

| SYMBOL              | PARAMETER                                 | CONDITIONS                                                                                                       |   | MIN                     | ТҮР   | MAX                     | UNITS                        |

|---------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------|---|-------------------------|-------|-------------------------|------------------------------|

| Power Meas          | surement                                  |                                                                                                                  |   |                         |       |                         |                              |

|                     | Resolution (No Missing Codes)             | (Note 5)                                                                                                         |   | 18                      |       |                         | Bit                          |

|                     | Full-Scale Power                          |                                                                                                                  |   |                         | 975   |                         | W                            |

|                     | Power Quantization Step                   |                                                                                                                  |   |                         | 100   |                         | mW                           |

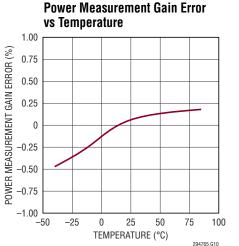

|                     | Power Gain Error                          |                                                                                                                  | • |                         |       | ±0.8<br>±1              | % of Reading<br>% of Reading |

|                     | Power Offset                              |                                                                                                                  |   |                         | ±2    |                         | LSB                          |

| INL <sub>P</sub>    | Power Integral Nonlinearity               | $ I  \ge 6A, V_D \ge 12V$ (Note 6)                                                                               |   |                         | ±0.3  |                         | % of Reading                 |

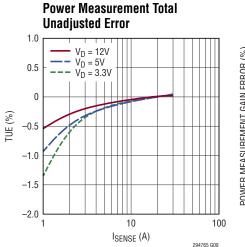

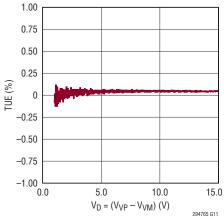

| TUE <sub>P</sub>    | Power Total Unadjusted Error              | $ I  \ge 6A, V_D \ge 12V$ (Note 6)                                                                               | • |                         |       | ±1.2<br>±1.5            | % of Reading<br>% of Reading |

|                     | Sampling Rate                             |                                                                                                                  |   |                         | 5.25  |                         | MHz                          |

| Timing              |                                           | •                                                                                                                |   |                         |       |                         |                              |

| TUE <sub>TB</sub>   | Time Base Total Unadjusted Error          | Internal Clock                                                                                                   | • |                         |       | ±0.5<br>±1              | % of Reading<br>% of Reading |

|                     |                                           | Ideal External Clock or Ideal 4MHz<br>Crystal (Note 5)                                                           | • |                         |       | ±340                    | ppm                          |

| t <sub>UPDATE</sub> | Update Time of Result Registers           |                                                                                                                  | • | 95                      | 100   | 105                     | ms                           |

| Energy Mea          | surement                                  |                                                                                                                  |   |                         |       |                         |                              |

| TUE <sub>E</sub>    | Energy Total Unadjusted Error             | $ I  \ge 6A, V_D \ge 12V$ , Ideal External Clock (Note 6)                                                        | • |                         |       | ±1.2<br>±1.5            | % of Reading<br>% of Reading |

|                     |                                           | $\begin{array}{l}  I  \geq 6A,  V_D \geq 12V,  Internal  Clock \\ (Note  6) \end{array}$                         | • |                         |       | ±1.5<br>±2.5            | % of Reading<br>% of Reading |

| Charge Mea          | asurement                                 | -                                                                                                                |   |                         |       |                         |                              |

| TUE <sub>C</sub>    | Charge Total Unadjusted Error             | $ I  \ge 6A$ , Ideal External Clock (Note 6)                                                                     | • |                         |       | ±1<br>±1.5              | % of Reading<br>% of Reading |

|                     |                                           | $ I  \ge 6A$ , Internal Clock (Note 6)                                                                           | • |                         |       | ±1.5<br>±2.5            | % of Reading<br>% of Reading |

| Temperatur          | e Measurement ADC                         |                                                                                                                  |   |                         |       |                         |                              |

|                     | Resolution (No Missing Codes)             | (Note 5)                                                                                                         |   | 13                      |       |                         | Bit                          |

|                     | Temperature Quantization Step             |                                                                                                                  |   |                         | 0.204 |                         | °C                           |

|                     | Temperature Error                         | (Note 5)                                                                                                         |   |                         | ±5    |                         | °C                           |

| Digital Inpu        | ts and Digital Outputs SCL, SDI, GPIO, A  | ILERT, SDO, CS, CLKI, ADO                                                                                        |   |                         |       |                         |                              |

| V <sub>ITH</sub>    | Logic Input Threshold                     | SCL, SDI, GPIO, CS, ADO                                                                                          |   | 0.3 • V <sub>OVDD</sub> |       | 0.7 • V <sub>OVDD</sub> | V                            |

| I <sub>IN</sub>     | Input Current SCL, SDI, GPIO              |                                                                                                                  |   |                         |       | ±1                      | μA                           |

| C <sub>IN</sub>     | Input Capacitance                         | (Note 5)                                                                                                         |   |                         |       | 10                      | pF                           |

| V <sub>OL</sub>     | Low Level Output Voltage SDO, GPIO, ALERT | $\begin{array}{l} V_{OVDD} \geq 3.3V, \ I_{PIN} = 3mA \\ 1.8V \leq V_{OVDD} < 3.3V, \ I_{PIN} = 1mA \end{array}$ | • |                         |       | 0.4<br>0.4              | V<br>V                       |

| V <sub>OH</sub>     | High Level Output Voltage (SDO)           | $I_{SDAO} = -0.5 \text{mA}$                                                                                      |   | V <sub>OVDD</sub> - 0.5 |       |                         | V                            |

|                     | CLKI Input Threshold                      |                                                                                                                  |   | 0.4                     | 0.7   | 2                       | V                            |

|                     | External Clock Frequency on Pin CLKI      |                                                                                                                  |   | 0.2                     |       | 25                      | MHz                          |

5

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C.

| SYMBOL                    | PARAMETER                                                                                              | CONDITIONS          |   | MIN                       | ТҮР | MAX | UNITS |

|---------------------------|--------------------------------------------------------------------------------------------------------|---------------------|---|---------------------------|-----|-----|-------|

| AD1, AD0                  | -                                                                                                      | 1                   |   | ,                         |     | I   |       |

|                           | Resistance Allowed on AD1 and AD0<br>When They Are Tied to OVDD or DGND<br>to Set a Valid L or H Level | See Table 3         | • |                           |     | 500 | Ω     |

|                           | Resistance to DGND to Set a Valid R<br>Level                                                           |                     | • | 20                        | 100 | 500 | kΩ    |

|                           | External Capacitive Load Allowed on AD1 and AD0 to Set a Valid R Level                                 |                     | • |                           |     | 100 | pF    |

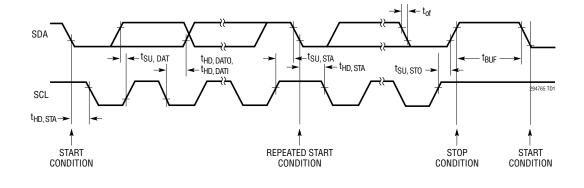

| I <sup>2</sup> C Bus Timi | ng                                                                                                     | ·                   | · |                           |     |     |       |

| f <sub>SCL(MAX)</sub>     | Maximum SCL Clock Frequency                                                                            |                     | • | 400                       | 900 |     | kHz   |

| t <sub>BUF(MIN)</sub>     | Bus Free Time Between STOP/START                                                                       |                     | • |                           |     | 1.3 | μs    |

| t <sub>SU,STA(MIN)</sub>  | Minimum Repeated START Setup Time                                                                      |                     | • |                           |     | 600 | ns    |

| t <sub>HD,STA(MIN)</sub>  | Minimum Hold Time (Repeated)<br>START Condition                                                        |                     | • |                           |     | 600 | ns    |

| t <sub>SU,STO(MIN)</sub>  | Minimum Set-Up Time for STOP<br>Condition                                                              |                     | • |                           |     | 600 | ns    |

| t <sub>su,dat(min)</sub>  | Minimum Data Set-Up Time Input                                                                         |                     | • |                           |     | 100 | ns    |

| t <sub>hd,dat(MIN)</sub>  | Minimum Data Hold Time Input                                                                           |                     | • |                           |     | 0   | ns    |

| t <sub>HD,DATO</sub>      | Data Hold Time Output                                                                                  |                     | • | 300                       |     | 900 | ns    |

| t <sub>RST</sub>          | Stuck Bus Reset Time                                                                                   | SCL or SDI Held Low | • | 25                        | 50  |     | ms    |

| t <sub>OF</sub>           | Data Output Fall Time                                                                                  | (Notes 4, 5)        | • | 20 + 0.1 • C <sub>E</sub> | }   |     | ns    |

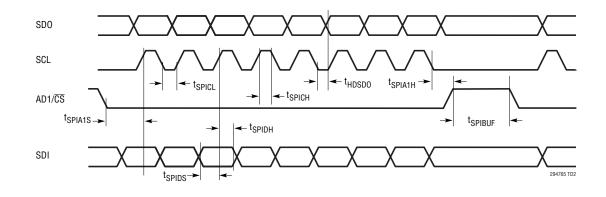

| SPI Bus Timi              | ing                                                                                                    |                     |   |                           |     |     |       |

| t <sub>SPIDS(MIN)</sub>   | Minimum SDI to SCL Data Setup                                                                          |                     | • |                           |     | 100 | ns    |

| t <sub>spibuf(Min)</sub>  | Minimum SPI Bus Free Time Between<br>Two CS Active States                                              |                     | • |                           |     | 4   | μs    |

| t <sub>SPIDH(MIN)</sub>   | Minimum SDI to SCL Data Hold                                                                           |                     | • |                           |     | 100 | ns    |

| t <sub>SPICH(MIN)</sub>   | Minimum SCL High State Duration                                                                        |                     | • |                           |     | 500 | ns    |

| t <sub>SPICL(MIN)</sub>   | Minimum SCL Low State Duration                                                                         |                     | • |                           |     | 500 | ns    |

| t <sub>SPIA1S(MIN)</sub>  | Minimum $\overline{CS}$ to First SCL Setup Time                                                        |                     | • |                           |     | 50  | ns    |

| t <sub>SPIA1H(MIN)</sub>  | Minimum $\overline{CS}$ to Last SCL Hold Time                                                          |                     | • |                           |     | 50  | ns    |

| t <sub>HDSDO</sub>        | SDO to SCL High to Low Output Hold Time                                                                |                     | • | 50                        |     | 350 | ns    |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: Positive currents flow into pins; negative currents flow out of pins. Minimum and maximum values refer to absolute values.

Note 3: Do not apply a voltage or current source to these pins. They must be connected to capacitive loads only. Pin CLKO may also be connected to a crystal as desired. Otherwise permanent damage may occur.

Note 4:  $C_B$  = capacitance of one bus line in pF (10pF  $\leq C_B \leq$  400pF).

Note 5: Guaranteed by design and characterization, not subject to test. Note 6: Guaranteed by design and test correlation.

Note 7:  $R_{SENSE}$  value is internally compensated for the actual value of the sense resistor.

Note 8:  $V_{OVDDFINAL}$  is the supply voltage value at OVDD at the end of its settling at power-up.

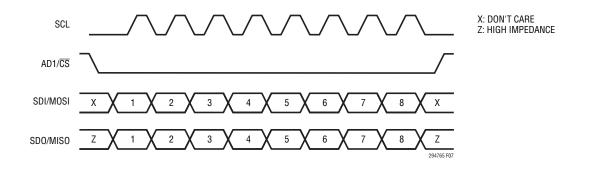

## TIMING DIAGRAMS

Definition of Timing on I<sup>2</sup>C Bus

**Definition of SPI Timing**

## TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , unless otherwise noted.

**DVCC Supply Current** vs Temperature

**Current Measurement Total Unadjusted Error**

**Current Measurement Integral** Nonlinearity

294765 G02

100

AVCC Supply Current Continuous

Continuous Mode,  $V_{AVCC} = V_{DVCC} = 15V$

50

75

25

TEMPERATURE (°C)

Mode vs Temperature

5

4

2

1

0

-50

-25

0

I<sub>AVCC</sub> (mA) 3

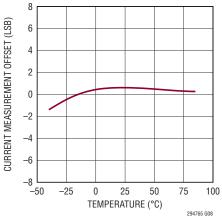

**Current Measurement Offset** Distribution

**Current Measurement Offset** vs Temperature

## **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , unless otherwise noted.

### Voltage Measurement ADC Total Unadjusted Error

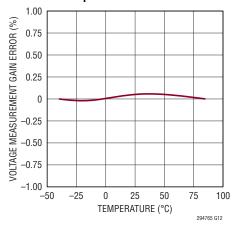

Voltage Measurement Gain Error vs Temperature

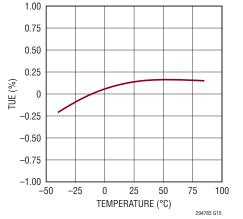

Time Base Total Unadjusted Error vs Temperature

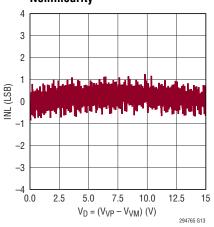

Voltage Measurement Integral Nonlinearity

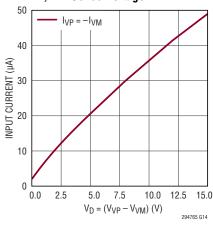

VP, VM Input Current vs VP, VM Sense Voltage

Charge Measurement Total Unadjusted Error vs Current

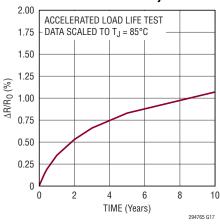

Sense Resistor Stability

Rev. 0

## PIN FUNCTIONS

**IM (Pins 1, 2, 3, 4, 5, 6, 7, 8):** Negative Current Input. Connects to internal current sense resistor. All eight pins must be tied together.

**AGND (Pin 9):** Analog Ground. See Layout Considerations in the Applications Information section.

**DGND (Pin 10):** Digital Ground. See Layout Considerations in the Applications Information section.

AD0 (Pin 11): Address Input 0. To select SPI mode, tie AD0 to OVDD. For I<sup>2</sup>C mode, tie AD0 to ground, either directly (L) or through a 100k $\Omega$  resistor (R), to select one of six I<sup>2</sup>C addresses. See Table 3 in the Applications Information section for details.

**AD1/CS (Pin 12):** Address Input 1/Chip Select. In SPI mode, this is the Chip Select input, active low. In  $I^2C$  mode, tie to OVDD (H), DGND (L), or through a 100k $\Omega$  resistor to ground (R) to select one of six  $I^2C$  addresses. See Table 3 in the Applications Information section for details.

**GPIO (Pin 13):** General Purpose I/O (Open Drain). Connect through a pull-up resistor to OVDD. Tie to ground if unused.

**ALERT (Pin 14):** ALERT Output. ALERT behaves as an open-drain logic output that pulls to ground if an unmasked Threshold register is exceeded or an unmasked error condition is detected. When the interface is operating in I<sup>2</sup>C mode, the ALERT pin follows the SMBus ARA (ALERT Response) protocol. See the I<sup>2</sup>C Mode section for more information. Tie ALERT to ground if unused.

**SCL (Pin 15):** Serial Clock. Serial clock input in both I<sup>2</sup>C and SPI Modes.

**SDO (Pin 17):** Serial Data Output. Data output in both  $I^2C$  and SPI modes. In  $I^2C$  mode, this pin may be tied to SDI to act as a standard bidirectional SDA pin, or kept separate to ease opto-isolation.

**SDI (Pin 18):** Serial Data Input. Data input in both  $I^2C$  and SPI modes. In  $I^2C$  mode, this pin may be tied to SDO to act as a standard bidirectional SDA pin, or kept separate to ease opto-isolation.

**OVDD (Pin 19):** Digital Interface Supply. Connect a  $1\mu$ F bypass capacitor from OVDD to DGND. The voltage at OVDD must reach 90% of its final value at the same time or before the voltage at AVCC/DVCC reaches this voltage level. This ensures that the device can read the AD0 and AD1 state correctly at power up.

**BYP (Pin 20):** Internal 2.5V Voltage Supply for Powering Internal Circuitry. Do not load. Connect a  $1\mu$ F bypass capacitor to DGND.

**DVCC (Pin 21):** Digital Power Supply. Connect a  $1\mu$ F bypass capacitor from DVCC to DGND. AVCC and DVCC should be connected together.

DNC (Pin 22): Do Not Connect.

**AVCC (Pin 23):** Analog Power Supply. Connect a  $1\mu$ F bypass capacitor from AVCC to AGND. AVCC and DVCC should be connected together.

**IP (Pins 24, 25, 26, 27, 28, 29, 30, 31):** Positive Current Input. Connects to internal current sense resistor. All eight pins must be tied together.

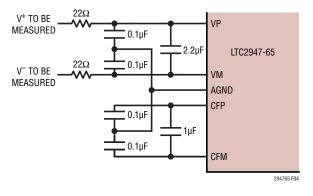

**VP (Pin 32):** Positive Voltage Sense Input. Connect to the positive terminal of the voltage to be measured. A  $22\Omega$  series resistor and a  $2.2\mu$ F bypass capacitor to VM are recommended.

**VM (Pin 33):** Negative Voltage Sense Input. Connect to the negative terminal of the voltage to be measured. A  $22\Omega$  series resistor and a  $2.2\mu$ F bypass capacitor to VP are recommended.

**CFP (Pin 34):** Positive Filter Pin. Connect a  $1\mu$ F bypass capacitor between CFP and CFM and a  $0.1\mu$ F common mode capacitor from CFP to AGND.

**CFM (Pin 36):** Negative Filter Pin. Connect a  $1\mu$ F bypass capacitor between CFP and CFM and a  $0.1\mu$ F common mode capacitor from CFM to AGND.

**CLKI (Pin 37):** Clock Input. Connect to ground if the internal clock is used. For improved accuracy, connect a crystal between CLKI and CLKO and matching capacitors to ground, or drive CLKI with an external clock. See the Timebase Control section for more information.

**CLKO (Pin 38):** Clock Output. Connect a crystal between CLKO and CLKI if used; leave floating otherwise.

**DGND (Pin 39):** Exposed Pad. Connect to DGND or leave floating.

**EXPOSED PAD 1 (Pin 40):** Internal current sense resistor. Do not connect to any metal or other conducting material. See the Layout Considerations section for more information.

NC (Pins 16 and 35): No connect. Leave these pins floating. Rev. 0

## **BLOCK DIAGRAM**

## OPERATION

### **OVERVIEW**

The LTC2947-65 is a high precision power and energy meter with integrated sense resistor for currents up to  $\pm$ 65A and voltages as high as 15V. It measures a total of seven parameters: current, voltage, power, charge (coulombs), energy, and run time, as well as its own chip temperature.

It includes three No Latency  $\Delta\Sigma$  analog-to-digital converters to simultaneously measure current, voltage, and power. It also measures die temperature and derives the accumulated quantities charge, energy, and time using an external clock or an on-board oscillator. It stores these values in internal registers that can be read out via the serial interface, configurable as either I<sup>2</sup>C or SPI.

The LTC2947-65 keeps track of the minimum and maximum measured values for each of the measured quantities. Thresholds can be set for each parameter, and the LTC2947-65 will set the corresponding bit in the Alert register and optionally alert the host by pulling low on the ALERT pin when a threshold is exceeded.

A GPIO pin is included that can be used for four different purposes. It can be configured as a general-purpose-logic input or output, as an output to automatically control a fan based on the LTC2947-65's internal silicon temperature measurement or as an input to enable and disable accumulation of charge, energy, and time.

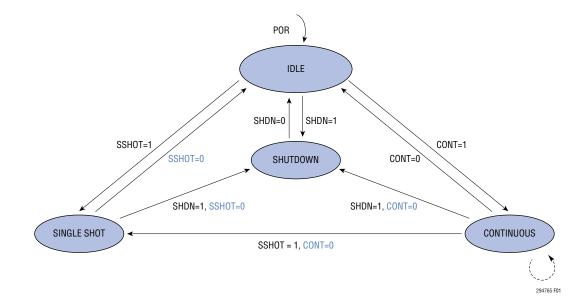

### **MODES OF OPERATION**

### Power Up

When all power supply voltages have risen above their UVLO thresholds, the LTC2947-65 boots up, sets all registers to their default state, and enters IDLE mode, where it waits for further instructions from the host. The LTC2947-65 requires about 100ms to boot up and enter the IDLE mode.

### IDLE

In IDLE mode, all internal circuitry is active but no measurements are being made. From IDLE, the LTC2947-65 can be instructed to go into single shot, continuous, or shutdown modes via the Operation Control control register.

### Single Shot (SSHOT)

When the SSHOT bit in the Operation Control register is set, the LTC2947-65 takes four measurements (current, voltage, power, and temperature), and updates the corresponding registers and the Minimum/Maximum and Threshold registers. No time measurements are made and the Charge and Energy registers are not updated. It then clears the SSHOT bit in the Operation Control register, sets the UPDATE bit in Status register and returns to the IDLE mode. One single shot measurement cycle takes 100ms. The host can poll the UPDATE bit in the Status register to detect the completion of the measurement cycle.

### **Continuous Measurement Mode (CONT)**

When the CONT bit in the Operation Control register is set, the LTC2947-65 repeatedly measures current, voltage, power, and temperature, recalculates energy, charge, time and updates the Minimum/Maximum Tracking and Threshold registers. Each measurement cycle takes about 100ms. The current and power ADCs run continuously in this mode, ensuring that no charge or energy is missed. The LTC2947-65 remains in continuous mode until bit CONT of the Operation Control register is reset by the user. If the SSHOT bit is set while in continuous mode, the LTC2947-65 completes the current measurement cycle and then enters single shot mode, clearing the CONT bit in the Operation Control register.

### Shutdown (SHDN)

When the SHDN bit in the Operation Control register is set, the LTC2947-65 goes into shutdown mode, and supply current reduces to about  $10\mu$ A. If the device is in the middle of a measurement cycle, in either single shot or continuous mode, it completes the cycle before entering shutdown and clearing the SSHOT or CONT bits. Shutdown clears the voltage, current, and temperature results, but preserves the values of the accumulated quantities charge and energy and all threshold and tracking values.

## OPERATION

While in shutdown mode, the LTC2947-65 continues to monitor the serial interface. In SPI mode, the LTC2947-65 transitions from shutdown to IDLE when CS goes low. In I<sup>2</sup>C mode, the LTC2947-65 transitions to IDLE after acknowledging the correct slave address. The LTC2947-65 requires about 100ms to wake up from shutdown. During this time, it ignores register writes and responds to register reads with 0x01. Once awake, the LTC2947-65 goes into IDLE mode and waits for further instructions. The host can poll the Operation Control register and watch for a 0x00 response to determine that the LTC2947-65 is awake and in IDLE mode.

In shutdown mode, the internal analog and digital supplies are switched off. This causes the UVLOA and UVLOD bits to be set when the LTC2947-65 resumes from shutdown. The UVLOSTBY bit and the PORA bit are only set if the supply voltage at AVCC/DVCC drops below  $V_{UVLO}$  and a power-on reset has occurred.

The state diagram (Figure 1) summarizes the different modes of operation of LTC2947-65. Transitions and control bit settings initiated by the user are marked in black while transitions and control bit settings caused by the device are marked in blue.

Switching between operating modes can require up to 100ms if a measurement cycle is in progress.

Figure 1. Modes of Operation

### **OPERATION** CURRENT, VOLTAGE AND TEMPERATURE MEASUREMENT

The LTC2947-65 measures each input with an ADC specifically tailored for the task. Current through the internal sense resistor is measured with a  $\Delta\Sigma$  ADC that has a measurement range of ±65A and a resolution of 6mA. The common mode voltage can range from 100mV below GND up to 15.5V, regardless of the supply voltage at AVCC. This ADC uses a first-order architecture and continuous offset calibration to ensure that all input samples are averaged with equal weight and none are missed—the current ADC is never "blind." A 10MHz sampling rate maintains averaging accuracy for all current waveforms including harmonics up to 2.5MHz. A new average value is reported every 100ms.

A second ADC sequentially measures both temperature and differential voltage between the VP and VM pins while the current measurement is being made. The temperature measurement is both reported to the host and used internally by the LTC2947-65 to compensate for the temperature drift of the internal current sense resistor, resulting in very stable current measurements. The voltage measurement has a 2mV resolution and temperature has a 0.204°C resolution. The differential voltage measurement range (VP-VM) ranges from –0.3V to 15.5V, independent of supply voltage.

Note that the temperature measurement is made with a sensor on the die, which can vary significantly from ambient temperature if the current in the internal sense resistor is high. A high supply voltage at AVCC/DVCC increases the internal power and will also increase the internal temperature.

### **POWER MEASUREMENT**

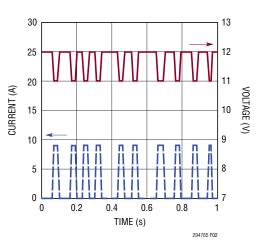

The LTC2947-65 measures power with a third ADC that multiplies voltage (VP-VM) and current at the full 5MHz sampling frequency, prior to any averaging due to the analog-todigital conversion. This maintains accuracy even if current and voltage change in phase during the 100ms conversion time, which can happen if the power is drawn from a source with significant impedance, such as a battery. Figure 2 shows an example of a 12V supply dropping to 11V due to internal series resistance when 9A current pulses are drawn by a load. In this example, the multiplication of average current with average voltage would lead to a 6% error in the calculated power as the voltage is significantly lower than the average voltage at the moments where the current is drawn. The scheme used by the LTC2947-65 avoids this error, maintaining specified accuracy with signals up to 50kHz.

Figure 2. Power Measurement of Transient Signals

# CHARGE, ENERGY MEASUREMENT AND ACCUMULATED TIME

The LTC2947-65 integrates the current and power measurements over time to calculate charge and energy flowing to or from the load. It also keeps track of total accumulated time used for the integration. The integration time base can be provided by the internal clock, an external clock attached to CLKI, or an external crystal connected to CLKI and CLKO. If an external clock is used, the LTC2947-65 presents time, charge and energy as a mathematical relationship to the external clock period.

For each of the quantities charge, energy, and time, the LTC2947-65 provides two sets of registers. Each register set can be separately configured to accumulate either based on the sign of the measured current, or by the level of the GPIO pin, or by the Control register settings. This allows the first set of accumulation registers to be configured to always integrate while the second set only integrates if current is positive (to account for battery charging efficiency, for example). A minimum current threshold can also be set below which integration is stopped.

### TIMEBASE: INTERNAL/EXTERNAL CLOCK/CRYSTAL

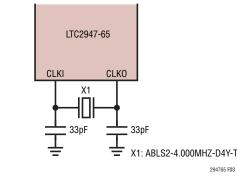

Accurately measuring charge and energy by integrating current and power requires a precise timing. The LTC2947-65 uses either a trimmed internal oscillator or an external clock as the time base for determining the integration period. It can use either an external square wave clock in a frequency range between 200kHz and 25MHz or a 4MHz crystal as an external clock input. If an external square wave is used, it should be connected to the CLKI pin and the CLKO pin should be left floating. Figure 3 shows the recommended circuit if a crystal is used to generate the reference clock.

When the internal clock is used, tie CLKI to DGND and leave CLKO floating.

Figure 3. Reference Clock with a Crystal

### Timebase Control

The LTC2947-65 uses the internal oscillator by default. If an external clock or a crystal is used, the PRE and DIV parameters in the Timebase Control register need to be set appropriately. The LTC2947-65 then compares its internal clock to the external frequency and represents time, charge, and energy as multiples of the external clock period. To accommodate the large range of allowed external frequencies, an internal pre-scaler must be configured via the Timebase Control register (0xE9).

The prescaler consists of 2 stages, with the first dividing the external frequency  $f_{REF}$  by a factor  $2^{PRE}$ , and the second by a factor DIV. PRE is set between 0 and 5 with bits [2:0] of the Timebase Control register (0xE9). PRE should be set to the lowest value that gives less than 1MHz when dividing the external frequency by  $2^{PRE}$  as shown in Table 1:

| Table 1. Parameter PRE with External Cloc | k |

|-------------------------------------------|---|

|-------------------------------------------|---|

| f <sub>REF</sub>                        | PRE | 2 <sup>PRE</sup> | PRE[2:0] |

|-----------------------------------------|-----|------------------|----------|

| $0.1MHz \le f_{REF} \le 1MHz$           | 0   | 1                | 000      |

| $1$ MHz < f <sub>REF</sub> $\leq 2$ MHz | 1   | 2                | 001      |

| $2MHz < f_{REF} \le 4MHz$               | 2   | 4                | 010      |

| $4MHz < f_{REF} \le 8MHz$               | 3   | 8                | 011      |

| 8MHz < f <sub>REF</sub> ≤ 16MHz         | 4   | 16               | 100      |

| 16MHz < f <sub>REF</sub> ≤ 25MHz        | 5   | 32               | 101      |

| Internal                                | 7   | -                | 111      |

The second stage of the prescaler then divides the result by a factor DIV. DIV is set between 0 and 31 by bits [7:3] of the Timebase Control register. DIV should be set to the next lower integer value of the ratio between the output of the first stage of the prescaler ( $f_{REF_1} = f_{REF}/2^{PRE}$ ) and 32768Hz or, in other terms:

$$\mathsf{DIV} = \mathsf{floor}\left(\frac{\mathsf{f}_{\mathsf{REF}}}{2^{\mathsf{PRE}} \bullet 32768\mathsf{Hz}}\right)$$

If a 4MHz crystal is used, the values are: PRE = 2, DIV = 30.

The QuikEval<sup>™</sup> software for the LTC2947-65 contains an easy-to-use calculator for these parameters.

Table 2 gives a few examples for common frequencies.

Table 2. Timebase Settings For Common Frequencies

| -                         |     |                  |                             |     |                           |

|---------------------------|-----|------------------|-----------------------------|-----|---------------------------|

| f <sub>REF</sub><br>(MHz) | PRE | 2 <sup>PRE</sup> | f <sub>REF_1</sub><br>(MHz) | DIV | TIMEBASE<br>Control [7:0] |

| 1MHz                      | 0   | 1                | 1                           | 30  | 1111 0000                 |

| 1.5MHz                    | 1   | 2                | 0.75                        | 22  | 1011 0001                 |

| 4MHz                      | 2   | 4                | 1                           | 30  | 1111 0010                 |

| 10MHz                     | 4   | 16               | 0.625                       | 19  | 1001 1100                 |

| 20MHz                     | 5   | 32               | 0.625                       | 19  | 1001 1101                 |

| 25MHz                     | 5   | 32               | 0.781                       | 23  | 1011 1101                 |

| Internal                  | 7   | -                | -                           | Х   | XXXX X111                 |

|                           |     |                  |                             |     |                           |

### **CONFIGURING THE GPIO PIN**

The LTC2947-65 has one GPIO pin that can be configured to be a general purpose input or a general purpose open drain output by means of the bit GPOEN in the GPIO Status and Control register (0x67)[0].

When the GPIO pin is configured as an input by setting 0x67[0] = 0, the status of the GPIO pin is reported by the GPI bit of the GPIO Status and Control register at (0x67) [4]. The state of the general purpose input pin can be used to control the accumulation of charge, energy and time by means of the Accumulator Control GPIO register (0xE3). This accumulation function can be enabled separately for each of the two sets of accumulation registers. Setting bits (0xE3)[1:0] to [01] enables accumulation of Charge1, Energy1 and Time1 when GPIO is 1, while setting bits (0xE3)[1:0] to [10] enables accumulation of Charge1, Energy1 and Time1 when GPIO is 0. Setting bits (0xE3)[1:0] to [00] disables the accumulation control of the first set of accumulation registers by the GPIO level. Similarly, accumulation of Charge2, Energy2 and Time2 can be controlled by bits (0xE3)[3:2] of the accumulation control GPIO Register.

When the GPIO pin is configured as an open drain output by setting (0x67)[0] = [1], it can be pulled low by writing bit GPO in the GPIO Status and Control register (0x67)[5] to 0 or released high by writing bit GPO to 1. As an open drain output, the GPIO pin can also be configured to control a fan as a function of measured temperature by setting bit FANEN (0x67)[6] to 1. Then, the GPIO pin becomes active as soon as a temperature measurement result is above the threshold TFANH written at (page1.0x9C) and (page1.0x9D), and is deactivated if the temperature falls below the threshold TFANL written at (page1.0x9E) and (page1.0x9F). The polarity of the GPIO pin can be configured by setting bit FANPOL at (0x67)[7] to 0 or 1, respectively. The GPIO output level is maintained in shutdown. Since the internal sampling rate of the GPIO state is 100ms the reaction on any change of that state as input or output may be in this time range.

### **INTERNAL SENSE RESISTOR**

The LTC2947-65 uses proprietary techniques to compensate for the internal sense resistor's temperature coefficient. A factory trim of both absolute value and tempco compensation, together with an ultralow offset ADC, contribute to the LTC2947-65's superior accuracy when current measurement is involved (i.e. current, power, charge, energy).

Like all sense resistors, the integrated sense resistor in the LTC2947-65 will exhibit minor long-term resistance shifts. See the Typical Performance Characteristics section for expected resistor drift performance under worstcase conditions. Drift will be much less at lower temperatures and/or currents.

### **CURRENT AND VOLTAGE INPUT FILTERING**

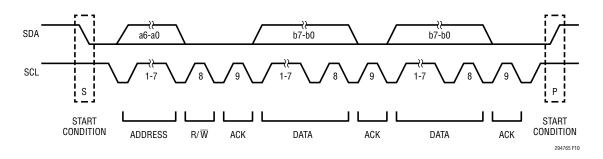

To ensure the full electrical performance of the ADCs for current, power and voltage, apply the input filtering circuitry as shown in Figure 4 to pins CFP, CFM, VP and VM. These components provide optimum input filtering for noise reduction. Equal time constants at the current and voltage inputs minimize errors in power measurement of transient signals due to different delays in each path.

Figure 4. Input Filtering

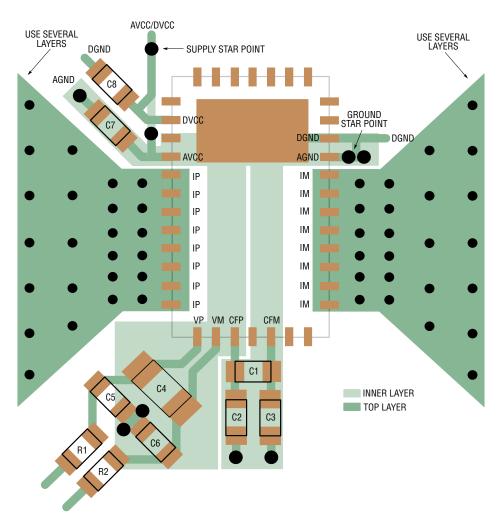

### LAYOUT CONSIDERATIONS

Lowering the electrical resistance of the PCB traces to the IP and IM pins minimizes heating of the area near the LTC2947-65 and the temperature increase of the LTC2947-65 itself. Methods to lower the electrical resistance of the PCB traces include increasing the width of these traces and the number of PCB layers and including a sufficient number of vias as shown in Figure 5.

When connecting to the IP and IM pins, it is recommended to use PCB traces with a 70µm minimum thickness or greater. The current reading value is slightly dependent on the thickness of IP and IM PCB traces below 70µm. The exposed pad between IP and IM must not have contact or be soldered to any electrically conducting PCB pad or track.

The input filter common-mode capacitors and pins CFP and CFM should be star-connected directly to the AGND pin. Any unrelated ground currents in this connection will cause measurement errors. This can be achieved by combining the ground tracks of the capacitors at CFP, CFM including the AGND pin to a separate small plane and connecting this plane at one point to the ground of the PCB. Figure 5 sketches this star connection concept; the interference to the ADC inputs is minimized. In the

Figure 5. Recommended Layout of Current Tracks, Voltage Input and Ground

same way, a small separate plane can collect the ground connections of the capacitors attached to DVCC, OVDD, including the DGND pin, and be connected to the same ground-starpoint as the AGND plane to the ground of the PCB.

The supplies of AVCC and DVCC pins should also be starrouted. The decoupling caps should be placed closer to these pins than the supply-starpoint.

The crystal oscillator's clock amplitude is sensitive to parasitics such as stray capacitance on the CLKOUT pin and coupling between the CLKIN and CLKOUT pins. It is

recommended that the CLKIN and CLKOUT traces from the LTC2947-65 to the crystal oscillator network be as short as practical, with the load capacitors placed next to the crystal. To minimize stray capacitances, avoid large ground planes and digital signals near the crystal network.

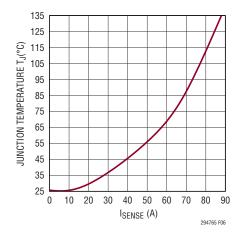

The heat dissipated in the internal current sense resistor ( $R_{SENSE}$ ) will yield a corresponding junction temperature rise. A plot of the Junction Temperature vs I<sub>SENSE</sub> for the layout illustrated in Figure 5 at ambient temperature (25°C) is illustrated in Figure 6.

Figure 6. Junction Temperature  $T_J \left( ^\circ C \right)$  vs  $I_{SENSE} \left( A \right)$

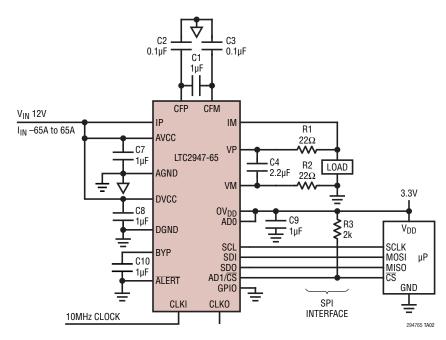

### SELECTING SPI OR I<sup>2</sup>C SERIAL INTERFACE

The serial interface of the LTC2947-65 can operate in either SPI or  $I^2C$  mode. To select SPI mode, tie AD0 to OVDD. To select  $I^2C$  mode, connect AD0 according to Table 3. The LTC2947-65 selects SPI or  $I^2C$  mode by reading pin AD0 when DVCC is powered up. To ensure proper mode detection, OVDD should be powered up before DVCC.

### **SPI MODE**

### **Physical Layer**

In SPI mode, the LTC2947-65 acts as a SPI slave, with the AD1 pin acting as  $\overline{CS}$  (chip select, active low). Logic input thresholds and output swings are set by the voltage at the OVDD pin, which should be connected to the same supply as the SPI master device. A 1µF bypass capacitor is recommended from OVDD to DGND. The SDI pin is often referred to as MOSI, the SDO pin as MISO. The LTC2947-65 samples data at SDI on the rising edge of SCL and changes data at SDO on the falling edge of SCL (often referred to as CPHA = 0, CPOL = 0).

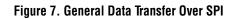

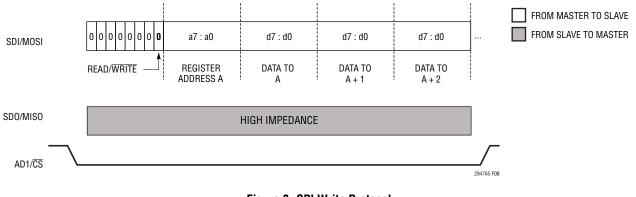

### Data Layer

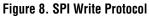

All data sent to the LTC2947-65 is transmitted in 8-bit bytes, MSB first. The LTC2947-65 returns data in this same format. Multiple bytes can be sent in a single transaction. Figure 8 and Figure 9 show typical write and read transactions.

#### Write Protocol

The master writes to the LTC2947-65 by sending 0x00 as the first byte in a transaction followed by the address of the first register to be written. The next transmitted byte will be written to this address. The LTC2947-65 increments its address pointer after each byte is received, so multiple bytes can be written as part of a single transaction. Incomplete bytes are discarded.

### **Read Protocol**

The master reads from the LTC2947-65 by sending 0x01 as the first byte in a transaction followed by the address of the first register to be read. The LTC2947-65 sends data bytes starting from that address, incrementing the address pointer after each byte sent. Any number of bytes can be read; if the address pointer reaches address 0xFF, it will roll over to address 0x00. Any data on the SDI line after the register address is ignored by the LTC2947-65.

### **SPI Alert Handling**

The LTC2947-65 can be configured to generate alerts via the ALERT pin when a variety of events occur. To enable alerts, set bit ALERTBEN in the Alert Master Control Enable register (0xE8)[0] (this is the default setting). Select which events trigger alerts by clearing bits in the Mask registers (addresses 0x88 to 0x8F).

If an alert is enabled, the corresponding event causes the ALERT pin to pull low. To release the ALERT pin in SPI mode, the master must read the Status, Threshold and Overflow Alert registers (0x80 to 0x87).

### I<sup>2</sup>C MODE

### I<sup>2</sup>C Device Addressing

If AD0 is not tied high at power up, the LTC2947-65 operates in I<sup>2</sup>C mode. The I<sup>2</sup>C address can be configured by connecting AD1 and AD0 as shown in Table 3. The levels are: L: low, tie to DGND, H: high, tie to OVDD, R: resistor, connect to DGND with a 100k $\Omega$  resistor. The LTC2947-65 will check AD0 and AD1 at the beginning of each I<sup>2</sup>C transaction and respond to the corresponding I<sup>2</sup>C address.

At power up if AD0 is tied low (to DGND) then the device is guaranteed to operate in  $I^2C$  mode. Maintaining AD0 low restricts the available addresses, but eases the OVDD sequencing requirement during power up.

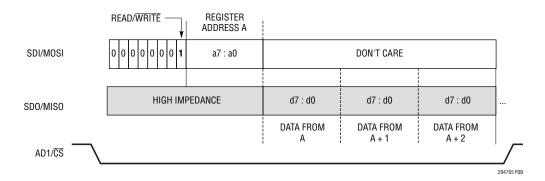

### START and STOP Conditions

When the I<sup>2</sup>C bus is idle, both SCL and SDA are in the HIGH state. The master signals the beginning of a transmission with a START condition by transitioning SDA from high to low while SCL stays high. When the master has finished communicating with the slave, it issues a STOP condition by transitioning SDA from LOW to high while SCL stays high. The bus is then free for another transmission.

### Stuck-Bus Reset

The LTC2947-65 I<sup>2</sup>C interface includes a stuck-bus timer to prevent it from holding the bus lines low indefinitely if the SCL signal is interrupted during a transfer. The timer

| Table | 3. | I <sup>2</sup> C | Addresses |

|-------|----|------------------|-----------|

|-------|----|------------------|-----------|

starts when either SCL or SDI is low, and resets when both SCL and SDI are high. If either SCL or SDI stay low for more than 50ms, the stuck-bus timer will reset the internal I<sup>2</sup>C interface to release the bus. Normal communication will resume at the next START command.

### Acknowledge

An acknowledge signal is used for handshaking between the master and the slave. When receiving data, the LTC2947-65 will pull the SDA line low every ninth clock cycle to acknowledge each data byte. If the slave fails to acknowledge by leaving SDA high, the master should abort the transmission by generating a STOP condition. Similarly, when the master is receiving data from the slave, it must generate acknowledge pulses by pulling down the SDA line every 9th clock. After the last byte has been received by the master, it may leave the SDA line high (not acknowledge) and issue a STOP condition to terminate the transmission.

### Write Protocol

The master begins a write operation with a START condition followed by the 7-bit slave address with the R/W bit set to zero. If the slave address matches the address programmed at its AD0/AD1 pins, the LTC2947-65 acknowledges the address byte. The master then sends a register address byte that indicates which internal register the master wishes to write. The LTC2947-65 acknowledges again and latches the register address into its internal register address pointer. The master then sends the data

| ADO | AD1 | 8-BIT ADDRESS<br>BYTE WRITE | 8-BIT ADDRESS<br>Byte read | 7-BIT DEVICE<br>Address | -  |    |    |    |    |    |    |     |

|-----|-----|-----------------------------|----------------------------|-------------------------|----|----|----|----|----|----|----|-----|

|     |     |                             |                            | a6:a0                   | a6 | a5 | a4 | a3 | a2 | a1 | a0 | R/W |

| L   | L   | 0xB8                        | 0xB9                       | 0x5C                    | 1  | 0  | 1  | 1  | 1  | 0  | 0  | 1/0 |

| L   | Н   | 0xBA                        | 0xBB                       | 0x5D                    | 1  | 0  | 1  | 1  | 1  | 0  | 1  | 1/0 |

| L   | R   | 0xBC                        | 0xBD                       | 0x5E                    | 1  | 0  | 1  | 1  | 1  | 1  | 0  | 1/0 |

| R   | L   | 0xC8                        | 0xC9                       | 0x64                    | 1  | 1  | 0  | 0  | 1  | 0  | 0  | 1/0 |

| R   | Н   | 0xCA                        | 0xCB                       | 0x65                    | 1  | 1  | 0  | 0  | 1  | 0  | 1  | 1/0 |

| R   | R   | 0xCC                        | 0xCD                       | 0x66                    | 1  | 1  | 0  | 0  | 1  | 1  | 0  | 1/0 |

Note 10: L: tie to DGND, H: tie to OVDD, R: resistor, connect to DGND with a 100 k  $\Omega$  resistor.

Figure 10. General Data Transfer Over I<sup>2</sup>C

| S | ADDRESS | W | A | REGISTER | A | DATA  | A | P |

|---|---------|---|---|----------|---|-------|---|---|

|   | a6:a0   | 0 | 0 | b7:b0    | 0 | b7:b0 | 0 |   |

Figure 11. I<sup>2</sup>C Write Byte Protocol

| S | ADDRESS | W | A | REGISTER | A | DATA  | A | DATA  | A | <br>DATA  | A   | Р       |

|---|---------|---|---|----------|---|-------|---|-------|---|-----------|-----|---------|

|   | a6:a0   | 0 | 0 | b7:b0    | 0 | b7:b0 | 0 | b7:b0 | 0 | <br>b7:b0 | 0   |         |

|   |         |   |   |          |   |       |   |       |   |           | 294 | 765 F12 |

Figure 12. I<sup>2</sup>C Write Multiple Bytes Protocol

| S | ADDRESS  | W | A | REGISTER | A | S | ADDRESS | R | A | DATA  | Ā       | Р |

|---|----------|---|---|----------|---|---|---------|---|---|-------|---------|---|

|   | a6:a0    | 0 | 0 | b7:b0    | 0 |   | a6:a0   | 1 | 0 | b7:b0 | 1       |   |

|   | 294765 F |   |   |          |   |   |         |   |   |       | 4765 F1 |   |

Figure 13. I<sup>2</sup>C Read Byte Protocol

| S | ADDRESS | W | A | REGISTER | A | S | ADDRESS | R | A | DATA  | A | DATA  | A | <br>DATA  | Ā    | Ρ       |

|---|---------|---|---|----------|---|---|---------|---|---|-------|---|-------|---|-----------|------|---------|

|   | a6:a0   | 0 | 0 | b7:b0    | 0 |   | a6:a0   | 1 | 0 | b7:b0 | 0 | b7:b0 | 0 | <br>b7:b0 | 1    |         |

|   |         |   |   |          |   |   |         |   |   |       |   |       |   |           | 2947 | 765 F14 |

- FROM MASTER TO SLAVE FROM SLAVE TO MASTER A: ACKNOWLEDGE (LOW) Ā: NOT-ACKNOWLEDGE (HIGH) R: READ BIT (HIGH) W: WRITE BIT (LOW)

- S: START CONDITION P: STOP CONDITION

byte(s) and the LTC2947-65 acknowledges and writes the data into the selected internal register. The register address pointer will automatically increment by one as each byte is acknowledged. The write operation terminates and the register address pointer resets to 0x00 when the master sends a STOP condition.

### **Read Protocol**

The master begins a read operation with a START condition followed by the 7-bit slave address with the  $R/\overline{W}$  bit set to zero. If the slave address matches the address programmed at its AD0/AD1 pins, the LTC2947-65 acknowledges and the master sends a register address byte that indicates which internal register the master wishes to read. The LTC2947-65 acknowledges again and latches the register address byte into its internal register address pointer. The master then sends a repeated START condition followed by the same 7-bit address with the  $R/\overline{W}$  bit now set to 1. The LTC2947-65 acknowledges one more time and then sends the contents of the requested register. If the master acknowledges, the LTC2947-65 will increment the register address pointer and send the contents of the next register, and send out data bytes. The read operation terminates and the register address pointer resets to 00h when the master sends a STOP condition.

| s | ALERT RESPONSE<br>ADDRESS | R | A | DEVICE<br>Address | W | Ā | Р |

|---|---------------------------|---|---|-------------------|---|---|---|

|   | 0001100                   | 1 | 0 | a6:a0             | 0 | 1 |   |

Figure 15. Serial Bus I<sup>2</sup>C Alert Response Protocol

### **SMBus Alert Response Protocol**

The LTC2947-65 uses the SMBus alert response protocol (ARA) to manage alerts in I<sup>2</sup>C mode. To enable alerts, set the ALERTBEN bit in the Alert Master Control Enable register (0xE8)[0]—this is the default setting. Select which events trigger alerts by clearing bits in the Alert Mask registers (addresses 0x88 to 0x8F).

If two or more devices on the same bus are generating alerts when the ARA is broadcasted, standard  $I^2C$  arbitration causes the device with the highest priority (lowest address) to reply first and the device with the lowest priority (highest address) to reply last. The bus master will repeat the alert response protocol until the ALERT line is released. Once the device causing the alert is identified, the master may read the Status, Threshold and Overflow Alert registers (0x80 to 0x87) to determine what caused the fault. In SPI mode, reading the Status or Alert registers will release the ALERT pin. In  $I^2C$  mode, the ALERT pin is released using the SMBus ARA protocol; reading the Status or Alert registers.

## **REGISTER MAP**

The LTC2947-65 is configured and communicates with the host system through its internal registers, addressed via the serial interface. There are a total of 496 register addresses arranged as two 256-byte pages in the LTC2947-65 register map, not all of which are used (Figure 16).

In order to facilitate the embedding of the LTC2947-65 into a system, C/C++ code examples targeting the

Linduino, Analog Devices' Arduino compatible development platform, are available at the LTC2947-65's Linduino Sketch Web page.

The headers provide register address definitions, register bit mask definitions, LSB values for RAW quantities, PRE/ DIV calculation from external oscillator frequencies, and LSB values for accumulated quantities depending on user defined PRE/DIV values.

|              |        |           |        |          |           |           |                  | OFFSE       | T         |           |           |           |             |           |          |            |

|--------------|--------|-----------|--------|----------|-----------|-----------|------------------|-------------|-----------|-----------|-----------|-----------|-------------|-----------|----------|------------|

|              | 0      | 1         | 2      | 3        | 4         | 5         | 6                | 7           | 8         | 9         | Α         | В         | С           | D         | E        | F          |

| BASE         |        |           |        |          |           |           |                  | P           | AGE 0     |           | ·         |           |             |           |          |            |

| 0x00         |        |           | C1[4   | 47:0]    |           |           |                  |             | E1[47:    | 0]        |           |           |             | TB        | I[31:0]  |            |

| 0x10         |        |           | C2[4   | 47:0]    |           |           |                  |             | E2[47:    | 0]        |           |           | TB2[31:0]   |           |          |            |

| 0x20         |        |           |        |          |           |           |                  |             |           |           |           |           |             |           |          |            |

| 0x30         |        |           |        |          |           |           |                  |             |           |           |           |           |             |           |          |            |

| 0x40         | IMAX[  |           |        | I[15:0]  |           | X[15:0]   |                  | 1IN[15:0]   |           |           |           |           |             |           |          |            |

| 0x50         | VMAX[  | 15:0]     | VMIN   | N[15:0]  | TEMPN     | MAX[15:0] | TEM              | PMIN[15:0]  | VDVCCM    | X[15:0]   | VDVCCN    | IIN[15:0] |             |           |          |            |

| 0x60         |        |           |        |          |           |           |                  | GPIOSTATCTL |           |           |           |           |             |           |          |            |

| 0x70         |        |           |        |          |           |           |                  |             |           |           |           |           |             |           |          |            |

| 0x80         | STATUS | STATVT    | STATIP | STATC    | STATE     | STATCEOF  | STATTB           | STATVDVCC   | STATUSM   | STATVTM   | STATIPM   | STATCM    | STATEM      | STATCEOFM | STATTBM  | STATVDVCCM |

| 0x90         |        | I[23:0]   |        |          | P[23:0]   |           |                  |             |           |           |           |           |             |           |          |            |

| 0xA0         | V[15   | i:0]      | TEMF   | P[15:0]  | VDVC      | C[15:0]   |                  |             |           |           |           |           |             |           |          |            |

| 0xB0         |        | IH1[23:0] |        |          | IH2[23:0] |           | IH3[23:0] IH4[23 |             |           |           | IH4[23:0] |           |             | IH5[23:0] |          |            |

| 0xC0         |        |           |        |          |           |           |                  |             |           |           |           |           |             |           |          |            |

| 0xD0         |        |           |        |          |           |           |                  |             |           |           |           |           |             |           |          |            |

| 0xE0         |        | ACCICTL   |        | ACCGPCTL | ACCIDB    |           |                  |             | ALERTBCTL | TBCTL     |           |           |             |           |          |            |

| 0xF0         | OPCTL  |           |        |          |           |           |                  |             |           |           |           |           |             |           |          | PGCTL      |

|              |        |           |        |          |           |           |                  | P           | AGE 1     |           |           |           |             |           |          |            |

| 0x00         |        |           |        | [47:0]   |           |           | C1TL[47:0]       |             |           |           |           |           |             | TB11      | [H[31:0] |            |

| 0x10         |        |           |        | [47:0]   |           |           | E1TL[47:0]       |             |           |           |           |           |             |           |          |            |

| 0x20         |        |           |        | [47:0]   |           |           | C2TL[47:0]       |             |           |           |           |           | TB2TH[31:0] |           |          |            |

| 0x30         |        |           | E2TH   | [47:0]   |           | 1         |                  | Г           | E2TL[47   | ':0]<br>I |           |           | <u> </u>    |           |          |            |

| 0x40         |        |           |        |          |           |           |                  |             |           |           |           |           |             |           |          |            |

| 0x50         |        |           |        |          |           |           |                  |             |           |           |           |           |             |           |          |            |

| 0x60         |        |           |        |          |           |           |                  |             |           |           |           |           |             |           |          |            |

| 0x70         | 171164 | 5-01      | 1711   | 15.01    | DTU       | 1645-01   |                  |             |           |           |           |           |             |           |          |            |

| 0x80         | ITH[1  |           |        | [15:0]   |           | [15:0]    |                  | [L[15:0]    |           |           | 100100-0  |           |             |           |          |            |

| 0x90         | VTH[1  | 5:0]      | VTL    | [15:0]   | TEMP      | TH[15:0]  | TEN              | IPTL[15:0]  | VDVCCT    | H[15:0]   | VDVCC     | [L[15:0]  | TEMPF       | ANH[15:0] | ТЕМР     | FANL[15:0] |

| 0xA0         |        |           |        |          |           |           |                  |             |           |           |           |           |             |           |          |            |

| 0xB0         |        |           |        |          |           |           |                  |             |           |           |           |           |             |           |          |            |

| 0xC0<br>0xD0 |        |           |        |          |           |           |                  |             |           |           |           |           |             |           |          |            |

| 0xD0<br>0xE0 |        |           |        |          |           |           |                  |             |           |           |           |           |             |           |          |            |

| 0xE0<br>0xF0 | OPCTL  |           |        |          |           |           |                  |             |           |           |           |           |             |           |          | PGCTL      |

| UXFU         | 0      | 1         | 2      | 3        | 4         | 5         | 6                | 7           | 8         | 9         | A         | В         | С           | D         | E        | F          |

|              | 0      | 1         | 2      | 5        | 4         | 5         | 0                | /<br>0FFSE  |           | 3         | А         | 0         | U           | 0         |          | -          |

Figure 16. Register Map

### **REGISTER NAMING CONVENTIONS**

- RW Read-Write

- RO Read Only

- COR Clear on Read

- DEF Default Value

- SI Signed Integer

- UI Unsigned Integer

### PAGING MECHANISM

The memory map of the LTC2947-65 is organized into two pages, PAGE0 and PAGE1. PAGE0 contains all quantity, control and status registers while PAGE1 contains all threshold registers. Each page has a register address space ranging from 0x00 to 0xEF, with each register consisting of one 8-bit byte of data. Multiple-byte data is stored with most significant byte at the lowest address (little-endian). For instance, the MSB C1[47:40] of the quantity C1 is stored at address 0x00 in PAGE0.

Some addresses in the register map are not used and are reserved. Bits in non-reserved registers that are not explicitly described are also reserved. Writing to unused reserved registers or reserved bits in non-reserved registers may result in unwanted behavior of the LTC2947-65; writing 0 to reserved bits in non-reserved registers is allowed. Reading of unused registers is generally harmless but will return random data.

Addresses in the range 0xF0 to 0xFF are used to control page access and are common to both pages. These registers (0PCTL (0xF0) and PGCTL (0XFF)) must be written with single byte transactions. Do not write as part of a multiple-byte write.