LTC3035

<sup>7</sup> 300mA VLDO Linear Regulator with Charge Pump Bias Generator

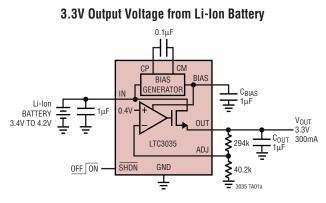

The LTC<sup>®</sup>3035 is a micropower, VLDO<sup>™</sup> (very low drop-

out) linear regulator which operates from input voltages as low as 1.7V. The device is capable of supplying 300mA of

output current with a typical dropout voltage of only

45mV. To allow operation at low input voltages the LTC3035

includes a charge pump generator that provides the nec-

essary bias voltage for the internal LDO circuitry. Output

current comes directly from the input supply for high

efficiency regulation. The charge pump bias generator

requires only a  $0.1\mu$ F flying capacitor and a  $1\mu$ F bypass

capacitor for operation. The low 0.4V internal reference

voltage allows the LTC3035 to be programmed to much

lower output voltages than commonly available in LDOs.

The output voltage is programmed via two tiny SMD resistors. The LTC3035's low guiescent current makes it

Other features include high output voltage accuracy, excellent transient response, stability with ultralow ESR

ceramic capacitors as small as 1µF, short-circuit and

thermal overload protection, output current limiting and

reverse output current protection. The LTC3035 is avail-

able in a tiny, low profile  $(3mm \times 2mm \times 0.75mm)$  8-lead

T, LTC and LT are registered trademarks of Linear Technology Corporation.

VLDO is a trademark of Linear Technology Corporation.

All other trademarks are the property of their respective owners.

Protected by U.S. Patents, including 6411531, others pending.

an ideal choice for use in battery-powered systems.

DESCRIPTION

DFN package.

## FEATURES

- Wide Input Voltage Range: 1.7V to 5.5V

- Wide Adjustable Output Voltage Range: 0.4V to 3.6V

- Built-In Charge Pump Generates High Side Bias

- Very Low Dropout: 45mV at 300mA

- ±2% Voltage Accuracy Over Temperature, Supply, Load

- Fast Transient Recovery

- Low Operating Current: I<sub>IN</sub> = 100µA Typ

- Low Shutdown Current:  $I_{IN} = 1\mu A Typ$

- Stable with Ceramic Capacitor Down to 1µF

- Output Current Limit

- Thermal Overload Protected

- Reverse Output Current Protected

- Available in 8-Lead (3mm × 2mm) DFN Package

# **APPLICATIONS**

- Li-Ion to 3.3V Low Dropout Supplies

- 2 × AA to 1.8V Low Dropout Supplies

- Low Power Handheld Devices

- Low Voltage Logic Supplies

- DSP Power Supplies

- Cellular Phones

- Portable Electronic Equipment

- Handheld Medical Instruments

- Post Regulator for Switching Supply Noise Rejection

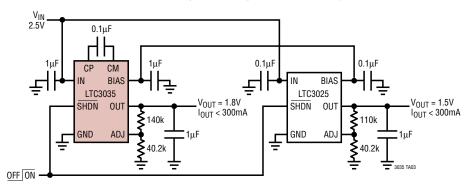

### **TYPICAL APPLICATION**

#### **LINEAR** TECHNOLOGY

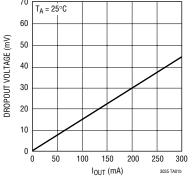

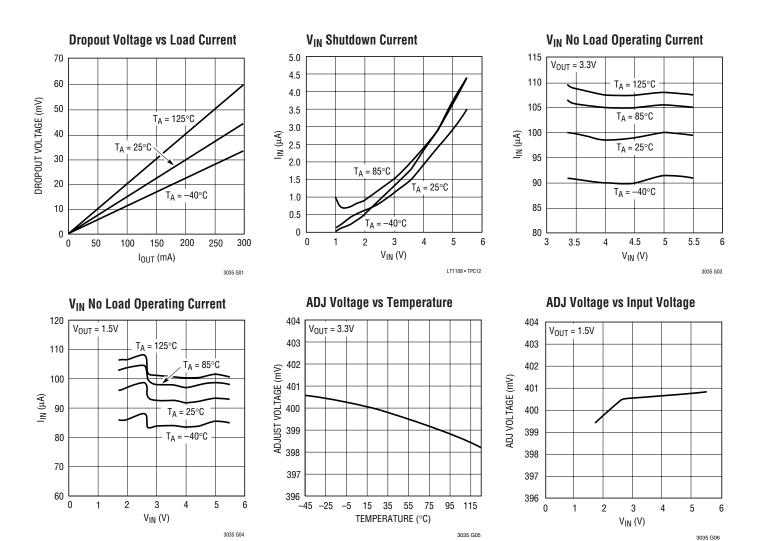

# Dropout Voltage vs Load Current

3035f

# **ABSOLUTE MAXIMUM RATINGS**

(Notes 1, 2)

| V <sub>IN</sub> to GND         | 0.3V to 6V    |

|--------------------------------|---------------|

| SHDN to GND                    | 0.3V to 6V    |

| CP, CM, BIAS to GND            | 0.3V to 6V    |

| ADJ to GND                     | 0.3V to 6V    |

| V <sub>OUT</sub> to GND        | 0.3V to 6V    |

| Operating Junction Temperature |               |

| (Note 3)                       | 40°C to 125°C |

| Storage Temperature Range      | 65°C to 125°C |

| Output Short Circuit Duration  | Indefinite    |

|                                |               |

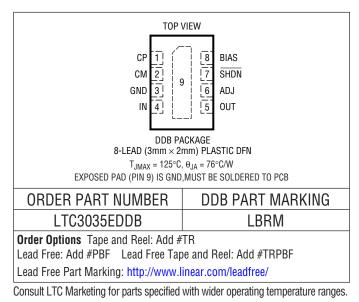

# PACKAGE/ORDER INFORMATION

### **ELECTRICAL CHARACTERISTICS** The • denotes specifications which apply over the full specified temperature

range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{IN} = 3.6V$ ,  $V_{OUT} = 3.3V$ ,  $C_{FLY} = 0.1\mu$ F,  $C_{OUT} = 1\mu$ F,  $C_{IN} = 1\mu$ F,  $C_{BIAS} = 1\mu$ F (all capacitors ceramic) unless otherwise noted.

| PARAMETER                                                                          | CONDITIONS                                                                                                                                                          |   | MIN                           | ТҮР                         | MAX                           | UNITS  |

|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------------------------|-----------------------------|-------------------------------|--------|

| V <sub>IN</sub> Operating Voltage (Note 4)                                         |                                                                                                                                                                     |   | 1.7                           |                             | 5.5                           | V      |

| V <sub>BIAS</sub> Output Voltage Range                                             | $\begin{array}{c} 2.63V \leq V_{IN} \leq 5.5V \\ 1.7V \leq V_{IN} \leq 2.63V \end{array} \hspace{1.5cm} \bullet$                                                    |   | 4.8<br>1.85 • V <sub>IN</sub> | 5<br>1.90 • V <sub>IN</sub> | 5.3<br>1.95 • V <sub>IN</sub> | V<br>V |

| V <sub>OUT</sub> Output Voltage Range                                              |                                                                                                                                                                     |   | V <sub>ADJ</sub>              |                             | 3.6                           | V      |

| V <sub>IN</sub> Operating Current                                                  | I <sub>OUT</sub> = 10μA                                                                                                                                             |   |                               | 100                         | 200                           | μA     |

| V <sub>IN</sub> Shutdown Current                                                   | V <sub>SHDN</sub> = 0V                                                                                                                                              |   |                               | 1                           | 5                             | μA     |

| V <sub>ADJ</sub> Regulation Voltage (Note 5)                                       | on Voltage (Note 5) $ \begin{array}{c} 1mA \leq I_{OUT} \leq 300mA, \ 1.7V \leq V_{IN} \leq 5.5V, \\ V_{OUT} = 1.5V \end{array} \right) \bullet \label{eq:Voltage}$ |   | 0.392                         | 0.4                         | 0.408                         | V      |

| I <sub>ADJ</sub> ADJ Input Current                                                 | $V_{ADJ} = 0.4V$                                                                                                                                                    |   | -50                           | 0                           | 50                            | nA     |

| OUT Load Regulation (Referred to ADJ Pin) I <sub>OUT</sub> = 1mA to 300mA          |                                                                                                                                                                     |   |                               | -0.2                        |                               | mV     |

| Dropout Voltage (Note 6)                                                           | V <sub>IN</sub> = 1.7V, V <sub>ADJ</sub> = 0.37V, I <sub>OUT</sub> = 300mA                                                                                          | • |                               | 45                          | 100                           | mV     |

| I <sub>OUT</sub> Continuous Output Current                                         |                                                                                                                                                                     |   | 300                           |                             |                               | mA     |

| I <sub>OUT</sub> Short Circuit Output Current                                      | $V_{ADJ} = V_{OUT} = 0$                                                                                                                                             |   |                               | 760                         |                               | mA     |

| V <sub>OUT</sub> Output Noise Voltage F = 10Hz to 100kHz, I <sub>OUT</sub> = 150mA |                                                                                                                                                                     |   | 150                           |                             | μVrms                         |        |

| V <sub>IH</sub> SHDN Input High Voltage                                            |                                                                                                                                                                     | • | 1.1                           |                             |                               | V      |

| V <sub>IL</sub> SHDN Input Low Voltage                                             |                                                                                                                                                                     |   |                               |                             | 0.3                           | V      |

| I <sub>IH</sub> SHDN Input High Current                                            | $\overline{SHDN} = V_{IN}$                                                                                                                                          |   | -1                            |                             | 1                             | μA     |

| I <sub>IL</sub> SHDN Input Low Current                                             | SHDN = 0V                                                                                                                                                           |   | -1                            |                             | 1                             | μA     |

Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 125°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

Note 3: The LTC3035 regulator is tested and specified under pulse load conditions such that  $T_J \approx T_A$ . The LTC3035 is 100% production tested at 25°C. Performance at -40°C and 125°C is assured by design, characterization and correlation with statistical process control. Note 4: Min Operating Input Voltage required for regulation is:

$V_{IN} \ge V_{OUT} + V_{DROPOUT}$  and  $V_{IN} \ge 1.7V$

3035f

# **ELECTRICAL CHARACTERISTICS**

**Note 5:** Operating conditions are limited by maximum junction temperature. The regulated output voltage specification will not apply for all possible combinations of input voltage and output current. When operating at maximum input voltage, the output current range must be limited.

**Note 6:** Dropout voltage is minimum input to output voltage differential needed to maintain regulation at a specified output current. In dropout, the output voltage will be equal to  $V_{IN} - V_{DROPOUT}$ .

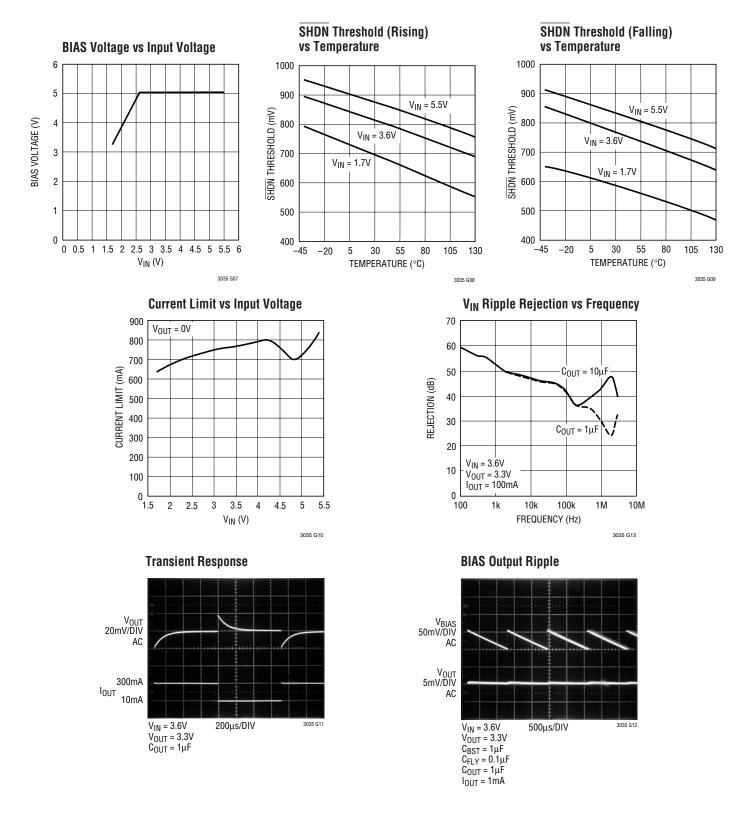

# **TYPICAL PERFORMANCE CHARACTERISTICS**

# **TYPICAL PERFORMANCE CHARACTERISTICS**

3035f

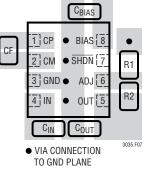

### **PIN FUNCTIONS**

**CP (Pin 1):** Flying Capacitor Positive Terminal.

CM (Pin 2): Flying Capacitor Negative Terminal.

**GND (Pin 3):** Ground. Connect to a ground plane.

**IN (Pin 4):** Input Supply Voltage. The output load current is supplied directly from IN. The IN pin should be locally bypassed to ground if the LTC3035 is more than a few inches away from another source of bulk capacitance. In general, the output impedance of a battery rises with frequency, so it is usually adviseable to include an input bypass capacitor when supplying IN from a battery. A capacitor of  $1\mu$ F is usually sufficient.

**OUT (Pin 5):** Regulated Output Voltage. The OUT pin supplies power to the load. A minimum ceramic output capacitor of at least  $1\mu$ F is required to ensure stability. Larger output capacitors may be required for applications with large transient loads to limit peak voltage transients. See the Applications Information section for more information on output capacitance.

**ADJ (Pin 6):** Adjust Input Pin. This is the input to the error amplifier. The ADJ pin reference voltage is 0.4V referenced to ground. The output voltage range is 0.4V to 3.6V and is set by connecting ADJ to a resistor divider from OUT to GND.

**SHDN** (Pin 7): Shutdown Input, Active Low. This pin is used to put the LTC3035 into shutdown. The SHDN pin current is typically less than 10nA. The SHDN pin cannot be left floating and must be tied to a valid logic level if not used.

**BIAS (Pin 8):** BIAS Output Voltage Pin. BIAS is the output of the charge pump and provides the high side supply for the LTC3035 LDO circuitry. This pin should be locally bypassed to ground by a  $1\mu$ F or greater capacitor as close as possible to the pin. Nothing else should be connected to this pin.

**Exposed Pad (Pin 9):** Ground and Heat Sink. Must be soldered to PCB ground plane or large pad for optimal thermal performance.

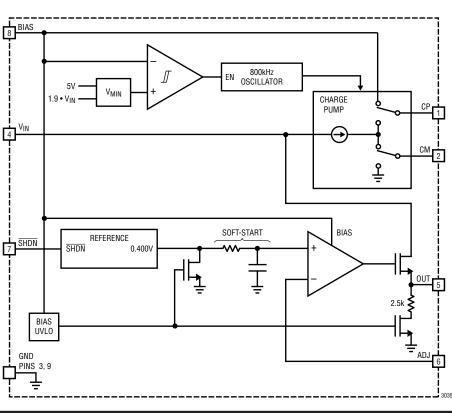

# **BLOCK DIAGRAM**

3035

## **APPLICATIONS INFORMATION** (Refer to Block Diagram)

The LTC3035 is a VLDO (very low dropout) linear regulator which operates from input voltages between 1.7V and 5.5V. The LDO uses an internal NMOS transistor as the pass device in a source-follower configuration. The internal charge pump generator provides the high supply necessary for the LDO circuitry while the output current comes directly from the IN input for high efficiency regulation.

### **Charge Pump Operation**

The LTC3035 contains a charge pump to produce the necessary bias voltage supply for the LDO. The charge pump utilizes Burst Mode operation to achieve high efficiency for the relatively low current levels needed for the LDO circuitry. The charge pump requires only a small  $0.1\mu$ F flying capacitor between the CP and CM pins and a  $1\mu$ F bypass capacitor at BIAS.

An internal oscillator centered at 800kHz controls the two-phase switching cycle of the charge pump. During the first phase a current source charges the flying capacitor between  $V_{IN}$  and GND. During the second phase, the capacitor's positive terminal connects to BIAS and the current source drives the capacitor's minus terminal, delivering charge to the BIAS bypass capacitor and increasing its voltage.

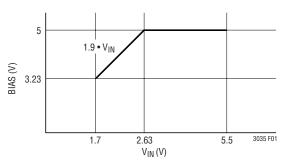

A burst comparator with hysteresis monitors the voltage on the BIAS pin. When BIAS is above the upper threshold of the comparator, the oscillator is disabled and no switching occurs. When BIAS falls below the comparator's lower threshold, the oscillator is enabled and the BIAS pin gets charged. The thresholds of the burst comparator are dynamically adjusted to maintain a DC level shown by Figure 1. BIAS regulates to  $1.9 \cdot V_{\rm IN}$  or 5V, whichever voltage is lower. The voltage ripple at BIAS is controlled to approximately 1% of its DC value.

### LDO Operation

An undervoltage lockout comparator (UVLO) senses the BIAS voltage to ensure that the BIAS supply for the LDO is greater than 90% of its regulation value before enabling the LDO. Once the LDO gets enabled, the UVLO threshold switches to 50% of its regulation value. Thus the BIAS voltage must fall below 50% of its regulation voltage

Figure 1. LTC3035 BIAS Voltage vs  $V_{\text{IN}}$  Voltage

before the LDO disables. When the LDO is disabled, OUT is pulled to GND through the external divider and an internal 2.5k resistor.

The LDO provides a high accuracy output capable of supplying 300mA of output current with a typical dropout voltage of only 45mV. A single ceramic capacitor as small as  $1\mu$ F is all that is required for output bypassing. The low reference voltage allows the LTC3035 output to be programmed from 0.4V to 3.6V.

As shown in the Block Diagram, the charge pump output at BIAS supplies the LDO circuitry while the output current comes directly from the IN input for high efficiency regulation. The low quiescent supply current,  $I_{IN} = 100\mu A$ , drops to  $I_{IN} = 1\mu A$  typical in shutdown making the LTC3035 an ideal choice for use in battery-powered systems.

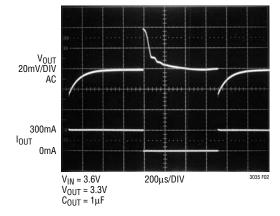

The device also includes current limit, thermal overload protection, and reverse output current protection. The fast transient response of the follower output stage overcomes the traditional tradeoff between dropout voltage, quiescent current and load transient response inherent in most LDO regulator architectures. The LTC3035 also includes overshoot detection circuitry which brings the output back into regulation when going from heavy to light output loads (see Figure 2).

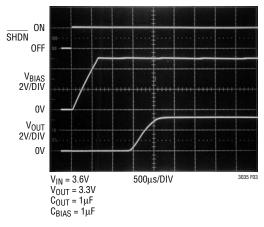

The LTC3035 also includes a soft-start feature to prevent excessive current flow during start-up. After the BIAS voltage reaches regulation, the soft-start circuitry gradually increases the LDO reference voltage from 0V to 0.4V over a period of about  $600\mu s$ . There is a short  $700\mu s$  delay from the time BIAS reaches regulation until the LDO output starts to rise (see Figure 3).

### **APPLICATIONS INFORMATION**

Figure 2. Output Step Response

Figure 3. Bias and Output Start-Up Waveforms

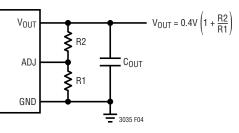

#### Adjustable Output Voltage

The output voltage is set by the ratio of two external resistors as shown in Figure 4. The device servos the output to maintain the ADJ pin voltage at 0.4V (referenced to ground). Thus the current in R1 is equal to 0.4V/R1. For good transient response, stability and accuracy the current in R1 should be at least  $8\mu$ A, thus the value of R1 should be no greater than 50k. The current in R2 is the current in R1 plus the ADJ pin bias current. Since the ADJ pin bias current is typically <10nA it can be ignored in the output voltage calculation. The output voltage can be calculated using the formula in Figure 4. Note that in shutdown the output is turned off and the divider current will be zero once C<sub>OUT</sub> is discharged.

The LTC3035 operates at a relatively high gain of  $-0.7 \mu V/mA$  referred to the ADJ input. Thus a load

Figure 4. Programming the LTC3035

current change of 1mA to 300mA produces a -0.2mV drop at the ADJ input. To calculate the change refered to the output simply multiply by the gain of the feedback network (i.e., 1 + R2/R1). For example, to program the output for 3.3V choose R2/R1 = 7.25. In this example an output current change of 1mA to 300mA produces  $-0.2mV \cdot (1 + 7.25) = 1.65mV$  drop at the output.

#### **Output Capacitance and Transient Response**

The LTC3035 is designed to be stable with a wide range of ceramic output capacitors. The ESR of the output capacitor affects stability, most notably with small capacitors. An output capacitor of  $1\mu$ F or greater with an ESR of  $0.05\Omega$  or less is recommended to ensure stability. The LTC3035 is a micropower device and output transient response will be a function of output capacitance. Larger values of output capacitance decrease the peak deviations and provide improved transient response for larger load current changes. Note that bypass capacitors used to decouple individual components powered by the LTC3035 will increase the effective output capacitor value. High ESR tantalum and electrolytic capacitors may be used, but a low ESR ceramic capacitor must be in parallel at the output. There is no minimum ESR or maximum capacitor size requirements.

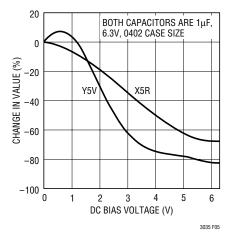

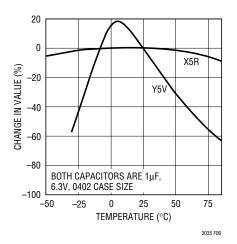

Extra consideration must be given to the use of ceramic capacitors. Ceramic capacitors are manufactured with a variety of dielectrics, each with different behavior across temperature and applied voltage. The most common dielectrics used are Z5U, Y5V, X5R and X7R. The Z5U and Y5V dielectrics are good for providing high capacitances in a small package, but exhibit strong voltage and temperature coefficients as shown in Figures 5 and 6. When used with a 3.3V regulator, a 1 $\mu$ F Y5V capacitor can lose as much as 80% of its rated capacitance over the operating

# **APPLICATIONS INFORMATION**

Figure 5. Ceramic Capacitor DC Bias Characteristics

Figure 6. Ceramic Capacitor Temperature Characteristics

temperature range. The X5R only loses about 40% of its rated capacitance over the operating temperature range. The X5R and X7R dielectrics result in more stable characteristics and are more suitable for use as the output capacitor. The X7R type has better stability across temperature and bias voltage, while the X5R is less expensive and is available in higher values. In all cases, the output capacitance should never drop below  $0.4\mu$ F, or instability or degraded performance may occur.

#### **Charge Pump Component Selection**

The flying capacitor controls the strength of the charge pump. In order for the charge pump to deliver its maximum

available current, a  $0.1\mu$ F or greater ceramic capacitor should be used. Warning: A polarized capacitor such as tantalum or aluminum should never be used for the flying capacitor since its voltage can reverse upon start-up of the LTC3035. Low ESR ceramic capacitors should always be used for the flying capacitor.

A 1 $\mu$ F or greater low ESR (<0.1 $\Omega$ ) ceramic capacitor is recommended to bypass the BIAS pin. Larger values of capacitance will not reduce the size of the BIAS ripple much, but will decrease the ripple frequency proportionally. The BIAS pin should maintain 0.4 $\mu$ F of capacitance at all times to ensure correct operation. High ESR tantalum and electrolytic capacitors may be used, but a low ESR ceramic must be used in parallel for correct operation. It is also recommended that IN be bypassed to ground with a 1 $\mu$ F or greater ceramic capacitor.

#### **Thermal Considerations**

The power handling capability of the device will be limited by the maximum rated junction temperature (125°C). The power dissipated by the device will be the output current multiplied by the input/output voltage differential:

$(I_{OUT})(V_{IN} - V_{OUT})$

The LTC3035 has internal thermal limiting designed to protect the device during momentary overload conditions. For continuous normal conditions, the maximum junction temperature rating of 125°C must not be exceeded. It is important to give careful consideration to all sources of thermal resistance from junction to ambient. Additional heat sources mounted nearby must also be considered.

For surface mount devices, heat sinking is accomplished by using the heat-spreading capabilities of the PC board and its copper traces. Copper board stiffeners and plated through holes can also be used to spread the heat generated by power devices.

A junction to ambient thermal coefficient of 76°C/W is achieved by connecting the Exposed Pad of the DFN package directly to a ground plane of about 2500mm<sup>2</sup>.

# OPERATION

#### **Calculating Junction Temperature**

Example: Given an output voltage of 1.5V, an input voltage of 1.8V to 3V, an output current range of 0mA to 100mA and a maximum ambient temperature of 50°C, what will the maximum junction temperature be?

The power dissipated by the device will be approximately:

$I_{OUT(MAX)}(V_{IN(MAX)} - V_{OUT})$

where:

```

I_{OUT(MAX)} = 100 \text{mA}

```

$V_{IN(MAX)} = 3V$

S0:

P = 100 mA(3V - 1.5V) = 0.15W

Even under worst-case conditions LTC3035's BIAS pin power dissipation is only about 1mW, thus can be ignored. The junction to ambient thermal resistance will be on the order of 76°C/W. The junction temperature rise above ambient will be approximately equal to:

$0.15W(76^{\circ}C/W) = 11.4^{\circ}C$

The maximum junction temperature will then be equal to the maximum junction temperature rise above ambient plus the maximum ambient temperature or:

$T = 50^{\circ}C + 11.4^{\circ}C = 61.4^{\circ}C$

#### Short-Circuit/Thermal Protection

The LTC3035 has built-in output short-circuit current limiting as well as over temperature protection. During short-circuit conditions, internal circuitry automatically limits the output current to approximately 760mA. At higher temperatures, or in cases where internal power dissipation causes excessive self heating on chip, the thermal shutdown circuitry will shut down the charge pump and LDO when the junction temperature exceeds approximately 155°C. It will reenable the converter and LDO once the junction temperature drops back to approximately 140°C. The LTC3035 will cycle in and out of thermal shutdown without latch-up or damage until the overstress condition is removed. Long term overstress  $(T_J>125^{\circ}C)$  should be avoided as it can degrade the performance or shorten the life of the part.

#### **Layout Considerations**

Connection from the BIAS and OUT pins to their respective ceramic bypass capacitor should be kept as short as possible. The ground side of the bypass capacitors should be connected directly to the ground plane for best results or through short traces back to the GND pin of the part. Long traces will increase the effective series ESR and inductance of the capacitor which can degrade performance.

The CP and CM pins of the charge pump are switching nodes. The transition edge rates of these pins can be quite fast (~10ns). Thus care must be taken to make sure these nodes do not couple capacitively to other nodes (especially the ADJ pin). Place the flying capacitor as close as possible to the CP and CM pins for optimum charge pump performance.

Because the ADJ pin is relatively high impedance (depending on the resistor divider used), stray capacitance at this pin should be minimized (<10pF) to prevent phase shift in the error amplifier loop. Additional special attention should be given to any stray capacitances that can couple external signals onto the ADJ pin producing undesirable output ripple. For optimum performance connect the ADJ pin to R1 and R2 with a short PCB trace and minimize all other stray capacitance to the ADJ pin. Figure 7 shows an example layout for the LTC3035.

Figure 7. Suggested Layout

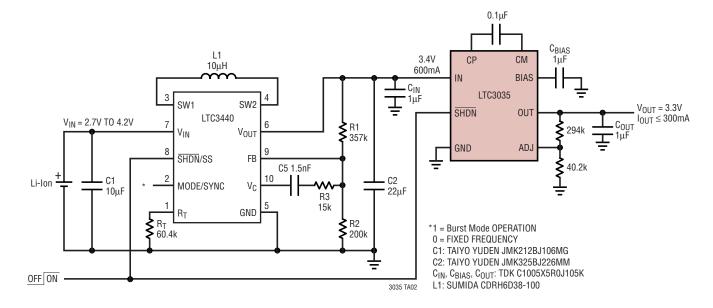

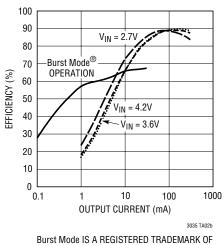

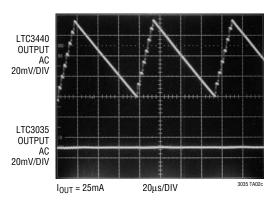

## **TYPICAL APPLICATION**

#### Low Noise Li-Ion to 3.3V Supply

**Efficiency vs Output Current**

Burst Mode IS A REGISTERED TRADEMARK C LINEAR TECHNOLOGY CORPORATION

**Ripple Rejection**

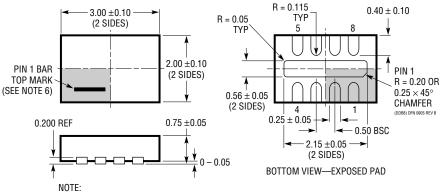

### PACKAGE DESCRIPTION

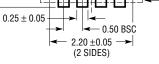

8-Lead Plastic DFN (3mm × 2mm) (Reference LTC DWG # 05-08-1702 Rev B)  $0.61 \pm 0.05$ (2 SIDES) 0.70 ±0.05 2.55 ±0.05  $1.15\pm\!0.05$ \_\_\_ ¥ PACKAGE

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS

**DDB Package**

OUTLINE

1. DRAWING CONFORMS TO VERSION (WECD-1) IN JEDEC PACKAGE OUTLINE M0-229 2. DRAWING NOT TO SCALE

DHAWING NOT TO SCALE

ALL DIMENSIONS ARE IN MILLIMETERS

DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

5. EXPOSED PAD SHALL BE SOLDER PLATED

6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

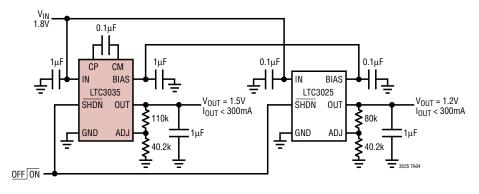

# **TYPICAL APPLICATIONS**

Dual LDO Output (1.8V, 1.5V) from 2.5V Supply Rail

# **RELATED PARTS**

| PART NUMBER          | DESCRIPTION                                   | COMMENTS                                                                                                                                                                                                                                                                                                                        |  |  |

|----------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| LT <sup>®</sup> 1761 | 100mA, Low Noise Micropower, LDO              | $V_{IN}$ : 1.8V to 20V, $V_{OUT(MIN)}$ = 1.22V, $V_{DO}$ = 0.30V, $I_Q$ = 20µA, $I_{SD}$ < 1µA, $V_{OUT}$ = Adj, 1.5V, 1.8V, 2V, 2.5V, 2.8V, 3V, 3.3V, 5V, ThinSOT <sup>™</sup> Package.<br>Low Noise < 20µV <sub>RMSP-P</sub> , Stable with 1µF Ceramic Capacitors                                                             |  |  |

| LT1762               | 150mA, Low Noise Micropower LDO               | $V_{IN}$ : 1.8V to 20V, $V_{OUT(MIN)}$ = 1.22V, $V_{DO}$ = 0.30V, $I_Q$ = 25µA, $I_{SD}$ < 1µA, $V_{OUT}$ = Adj, 2.5V, 3V, 3.3V, 5V, MS8 Package. Low Noise < 20µ $V_{RMSP-P}$                                                                                                                                                  |  |  |

| LT1763               | 500mA, Low Noise Micropower LDO               | $ \begin{array}{l} V_{\text{IN}}\!\!: 1.8V \text{ to } 20V,  V_{\text{OUT}(\text{MIN})} = 1.22V,  V_{\text{DO}} = 0.30V,  I_{\text{Q}} = 30 \mu\text{A},  I_{\text{SD}} < 1 \mu\text{A},  V_{\text{OUT}} = 1.5, \\ 1.8V,  2.5V,  3V,  3.3V,  5V,  \text{S8}  \text{Package. Low Noise} < 20 \mu V_{\text{RMSP-P}} \end{array} $ |  |  |

| LTC1844              | 150mA, Very Low Dropout LDO                   | $V_{IN}$ : 1.6V to 6.5V, $V_{OUT(MIN)}$ = 1.25V, $V_{DO}$ = 0.08V, $I_Q$ = 40µA, $I_{SD}$ < 1µA, $V_{OUT}$ = Adj, 1.5V, 1.8V, 2.5V, 2.8V, 3.3V, ThinSOT Package. Low Noise < 30µV <sub>RMSP-P</sub> , Stable with 1µF Ceramic Capacitors                                                                                        |  |  |

| LT1962               | 300mA, Low Noise Micropower LDO               | $V_{IN}$ : 1.8V to 20V, $V_{OUT(MIN)}$ = 1.22V, $V_{DO}$ = 0.27V, $I_Q$ = 30µA, $I_{SD}$ < 1µA, $V_{OUT}$ = 1.5, 1.8V, 2.5V, 3V, 3.3V, 5V, MS8 Package. Low Noise < 20µ $V_{RMSP-P}$                                                                                                                                            |  |  |

| LT3020               | 100mA, Low Voltage, VLDO                      | $V_{IN}\!\!:$ 0.9V to 10V, $V_{OUT(MIN)}$ = 0.20V, $V_{DO}$ = 0.15V, $I_Q$ = 120µA, $I_{SD}$ < 3µA, $V_{OUT}$ = Adj, DFN, MS8 Package                                                                                                                                                                                           |  |  |

| LTC3025              | 300mA, Micropower VLDO Linear Regulator       | $V_{\text{IN}}$ : 0.9V to 5.5V, $V_{\text{BIAS}}$ : 2.5V to 5.5V, $V_{\text{OUT}(\text{MIN})}$ = 0.4V, $V_{\text{D0}}$ = 0.05V, $I_{\text{Q}}$ = 54µA, $I_{\text{SD}}$ < 1µA, $V_{\text{OUT}}$ = Adj, DFN Package. Stable with 1µF Ceramic Capacitors                                                                           |  |  |

| LTC3026              | 1.5A, Low Input Voltage VLDO Linear Regulator | $V_{\text{IN}}$ : 1.14V to 3.5V (Boost Enabled), 1.14V to 5.5V (External 5V Boost), $V_{\text{OUT}(\text{MIN})} = 0.4V, V_{\text{D0}} = 0.15V, I_{\text{Q}} = 400 \mu\text{A}, I_{\text{SD}} < 1 \mu\text{A}, V_{\text{OUT}} = \text{Adj},$ DFN, MSOP Packages. Stable with 10 $\mu$ F Ceramic Capacitors                       |  |  |

ThinSOT is a trademark of Linear Technology Corporation.

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for LDO Voltage Regulators category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below :

AP7363-SP-13 L79M05TL-E TCR3DF185,LM(CT TCR3DF24,LM(CT TCR3DF285,LM(CT TCR3DF31,LM(CT TCR3DF45,LM(CT MP2013GQ-33-Z 059985X NCP4687DH15T1G 701326R TCR2EN28,LF(S NCV8170AXV250T2G TCR3DF27,LM(CT TCR3DF19,LM(CT TCR3DF125,LM(CT TCR2EN18,LF(S AP2112R5A-3.3TRG1 AP7315-25W5-7 IFX30081LDVGRNXUMA1 NCV47411PAAJR2G AP2113KTR-G1 AP2111H-1.2TRG1 ZLD01117QK50TC AZ1117IH-1.8TRG1 AZ1117ID-ADJTRG1 TCR3DG12,LF MIC5514-3.3YMT-T5 MIC5512-1.2YMT-T5 MIC5317-2.8YM5-T5 SCD7912BTG NCP154MX180270TAG SCD33269T-5.0G NCV8170BMX330TCG NCV8170AMX120TCG NCP706ABMX300TAG NCP153MX330180TCG NCP114BMX075TCG MC33269T-3.5G CAT6243-ADJCMT5T TCR3DG33,LF AP2127N-1.0TRG1 TCR4DG35,LF LT1117CST-3.3 TAR5S15U(TE85L,F) TCR3UG19A,LF TCR4DG105,LF NCV8170AMX360TCG MIC94310-NYMT-T5