## **FEATURES**

- V<sub>IN</sub> Range: 1.8V to 5.5V, 500mV After Start-Up

- Output Voltage Range: 2.2V to 15V

- 800mA Output Current for V<sub>IN</sub> = 5V and V<sub>OUT</sub> = 12V

- Output Disconnects from Input When Shut Down

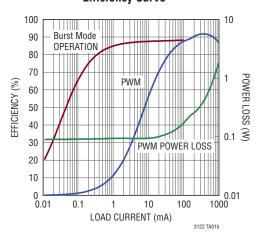

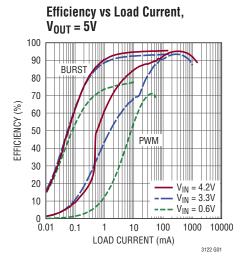

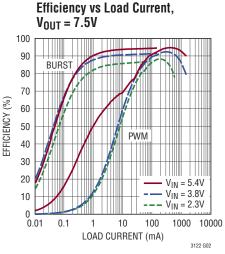

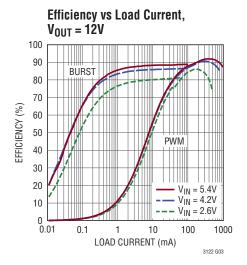

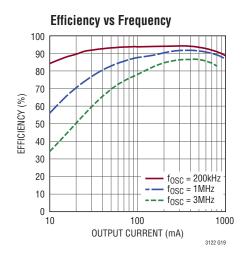

- Synchronous Rectification: Up to 95% Efficiency

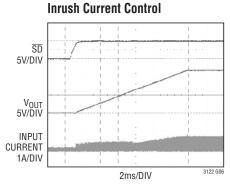

- Inrush Current Limit

- Up to 3MHz Adjustable Switching Frequency Synchronizable to External Clock

- Selectable Burst Mode® Operation: 25µA I<sub>O</sub>

- Output Overvoltage Protection

- Soft-Start

- $<1\mu$ A I<sub>Q</sub> in Shutdown

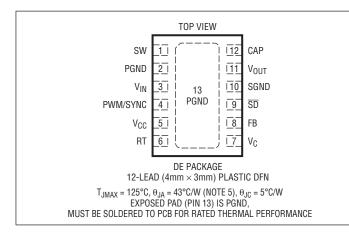

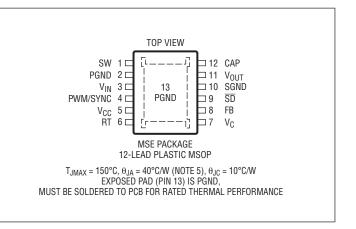

- 12-Lead, 3mm × 4mm × 0.75mm Thermally Enhanced DFN and MSOP Packages

## **APPLICATIONS**

- RF Power

- Piezo Actuators

- Small DC Motors

- 12V Analog Rail From Battery, 5V, or Backup Capacitor

T, LT, LTC, LTM, Linear Technology, the Linear logo and Burst Mode are registered trademarks and ThinSOT is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners.

## 15V, 2.5A Synchronous Step-Up DC/DC Converter with Output Disconnect

## DESCRIPTION

The LTC®3122 is a synchronous step-up DC/DC converter with true output disconnect and inrush current limiting. The 2.5A current limit along with the ability to program output voltages up to 15V makes the LTC3122 well suited for a variety of demanding applications. Once started, operation will continue with inputs down to 500mV, extending runtime in many applications.

The LTC3122 features output disconnect in shutdown, dramatically reducing input power drain and enabling  $V_{OUT}$  to completely discharge. Adjustable PWM switching from 100kHz to 3MHz optimizes applications for highest efficiency or smallest solution footprint. The oscillator can also be synchronized to an external clock for noise sensitive applications. Selectable Burst Mode operation reduces quiescent current to  $25\mu A$ , ensuring high efficiency across the entire load range. An internal soft-start limits inrush current during start-up.

Other features include a <1 $\mu$ A shutdown current and robust protection under short-circuit, thermal overload, and output overvoltage conditions. The LTC3122 is offered in both a low profile 12-lead (3mm × 4mm × 0.75 mm) DFN package and a 12-lead thermally enhanced MSOP package.

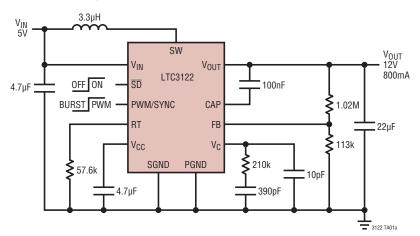

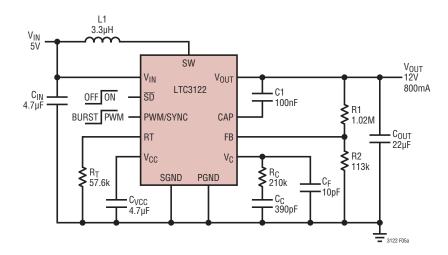

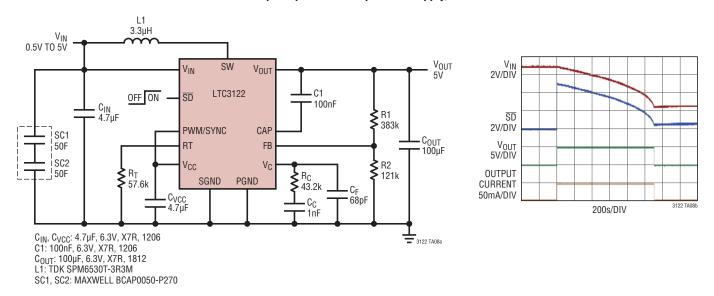

## TYPICAL APPLICATION

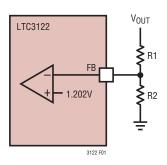

#### 5V to 12V Synchronous Boost Converter with Output Disconnect

#### **Efficiency Curve**

## **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| V <sub>IN</sub> Voltage                      | 0.3V to 6V              |

|----------------------------------------------|-------------------------|

| V <sub>OUT</sub> Voltage                     | 0.3V to 18V             |

| SW Voltage (Note 2)                          | 0.3V to 18V             |

| SW Voltage (Pulsed < 100ns) (Note 2)         | 0.3V to 19V             |

| V <sub>C</sub> , RT Voltage                  | 0.3V to V <sub>CC</sub> |

| CAP Voltage                                  |                         |

| V <sub>OUT</sub> < 5.7V0.3V t                | $0 (V_{OUT} + 0.3V)$    |

| $5.7V \le V_{OUT} \le 11.7V(V_{OUT} - 6V) t$ | $0 (V_{OUT} + 0.3V)$    |

| V <sub>OUT</sub> > 11.7V(V <sub>O</sub>      |                         |

| All Other Pins                    | 0.3V to 6V       |

|-----------------------------------|------------------|

| Operating Junction Temperature Ra | nge (Notes 3, 4) |

| LTC3122E/LTC3122I                 | 40°C to 125°C    |

| LTC3122H                          | 40°C to 150°C    |

| Storage Temperature Range         | 65°C to 150°C    |

| MSE Lead Temperature (Soldering,  | 10sec)300°C      |

## PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|-------------------|---------------|---------------------------------|-------------------|

| LTC3122EDE#PBF   | LTC3122EDE#TRPBF  | 3122          | 12-Lead (4mm × 3mm) Plastic DFN | -40°C to 125°C    |

| LTC3122IDE#PBF   | LTC3122IDE#TRPBF  | 3122          | 12-Lead (4mm × 3mm) Plastic DFN | -40°C to 125°C    |

| LTC3122EMSE#PBF  | LTC3122EMSE#TRPBF | 3122          | 12-Lead Plastic MSOP            | -40°C to 125°C    |

| LTC3122IMSE#PBF  | LTC3122IMSE#TRPBF | 3122          | 12-Lead Plastic MSOP            | -40°C to 125°C    |

| LTC3122HMSE#PBF  | LTC3122HMSE#TRPBF | 3122          | 12-Lead Plastic MSOP            | -40°C to 150°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ (Note 3). $V_{IN} = 3.6V$ , $V_{OUT} = 12V$ , RT = 57.6k unless otherwise noted.

| PARAMETER                               | CONDITIONS                                                                        |   | MIN.                  | TYP      | MAX                 | UNITS                    |

|-----------------------------------------|-----------------------------------------------------------------------------------|---|-----------------------|----------|---------------------|--------------------------|

| Minimum Start-Up Voltage                | $V_{OUT} = 0V$                                                                    | • |                       | 1.7      | 1.8                 | V                        |

| Input Voltage Range                     | After V <sub>OUT</sub> ≥ 2.2V                                                     | • | 0.5                   |          | 5.5                 | V                        |

| Output Voltage Adjust Range             |                                                                                   | • | 2.2                   |          | 15                  | V                        |

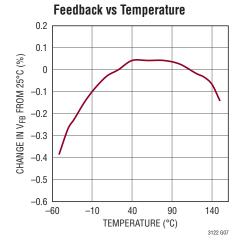

| Feedback Voltage                        |                                                                                   | • | 1.178                 | 1.202    | 1.225               | V                        |

| Feedback Input Current                  | V <sub>FB</sub> = 1.4V                                                            |   |                       | 1        | 50                  | nA                       |

| Quiescent Current, Shutdown             | $V_{\overline{SD}} = 0V$ , $V_{OUT} = 0V$ , Not Including Switch Leakage          |   |                       | 0.01     | 1                   | μА                       |

| Quiescent Current, Active               | $V_C = 0V$ , Measured On $V_{IN}$ , Non-Switching                                 |   |                       | 500      | 700                 | μА                       |

| Quiescent Current, Burst                | Measured on $V_{IN}$ , $V_{FB} > 1.4V$<br>Measured on $V_{OUT}$ , $V_{FB} > 1.4V$ |   |                       | 25<br>10 | 40<br>20            | μ <b>Α</b><br>μ <b>Α</b> |

| N-channel MOSFET Switch Leakage Current | $V_{SW} = 15V$ , $V_{OUT} = 15V$ , $V_{C} = 0V$                                   | • |                       | 0.1      | 30                  | μА                       |

| P-channel MOSFET Switch Leakage Current | $V_{SW} = 0V, V_{OUT} = 15V, V_{\overline{SD}} = 0V$                              | • |                       | 0.1      | 70                  | μА                       |

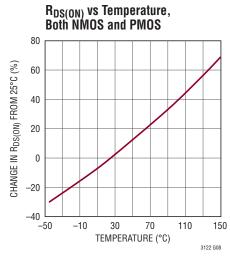

| N-channel MOSFET Switch On-Resistance   |                                                                                   |   |                       | 0.121    |                     | Ω                        |

| P-channel MOSFET Switch On-Resistance   |                                                                                   |   |                       | 0.188    |                     | Ω                        |

| N-channel MOSFET Current Limit          |                                                                                   | • | 2.5                   | 3.5      | 4.5                 | А                        |

| Maximum Duty Cycle                      | V <sub>FB</sub> = 1.0V                                                            | • | 90                    | 94       |                     | %                        |

| Minimum Duty Cycle                      | V <sub>FB</sub> = 1.4V                                                            | • |                       |          | 0                   | %                        |

| Switching Frequency                     |                                                                                   | • | 0.85                  | 1        | 1.15                | MHz                      |

| SYNC Frequency Range                    |                                                                                   | • | 0.1                   |          | 3                   | MHz                      |

| PWM/SYNC Input High                     |                                                                                   | • | 0.9 • V <sub>CC</sub> |          |                     | V                        |

| PWM/SYNC Input Low                      |                                                                                   | • |                       |          | 0.1•V <sub>CC</sub> | V                        |

| PWM/SYNC Input Current                  | V <sub>PWM/SYNC</sub> = 5.5V                                                      |   |                       | 0.01     | 1                   | μА                       |

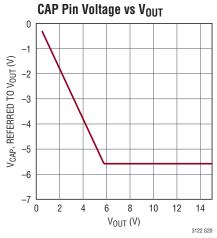

| CAP Clamp Voltage                       | $V_{OUT} > 6.1V$ , Referenced to $V_{OUT}$                                        |   | -5.2                  | -5.6     | -6.0                | V                        |

| V <sub>CC</sub> Regulation Voltage      | V <sub>IN</sub> < 2.8V, V <sub>OUT</sub> > 5V                                     |   | 4                     | 4.25     | 4.5                 | V                        |

| Error Amplifier Transconductance        |                                                                                   | • | 70                    | 95       | 120                 | μS                       |

| Error Amplifier Output Current          |                                                                                   |   |                       | ±25      |                     | μА                       |

| Soft-Start Time                         |                                                                                   |   |                       | 10       |                     | ms                       |

| SD Input High                           |                                                                                   | • | 1.6                   |          |                     | V                        |

| SD Input Low                            |                                                                                   | • |                       |          | 0.25                | V                        |

| SD Input Current                        | $V_{\overline{SD}} = 5.5V$                                                        |   |                       | 1        | 2                   | μА                       |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** Voltage transients on the SW pin beyond the DC limit specified in the Absolute Maximum Ratings are non-disruptive to normal operations when using good layout practices, as shown on the demo board or described in the data sheet or application notes.

**Note 3:** The LTC3122 is tested under pulsed load conditions such that  $T_A \approx T_J$ . The LTC3122E is guaranteed to meet performance specifications from 0°C to 85°C. Specifications over the –40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC3122I is guaranteed to meet specifications over the full –40°C to 125°C operating junction

temperature range. The LTC3122H is guaranteed to meet specifications over the full –40°C to 150°C operating junction range. The junction temperature (T<sub>J</sub> in °C) is calculated from the ambient temperature (T<sub>A</sub> in °C) and power dissipation (P<sub>D</sub> in Watts) according to the formula: T<sub>J</sub> = T<sub>A</sub> + (P<sub>D</sub> •  $\theta_{JA}$ ) where  $\theta_{JA}$  is the thermal impedance of the package.

**Note 4:** The LTC3122 includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 150°C when overtemperature shutdown is active. Continuous operation above the specified maximum operating junction temperature may result in device degradation or failure.

**Note 5:** Failure to solder the exposed backside of the package to the PC board ground plane will result in a thermal impedance much higher than the rated package specifications.

## TYPICAL PERFORMANCE CHARACTERISTICS

Configured as front page application unless otherwise specified.

## TYPICAL PERFORMANCE CHARACTERISTICS

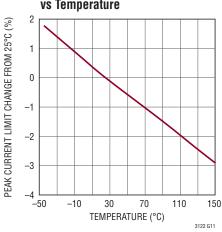

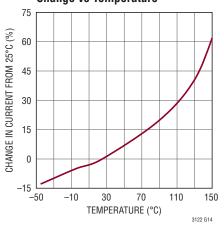

# Peak Current Limit Change vs Temperature

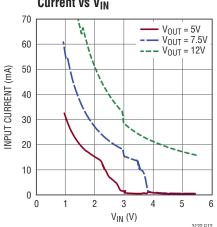

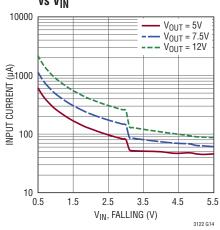

#### PWM Operation No Load Input Current vs V<sub>IN</sub>

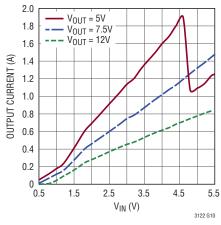

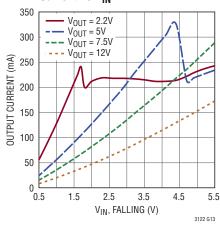

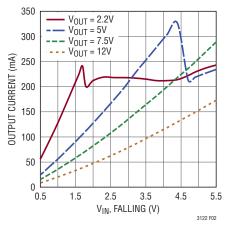

#### Burst Mode Maximum Output Current vs V<sub>IN</sub>

# Burst Mode No Load Input Current vs V<sub>IN</sub>

#### Burst Mode Quiescent Current Change vs Temperature

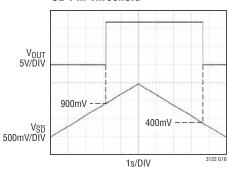

#### SD Pin Threshold

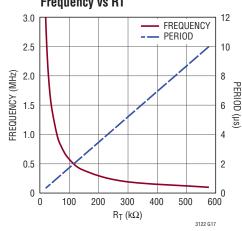

#### Frequency vs RT

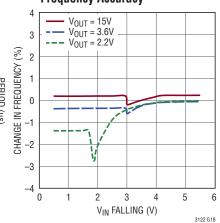

## Frequency Accuracy

## TYPICAL PERFORMANCE CHARACTERISTICS

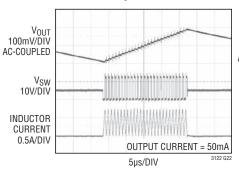

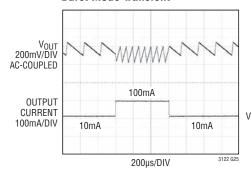

**Burst Mode Operation**

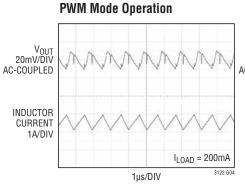

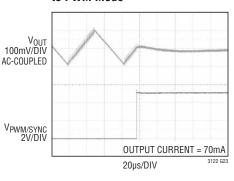

Burst Mode Operation to PWM Mode

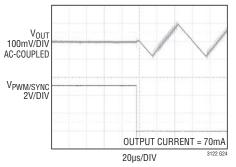

PWM Mode to Burst Mode Operation

**Burst Mode Transient**

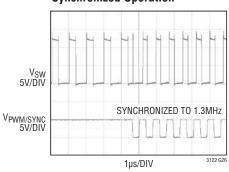

**Synchronized Operation**

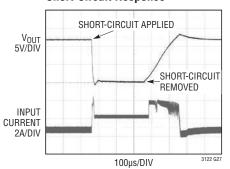

**Short-Circuit Response**

## PIN FUNCTIONS

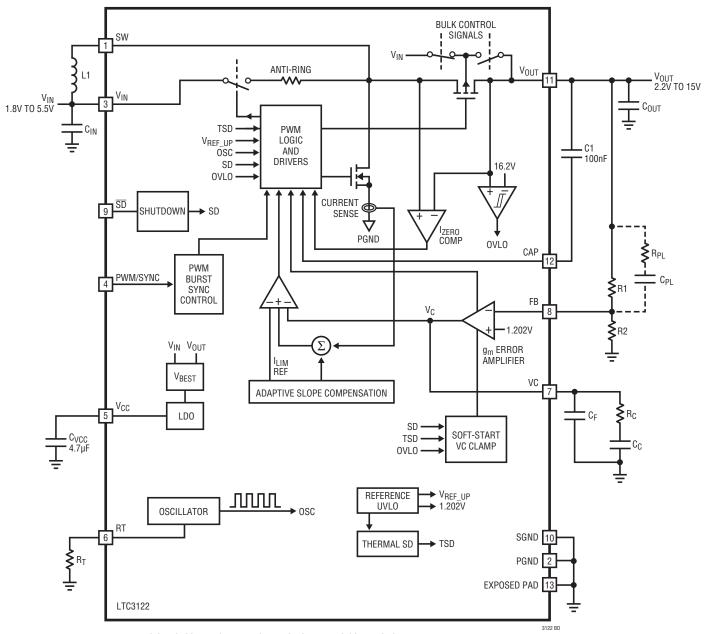

**SW** (**Pin 1**): Switch Pin. Connect an inductor from this pin to  $V_{IN}$ . Keep PCB trace lengths as short and wide as possible to reduce EMI and voltage overshoot. When  $V_{OUT} \ge V_{IN} + 2V$ , an internal anti-ringing resistor is connected between SW and  $V_{IN}$  after the inductor current has dropped to near zero, to minimize EMI. The anti-ringing resistor is also activated in shutdown and during the sleep periods of Burst Mode operation.

**PGND** (Pins 2, 13): Power Ground. When laying out your PCB, provide a short, direct path between PGND and the output capacitor and tie directly to the ground plane. The exposed pad is ground and **must be** soldered to the PCB ground plane for rated thermal performance.

$V_{IN}$  (Pin 3): Input Supply Pin. The device is powered from  $V_{IN}$  unless  $V_{OUT}$  exceeds  $V_{IN}$  and  $V_{IN}$  is less than 3V. Place a low ESR ceramic bypass capacitor of at least  $4.7\mu F$  from  $V_{IN}$  to PGND. X5R and X7R dielectrics are preferred for their superior voltage and temperature characteristics.

**PWM/SYNC (Pin 4):** Burst Mode Operation Select and Oscillator Synchronization. **Do not leave this pin floating.**

- PWM/SYNC = High. Disable Burst Mode Operation and maintain low noise, constant frequency operation.

- PWM/SYNC = Low. The converter operates in Burst Mode operation, independent of load current.

- PWM/SYNC = External CLK. The internal oscillator is synchronized to the external CLK signal. Burst Mode operation is disabled. A clock pulse width between 100ns and 2µs is required to synchronize the oscillator. An external resistor must be connected between RT and GND to program the oscillator slightly below the desired synchronization frequency.

In non-synchronized applications, repeated clocking of the PWM/SYNC pin to affect an operating mode change is supported with these restrictions:

- Boost Mode ( $V_{OUT} > V_{IN}$ ):  $I_{OUT} < 500 \mu A$ :  $f_{PWM/SYNC} \le 100 Hz$ ,  $I_{OUT} \ge 500 \mu A$ :  $f_{PWM/SYNC} \le 5 kHz$

- Buck Mode ( $V_{OUT} < V_{IN}$ ):  $I_{OUT} < 5mA$ :  $f_{PWM/SYNC} \le 5Hz$ ,  $I_{OUT} \ge 5mA$ :  $f_{PWM/SYNC} \le 5kHz$

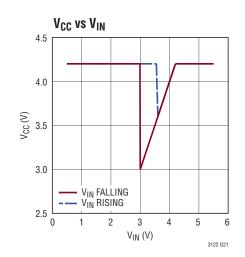

$V_{CC}$  (Pin 5):  $V_{CC}$  Regulator Output. Connect a low-ESR filter capacitor of at least 4.7μF from this pin to GND to provide a regulated rail approximately equal to the lower of  $V_{IN}$  and 4.25V. When  $V_{OUT}$  is higher than  $V_{IN}$ , and  $V_{IN}$  falls below 3V,  $V_{CC}$  will regulate to the lower of approximately  $V_{OUT}$  and 4.25V. A UVLO event occurs if  $V_{CC}$  drops below 1.6V. Switching is inhibited, and a soft-start is initiated when  $V_{CC}$  returns above 1.7V.

**RT (Pin 6):** Frequency Adjust Pin. Connect an external resistor (R<sub>T</sub>) from this pin to SGND to program the oscillator frequency according to the formula:

$$R_T = 57.6/f_{OSC}$$

where  $f_{OSC}$  is in MHz and R<sub>T</sub> is in k $\Omega$ .

**VC (Pin 7):** Error Amplifier Output. A frequency compensation network is connected to this pin to compensate the control loop. See Compensating the Feedback Loop section for guidelines.

**FB** (**Pin 8**): Feedback Input to the Error Amplifier. Connect the resistor divider tap to this pin. Connect the top of the divider to  $V_{OUT}$  and the bottom of the divider to SGND. The output voltage can be adjusted from 2.2V to 15V according to this formula:

$$V_{OUT} = 1.202V \cdot (1 + R1/R2)$$

**SD** (**Pin 9**): Logic Controlled Shutdown Input. Bringing this pin above 1.6V enables normal, free-running operation, forcing this pin below 0.25V shuts the LTC3122 down, with quiescent current below 1μA. **Do not leave this pin floating**.

**SGND** (**Pin 10**): Signal Ground. When laying out a PC board, provide a short, direct path between SGND and the (–) side of the output capacitor.

$V_{OUT}$  (Pin 11): Output Voltage Sense and the Source of the Internal Synchronous Rectifier MOSFET. Driver bias is derived from  $V_{OUT}$ . Connect the output filter capacitor from  $V_{OUT}$  to PGND, as close to the IC as possible. A minimum value of  $10\mu F$  ceramic is recommended.  $V_{OUT}$  is disconnected from  $V_{IN}$  when  $\overline{SD}$  is low.

**CAP (Pin 12):** Serves as the Low Reference for the Synchronous Rectifier Gate Drive. Connect a low ESR filter capacitor (typically 100nF) from this pin to  $V_{OUT}$  to provide an elevated ground rail, approximately 5.6V below  $V_{OUT}$ , used to drive the synchronous rectifier.

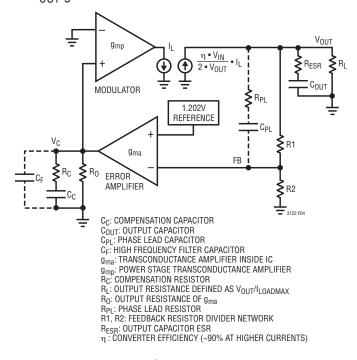

## **BLOCK DIAGRAM**

THE VALUES OF RC, CC, AND CF ARE BASED UPON OPERATING CONDITIONS. PLEASE REFER TO COMPENSATING THE FEEDBACK LOOP SECTION FOR GUIDELINES TO DETERMINE OPTIMAL VALUES OF THESE COMPONENTS.

## **OPERATION**

The LTC3122 is an adjustable frequency, 100kHz to 3MHz synchronous boost converter housed in either a 12-lead 4mm × 3mm DFN or a thermally enhanced MSOP package. The LTC3122 offers the unique ability to start-up and regulate the output from inputs as low as 1.8V and continue to operate from inputs as low as 0.5V. Output voltages can be programmed between 2.2V and 15V. The device also features fixed frequency, current mode PWM control for exceptional line and load regulation. The current mode architecture with adaptive slope compensation provides excellent transient load response and requires minimal output filtering. An internal 10ms closed loop soft-start simplifies the design process while minimizing the number of external components.

With its low R<sub>DS(ON)</sub> and low gate charge internal N-channel MOSFET switch and P-channel MOSFET synchronous rectifier, the LTC3122 achieves high efficiency over a wide range of load current. High efficiency is achieved at light loads when Burst Mode operation is commanded. Operation can be best understood by referring to the Block Diagram.

#### LOW VOLTAGE OPERATION

The LTC3122 is designed to allow start-up from input voltages as low as 1.8V. When  $V_{OUT}$  exceeds 2.2V, the LTC3122 continues to regulate its output, even when  $V_{IN}$  falls to as low as 0.5V. The limiting factors for the application become the availability of the input source to supply sufficient power to the output at the low voltages, and the maximum duty cycle. Note that at low input voltages, small voltage drops due to series resistance become critical and greatly limit the power delivery capability of the converter. This feature extends operating times by maximizing the amount of energy that can be extracted from the input source.

#### LOW NOISE FIXED FREQUENCY OPERATION

#### Soft-Start

The LTC3122 contains internal circuitry to provide closed-loop soft-start operation. The soft-start utilizes a linearly increasing ramp of the error amplifier reference voltage from zero to its nominal value of 1.202V in approximately 10ms, with the internal control loop driving  $V_{OUT}$  from

zero to its final programmed value. This limits the inrush current drawn from the input source. As a result, the duration of the soft-start is largely unaffected by the size of the output capacitor or the output regulation voltage. The closed loop nature of the soft-start allows the converter to respond to load transients that might occur during the soft-start interval. The soft-start period is reset by a shutdown command on  $\overline{SD}$ , a UVLO event on  $V_{CC}$  ( $V_{CC}$  < 1.6V), an overvoltage event on  $V_{OUT}$  ( $V_{OUT} \ge 16.2$ V), or an overtemperature event (thermal shutdown is invoked when the die temperature exceeds 170°C). Upon removal of these fault conditions, the LTC3122 will soft-start the output voltage.

## **Error Amplifier**

The non-inverting input of the transconductance error amplifier is internally connected to the 1.202V reference and the inverting input is connected to FB. An external resistive voltage divider from  $V_{OUT}$  to ground programs the output voltage from 2.2V to 15V via FB as shown in Figure 1.

$$V_{OUT} = 1.202V \left( 1 + \frac{R1}{R2} \right)$$

Selecting an R2 value of  $121k\Omega$  to have approximately  $10\mu A$  of bias current in the  $V_{OUT}$  resistor divider yields the formula:

$$R1 = 100.67 \cdot (V_{OUT} - 1.202V)$$

where R1 is in  $k\Omega$ .

Power converter control loop compensation is set by a simple RC network between  $V_{\text{C}}$  and ground.

Figure 1. Programming the Output Voltage

For more information www.linear.com/LTC3122

/ INFAD

## **OPERATION**

#### **Internal Current Limit**

The current limit comparator shuts off the N-channel MOSFET switch once its threshold is reached. Peak switch current is limited to 3.5A, independent of input or output voltage, except when  $V_{OUT}$  is below 1.5V, resulting in the current limit being approximately half of the nominal peak.

Lossless current sensing converts the peak current signal of the N-channel MOSFET switch into a voltage that is summed with the internal slope compensation. The summed signal is compared to the error amplifier output to provide a peak current control command for the PWM.

## **Zero Current Comparator**

The zero current comparator monitors the inductor current being delivered to the output and shuts off the synchronous rectifier when this current reduces to approximately 50mA. This prevents the inductor current from reversing in polarity, improving efficiency at light loads.

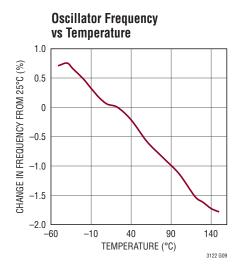

#### Oscillator

The internal oscillator is programmed to the desired switching frequency with an external resistor from the RT pin to GND according to the following formula:

$$f_{\text{OSC}}(\text{MHz}) = \left(\frac{57.6}{R_{\text{T}}(k\Omega)}\right)$$

The oscillator also can be synchronized to an external frequency by applying a pulse train to the PWM/SYNC pin. An external resistor must be connected between RT and GND to program the oscillator to a frequency approximately 25% below that of the externally applied pulse train used for synchronization.  $R_T$  is selected in this case according to this formula:

$$R_{T}(k\Omega) = \left(\frac{73.2}{f_{SYNC}(MHz)}\right)$$

#### **Output Disconnect**

The LTC3122's output disconnect feature eliminates body diode conduction of the internal P-channel MOSFET rectifier. This allows for  $V_{OUT}$  to discharge to OV during

shutdown, and draw no current from the input source. It also allows for inrush current limiting at turn-on, minimizing surge currents seen by the input supply. Note that to obtain the advantages of output disconnect, there must not be an external Schottky diode connected between SW and  $V_{OUT}$ . The output disconnect feature also allows  $V_{OUT}$  to be pulled high, without reverse current being backfed into the power source connected to  $V_{IN}$ .

#### Shutdown

The boost converter is disabled by pulling  $\overline{SD}$  below 0.25V and enabled by pulling  $\overline{SD}$  above 1.6V. Note that  $\overline{SD}$  can be driven above  $V_{IN}$  or  $V_{OUT}$ , as long as it is limited to less than the absolute maximum rating.

#### Thermal Shutdown

If the die temperature exceeds 170°C typical, the LTC3122 will go into thermal shutdown (TSD). All switches will be turned off until the die temperature drops by approximately 7°C, when the device re-initiates a soft-start and switching can resume.

#### **Boost Anti-Ringing Control**

When  $V_{OUT} \ge V_{IN} + 2V$ , the anti-ringing control connects a resistor across the inductor to damp high frequency ringing on the SW pin during discontinuous current mode operation when the inductor current has dropped to near zero. Although the ringing of the resonant circuit formed by L and  $C_{SW}$  (capacitance on SW pin) is low energy, it can cause EMI radiation.

### **V<sub>CC</sub>** Regulator

An internal low dropout regulator generates the 4.25V (nominal)  $V_{CC}$  rail from  $V_{IN}$  or  $V_{OUT}$ , depending upon operating conditions.  $V_{CC}$  is supplied from  $V_{IN}$  when  $V_{IN}$  is greater than 3.5V, otherwise the greater of  $V_{IN}$  and  $V_{OUT}$  is used. The  $V_{CC}$  rail powers the internal control circuitry and power MOSFET gate drivers of the LTC3122. The  $V_{CC}$  regulator is disabled in shutdown to reduce quiescent current and is enabled by forcing the  $\overline{SD}$  pin above its threshold. A 4.7 $\mu F$  or larger capacitor must be connected between  $V_{CC}$  and SGND.

LINEAR TECHNOLOGY

## **Overvoltage Lockout**

An overvoltage condition occurs when  $V_{OUT}$  exceeds approximately 16.2V. Switching is disabled and the internal soft-start ramp is reset. Once  $V_{OUT}$  drops below approximately 15.6V, a soft-start cycle is initiated and switching is enabled. If the boost converter output is lightly loaded so that the time constant product of the output capacitance,  $C_{OUT}$ , and the output load resistance,  $R_{OUT}$  is near or greater than the soft-start time of approximately 10ms, the soft-start ramp may end before or soon after switching resumes, defeating the inrush current limiting of the closed loop soft-start following an overvoltage event.

#### **Short-Circuit Protection**

The LTC3122 output disconnect feature allows output short-circuit protection. To reduce power dissipation under overload and short-circuit conditions, the peak switch current limit is reduced to 1.6A. Once  $V_{OUT} > 1.5V$ , the current limit is set to its nominal value of 3.5A.

## $V_{IN} > V_{OUT}$ Operation

The LTC3122 step-up converter will maintain voltage regulation even when the input voltage is above the desired output voltage. Note that operating in this mode will exhibit lower efficiency and a reduced output current capability. Refer to the Typical Performance Characteristics section for details.

#### **Burst Mode OPERATION**

When the PWM/SYNC pin is held low, the boost converter operates in Burst Mode operation to improve efficiency at light loads and reduce standby current at no load. The input thresholds for this pin are determined relative to  $V_{CC}$  with a low being less than 10% of  $V_{CC}$  and a high being greater than 90% of  $V_{CC}$ . The LTC3122 will operate in fixed frequency PWM mode even if Burst Mode operation is commanded during soft-start.

In Burst Mode operation, the LTC3122 switches asynchronously. The inductor current is first charged to 600mA by turning on the N-channel MOSFET switch. Once this current threshold is reached, the N-channel is turned off and the P-channel synchronous switch is turned on, delivering current to the output. When the inductor current discharges to approximately zero, the cycle repeats. In Burst Mode operation, energy is delivered to the output until the nominal regulation value is reached, at which point the LTC3122 transitions to sleep mode. In sleep, the output switches are turned off and the LTC3122 consumes only 25µA of quiescent current. When the output voltage droops approximately 1%, switching resumes. This maximizes efficiency at very light loads by minimizing switching and guiescent losses. Output voltage ripple in Burst Mode operation is typically 1% to 2% peak-to-peak. Additional output capacitance (10µF or greater), or the addition of a small feed-forward capacitor (10pF to 50pF) connected between V<sub>OLIT</sub> and FB can help further reduce the output ripple.

The maximum output current ( $I_{OUT}$ ) capability in Burst Mode operation varies with  $V_{IN}$  and  $V_{OUT}$ , as shown in Figure 2.

Figure 2. Burst Mode Maximum Output Current vs  $V_{\text{IN}}$

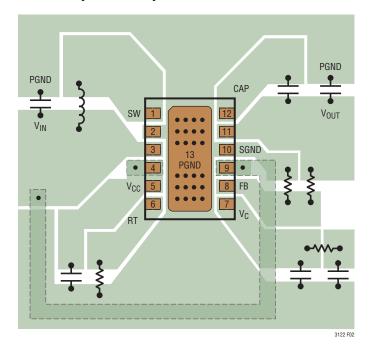

#### **PCB LAYOUT GUIDELINES**

The high switching frequency of the LTC3122 demands careful attention to board layout. A careless layout will result in reduced performance. Maximizing the copper area for ground will help to minimize die temperature rise. A multilayer board with a separate ground plane is ideal, but not absolutely necessary. See Figure 3 for an example of a two-layer board layout.

Figure 3. Traces Carrying High Current Are Direct (PGND, SW,  $\rm V_{IN}$  and  $\rm V_{OUT}$ ). Trace Area at FB and  $\rm V_{C}$  Are Kept Low. Trace Length to Input Supply Should Be Kept Short.  $\rm V_{IN}$  and  $\rm V_{OUT}$  Ceramic Capacitors Should Be Placed as Close to the LTC3122 Pins as Possible

#### SCHOTTKY DIODE

Although it is not required, adding a Schottky diode from SW to  $V_{OUT}$  can improve the converter efficiency by about 4%. Note that this defeats the output disconnect and short-circuit protection features of the LTC3122.

#### COMPONENT SELECTION

#### Inductor Selection

The LTC3122 can utilize small surface mount inductors due to its high switching frequency (up to 3MHz). Larger values of inductance will allow slightly greater output cur-

rent capability by reducing the inductor ripple current. The minimum inductance value, L, is inversely proportional to operating frequency and is given by the following equation:

$$L > \frac{V_{IN} \cdot (V_{OUT} - V_{IN})}{f \cdot Ripple \cdot V_{OUT}} \mu H \text{ and } L > \frac{3}{f}$$

where:

Ripple = Allowable inductor current ripple (amps peak-to-peak)

f = Switching Frequency in MHz

The inductor current ripple is typically set for 20% to 40% of the maximum inductor current. High frequency ferrite core inductor materials reduce frequency dependent power losses compared to cheaper powdered iron types, improving efficiency. The inductor should have low ESR (series resistance of the windings) to reduce the I<sup>2</sup>R power losses, and must be able to support the peak inductor current without saturating. Molded chokes and some chip inductors usually do not have enough core area to support the peak inductor currents of 3A to 4A seen on the LTC3122. To minimize radiated noise, use a shielded inductor.

See Table 1 for suggested components and suppliers.

Table 1. Recommended Inductors

| PART NUMBER         | VALUE<br>(μH) | DCR<br>(mΩ) | MAX DC<br>CURRENT<br>(A) | SIZE (mm)<br>W × L × H       |

|---------------------|---------------|-------------|--------------------------|------------------------------|

| Coilcraft LPS4018   | 1             | 42          | 3.8                      | 4 × 4 × 1.8                  |

| Coilcraft MSS7341   | 3.3           | 20          | 3.72                     | 7.3 × 7.3 × 4.1              |

| Coilcraft MSS1260T  | 33            | 54.9        | 4.34                     | 12.3 × 12.3 × 6.2            |

| Coiltronics DRQ73   | 0.992         | 24          | 3.99                     | $7.6 \times 7.6 \times 3.55$ |

| Coiltronics SD7030  | 3.3           | 24          | 3                        | $7 \times 7 \times 3$        |

| Coiltronics DR125   | 33            | 59          | 3.84                     | $12.5 \times 12.5 \times 6$  |

| Murata LQH6PP       | 1             | 9           | 4.3                      | 6 × 6 × 4.3                  |

| Murata LQH6PP       | 3.3           | 16          | 3.8                      | 6 × 6 × 4.3                  |

| Sumida CDRH50D28RNP | 1.2           | 13          | 4.8                      | 5 × 5 × 2.8                  |

| Sumida CDRH8D28NP   | 3.3           | 18          | 4                        | 8 × 8 × 3                    |

| Sumida CDRH129HF    | 33            | 53          | 4.25                     | 12 × 12 × 10                 |

| Taiyo-Yuden NR6045  | 3             | 31          | 3.2                      | 6 × 6 × 4.5                  |

| TDK LTF5022T        | 1.2           | 25          | 4.2                      | 5 × 5.2 × 2.2                |

| TDK SPM6530T        | 3.3           | 20          | 4.1                      | 7 × 7 × 3.2                  |

| TDK VLF12060T       | 33            | 53          | 3.4                      | 11.7 × 12 × 6                |

| Würth WE-PD         | 3.3           | 32.5        | 3.1                      | $7.3 \times 7.3 \times 2$    |

LINEAR TECHNOLOGY

## **Output and Input Capacitor Selection**

Low ESR (equivalent series resistance) capacitors should be used to minimize the output voltage ripple. Multilayer ceramic capacitors are an excellent choice as they have extremely low ESR and are available in small footprints. X5R and X7R dielectric materials are preferred for their ability to maintain capacitance over wide voltage and temperature ranges. Y5V types should not be used. Although ceramic capacitors are recommended, low ESR tantalum capacitors may be used as well.

When selecting output capacitors, the magnitude of the peak inductor current, together with the ripple voltage specification, determine the choice of the capacitor. Both the ESR (equivalent series resistance) of the capacitor and the charge stored in the capacitor each cycle contribute to the output voltage ripple.

The ripple due to the charge is approximately:

$$V_{\text{RIPPLE(CHARGE)}} \approx \frac{I_{\text{P}} \cdot V_{\text{IN}}}{C_{\text{OUT}} \cdot V_{\text{OUT}} \cdot f}$$

where IP is the peak inductor current.

The ESR of  $C_{OUT}$  is usually the most dominant factor for ripple in most power converters. The ripple due to the capacitor ESR is:

$$V_{RIPPLE(ESR)} = I_{LOAD} \bullet R_{ESR} \bullet \frac{V_{OUT}}{V_{IN}}$$

where R<sub>ESR</sub> = capacitor equivalent series resistance.

The input filter capacitor reduces peak currents drawn from the input source and reduces input switching noise. A low ESR bypass capacitor with a value of at least  $4.7\mu F$  should be located as close to the  $V_{IN}$  pin as possible.

Low ESR and high capacitance are critical to maintain low output voltage ripple. Capacitors can be used in parallel for even larger capacitance values and lower effective ESR. Ceramic capacitors are often utilized in switching converter applications due to their small size, low ESR and low leakage currents. However, many ceramic capacitors experience significant loss in capacitance from their rated value with increased DC bias voltage. It is not uncommon for a small surface mount capacitor to lose more than 50%

of its rated capacitance when operated near its rated voltage. As a result it is sometimes necessary to use a larger capacitor value or a capacitor with a larger value and case size, such as 1812 rather than 1206, in order to actually realize the intended capacitance at the full operating voltage. Be sure to consult the vendor's curve of capacitance vs DC bias voltage. Table 2 shows a sampling of capacitors suited for LTC3122 applications.

**Table 2. Representative Output Capacitors**

| Table 2. nepresentative output Gapacitors |               |                |                                                              |  |  |  |

|-------------------------------------------|---------------|----------------|--------------------------------------------------------------|--|--|--|

| MANUFACTURER,<br>Part number              | VALUE<br>(μF) | VOLTAGE<br>(V) | SIZE L $\times$ W $\times$ H (mm)<br>TYPE, ESR (m $\Omega$ ) |  |  |  |

| AVX,<br>12103D226MAT2A                    | 22            | 25             | $3.2 \times 2.5 \times 2.79$ , X5R Ceramic                   |  |  |  |

| Kemet,<br>C2220X226K3RACTU                | 22            | 25             | $5.7 \times 5.0 \times 2.4$ , X7R Ceramic                    |  |  |  |

| Kemet,<br>A700D226M016ATE030              | 22            | 16             | $7.3\times4.3\times2.8,$ Alum. Polymer, $30\text{m}\Omega$   |  |  |  |

| Murata,<br>GRM32ER71E226KE15L             | 22            | 25             | $3.2 \times 2.5 \times 2.5$ , X7R Ceramic                    |  |  |  |

| Nichicon,<br>PLV1E121MDL1                 | 82            | 25             | $8 \times 8 \times 12$ , Alum. Polymer, $25m\Omega$          |  |  |  |

| Panasonic,<br>ECJ-4YB1E226M               | 22            | 25             | 3.2 × 2.5 × 2.5,<br>X5R Ceramic                              |  |  |  |

| Sanyo,<br>25TQC22MV                       | 22            | 25             | $7.3 \times 4.3 \times 3.1$ , POSCAP, $50 \text{m}\Omega$    |  |  |  |

| Sanyo,<br>16TQC100M                       | 100           | 16             | $7.3 \times 4.3 \times 1.9$ , POSCAP, $45 \text{m}\Omega$    |  |  |  |

| Sanyo,<br>25SVPF47M                       | 47            | 25             | $6.6 \times 6.6 \times 5.9$ , OS-CON, $30\text{m}\Omega$     |  |  |  |

| Taiyo Yuden,<br>TMK325BJ226MM-T           | 22            | 25             | 3.2 × 2.5 × 2.5,<br>X5R Ceramic                              |  |  |  |

| TDK,<br>CKG57NX5R1E476M                   | 47            | 25             | 6.5 × 5.5 × 5.5,<br>X5R Ceramic                              |  |  |  |

| Cap-XX<br>GS230F                          | 1.2Farads     | 4.5            | $39 \times 17 \times 3.8$ $28 \text{m}\Omega$                |  |  |  |

| Cooper<br>A1030-2R5155                    | 1.5Farads     | 2.5            | $\emptyset$ = 10, L = 30 60m $\Omega$                        |  |  |  |

| Maxwell<br>BCAP0050-P270                  | 50Farads      | 2.5            | $\emptyset$ = 18, L = 40 20m $\Omega$                        |  |  |  |

For applications requiring a very low profile and very large capacitance, the GS, GS2 and GW series from Cap-XX and PowerStor Aerogel Capacitors from Cooper all offer very high capacitance and low ESR in various low profile packages.

A method for improving the converter's transient response uses a small feed-forward series network of a capacitor and

a resistor across the top resistor of the feedback divider (from  $V_{OUT}$  to FB). This adds a phase-lead zero and pole to the transfer function of the converter as calculated in the Compensating the Feedback Loop section.

#### OPERATING FREQUENCY SELECTION

There are several considerations in selecting the operating frequency of the converter. Typically the first consideration is to stay clear of sensitive frequency bands, which cannot tolerate any spectral noise. For example, in products incorporating RF communications, the 455kHz IF frequency is sensitive to any noise, therefore switching above 600kHz is desired. Some communications have sensitivity to 1.1MHz and in that case a 1.5MHz switching converter frequency may be employed. A second consideration is the physical size of the converter. As the operating frequency is increased, the inductor and filter capacitors typically can be reduced in value, leading to smaller sized external components. The smaller solution size is typically traded for efficiency, since the switching losses due to gate charge increase with frequency.

Another consideration is whether the application can allow pulse-skipping. When the boost converter pulse-skips, the minimum on-time of the converter is unable to support the duty cycle. This results in a low frequency component to the output ripple. In many applications where physical size is the main criterion, running the converter in this mode is acceptable. In applications where it is preferred not to enter this mode, the maximum operating frequency is given by:

$$f_{\text{MAX\_NOSKIP}} \le \frac{V_{\text{OUT}} - V_{\text{IN}}}{V_{\text{OUT}} \cdot t_{\text{ON(MIN)}}} Hz$$

where  $t_{ON(MIN)}$  = minimum on-time = 100ns.

#### Thermal Considerations

For the LTC3122 to deliver its full power, it is imperative that a good thermal path be provided to dissipate the heat generated within the package. This can be accomplished by taking advantage of the large thermal pad on the underside of the IC. It is recommended that multiple vias in the printed circuit board be used to conduct heat away from the IC and into a copper plane with as much area as

possible. If the junction temperature rises above  $\sim 170^{\circ}$ C, the part will go into thermal shutdown, and all switching will stop until the temperature drops approximately  $7^{\circ}$ C.

#### Compensating the Feedback Loop

The LTC3122 uses current mode control, with internal adaptive slope compensation. Current mode control eliminates the second order filter due to the inductor and output capacitor exhibited in voltage mode control, and simplifies the power loop to a single pole filter response. Because of this fast current control loop, the power stage of the IC combined with the external inductor can be modeled by a transconductance amplifier  $g_{mp}$  and a current controlled current source. Figure 4 shows the key equivalent small signal elements of a boost converter.

The DC small-signal loop gain of the system shown in Figure 4 is given by the following equation:

$$G_{BOOST} = G_{EA} \cdot G_{MP} \cdot G_{POWER} \cdot \frac{R2}{R1 + R2}$$

where  $G_{EA}$  is the DC gain of the error amplifier,  $G_{MP}$  is the modulator gain, and  $G_{POWER}$  is the inductor current to  $V_{OUT}$  gain.

Figure 4. Boost Converter Equivalent Model

LINEAR

$$G_{FA} = g_{ma} \cdot R_0 \approx 950 \text{V/V}$$

(Not Adjustable;  $g_{ma} = 95\mu S$ ,  $R_0 \approx 10 M\Omega$ )

$$G_{MP} = g_{mp} = \frac{\Delta I_L}{\Delta V_C} \approx 3.4S \text{ (Not Adjustable)}$$

$$G_{POWER} = \frac{\Delta V_{OUT}}{\Delta I_{L}} = \frac{\eta \cdot V_{IN}}{2 \cdot I_{OUT}}$$

Combining the two equations above yields:

$$G_{DC} = G_{MP} \cdot G_{POWER} \approx \frac{1.7 \cdot \eta \cdot V_{IN}}{I_{OUT}} V/V$$

Converter efficiency  $\eta$  will vary with I<sub>OUT</sub> and switching frequency  $f_{OSC}$  as shown in the typical performance characteristics curves.

Output Pole: P1 =

$$\frac{2}{2 \cdot \pi \cdot R_{L} \cdot C_{OUT}}$$

Hz

Error Amplifier Pole: P2 =

$$\frac{1}{2 \cdot \pi \cdot R_0 \cdot (C_C + C_F)}$$

Hz

Error Amplifier Zero: Z1 =

$$\frac{1}{2 \cdot \pi \cdot R_C \cdot C_C}$$

Hz

ESR Zero: Z2 =

$$\frac{1}{2 \cdot \pi \cdot R_{ESR} \cdot C_{OUT}}$$

Hz

RHP Zero: Z3 =

$$\frac{{V_{IN}}^2 \cdot R_L}{2 \cdot \pi \cdot {V_{OUT}}^2 \cdot L} Hz$$

High Frequency Pole: P3 >

$$\frac{f_{OSC}}{3}$$

Phase Lead Zero:

$$Z4 = \frac{1}{2 \cdot \pi \cdot (R1 + R_{PL}) \cdot C_{PL}} Hz$$

Phase Lead Pole: P4 =

$$\frac{1}{2 \cdot \pi \cdot \left(\frac{R1 \cdot R2}{R1 + R2} + R_{PL}\right) \cdot C_{PL}}$$

Error Amplifier Filter Pole:

$$P5 = \frac{1}{2 \bullet \pi \bullet R_C \bullet \left(\frac{C_C \bullet C_F}{C_C + C_F}\right)} Hz$$

The current mode zero (Z3) is a right half plane zero which can be an issue in feedback control design, but is manageable with proper external component selection. As a general rule, the frequency at which the open-loop gain of the converter is reduced to unity, known as the crossover frequency  $f_{\rm C}$ , should be set to less than one third of the right half plane zero (Z3), and under one eighth of the switching frequency  $f_{\rm OSC}$ . Once  $f_{\rm C}$  is selected, the values for the compensation components can be calculated using a bode plot of the power stage or two generally valid assumptions: P1 dominates the gain of the power stage for frequencies lower than  $f_{\rm C}$  and  $f_{\rm C}$  is much higher than P2. First calculate the power stage gain at  $f_{\rm C}$ ,  $G_{f\rm C}$  in V/V. Assuming the output pole P1 dominates  $G_{f\rm C}$  for this range, it is expressed by:

$$G_{fC} \approx \frac{G_{DC}}{\sqrt{1 + \left(\frac{f_C}{P1}\right)^2}} V/V$$

Decide how much phase margin  $(\Phi_m)$  is desired. Greater phase margin can offer more stability while lower phase margin can yield faster transient response. Typically,  $\Phi_m \approx 60^\circ$  is optimal for minimizing transient response time while allowing sufficient margin to account for component variability.  $\Phi_1$  is the phase boost of Z1, P2, and P5 while  $\Phi_2$  is the phase boost of Z4 and P4. Select  $\Phi_1$  and  $\Phi_2$  such that

$$\Phi_1 \le 74^\circ$$

;  $\Phi_2 \le \left(2 \cdot \tan^{-1} \sqrt{\frac{V_{0UT}}{1.2V}}\right) - 90^\circ$  and

$$\Phi_1 + \Phi_2 = \Phi_m + \tan^{-1} \left( \frac{f_c}{Z_3} \right)$$

where  $V_{OUT}$  is in V and  $f_C$  and Z3 are in kHz.

Setting Z1, P5, Z4, and P4 such that

Z1 =

$$\frac{f_{C}}{\sqrt{a_{1}}}$$

, P5 =  $f_{C}\sqrt{a_{1}}$ , Z4 =  $\frac{f_{C}}{\sqrt{a_{2}}}$ , P4 =  $f_{C}\sqrt{a_{2}}$

allows  $a_1$  and  $a_2$  to be determined using  $\Phi_1$  and  $\Phi_2$

$$a_1 = \tan^2\left(\frac{\Phi_1 + 90^\circ}{2}\right), a_2 = \tan^2\left(\frac{\Phi_2 + 90^\circ}{2}\right)$$

The compensation will force the converter gain  $G_{BOOST}$  to unity at  $f_C$  by using the following expression for  $C_C$ :

$$\begin{split} \mathbf{C_{C}} &= \frac{10^{3} \bullet \mathbf{g_{ma}} \bullet \mathbf{R2} \bullet \mathbf{G_{fC}} (\mathbf{a_{1}} - \mathbf{1}) \sqrt{\mathbf{a_{2}}}}{2\pi \bullet f_{\mathbf{C}} \bullet (\mathbf{R1} + \mathbf{R2}) \sqrt{\mathbf{a_{1}}}} \, \mathbf{pF} \\ (\mathbf{g_{ma}} \text{ in } \mu \mathbf{S}, \, f_{\mathbf{C}} \text{ in kHz, } \mathbf{G_{fC}} \text{ in V/V}) \end{split}$$

Once  $C_C$  is calculated,  $R_C$  and  $C_F$  are determined by:

$$R_{C} = \frac{10^{6} \cdot \sqrt{a_{1}}}{2\pi \cdot f_{C} \cdot C_{C}} k\Omega \ (f_{C} \text{ in kHz, } C_{C} \text{ in pF})$$

$$C_{F} = \frac{C_{C}}{a_{1} - 1}$$

The values of the phase lead components are given by the expressions:

$$R_{PL} = \frac{R1 - a_2 \cdot \left(\frac{R1 \cdot R2}{R1 + R2}\right)}{a_2 - 1} k\Omega \text{ and}$$

$$C_{PL} = \frac{10^6 (a_2 - 1)(R1 + R2)}{2\pi \cdot f_C \cdot R1^2 \sqrt{a_2}} pF$$

where R1, R2, and R<sub>PL</sub> are in  $k\Omega$  and  $f_{C}$  is in kHz.

Note that selecting  $\Phi_2$  = 0° forces  $a_2$  = 1, and so the converter will have Type II compensation and therefore no feedforward:  $R_{PL}$  is open (infinite impedance) and  $C_{PL}$  = 0pF. If  $a_2$  = 0.833 •  $V_{OUT}$  (its maximum), feedforward is maximized;  $R_{PL}$  = 0 and  $C_{PL}$  is maximized for this compensation method.

Once the compensation values have been calculated, obtaining a converter bode plot is strongly recommended to verify calculations and adjust values as required.

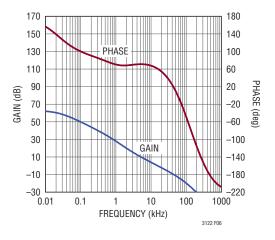

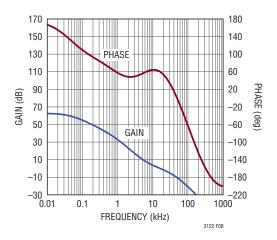

Using the circuit in Figure 5 as an example, Table 3 shows the parameters used to generate the bode plot shown in Figure 6.

Table 3. Bode Plot Parameters for Type II Compensation

| PARAMETER        | VALUE | UNITS | COMMENT      |

|------------------|-------|-------|--------------|

| V <sub>IN</sub>  | 5     | V     | App Specific |

| V <sub>OUT</sub> | 12    | V     | App Specific |

| R <sub>L</sub>   | 15    | Ω     | App Specific |

| C <sub>OUT</sub> | 22    | μF    | App Specific |

| R <sub>ESR</sub> | 5     | mΩ    | App Specific |

| L                | 3.3   | μН    | App Specific |

| $f_{OSC}$        | 1     | MHz   | Adjustable   |

| R1               | 1020  | kΩ    | Adjustable   |

| R2               | 113   | kΩ    | Adjustable   |

| 9 <sub>ma</sub>  | 95    | μS    | Fixed        |

| $R_0$            | 10    | MΩ    | Fixed        |

| 9 <sub>mp</sub>  | 3.4   | S     | Fixed        |

| η                | 80    | %     | App Specific |

| R <sub>C</sub>   | 210   | kΩ    | Adjustable   |

| C <sub>C</sub>   | 390   | pF    | Adjustable   |

| C <sub>F</sub>   | 10    | pF    | Adjustable   |

| R <sub>PL</sub>  | 0     | kΩ    | Optional     |

| C <sub>PL</sub>  | 0     | pF    | Optional     |

From Figure 6, the phase is 60° when the gain reaches 0dB, so the phase margin of the converter is 60°. The crossover frequency is 15kHz, which is more than three times lower than the 108.4kHz frequency of the RHP zero to achieve adequate phase margin.

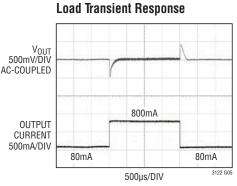

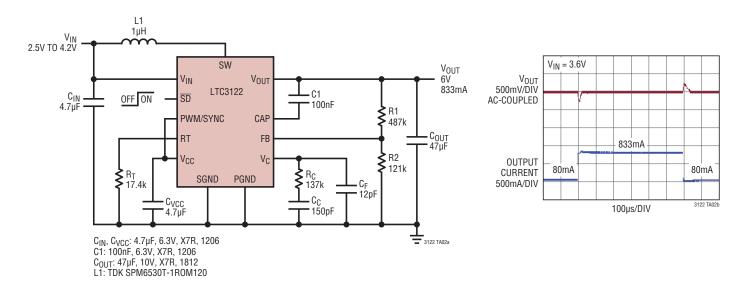

#### Switching Waveforms with 800mA Load

# VOUT 100mV/DIV AC-COUPLED SW 10V/DIV INDUCTOR CURRENT 1A/DIV 200ns/DIV 3122 F05b

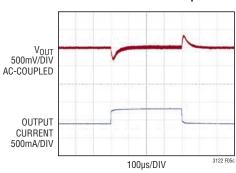

# Transient Response with 400mA to 800mA Load Step

Figure 5. 1MHz, 5V to 12V, 800mA Boost Converter

Figure 6. Bode Plot for Example Converter

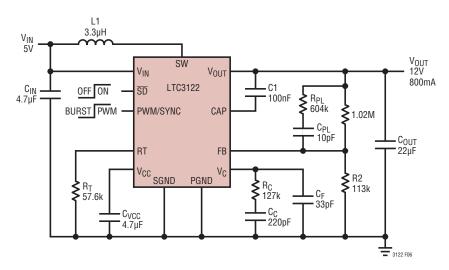

Figure 7. Boost Converter with Phase Lead

The circuit in Figure 7 shows the same application as that in Figure 5 with Type III compensation. This is accomplished by adding  $C_{PL}$  and  $R_{PL}$  and adjusting  $C_{C}$ ,  $C_{F}$ , and  $R_{C}$  accordingly. Table 4 shows the parameters used to generate the bode plot shown in Figure 8.

Table 4. Bode Plot Parameters for Type III Compensation

| PARAMETER                  | VALUE | UNITS | COMMENT      |

|----------------------------|-------|-------|--------------|

| $\overline{V_{IN}}$        | 5     | V     | App Specific |

| $\overline{V_{OUT}}$       | 12    | V     | App Specific |

| $\overline{R_L}$           | 15    | Ω     | App Specific |

| $\overline{C_{OUT}}$       | 22    | μF    | App Specific |

| R <sub>ESR</sub>           | 5     | mΩ    | App Specific |

| L                          | 3.3   | μH    | App Specific |

| $\overline{f_{	ext{OSC}}}$ | 1     | MHz   | Adjustable   |

| R1                         | 113   | kΩ    | Adjustable   |

| R2                         | 1020  | kΩ    | Adjustable   |

| g <sub>ma</sub>            | 95    | μS    | Fixed        |

| $R_0$                      | 10    | MΩ    | Fixed        |

| g <sub>mp</sub>            | 3.4   | S     | Fixed        |

| η                          | 80    | %     | App Specific |

| $\overline{R_C}$           | 127   | kΩ    | Adjustable   |

| $\overline{C_C}$           | 220   | pF    | Adjustable   |

| $C_{F}$                    | 33    | pF    | Adjustable   |

| R <sub>PL</sub>            | 604   | kΩ    | Adjustable   |

| $C_{PL}$                   | 10    | pF    | Adjustable   |

From Figure 8, the phase margin is still optimized at  $60^{\circ}$  and the crossover frequency remains 15kHz. Adding  $C_{PL}$  and  $R_{PL}$  provides some feedforward signal in Burst Mode operation, leading to lower output voltage ripple.

Figure 8. Bode Plot Showing Phase Lead

LINEAR TECHNOLOGY

#### Single Li-Cell to 6V, 5W, 3MHz Synchronous Boost Converter for RF Transmitter

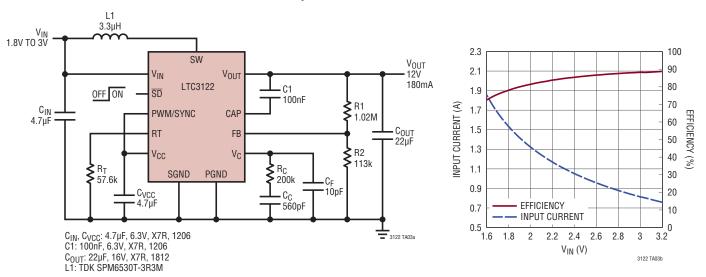

#### 2 AA Cell to 12V Synchronous Boost Converter, 180mA

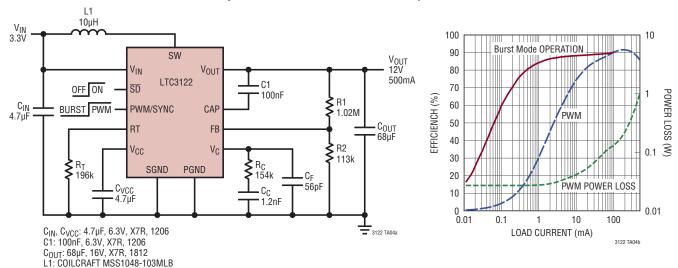

#### 3.3V to 12V, 300kHz Synchronous Boost Converter with Output Disconnect, 500mA

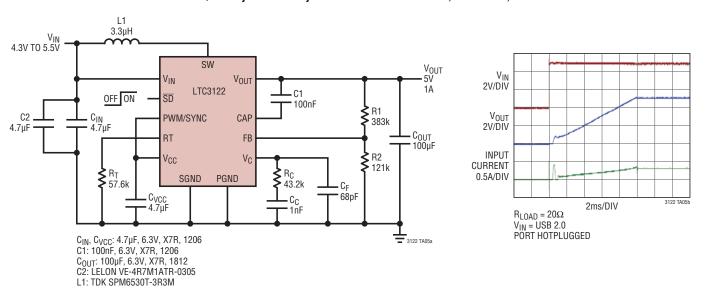

#### USB/Battery Powered Synchronous Boost Converter, 4.3V to 5V, 1A

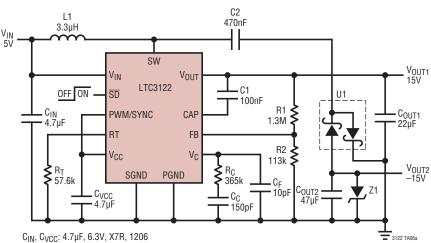

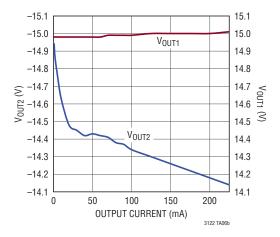

#### 5V to Dual Output Synchronous Boost Converter, ±15V

$\begin{array}{l} C_{IN},\,C_{VCC};\,4.7\mu F,\,6.3V,\,X7R,\,1206\\ C_{OUT2};\,47\mu F,\,16V,\,X7R,\,1206\\ C1:\,100n F,\,6.3V,\,X7R,\,1206\\ C_{OUT1}:\,22\mu F,\,16V,\,X7R,\,1812\\ C2:\,470n F,\,25V,\,X7R,\,1206\\ L1:\,TDK\,SPM6530T-3R3M \end{array}$

U1: CENTRAL SEMICONDUCTOR CBAT54S

Z1: DIODES, INC. DDZ16ASF-7

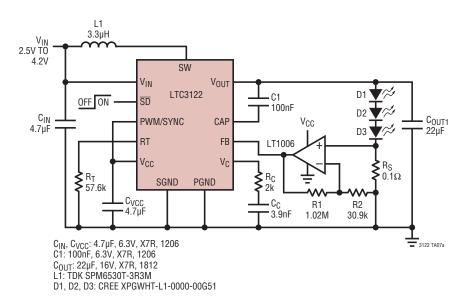

Single Li-Cell 3-LED Driver, 2.5V/4.2V to 350mA

100 POWER LOSS 0.1 POWER LOSS 0.1 O.1 VIN (V)

## PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

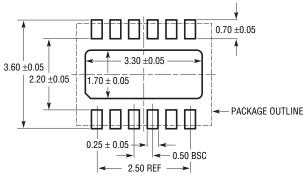

#### DE/UE Package 12-Lead Plastic DFN (4mm × 3mm)

(Reference LTC DWG # 05-08-1695 Rev D)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS APPLY SOLDER MASK TO AREAS THAT ARE NOT SOLDERED

- NOTE:

- 1. DRAWING PROPOSED TO BE A VARIATION OF VERSION (WGED) IN JEDEC PACKAGE OUTLINE M0-229

- 2. DRAWING NOT TO SCALE

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

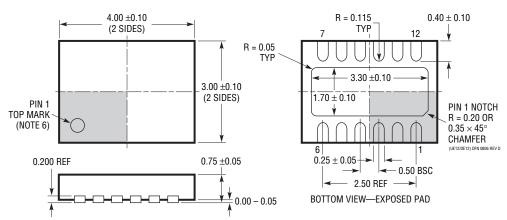

## PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

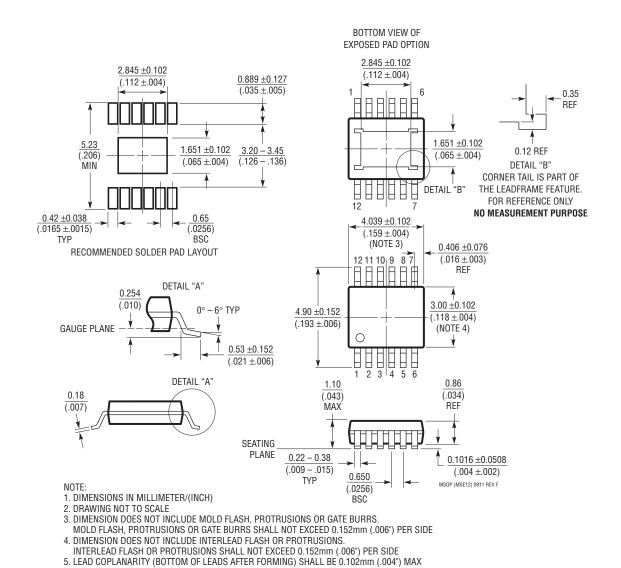

#### MSE Package 12-Lead Plastic MSOP, Exposed Die Pad

(Reference LTC DWG # 05-08-1666 Rev F)

EXPOSED PAD DIMENSION DOES INCLUDE MOLD FLASH. MOLD FLASH ON E-PAD SHALL NOT EXCEED 0.254mm (.010") PER SIDE.

LINEAR TECHNOLOGY

## **REVISION HISTORY**

| REV | DATE  | DESCRIPTION                                                                              | PAGE NUMBER |

|-----|-------|------------------------------------------------------------------------------------------|-------------|

| Α   | 05/13 | Clarified temperature ranges.                                                            | 2           |

|     |       | Added LTC3122HMSE#PBF to the Order Information.                                          | 2           |

|     |       | Added H-grade to Note 3, clarified N/P channel switch leakage current.                   | 3           |

|     |       | Clarified Load Transient Response graph.                                                 | 4           |

|     |       | Clarified Burst Mode Operation No Load graph.                                            | 5           |

|     |       | Clarified multiple graphs.                                                               | 6           |

|     |       | Clarified SW (Pin 1) description.                                                        | 7           |

|     |       | Clarified the Block Diagram.                                                             | 8           |

|     |       | Clarified Boost Anti-Ringing Control description.                                        | 10          |

|     |       | Clarified Transient Response graph.                                                      | 17          |

|     |       | Clarified components values of Typical Applications, clarified Load Step Response graph. | 19          |

|     |       | Clarified components values of Typical Applications, clarified graphs.                   | 20          |

|     |       | Clarified components values of Typical Applications, clarified graphs.                   | 21          |

|     |       | Clarified components values of Typical Applications, clarified graphs.                   | 24          |

#### Dual Supercapacitor Backup Power Supply, 0.5V to 5V

## **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                                                                                        | COMMENTS                                                                                                                                 |

|-------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| LTC3421     | 3A I <sub>SW</sub> , 3MHz, Synchronous Step-Up DC/DC Converter with Output Disconnect                              | 95% Efficiency, $V_{IN}$ = 0.5V to 4.5V, $V_{OUT(MAX)}$ = 5.25V, $I_Q$ = 12 $\mu$ A, $I_{SD}$ < 1 $\mu$ A, QFN24 Package                 |

| LTC3422     | 1.5A I <sub>SW</sub> , 3MHz Synchronous Step-Up DC/DC Converter with Output Disconnect                             | 95% Efficiency, $V_{IN}$ = 0.5V to 4.5V, $V_{OUT(MAX)}$ = 5.25V, $I_Q$ = 25 $\mu$ A, $I_{SD}$ < 1 $\mu$ A, 3mm × 3mm DFN Package         |

| LTC3112     | 2.5A I <sub>SW</sub> , 750kHz, Synchronous Buck-Boost DC/DC Converter with Output Disconnect, Burst Mode Operation | 95% Efficiency, $V_{IN}$ = 2.7V to 15V, $V_{OUT(MAX)}$ = 14V, $I_Q$ = 50 $\mu$ A, $I_{SD}$ < 1 $\mu$ A, 4mm × 5mm DFN and TSSOP Packages |

| LTC3458     | 1.4A I <sub>SW</sub> , 1.5MHz, Synchronous Step-Up DC/DC Converter/<br>Output Disconnect/Burst Mode Operation      | 93% Efficiency, $V_{IN}$ = 1.5V to 6V, $V_{OUT(MAX)}$ = 7.5V, $I_Q$ = 15 $\mu$ A, $I_{SD}$ < 1 $\mu$ A, DFN12 Package                    |

| LTC3528     | 1A I <sub>SW</sub> , 1MHz, Synchronous Step-Up DC/DC Converter with Output Disconnect/Burst Mode Operation         | 94% Efficiency, $V_{IN}$ = 700mV to 5.25V, $V_{OUT(MAX)}$ = 5.25V, $I_Q$ = 12 $\mu$ A, $I_{SD}$ < 1 $\mu$ A, 3mm × 2mm DFN Package       |

| LTC3539     | 2A I <sub>SW</sub> , 1MHz/2MHz, Synchronous Step-Up DC/DC Converters with Output Disconnect/Burst Mode Operation   | 94% Efficiency, $V_{IN}$ = 700mV to 5.25V, $V_{OUT(MAX)}$ = 5.25V, $I_Q$ = 10 $\mu$ A, $I_{SD}$ < 1 $\mu$ A, 3mm × 2mm DFN Package       |

| LTC3459     | 70mA I <sub>SW</sub> , 10V Micropower Synchronous Boost Converter/<br>Output Disconnect/Burst Mode Operation       | $V_{IN}$ = 1.5V to 5.5V, $V_{OUT(MAX)}$ = 10V, $I_Q$ = 10 $\mu$ A, $I_{SD}$ < 1 $\mu$ A, ThinSOT <sup>TM</sup> Package                   |

| LTC3499     | 750mA Synchronous Step-Up DC/DC Converters with Reverse-Battery Protection                                         | 94% Efficiency, $V_{IN}$ = 1.8V to 5.5V, $V_{OUT(MAX)}$ = 6V, $I_Q$ = 20 $\mu$ A, $I_{SD}$ < 1 $\mu$ A, 3mm × 3mm DFN and MSOP Packages  |

| LTC3115-1   | 40V, 2A Synchronous Buck-Boost DC/DC Converter                                                                     | 95% Efficiency, $V_{IN}$ = 2.7V to 40V, $V_{OUT(MAX)}$ = 40V, $I_Q$ = 50 $\mu$ A, $I_{SD}$ < 3 $\mu$ A, 4mm × 5mm DFN and TSSOP Packages |

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Voltage Regulators category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below:

TLF30682QVS01XUMA1 TPSM84209RKHR FAN53526UC106X FAN53526UC128X MP1587EN-LF FAN48610BUC33X

FAN48617UC50X FAN53526UC89X MIC45116-1YMP-T1 NCV891234MW50R2G AST1S31PUR 16017 A6986FTR NCP81103MNTXG

NCP81203PMNTXG MAX17242ETPA+ MAX16935RATEB/V+ MP2313GJ-Z NCP81208MNTXG MP8759GD-Z FAN53526UC100X

FAN53526UC84X PCA9412AUKZ MP2314SGJ-Z AS1340A-BTDM-10 MP3421GG-P NCP81109GMNTXG MP6003DN-LF-Z

MAX16935BAUES/V+ LT8315IFE#PBF SCY1751FCCT1G NCP81109JMNTXG MAX16956AUBA/V+ AP3409ADNTR-G1

FAN48623UC36FX MPQ2454GH MPQ2454GH-AEC1 MP21148GQD-P AS3701B-BWLM-68 MPQ2143DJ-P MP9942AGJ-P

MP8759GD-P MP5610GQG-P MP28200GG-P MP2451DJ-LF-Z MP2326GD-P MP2314SGJ-P MP2158AGQH-P MP2148GQD-18-P

MP1470HGJ-P