# LTC3555/LTC3555-X

## High Efficiency USB Power Manager + Triple Step-Down DC/DC DESCRIPTION

The LTC®3555 family are highly integrated USB compatible power management and battery charger ICs for

Li-Ion/Polymer battery applications. They include a high

efficiency current limited switching PowerPath manager with automatic load prioritization, a battery charger, an ideal

diode and three general purpose synchronous step-down

The LTC3555 family limits input current to either 100mA

or 500mA for USB applications or 1A for adapter-powered

applications. Unlike linear chargers, the LTC3555 family's

switching architecture transmits nearly all of the power available from the USB port to the load with minimal loss

and heat which eases thermal constraints in small spaces.

Two of the three general purpose switching regulators can

provide up to 400mA and the third can deliver 1A. The

entire product can be controlled via I<sup>2</sup>C or simple I/O. The

LTC3555-1/LTC3555-3 versions offer "instant-on" power

delivery to the portable product even with a very low battery

voltage. The LTC3555-3 version also has a reduced charger float voltage of 4.100V for battery safety and longevity.

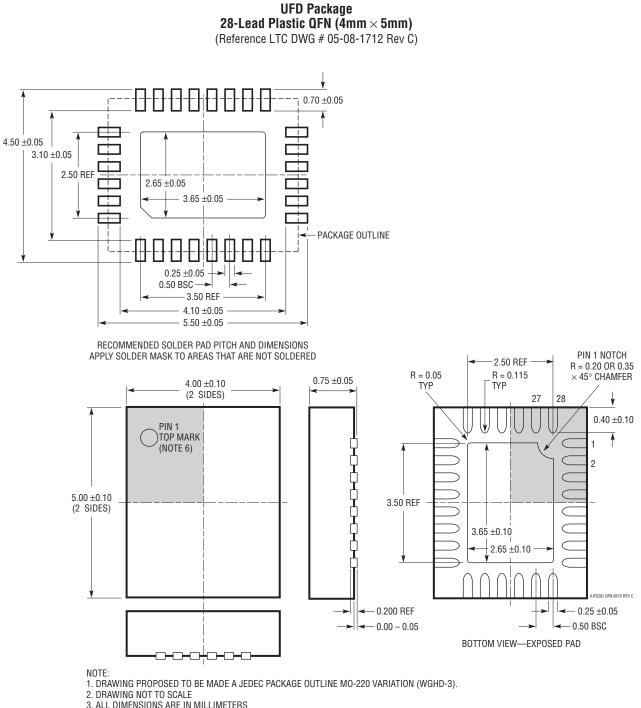

The LTC3555 family is available in the low profile 28-pin  $(4mm \times 5mm \times 0.75mm)$  QFN surface mount package.

∠, LT, LTC, LTM Linear Technology, the Linear logo and Burst Mode are registered trademarks and PowerPath and Bat-Track are trademarks of Linear Technology Corporation. All other

V<sub>BUS</sub> = 5V

IBAT = 0mA 10x MODE

10

0.01

- 0m4

trademarks are the property of their respective owners. Protected by U.S. Patents, including

switching regulators.

6522118 and 6404251

# FEATURES

**Power Manager**

- High Efficiency Switching PowerPath<sup>™</sup> Controller with Bat-Track<sup>™</sup> Adaptive Output Control

- Programmable USB or Wall Current Limit (100mA/500mA/1A)

- Full Featured Li-Ion/Polymer Battery Charger

- 1.5A Maximum Charge Current

- Internal 180m $\Omega$  Ideal Diode + External Ideal Diode Controller Powers Load in Battery Mode

- Low No-Load Quiescent Current when Powered from BAT (<32µA)

### DC/DCs

- Triple High Efficiency Step-Down DC/DCs (1A/400mA/400mA IOUT)

- All Regulators Operate at 2.25MHz

- Dynamic Voltage Scaling on Two Outputs

- $I^2C$  or Independent Enable, V<sub>OUT</sub> Controls

- Low No-Load Quiescent Current: 20µA

- 28-Pin (4mm  $\times$  5mm  $\times$  0.75mm) QFN Package

# APPLICATIONS

- HDD-Based MP3 Players, PDAs, GPS, PMPs

- Portable Medical Products

- Handheld Instrumentation

- Other USB-Based Handheld Products

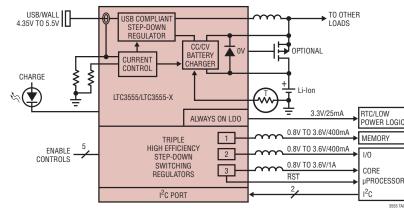

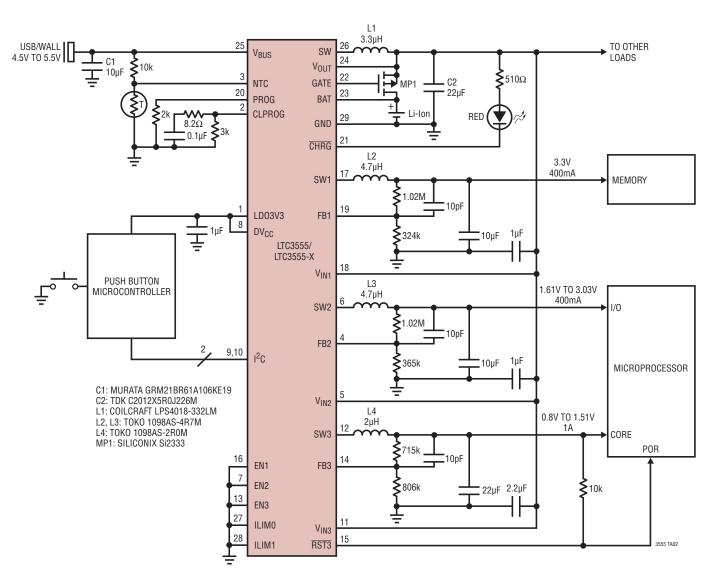

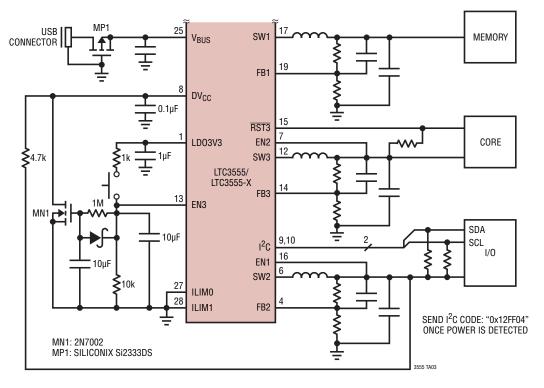

# TYPICAL APPLICATION

High Efficiency PowerPath Manager and Triple Step-Down Regulator

0.1

I<sub>OUT</sub> (A) 3555 TA01b

# ABSOLUTE MAXIMUM RATINGS

| (Notes 1, 2, 3)                                                                                        |

|--------------------------------------------------------------------------------------------------------|

| V <sub>BUS</sub> (Transient) t < 1ms,                                                                  |

| Duty Cycle < 1%0.3V to 7V                                                                              |

| V <sub>IN1</sub> , V <sub>IN2</sub> , V <sub>IN3</sub> , V <sub>BUS</sub> (Static), DV <sub>CC</sub> , |

| FB1, FB2, FB3, NTC, BAT, SCL, SDA,                                                                     |

| RST3, CHRG –0.3V to 6V                                                                                 |

| EN1, EN2, EN3 –0.3V to V <sub>OUT</sub> +0.3V                                                          |

| $I_{LIM0}$ , $I_{LIM1}$ 0.3V to MAX ( $V_{BUS}$ , $V_{OUT}$ BAT)                                       |

| I <sub>CLPROG</sub> 3mA                                                                                |

| I <sub>RST3</sub> , I <sub>CHRG</sub> 50mA                                                             |

| I <sub>PROG</sub> 2mA                                                                                  |

| I <sub>LD03V3</sub>                                                                                    |

| I <sub>SW1</sub> , I <sub>SW2</sub> 600mA                                                              |

| I <sub>SW</sub> , I <sub>SW3</sub> , I <sub>BAT</sub> , I <sub>VOUT</sub> 2A                           |

| Junction Temperature 125°C                                                                             |

| Operating Temperature Range (Note 2)–40°C to 85°C                                                      |

| Storage Temperature Range –65°C to 125°C                                                               |

|                                                                                                        |

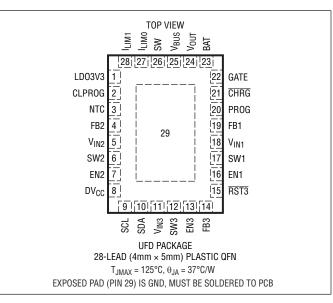

# PIN CONFIGURATION

# **ORDER INFORMATION**

### http://www.linear.com/product/LTC3555#orderinfo

| LEAD FREE FINISH  | TAPE AND REEL       | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|-------------------|---------------------|---------------|---------------------------------|-------------------|

| LTC3555EUFD#PBF   | LTC3555EUFD#TRPBF   | 3555          | 28-Lead (4mm x 5mm) Plastic QFN | –40°C to 85°C     |

| LTC3555IUFD#PBF   | LTC3555IUFD#TRPBF   | 3555          | 28-Lead (4mm x 5mm) Plastic QFN | -40°C to 85°C     |

| LTC3555EUFD-1#PBF | LTC3555EUFD-1#TRPBF | 35551         | 28-Lead (4mm x 5mm) Plastic QFN | -40°C to 85°C     |

| LTC3555IUFD-1#PBF | LTC3555IUFD-1#TRPBF | 35551         | 28-Lead (4mm x 5mm) Plastic QFN | -40°C to 85°C     |

| LTC3555EUFD-3#PBF | LTC3555EUFD-3#TRPBF | 35553         | 28-Lead (4mm x 5mm) Plastic QFN | -40°C to 85°C     |

| LTC3555IUFD-3#PBF | LTC3555IUFD-3#TRPBF | 35553         | 28-Lead (4mm x 5mm) Plastic QFN | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

# **ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating

temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C.  $V_{BUS} = 5V$ , BAT = 3.8V,  $DV_{CC} = 3.3V$ ,  $R_{PROG} = 1k$ ,  $R_{CLPROG} = 3k$ , unless otherwise noted.

| SYMBOL                        | PARAMETER                          | CONDITIONS                                                                                                                                     | CONDITIONS  |                          | ТҮР                      | MAX                        | UNITS                |  |

|-------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------|--------------------------|----------------------------|----------------------|--|

| PowerPath Switching Regulator |                                    |                                                                                                                                                |             |                          |                          |                            |                      |  |

| V <sub>BUS</sub>              | Input Supply Voltage               |                                                                                                                                                |             | 4.35                     |                          | 5.5                        | V                    |  |

| I <sub>BUSLIM</sub>           | Total Input Current                | 1x Mode, V <sub>OUT</sub> = BAT<br>5x Mode, V <sub>OUT</sub> = BAT<br>10x Mode, V <sub>OUT</sub> = BAT<br>Suspend Mode, V <sub>OUT</sub> = BAT | •<br>•<br>• | 87<br>436<br>800<br>0.31 | 95<br>460<br>860<br>0.38 | 100<br>500<br>1000<br>0.50 | mA<br>mA<br>mA<br>mA |  |

| I <sub>VBUSQ</sub>            | V <sub>BUS</sub> Quiescent Current | 1x Mode, I <sub>OUT</sub> = 0mA<br>5x Mode, I <sub>OUT</sub> = 0mA<br>10x Mode, I <sub>OUT</sub> = 0mA<br>Suspend Mode, I <sub>OUT</sub> = 0mA |             |                          | 7<br>15<br>15<br>0.044   |                            | mA<br>mA<br>mA<br>mA |  |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>BUS</sub> = 5V, BAT = 3.8V, DV<sub>CC</sub> = 3.3V, R<sub>PROG</sub> = 1k, R<sub>CLPROG</sub> = 3k, unless otherwise noted.

| SYMBOL                          | PARAMETER                                                            | CONDITIONS                                                                                                                                                   |   | MIN                              | TYP                              | MAX                              | UNITS                            |

|---------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------------------|----------------------------------|----------------------------------|----------------------------------|

| h <sub>CLPROG</sub><br>(Note 4) | Ratio of Measured V <sub>BUS</sub> Current to CLPROG Program Current | 1x Mode<br>5x Mode<br>10x Mode<br>Suspend Mode                                                                                                               |   |                                  | 224<br>1133<br>2140<br>11.3      |                                  | mA/mA<br>mA/mA<br>mA/mA<br>mA/mA |

| I <sub>OUT(POWERPATH)</sub>     | V <sub>OUT</sub> Current Available Before<br>Loading BAT             | 1x Mode, BAT = 3.3V<br>5x Mode, BAT = 3.3V<br>10x Mode, BAT = 3.3V<br>Suspend Mode                                                                           |   |                                  | 135<br>672<br>1251<br>0.32       |                                  | mA<br>mA<br>mA<br>mA             |

| V <sub>CLPROG</sub>             | CLPROG Servo Voltage in Current<br>Limit                             | 1x, 5x, 10x Modes<br>Suspend Mode                                                                                                                            |   |                                  | 1.188<br>100                     |                                  | V<br>mV                          |

| V <sub>UVLO_VBUS</sub>          | V <sub>BUS</sub> Undervoltage Lockout                                | Rising Threshold<br>Falling Threshold                                                                                                                        |   | 3.95                             | 4.30<br>4.00                     | 4.35                             | V<br>V                           |

| V <sub>UVLO_VBUS-BAT</sub>      | V <sub>BUS</sub> to BAT Differential Undervoltage<br>Lockout         | Rising Threshold<br>Falling Threshold                                                                                                                        |   |                                  | 200<br>50                        |                                  | mV<br>mV                         |

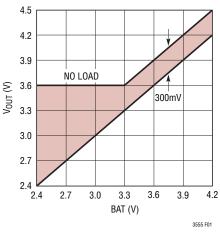

| V <sub>OUT</sub>                | V <sub>OUT</sub> Voltage                                             | 1x, 5x, 10x Modes, 0V < BAT < 4.2V,<br>I <sub>OUT</sub> = 0mA, Battery Charger Off                                                                           |   | 3.4                              | BAT + 0.3                        | 4.7                              | V                                |

|                                 |                                                                      | USB Suspend Mode, $I_{VOUT} = 250 \mu A$                                                                                                                     |   | 4.5                              | 4.6                              | 4.7                              | V                                |

| f <sub>OSC</sub>                | Switching Frequency                                                  |                                                                                                                                                              |   | 1.8                              | 2.25                             | 2.7                              | MHz                              |

| R <sub>PMOS_POWERPATH</sub>     | PMOS On Resistance                                                   |                                                                                                                                                              |   |                                  | 0.18                             |                                  | Ω                                |

| R <sub>NMOS_POWERPATH</sub>     | NMOS On Resistance                                                   |                                                                                                                                                              |   |                                  | 0.30                             |                                  | Ω                                |

| PEAK_POWERPATH                  | Peak Switch Current Limit                                            | 1x, 5x Modes<br>10x                                                                                                                                          |   |                                  | 2<br>3                           |                                  | A<br>A                           |

| Battery Charger                 |                                                                      |                                                                                                                                                              |   |                                  |                                  |                                  |                                  |

| V <sub>FLOAT</sub>              | BAT Regulated Output Voltage                                         | LTC3555/LTC3555-1<br>LTC3555/LTC3555-1<br>LTC3555-3<br>LTC3555-3                                                                                             | • | 4.179<br>4.165<br>4.079<br>4.065 | 4.200<br>4.200<br>4.100<br>4.100 | 4.221<br>4.235<br>4.121<br>4.135 | V<br>V<br>V<br>V                 |

| I <sub>CHG</sub>                | Constant Current Mode Charge<br>Current                              | R <sub>PROG</sub> = 1k<br>R <sub>PROG</sub> = 5k                                                                                                             |   | 980<br>185                       | 1022<br>204                      | 1065<br>223                      | mA<br>mA                         |

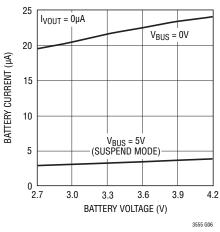

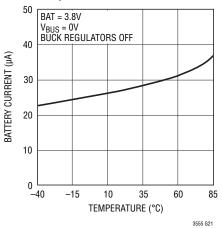

| I <sub>BAT</sub>                | Battery Drain Current                                                | $V_{BUS} > V_{UVLO}$ , Battery Charger Off, $I_{VOUT} = 0\mu A$<br>$V_{BUS} = 0V$ , $I_{VOUT} = 0\mu A$ (Ideal Diode Mode)<br>LTC3555<br>LTC3555-1/LTC3555-3 |   | 2                                | 3.5<br>27<br>32                  | 5<br>38<br>44                    | μΑ<br>μΑ<br>μΑ                   |

| V <sub>PROG</sub>               | PROG Pin Servo Voltage                                               |                                                                                                                                                              |   |                                  | 1.000                            |                                  | V                                |

| V <sub>PROG_TRKL</sub>          | PROG Pin Servo Voltage in Trickle<br>Charge                          | BAT < V <sub>TRKL</sub>                                                                                                                                      |   |                                  | 0.100                            |                                  | V                                |

| V <sub>C/10</sub>               | C/10 Threshold Voltage at PROG                                       |                                                                                                                                                              |   |                                  | 100                              |                                  | mV                               |

| h <sub>PROG</sub>               | Ratio of I <sub>BAT</sub> to PROG Pin Current                        |                                                                                                                                                              |   |                                  | 1022                             |                                  | mA/mA                            |

| I <sub>TRKL</sub>               | Trickle Charge Current                                               | BAT < V <sub>TRKL</sub>                                                                                                                                      |   |                                  | 100                              |                                  | mA                               |

| V <sub>TRKL</sub>               | Trickle Charge Threshold Voltage                                     | BAT Rising                                                                                                                                                   |   | 2.7                              | 2.85                             | 3.0                              | V                                |

| $\Delta V_{TRKL}$               | Trickle Charge Hysteresis Voltage                                    |                                                                                                                                                              |   |                                  | 135                              |                                  | mV                               |

| $\Delta V_{\text{RECHRG}}$      | Recharge Battery Threshold Voltage                                   | Threshold Voltage Relative to V <sub>FLOAT</sub>                                                                                                             |   | -75                              | -100                             | -125                             | mV                               |

| t <sub>TERM</sub>               | Safety Timer Termination                                             | Timer Starts when BAT = V <sub>FLOAT</sub>                                                                                                                   |   | 3.3                              | 4                                | 5                                | Hour                             |

| t <sub>BADBAT</sub>             | Bad Battery Termination Time                                         | BAT < V <sub>TRKL</sub>                                                                                                                                      |   | 0.42                             | 0.5                              | 0.63                             | Hour                             |

| h <sub>C/10</sub>               | End of Charge Indication Current Ratio                               | 1                                                                                                                                                            |   | 0.088                            | 0.1                              | 0.112                            | mA/mA                            |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>BUS</sub> = 5V, BAT = 3.8V, DV<sub>CC</sub> = 3.3V, R<sub>PROG</sub> = 1k, R<sub>CLPROG</sub> = 3k, unless otherwise noted.

| SYMBOL                                      | PARAMETER                                                                     | CONDITIONS                                              | MIN     | ТҮР         | MAX  | UNITS                                  |

|---------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------|---------|-------------|------|----------------------------------------|

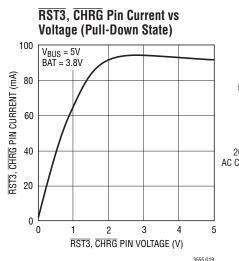

| V <sub>CHRG</sub>                           | CHRG Pin Output Low Voltage                                                   | I <sub>CHRG</sub> = 5mA                                 |         | 65          | 100  | mV                                     |

| ICHRG                                       | CHRG Pin Leakage Current                                                      | V <sub>CHRG</sub> = 5V                                  |         |             | 1    | μA                                     |

| R <sub>ON_CHG</sub>                         | Battery Charger Power FET On<br>Resistance (Between V <sub>OUT</sub> and BAT) |                                                         |         | 0.18        |      | Ω                                      |

| T <sub>LIM</sub>                            | Junction Temperature in Constant<br>Temperature Mode                          |                                                         |         | 110         |      | °C                                     |

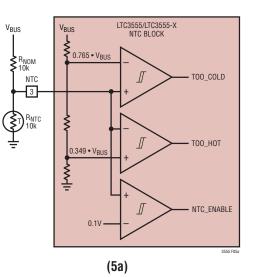

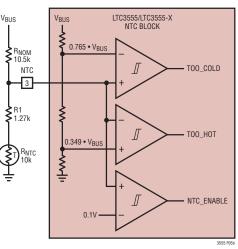

| NTC                                         |                                                                               |                                                         | · · ·   |             |      |                                        |

| V <sub>COLD</sub>                           | Cold Temperature Fault Threshold<br>Voltage                                   | Rising Threshold<br>Hysteresis                          | 75.0    | 76.5<br>1.5 | 78.0 | %V <sub>BUS</sub><br>%V <sub>BUS</sub> |

| V <sub>HOT</sub>                            | Hot Temperature Fault Threshold<br>Voltage                                    | Falling Threshold<br>Hysteresis                         | 33.4    | 34.9<br>1.5 | 36.4 | %V <sub>BUS</sub><br>%V <sub>BUS</sub> |

| V <sub>DIS</sub>                            | NTC Disable Threshold Voltage                                                 | Falling Threshold<br>Hysteresis                         | 0.7     | 1.7<br>50   | 2.7  | %V <sub>BUS</sub><br>mV                |

| I <sub>NTC</sub>                            | NTC Leakage Current                                                           | $V_{NTC} = V_{BUS} = 5V$                                | -50     |             | 50   | nA                                     |

| ldeal Diode                                 |                                                                               |                                                         | <b></b> |             |      |                                        |

| V <sub>FWD</sub>                            | Forward Voltage                                                               | $V_{BUS} = 0V$ , $I_{VOUT} = 10mA$<br>$I_{VOUT} = 10mA$ |         | 2<br>15     |      | mV<br>mV                               |

| R <sub>DROPOUT</sub>                        | Internal Diode On Resistance, Dropout                                         | V <sub>BUS</sub> = 0V                                   |         | 0.18        |      | Ω                                      |

| I <sub>MAX_DIODE</sub>                      | Internal Diode Current Limit                                                  |                                                         | 1.6     |             |      | A                                      |

| Always On 3.3V L                            | DO Supply                                                                     | 1                                                       |         |             |      |                                        |

| V <sub>LDO3V3</sub>                         | Regulated Output Voltage                                                      | 0mA < I <sub>LD03V3</sub> < 25mA                        | 3.1     | 3.3         | 3.5  | V                                      |

| R <sub>CL_LD03V3</sub>                      | Closed-Loop Output Resistance                                                 |                                                         | 4       |             |      | Ω                                      |

| R <sub>OL_LDO3V3</sub>                      | Dropout Output Resistance                                                     |                                                         |         | 23          |      | Ω                                      |

| Logic (I <sub>LIMO</sub> , I <sub>LIM</sub> | 1, EN1, EN2, EN3)                                                             | 1                                                       |         |             |      | 1                                      |

| V <sub>IL</sub>                             | Logic Low Input Voltage                                                       |                                                         |         |             | 0.4  | V                                      |

| V <sub>IH</sub>                             | Logic High Input Voltage                                                      |                                                         | 1.2     |             |      | V                                      |

| I <sub>PD1</sub>                            | I <sub>LIM0</sub> , I <sub>LIM1</sub> , EN1, EN2, EN3<br>Pull-Down Currents   |                                                         |         | 2           |      | μA                                     |

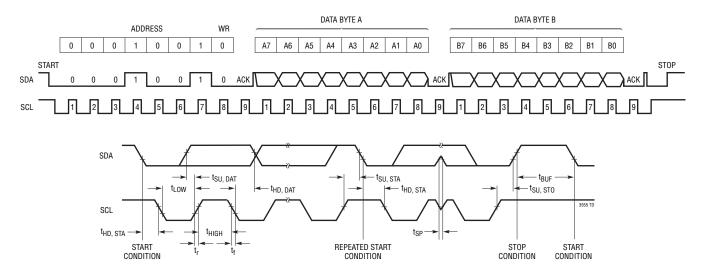

| I <sup>2</sup> C Port                       |                                                                               |                                                         |         |             |      |                                        |

| DV <sub>CC</sub>                            | Input Supply Voltage                                                          |                                                         | 1.6     |             | 5.5  | V                                      |

| IDVCC                                       | DV <sub>CC</sub> Current                                                      | SCL/SDA = 0kHz                                          |         | 0.5         |      | μA                                     |

| V <sub>DVCC_UVLO</sub>                      | DV <sub>CC</sub> UVLO                                                         |                                                         |         | 1.0         |      | V                                      |

| ADDRESS                                     | l <sup>2</sup> C Address                                                      |                                                         |         | 0001 001[0  | ]    |                                        |

| V <sub>IH</sub> , SDA, SCL                  | Input High Threshold                                                          |                                                         | 70      |             |      | %DV <sub>CC</sub>                      |

| V <sub>IL</sub> , SDA, SCL                  | Input Low Threshold                                                           |                                                         |         |             | 30   | %DV <sub>CC</sub>                      |

| I <sub>PD2</sub> SDA, SCL                   | Pull-Down Current                                                             |                                                         |         | 2           |      | μA                                     |

| V <sub>OL</sub>                             | Digital Output Low (SDA)                                                      | I <sub>PULLUP</sub> = 3mA                               |         |             | 0.4  | V                                      |

| f <sub>SCL</sub>                            | Clock Operating Frequency                                                     |                                                         |         |             | 400  | kHz                                    |

| t <sub>BUF</sub>                            | Bus Free Time Between Stop and Start<br>Condition                             |                                                         | 1.3     |             |      | μs                                     |

| t <sub>hd_sta</sub>                         | Hold Time After (Repeated) Start<br>Condition                                 |                                                         | 0.6     |             |      | μs                                     |

| t <sub>SU_STA</sub>                         | Repeated Start Condition Setup Time                                           |                                                         | 0.6     |             |      | μs                                     |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>BUS</sub> = 5V, BAT = 3.8V, DV<sub>CC</sub> = 3.3V, R<sub>PROG</sub> = 1k, R<sub>CLPROG</sub> = 3k, unless otherwise noted.

| SYMBOL                   | PARAMETER                                                                                                                                                     | CONDITIONS                                                                                                                                                                                    |   | MIN             | ТҮР                   | MAX                 | UNITS                      |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------|-----------------------|---------------------|----------------------------|

| t <sub>su_std</sub>      | Stop Condition Time                                                                                                                                           |                                                                                                                                                                                               |   | 0.6             |                       |                     | μs                         |

| t <sub>HD_DAT(OUT)</sub> | Data Hold Time                                                                                                                                                |                                                                                                                                                                                               |   | 225             |                       |                     | ns                         |

| t <sub>HD_DAT(IN)</sub>  | Input Data Hold Time                                                                                                                                          |                                                                                                                                                                                               |   | 0               |                       | 900                 | ns                         |

| t <sub>SU_DAT</sub>      | Data Setup Time                                                                                                                                               |                                                                                                                                                                                               |   | 100             |                       |                     | ns                         |

| t <sub>LOW</sub>         | Clock Low Period                                                                                                                                              |                                                                                                                                                                                               |   | 1.3             |                       |                     | μs                         |

| t <sub>HIGH</sub>        | Clock High Period                                                                                                                                             |                                                                                                                                                                                               |   | 0.6             |                       |                     | μs                         |

| t <sub>f</sub>           | Clock Data Fall Time                                                                                                                                          |                                                                                                                                                                                               |   | 20              |                       | 300                 | ns                         |

| t <sub>r</sub>           | Clock Data Rise Time                                                                                                                                          |                                                                                                                                                                                               |   | 20              |                       | 300                 | ns                         |

| t <sub>SP</sub>          | Spike Suppression Time                                                                                                                                        |                                                                                                                                                                                               |   |                 |                       | 50                  | ns                         |

| General Purpos           | e Switching Regulators 1, 2 and 3                                                                                                                             |                                                                                                                                                                                               |   |                 |                       |                     | 1                          |

| V <sub>IN1,2,3</sub>     | Input Supply Voltage                                                                                                                                          |                                                                                                                                                                                               |   | 2.7             |                       | 5.5                 | V                          |

| V <sub>OUTUVLO</sub>     | V <sub>OUT</sub> UVLO—V <sub>OUT</sub> Falling<br>V <sub>OUT</sub> UVLO—V <sub>OUT</sub> Rising                                                               | V <sub>IN1,2,3</sub> Connected to V <sub>OUT</sub> Through Low<br>Impedance. Switching Regulators are Disabled in<br>UVLO                                                                     |   | 2.5             | 2.6<br>2.8            | 2.9                 | V<br>V                     |

| f <sub>OSC</sub>         | Oscillator Frequency                                                                                                                                          |                                                                                                                                                                                               |   | 1.8             | 2.25                  | 2.7                 | MHz                        |

| I <sub>FB1,2,3</sub>     | FBx Input Current                                                                                                                                             | V <sub>FB1,2,3</sub> = 0.85V                                                                                                                                                                  |   | -50             |                       | 50                  | nA                         |

| D <sub>1,2,3</sub>       | Maximum Duty Cycle                                                                                                                                            |                                                                                                                                                                                               |   | 100             |                       |                     | %                          |

| R <sub>SW1,2,3_PD</sub>  | SWx Pull-Down in Shutdown                                                                                                                                     |                                                                                                                                                                                               |   |                 | 10                    |                     | kΩ                         |

| General Purpos           | e Switching Regulator 1                                                                                                                                       |                                                                                                                                                                                               |   |                 |                       |                     |                            |

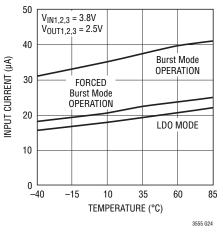

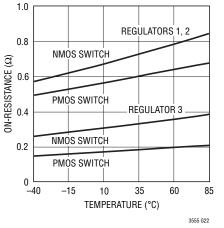

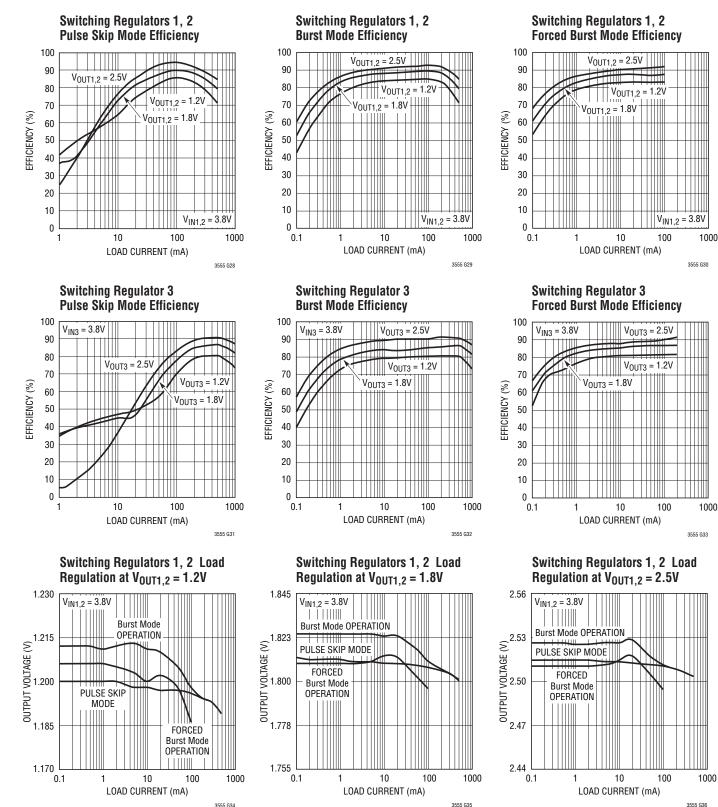

| I <sub>VIN1</sub>        | Pulse Skip Mode Input Current<br>Burst Mode Input Current<br>Forced Burst Mode <sup>®</sup> Input Current<br>LDO Mode Input Current<br>Shutdown Input Current | $I_{OUT1} = 0\mu A \text{ (Note 6)}$<br>$I_{OUT1} = 0\mu A, FB1 = 0V$ |   |                 | 225<br>35<br>20<br>20 | 60<br>35<br>35<br>1 | Ац<br>Ац<br>Ац<br>Ац<br>Ац |

| ILIMSW1                  | PMOS Switch Current Limit                                                                                                                                     | Pulse Skip/Burst Mode Operation                                                                                                                                                               |   | 600             | 800                   | 1100                | mA                         |

| I <sub>OUT1</sub>        | Available Output Current                                                                                                                                      | Pulse Skip/Burst Mode Operation (Note 7)<br>Forced Burst Mode Operation (Note 7)<br>LDO Mode (Note 7)                                                                                         |   | 400<br>60<br>50 |                       |                     | mA<br>mA<br>mA             |

| V <sub>FB1</sub>         | V <sub>FB1</sub> Servo Voltage                                                                                                                                | (Note 8)                                                                                                                                                                                      | • | 0.78            | 0.80                  | 0.82                | V                          |

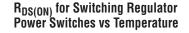

| R <sub>P1</sub>          | PMOS R <sub>DS(ON)</sub>                                                                                                                                      |                                                                                                                                                                                               |   |                 | 0.6                   |                     | Ω                          |

| R <sub>N1</sub>          | NMOS R <sub>DS(ON)</sub>                                                                                                                                      |                                                                                                                                                                                               |   |                 | 0.7                   |                     | Ω                          |

| R <sub>LDO_CL1</sub>     | LDO Mode Closed-Loop R <sub>OUT</sub>                                                                                                                         |                                                                                                                                                                                               |   |                 | 0.25                  |                     | Ω                          |

| R <sub>LDO_OL1</sub>     | LDO Mode Open-Loop R <sub>OUT</sub>                                                                                                                           | (Note 9)                                                                                                                                                                                      |   |                 | 2.5                   |                     | Ω                          |

| <b>General Purpos</b>    | e Switching Regulator 2                                                                                                                                       | · · · ·                                                                                                                                                                                       |   |                 |                       |                     |                            |

| I <sub>VIN2</sub>        | Pulse Skip Mode Input Current<br>Burst Mode Input Current<br>Forced Burst Mode Input Current<br>LDO Mode Input Current<br>Shutdown Input Current              |                                                                                                                                                                                               |   |                 | 225<br>35<br>20<br>20 | 60<br>35<br>35<br>1 | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ |

| ILIMSW2                  | PMOS Switch Current Limit                                                                                                                                     | Pulse Skip/Burst Mode Operation                                                                                                                                                               |   | 600             | 800                   | 1100                | mA                         |

| I <sub>OUT2</sub>        | Available Output Current                                                                                                                                      | Pulse Skip/Burst Mode Operation (Note 7)<br>Forced Burst Mode Operation (Note 7)<br>LDO Mode (Note 7)                                                                                         |   | 400<br>60<br>50 |                       |                     | mA<br>mA<br>mA             |

## **ELECTRICAL CHARACTERISTICS**

The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{BUS} = 5V$ , BAT = 3.8V,  $DV_{CC} = 3.3V$ ,  $R_{PROG} = 1k$ ,  $R_{CLPROG} = 3k$ , unless otherwise noted.

| SYMBOL               | PARAMETER                                                                                                                                        | CONDITIONS                                                                                            |   | MIN               | ТҮР                   | MAX                 | UNITS                |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---|-------------------|-----------------------|---------------------|----------------------|

| V <sub>FBHIGH2</sub> | Maximum Servo Voltage                                                                                                                            | Full Scale (1, 1, 1, 1) (Note 8)                                                                      |   | 0.78              | 0.80                  | 0.82                | V                    |

| V <sub>FBLOW2</sub>  | Minimum Servo Voltage                                                                                                                            | Zero Scale (0, 0, 0, 0) (Note 8)                                                                      |   | 0.405             | 0.425                 | 0.445               | V                    |

| V <sub>LSB2</sub>    | V <sub>FB2</sub> Servo Voltage Step Size                                                                                                         |                                                                                                       |   |                   | 25                    |                     | mV                   |

| R <sub>P2</sub>      | PMOS R <sub>DS(ON)</sub>                                                                                                                         |                                                                                                       |   |                   | 0.6                   |                     | Ω                    |

| R <sub>N2</sub>      | NMOS R <sub>DS(ON)</sub>                                                                                                                         |                                                                                                       |   |                   | 0.7                   |                     | Ω                    |

| R <sub>LDO_CL2</sub> | LDO Mode Closed-Loop R <sub>OUT</sub>                                                                                                            |                                                                                                       |   |                   | 0.25                  |                     | Ω                    |

| R <sub>LD0_0L2</sub> | LDO Mode Open-Loop R <sub>OUT</sub>                                                                                                              | (Note 9)                                                                                              |   |                   | 2.5                   |                     | Ω                    |

| General Purpo        | ose Switching Regulator 3                                                                                                                        | - ·                                                                                                   |   |                   |                       |                     |                      |

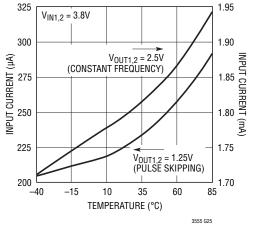

| I <sub>VIN3</sub>    | Pulse Skip Mode Input Current<br>Burst Mode Input Current<br>Forced Burst Mode Input Current<br>LDO Mode Input Current<br>Shutdown Input Current |                                                                                                       |   |                   | 225<br>35<br>20<br>20 | 60<br>35<br>35<br>1 | μΑ<br>μΑ<br>μΑ<br>μΑ |

| I <sub>LIMSW3</sub>  | PMOS Switch Current Limit                                                                                                                        | Pulse Skip/Burst Mode Operation                                                                       |   | 1500              | 2000                  | 2800                | mA                   |

| I <sub>OUT3</sub>    | Available Output Current                                                                                                                         | Pulse Skip/Burst Mode Operation (Note 7)<br>Forced Burst Mode Operation (Note 7)<br>LDO Mode (Note 7) |   | 1000<br>150<br>50 |                       |                     | mA<br>mA<br>mA       |

| V <sub>FBHIGH3</sub> | Maximum Servo Voltage                                                                                                                            | Full Scale (1, 1, 1, 1) (Note 8)                                                                      | • | 0.78              | 0.80                  | 0.82                | V                    |

| V <sub>FBLOW3</sub>  | Minimum Servo Voltage                                                                                                                            | Zero Scale (0, 0, 0, 0) (Note 8)                                                                      |   | 0.405             | 0.425                 | 0.445               | V                    |

| V <sub>LSB3</sub>    | V <sub>FB</sub> Servo Voltage Step Size                                                                                                          |                                                                                                       |   |                   | 25                    |                     | mV                   |

| R <sub>P3</sub>      | PMOS R <sub>DS(ON)</sub>                                                                                                                         |                                                                                                       |   |                   | 0.18                  |                     | Ω                    |

| R <sub>N3</sub>      | NMOS R <sub>DS(ON)</sub>                                                                                                                         |                                                                                                       |   |                   | 0.30                  |                     | Ω                    |

| R <sub>LDOCL3</sub>  | LDO Mode Closed Loop R <sub>OUT</sub>                                                                                                            |                                                                                                       |   |                   | 0.25                  |                     | Ω                    |

| R <sub>LD00L3</sub>  | LDO Mode Open Loop R <sub>OUT</sub>                                                                                                              | (Note 9)                                                                                              |   |                   | 2.5                   |                     | Ω                    |

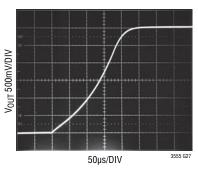

| t <sub>RST3</sub>    | Power On Reset Time for Switching Regulator                                                                                                      | $V_{FB3}$ Within 92% of Final Value to $\overline{RST3}$ Hi-Z                                         |   |                   | 230                   |                     | ms                   |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: The LTC3555E/LTC3555E-X are guaranteed to meet performance specifications from 0°C to 85°C. Specifications over the -40°C to 85°C operating temperature range are assured by design, characterization and correlation with statistical process controls. The LTC35551/LTC35551-X are guaranteed to meet performance specifications over the full -40°C to 85°C operating temperature range.

Note 3: The LTC3555/LTC3555-X include overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 125°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

Note 4: Total input current is the sum of quiescent current, IVBUSO, and measured current given by:

$V_{CLPROG}/R_{CLPROG} \bullet (h_{CLPROG} + 1)$

Note 5:  $h_{C/10}$  is expressed as a fraction of measured full charge current with indicated PROG resistor.

Note 6: FBx above regulation such that regulator is in sleep. Specification does not include resistive divider current reflected back to VINx.

Note 7: Guaranteed by design but not explicitly tested.

Note 8: Applies to pulse skip, Burst Mode operation and forced Burst Mode operation only.

Note 9: Inductor series resistance adds to open-loop R<sub>OUT</sub>.

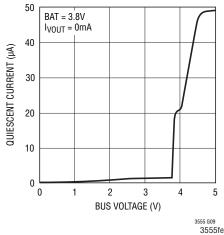

**Battery Drain Current** vs Battery Voltage

V<sub>BUS</sub> Current vs V<sub>BUS</sub> Voltage (Suspend)

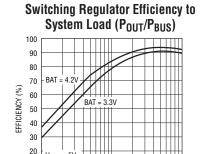

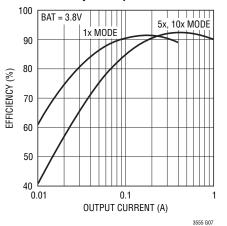

**PowerPath Switching Regulator** Efficiency vs Output Current

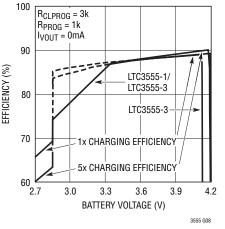

BATTERY VOLTAGE (V)

3.6

LTC3555-3

3.9

4.2

3555 G04

**Battery Charging Efficiency vs** Battery Voltage with No External Load (PBAT/PBUS)

300

200

100

0

2.7

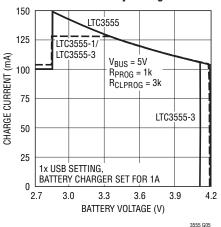

5x USB SETTING.

3.0

BATTERY CHARGER SET FOR 1A

3.3

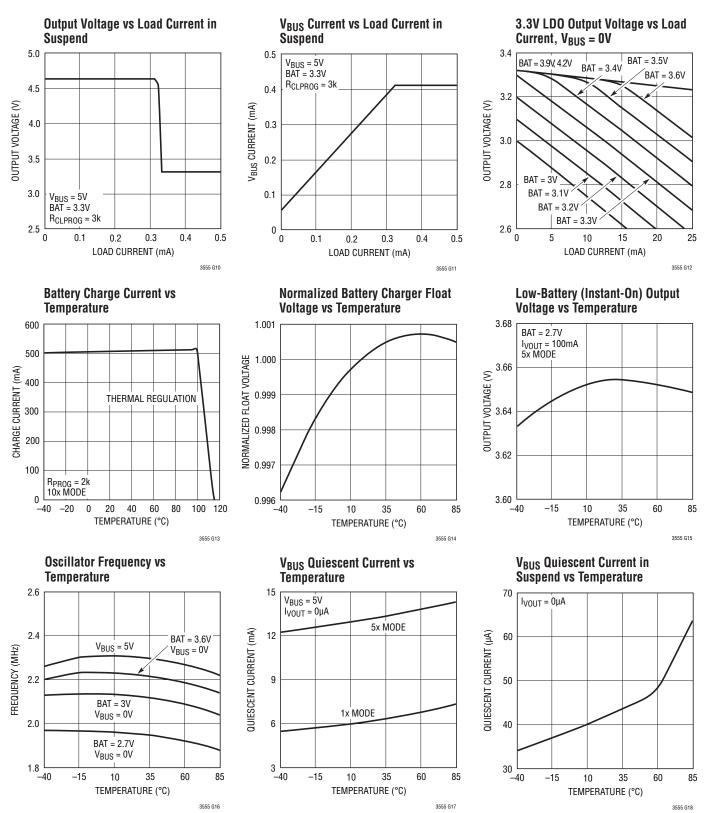

3.3V LDO Step Response (5mA to 15mA)

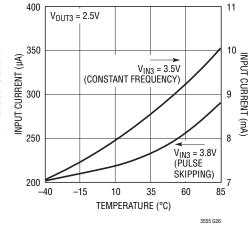

Switching Regulator Current Limit

REGULATOR 3

REGULATORS 1, 2

10

TEMPERATURE (°C)

vs Temperature

V<sub>IN1,2,3</sub> = 3.8V

-15

2.0

1.5

1.0

0.5

0

-40

CURRENT LIMIT (A)

Battery Drain Current vs Temperature

Switching Regulator Low Power Mode Quiescent Currents

Switching Regulator Soft-Start Waveform

3555fe

#### Switching Regulator 3 Pulse Skip Mode Quiescent Currents

35

60

85

3555 G23

# PIN FUNCTIONS

**LD03V3 (Pin 1):** 3.3V LD0 Output Pin. This pin provides a regulated always-on 3.3V supply voltage. LD03V3 gets its power from  $V_{OUT}$ . It may be used for light loads such as a watchdog microprocessor or real time clock. A 1µF capacitor is required from LD03V3 to ground. If the LD03V3 output is not used it should be disabled by connecting it to  $V_{OUT}$ .

**CLPROG (Pin 2):** USB Current Limit Program and Monitor Pin. A resistor from CLPROG to ground determines the upper limit of the current drawn from the  $V_{BUS}$  pin. A fraction of the  $V_{BUS}$  current is sent to the CLPROG pin when the synchronous switch of the PowerPath switching regulator is on. The switching regulator delivers power until the CLPROG pin reaches 1.188V. Several  $V_{BUS}$  current limit settings are available via user input which will typically correspond to the 500mA and 100mA USB specifications. A multi-layer ceramic averaging capacitor or R-C network is required at CLPROG for filtering.

**NTC (Pin 3):** Input to the Thermistor Monitoring Circuits. The NTC pin connects to a battery's thermistor to determine if the battery is too hot or too cold to charge. If the battery's temperature is out of range, charging is paused until it re-enters the valid range. A low drift bias resistor is required from  $V_{BUS}$  to NTC and a thermistor is required from NTC to ground. If the NTC function is not desired, the NTC pin should be grounded.

**FB2 (Pin 4):** Feedback Input for Switching Regulator 2. When regulator 2's control loop is complete, this pin servos to 1 of 16 possible set-points based on the commanded value from the  $l^2C$  serial port. See Table 4.

$V_{IN2}$  (Pin 5): Power Input for Switching Regulator 2. This pin will generally be connected to  $V_{OUT}$ . A 1µF MLCC capacitor is recommended on this pin.

**SW2 (Pin 6):** Power Transmission Pin for Switching Regulator 2.

**EN2 (Pin 7):** Logic Input. This logic input pin independently enables switching regulator 2. This pin is logically OR-ed with its corresponding bit in the I<sup>2</sup>C serial port. See Table 2.

$DV_{CC}$  (Pin 8): Logic Supply for the I<sup>2</sup>C Serial Port. If the serial port is not needed it can be disabled by grounding  $DV_{CC}$ . When  $DV_{CC}$  is grounded, chip control is automatically passed to the individual logic input pins.

**SCL (Pin 9):** Clock Input Pin for the  $I^2C$  Serial Port. The  $I^2C$  logic levels are scaled with respect to  $DV_{CC}$ . If  $DV_{CC}$  is grounded, the SCL pin is equivalent to the B5 bit in the  $I^2C$  serial port. SCL in conjunction with SDA determine the operating modes of switching regulators 1, 2 and 3 when  $DV_{CC}$  is grounded. See Tables 2 and 5.

**SDA (Pin 10):** Data Input Pin for the I<sup>2</sup>C Serial Port. The I<sup>2</sup>C logic levels are scaled with respect to  $DV_{CC}$ . If  $DV_{CC}$  is grounded, the SDA pin is equivalent to the B6 bit in the I<sup>2</sup>C serial port. SDA in conjunction with SCL determine the operating modes of switching regulators 1, 2 and 3 when  $DV_{CC}$  is grounded. See Tables 2 and 5.

$V_{IN3}$  (Pin 11): Power Input for Switching Regulator 3. This pin will generally be connected to  $V_{OUT}$ . A 1µF MLCC capacitor is recommended on this pin.

**SW3 (Pin 12):** Power Transmission Pin for Switching Regulator 3.

**EN3 (Pin 13):** Logic Input. This logic input pin independently enables switching regulator 3. This pin is logically OR-ed with its corresponding bit in the I<sup>2</sup>C serial port. See Table 2.

**FB3 (Pin 14):** Feedback Input for Switching Regulator 3. When regulator 3's control loop is complete, this pin servos to 1 of 16 possible set-points based on the commanded value from the  $I^2C$  serial port. See Table 4.

**RST3 (Pin 15):** Logic Output. This in an open-drain output which indicates that switching regulator 3 has settled to its final value. It can be used as a power-on reset for the primary microprocessor or to enable the other switching regulators for supply sequencing.

**EN1 (Pin 16):** Logic Input. This logic input pin independently enables switching regulator 1. This pin is logically OR-ed with its corresponding bit in the I<sup>2</sup>C serial port. See Table 2.

# PIN FUNCTIONS

**SW1 (Pin 17):** Power Transmission Pin for Switching Regulator 1.

$V_{IN1}$  (Pin 18): Power Input for Switching Regulator 1. This pin will generally be connected to  $V_{OUT}$ . A 1µF MLCC capacitor is recommended on this pin.

**FB1 (Pin 19):** Feedback Input for Switching Regulator 1. When regulator 1's control loop is complete, this pin servos to a fixed voltage of 0.8V.

**PROG (Pin 20):** Charge Current Program and Charge Current Monitor Pin. Connecting a resistor from PROG to ground programs the charge current. If sufficient input power is available in constant-current mode, this pin servos to 1V. The voltage on this pin always represents the actual charge current.

**CHRG** (Pin 21): Open-Drain Charge Status Output. The CHRG pin indicates the status of the battery charger. Four possible states are represented by CHRG: charging, not charging, unresponsive battery and battery temperature out of range. CHRG is modulated at 35kHz and switches between a low and a high duty cycle for easy recognition by either humans or microprocessors. See Table 1. CHRG requires a pull-up resistor and/or LED to provide indication.

**GATE (Pin 22):** Analog Output. This pin controls the gate of an optional external P-channel MOSFET transistor used to supplement the ideal diode between  $V_{OUT}$  and BAT. The external ideal diode operates in parallel with the internal ideal diode. The source of the P-channel MOSFET should be connected to  $V_{OUT}$  and the drain should be connected to BAT. If the external ideal diode FET is not used, GATE should be left floating.

**BAT (Pin 23):** Single Cell Li-Ion Battery Pin. Depending on available  $V_{BUS}$  power, a Li-Ion battery on BAT will either deliver power to  $V_{OUT}$  through the ideal diode or be charged from  $V_{OUT}$  via the battery charger.

**V<sub>OUT</sub> (Pin 24):** Output voltage of the Switching PowerPath Controller and Input Voltage of the Battery Charger. The majority of the portable product should be powered from V<sub>OUT</sub>. The LTC3555 family will partition the available power between the external load on V<sub>OUT</sub> and the internal battery charger. Priority is given to the external load and any extra power is used to charge the battery. An ideal diode from BAT to V<sub>OUT</sub> ensures that V<sub>OUT</sub> is powered even if the load exceeds the allotted power from V<sub>BUS</sub> or if the V<sub>BUS</sub> power source is removed. V<sub>OUT</sub> should be bypassed with a low impedance ceramic capacitor.

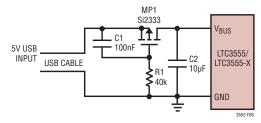

$V_{BUS}$  (Pin 25): Primary Input Power Pin. This pin delivers power to  $V_{OUT}$  via the SW pin by drawing controlled current from a DC source such as a USB port or wall adapter.

**SW (Pin 26):** Power Transmission Pin for the USB Power Path. The SW pin delivers power from  $V_{BUS}$  to  $V_{OUT}$  via the step-down switching regulator. A 3.3µH inductor should be connected from SW to  $V_{OUT}$ .

**I**<sub>LIM0</sub>, **I**<sub>LIM1</sub> (**Pins 27, 28**): Logic Inputs. I<sub>LIM0</sub> and I<sub>LIM1</sub> control the current limit of the PowerPath switching regulator. See Table 3. Both of the I<sub>LIM0</sub> and I<sub>LIM1</sub> pins are logically OR-ed with their corresponding bits in the I<sup>2</sup>C serial port. See Table 2.

**Exposed Pad (Pin 29):** Ground. The Exposed Pad should be connected to a continuous ground plane on the second layer of the printed circuit board by several vias directly under the part.

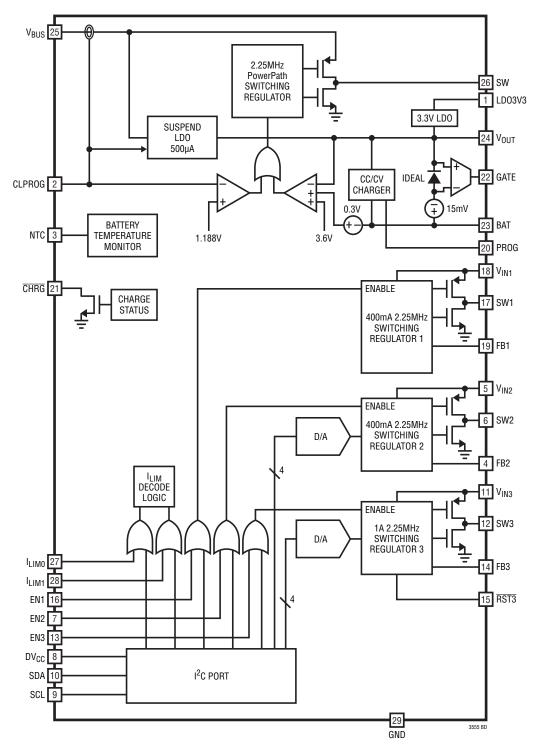

# **BLOCK DIAGRAM**

# TIMING DIAGRAM

### Introduction

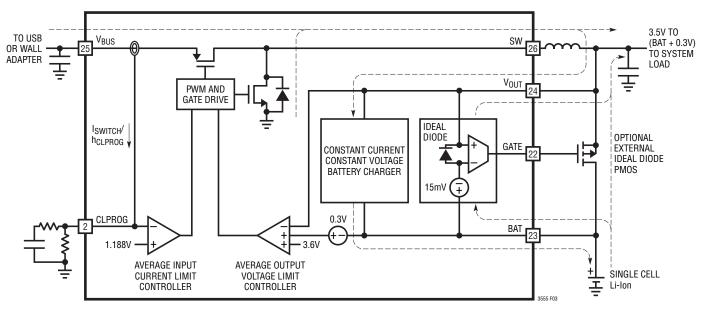

The LTC3555 family are highly integrated power management ICs which include a high efficiency switch mode PowerPath controller, a battery charger, an ideal diode, an always-on LDO and three general purpose step-down switching regulators. The entire chip is controlled by either direct digital control, by an I<sup>2</sup>C serial port or both.

Designed specifically for USB applications, the PowerPath controller incorporates a precision average input current step-down switching regulator to make maximum use of the allowable USB power. Because power is conserved, the LTC3555 family allows the load current on  $V_{OUT}$  to exceed the current drawn by the USB port without exceeding the USB load specifications.

The PowerPath switching regulator and battery charger communicate to ensure that the input current never violates the USB specifications.

The ideal diode from BAT to  $V_{OUT}$  guarantees that ample power is always available to  $V_{OUT}$  even if there is insufficient or absent power at  $V_{BUS}.$

An "always on" LDO provides a regulated 3.3V from available power at  $V_{OUT}$ . Drawing very little quiescent current, this LDO will be on at all times and can be used to supply up to 25mA.

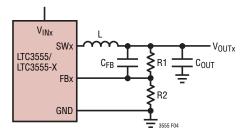

The three general purpose switching regulators can be independently enabled via either direct digital control or by operating the  $I^2C$  serial port. Under  $I^2C$  control, two of the three switching regulators have adjustable set-points so that voltages can be reduced when high processor performance is not needed. Along with constant frequency PWM mode, all three switching regulators have a low power burst-only mode setting as well as automatic Burst Mode operation and LDO modes for significantly reduced quiescent current under light load conditions.

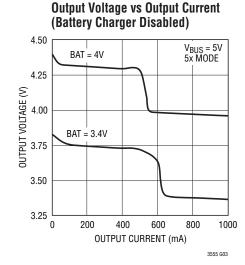

### High Efficiency Switching PowerPath Controller

Whenever  $V_{BUS}$  is available and the PowerPath switching regulator is enabled, power is delivered from  $V_{BUS}$  to  $V_{OUT}$  via SW.  $V_{OUT}$  drives the combination of the external load (switching regulators 1, 2 and 3) and the battery charger.

If the combined load does not exceed the PowerPath switching regulator's programmed input current limit,  $V_{OUT}$  will track 0.3V above the battery. By keeping the voltage across the battery charger low, efficiency is optimized because power lost to the linear battery charger is minimized. Power available to the external load is therefore optimized.

If the combined load at  $V_{OUT}$  is large enough to cause the switching power supply to reach the programmed input current limit, the battery charger will reduce its charge current by that amount necessary to enable the external load to be satisfied. Even if the battery charge current is set to exceed the allowable USB current, the USB specification will not be violated. The switching regulator will limit the average input current so that the USB specification is never violated. Furthermore, load current at  $V_{OUT}$  will always be prioritized and only excess available power will be used to charge the battery.

If the voltage at BAT is below 3.3V, or the battery is not present, and the load requirement does not cause the switching regulator to exceed the USB specification,  $V_{OUT}$  will regulate at 3.6V. If the load exceeds the available power,  $V_{OUT}$  will drop to a voltage between 3.6V and the battery voltage. If there is no battery present when the load exceeds the available USB power,  $V_{OUT}$  can drop toward ground.

The power delivered from  $V_{BUS}$  to  $V_{OUT}$  is controlled by a 2.25MHz constant-frequency step-down switching regulator. To meet the USB maximum load specification, the switching regulator includes a control loop which ensures that the average input current is below the level programmed at CLPROG.

The current at CLPROG is a fraction ( $h_{CLPROG}^{-1}$ ) of the V<sub>BUS</sub> current. When a programming resistor and an averaging capacitor are connected from CLPROG to GND, the voltage on CLPROG represents the average input current of the switching regulator. When the input current approaches the programmed limit, CLPROG reaches V<sub>CLPROG</sub>, 1.188V, and power out is held constant. The input current limit is programmed by the I<sub>LIMO</sub> and I<sub>LIM1</sub> pins or by the I<sup>2</sup>C serial port. It can be configured to limit average input current to one of several possible settings as well as be deactivated (USB suspend). The input current limit will be set by the V<sub>CLPROG</sub> servo voltage and the resistor on CLPROG according to the following expression:

$$I_{VBUS} = I_{VBUSQ} + \frac{V_{CLPROG}}{R_{CLPROG}} \bullet (h_{CLPROG} + 1)$$

Figure 1 shows the range of possible voltages at  $V_{\text{OUT}}$  as a function of battery voltage.

Figure 1. V<sub>OUT</sub> vs BAT

### The LTC3555 vs the LTC3555-1 and LTC3555-3

For very low battery voltages, the battery charger acts like a load and, due to limited input power, its current will tend to pull  $V_{OUT}$  below the 3.6V "instant-on" voltage. To prevent  $V_{OUT}$  from falling below this level, the LTC3555-1 and LTC3555-3 include an undervoltage circuit that automatic detects that  $V_{OUT}$  is falling and reduces the battery charge current as needed. This reduction ensures that load current and output voltage are always prioritized and yet delivers as much battery charge current as possible. The standard LTC3555 does not include this circuit and thus favors maximum charge current at all times over output voltage preservation.

If instant-on operation under low battery conditions is a requirement then the LTC3555-1 or LTC3555-3 should be used. If maximum charge efficiency at low battery voltages is preferred, and instant-on operation is not a requirement, then the standard LTC3555 should be selected. All versions of the LTC3555 family will start up with a removed battery.

The LTC3555-3 has a battery charger float voltage of 4.100V rather than the 4.200V float voltage of the LTC3555 and LTC3555-1.

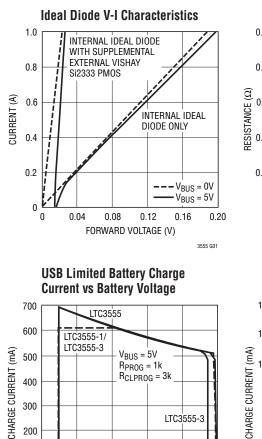

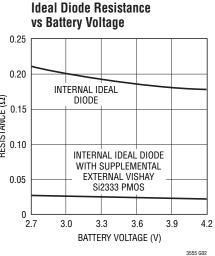

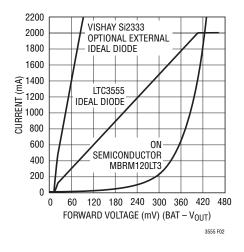

### Ideal Diode from BAT to $V_{\mbox{OUT}}$

The LTC3555 family has an internal ideal diode as well as a controller for an optional external ideal diode. The ideal diode controller is always on and will respond quickly whenever  $V_{OUT}$  drops below BAT.

3555fe

If the load current increases beyond the power allowed from the switching regulator, additional power will be pulled from the battery via the ideal diode. Furthermore, if power to V<sub>BUS</sub> (USB or wall power) is removed, then all of the application power will be provided by the battery via the ideal diode. The transition from input power to battery power at V<sub>OUT</sub> will be quick enough to allow only the 10µF capacitor to keep V<sub>OUT</sub> from drooping. The ideal diode consists of a precision amplifier that enables a large on-chip P-channel MOSFET transistor whenever the voltage at V<sub>OUT</sub> is approximately 15mV (V<sub>FWD</sub>) below the voltage

at BAT. The resistance of the internal ideal diode is approximately 180m  $\Omega$ . If this is sufficient for the application, then no external components are necessary. However, if more conductance is needed, an external P-channel MOSFET transistor can be added from BAT to V<sub>OUT</sub>.

When an external P-channel MOSFET transistor is present, the GATE pin of the LTC3555 family drives its gate for automatic ideal diode control. The source of the external P-channel MOSFET should be connected to  $V_{OUT}$  and the drain should be connected to BAT. Capable of driving a 1nF load, the GATE pin can control an external P-channel MOSFET transistor having an on-resistance of 40m $\Omega$  or lower.

### Suspend LDO

If the LTC3555 family is configured for USB suspend mode, the switching regulator is disabled and the suspend LDO provides power to the  $V_{OUT}$  pin (presuming there is power available to  $V_{BUS}$ ). This LDO will prevent the battery from running down when the portable product has access to a suspended USB port. Regulating at 4.6V, this LDO only becomes active when the switching converter is disabled (suspended). To remain compliant with the USB specification, the input to the LDO is current limited so that it will not exceed the 500µA low power suspend

specification. If the load on  $V_{\text{OUT}}$  exceeds the suspend current limit, the additional current will come from the battery via the ideal diode.

### 3.3V Always-On LDO Supply

The LTC3555 family includes a low quiescent current low dropout regulator that is always powered. This LDO can be used to provide power to a system pushbutton controller, standby microcontroller or real time clock. Designed to deliver up to 25mA, the always-on LDO requires at least a 1 $\mu$ F low impedance ceramic bypass capacitor for compensation. The LDO is powered from V<sub>OUT</sub>, and therefore will enter dropout at loads less than 25mA as V<sub>OUT</sub> falls near 3.3V. If the LDO3V3 output is not used, it should be disabled by connecting it to V<sub>OUT</sub>.

### V<sub>BUS</sub> Undervoltage Lockout (UVLO)

An internal undervoltage lockout circuit monitors V<sub>BUS</sub> and keeps the PowerPath switching regulator off until V<sub>BUS</sub> rises above 4.30V and is about 200mV above the battery voltage. Hysteresis on the UVLO turns off the regulator if V<sub>BUS</sub> drops below 4.00V or to within 50mV of BAT. When this happens, system power at V<sub>OUT</sub> will be drawn from the battery via the ideal diode.

### **Battery Charger**

The LTC3555 family includes a constant-current/ constant-voltage battery charger with automatic recharge, automatic termination by safety timer, low voltage trickle charging, bad cell detection and thermistor sensor input for out-of-temperature charge pausing.

### **Battery Preconditioning**

When a battery charge cycle begins, the battery charger first determines if the battery is deeply discharged. If the battery voltage is below  $V_{TRKL}$ , typically 2.85V, an automatic trickle charge feature sets the battery charge current to 10% of the programmed value. If the low voltage persists for more than 1/2 hour, the battery charger automatically terminates and indicates via the CHRG pin that the battery was unresponsive.

Once the battery voltage is above 2.85V, the battery charger begins charging in full power constant-current mode. The

current delivered to the battery will try to reach 1022V/ R<sub>PROG</sub>. Depending on available input power and external load conditions, the battery charger may or may not be able to charge at the full programmed rate. The external load will always be prioritized over the battery charge current. The USB current limit programming will always be observed and only additional power will be available to charge the battery. When system loads are light, battery charge current will be maximized.

### **Charge Termination**

The battery charger has a built-in safety timer. When the voltage on the battery reaches the pre-programmed float voltage, the battery charger will regulate the battery voltage and the charge current will decrease naturally. Once the battery charger detects that the battery has reached the float voltage, the four hour safety timer is started. After the safety timer expires, charging of the battery will discontinue and no more current will be delivered.

### **Automatic Recharge**

After the battery charger terminates, it will remain off drawing only microamperes of current from the battery. If the portable product remains in this state long enough, the battery will eventually self discharge. To ensure that the battery is always topped off, a charge cycle will automatically begin when the battery voltage falls below the recharge threshold which is typically 100mV less than the charger's float voltage. In the event that the safety timer is running when the battery voltage falls below the recharge threshold, it will reset back to zero. To prevent brief excursions below the recharge threshold from resetting the safety timer, the battery voltage must be below the recharge threshold for more than 1.3ms. The charge cycle and safety timer will also restart if the V<sub>BUS</sub> UVLO cycles low and then high (e.g., V<sub>BUS</sub> is removed and then replaced), or if the battery charger is cycled on and off by the I<sup>2</sup>C port.

### **Charge Current**

The charge current is programmed using a single resistor from PROG to ground. 1/1022th of the battery charge current is sent to PROG which will attempt to servo to 1.000V. Thus, the battery charge current will try to reach

1022 times the current in the PROG pin. The program resistor and the charge current are calculated using the following equations:

$R_{PROG} = \frac{1022V}{I_{CHG}}, I_{CHG} = \frac{1022V}{R_{PROG}}$

In either the constant-current or constant-voltage charging modes, the voltage at the PROG pin will be proportional to the actual charge current delivered to the battery. Therefore, the actual charge current can be determined at any time by monitoring the PROG pin voltage and using the following equation:

$$I_{BAT} = \frac{V_{PROG}}{R_{PROG}} \bullet 1022$$

In many cases, the actual battery charge current,  $I_{BAT},$  will be lower than  $I_{CHG}$  due to limited input power available and prioritization with the system load drawn from  $V_{OUT}.$

### **Charge Status Indication**

The  $\overline{\text{CHRG}}$  pin indicates the status of the battery charger. Four possible states are represented by  $\overline{\text{CHRG}}$  which include charging, not charging, unresponsive battery, and battery temperature out of range.

The signal at the CHRG pin can be easily recognized as one of the above four states by either a human or a microprocessor. An open-drain output, the CHRG pin can drive an indicator LED through a current limiting resistor for human interfacing or simply a pull-up resistor for microprocessor interfacing.

To make the CHRG pin easily recognized by both humans and microprocessors, the pin is either low for charging, high for not charging, or it is switched at high frequency (35kHz) to indicate the two possible faults, unresponsive battery and battery temperature out of range.

When charging begins, CHRG is pulled low and remains low for the duration of a normal charge cycle. When charging is complete, i.e., the BAT pin reaches the float voltage and the charge current has dropped to one tenth of the programmed value, the CHRG pin is released (Hi-Z). If a fault occurs, the pin is switched at 35kHz. While switching, its duty cycle is modulated between a low and high value at a very low frequency. The low and high duty cycles are disparate enough to make an LED appear to be on or off thus giving the appearance of "blinking". Each of the two faults has its own unique "blink" rate for human recognition as well as two unique duty cycles for machine recognition.