## FEATURES

- Full Featured Li-Ion/Polymer Charger/PowerPath™ Controller with Instant-On Operation

- Triple Adjustable High Efficiency Step-Down Switching Regulators (800mA, 500mA, 500mA I<sub>OUT</sub>)

- 6µA Battery Drain Current in Hard Reset

- Bat-Track<sup>™</sup> Control for External HV Buck DC/DCs

- I<sup>2</sup>C Adjustable SW Slew Rates for EMI Reduction

- High Temperature Battery Voltage Reduction Improves Safety and Reliability

- Overvoltage Protection for USB (V<sub>BUS</sub>)/Wall Inputs Provides Protection to 30V

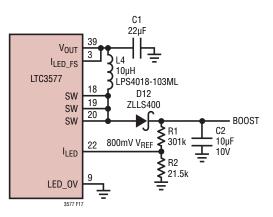

- Integrated 40V Series LED Backlight Driver with 60dB Brightness Control and Gradation via I<sup>2</sup>C

- 1.5A Maximum Charge Current with Thermal Limiting

- Battery Float Voltage: 4.2V (LTC3577)

- 4.1V (LTC3577-1)

- Pushbutton On/Off Control with System Reset

- Dual 150mA Current Limited LDOs

- Small 4mm × 7mm 44-Pin QFN Package

## **APPLICATIONS**

- PNDs, DMB/DVB-H; Digital/Satellite Radio; Media Players

- Portable Industrial/Medical Products

- Universal Remotes, Photo Viewers

- Other USB-Based Handheld Products

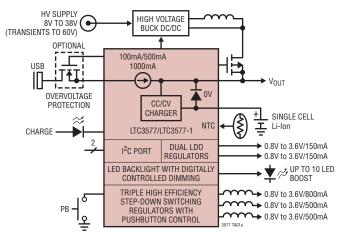

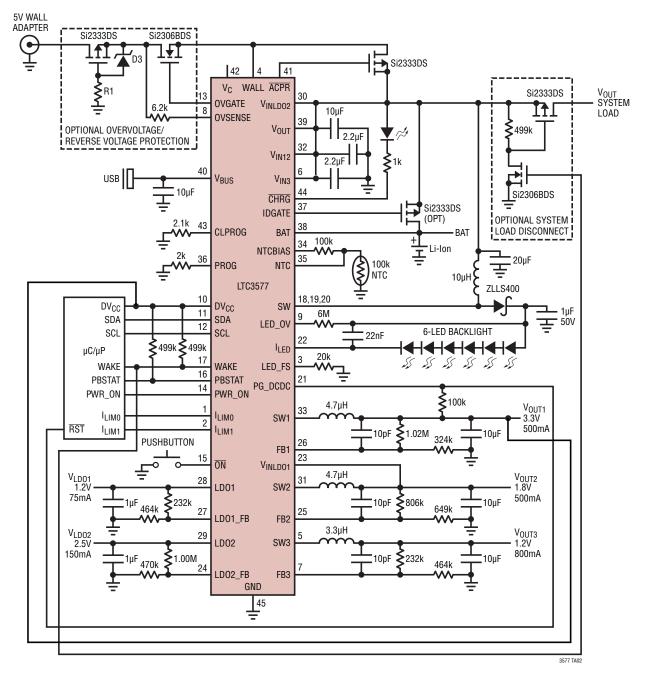

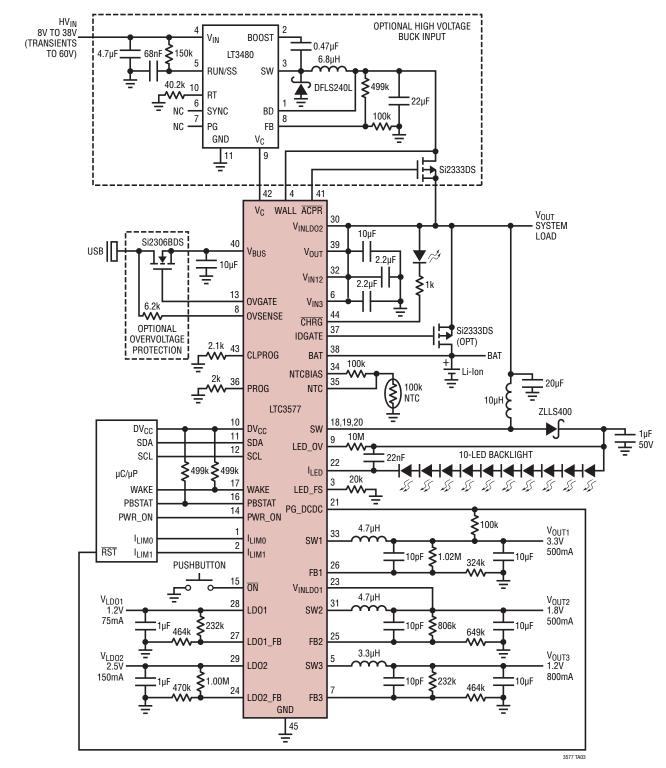

## TYPICAL APPLICATION

### LOGY Highly Integrated 6-Channel Portable PMIC DESCRIPTION

The LTC®3577 is a highly integrated power management IC for single cell Li-Ion/Polymer battery applications. It includes a PowerPath manager with automatic load prioritization, a battery charger, an ideal diode, input overvoltage protection and numerous other internal protection features. The LTC3577 is designed to accurately charge from current limited supplies such as USB by automatically reducing charge current such that the sum of the load current and the charge current does not exceed the programmed input current limit (100mA or 500mA modes). The LTC3577 reduces the battery voltage at elevated temperatures to improve safety and reliability. Efficient high current charging from supplies up to 38V is available using the on-chip Bat-Track controller. The LTC3577 also includes a pushbutton input to control the three synchronous step-down switching regulators and system reset. The onboard LED backlight boost circuitry can drive up to 10 series LEDs and includes versatile digital dimming via I<sup>2</sup>C input. The I<sup>2</sup>C input also controls two 150mA LDOs as well as other operating modes and status read back. The LTC3577 is available in a low profile  $4mm \times 7mm \times 0.75mm$  44-pin QFN package.

LTC3577/LTC3577-1

## TABLE OF CONTENTS

| Applications                            |

|-----------------------------------------|

| Typical Application                     |

| Description1                            |

| Absolute Maximum Ratings                |

|                                         |

| Order Information                       |

| Pin Configuration                       |

| Electrical Characteristics              |

| Typical Performance Characteristics     |

| Pin Functions                           |

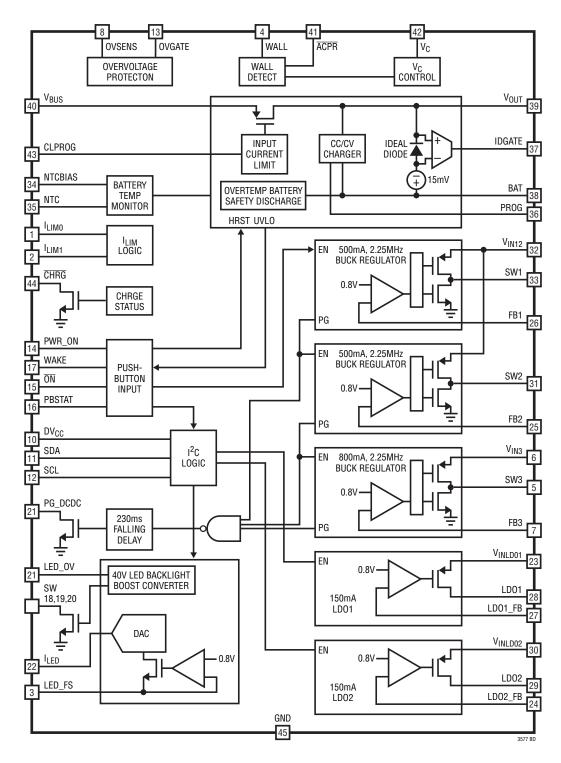

| Block Diagram                           |

| PowerPath Operation                     |

| Low Dropout Linear Regulator Operation  |

| Step-Down Switching Regulator Operation |

| LED Backlight/Boost Operation           |

| I <sup>2</sup> C Operation              |

| Pushbutton Interface Operation          |

| Layout and Thermal Considerations       |

| Typical Applications                    |

| Package Description                     |

| Related Parts                           |

| Revision History                        |

### **ABSOLUTE MAXIMUM RATINGS**

(Notes 1, 2, 3)

| $V_{SW}0.3V$ to $45V$                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------|

| V <sub>BUS</sub> , V <sub>OUT</sub> , V <sub>IN12</sub> , V <sub>IN3</sub> , V <sub>INLD01</sub> , V <sub>INLD02</sub> , WALL |

| t < 1ms and Duty Cycle < 1%0.3V to 7V                                                                                         |

| Steady State0.3V to 6V                                                                                                        |

| CHRG, BAT, LED_FS, LED_OV, PWR_ON, WAKE,                                                                                      |

| PBSTAT, PG_DCDC, FB1, FB2, FB3, LD01, LD01_FB,                                                                                |

| LD02, LD02_FB, DV <sub>CC</sub> , SCL, SDA –0.3V to 6V                                                                        |

| NTC, PROG, CLPROG, ON, I <sub>LIM0</sub> , I <sub>LIM1</sub>                                                                  |

| (Note 4)0.3V to V <sub>CC</sub> + 0.3V                                                                                        |

| I <sub>VBUS</sub> , I <sub>VOUT</sub> , I <sub>BAT</sub> , Continuous (Note 16)2A                                             |

| I <sub>SW3</sub> , Continuous (Note 16) 850mA                                                                                 |

| I <sub>SW2</sub> , I <sub>SW1</sub> , Continuous (Note 16) 600mA                                                              |

| I <sub>LD01</sub> , I <sub>LD02</sub> , Continuous (Note 16) 200mA                                                            |

| ICHRG, IACPR, IWAKE, IPBSTAT, IPG_DCDC75mA                                                                                    |

| IOVSENS                                                                                                                       |

| I <sub>CLPROG</sub> , I <sub>PROG</sub> , I <sub>LED_FS</sub> , I <sub>LED_OV</sub> 2mA                                       |

| Junction Temperature110°C                                                                                                     |

| Operating Temperature Range40°C to 85°C                                                                                       |

| Storage Temperature Range –65°C to 125°C                                                                                      |

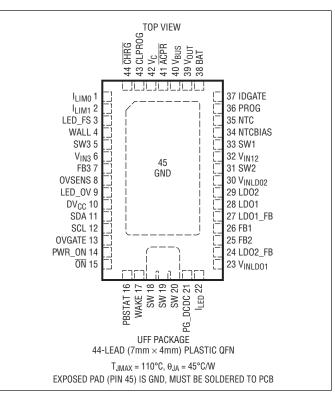

## PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH  | TAPE AND REEL       | PART MARKING | PACKAGE DESCRIPTION                    | TEMPERATURE RANGE |

|-------------------|---------------------|--------------|----------------------------------------|-------------------|

| LTC3577EUFF#PBF   | LTC3577EUFF#TRPBF   | 3577         | 44-Lead (4mm × 7mm) Plastic QFN        | -40°C to 85°C     |

| LTC3577EUFF-1#PBF | LTC3577EUFF-1#TRPBF | 35771        | 44-Lead (4mm $\times$ 7mm) Plastic QFN | –40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** Power Manager. The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}$ C. $V_{BUS} = 5V$ , $V_{BAT} = 3.8V$ , $I_{LIM0} = I_{LIM1} = WALL = 0V$ , $V_{INLD01} = V_{INLD02} = V_{IN12} = V_{IN3} = V_{OUT}$ , $R_{PR0G} = 2k$ , $R_{CLPR0G} = 2.1k$ , unless otherwise noted.

| SYMBOL                 | PARAMETER                                                                                        | CONDITIONS                                                                                                                                                 |   | MIN                              | ТҮР                              | MAX                              | UNITS            |

|------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------------------|----------------------------------|----------------------------------|------------------|

| Input Power            | Supply                                                                                           | 1                                                                                                                                                          |   |                                  |                                  |                                  |                  |

| V <sub>BUS</sub>       | Input Supply Voltage                                                                             |                                                                                                                                                            |   | 4.35                             |                                  | 5.5                              | V                |

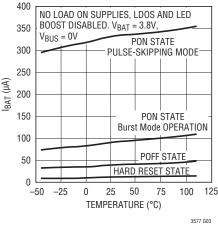

| I <sub>BUS(LIM)</sub>  | Total Input Current (Note 5)                                                                     | $      I_{LIM0} = 0V, I_{LIM1} = 0V (1x Mode)       I_{LIM0} = 5V, I_{LIM1} = 5V (5x Mode)       I_{LIM0} = 5V, I_{LIM1} = 0V (10x Mode) $                 | • | 80<br>450<br>900                 | 90<br>475<br>950                 | 100<br>500<br>1000               | mA<br>mA<br>mA   |

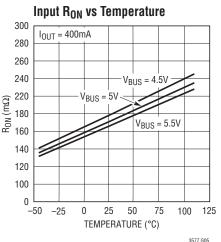

| I <sub>BUSQ</sub>      | Input Quiescent Current, POFF State                                                              | 1x, 5x, 10x Modes<br>I <sub>LIM0</sub> = 0V, I <sub>LIM1</sub> = 5V (Suspend Mode)                                                                         |   |                                  | 0.42<br>0.042                    | 0.1                              | mA<br>mA         |

| h <sub>CLPROG</sub>    | Ratio of Measured V <sub>BUS</sub> Current to CLPROG Program Current                             |                                                                                                                                                            |   |                                  | 1000                             |                                  | mA/mA            |

| V <sub>CLPROG</sub>    | CLPROG Servo Voltage in Current<br>Limit                                                         | 1x Mode<br>5x Mode<br>10x Mode                                                                                                                             |   |                                  | 0.2<br>1.0<br>2.0                |                                  | V<br>V<br>V      |

| V <sub>UVLO</sub>      | V <sub>BUS</sub> Undervoltage Lockout                                                            | Rising Threshold<br>Falling Threshold                                                                                                                      |   | 3.5                              | 3.8<br>3.7                       | 3.9                              | V<br>V           |

| V <sub>DUVLO</sub>     | V <sub>BUS</sub> to V <sub>OUT</sub> Differential Undervoltage<br>Lockout                        | Rising Threshold<br>Falling Threshold                                                                                                                      |   |                                  | 50<br>50                         | 100                              | mV<br>mV         |

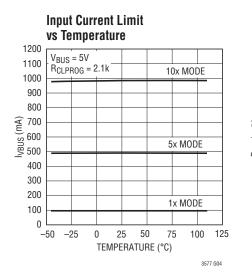

| R <sub>ON_ILIM</sub>   | Input Current Limit Power FET On-<br>Resistance (Between V <sub>BUS</sub> and V <sub>OUT</sub> ) |                                                                                                                                                            |   |                                  | 200                              |                                  | mΩ               |

| Battery Chai           | ger                                                                                              |                                                                                                                                                            |   |                                  |                                  | I                                |                  |

| V <sub>FLOAT</sub>     | V <sub>BAT</sub> Regulated Output Voltage                                                        | LTC3577<br>LTC3577, $0 \le T_A \le 85^{\circ}C$<br>LTC3577-1<br>LTC3577-1, $0 \le T_A \le 85^{\circ}C$                                                     |   | 4.179<br>4.165<br>4.079<br>4.065 | 4.200<br>4.200<br>4.100<br>4.100 | 4.221<br>4.235<br>4.121<br>4.135 | V<br>V<br>V<br>V |

| I <sub>CHG</sub>       | Constant-Current Mode Charge Current                                                             | R <sub>PROG</sub> = 1k, Input Current Limit = 2A<br>R <sub>PROG</sub> = 2k, Input Current Limit = 1A<br>R <sub>PROG</sub> = 5k, Input Current Limit = 0.4A | • | 950<br>465<br>180                | 1000<br>500<br>200               | 1050<br>535<br>220               | mA<br>mA<br>mA   |

| I <sub>BATQ_HR</sub>   | Battery Drain Current, Hard Reset                                                                | $V_{BUS} = 0V, I_{OUT} = 0\mu A$                                                                                                                           |   |                                  | 7                                | 15                               | μA               |

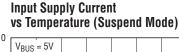

| I <sub>BATQ_OFF</sub>  | Battery Drain Current, POFF State                                                                | V <sub>BAT</sub> = 4.3V, Charger Time Out<br>V <sub>BUS</sub> = 0V                                                                                         |   |                                  | 6<br>40                          | 27<br>100                        | μΑ<br>μΑ         |

| I <sub>BATQ_ON</sub>   | Battery Drain Current, PON State<br>LDOs, and LED Backlight Disabled                             | V <sub>BUS</sub> = 0V, I <sub>OUT</sub> = 0µA, No Load on<br>Supplies, Burst Mode Operation (Note 10)                                                      |   |                                  | 90                               | 160                              | μA               |

| V <sub>PROG,CHG</sub>  | PROG Pin Servo Voltage                                                                           | V <sub>BAT</sub> > V <sub>TRKL</sub>                                                                                                                       |   |                                  | 1.000                            |                                  | V                |

| V <sub>PROG,TRKL</sub> | PROG Pin Servo Voltage in Trickle<br>Charge                                                      | V <sub>BAT</sub> < V <sub>TRKL</sub>                                                                                                                       |   |                                  | 0.100                            |                                  | V                |

| h <sub>PROG</sub>      | Ratio of I <sub>BAT</sub> to PROG Pin Current                                                    |                                                                                                                                                            |   |                                  | 1000                             |                                  | mA/mA            |

| I <sub>TRKL</sub>      | Trickle Charge Current                                                                           | V <sub>BAT</sub> < V <sub>TRKL</sub>                                                                                                                       |   | 40                               | 50                               | 60                               | mA               |

| V <sub>TRKL</sub>      | Trickle Charge Rising Threshold<br>Trickle Charge Falling Threshold                              | V <sub>BAT</sub> Rising<br>V <sub>BAT</sub> Falling                                                                                                        |   | 2.5                              | 2.85<br>2.75                     | 3.0                              | V<br>V           |

| $\Delta V_{RECHRG}$    | Recharge Battery Threshold Voltage                                                               | Threshold Voltage Relative to V <sub>FLOAT</sub>                                                                                                           |   | -75                              | -100                             | -125                             | mV               |

| t <sub>TERM</sub>      | Safety Timer Termination Period                                                                  | Timer Starts When V <sub>BAT</sub> = V <sub>FLOAT</sub> – 50mV                                                                                             |   | 3.2                              | 4                                | 4.8                              | Hour             |

| t <sub>BADBAT</sub>    | Bad Battery Termination Time                                                                     | V <sub>BAT</sub> < V <sub>TRKL</sub>                                                                                                                       |   | 0.4                              | 0.5                              | 0.6                              | Hour             |

| h <sub>C/10</sub>      | End-of-Charge Indication Current Ratio                                                           | (Note 6)                                                                                                                                                   |   | 0.085                            | 0.1                              | 0.11                             | mA/mA            |

| R <sub>ON_CHG</sub>    | Battery Charger Power FET On-<br>Resistance (Between V <sub>OUT</sub> and BAT)                   |                                                                                                                                                            |   |                                  | 200                              |                                  | mΩ               |

| T <sub>LIM</sub>       | Junction Temperature in Constant<br>Temperature Mode                                             |                                                                                                                                                            |   |                                  | 110                              |                                  | °C               |

# **ELECTRICAL CHARACTERISTICS** Power Manager. The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}$ C. $V_{BUS} = 5V$ , $V_{BAT} = 3.8V$ , $I_{LIMO} = I_{LIM1} = WALL = 0V$ , $V_{INLDO1} = V_{INLDO2} = V_{IN12} = V_{IN3} = V_{OUT}$ , $R_{PROG} = 2k$ , $R_{CLPROG} = 2.1k$ , unless otherwise noted.

| SYMBOL                   | PARAMETER                                    | CONDITIONS                                                                                  | MIN                    | ТҮР                            | MAX              | UNITS                                          |

|--------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------|------------------------|--------------------------------|------------------|------------------------------------------------|

| NTC, Battery             | / Discharge Protection                       |                                                                                             |                        |                                |                  | <b>_</b>                                       |

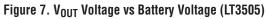

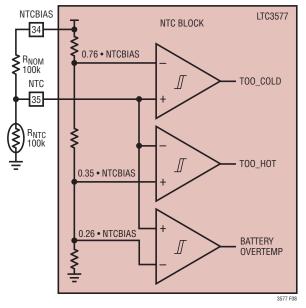

| V <sub>COLD</sub>        | Cold Temperature Fault Threshold<br>Voltage  | Rising NTC Voltage<br>Hysteresis                                                            | 75                     | 76<br>1.3                      | 77               | %V <sub>NTCBIAS</sub><br>%V <sub>NTCBIAS</sub> |

| V <sub>HOT</sub>         | Hot Temperature Fault Threshold<br>Voltage   | Falling NTC Voltage<br>Hysteresis                                                           | 34                     | 35<br>1.3                      | 36               | %Vntcbias<br>%Vntcbias                         |

| V <sub>2HOT</sub>        | NTC Discharge Threshold Voltage              | Falling NTC Voltage<br>Hysteresis                                                           | 24.5                   | 25.5<br>50                     | 26.5             | %V <sub>NTCBIAS</sub><br>mV                    |

| INTC                     | NTC Leakage Current                          | $V_{NTC} = V_{BUS} = 5V$                                                                    | -50                    |                                | 50               | nA                                             |

| I <sub>BAT2HOT</sub>     | BAT Discharge Current                        | $V_{BAT} = 4.1V$ , NTC < $V_{TOO_HOT}$                                                      |                        | 180                            |                  | mA                                             |

| V <sub>BAT2HOT</sub>     | BAT Discharge Threshold                      | I <sub>BAT</sub> < 0.1mA, NTC < V <sub>TOO_HOT</sub>                                        |                        | 3.9                            |                  | V                                              |

| ldeal Diode              |                                              |                                                                                             |                        |                                |                  |                                                |

| V <sub>FWD</sub>         | Forward Voltage Detection                    | I <sub>OUT</sub> = 10mA                                                                     | 5                      | 15                             | 25               | mV                                             |

| R <sub>DROPOUT</sub>     | Diode On-Resistance, Dropout                 | I <sub>OUT</sub> = 200mA                                                                    |                        | 200                            |                  | mΩ                                             |

| I <sub>MAX</sub>         | Diode Current Limit                          | (Note 7)                                                                                    |                        | 3.6                            |                  | A                                              |

| Overvoltage              | Protection                                   |                                                                                             |                        |                                |                  |                                                |

| VOVCUTOFF                | Overvoltage Protection Threshold             | Rising Threshold, R <sub>OVSENS</sub> = 6.2k                                                | 6.10                   | 6.35                           | 6.70             | V                                              |

| V <sub>OVGATE</sub>      | OVGATE Output Voltage                        | Input Below V <sub>OVCUTOFF</sub><br>Input Above V <sub>OVCUTOFF</sub>                      |                        | 1.88 • V <sub>OVSEN</sub><br>0 | <sub>IS</sub> 12 | V<br>V                                         |

| IOVSENSQ                 | OVSENS Quiescent Current                     | V <sub>OVSENS</sub> = 5V                                                                    |                        | 40                             |                  | μΑ                                             |

| t <sub>RISE</sub>        | OVGATE Time to Reach Regulation              | C <sub>OVGATE</sub> = 1nF                                                                   |                        | 2.5                            |                  | ms                                             |

| Wall Adapte              | r                                            |                                                                                             | · ·                    |                                |                  |                                                |

| VACPR                    | ACPR Pin Output High Voltage                 | I <sub>ACPR</sub> = 0.1mA<br>I <sub>ACPR</sub> = 1mA                                        | V <sub>OUT</sub> – 0.3 | V <sub>OUT</sub>               | 0.3              | V<br>V                                         |

| V <sub>W</sub>           | Absolute Wall Input Threshold Voltage        | V <sub>WALL</sub> Rising<br>V <sub>WALL</sub> Falling                                       | 3.1                    | 4.3<br>3.2                     | 4.45             | V<br>V                                         |

| $\Delta V_W$             | Differential Wall Input Threshold<br>Voltage | V <sub>WALL</sub> – V <sub>BAT</sub> Falling<br>V <sub>WALL</sub> – V <sub>BAT</sub> Rising | 0                      | 25<br>75                       | 100              | mV<br>mV                                       |

| I <sub>QWALL</sub>       | Wall Operating Quiescent Current             | $I_{WALL} + I_{VOUT}, I_{BAT} = 0mA,$<br>WALL = V <sub>OUT</sub> = 5V                       |                        | 440                            |                  | μA                                             |

| Logic (I <sub>LIMO</sub> | , I <sub>LIM1</sub> and CHRG)                |                                                                                             |                        |                                |                  |                                                |

| V <sub>IL</sub>          | Input Low Voltage                            | I <sub>LIMO</sub> , I <sub>LIM1</sub>                                                       |                        |                                | 0.4              | V                                              |

| V <sub>IH</sub>          | Input High Voltage                           | I <sub>LIMO</sub> , I <sub>LIM1</sub>                                                       | 1.2                    |                                |                  | V                                              |

| I <sub>PD</sub>          | Static Pull-Down Current                     | $I_{LIM0}, I_{LIM1}; V_{PIN} = 1V$                                                          |                        | 2                              |                  | μA                                             |

| V <sub>CHRG</sub>        | CHRG Pin Output Low Voltage                  | I <sub>CHRG</sub> = 10mA                                                                    |                        | 0.15                           | 0.4              | V                                              |

| ICHRG                    | CHRG Pin Input Current                       | $V_{BAT} = 4.5V, V_{\overline{CHRG}} = 5V$                                                  |                        | 0                              | 1                | μΑ                                             |

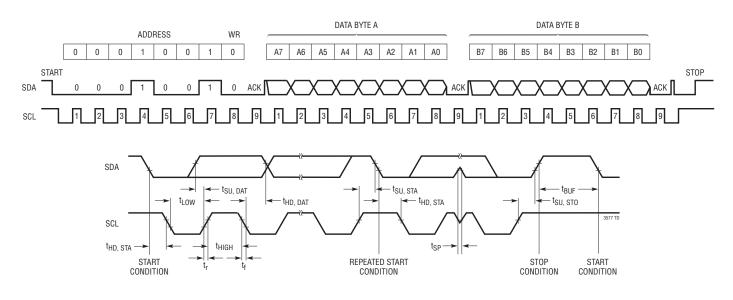

## **ELECTRICAL CHARACTERISTICS** I<sup>2</sup>C Interface. The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. DV<sub>CC</sub> = 3.3V, V<sub>OUT</sub> = 3.8V, unless otherwise noted.

| SYMBOL                 | PARAMETER                             | CONDITIONS                                         | MIN | ТҮР      | MAX | UNITS             |

|------------------------|---------------------------------------|----------------------------------------------------|-----|----------|-----|-------------------|

| DV <sub>CC</sub>       | Input Supply Voltage                  |                                                    | 1.6 |          | 5.5 | V                 |

| IDVCC                  | DV <sub>CC</sub> Supply Current       | SCL = 400kHz<br>SCL = SDA = 0kHz                   |     | 1<br>0.4 |     | μΑ<br>μΑ          |

| V <sub>DVCC,UVLO</sub> | DV <sub>CC</sub> UVLO                 |                                                    |     | 1.0      |     | V                 |

| V <sub>IH</sub>        | Input HIGH Voltage                    |                                                    |     | 50       | 70  | %DV <sub>CC</sub> |

| V <sub>IL</sub>        | Input LOW Voltage                     |                                                    | 30  | 50       |     | %DV <sub>CC</sub> |

| I <sub>IH</sub>        | Input HIGH Leakage Current            | $SDA = SCL = DV_{CC} = 5.5V$                       | -1  |          | 1   | μA                |

| IIL                    | Input LOW Leakage Current             | $SDA = SCL = 0V$ , $DV_{CC} = 5.5V$                | -1  |          | 1   | μA                |

| V <sub>OL</sub>        | SDA Output LOW Voltage                | I <sub>SDA</sub> = 3mA                             |     |          | 0.4 | V                 |

| Timing Chara           | cteristics (Note 8) (All Values are R | eferenced to V <sub>IH</sub> and V <sub>IL</sub> ) |     |          |     |                   |

| f <sub>SCL</sub>       | SCL Clock Frequency                   |                                                    |     |          | 400 | kHz               |

| t <sub>LOW</sub>       | LOW Period of the SCL Clock           |                                                    | 1.3 |          |     | μs                |

| t <sub>HIGH</sub>      | HIGH Period of the SCL Clock          |                                                    | 0.6 |          |     | μs                |

| t <sub>BUF</sub>       | Bus Free Time Between Stop and        | Start Condition                                    | 1.3 |          |     | μs                |

| t <sub>HD,STA</sub>    | Hold Time After (Repeated) Start (    | Condition                                          | 0.6 |          |     | μs                |

| t <sub>SU,STA</sub>    | Setup Time for a Repeated Start C     | ondition                                           | 0.6 |          |     | μs                |

| t <sub>SU,STO</sub>    | Stop Condition Setup Time             |                                                    | 0.6 |          |     | μs                |

| t <sub>HD,DATO</sub>   | Output Data Hold Time                 |                                                    | 0   |          | 900 | ns                |

| t <sub>HD,DATI</sub>   | Input Data Hold Time                  |                                                    | 0   |          |     | ns                |

| t <sub>SU,DAT</sub>    | Data Setup Time                       |                                                    | 100 |          |     | ns                |

| t <sub>SP</sub>        | Input Spike Suppression Pulse Wi      | dth                                                |     |          | 50  | ns                |

## **Step-Down Switching Regulators.** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>OUT</sub> = V<sub>IN12</sub> = V<sub>IN3</sub> = 3.8V, all regulators enabled unless otherwise noted.

| SYMBOL                               | PARAMETER                               | CONDITIONS                                                                   |   | MIN          | ТҮР        | MAX           | UNITS  |

|--------------------------------------|-----------------------------------------|------------------------------------------------------------------------------|---|--------------|------------|---------------|--------|

| Step-Down Sw                         | itching Regulators (Buck1, Buck2 and Bu | ick3)                                                                        |   |              |            |               |        |

| V <sub>IN12</sub> , V <sub>IN3</sub> | Input Supply Voltage                    | (Note 9)                                                                     | • | 2.7          |            | 5.5           | V      |

| V <sub>OUT</sub> UVLO                | V <sub>OUT</sub> Falling                | $V_{\text{IN12}}$ and $V_{\text{IN3}}$ Connected to $V_{\text{OUT}}$ Through |   | 2.5          | 2.7        |               | V      |

|                                      | V <sub>OUT</sub> Rising                 | Low Impedance. Switching Regulators are Disabled Below V <sub>OUT</sub> UVLO |   |              | 2.8        | 2.9           | V      |

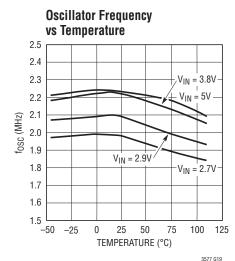

| f <sub>OSC</sub>                     | Oscillator Frequency                    |                                                                              |   | 1.91         | 2.25       | 2.59          | MHz    |

| 800mA Step-D                         | own Switching Regulator 3 (Buck3 – Pus  | hbutton Enabled, Third in Sequence)                                          |   |              |            |               |        |

| IVIN3Q                               | Pulse-Skipping Mode Input Current       | (Note 10)                                                                    |   |              | 100        |               | μA     |

|                                      | Burst Mode Operation Input Current      | (Note 10)                                                                    |   |              | 17         |               | μA     |

|                                      | Shutdown Input Current                  |                                                                              |   |              | 0.01       |               | μA     |

| I <sub>LIM3</sub>                    | Peak PMOS Current Limit                 | (Note 7)                                                                     |   | 1000         | 1400       | 1700          | mA     |

| V <sub>FB3</sub>                     | Feedback Voltage                        | Pulse-Skipping Mode<br>Burst Mode Operation                                  | • | 0.78<br>0.78 | 0.8<br>0.8 | 0.82<br>0.824 | V<br>V |

| I <sub>FB3</sub>                     | FB3 Input Current                       | (Note 10)                                                                    |   | -0.05        |            | 0.05          | μA     |

| D3                                   | Max Duty Cycle                          | FB3 = 0V                                                                     |   | 100          |            |               | %      |

| R <sub>P3</sub>                      | R <sub>DS(ON)</sub> of PMOS             |                                                                              |   |              | 0.3        |               | Ω      |

| R <sub>N3</sub>                      | R <sub>DS(ON)</sub> of NMOS             |                                                                              |   |              | 0.4        |               | Ω      |

## **ELECTRICAL CHARACTERISTICS** Step-Down Switching Regulators. The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>OUT</sub> = V<sub>IN12</sub> = V<sub>IN3</sub> = 3.8V,

all regulators enabled unless otherwise noted.

| SYMBOL              | PARAMETER                                | CONDITIONS                                  |   | MIN          | ТҮР        | MAX           | UNITS  |

|---------------------|------------------------------------------|---------------------------------------------|---|--------------|------------|---------------|--------|

| R <sub>SW3_PD</sub> | SW3 Pull-Down in Shutdown                | POFF State                                  |   |              | 10         |               | kΩ     |

| 500mA Step          | -Down Switching Regulator 2 (Buck2 – Pus | hbutton Enabled, Second in Sequence)        |   |              |            |               | ·      |

| I <sub>VIN12Q</sub> | Pulse-Skipping Mode Input Current        | (Note 10)                                   |   |              | 100        |               | μA     |

|                     | Burst Mode Operation Input Current       | (Note 10)                                   |   |              | 17         |               | μA     |

|                     | Shutdown Input Current                   |                                             |   |              | 0.01       |               | μA     |

| I <sub>LIM2</sub>   | Peak PMOS Current Limit                  | (Note 7)                                    |   | 650          | 900        | 1200          | mA     |

| V <sub>FB2</sub>    | Feedback Voltage                         | Pulse-Skipping Mode<br>Burst Mode Operation | • | 0.78<br>0.78 | 0.8<br>0.8 | 0.82<br>0.824 | V<br>V |

| I <sub>FB2</sub>    | FB2 Input Current                        | (Note 10)                                   |   | -0.05        |            | 0.05          | μA     |

| D2                  | Max Duty Cycle                           | FB2 = 0V                                    |   | 100          |            |               | %      |

| R <sub>P2</sub>     | R <sub>DS(ON)</sub> of PMOS              | I <sub>SW2</sub> = 100mA                    |   |              | 0.6        |               | Ω      |

| R <sub>N2</sub>     | R <sub>DS(ON)</sub> of NMOS              | I <sub>SW2</sub> = -100mA                   |   |              | 0.6        |               | Ω      |

| R <sub>SW2_PD</sub> | SW2 Pull-Down in Shutdown                | POFF State                                  |   |              | 10         |               | kΩ     |

| 500mA Step          | -Down Switching Regulator 1 (Buck1 – Pus | hbutton Enabled, First in Sequence)         | · |              |            |               |        |

| I <sub>VIN12Q</sub> | Pulse-Skipping Mode Input Current        | (Note 10)                                   |   |              | 100        |               | μA     |

|                     | Burst Mode Operation Input Current       | (Note 10)                                   |   |              | 17         |               | μA     |

|                     | Shutdown Input Current                   |                                             |   |              | 0.01       |               | μA     |

| I <sub>LIM1</sub>   | Peak PMOS Current Limit                  | (Note 7)                                    |   | 650          | 900        | 1200          | mA     |

| V <sub>FB1</sub>    | Feedback Voltage                         | Pulse-Skipping Mode<br>Burst Mode Operation | • | 0.78<br>0.78 | 0.8<br>0.8 | 0.82<br>0.824 | V<br>V |

| I <sub>FB1</sub>    | FB1 Input Current                        | (Note 10)                                   |   | -0.05        |            | 0.05          | μA     |

| D1                  | Max Duty Cycle                           | FB1 = 0V                                    |   | 100          |            |               | %      |

| R <sub>P1</sub>     | R <sub>DS(ON)</sub> of PMOS              | I <sub>SW1</sub> = 100mA                    |   |              | 0.6        |               | Ω      |

| R <sub>N1</sub>     | R <sub>DS(ON)</sub> of NMOS              | I <sub>SW1</sub> = -100mA                   |   |              | 0.6        |               | Ω      |

| R <sub>SW1_PD</sub> | SW1 Pull-Down in Shutdown                | POFF State                                  |   |              | 10         |               | kΩ     |

**LDO Regulators.** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>INLD01</sub> = V<sub>INLD02</sub> = V<sub>OUT</sub> = V<sub>BAT</sub> = 3.8V, LD01 and LD02 enabled unless otherwise noted.

| SYMBOL                                           | PARAMETER                                                                             | CONDITIONS                                                                                           |   | MIN  | ТҮР        | MAX     | UNITS    |

|--------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---|------|------------|---------|----------|

| LDO Regula                                       | tor 1 (LDO1 – Enabled via I <sup>2</sup> C)                                           |                                                                                                      |   |      |            |         |          |

| V <sub>INLD01</sub>                              | Input Voltage Range                                                                   | $V_{INLDO1} \le V_{OUT} + 0.3V$                                                                      |   | 1.65 |            | 5.5     | V        |

| V <sub>OUT_UVLO</sub>                            | V <sub>OUT</sub> Falling<br>V <sub>OUT</sub> Rising                                   | LDO1 is Disabled Below V <sub>OUT</sub> UVLO                                                         |   | 2.5  | 2.7<br>2.8 | 2.9     | V<br>V   |

| I <sub>QLD01_</sub> V0<br>I <sub>QLD01_</sub> VI | LD01 V <sub>OUT</sub> Quiescent Current<br>LD01 V <sub>INLD01</sub> Quiescent Current | LD01 Enabled, PON State, I <sub>LD01</sub> = 0mA<br>LD01 Enabled, PON State, I <sub>LD01</sub> = 0mA |   |      | 18<br>0.1  | 30<br>2 | μA<br>μA |

| I <sub>VINLD01</sub>                             | Shutdown Current                                                                      | LDO1 Disabled, PON or POFF State                                                                     |   |      | 0.01       | 1       | μA       |

| V <sub>LD01_FB</sub>                             | LDO1_FB Regulated Feedback Voltage                                                    | I <sub>LD01</sub> = 1mA                                                                              | • | 0.78 | 0.8        | 0.82    | V        |

|                                                  | LDO1_FB Line Regulation (Note 11)                                                     | I <sub>LD01</sub> = 1mA, V <sub>IN</sub> = 1.65V to 5.5V                                             |   |      | 0.4        |         | mV/V     |

|                                                  | LDO1_FB Load Regulation (Note 11)                                                     | I <sub>LD01</sub> = 1mA to 150mA                                                                     |   |      | 5          |         | μV/mA    |

| I <sub>LD01_FB</sub>                             | LD01_FB Input Current                                                                 | LD01_FB = 0.8V                                                                                       |   | -50  |            | 50      | nA       |

| I <sub>LD01_0C</sub>                             | Available Output Current                                                              |                                                                                                      | • | 150  |            |         | mA       |

# **ELECTRICAL CHARACTERISTICS** LDO Regulators. The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}$ C. $V_{INLDO1} = V_{INLDO2} = V_{OUT} = V_{BAT} = 3.8$ V, LDO1 and LDO2 enabled unless otherwise noted.

| SYMBOL                                         | PARAMETER                                                                             | CONDITIONS                                                                                                                                                             | MIN  | ТҮР               | MAX               | UNITS                                        |

|------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------|-------------------|----------------------------------------------|

| I <sub>LD01_SC</sub>                           | Short-Circuit Output Current                                                          |                                                                                                                                                                        |      | 270               |                   | mA                                           |

| V <sub>DROP1</sub>                             | Dropout Voltage (Note 12)                                                             | I <sub>LD01</sub> = 150mA, V <sub>INLD01</sub> = 3.6V<br>I <sub>LD01</sub> = 150mA, V <sub>INLD01</sub> = 2.5V<br>I <sub>LD01</sub> = 75mA, V <sub>INLD01</sub> = 1.8V |      | 160<br>200<br>170 | 260<br>320<br>280 | mV<br>mV<br>mV                               |

| R <sub>LD01_PD</sub>                           | Output Pull-Down Resistance in Shutdown                                               | LDO1 Disabled                                                                                                                                                          |      | 10                |                   | kΩ                                           |

| LDO Regula                                     | tor 2 (LDO2 – Enabled via I <sup>2</sup> C)                                           |                                                                                                                                                                        |      |                   |                   | <u>.                                    </u> |

| V <sub>INLD02</sub>                            | Input Voltage Range                                                                   | $V_{INLDO2} \le V_{OUT} + 0.3V$                                                                                                                                        | 1.65 |                   | 5.5               | V                                            |

| V <sub>OUT_UVLO</sub>                          | V <sub>OUT</sub> Falling<br>V <sub>OUT</sub> Rising                                   | LDO2 is Disabled Below V <sub>OUT</sub> UVLO                                                                                                                           | 2.5  | 2.7<br>2.8        | 2.9               | V<br>V                                       |

| I <sub>QLD02_V0</sub><br>I <sub>QLD02_VI</sub> | LDO2 V <sub>OUT</sub> Quiescent Current<br>LDO2 V <sub>INLDO2</sub> Quiescent Current | LDO2 Enabled, PON State, I <sub>LDO2</sub> = 0mA<br>LDO2 Enabled, PON State, I <sub>LDO2</sub> = 0mA                                                                   |      | 18<br>0.1         | 30<br>2           | μA<br>μA                                     |

| I <sub>VINLD02</sub>                           | Shutdown Current                                                                      | LDO2 Disabled, PON or POFF State                                                                                                                                       |      | 0.01              | 1                 | μA                                           |

| V <sub>LD02_FB</sub>                           | LD02_FB Regulated Output Voltage                                                      | $I_{LDO2} = 1 \text{mA}$                                                                                                                                               | 0.78 | 0.8               | 0.82              | V                                            |

|                                                | LD02_FB Line Regulation (Note 11)                                                     | I <sub>LD02</sub> = 1mA, V <sub>IN</sub> = 1.65V to 5.5V                                                                                                               |      | 0.4               |                   | mV/V                                         |

|                                                | LD02_FB Load Regulation (Note 11)                                                     | I <sub>LD02</sub> = 1mA to 150mA                                                                                                                                       |      | 5                 |                   | μV/mA                                        |

| I <sub>LD02_FB</sub>                           | LD02_FB Input Current                                                                 | LD02_FB = 0.8V                                                                                                                                                         | -50  |                   | 50                | nA                                           |

| I <sub>LDO2_OC</sub>                           | Available Output Current                                                              |                                                                                                                                                                        | 150  |                   |                   | mA                                           |

| I <sub>LD02_SC</sub>                           | Short-Circuit Output Current                                                          |                                                                                                                                                                        |      | 270               |                   | mA                                           |

| V <sub>DROP2</sub>                             | Dropout Voltage (Note 12)                                                             | I <sub>LD02</sub> = 150mA, V <sub>INLD02</sub> = 3.6V<br>I <sub>LD02</sub> = 150mA, V <sub>INLD02</sub> = 2.5V<br>I <sub>LD01</sub> = 75mA, V <sub>INLD01</sub> = 1.8V |      | 160<br>200<br>170 | 260<br>320<br>280 | mV<br>mV<br>mV                               |

| R <sub>LD02_PD</sub>                           | Output Pull-Down Resistance in Shutdown                                               | LDO2 Disabled                                                                                                                                                          |      | 14                |                   | kΩ                                           |

## **LED Boost Switching Regulator.** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>IN3</sub> = V<sub>OUT</sub> = 3.8V, R<sub>OV</sub> = 10M, R<sub>LED\_FS</sub> = 20k, boost regulator disabled unless otherwise noted.

| SYMBOL                              | PARAMETER                                                 | CONDITIONS                      |   | MIN  | ТҮР         | MAX  | UNITS    |

|-------------------------------------|-----------------------------------------------------------|---------------------------------|---|------|-------------|------|----------|

| V <sub>IN3</sub> , V <sub>OUT</sub> | Operating Supply Range                                    | (Note 9)                        | • | 2.7  |             | 5.5  | V        |

| I <sub>VOUT_LED</sub>               | Operating Quiescent Current<br>Shutdown Quiescent Current | (Notes 10, 14)                  |   |      | 560<br>0.01 |      | μΑ<br>μΑ |

| V <sub>LED_OV</sub>                 | LED_OV Overvoltage Threshold                              | LED_OV Rising<br>LED_OV Falling |   | 0.6  | 1.0<br>0.85 | 1.25 | V<br>V   |

| ILIM                                | Peak NMOS Switch Current                                  |                                 |   | 800  | 1000        | 1200 | mA       |

| I <sub>LED_FS</sub>                 | ILED Pin Full-Scale Operating Current                     |                                 |   | 18   | 20          | 22   | mA       |

| I <sub>LED_DIM</sub>                | I <sub>LED</sub> Pin Full-Scale Dimming Range             | 64 Steps                        |   |      | 60          |      | dB       |

| R <sub>NSWON</sub>                  | R <sub>DS(ON)</sub> of NMOS Switch                        |                                 |   |      | 240         |      | mΩ       |

| INSWOFF                             | NMOS Switch-Off Leakage Current                           | V <sub>SW</sub> = 5.5V          |   |      | 0.01        | 1    | μA       |

| f <sub>OSC</sub>                    | Oscillator Frequency                                      |                                 |   | 0.95 | 1.125       | 1.3  | MHz      |

| V <sub>LED_FS</sub>                 | LED_FS Pin Voltage                                        |                                 | • | 780  | 800         | 820  | mV       |

| I <sub>LED_OV</sub>                 | LED_OV Pin Current                                        | $R_{LED_{FS}} = 20k$            | • | 3.8  | 4           | 4.2  | μA       |

| D <sub>BOOST</sub>                  | Maximum Duty Cycle                                        | $I_{LED} = 0$                   |   |      | 97          |      | %        |

| V <sub>BOOSTFB</sub>                | Boost Mode I <sub>LED</sub> Feedback Voltage              |                                 | • | 775  | 800         | 825  | mV       |

## **ELECTRICAL CHARACTERISTICS** Pushbutton Controller. The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>OUT</sub> = 3.8V, unless otherwise noted.

| SYMBOL                  | PARAMETER                                           | CONDITIONS                                                |          | MIN      | ТҮР        | MAX      | UNITS    |

|-------------------------|-----------------------------------------------------|-----------------------------------------------------------|----------|----------|------------|----------|----------|

| Pushbutton Pi           | in (ON)                                             |                                                           |          |          |            |          |          |

| V <sub>OUT</sub>        | Pushbutton Operating Supply Range                   | (Note 9)                                                  |          | 2.7      |            | 5.5      | V        |

| V <sub>OUT</sub> UVLO   | V <sub>OUT</sub> Falling<br>V <sub>OUT</sub> Rising | Pushbutton is Disabled Below V <sub>OUT</sub> UVLO        |          | 2.5      | 2.7<br>2.8 | 2.9      | V<br>V   |

| V <sub>ON_TH</sub>      | ON Threshold Rising<br>ON Threshold Falling         |                                                           |          | 0.4      | 0.8<br>0.7 | 1.2      | V<br>V   |

| I <sub>ON</sub>         | ON Input Current                                    | $V_{\overline{ON}} = V_{OUT}$<br>$V_{\overline{ON}} = 0V$ |          | -1<br>-4 | -9         | 1<br>-14 | μΑ<br>μΑ |

| Power-On Inp            | ut Pin (PWR_ON)                                     |                                                           | <b>i</b> |          |            |          |          |

| V <sub>PWR_ON</sub>     | PWR_ON Threshold Rising<br>PWR_ON Threshold Falling |                                                           |          | 0.4      | 0.8<br>0.7 | 1.2      | V<br>V   |

| I <sub>PWR_ON</sub>     | PWR_ON Input Current                                | $V_{PWR_ON} = 3V$                                         |          | -1       |            | 1        | μA       |

| Status Output           | Pins (PBSTAT, WAKE, PG_DCDC)                        |                                                           |          |          |            |          |          |

| IPBSTAT                 | PBSTAT Output High Leakage Current                  | V <sub>PBSTAT</sub> = 3V                                  |          | -1       |            | 1        | μA       |

| V <sub>PBSTAT</sub>     | PBSTAT Output Low Voltage                           | I <sub>PBSTAT</sub> = 3mA                                 |          |          | 0.1        | 0.4      | V        |

| I <sub>WAKE</sub>       | Wake Output High Leakage Current                    | V <sub>WAKE</sub> = 3V                                    |          | -1       |            | 1        | μA       |

| V <sub>WAKE</sub>       | Wake Low Output Voltage                             | I <sub>WAKE</sub> = 3mA                                   |          |          | 0.1        | 0.4      | V        |

| I <sub>PG_DCDC</sub>    | PG_DCDC Output High Leakage Current                 | $V_{PG_DCDC} = 3V$                                        |          | -1       |            | 1        | μA       |

| V <sub>PG_DCDC</sub>    | PG_DCDC Output Low Voltage                          | I <sub>PG_DCDC</sub> = 3mA                                |          |          | 0.1        | 0.4      | V        |

| V <sub>THPG_DCDC</sub>  | PG_DCDC Threshold Voltage                           | (Note 13)                                                 |          |          | -8         |          | %        |

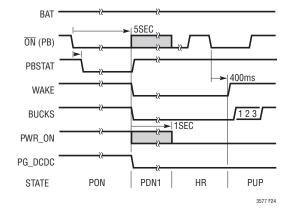

| Pushbutton Ti           | ming Parameters                                     |                                                           |          |          |            |          |          |

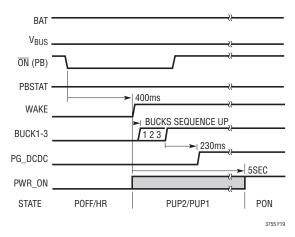

| t <sub>on_pbstat1</sub> | ON Low Time to PBSTAT Low                           | WAKE High                                                 |          |          | 50         |          | ms       |

| t <sub>ON_PBSTAT2</sub> | ON High to PBSTAT High                              | PBSTAT Low > t <sub>PBSTAT_PW</sub>                       |          |          | 900        |          | μs       |

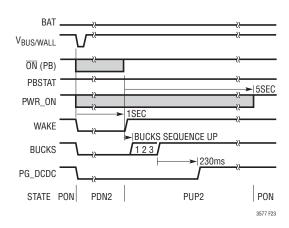

| t <sub>on_wake</sub>    | ON Low Time to WAKE High                            | WAKE Low > t <sub>PWR_ONBK2</sub>                         |          |          | 400        |          | ms       |

| t <sub>ON_HR</sub>      | ON Low to Hard Reset                                | Hard Reset = All Supplies Disabled                        |          | 4.2      | 5          | 5.8      | Seconds  |

| t <sub>PBSTAT_PW</sub>  | PBSTAT Minimum Pulse Width                          |                                                           |          | 40       | 50         | 60       | ms       |

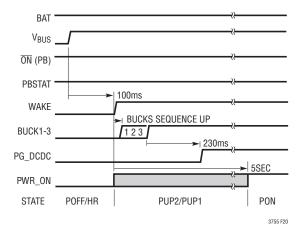

| t <sub>WAKE_EXTP</sub>  | WAKE High from USB or Wall Present                  | WAKE Low > $t_{PWR_ONBK2}$                                |          |          | 100        |          | ms       |

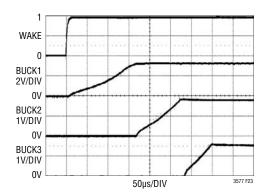

| t <sub>WAKE_DCDC</sub>  | WAKE High to Buck1 Enable                           | WAKE Low > t <sub>PWR_ONBK2</sub>                         |          |          | 5          |          | μs       |

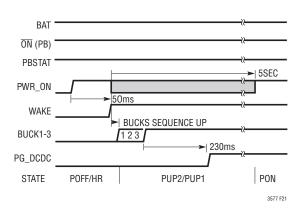

| t <sub>PWR_ONH</sub>    | PWR_ON High to WAKE High                            | WAKE Low > t <sub>PWR_ONBK2</sub>                         |          |          | 50         |          | ms       |

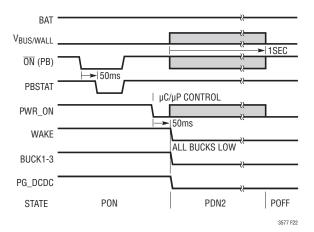

| t <sub>PWR_ONL</sub>    | PWR_ON Low to WAKE Low                              | WAKE High > t <sub>PWR_ONBK1</sub>                        |          |          | 50         |          | ms       |

| t <sub>PWR_ONBK1</sub>  | PWR_ON Power-Up Blanking                            | WAKE Rising Until PWR_ON Low Recognized                   |          |          | 5          |          | Seconds  |

| t <sub>PWR_ONBK2</sub>  | PWR_ON Power-Down Blanking                          | WAKE Falling Until PWR_ON High Recognized                 |          |          | 1          |          | Seconds  |

| t <sub>PG_DCDCH</sub>   | Bucks in Regulation to PG_DCDC High                 | All Bucks Within PG_DCDC Threshold Voltage                |          |          | 230        |          | ms       |

| t <sub>PG_DCDCL</sub>   | Bucks Disabled to PG_DCDC Low                       | All Bucks Disabled                                        |          |          | 44         |          | μs       |

9

## **ELECTRICAL CHARACTERISTICS**

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC3577E/LTC3577E-1 are guaranteed to meet performance specifications from 0°C to 85°C. Specifications over the –40°C to 85°C operating temperature range are assured by design, characterization and correlation with statistical process controls.

**Note 3:** This IC includes over temperature protection that is intended to protect the device during momentary overload conditions. Junction temperatures will exceed 110°C when over temperature protection is active. Continuous operation above the specified maximum operating junction temperature may result in device degradation or failure.

Note 4: V<sub>CC</sub> is the greater of V<sub>BUS</sub>, V<sub>OUT</sub> or BAT.

Note 5: Total input current is the sum of quiescent current,  $I_{BUSQ}$ , and measured current given by  $V_{CLPROG}/R_{CLPROG} \bullet (h_{CLPROG} + 1)$ .

Note 6:  $h_{C/10}$  is expressed as a fraction of measured full charge current with indicated PROG resistor.

**Note 7:** The current limit features of this part are intended to protect the IC from short term or intermittent fault conditions. Continuous operation above the specified maximum pin current rating may result in device degradation or failure.

**Note 8:** The serial port is tested at rated operating frequency. Timing parameters are tested and/or guaranteed by design.

Note 9: V<sub>OUT</sub> not in UVLO.

Note 10: FB high, not switching.

**Note 11:** Measured with the LDO running unity gain with output tied to feedback pin.

**Note 12:** Dropout voltage is the minimum input to output voltage differential needed for an LDO to maintain regulation at a specified output current. When an LDO is in dropout, its output voltage will be equal to  $V_{IN} - V_{DROP}$ .

**Note 13:** PG\_DCDC threshold is expressed as a percentage difference from the Buck1-3 regulation voltages. The threshold is measured from Buck1-3 output rising.

**Note 14:**  $I_{VOUT\_LED}$  is the sum of  $V_{OUT}$  and  $V_{IN3}$  current due to LED driver. **Note 15:** The  $I_{BATQ}$  specifications represent the total battery load assuming  $V_{INLDO1}$ ,  $V_{INLDO2}$ ,  $V_{IN12}$  and  $V_{IN3}$  are tied directly to  $V_{OUT}$ .

Note 16: Long-term current density rating for the part.

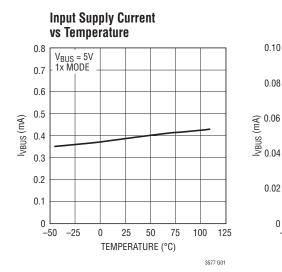

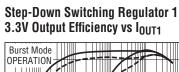

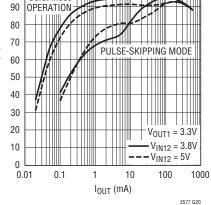

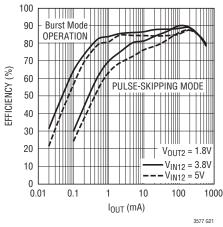

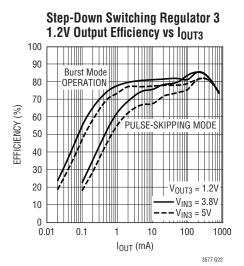

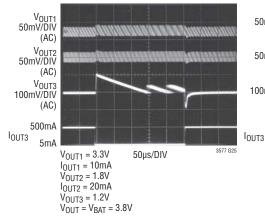

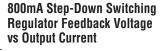

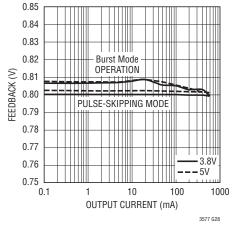

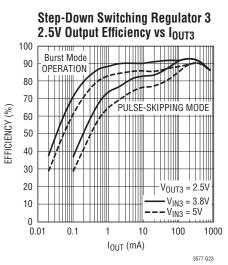

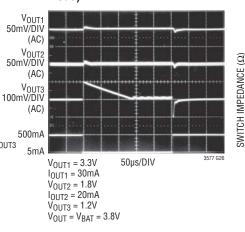

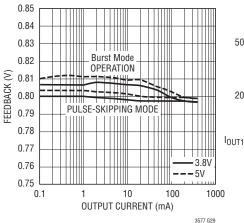

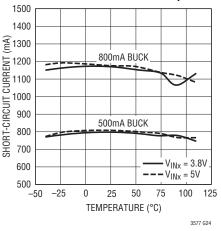

## **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ unless otherwise specified

-25

0 25 50 75 100 125

TEMPERATURE (°C)

3577 G02

-50

## Battery Drain Current vs Temperature

### **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ unless otherwise specified

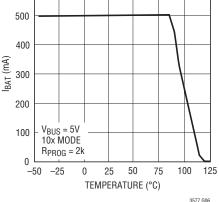

Charge Current vs Temperature (Thermal Regulation)

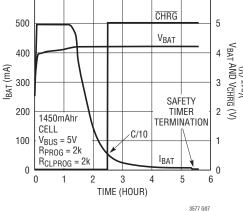

Battery Current and Voltage vs Time

6

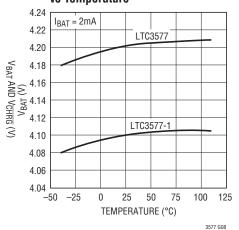

Battery Regulation (Float) Voltage vs Temperature

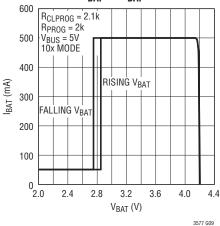

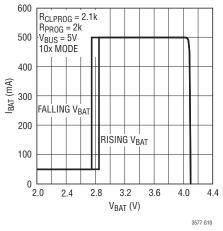

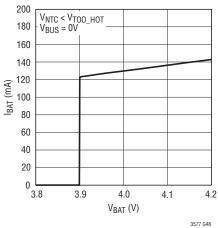

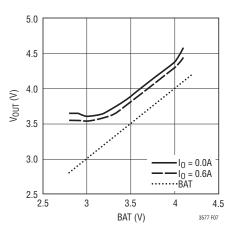

LTC3577 I<sub>BAT</sub> vs V<sub>BAT</sub>

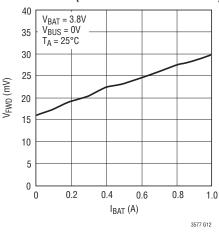

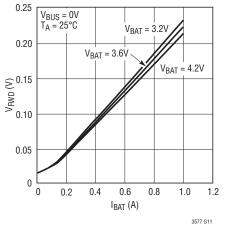

Forward Voltage vs Ideal Diode Current (with Si2333DS External FET)

LTC3577-1 I<sub>BAT</sub> vs V<sub>BAT</sub>

#### Forward Voltage vs Ideal Diode Current (No External FET)

## **TYPICAL PERFORMANCE CHARACTERISTICS** T<sub>A</sub> = 25°C unless otherwise specified

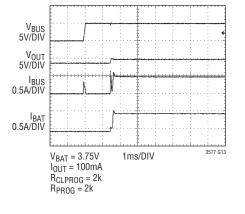

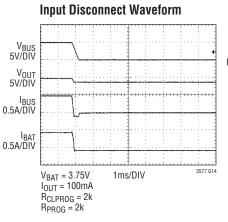

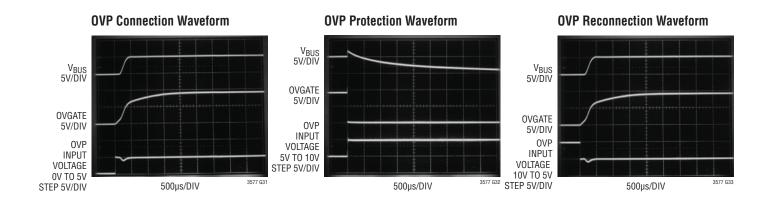

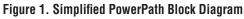

#### **Input Connect Waveform**

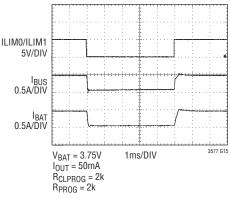

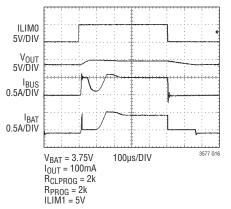

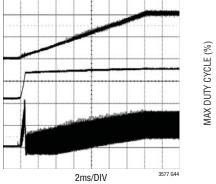

#### Switching from 1x to 5x Mode

## Switching from Suspend Mode to 5x Mode

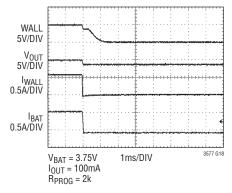

#### WALL Connect Waveform WALL 5V/DIV VOUT 5V/DIV IWALL 0.5A/DIV VBAT = 3.75V 1ms/DIV Strong VBAT = 100mA RPROG = 2k

#### WALL Disconnect Waveform

100

EFFICIENCY (%)

#### Step-Down Switching Regulator 2 1.8V Output Efficiency vs I<sub>OUT2</sub>

## **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ unless otherwise specified

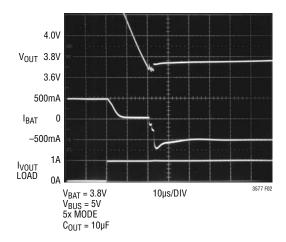

Step-Down Switching Regulator Output Transient (Burst Mode Operation)

Step-Down Switching Regulator Output Transient (Pulse-Skipping Mode)

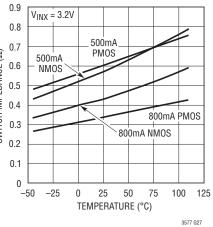

#### 500mA Step-Down Switching Regulator Feedback Voltage vs Output Current

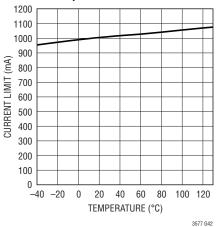

#### Step-Down Switching Regulator Short-Circuit Current vs Temperature

#### Step-Down Switching Regulator Switch Impedance vs Temperature

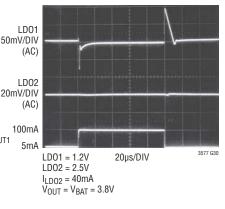

LDO Load Step

## **TYPICAL PERFORMANCE CHARACTERISTICS** T<sub>A</sub> = 25°C unless otherwise specified

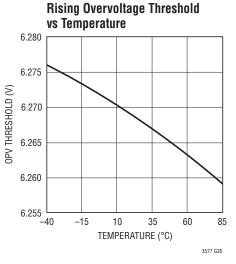

**OVSENS** Quiescent Current vs Temperature 37 V<sub>OVSENS</sub> = 5V 35 QUIESCENT CURRENT (µA) 33 31 29 27 -40 -15 10 35 60 85 TEMPERATURE (°C) 3577 G34

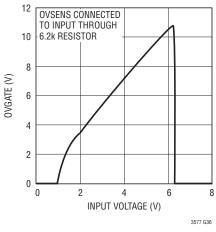

#### **OVGATE vs OVSENS**

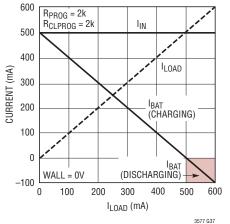

#### Input and Battery Current vs Load Current

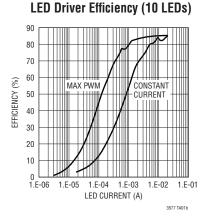

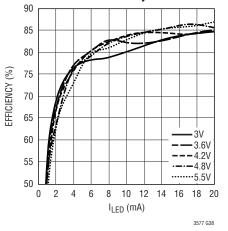

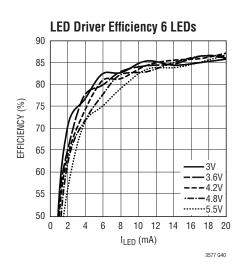

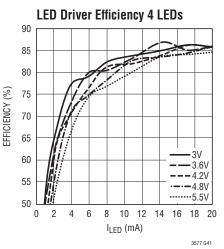

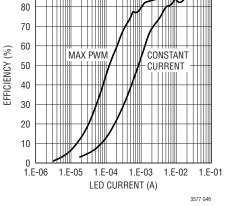

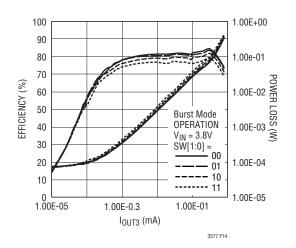

LED Driver Efficiency 10 LEDs

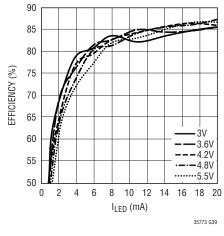

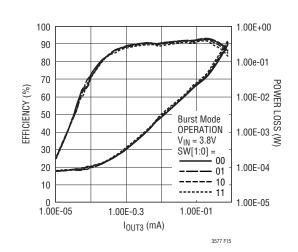

LED Driver Efficiency 8 LEDs

### **TYPICAL PERFORMANCE CHARACTERISTICS** T<sub>A</sub> = 25°C unless otherwise specified

**DAC Code vs LED Current**

70

60

50

30

20

10

0

90

0 10

LED PWM

20 30 40 50

DAC CODE

CURRENT (dB) 40 60dB = 20mA  $0dB = 20\mu A$

$R_{LED_{FS}} = 20k$

LED Boost Start-Up Transient

I<sub>LED</sub> 10mA/DIV

V<sub>BOOST</sub> 20V/DIV

200mA/DIV

70

3577 G43

60

#### LED Boost Current Limit vs Temperature

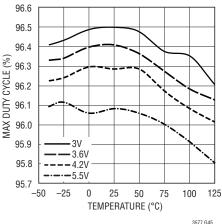

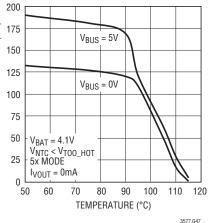

#### **LED Boost Maximum Duty Cycle** vs Temperature

vs Constant Current Efficiency BATTERY DISCHARGE CURRENT (mA)

**Battery Discharge** vs Temperature

#### Too Hot BAT Discharge

## PIN FUNCTIONS

$I_{LIM0}$ ,  $I_{LIM1}$  (Pins 1, 2): Input Current Control Pins.  $I_{LIM0}$  and  $I_{LIM1}$  control the input current limit. See Table 1 in the "USB PowerPath Controller" section. Both pins are pulled low by a weak current sink.

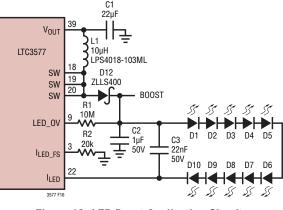

**LED\_FS (Pin 3):** A resistor between this pin and ground sets the full-scale output current of the  $I_{LED}$  pin.

**WALL (Pin 4):** Wall Adapter Present Input. Pulling this pin above 4.3V will disconnect the power path from  $V_{BUS}$  to  $V_{OUT}$ . The ACPR pin will also be pulled low to indicate that a wall adapter has been detected.

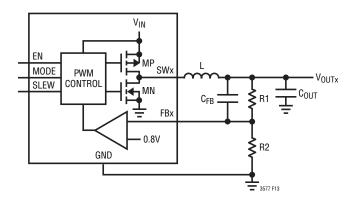

**SW3 (Pin 5):** Power Transmission (Switch) Pin for Step-Down Switching Regulator 3 (buck3).

$V_{IN3}\,(Pin\,6)$ : Power Input for Step-Down Switching Regulator 3. This pin should be connected to  $V_{OUT}.$

**FB3 (Pin 7):** Feedback Input for Step-Down Switching Regulator 3 (buck3). This pin servos to a fixed voltage of 0.8V when the control loop is complete.

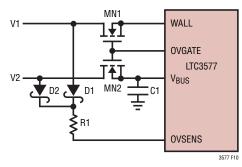

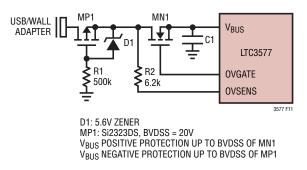

**OVSENSE (Pin 8):** Overvoltage Protection Sense Input. OVSENSE should be connected through a 6.2k resistor to the input power connector and the drain of an external N-channel MOS pass transistor. When the voltage on this pin exceeds a preset level, the OVGATE pin will be pulled to GND to disable the pass transistor and protect downstream circuitry.

**LED\_OV (Pin 9):** A resistor between this pin and the boosted LED backlight voltage sets the overvoltage limit on the boost output. If the boost voltage exceeds the programmed limit the LED boost converter will be disabled.

$DV_{CC}$  (Pin 10): Supply Voltage for I<sup>2</sup>C Lines. This pin sets the logic reference level of the LTC3577. A UVLO circuit on the DV<sub>CC</sub> pin forces all registers to all 0s whenever DV<sub>CC</sub> is <1V. Bypass to GND with a 0.1µF capacitor.

**SDA (Pin 11):**  $I^2C$  Data Input. Serial data is shifted one bit per clock to control the LTC3577. The logic level for SDA is referenced to  $DV_{CC}$ .

SCL (Pin 12):  $I^2C$  Clock Input. The logic level for SCL is referenced to  $DV_{CC}$ .

**OVGATE (Pin 13):** Overvoltage Protection Gate Output. Connect OVGATE to the gate pin of an external N-channel MOS pass transistor. The source of the transistor should be connected to  $V_{BUS}$  and the drain should be connected to the product's DC input connector. In the absence of an overvoltage condition, this pin is connected to an internal charge pump capable of creating sufficient overdrive to fully enhance this transistor. If an overvoltage condition is detected, OVGATE is brought rapidly to GND to prevent damage. OVGATE works in conjunction with OVSENSE to provide this protection.

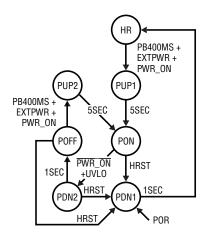

**PWR\_ON (Pin 14):** Logic Input Used to Keep Buck DC/DCs Enabled After Power-Up. May also be used to enable the buck DC/DCs directly (sequence = buck1  $\rightarrow$  buck2  $\rightarrow$  buck3). See the "Pushbutton Interface Operation" section for more information.

**ON** (Pin 15): Pushbutton Input. A weak internal pull-up forces  $\overline{ON}$  high when left floating. A normally open pushbutton is connected from  $\overline{ON}$  to ground to force a low state on this pin.

**PBSTAT (Pin 16):** Open-drain output is a de-bounced and buffered version of  $\overline{ON}$  to be used for processor interrupts.

**WAKE (Pin 17):** Open-Drain Output. The WAKE pin indicates the operating state of the buck DC/DCs. If WAKE is Hi-Z, the buck DC/DCs are enabled and either up or powering up. A low on WAKE indicates that the buck DC/DCs are either powered down or are powering down. See the "Pushbutton Interface Operation" section for more information.

**SW (Pins 18,19,20):** Power Transmission (Switch) Pin for LED Boost Converter. See the "LED Backlight/Boost Operation" section for circuit hook-up and component selection. I<sup>2</sup>C is used to control LED driver enable. I<sup>2</sup>C default is LED driver off.

**PG\_DCDC (Pin 21):** Open-Drain Output. PG\_DCDC goes high impedance 230ms after all buck DC/DCs are in regulation (within 8% of final value).

## PIN FUNCTIONS

**I**<sub>LED</sub> (**Pin 22**): Series LED Backlight Current Sink Output. This pin is connected to the cathode end of the series LED backlight string. The current drawn through the series LEDs can be programmed via a 6-bit 60dB DAC and dimmed via an internal 4-bit PWM function.  $I^2C$  is used to control LED driver enable, brightness, gradation (soft on/soft off).  $I^2C$ default is LED driver off, current = 0mA.

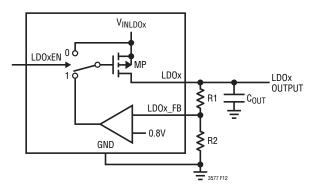

$V_{INLDO1}$  (Pin 23): Input Supply of Low Dropout Linear Regulator 1 (LDO1). This pin should be bypassed to ground with a 1µF or greater ceramic capacitor.

**LD02\_FB (Pin 24):** Feedback Voltage Input for Low Dropout Linear Regulator 2 (LD02). LD02 output voltage is set using an external resistor divider between LD02 and LD02\_FB.

**FB2 (Pin 25):** Feedback Input for Step-Down Switching Regulator 2 (buck2). This pin servos to a fixed voltage of 0.8V when the control loop is complete.

**FB1 (Pin 26):** Feedback Input for Step-Down Switching Regulator 1 (buck1). This pin servos to a fixed voltage of 0.8V when the control loop is complete.

**LD01\_FB (Pin 27):** Feedback Voltage Input for Low Dropout Linear Regulator 1 (LD01). LD01 output voltage is set using an external resistor divider between LD01 and LD01\_FB.

**LD01 (Pin 28):** Output of Low Dropout Linear Regulator 1. This pin must be bypassed to ground with a  $1\mu$ F or greater ceramic capacitor.

**LD02 (Pin 29):** Output of Low Dropout Linear Regulator 2. This pin must be bypassed to ground with a  $1\mu$ F or greater ceramic capacitor.

$V_{INLDO2}$  (Pin 30): Input Supply of Low Dropout Linear Regulator 2 (LDO2). This pin should be bypassed to ground with a 1µF or greater ceramic capacitor.

**SW2 (Pin 31):** Power Transmission (Switch) Pin for Step-Down Switching Regulator 2 (buck2).

$V_{IN12}$  (Pin 32): Power Input for Step-Down Switching Regulators 1 and 2. This pin will generally be connected to  $V_{OUT}$ .

**SW1 (Pin 33):** Power Transmission (Switch) Pin for Step-Down Switching Regulator 1 (buck1). **NTCBIAS (Pin 34):** Output Bias Voltage for NTC. A resistor from this pin to the NTC pin will bias the NTC thermistor.

**NTC (Pin 35):** The NTC pin connects to a battery's thermistor to determine if the battery is too hot or too cold to charge. If the battery's temperature is out of range, charging is paused until it drops back into range. A low drift bias resistor is required from NTCBIAS to NTC and a thermistor is required from NTC to ground.

**PROG (Pin 36):** Charge Current Program and Charge Current Monitor Pin. Connecting a resistor from PROG to ground programs the charge current:

$$_{CHG} = \frac{1000V}{R_{PROG}} (A)$$

I

If sufficient input power is available in constant current mode, this pin servos to 1V. The voltage on this pin always represents the actual charge current.

**IDGATE (Pin 37):** Ideal Diode Gate Connection. This pin controls the gate of an optional external P-channel MOSFET transistor used to supplement the internal ideal diode. The source of the P-channel MOSFET should be connected to  $V_{OUT}$  and the drain should be connected to BAT. It is important to maintain high impedance on this pin and minimize all leakage paths.

**BAT (Pin 38):** Single Cell Li-Ion Battery Pin. Depending on available power and load, a Li-Ion battery on BAT will either deliver system power to  $V_{OUT}$  through the ideal diode or be charged from the battery charger.

**V<sub>OUT</sub> (Pin 39):** Output Voltage of the PowerPath Controller and Input Voltage of the Battery Charger. The majority of the portable product should be powered from V<sub>OUT</sub>. The LTC3577 will partition the available power between the external load on V<sub>OUT</sub> and the internal battery charger. Priority is given to the external load and any extra power is used to charge the battery. An ideal diode from BAT to V<sub>OUT</sub> ensures that V<sub>OUT</sub> is powered even if the load exceeds the allotted input current from V<sub>BUS</sub> or if the V<sub>BUS</sub> power source is removed. V<sub>OUT</sub> should be bypassed with a low impedance multilayer ceramic capacitor.

## PIN FUNCTIONS

$V_{BUS}$  (Pin 40): USB Input Voltage.  $V_{BUS}$  will usually be connected to the USB port of a computer or a DC output wall adapter.  $V_{BUS}$  should be bypassed with a low impedance multilayer ceramic capacitor.

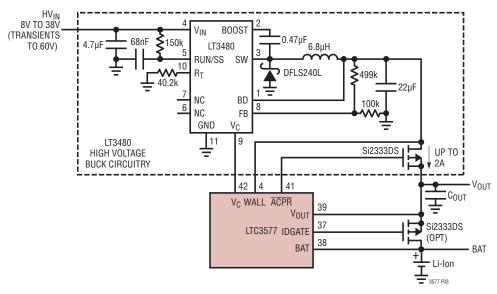

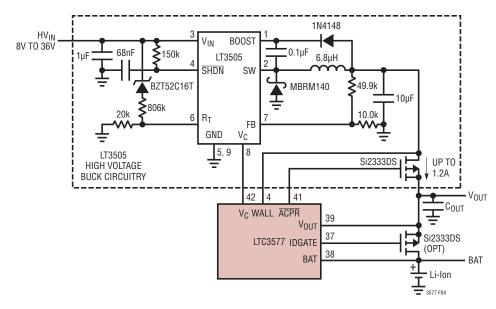

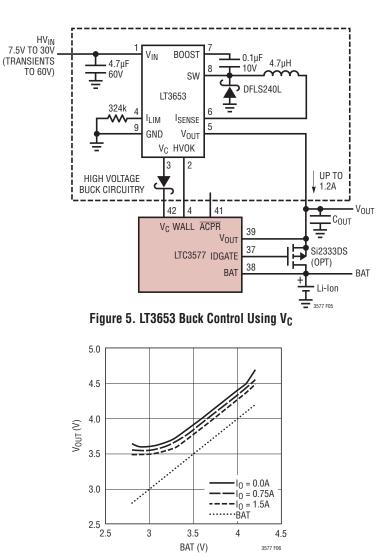

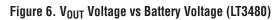

**ACPR** (Pin 41): Wall Adapter Present Output (Active Low). A low on this pin indicates that the wall adapter input comparator has had its input pulled above its input threshold (typically 4.3V). This pin can be used to drive the gate of an external P-channel MOSFET to provide power to V<sub>OUT</sub> from a power source other than a USB port.

$V_C$  (Pin 42): High Voltage Buck Regulator Control Pin. This pin can be used to drive the V<sub>C</sub> pin of an approved external high voltage buck switching regulator. The V<sub>C</sub> pin is designed to work with the LT®3480, LT3653 and LT3505. Consult factory for additional approved high voltage buck regulators. See the "External HV Buck Control through the VC Pin" section for operating information. **CLPROG (Pin 43):** Input Current Program and Input Current Monitor Pin. A resistor from CLPROG to ground determines the upper limit of the current drawn from the  $V_{BUS}$  pin (i.e., the input current limit). A precise fraction of the input current,  $h_{CLPROG}$ , is sent to the CLPROG pin. The input PowerPath delivers current until the CLPROG pin reaches 2V (10x mode), 1V (5x mode) or 0.2V (1x mode). Therefore, the current drawn from V<sub>BUS</sub> will be limited to an amount given by  $h_{CLPROG}$  and  $R_{CLPROG}$ . In USB applications the resistor  $R_{CLPROG}$  should be set to no less than 2.1k.

**CHRG** (Pin 44): Open-Drain Charge Status Output. The CHRG pin indicates the status of the battery charger. If CHRG is high then the charger is near the float voltage (charge current less than 1/10th programmed charge current) or charging is complete and charger is disabled. A low on CHRG indicates that the charger is enabled. For more information see the "Charge Status Indication" section.

**Ground (Exposed Pad Pin 45):** The exposed package pad is ground and must be soldered to PCB ground for electrical contact and rated thermal performance.

### **BLOCK DIAGRAM**

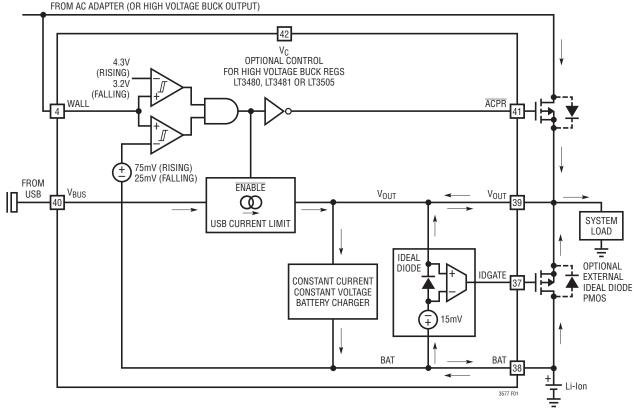

#### PowerPath OPERATION

#### Introduction

The LTC3577 is a highly integrated power management IC that features:

- PowerPath controller

- Battery charger

- Ideal diode

- Input overvoltage protection

- Pushbutton controller

- Three step-down switching regulators

- High voltage buck regulator  $V_{\mbox{C}}$  controller

- Two low dropout linear regulators

- 40V LED backlight controller

Designed specifically for USB applications, the PowerPath controller incorporates a precision input current limit which communicates with the battery charger to ensure