# Hot Swappable 2-Wire Bus Buffer with Low Voltage Level Translation

#### **FEATURES**

- Level Translates 1V Signals to Standard 3.3V and 5V Logic Rails

- Allows Bus Pull-Up Voltages as Low as 1V on SDAIN and SCLIN

- Bidirectional Buffer\* for SDA and SCL Lines Increases Fanout

- Prevents SDA and SCL Corruption During Live Board Insertion and Removal from Backplane

- Isolates Input SDA and SCL Line from Output

- 10kV Human Body Model ESD Protection

- Supports Clock Stretching, Arbitration and Synchronization

- High Impedance SDA, SCL Pins for V<sub>CC</sub> = 0V

- CS Gates Connection from Input to Output

- Compatible with I<sup>2</sup>C<sup>™</sup>, I<sup>2</sup>C Fast Mode and SMBus Standards (Up to 400kHz Operation)

- Small 8-Pin MSOP and DFN (3mm × 3mm) Packages

### **APPLICATIONS**

- Hot Board Insertion

- Servers

- Capacitance Buffer/Bus Extender

- Desktop Computers

#### DESCRIPTION

The LTC®4301L hot swappable, 2-wire bus buffer allows I/O card insertion into a live backplane without corruption of the data and clock busses. In addition, the LTC4301L SDAIN and SCLIN pins are compatible with systems with pull-up voltages as low as 1V. Control circuitry prevents the backplane from being connected to the card until a stop bit or a bus idle is present. When the connection is made, the LTC4301L provides bidirectional buffering, keeping the backplane and card capacitances isolated.

When driven low, the  $\overline{CS}$  input pin allows the part to connect after a stop bit or bus idle occurs. Driving  $\overline{CS}$  high breaks the connection between SCLIN and SCLOUT and between SDAIN and SDAOUT. A logic high on READY indicates that the backplane and card sides are connected together.

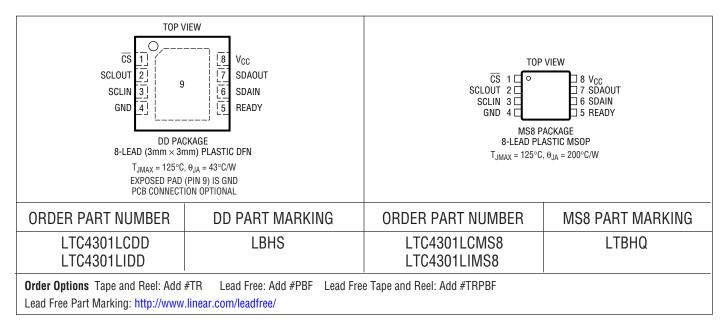

The LTC4301L is offered in 8-pin DFN ( $3mm \times 3mm$ ) and MSOP packages.

7, LT, LTC and LTM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents including 7032051.

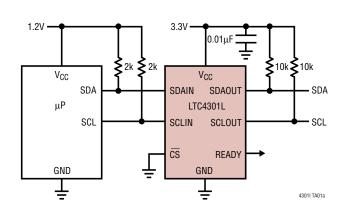

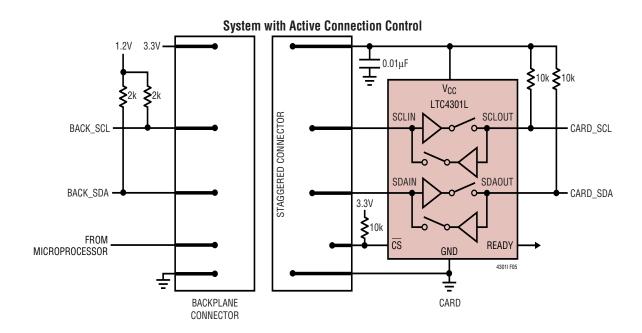

# TYPICAL APPLICATION

LINEAR

# **ABSOLUTE MAXIMUM RATINGS** (Note 1)

| V <sub>CC</sub> to GND          | –0.3V to 7V   |

|---------------------------------|---------------|

| SDAIN, SCLIN, SDAOUT, SCLOUT, C | S –0.3V to 7V |

| READY                           | 0.3V to 6V    |

| Operating Temperature Range     |               |

| LTC4301LC                       | 0°C to 70°C   |

| LTC4301LI                       | 40°C to 85°C  |

| Storage Temperature Range       |               |

|---------------------------------|---------------|

| MSOP                            | 65°C to 150°C |

| DFN                             | 65°C to 125°C |

| Lead Temperature (Soldering, 10 | sec) 300°C    |

# PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ indicates specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{CC} = 2.7V$ to 5.5V, unless otherwise noted.

| SYMBOL              | PARAMETER                  | CONDITIONS                                                                           |   | MIN  | TYP        | MAX  | UNITS    |

|---------------------|----------------------------|--------------------------------------------------------------------------------------|---|------|------------|------|----------|

| Power Sup           | oply                       |                                                                                      |   |      |            |      |          |

| V <sub>CC</sub>     | Positive Supply Voltage    |                                                                                      | • | 2.7  |            | 5.5  | V        |

| I <sub>CC</sub>     | Supply Current             | $V_{CC} = 5.5V, V_{SDAIN} = V_{SCLIN} = 0V$<br>$V_{CC} = 5.5V, \overline{CS} = 5.5V$ | • |      | 4.5<br>300 | 6.2  | mA<br>μA |

| Start-Up C          | ircuitry                   |                                                                                      |   |      |            |      |          |

| V <sub>PRE</sub>    | Precharge Voltage          | SDAOUT, SCLOUT Floating                                                              | • | 0.85 | 1.05       | 1.25 | V        |

| t <sub>IDLE</sub>   | Bus Idle Time              |                                                                                      | • | 60   | 95         | 175  | μS       |

| RDY <sub>VOL</sub>  | READY Output Low Voltage   | I <sub>PULLUP</sub> = 3mA                                                            | • |      |            | 0.4  | V        |

| V <sub>THR</sub> CS | Connection Sense Threshold |                                                                                      |   | 0.8  | 1.4        | 2    | V        |

| I <sub>CS</sub>     | CS Input Current           | CS from 0V to V <sub>CC</sub>                                                        |   |      | ±0.1       | ±1   | μА       |

LINEAR

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ indicates specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25 \,^{\circ}\text{C}$ . $V_{CC} = 2.7 \text{V}$ to 5.5V, unless otherwise noted.

| SYMBOL               | PARAMETER                                                                                        | CONDITIONS                                                               |   | MIN          | TYP        | MAX         | UNITS    |

|----------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---|--------------|------------|-------------|----------|

| $V_{THR}$            | SDAIN, SCLIN Logic Input Threshold Voltage<br>SDAOUT, SCLOUT Logic Input Threshold Voltage       | Rising Edge<br>Rising Edge                                               |   | 0.45<br>1.55 | 0.6<br>1.8 | 0.75<br>2.0 | V        |

| V <sub>HYS</sub>     | SDAIN, SCLIN Logic Input Threshold Hysteresis<br>SDAOUT, SCLOUT Logic Input Threshold Hysteresis | (Note 3)<br>(Note 3)                                                     |   |              | 85<br>50   |             | mV<br>mV |

| t <sub>PLH</sub>     | CS Delay On-Off<br>READY Delay Off-On                                                            |                                                                          |   |              | 10<br>10   |             | ns<br>ns |

| t <sub>PHL</sub>     | CS Delay Off-On<br>READY Delay On-Off                                                            |                                                                          |   |              | 95<br>10   |             | μs<br>ns |

| I <sub>OFF</sub>     | Ready Off Leakage Current                                                                        |                                                                          |   |              | ±0.1       |             | μΑ       |

| Input-Outp           | out Connection                                                                                   |                                                                          |   |              |            |             | <u> </u> |

| V <sub>OS</sub>      | Input-Output Offset Voltage                                                                      | 10k to $V_{CC}$ on SDA, SCL, $V_{CC}$ = 3.3V, SDA or SCL = 0.2V (Note 2) | • | 0            | 100        | 175         | mV       |

| C <sub>IN</sub>      | Digital Input Capacitance SDAIN, SDAOUT, SCLIN, SCLOUT                                           | (Note 3)                                                                 |   |              |            | 10          | pF       |

| I <sub>LEAK</sub>    | Input Leakage Current                                                                            | SDA, SCL Pins                                                            |   |              |            | ±5          | μА       |

| V <sub>OL</sub>      | Output Low Voltage, Input = 0V                                                                   | SDA, SCL Pins,<br>I <sub>SINK</sub> = 3mA, V <sub>CC</sub> = 2.7V        | • | 0            |            | 0.4         | V        |

|                      |                                                                                                  | SDA, SCL Pins,<br>I <sub>SINK</sub> = 1mA, V <sub>CC</sub> = 2.7V        |   | 0            |            | 0.2         | V        |

| Timing Ch            | aracteristics                                                                                    |                                                                          |   |              |            |             |          |

| f <sub>I2C,MAX</sub> | I <sup>2</sup> C Maximum Operating Frequency                                                     | (Note 3)                                                                 |   | 400          | 600        |             | kHz      |

| t <sub>BUF</sub>     | Bus Free Time Between Stop and Start<br>Condition                                                | (Note 3)                                                                 |   |              |            | 1.3         | μѕ       |

| t <sub>HD,STA</sub>  | Hold Time After (Repeated) Start Condition                                                       | (Note 3)                                                                 |   |              |            | 100         | ns       |

| t <sub>SU,STA</sub>  | Repeated Start Condition Set-Up Time                                                             | (Note 3)                                                                 |   |              |            | 0           | ns       |

| t <sub>SU,STO</sub>  | Stop Condition Set-Up Time                                                                       | (Note 3)                                                                 |   |              |            | 0           | ns       |

| t <sub>HD,DATI</sub> | Data Hold Time Input                                                                             | (Note 3)                                                                 |   |              |            | 0           | ns       |

| t <sub>SU,DAT</sub>  | Data Set-Up Time                                                                                 | (Note 3)                                                                 |   |              |            | 100         | ns       |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

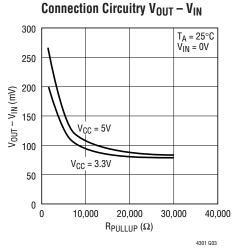

**Note 2:** The connection circuitry always regulates its output to a higher voltage than its input. The magnitude of this offset voltage as a function of the pull-up resistor and  $V_{CC}$  voltage is shown in the Typical Performance Characteristics section.

Note 3: Determined by design, not tested in production.

#### TYPICAL PERFORMANCE CHARACTERISTICS

I<sub>CC</sub> vs Temperature 4.9 4.8  $V_{CC} = 5.5V$ 4.7 4.6 4.5  $V_{CC} = 3.3V$ 4.4 2 4.3  $V_{CC} = 2.7V$ 4.2 4.1 4.0 3.9 -80 -60 -40 -20 20 40 60 80 100 0 TEMPERATURE (°C) 4301 G01

Input - Output High to Low

## PIN FUNCTIONS

**CS** (**Pin 1**): The connection sense pin is <u>a 1</u>.4V threshold digital input pin. For normal operation  $\overline{CS}$  is grounded. Driving  $\overline{CS}$  above the 1.4V threshold isolates SDAIN from SDAOUT and SCLIN from SCLOUT and asserts READY low.

**SCLOUT (Pin 2):** Serial Clock Output. Connect this pin to the SCL bus on the card.

**SCLIN (Pin 3):** Serial Clock Input. Connect this pin to SCL on the bus backplane.

**GND (Pin 4, 9):** Ground. Connect this pin to a ground plane for best results. Exposed pad (DFN package) is ground.

**READY (Pin 5):** The READY pin is an open drain N-channel MOSFET output which pulls down when  $\overline{CS}$  is high or when the start-up sequence described in the Operation section has not been completed. READY goes high when  $\overline{CS}$  is low and a start-up is complete.

**SDAIN (Pin 6):** Serial Data Input. Connect this pin to the SDA bus on the backplane.

**SDAOUT (Pin 7):** Serial Data Output. Connect this pin to the SDA bus on the card.

$V_{CC}$  (Pin 8): Main Input Supply. Place a bypass capacitor of at least 0.01 $\mu$ F close to  $V_{CC}$  for best results.

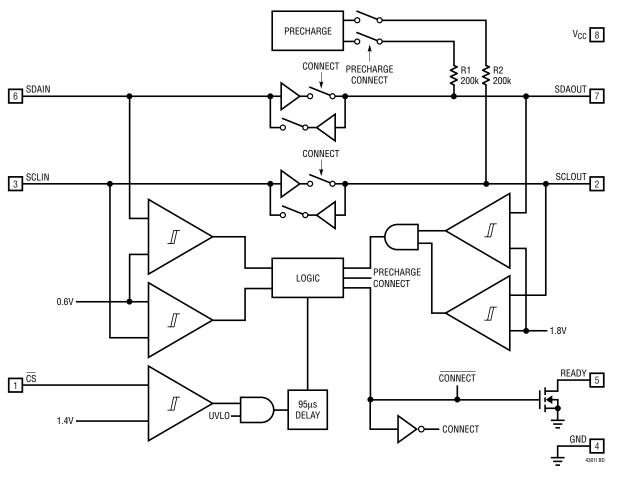

# **BLOCK DIAGRAM**

LTC4301L Supply Independent 2-Wire Bus Buffer

#### **OPERATION**

#### Start-Up

When the LTC4301L first receives power on its  $V_{CC}$  pin, either during power-up or live insertion, it starts in an undervoltage lockout (UVLO) state, ignoring any activity on the SDA or SCL pins until  $V_{CC}$  rises above 2.5V. This is to ensure that the part does not try to function until it has enough voltage to do so.

During this time, the 1V precharge circuitry is active and forces 1V through 200k nominal resistors to the SDAOUT and SCLOUT pins. Precharging the SCLOUT and SDAOUT pins to 1V minimizes the worst-case voltage differential these pins will see at the moment of connection, therefore minimizing bus disturbances.

Once the LTC4301L comes out of UVLO, it assumes that SDAIN and SCLIN have been inserted into a live system and that SDAOUT and SCLOUT are being powered up at the same time as itself. Therefore, it looks for either a stop bit or bus idle condition on the backplane side to indicate the completion of a data transaction. When either one occurs, the part also verifies that both the SDAOUT and SCLOUT voltages are high. When all of these conditions are met, the input-to-output connection circuitry is activated, joining the SDA and SCL busses on the I/O card with those on the backplane.

#### **Connection Circuitry**

Once the connection circuitry is activated, the functionality of the SDAIN and SDAOUT pins is identical. A low forced on either pin at any time results in both pin voltages being low. For proper operation, logic low input voltages should be no higher than 0.4V with respect to the ground pin voltage of the LTC4301L. SDAIN and SDAOUT enter a logic high state only when all devices on both SDAIN and SDAOUT release high. The same is true for SCLIN and SCLOUT. This important feature ensures that clock stretching, clock synchronization, arbitration and the acknowledge protocol always work, regardless of how the devices in the system are tied to the LTC4301L.

Another key feature of the connection circuitry is that it provides bidirectional buffering, keeping the backplane and card capacitances isolated. Because of this isolation, the waveforms on the backplane busses look slightly different than the corresponding card bus waveforms as described here.

#### Input-to-Output Offset Voltage

When a logic low voltage,  $V_{LOW1}$ , is driven on any of the LTC4301L's data or clock pins, the LTC4301L regulates the voltage on the other side of the device (call it  $V_{LOW2}$ ) at a slightly higher voltage, as directed by the following equation:

$$V_{1.0W2} = V_{1.0W1} + 75 \text{mV} + (V_{CC}/R) \cdot 70 \Omega \text{ (typical)}$$

where R is the bus pull-up resistance in ohms. For example, if a device is forcing SDAOUT to 10mV where  $V_{CC} = 3.3V$  and the pull-up resistor R on SDAIN is 10k, then the voltage on SDAIN = 10mV + 75mV + (3.3/10000) • 70 = 108mV(typical). See the Typical Performance Characteristics section for curves showing the offset voltage as a function of  $V_{CC}$  and R.

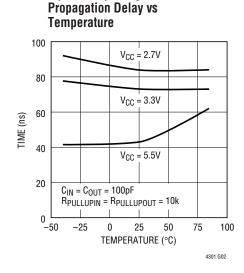

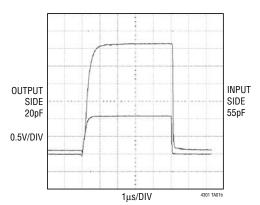

#### **Propagation Delays**

During a rising edge, the rise time on each side is determined by the bus pull-up resistor and the equivalent capacitance on the line. In Figure 1,  $V_{CC}$  = 3.3V, SDAOUT and SCLOUT are pulled-up to 3.3V with 10k resistor (20pF on this side) and SDAIN and SCLIN are pulled-up to 1.2V with a 2k resistor (55pF on this side). Lower pull-up resistor values are used on the input side to allow the output side to be released sooner.

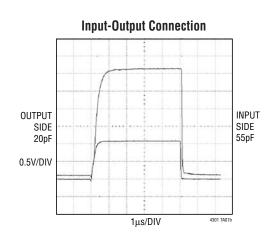

Figure 1. Input-Output Connection

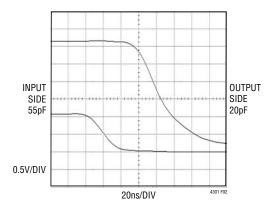

There is a finite high to low propagation delay through the connection circuitry for falling waveforms. Figure 2 shows the falling edge waveforms for the same pull-up resistors and equivalent capacitance conditions as used in Figure 1. An external N-channel MOSFET device pulls down the voltage on the side with 55pF capacitance; LTC4301L pulls down the voltage on the opposite side with a delay of 60ns.

4301lfa

#### **OPERATION**

This delay is always positive and is a function of supply voltage, temperature and the pull-up resistors and equivalent bus capacitances on both sides of the bus. The Typical Performance Characteristics section shows the high to low propagation delay as a function of temperature and voltage for 10k pull-up resistors pulled-up to  $V_{\rm CC}$  and 100pF equivalent capacitance on both sides of the part. Larger output capacitances translate to longer delays (up to 150ns). Users must quantify the difference in propaga-

Figure 2. Input-Output Connection High to Low Propagation Delay

tion times for a rising edge versus a falling edge in their systems and adjust setup and hold times accordingly.

#### **Ready Digital Output**

This pin provides a digital flag which is low when either CS is high or the start-up sequence described earlier in this section has not been completed. READY goes high when  $\overline{\text{CS}}$  is low and start-up is complete. The pin is driven by an open-drain pull-down capable of sinking 3mA while holding 0.4V on the pin. Connect a resistor of 10k to  $V_{CC}$  to provide the pull-up.

#### **Connection Sense**

When the  $\overline{\text{CS}}$  pin is driven above 1.4V with respect to the LTC4301L's ground, the backplane side is disconnected from the card side and the READY pin is internally pulled low. When the pin voltage is low, the part waits for data transactions on both the backplane and card sides to be complete (as described in the Start-Up section) before reconnecting the two sides. At this time the internal pulldown on READY releases.

### APPLICATIONS INFORMATION

#### **Live Insertion and Capacitance Buffering Application**

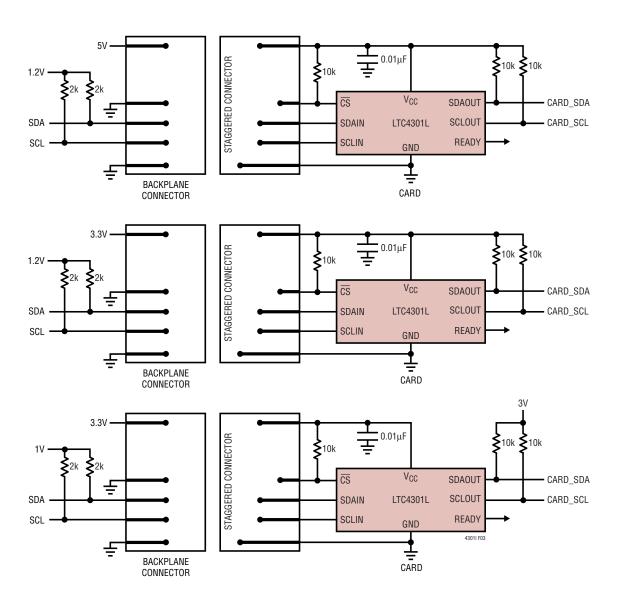

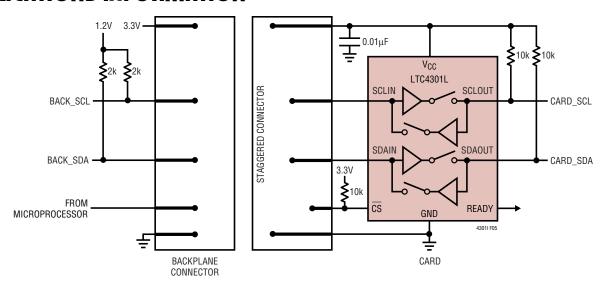

Figure 3 illustrates applications of the LTC4301L with different bus pull-up and  $V_{CC}$  voltages, demonstrating its ability to recognize and buffer bus data levels that are above or below its  $V_{CC}$  supply. All of these applications take advantage of the LTC4301L's Hot Swap<sup>TM</sup> controlling, capacitance buffering and precharge features. If the I/O cards were plugged directly into the backplane without the LTC4301L buffer, all of the backplane and card capacitances would add directly together, making rise- and fall-time requirements difficult to meet. Placing an LTC4301L on the edge of each card, however, isolates the card capacitance from the backplane. For a given I/O card, the LTC4301L drives the capacitance of everything on the card and the backplane must drive only the capacitance of the LTC4301L, which is less than 10pF.

In most applications the LTC4301L will be used with a staggered connector where  $V_{CC}$  and GND will be long pins. SDA and SCL are medium length pins to ensure that the  $V_{CC}$  and GND pins make contact first. This will allow the precharge circuitry to be activated on SDA and SCL before they make contact.  $\overline{CS}$  is a short pin that is pulled up when not connected. This is to ensure that the connection between the backplane and the cards data and clock busses is not enabled until the transients associated with live insertion have settled.

Figure 4 shows the LTC4301L in an application where all of the pins have the same length. In this case, an RC filter circuit on the I/O card with a product of 10ms provides a filter to prevent the LTC4301L from becoming activated until the transients associated with live insertion have settled. Connect the capacitor between  $V_{CC}$  and  $\overline{\mbox{CS}}$ , and the resistor from  $\overline{\mbox{CS}}$  to GND.

Hot Swap is a trademark of Linear Technology Corporation.

4301lfa

# **APPLICATIONS INFORMATION**

Figure 3. Typical Supply Independent Applications

# **APPLICATIONS INFORMATION**

Figure 4. Inserting Multiple I/O Cards into a Live Backplane Using a Connector with All the Pins the Same Length

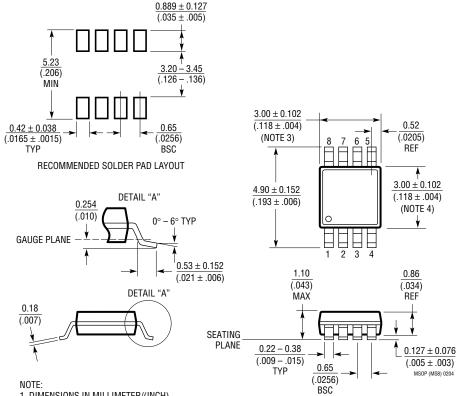

## PACKAGE DESCRIPTION

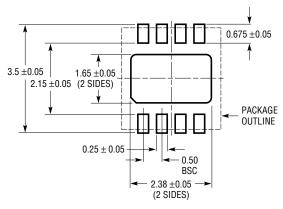

#### **DD Package** 8-Lead Plastic DFN (3mm × 3mm)

(Reference LTC DWG # 05-08-1698)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS

- NOTE:

- 1. DRAWING TO BE MADE A JEDEC PACKAGE OUTLINE M0-229 VARIATION OF (WEED-1)

2. DRAWING NOT TO SCALE

3. ALL DIMENSIONS ARE IN MILLIMETERS

- A. LIMENSIONS ARE IN MILLIMETERS

DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH, MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE 5. EXPOSED PAD SHALL BE SOLDER PLATED

SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON TOP AND BOTTOM OF PACKAGE

## PACKAGE DESCRIPTION

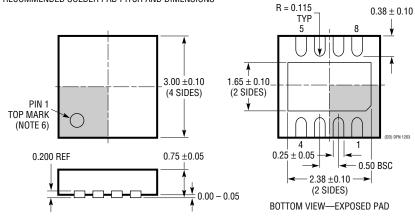

#### MS8 Package 8-Lead Plastic MSOP

(Reference LTC DWG # 05-08-1660)

- NUTE:

1. DIMENSIONS IN MILLIMETER/(INCH)

2. DRAWING NOT TO SCALE

3. DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

- 4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE 5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX

# TYPICAL APPLICATION

## RELATED PARTS

| PART NUMBER           | DESCRIPTION                                                                      | COMMENTS                                                                                                             |  |

|-----------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|

| LTC1380/LTC1393       | Single-Ended 8-Channel/Differential 4-Channel Analog<br>Mux with SMBus Interface | Low $R_{0N}$ : $35\Omega$ Single-Ended/70 $\Omega$ Differential, Expandable to 32 Single or 16 Differential Channels |  |

| LTC1427-50            | Micropower, 10-Bit Current Output DAC with SMBus Interface                       | Precision 50μA ± 2.5% Tolerance Over Temperature,<br>4 Selectable SMBus Addresses, DAC Powers up at Zero or Midscale |  |

| LTC1623               | Dual High Side Switch Controller with SMBus Interface                            | 8 Selectable Addresses/16-Channel Capability                                                                         |  |

| LTC1663               | SMBus Interface 10-Bit Rail-to-Rail Micropower DAC                               | DNL < 0.75LSB Max, 5-Lead SOT-23 Package                                                                             |  |

| LTC1694/LTC1694-1     | SMBus Accelerator                                                                | Improved SMBus/I <sup>2</sup> C Rise-Time,<br>Ensures Data Integrity with Multiple SMBus/I <sup>2</sup> C Devices    |  |

| LT1786F               | SMBus Controlled CCFL Switching Regulator                                        | 1.25A, 200kHz, Floating or Grounded Lamp Configurations                                                              |  |

| LTC1695               | SMBus/l <sup>2</sup> C Fan Speed Controller in ThinSOT™                          | 0.75Ω PMOS 180mA Regulator, 6-Bit DAC                                                                                |  |

| LTC1840               | Dual I <sup>2</sup> C Fan Speed Controller                                       | Two 100µA 8-Bit DACs, Two Tach Inputs, Four GPI0                                                                     |  |

| LTC4300A-1/LTC4300A-2 | Hot Swappable 2-Wire Bus Buffer                                                  | Isolates Backplane and Card Capacitances                                                                             |  |

| LTC4301               | Supply Independent Hot Swappable 2-Wire Bus Buffer                               | Supply Independent                                                                                                   |  |

| LTC4302-1/LTC4302-2   | Addressable 2-Wire Bus Buffer                                                    | Address Expansion, GPIO, Software Controlled                                                                         |  |

ThinSOT is a trademark of Linear Technology Corporation.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Interface - Signal Buffers, Repeaters category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below:

PI6ULS5V9509UEX PI3HDMI101-BZHEX PI3EQX12904AZHEX PI6ULS5V9306WEX PI3EQX1004EZTFEX PI6ULS5V9509WEX PI3EQX6801AZDEX 48705-3001R2 48705-6501R2 DS280BR820ZBLT PCA9617ADPJ PI6ULS5V9515AWEX PI3HDMI101ZHE P82B715TD.112 LTC4315CDE#PBF LTC4300-1CMS8#PBF DS110DF1610FB/NOPB LTC4301LCDD#PBF LTC4303IDD#PBF LTC4315IMS#TRPBF LTC4304IMS#PBF DS280DF810ABVT LTC4313IDD-3#PBF LTC4315IDE#PBF LTC4300-1IMS8#PBF LTC4313IMS8-3#TRPBF LTC4300-2IMS8#PBF LTC4313IMS8-1#PBF LTC4300A-1CMS8#PBF LTC4304CDD#PBF LTC4307CMS8-1#TRPBF PI3EQX1002B1ZLEX PI3EQX12904EZHEX PI6ULS5V9517BUEX LTC4301LIMS8 LTC4313IDD-3#TRPBF PI3EQX1002EZREX LTC4309IGN#PBF LTC4309CGN#PBF P82B96TDS900,118 PCA9515AD,118 MAX9169EUE+ LTC4302IMS-2#PBF LTC4304CMS#PBF LTC4302CMS-1#PBF PI6ULS5V9306UEX LTC4300A-1CMS8#TRPBF P82B715TD,112 PCA9507DP,118 PCA9515ADP,118