LTC4353

# Dual Low Voltage Ideal Diode Controller

### FEATURES

- Low Loss Replacement for Power Diodes

- Controls N-Channel MOSFETs

- OV to 18V Supply ORing or Holdup

- 1µs Gate Turn-On and Turn-Off Time

- Enable Inputs

- MOSFET On-Status Outputs

- 16-Lead MSOP and DFN (4mm × 3mm) Packages

### **APPLICATIONS**

- Redundant Power Supplies

- Supply Holdup

- High Availability Systems and Servers

- Telecom and Network Infrastructure

### DESCRIPTION

The LTC<sup>®</sup>4353 controls external N-channel MOSFETs to implement an ideal diode function. It replaces two high power Schottky diodes and their associated heat sinks, saving power and board area. The ideal diode function permits low loss power supply ORing and supply holdup applications.

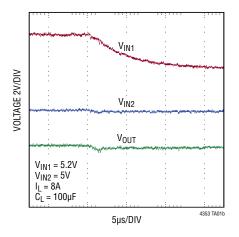

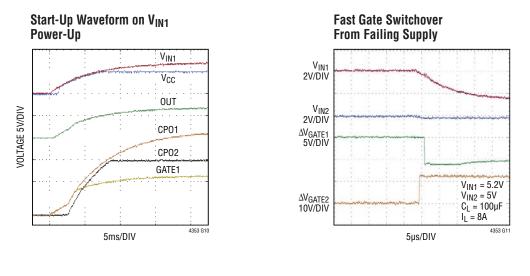

The LTC4353 regulates the forward-voltage drop across the MOSFET to ensure smooth current transfer in diode-OR applications. A fast turn-on reduces the load voltage droop during supply switchover. If the input supply fails or is shorted, a fast turn-off minimizes reverse-current transients.

The controller operates with supplies from 2.9V to 18V. If both supplies are below 2.9V, an external supply is needed at the  $V_{CC}$  pin. Enable inputs can be used to turn off the MOSFET and put the controller in a low current state. Status outputs indicate whether the MOSFETs are on or off.

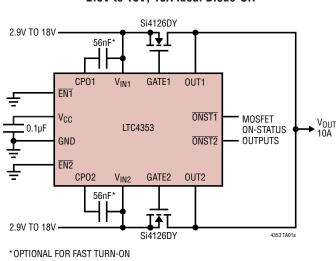

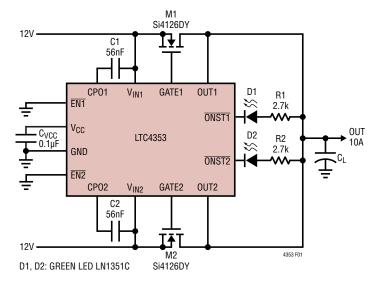

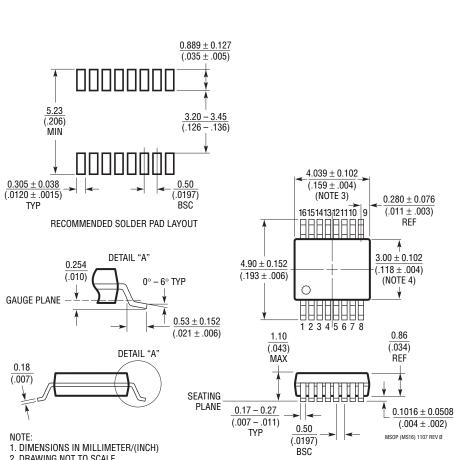

# TYPICAL APPLICATION

2.9V to 18V, 10A Ideal Diode-OR

#### Output Maintained with Failing Input Supply

# ABSOLUTE MAXIMUM RATINGS (Notes 1, 2)

| V <sub>IN1</sub> , V <sub>IN2</sub> , OUT1, OUT2 Voltages | 2V to 24V    |

|-----------------------------------------------------------|--------------|

| V <sub>CC</sub> Voltage                                   | 0.3V to 6.5V |

| GATE1, GATE2 Voltages (Note 3)                            | 0.3V to 34V  |

| CPO1, CPO2 Voltages (Note 3)                              | 0.3V to 34V  |

| EN1, EN2, ONST1, ONST2 Voltages                           | 0.3V to 24V  |

| CPO1, CPO2 Average Current                                | 10mA         |

| ONST1, ONST2 Currents                                     | 5mA          |

| Operating Ambient Temperature Range  |                  |

|--------------------------------------|------------------|

| LTC4353C                             | 0°C to 70°C      |

| LTC4353I                             | 40°C to 85°C     |

| Storage Temperature Range            | . –65°C to 150°C |

| Lead Temperature (Soldering, 10 sec) |                  |

| MS Package                           | 300°C            |

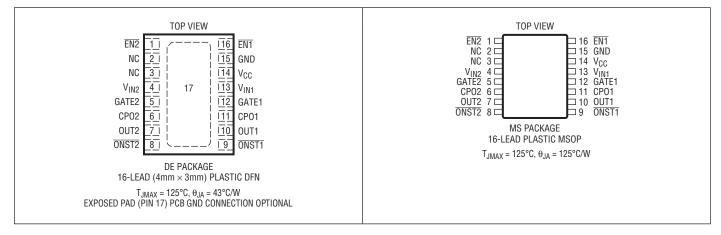

### PIN CONFIGURATION

# **ORDER INFORMATION**

| LEAD FREE FINISH | TAPE AND REEL    | PART MARKING* | PACKAGE DESCRIPTION            | TEMPERATURE RANGE |

|------------------|------------------|---------------|--------------------------------|-------------------|

| LTC4353CDE#PBF   | LTC4353CDE#TRPBF | 4353          | 16-Pin (4mm × 3mm) Plastic DFN | 0°C to 70°C       |

| LTC4353IDE#PBF   | LTC4353IDE#TRPBF | 4353          | 16-Pin (4mm × 3mm) Plastic DFN | -40°C to 85°C     |

| LTC4353CMS#PBF   | LTC4353CMS#TRPBF | 4353          | 16-Pin Plastic MSOP            | 0°C to 70°C       |

| LTC4353IMS#PBF   | LTC4353IMS#TRPBF | 4353          | 16-Pin Plastic MSOP            | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

4353f

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes those specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>IN1</sub> = V<sub>IN2</sub> = 12V, OUT = V<sub>IN</sub>, V<sub>CC</sub> Open, unless otherwise noted.

| SYMBOL                 | PARAMETER                                                                                                             | CONDITIONS                                                                                                                                                                                                                                                                                   |             | MIN                  | ТҮР                    | MAX                      | UNITS          |

|------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------|------------------------|--------------------------|----------------|

| Supplies               | 1                                                                                                                     |                                                                                                                                                                                                                                                                                              |             | ,                    |                        |                          |                |

| V <sub>IN</sub>        | $V_{IN1}, V_{IN2}$ Operating Range                                                                                    | With External V <sub>CC</sub> Supply                                                                                                                                                                                                                                                         | •           | 2.9<br>0             |                        | 18<br>V <sub>CC</sub>    | V<br>V         |

| V <sub>CC(EXT)</sub>   | V <sub>CC</sub> External Supply Operating Range                                                                       | $V_{IN1}, V_{IN2} \leq V_{CC}$                                                                                                                                                                                                                                                               | •           | 2.9                  |                        | 6                        | V              |

| V <sub>CC(REG)</sub>   | V <sub>CC</sub> Regulated Voltage                                                                                     |                                                                                                                                                                                                                                                                                              |             | 4.5                  | 5                      | 5.5                      | V              |

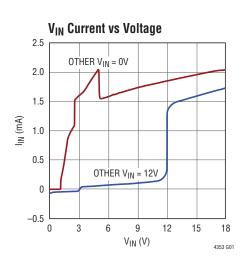

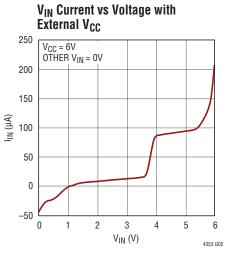

| IIN                    | V <sub>IN1</sub> , V <sub>IN2</sub> Current<br>Enabled, Higher Supply<br>Enabled, Lower Supply<br>Pull-Up<br>Disabled | $\begin{array}{l} \mbox{Other } V_{IN} = 11.7V, \mbox{ Both } \overline{EN} = 0V \\ \mbox{Other } V_{IN} = 12.3V, \mbox{ Both } \overline{EN} = 0V \\ \mbox{ Both } \underline{V_{IN}} = 0V,  V_{CC} = 5V, \mbox{ Both } \overline{EN} = 0V \\ \mbox{ Both } \overline{EN} = 1V \end{array}$ | •<br>•<br>• |                      | 1.5<br>200<br>45<br>75 | 2.5<br>300<br>-80<br>160 | mA<br>μA<br>μA |

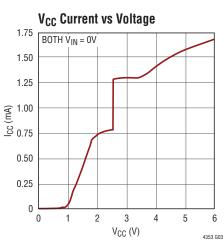

| Icc                    | V <sub>CC</sub> Current<br>Enabled<br>Disabled                                                                        | $V_{CC} = 5V$ , Both $V_{IN} = 1.2V$ , Both $\overline{EN} = 0V$<br>$V_{CC} = 5V$ , Both $V_{IN} = 1.2V$ , Both $\overline{EN} = 1V$                                                                                                                                                         | •           |                      | 1.5<br>88              | 2.2<br>190               | mA<br>μA       |

| V <sub>CC(UVLO)</sub>  | V <sub>CC</sub> Undervoltage Lockout Threshold                                                                        | V <sub>CC</sub> Rising                                                                                                                                                                                                                                                                       | •           | 2.3                  | 2.55                   | 2.7                      | V              |

| $\Delta V_{CC(HYST)}$  | V <sub>CC</sub> Undervoltage Lockout Hysteresis                                                                       |                                                                                                                                                                                                                                                                                              | •           | 40                   | 120                    | 300                      | mV             |

| Ideal Diode (          | Control                                                                                                               |                                                                                                                                                                                                                                                                                              |             |                      |                        |                          |                |

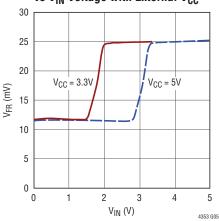

| V <sub>FR</sub>        | Forward Regulation Voltage (V <sub>IN</sub> – OUT)                                                                    | $V_{IN} = 1.2V, V_{CC} = 5V$<br>$V_{IN} = 12V$                                                                                                                                                                                                                                               | •           | 2<br>2               | 12<br>25               | 25<br>50                 | mV<br>mV       |

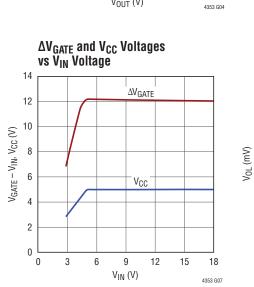

| $\Delta V_{GATE}$      | MOSFET Gate Drive (GATE – V <sub>IN</sub> )                                                                           | $\label{eq:VFWD} \begin{array}{l} V_{FWD} = 0.2V; \ I = 0, \ -1\mu\text{A}; \ \text{Highest} \ V_{IN} = 12V \\ V_{FWD} = 0.2V; \ I = 0, \ -1\mu\text{A}; \ \text{Highest} \ V_{IN} = 2.9V \end{array}$                                                                                       | •           | 10<br>4.5            | 12<br>7                | 14<br>9                  | V<br>V         |

| t <sub>ON(GATE)</sub>  | GATE1, GATE2 Turn-On Propagation Delay                                                                                | V <sub>FWD</sub> (= V <sub>IN</sub> – OUT) Step: –0.3V to 0.3V                                                                                                                                                                                                                               | •           |                      | 0.4                    | 1                        | μs             |

| t <sub>OFF(GATE)</sub> | GATE1, GATE2 Turn-Off Propagation Delay                                                                               | V <sub>FWD</sub> Step: 0.3V to -0.3V                                                                                                                                                                                                                                                         |             |                      | 0.3                    | 1                        | μs             |

| I <sub>GATE</sub>      | GATE1, GATE2 Fast Pull-Up Current<br>GATE1, GATE2 Fast Pull-Down Current<br>GATE1, GATE2 Off Pull-Down Current        | $ \begin{array}{l} V_{FWD} = 0.4V, \ \Delta V_{GATE} = 0V, \ CPO = 17V \\ V_{FWD} = -0.8V, \ \ \Delta V_{GATE} = 5V \\ Corresponding \ \overline{EN} = 1V, \ \Delta V_{GATE} = 2.5V \end{array} $                                                                                            | •           | -0.9<br>0.9<br>65    | -1.4<br>1.4<br>110     | -1.9<br>1.9<br>160       | Α<br>Α<br>μΑ   |

| Input/Output           | Pins                                                                                                                  |                                                                                                                                                                                                                                                                                              |             |                      |                        |                          |                |

| V <sub>EN(TH)</sub>    | EN1, EN2 Threshold Voltage                                                                                            | EN Falling                                                                                                                                                                                                                                                                                   |             | 580                  | 600                    | 620                      | mV             |

| $\Delta V_{EN(TH)}$    | EN1, EN2 Threshold Hysteresis                                                                                         |                                                                                                                                                                                                                                                                                              | •           | 2                    | 8                      | 20                       | mV             |

| I <sub>EN</sub>        | EN1, EN2 Current                                                                                                      | At 0.6V                                                                                                                                                                                                                                                                                      | •           |                      | 0                      | ±1                       | μA             |

| I <sub>OUT</sub>       | OUT1, OUT2 Current<br>Enabled<br>Disabled                                                                             | $OUTn = 0V, 12V; Both \overline{EN} = 0V$<br>Both $\overline{EN} = 1V$                                                                                                                                                                                                                       | •           | -4                   | 8                      | 160<br>16                | μA<br>μA       |

| I <sub>CPO(UP)</sub>   | CP01, CP02 Pull-Up Current                                                                                            | CPO = V <sub>IN</sub>                                                                                                                                                                                                                                                                        |             | -40                  | -70                    | -115                     | μA             |

| V <sub>OL</sub>        | ONST1, ONST2 Output Low Voltage                                                                                       | I = 1mA<br>I = 3mA                                                                                                                                                                                                                                                                           | •           |                      | 0.14<br>0.42           | 0.4<br>1.2               | V<br>V         |

| V <sub>OH</sub>        | ONST1, ONST2 Output High Voltage                                                                                      | I = -1µA                                                                                                                                                                                                                                                                                     |             | V <sub>CC</sub> -1.4 | $V_{CC} - 0.9$         | V <sub>CC</sub> - 0.5    | V              |

| IONST                  | ONST1, ONST2 Leakage Current                                                                                          | At 12V                                                                                                                                                                                                                                                                                       |             |                      | 0                      | ±1                       | μA             |

| $\Delta V_{GATE(ON)}$  | MOSFET On-Detect Threshold (GATE – VIN)                                                                               | ONST Pulls Low                                                                                                                                                                                                                                                                               |             | 0.28                 | 0.7                    | 1.1                      | V              |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to GND unless otherwise specified.

Note 3: Internal clamps limit the GATE and CPO pins to a minimum of 10V above, and a diode below the corresponding  $V_{\mbox{IN}}$  pin. Driving these pins to voltages beyond the clamp may damage the device.

4353

### TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$

$T_A=25^\circ C, \ V_{IN1}=V_{IN2}=12V, \ OUT=V_{IN}, \ V_{CC}$  open,

unless otherwise noted.

**OUT Current vs Voltage** 250 200 150 Ιουτ (μΑ) 100 50 0 -50 3 6 9 12 15 18 0 V<sub>OUT</sub> (V)

Forward Regulation Voltage vs  $V_{IN}$  Voltage with External  $V_{CC}$

**ONST** Output Low Voltage

2

3

IONST (mA)

4

5

4353 G08

vs Current

800

600

400

200

0

0

1

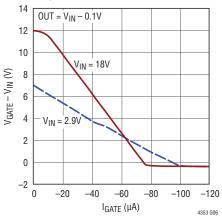

ΔV<sub>GATE</sub> Voltage vs Current

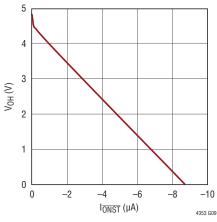

ONST Output High Voltage vs Current

4353f

# **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , $V_{IN1} = V_{IN2} = 12V$ , $OUT = V_{IN}$ , $V_{CC}$ open, unloss otherwise noted

unless otherwise noted.

### PIN FUNCTIONS

**CP01, CP02:** Charge Pump Output. Connect a capacitor from this pin to the corresponding  $V_{IN}$  pin. The value of this capacitor should be approximately 10× the gate capacitance (C<sub>ISS</sub>) of the MOSFET switch. The charge stored on this capacitor is used to pull-up the gate during a fast turn-on. Leave this pin open if fast turn-on is not needed.

**EN1**, **EN2**: Enable Input. Keep this pin below 0.6V to enable diode control on the corresponding supply. Driving this pin high shuts off the MOSFET gate (current can still flow through its body diode). The comparator has a built-in hysteresis of 8mV. Having both **EN** pins high lowers the current consumption of the controller.

**Exposed Pad (DE Package Only):** This pin may be left open or connected to device ground.

**GATE1, GATE2:** MOSFET Gate Drive Output. Connect this pin to the gate of the external N-channel MOSFET switch. An internal clamp limits the gate voltage to 12V above, and a diode below the input supply. During fast turn-on, a 1.4A pull-up current charges GATE from CPO. During fast turn-off, a 1.4A pull-down current discharges GATE to  $V_{IN}$ .

**GND:** Device Ground.

**ONST1**, **ONST2**: MOSFET Status Output. This pin is pulled low by an internal switch when GATE is more than 0.7V above  $V_{IN}$  to indicate an on MOSFET. An internal 500k resistor pulls this pin up to a diode below  $V_{CC}$ . It may be pulled above  $V_{CC}$  using an external pull-up. Tie to GND or leave open if unused.

**OUT1, OUT2:** Output Voltage Sense Input. Connect this pin to the load side of the MOSFET. The voltage sensed at this pin is used to control the MOSFET gate.

**V<sub>CC</sub>:** Low Voltage Supply. Connect a 0.1µF capacitor from this pin to ground. For V<sub>IN</sub>  $\geq$  2.9V, this pin provides decoupling for an internal regulator that generates a 5V supply. For applications where both V<sub>IN</sub> < 2.9V, also connect an external supply voltage in the 2.9V to 6V range to this pin.

$V_{\text{IN1}},~V_{\text{IN2}}$ : Voltage Sense and Supply Input. Connect this pin to the supply side of the MOSFET. The low voltage supply  $V_{\text{CC}}$  is generated from the higher of  $V_{\text{IN1}}$  and  $V_{\text{IN2}}$ . The voltage sensed at this pin is used to control the MOSFET gate.

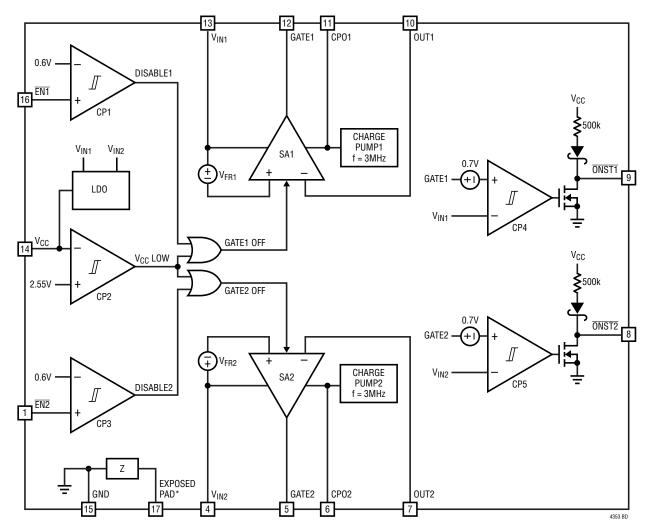

# FUNCTIONAL DIAGRAM

\*DE PACKAGE ONLY

# OPERATION

The LTC4353 controls N-channel MOSFETs to emulate two ideal diodes. When enabled, each servo amplifier (SA1, SA2) controls the gate of the external MOSFET to servo its forward voltage drop ( $V_{FWD} = V_{IN} - OUT$ ) to  $V_{FR}$ . The gate voltage rises to enhance the MOSFET if the load current causes the drop to exceed  $V_{FR}$ . For large output currents, the MOSFET gate is driven fully on and the voltage drop is equal to  $I_{FET} \bullet R_{DS(ON)}$ .

In the case of an input supply short-circuit, when the MOSFET is conducting, a large reverse current starts flowing from the load towards the input. SA detects this failure condition as soon as it appears, and turns off the MOSFET by rapidly pulling down its gate.

SA quickly pulls up the gate whenever it senses a large forward voltage drop. An external capacitor between the CPO and  $V_{IN}$  pins is needed for fast gate pull-up. This capacitor

is charged up, at device power-up, by the internal charge pump. The stored charge is used for the fast gate pull-up.

The GATE pin sources current from the CPO pin and sinks current to the V<sub>IN</sub> and GND pins. Clamps limit the GATE and CPO voltages to 12V above and a diode below V<sub>IN</sub>. Internal switches pull the ONST pins low when the GATE to V<sub>IN</sub> voltage exceeds 0.7V to indicate that power is passing through the MOSFET.

LDO is a low dropout regulator that generates a 5V supply at the V<sub>CC</sub> pin from the highest V<sub>IN</sub> input. When both V<sub>IN</sub> are below 2.9V, an external supply in the 2.9V to 6V range is required at the V<sub>CC</sub> pin.

$V_{CC}$  and  $\overline{EN}$  pin comparators, CP1 to CP3, control power passage. The MOSFET is held off whenever the  $\overline{EN}$  pin is above 0.6V, or the  $V_{CC}$  pin is below 2.55V. A high on both  $\overline{EN}$  pins lowers the current consumption of the device.

# **APPLICATIONS INFORMATION**

High availability systems often employ parallel connected power supplies or battery feeds to achieve redundancy and enhance system reliability. ORing diodes have been a popular means of connecting these supplies at the point of load. Diodes followed by storage capacitors also hold up supply voltages when an input voltage sags or has a brownout. The disadvantage of these approaches is the diode's significant forward-voltage drop and the resulting power loss. The LTC4353 solves these problems by using an external N-channel MOSFET as the pass element (see Figure 1). The MOSFET is turned on when power is being passed, allowing for a low voltage drop from the supply to the load. When the input source voltage drops below the output common supply voltage it turns off the MOSFET, thereby matching the function and performance of an ideal diode.

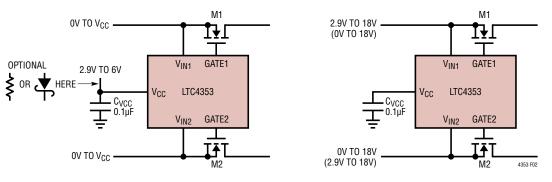

### **Power Supply Configuration**

The LTC4353 can operate with input supplies down to OV. This requires powering the V<sub>CC</sub> pin with an early external supply in the 2.9V to 6V range. In this range of operation V<sub>IN</sub> should be lower than V<sub>CC</sub>. If V<sub>CC</sub> powers up after V<sub>IN</sub> and backfeeding of V<sub>CC</sub> by the internal 5V LDO is a concern, then a series resistor (few 100 $\Omega$ ) or Schottky diode limits device power dissipation and backfeeding of a low V<sub>CC</sub> supply when any V<sub>IN</sub> is high. A 0.1µF bypass capacitor should also be connected between the V<sub>CC</sub> and GND pins, close to the device. Figure 2 illustrates this.

If either  $V_{IN}$  operates above 2.9V, the external supply at  $V_{CC}$  is not needed. The 0.1  $\mu F$  capacitor is still required for bypassing.

Figure 1. 12V Ideal Diode-OR with Status Lights

4353f

# **APPLICATIONS INFORMATION**

#### **MOSFET Selection**

The LTC4353 drives N-channel MOSFETs to conduct the load current. The important features of the MOSFET are its maximum drain-source voltage  $BV_{DSS}$ , maximum gate-source voltage  $V_{GS(MAX)}$ , and the on-resistance  $R_{DS(ON)}$ .

If an input is connected to ground, the full supply voltage can appear across the MOSFET. To survive this, the BV<sub>DSS</sub> must be higher than the supply voltages. The V<sub>GS(MAX)</sub> rating of the MOSFET should exceed 14V since that is the upper limit of the internal GATE to V<sub>IN</sub> clamp. The R<sub>DS(ON)</sub> of the MOSFET dictates the maximum voltage drop (I<sub>L</sub> • R<sub>DS(ON)</sub>) and the power dissipated (I<sub>L</sub><sup>2</sup> • R<sub>DS(ON)</sub>) in the MOSFET. Note that the minimum MOSFET voltage drop is controlled by the servo amplifier regulation voltage, hence, picking a very low R<sub>DS(ON)</sub> (below V<sub>FR</sub>/I<sub>L</sub>) may not be beneficial.

#### **CPO Capacitor Selection**

The recommended value of the capacitor between the CPO and  $V_{\rm IN}$  pins is approximately 10× the input capacitance  $C_{\rm ISS}$  of the MOSFET. A larger capacitor takes a correspondingly longer time to be charged by the internal charge pump. A smaller capacitor suffers more voltage drop during a fast gate turn-on event as it shares charge with the MOSFET gate capacitance.

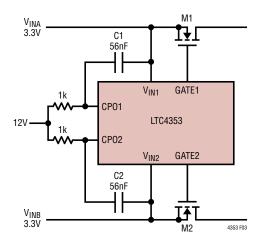

#### **External CPO Supply**

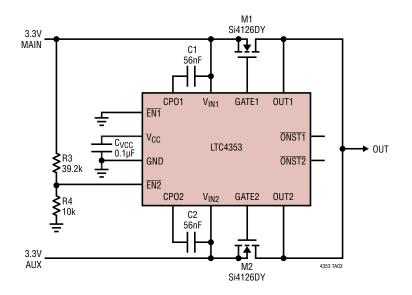

The internal charge pump takes milliseconds to charge up the CPO capacitor especially during device power-up. This time can be shortened by connecting an external supply to the CPO pin. A series resistor is needed to limit the current into the internal clamp between CPO and  $V_{IN}$  pins. The CPO supply should also be higher than the main input supply to meet the gate drive requirements of the MOSFET. Figure 3 shows such a 3.3V ideal diode application, where a 12V supply is connected to the CPO pins through a 1k resistor. The 1k limits the current into the CPO pin, when the  $V_{IN}$  pin is grounded. For the 8.7V gate drive (12V – 3.3V), logic-level MOSFETs would be an appropriate choice for M1 and M2.

#### **Input Transient Protection**

When the capacitances at the input and output are very small, rapid changes in current can cause transients that exceed the 24V absolute maximum rating of the  $V_{IN}$  and OUT pins. In ORing applications, one surge suppressor connected from OUT to ground clamps all the inputs. In the absence of a surge suppressor, an output capacitance of  $10\mu$ F is sufficient in most applications to prevent the transient from exceeding 24V.

Figure 3. 3.3V Ideal Diode with External 12V Supply Powering CPO for Faster Start-Up and Refresh

# **APPLICATIONS INFORMATION**

### **Design Example**

The following design example demonstrates the calculations involved for selecting components in a 12V system with 10A maximum load current (see Figure 1).

First, calculate the  $R_{DS(ON)}$  of the MOSFET to achieve the desired forward drop at full load. Assuming a  $V_{DROP}$  of 30mV:

$$\mathsf{R}_{\mathsf{DS}(\mathsf{ON})} \leq \frac{\mathsf{V}_{\mathsf{DROP}}}{\mathsf{I}_{\mathsf{LOAD}}} = \frac{30 \text{mV}}{10 \text{A}} = 3 \text{m} \Omega$$

The Si4126DY offers a good solution in a SO-8 sized package with a 2.8m $\Omega$  maximum  $R_{DS(ON)},$  30V  $BV_{DSS},$  and 20V  $V_{GS(MAX)}.$  The maximum power dissipation in the MOSFET is:

$\mathsf{P} = \mathsf{I}^2_{\mathsf{LOAD}} \bullet \mathsf{R}_{\mathsf{DS}(\mathsf{ON})} = (10\mathsf{A})^2 \bullet 2.8 \mathsf{m}\Omega = 0.3\mathsf{W}$

With a maximum steady-state thermal resistance  $\theta_{JA}$  of 35°C/W, 0.3W causes a modest 11°C rise in junction temperature of the Si4126DY above the ambient.

The input capacitance,  $C_{ISS}$ , of the Si4126DY is about 5500pF. Following the 10× recommendation, a 56nF capacitor is selected for C1 and C2.

LEDs, D1 and D2, require around 3mA for good luminous intensity. Accounting for a 2V diode drop and 0.6V  $V_{0L},\,$  R1 and R2 are set to 2.7k.

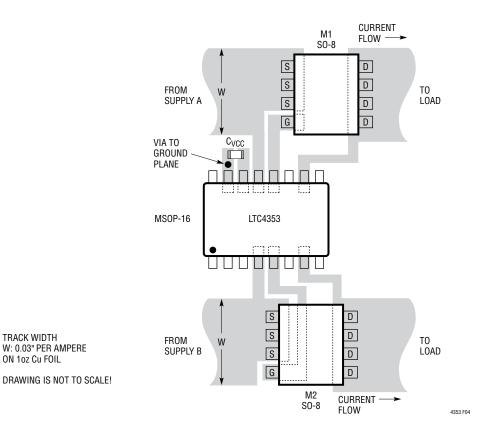

#### **PCB Layout Considerations**

Connect the  $V_{IN}$  and OUT pin traces as close as possible to the MOSFET's terminals. Keep the traces to the MOS-FET wide and short to minimize resistive losses. The PCB traces associated with the power path through the MOSFET should have low resistance (see Figure 4).

It is also important to put  $C_{VCC}$ , the bypass capacitor for the  $V_{CC}$  pin, as close as possible between  $V_{CC}$  and GND. Place C1 and C2 near the CPO and  $V_{IN}$  pins. Surge suppressors, when used, should be mounted close to the LTC4353 using short lead lengths.

### **TYPICAL APPLICATIONS**

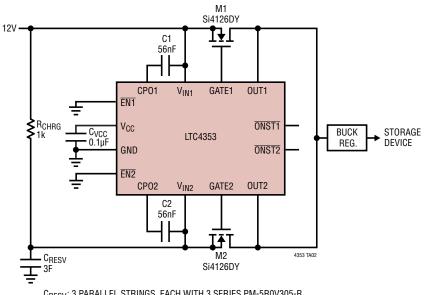

12V Supply with Capacitive Reservoir for Data Backup on Power Fail for Disk Drive and Solid-State Drive Applications

CRESV: 3 PARALLEL STRINGS, EACH WITH 3 SERIES PM-5R0V305-R

3.3V Main and Auxiliary Supply Diode-OR (Auxiliary Ideal Diode Disabled if Main Above 2.95V)

# TYPICAL APPLICATIONS

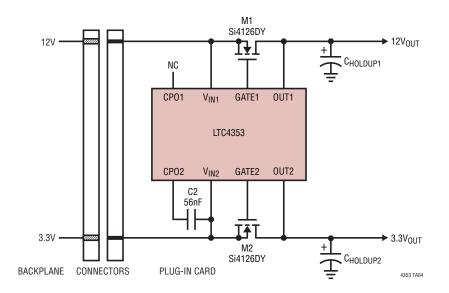

Plug-in Card Supply Holdup Using Ideal Diode at 12V and 3.3V Inputs

### **TYPICAL APPLICATIONS**

POWER SUPPLY MODULE 1 Si4126DY LOAD 1+I CARD 1 NC \_ \_ \_ CP01 GATE1 V<sub>IN1</sub> 0UT1 EN1 ÷ V<sub>CC</sub> **ONST1** 0.1µF LTC4353 12V · GND **ONST2** EN2 Ī CPO2 GATE2 OUT2  $V_{IN2}$ Т NC Si4126DY LOAD CARD 2 Ŀ POWER SUPPLY MODULE 2 Si4126DY 1+I NC CP01 GATE1 OUT1 V<sub>IN1</sub> EN1 ÷ **ONST1** V<sub>CC</sub> 0.1µF LTC4353 12V · GND **ONST2** EN2 CPO2 GATE2 OUT2 V<sub>IN2</sub> NC Si4126DY 4353 TA05

Redundant Power Supply System with ORing on Backplane, as in MicroTCA

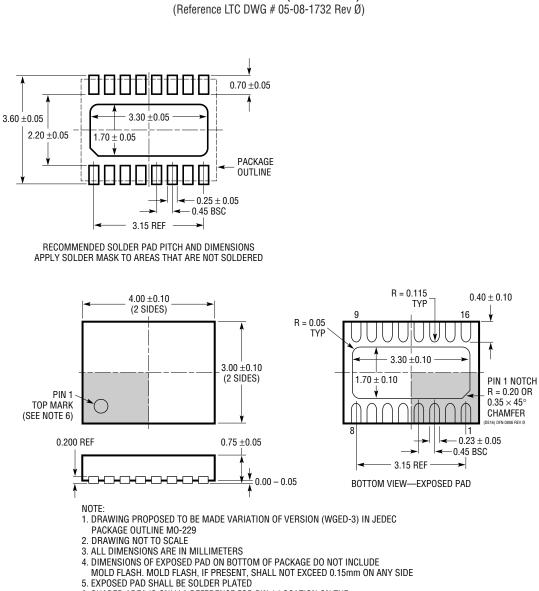

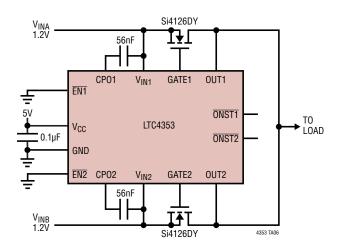

### PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

**DE Package** 16-Lead Plastic DFN (4mm  $\times$  3mm)

6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE

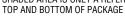

### PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

**MS Package 16-Lead Plastic MSOP** (Reference LTC DWG # 05-08-1669 Rev Ø)

2. DRAWING NOT TO SCALE

3. DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE 4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX

# TYPICAL APPLICATION

#### 1.2V Ideal Diode-OR

# **RELATED PARTS**

| PART NUMBER       | DESCRIPTION                                                           | COMMENTS                                                                                               |  |

|-------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| LTC1473/LTC1473L  | Dual PowerPath <sup>™</sup> Switch Driver                             | N-Channel, 4.75V to 30V/3.3V to 10V, SSOP-16 Package                                                   |  |

| LTC1479           | PowerPath Controller for Dual Battery Systems                         | Three N-Channel Drivers, 6V to 28V, SSOP-36 Package                                                    |  |

| LTC4352           | Low Voltage Ideal Diode Controller with Monitoring                    | N-Channel, OV to 18V, UV, OV, MSOP-12 and DFN-12 Packages                                              |  |

| LTC4354           | Negative Voltage Diode-OR Controller and Monitor                      | Dual N-Channel, -4.5V to -80V, SO-8 and DFN-8 Packages                                                 |  |

| LTC4355           | Positive High Voltage Ideal Diode-OR with Supply and Fuse Monitors    | Dual N-Channel, 9V to 80V, SO-16 and DFN-14 Packages                                                   |  |

| LTC4357           | Positive High Voltage Ideal Diode Controller                          | N-Channel, 9V to 80V, MSOP-8 and DFN-6 Packages                                                        |  |

| LTC4358           | 5A Ideal Diode                                                        | Internal N-Channel, 9V to 26.5V, TSSOP-16 and DFN-14 Packages                                          |  |

| LTC4370           | Two-Supply Diode-OR Current Sharing Controller                        | Dual N-Channel, OV to 18V, MSOP-16 and DFN-16 Packages                                                 |  |

| LTC4411           | 2.6A Low Loss Ideal Diode in ThinSOT™                                 | Internal P-Channel, 2.6V to 5.5V, 40µA I <sub>Q</sub> , SOT-23 Package                                 |  |

| LTC4412/LTC4412HV | Low Loss PowerPath Controller in ThinSOT                              | P-Channel, 2.5V to 28V/36V, 11µA I <sub>Q</sub> , SOT-23 Package                                       |  |

| LTC4413/LTC4413-1 | Dual 2.6A, 2.5V to 5.5V, Ideal Diodes in DFN-10                       | Dual Internal P-Channel, 2.5V to 5.5V, DFN-10 Package                                                  |  |

| LTC4414           | 36V Low Loss PowerPath Controller for Large<br>P-Channel MOSFETs      | P-Channel, 3V to 36V, 30 $\mu A$ I_Q, MSOP-8 Package                                                   |  |

| LTC4415           | Dual 4A Ideal Diodes with Adjustable Current Limit                    | Dual P-Channel 50m $\Omega$ Ideal Diodes, 1.7V to 5.5V, 15mV Forward Drop, MSOP-16 and DFN-16 Packages |  |

| LTC4416/LTC4416-1 | 36V Low Loss Dual PowerPath Controller for Large<br>P-Channel MOSFETs | Dual P-Channel, 3.6V to 36V, 70 $\mu A I_Q$ , MSOP-10 Package                                          |  |

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Power Management Specialised - PMIC category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below :

FAN7710VNSLG7NT4081VTRSLG7NT4192VTRAS3729B-BWLMMB39C831QN-G-EFE2LV56841PVD-XHL9781TRP91E0-I5NHGIS6AE102A0DGN1B200L9916AP4306BUKTR-G1SLG7NT4198VNCP392CSFCCT1GLPTM21L-1ABG100IISL69234IRAZ-TISL69259IRAZISL69228IRAZISL69269IRAZTPS53679RSBRAXP813FAN53870UC00XFDMF5085HPM10-W29A100GNCV97311MW50R2GWL2868C-20/TRTLE9263-3BQXTLE9263QXTEA2095T/1JTEA2017AAT/2YTPS650940A0RSKRLP2998MAXTPS65177ARHARLTC4359HMS8#TRPBFLTC4417IUF#TRPBFLTC4357MPMS8#TRPBFAXP717SQ24806AQSCRK805-2RK809-2MFS2633AMBA0ADMFS2613AMDA3ADMP5496GR-0001-ZMP5515GU-ZLTC4357HMS8#TRPBFLTC4353CMS#TRPBFAD5522JSVUZ-RLLTC4352CMS#TRPBFLTC4417CUF#TRPBFLTC4359HDCB#TRPBFLTC4359CMS8#TRPBFAD5522JSVUZ-RLLTC4352CMS#TRPBFLTC4417CUF#TRPBFLTC4359HDCB#TRPBF