# **Matched Monolithic Quad Transistor**

#### **FEATURES**

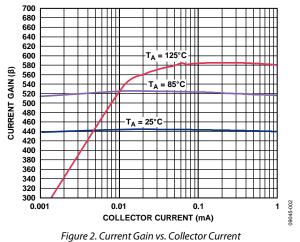

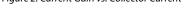

Low offset voltage: 400 µV maximum High current gain: 300 minimum Excellent current gain match: 4% maximum Low voltage noise density at 100 Hz, 1 mA 3 nV/√Hz maximum Excellent log conformance

Bulk resistance ( $r_{\text{BE}}$ ) = 0.6  $\Omega$  maximum Guaranteed matching for all transistors

#### APPLICATIONS

Low noise op amp front end Current mirror and current sink/source Low noise instrumentation amplifiers Voltage controlled attenuators Log amplifiers

#### **GENERAL DESCRIPTION**

The MAT14 is a quad monolithic NPN transistor that offers excellent parametric matching for precision amplifier and nonlinear circuit applications. Performance characteristics of the MAT14 include high gain (300 minimum) over a wide range of collector current, low noise (3 nV/ $\sqrt{\text{Hz}}$  maximum at 100 Hz, I<sub>c</sub> = 1 mA), and excellent logarithmic conformance. The MAT14 also features a low offset voltage of 100  $\mu$ V typical and tight current gain matching to within 4%. Each transistor of the MAT14 is individually tested to data sheet specifications. For matching parameters (offset voltage, input offset current, and gain match), each of the dual transistor combinations are

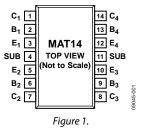

### **PIN CONFIGURATION**

**MAT14**

verified to meet stated limits. Device performance is guaranteed at an ambient temperature of 25°C and over the industrial temperature range.

The long-term stability of matching parameters is guaranteed by the protection diodes across the base emitter junction of each transistor. These diodes prevent degradation of beta and matching characteristics due to reverse bias, base emitter current. The superior logarithmic conformance and accurate matching characteristics of the MAT14 make it an excellent choice for use in log and antilog circuits. The MAT14 is an ideal choice in applications where low noise and high gain are required.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# TABLE OF CONTENTS

| Features                   | . 1 |

|----------------------------|-----|

| Applications               | . 1 |

| Pin Configuration          | . 1 |

| General Description        | . 1 |

| Revision History           | . 2 |

| Specifications             | . 3 |

| Electrical Characteristics | . 3 |

| Absolute Maximum Ratings   | . 4 |

| Thermal Resistance                  | 4 |

|-------------------------------------|---|

| ESD Caution                         |   |

| Typical Performance Characteristics | 5 |

| Theory of Operation                 | 8 |

| Applications Information            | 8 |

| Outline Dimensions                  | 9 |

| Ordering Guide                      | 9 |

### **REVISION HISTORY**

12/10—Rev. 0 to Rev. A

| Changes to General Description                    | 1 |

|---------------------------------------------------|---|

| Changes to Operating Temperature Range in Table 2 | 4 |

| Updated Outline Dimensions                        | 9 |

| Changes to Ordering Guide                         | 9 |

|                                                   |   |

10/10—Revision 0: Initial Version

# **SPECIFICATIONS**

### **ELECTRICAL CHARACTERISTICS**

$\rm T_{A}$  = 25°C, unless otherwise specified.

Table 1.

| Parameter                                        | Symbol                          | Test Conditions/Comments                                               | Min | Тур  | Max  | Unit       |

|--------------------------------------------------|---------------------------------|------------------------------------------------------------------------|-----|------|------|------------|

| DC AND AC CHARACTERISTICS                        |                                 |                                                                        |     |      |      |            |

| Current Gain                                     | h <sub>FE</sub>                 | $10 \ \mu A \le I_C \le 1 \ mA$                                        |     |      |      |            |

|                                                  |                                 | $0 V \le V_{CB} \le 30 V^1$                                            | 300 | 600  |      |            |

|                                                  |                                 | $-40^{\circ}C \le T_{A} \le +85^{\circ}C$                              | 200 | 500  |      |            |

| Current Gain Match                               | $\Delta h_{FE}$                 | $I_{c} = 100 \mu A^{2}$                                                |     | 1    | 4    | %          |

|                                                  |                                 | $0 \text{ V} \leq \text{V}_{CB} \leq 30 \text{ V}$                     |     |      |      |            |

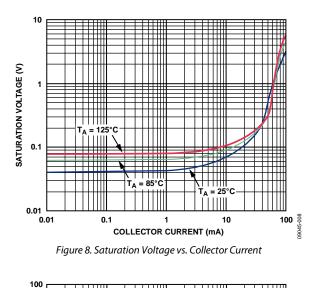

| Noise Voltage Density                            | e <sub>N</sub>                  | $I_{c} = 1 \text{ mA}, V_{cB} = 0^{3}$                                 |     |      |      |            |

|                                                  |                                 | $f_0 = 10 \text{ Hz}$                                                  |     | 2    | 4    | nV/√Hz     |

|                                                  |                                 | $f_0 = 100 \text{ Hz}$                                                 |     | 1.8  | 3    | nV/√Hz     |

|                                                  |                                 | $f_0 = 1 \text{ kHz}$                                                  |     | 1.8  | 3    | nV/√Hz     |

| Offset Voltage                                   | V <sub>os</sub>                 | $10 \ \mu A \le I_C \le 1 \ m A^4$                                     |     |      |      |            |

| 5                                                | 03                              | $0 \text{ V} \leq \text{V}_{CB} \leq 30 \text{ V}$                     |     | 100  | 400  | μV         |

|                                                  |                                 | $-40^{\circ}C \le T_{A} \le +85^{\circ}C$                              |     | 120  | 520  | μV         |

| Offset Voltage Change vs. V <sub>cs</sub> Change | $\Delta V_{OS} / \Delta V_{CB}$ | $0 V \le V_{CB} \le 30 V^4$                                            |     |      |      | P. 1       |

|                                                  |                                 | $10 \mu\text{A} \le I_c \le 1 \text{mA}$                               |     | 100  | 200  | μV         |

| Offset Voltage Change vs. I <sub>c</sub> Change  | $\Delta V_{os} / \Delta I_{c}$  | $10 \ \mu A \le I_C \le 1 \ m A^4$ , $V_{CB} = 0 \ V$                  |     | 10   | 50   | μV         |

| Offset Voltage Drift                             | $\Delta V_{OS} \Delta T$        | $-40^{\circ}C \le T_{A} \le +85^{\circ}C$                              |     | 10   | 50   | μ <b>ν</b> |

| onservolage blire                                |                                 | $I_{c} = 100 \ \mu A, V_{CB} = 0 V$                                    |     | 0.4  | 2    | μV/°C      |

| Breakdown Voltage                                | BV <sub>CEO</sub>               | $I_{c} = 100 \mu\text{A}$                                              | 40  | 0.4  | 2    | V V        |

| Diculture                                        | DVCEO                           | $-40^{\circ}C \le T_{A} \le +85^{\circ}C$                              | 40  |      |      | v          |

| Gain-Bandwidth Product                           | f <sub>T</sub>                  | $I_c = 1 \text{ mA}, V_{ce} = 10 \text{ V}$                            | -0  | 300  |      | MHz        |

| Collector Leakage Current                        | 'T                              | $r_{\rm C} = 1.000$                                                    |     | 500  |      |            |

| Base                                             |                                 | $V_{CB} = 40 \text{ V}$                                                |     | 5    |      | pА         |

| Dase                                             | I <sub>CBO</sub>                | $v_{CB} = 40 v$<br>-40°C $\leq T_{A} \leq +85°C$                       |     | 0.5  |      | nA         |

| Substrate                                        |                                 | $V_{cs} = 40 \text{ V}$                                                |     | 0.5  |      | nA         |

| Substrate                                        | I <sub>cs</sub>                 | $v_{cs} = 40 v$<br>-40°C ≤ T <sub>A</sub> ≤ +85°C                      |     | 0.5  |      |            |

| Emittor                                          |                                 |                                                                        |     |      |      | nA         |

| Emitter                                          | I <sub>CES</sub>                | $V_{CE} = 40 V$                                                        |     | 3    |      | nA         |

| land to Comment                                  |                                 | $-40^{\circ}C \le T_A \le +85^{\circ}C$                                |     | 5    |      | nA         |

| Input Current                                    |                                 |                                                                        |     | 165  | 220  |            |

| Bias                                             | I <sub>B</sub>                  | $I_{c} = 100 \ \mu\text{A}, 0 \ \text{V} \le V_{CB} \le 30 \ \text{V}$ |     | 165  | 330  | nA         |

| 011                                              |                                 | $-40^{\circ}C \le T_A \le +85^{\circ}C$                                |     | 200  | 500  | nA         |

| Offset                                           | I <sub>os</sub>                 | $I_{c} = 100 \ \mu A, V_{CB} = 0 \ V$                                  |     | 2    | 13   | nA         |

|                                                  |                                 | $-40^{\circ}C \le T_A \le +85^{\circ}C$                                |     | 8    | 40   | nA         |

| Offset Drift                                     | $\Delta I_{os}/\Delta T$        | $I_c = 100 \mu\text{A}$                                                |     |      |      |            |

|                                                  |                                 | $-40^{\circ}C \le T_A \le +85^{\circ}C$                                |     | 100  | _    | pA/°C      |

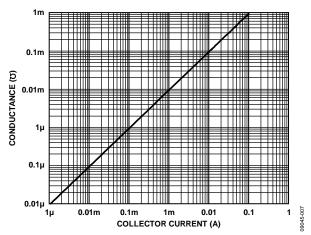

| Collector Saturation Voltage                     | V <sub>CE(SAT)</sub>            | $I_{c} = 1 \text{ mA}, I_{B} = 100 \mu\text{A}$                        |     | 0.03 | 0.06 | V          |

| Output Capacitance                               | C <sub>OBO</sub>                | $V_{CB} = 15 \text{ V}, I_{E}^{5} = 0, f = 1 \text{ MHz}$              |     | 10   |      | pF         |

| Bulk Resistance                                  | r <sub>BE</sub>                 | $10 \ \mu A \le I_C \le 10 \ mA, V_{CB} = 0 \ V^6$                     |     | 0.4  | 0.6  | Ω          |

| Input Capacitance                                | C <sub>EBO</sub>                | $V_{CB} = 15 \text{ V}, I_{E} = 0, f = 1 \text{ MHz}$                  |     | 40   |      | pF         |

<sup>1</sup> Current gain measured at I<sub>C</sub> = 10 μA, 100 μA, and 1 mA. <sup>2</sup> Current gain match (Δh<sub>FE</sub>) defined as:  $\Delta h_{FE} = (100(\Delta I_B)(h_{FE min})/I_C)$ . <sup>3</sup> Sample tested. <sup>4</sup> Measured at I<sub>C</sub> = 10 μA and guaranteed by design over the specified range of I<sub>C</sub>. <sup>5</sup> See Table 2 for the emitter current rating.

<sup>6</sup> Guaranteed by design.

### **ABSOLUTE MAXIMUM RATINGS**

### Table 2.

| Parameter                                          | Rating          |  |  |

|----------------------------------------------------|-----------------|--|--|

| Voltage                                            |                 |  |  |

| Collector-to-Base Voltage (BV <sub>CBO</sub> )     | 40 V            |  |  |

| Collector-to-Emitter Voltage (BV <sub>CEO</sub> )  | 40 V            |  |  |

| Collector-to-Collector Voltage (BV <sub>cc</sub> ) | 40 V            |  |  |

| Emitter-to-Emitter Voltage (BV <sub>EE</sub> )     | 40 V            |  |  |

| Current                                            |                 |  |  |

| Collector Current (I <sub>c</sub> )                | 30 mA           |  |  |

| Emitter Current (I <sub>E</sub> )                  | 30 mA           |  |  |

| Temperature                                        |                 |  |  |

| Storage Temperature Range                          | -65°C to +150°C |  |  |

| Operating Temperature Range                        | -40°C to +85°C  |  |  |

| Junction Temperature Range                         | -65°C to +150°C |  |  |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

### Table 3. Thermal Resistance

| Package Type | θ <sub>JA</sub> | θ <sub>JC</sub> | Unit |

|--------------|-----------------|-----------------|------|

| 14-Lead SOIC | 115             | 36              | °C/W |

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

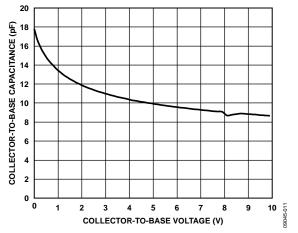

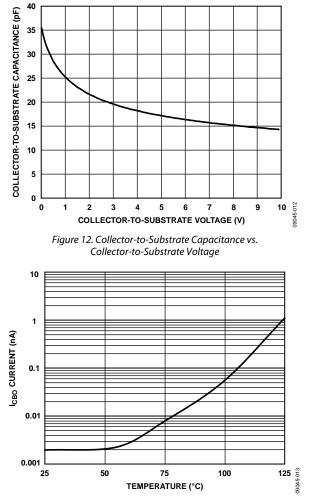

### **TYPICAL PERFORMANCE CHARACTERISTICS**

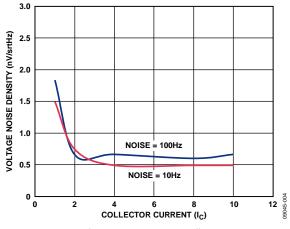

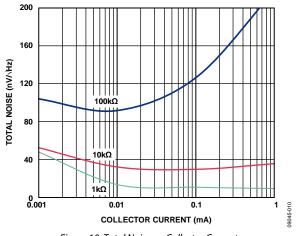

Figure 4. Voltage Noise Density vs. Collector Current

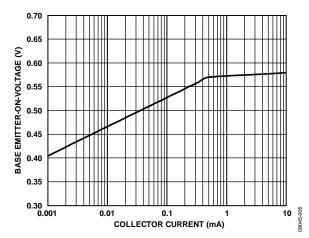

Figure 5. Base Emitter-On-Voltage vs. Collector Current

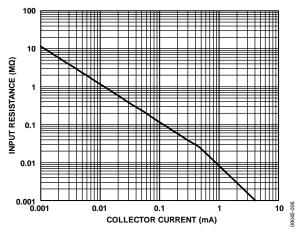

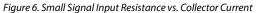

*Figure 7. Small Signal Output Conductance vs. Collector Current*

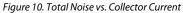

Figure 11. Collector-to-Base Capacitance vs. Collector-to-Base Voltage

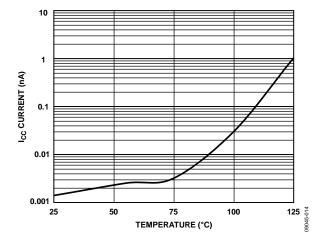

Figure 13. Collector-to-Base Leakage vs. Temperature

Figure 14. Collector-to-Collector Leakage vs. Temperature

# THEORY OF OPERATION APPLICATIONS INFORMATION

To minimize coupling between devices, tie one of the substrate pins (Pin 4 or Pin 11) to the most negative circuit potential. Note that Pin 4 and Pin 11 are internally connected.

### **Applications Current Sources**

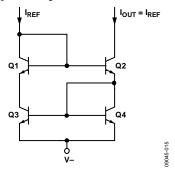

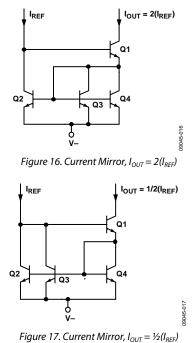

MAT14 can be used to implement a variety of high impedance current mirrors as shown in Figure 15, Figure 16, and Figure 17. These current mirrors can be used as biasing elements and load devices for amplifier stages.

Figure 15. Unity-Gain Current Mirror,  $I_{OUT} = I_{REF}$

The unity-gain current mirror shown in Figure 15 has an accuracy of better than 1% and an output impedance of more than 100 M $\Omega$  at 100  $\mu A.$

Figure 16 and Figure 17 each show a modified current mirror; Figure 16 is designed for a current gain of two (2), and Figure 17 is designed for a current gain of one-half (½). The accuracy of these mirrors is reduced from that of the unity-gain source due to base current errors but remains better than 2%.

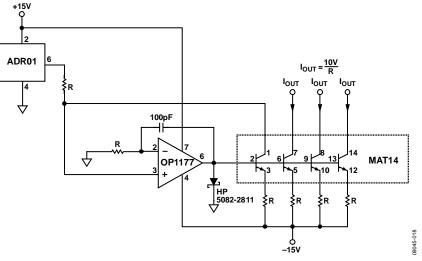

Figure 18 is a temperature independent current sink that has an accuracy of better than 1% at an output current of 100  $\mu$ A to 1 mA. A Schottky diode acts as a clamp to ensure correct circuit startup at power-on. Use 1% metal film type resistors in this circuit.

Figure 18. Temperature Independent Current Sink,  $I_{OUT} = 10 V/R$

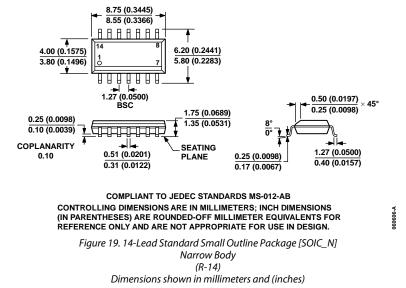

### **OUTLINE DIMENSIONS**

### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                             | Package Option |

|--------------------|-------------------|-------------------------------------------------|----------------|

| MAT14ARZ           | -40°C to +85°C    | 14-Lead Standard Small Outline Package [SOIC_N] | R-14           |

| MAT14ARZ-R7        | -40°C to +85°C    | 14-Lead Standard Small Outline Package [SOIC_N] | R-14           |

| MAT14ARZ-RL        | -40°C to +85°C    | 14-Lead Standard Small Outline Package [SOIC_N] | R-14           |

<sup>1</sup> Z = RoHS Compliant Part.

# NOTES

### NOTES

# NOTES

©2010 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D09045-0-12/10(A)

www.analog.com

Rev. A | Page 12 of 12

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Bipolar Transistors - BJT category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below :

619691C MCH4017-TL-H BC546/116 BC557/116 BSW67A NTE158 NTE187A NTE195A NTE2302 NTE2330 NTE63 C4460 2SA1419T-TD-H 2SA1721-O(TE85L,F) 2SA2126-E 2SB1204S-TL-E 2SD2150T100R SP000011176 FMMTA92QTA 2N2369ADCSM 2N5769 2SC2412KT146S 2SC5490A-TL-H 2SD1816S-TL-E 2SD1816T-TL-E CMXT2207 TR CPH6501-TL-E MCH4021-TL-E US6T6TR NJL0281DG 732314D CMXT3906 TR CPH3121-TL-E CPH6021-TL-H 873787E IMZ2AT108 UMX21NTR MCH6102-TL-E NJL0302DG 2N3583 2SA1434-TB-E 2SC3143-4-TB-E 2SD1621S-TD-E NTE103 30A02MH-TL-E NSV40301MZ4T1G NTE101 NTE13 NTE15 NTE16001