# VR13.HC and AI Cores Dual-Output Voltage Regulator Chipset

### **General Description**

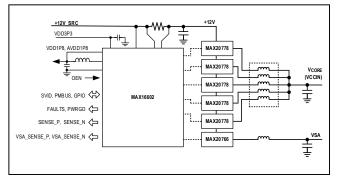

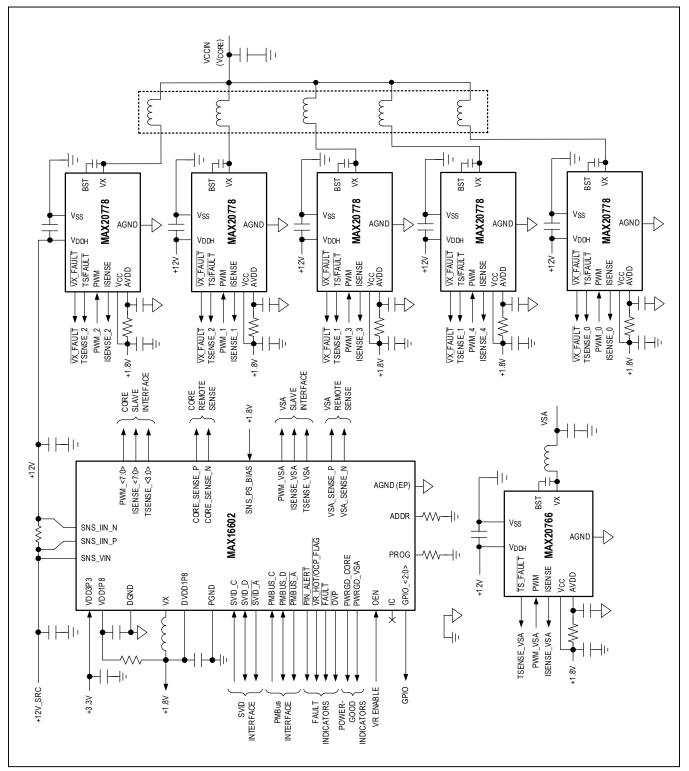

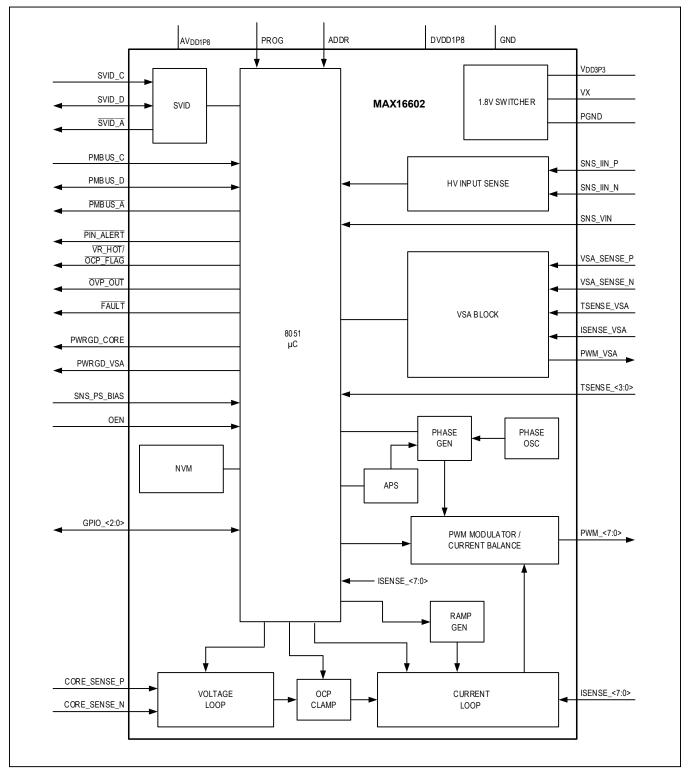

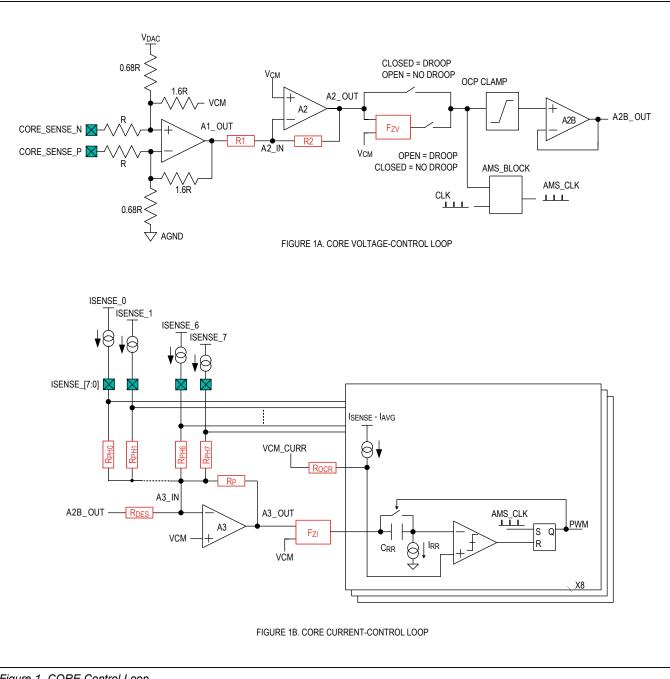

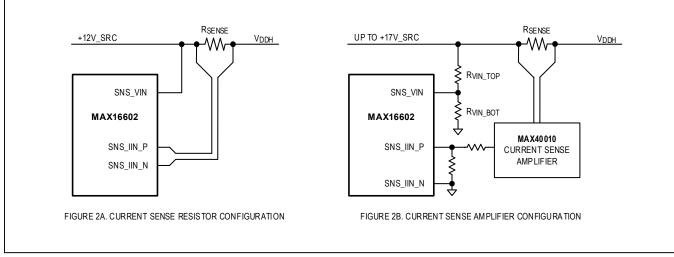

The MAX16602 IC provides a high-density, flexible and scalable solution to power AI cores or Intel<sup>®</sup> VR13.HC server CPUs. This Maxim controller IC employs coupled inductors and smart power-stage ICs to implement high-efficiency core regulators with enhanced transient response and low-quiescent current. An additional single-phase output generates the VSA rail in the system using a single-phase smart power stage. The complete circuit is a highly efficient (8+1) multiphase synchronous buck converter with extensive status and parameter-measurement features. The controller also supports PWM paralleling to control up to 16 phases. A single, scalable PCB design with appropriate smart power-stage IC selection can be used to produce regulators with a wide range of current ratings.

The IC's architecture simplifies design, reduces component count, enables advanced power management and telemetry, and increases energy savings over the full load range. Autonomous phase-shedding is implemented to maintain high efficiency across the entire load range.

Regulator parameters for protection and shutdown can be set and monitored through the serial interface using the PMBus<sup>™</sup> protocol. Power-stage faults, input and output voltage, input and output current, input power, and the temperature of each smart power-stage IC are readable over the serial interface. The critical fault retention feature prevents exothermic events after a power-device fault. The smart power-stage ICs communicate with the controller IC through analog and digital signals that are also readable through the registers in the controller IC. Preset and user configurations are programmed in nonvolatile memory (NVM). MTP-programmable NVM circuits allow for seven field modifications.

An integrated 3.3V to 1.8V regulator supports both MAX16602 and power-stage ICs with 1.8V bias supplies. SNS\_PS\_BIAS monitoring also allows for flexible bias and sequencing.

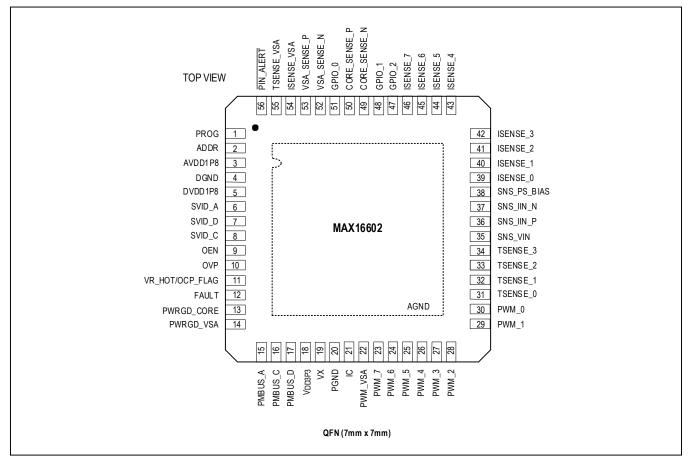

The MAX16602 is available in a 56-pin, 7mm x 7mm QFN package.

#### Ordering Information appears at end of data sheet.

Intel is a registered trademark of Intel Corporation. PMBus is a trademark of SMIF, Inc.

### **Benefits and Features**

- High Power Density and Efficiency

- Smart Power-Stage Support: MAX20778/A, MAX20779/A/B/C, MAX20780, MAX20790, MAX16604

- Top-Tier Efficiency (95.6% Peak Efficiency at 1.8V<sub>OUT</sub>)

- · Integrated Input Power Monitor

- Telemetry Through PMBus

- Digitally Programmable Configuration

- · Input Voltage, Current, and Power Monitoring

- Power-Stage Temperature Monitoring and Reporting

- Advanced Power Management

- Autonomous Phase-Shedding

- Orthogonal Current Rebalance for Phase-Current Balance During Transients

- Low-Quiescent Current—Improves Light-Load and Standby Efficiency

- Protection Features

- Input and Bias Supply Undervoltage Protection

- Overcurrent Protection

- Critical Fault-Flag Output Pin

### **Applications**

- High-Current Multiphase Voltage Regulators

- AI Cores and XPUs

- VR13.HC CPUs and Memory

- Graphics Processors

- Networking ASICs

- Servers and Workstations

- Enterprise Storage

- Communications and Networking Equipment Supply

## **Typical Operating Circuit**

# VR13.HC and AI Cores Dual-Output Voltage Regulator Chipset

### **Absolute Maximum Ratings**

| AV <sub>DD1P8</sub> to AGND   | 0.3V to +2.4V                      |

|-------------------------------|------------------------------------|

| DVDD1P8 to DGND               |                                    |

| V <sub>DD3P3</sub> to DGND    | 0.3V to +4V                        |

| SNS_PS_BIAS to DGND           | 0.3V to V <sub>DD3P3</sub> + 0.3V  |

| CORE_SENSE_P to AGND          | 0.3V to AV <sub>DD1P8</sub> + 0.3V |

| PMBUS_A, PMBUS_D,             |                                    |

| PMBUS_C to DGND               | 0.3V to V <sub>DD3P3</sub> + 0.3V  |

| SVID_A, SVID_D to DGND        | 0.3V to AV <sub>DD1P8</sub> + 0.3V |

| SVID_C to DGND                | 0.3V to + 2.4V                     |

| GPIO_0, GPIO_1,               |                                    |

| GPIO_2 to DGND (Note 1)       | 0.3V to V <sub>DD3P3</sub> + 0.3V  |

| IC to DGND                    | 0.3V to +7.5V                      |

| OEN, OVP, VR_HOT, FAULT to DO | GND0.3V to +4V                     |

| PWRGD_CORE, VSA_PWRGD to D    | GND                                |

|                               | 0.3V to V <sub>DD3P3</sub> + 0.3V  |

| PIN_ALERT to DGND             | 0.3V to V <sub>DD3P3</sub> + 0.3V  |

| CORE_SENSE_N to AGND          | 0.3V to AV <sub>DD1P8</sub> + 0.3V |

|                               |                                    |

#### VSA SENSE P, VSA SENSE N to AGND

| ADDR, PROG to AGND                                                                                                                                                                                                                                               | -0.3V to AV <sub>DD1P8</sub> + 0.3V                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| TSENSE_VSA to DGND0.3V to V <sub>DVDD1P8</sub> + 0.3V         ISENSE_<7:0>, ISENSE_VSA         to AGND                                                                                                                                                           |                                                            |

| ISENSE_<7:0>, ISENSE_VSA<br>to AGND                                                                                                                                                                                                                              | PWM_<7:0>, PWM_VSA, TSENSE_<3:0>,                          |

| to AGND0.3V to AV <sub>DD1P8</sub> + 0.3V<br>VX to PGND0.3V to V <sub>DD3P3</sub> + 0.3V<br>V <sub>IN</sub> , SNS_IN_P, SNS_IN_N to AGND0.3V to +13.7V<br>AGND to DGND0.3V to +0.3V<br>PGND to DGND0.3V to +0.3V<br>Junction Temperature (T <sub>J</sub> )+150°C | TSENSE_VSA to DGND0.3V to V <sub>DVDD1P8</sub> + 0.3V      |

| VX to PGND0.3V to V <sub>DD3P3</sub> + 0.3V<br>V <sub>IN</sub> , SNS_IN_P, SNS_IN_N to AGND0.3V to +13.7V<br>AGND to DGND0.3V to +0.3V<br>PGND to DGND0.3V to +0.3V<br>Junction Temperature (T <sub>J</sub> )+150°C                                              | ISENSE_<7:0>, ISENSE_VSA                                   |

| V <sub>IN</sub> , SNS_IN_P, SNS_IN_N to AGND0.3V to +13.7V<br>AGND to DGND0.3V to +0.3V<br>PGND to DGND0.3V to +0.3V<br>Junction Temperature (T <sub>J</sub> )+150°C                                                                                             | to AGND0.3V to AV <sub>DD1P8</sub> + 0.3V                  |

| AGND to DGND0.3V to +0.3V<br>PGND to DGND0.3V to +0.3V<br>Junction Temperature (T <sub>J</sub> )+150°C                                                                                                                                                           | VX to PGND0.3V to V <sub>DD3P3</sub> + 0.3V                |

| PGND to DGND0.3V to +0.3V<br>Junction Temperature (T <sub>J</sub> )+150°C                                                                                                                                                                                        | V <sub>IN</sub> , SNS_IN_P, SNS_IN_N to AGND0.3V to +13.7V |

| Junction Temperature (T <sub>J</sub> )+150°C                                                                                                                                                                                                                     | AGND to DGND0.3V to +0.3V                                  |

| Junction Temperature (T <sub>J</sub> )+150°C<br>Storage Temperature Range65°C to +150°C                                                                                                                                                                          | PGND to DGND0.3V to +0.3V                                  |

| Storage Temperature Range65°C to +150°C                                                                                                                                                                                                                          | Junction Temperature (T <sub>J</sub> )+150°C               |

|                                                                                                                                                                                                                                                                  | Storage Temperature Range65°C to +150°C                    |

| Peak Reflow Temperature Lead-Free+260°C                                                                                                                                                                                                                          | Peak Reflow Temperature Lead-Free+260°C                    |

**Note 1:** Not higher than +2.4V if used for analog input functions.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

| 56 QFN                                |                  |  |  |  |  |

|---------------------------------------|------------------|--|--|--|--|

| Package Code                          | G5677+2          |  |  |  |  |

| Outline Number                        | <u>21-100073</u> |  |  |  |  |

| Land Pattern Number                   | 90-0455          |  |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD  |                  |  |  |  |  |

| Junction to Ambient ( $\theta_{JA}$ ) | 29.5°C/W         |  |  |  |  |

| Junction to Case (θ <sub>JC</sub> )   | 2.6°C/W          |  |  |  |  |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

# VR13.HC and AI Cores Dual-Output Voltage Regulator Chipset

### **Electrical Characteristics**

| PARAMETER                                 | SYMBOL                                         | CONDITIONS            |                                                                                                 | MIN                          | TYP    | MAX | UNITS |    |

|-------------------------------------------|------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------|------------------------------|--------|-----|-------|----|

| SUPPLY VOLTAGES AND                       | SUPPLY CURRE                                   | NT                    |                                                                                                 |                              |        |     |       | 1  |

| Bias Supply Voltage<br>Range              | V <sub>AVDD1P8</sub> ,<br>V <sub>DVDD1P8</sub> |                       |                                                                                                 |                              | 1.7    |     | 1.9   | V  |

| Trange                                    | V <sub>DD3P3</sub>                             |                       |                                                                                                 |                              | 3.0    |     | 3.6   | V  |

| 1.8V Bias Supply Current                  | I <sub>AVDD1P8</sub> +<br>I <sub>DVDD1P8</sub> | System ope            | erational                                                                                       |                              |        |     | 52    | mA |

| V <sub>DD3P3</sub> Bias Supply<br>Current | I <sub>VDD3P3</sub>                            | 1.8V switch           | er off (VX = 3.3∖                                                                               | <i>(</i> )                   |        |     | 500   | μA |

| OUTPUT-VOLTAGE RANG                       | E AND ACCURA                                   | CY                    |                                                                                                 |                              |        |     |       |    |

| Output-Voltage Range                      |                                                | 5mV mode              |                                                                                                 | CORE and VSA                 | 0.25   |     | 1.52  | V  |

| Output-voltage Mange                      |                                                | 10mV mode             | 9                                                                                               | CORE only                    | 0.5    |     | 2.3   | V  |

|                                           |                                                |                       |                                                                                                 | 1.0V to 1.52V                | -0.5   |     | +0.5  | %  |

|                                           | V <sub>OUT_VSA</sub>                           | $T_A = 0^{\circ}C$ to | +85°C                                                                                           | 0.8V to 0.995V               | -5     |     | +5    | mV |

|                                           |                                                |                       |                                                                                                 | 0.25V to 0.795V              | -8     |     | +8    | mV |

| DC Cat Daint Talaranaa                    | Vout_core                                      |                       | 1.5V to 2                                                                                       |                              | -0.5   |     | +0.5  | %  |

| DC Set-Point Tolerance                    |                                                |                       |                                                                                                 |                              | -0.52  |     | +0.52 | %  |

|                                           |                                                | 0.5V to 0.6           |                                                                                                 | 0.7V to 0.995V               | -5     |     | +5    | mV |

|                                           |                                                |                       |                                                                                                 | 0.5V to 0.695V               | -8     |     | +8    | mV |

|                                           |                                                |                       |                                                                                                 | 0.25V to 0.495V              | -9     |     | +9    | mV |

|                                           | R <sub>LOADLINE</sub><br>Range 1               | Range                 | 0xD8[5] = 0, 0xD8[1] = 1,           0xD3[7] = 0,           R <sub>DES</sub> = 92Ω, LSB = 7.48μΩ |                              | 0.516  |     | 0.98  | mΩ |

|                                           | -                                              | Accuracy              | $T_A = 0^\circ C$ to +                                                                          | 85°C                         | -2.3   |     | +2.3  | %  |

|                                           | R <sub>LOADLINE</sub><br>Range 2               | Range                 | 0xD8[5] = 0, 0<br>0xD3[7] = 0,                                                                  |                              | 0.397  |     | 0.753 | mΩ |

|                                           |                                                | Accuracy              | $T_A = 0^{\circ}C$ to +                                                                         | $T_A = 0^{\circ}C$ to +85°C  |        |     | +2.3  | %  |

| DC Load Line                              | ne RLOADLINE<br>Range 3                        | Range                 | 0xD8[5] = 0, 0xD8[1] = 0,<br>0xD3[7] = 1,<br>$R_{DES} = 73.25\Omega, LSB = 4.58\mu\Omega$       |                              | 0.316  |     | 0.600 | mΩ |

|                                           |                                                | Accuracy              | $T_A = 0^{\circ}C$ to +                                                                         | 85°C                         | -2.3   |     | +2.3  | %  |

|                                           | R <sub>LOADLINE</sub><br>Range 4               | Range                 | 0xD8[5] = 1, 0<br>0xD3[7] = 0,<br>R <sub>DES</sub> = 92Ω,                                       | )xD8[1] = 1,<br>LSB = 2.44μΩ | 0.1735 |     | 0.325 | mΩ |

|                                           |                                                | Accuracy              | $T_A = 0^{\circ}C$ to +                                                                         | 85°C                         | -3     |     | +3    | %  |

| -                                         |                                                | Range                 | 0xD8[5] = 1, 0xD8[1] = 0,                                                                       |                              | 0.108  |     | 0.197 | mΩ |

|                                           |                                                | Accuracy              | $T_A = 0^{\circ}C$ to +                                                                         | 85°C                         | -5     |     | +5    | %  |

# VR13.HC and AI Cores Dual-Output Voltage Regulator Chipset

### **Electrical Characteristics (continued)**

| PARAMETER                                        | SYMBOL                         | CONDITIONS                                                                                                                                             | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| CORE_SENSE_P,<br>VSA_SENSE_P Leakage<br>Current  | ICORE_SENSE_P,<br>IVSA_SENSE_P | CORE_SENSE_P = 2.3V, CORE_SENSE_N = 0V,<br>VSA_SENSE_P = 1.52V, VSA_SENSE_N = 0V,<br>OEN = 0                                                           |      |      | 90   | μA    |

| VID TRANSITION SLEW F                            | RATE                           | · · · · · · · · · · · · · · · · · · ·                                                                                                                  |      |      |      |       |

| CORE Slew-Rate                                   | CORE_SR                        | Slow, including soft-start<br>(CORE_SR <sub>SLW</sub> = CORE_SR <sub>FST</sub> /4)                                                                     | -5   |      | +5   | %     |

| Accuracy                                         | (Note 2)                       | Fast (CORE_SR <sub>FST</sub> = 27mV/µs)                                                                                                                | -5   |      | +5   | %     |

| VSA Slew-Rate Accuracy                           | VSA_SR<br>(Note 2)             | Slow, including soft-start<br>(VSA_SR <sub>SLW</sub> = VSA_SR <sub>FST</sub> /4)                                                                       | -5   |      | +5   | %     |

|                                                  | (Note 2)                       | Fast (VSA_SR <sub>FST</sub> = 10.7mV/µs)                                                                                                               | -5   |      | +5   | %     |

| SWITCHING FREQUENCY                              | Y                              |                                                                                                                                                        |      |      |      |       |

| CORE Switching                                   | <sup>f</sup> sw_core           | CORE switching-frequency range,<br>0.1667µs switching period step                                                                                      | 300  |      | 857  | kHz   |

| Frequency                                        |                                | CORE switching-frequency accuracy                                                                                                                      | -10  |      | +10  | %     |

|                                                  | fsw_vsa                        | Low-switching frequency                                                                                                                                | 599  | 667  | 735  | kHz   |

| VSA Switching Frequency                          |                                | High-switching frequency                                                                                                                               | 720  | 800  | 880  | kHz   |

| SUPPLY UVLO                                      |                                |                                                                                                                                                        |      |      |      |       |

| V <sub>DD1P8</sub> UVLO                          | V <sub>DD1P8_UVLO</sub>        | V <sub>DD1P8</sub> rising, 50mV (typ) hysteresis                                                                                                       | 1.62 | 1.64 | 1.66 | V     |

| V <sub>DD3P3</sub> UVLO                          | V <sub>DD3P3_UVLO</sub>        | V <sub>DD3P3</sub> rising, 50mV (typ) hysteresis                                                                                                       | 2.87 | 2.91 | 2.95 | V     |

|                                                  |                                | V <sub>IN</sub> rising, 1V (typ) hysteresis, 0xD9[5] = 0,<br>0xD9[3:0] = 0                                                                             | 9.6  | 10.1 | 10.5 | V     |

| 12V Input UVLO                                   | V <sub>IN_UVLO</sub>           | $V_{IN}$ rising, 1V (typ) hysteresis<br>0xD9[5] = 1, 0xD9[3:0] = 0<br>$V_{IN}$ divider RV <sub>IN_TOP</sub> = 4.75kΩ,<br>RV <sub>IN_BOT</sub> = 19.6kΩ | 9.7  | 10.2 | 10.6 | V     |

| SNS_PS_BIAS<br>Undervoltage                      | V <sub>PS_BIAS_UV</sub>        | Power-stage supply undervoltage threshold rising; 60mV (typ) hysteresis                                                                                | 1.52 | 1.55 | 1.58 | V     |

| VIN_UVLO Delay to<br>Shutdown                    | td <sub>VIN_UVLO</sub>         |                                                                                                                                                        |      | 5    |      | μs    |

| SNS_PS_BIAS<br>Undervoltage Delay to<br>Shutdown | td <sub>SNS_PS_BIAS</sub>      |                                                                                                                                                        |      | 5    |      | μs    |

# VR13.HC and AI Cores Dual-Output Voltage Regulator Chipset

### **Electrical Characteristics (continued)**

| PARAMETER                                   | SYMBOL                              | CONDITION                                                                                                                                             | S                       | MIN   | TYP    | MAX    | UNITS |

|---------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------|--------|--------|-------|

| OUTPUT OVERVOLTAGE                          | AND UNDERVOL                        | AGE PROTECTION                                                                                                                                        |                         |       |        |        | ,     |

| 0                                           |                                     |                                                                                                                                                       | 5mV mode                | 180   | 200    | 220    | mV    |

| Output Overvoltage-<br>Protection Threshold | Vovp_core,<br>V <sub>OVP_</sub> vsa | Referred to VID setting,<br>10mV (typ) hysteresis                                                                                                     | 10mV mode,<br>CORE only | 230   | 250    | 270    | mV    |

| Fixed Umbrella                              |                                     | Referred to CORE_                                                                                                                                     | 5mV mode                | 2.41  | 2.50   | 2.59   | V     |

| Overvoltage-Protection<br>Threshold         | VUM_OVP_CORE,<br>VUM_OVP_VSA        | SENSE_P, VSA_SENSE_P,<br>7mV (typ) hysteresis                                                                                                         | 10mV mode,<br>CORE only | 2.41  | 2.50   | 2.59   | V     |

| Overvoltage to OVP Delay                    | <sup>t</sup> OV_DELAY               | Delay from $V_{OUT} > V_{TH}$ to $\overline{C}$                                                                                                       | <b>VP</b> asserted      |       | 700    |        | ns    |

| OVERCURRENT PROTEC                          | TION                                | ·                                                                                                                                                     |                         |       |        |        |       |

| OCP Timeout and Hiccup<br>Mode On-Time      | tOCP                                |                                                                                                                                                       |                         |       | 5      |        | ms    |

| Hiccup Mode Off-Time                        | <sup>t</sup> HICCUP_OFF             |                                                                                                                                                       |                         |       | 45     |        | ms    |

| CORE Positive OCP<br>Current-Limit Range    |                                     | 0xD8[0] = 0, LSB = 2.76A<br>ocp_code (0xD3[3:0]) from 0                                                                                               | to 11                   | 27.58 |        | 57.94  | A     |

| per Phase                                   | IPOCP_CORE_PH                       | 0xD8[0] = 1, LSB = 5.52A<br>ocp_code (0xD3[3:0]) from 0                                                                                               | to 11                   | 55.16 |        | 115.18 | A     |

| CORE Positive OCP<br>System Current-Limit   |                                     | 0xD8[0] = 0,<br>I <sub>POCP_C</sub> = (27.58A + 2.76A x ocp_code) x n_ph<br>7 and 8 phase systems with ocp_code > 5 will<br>be clamped at n_ph = 6    |                         | 27.58 |        | 347.64 | A     |

| Range                                       | IPOCP_CORE                          | 0xD8[0] = 1,<br>$I_{POCP_C} = (55.16A + 5.52A \times ocp_code) \times n_ph$<br>7 and 8 phase systems with ocp_code > 5<br>will be clamped at n_ph = 6 |                         | 55.16 |        | 695.28 | A     |

|                                             |                                     | Range 27.58A to 38.62A                                                                                                                                |                         | -25   |        | +25    |       |

|                                             |                                     | Range 41.38A to 46.90A                                                                                                                                |                         | -20   |        | +20    |       |

|                                             |                                     | Range 49.66A to 52.42A                                                                                                                                |                         | -17   |        | +17    |       |

|                                             |                                     | Range 55.18A to 60.68A                                                                                                                                |                         | -15   |        | +15    |       |

| CORE Positive OCP<br>Accuracy               |                                     | Range 66.20A to 82.76A                                                                                                                                |                         | -12.5 |        | +12.5  | %     |

| , local acy                                 |                                     | Range 88.28A to 107.58A                                                                                                                               |                         | -10   |        | +10    |       |

|                                             |                                     | Range 110.36A to 151.7A                                                                                                                               |                         | -8    |        | +8     |       |

|                                             |                                     | Range 154.48A to 187.60A                                                                                                                              |                         | -6    |        | +6     |       |

|                                             |                                     | Range 193.10A to 695.28A                                                                                                                              |                         | -5    |        | +5     |       |

| CORE Negative OCP<br>Current-Limit Ratio to |                                     | 0xD3[4] = 0, wrt POCP 0xD8[0] = 1                                                                                                                     |                         |       | -33    |        | %     |

| CORE Positive OCP<br>Current Limit          |                                     | 0xD3[4] = 1, wrt POCP 0xD8                                                                                                                            | 5[0] = 1                |       | -16.66 |        | /0    |

# VR13.HC and AI Cores Dual-Output Voltage Regulator Chipset

### **Electrical Characteristics (continued)**

| PARAMETER                                                                 | SYMBOL                    | CO                                                                                        | NDITIONS                 | MIN   | TYP  | MAX   | UNITS |

|---------------------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------|--------------------------|-------|------|-------|-------|

|                                                                           |                           | Range -9.18A to -11                                                                       | .94A                     | -35   |      | +35   |       |

|                                                                           |                           | Range -12.86A to -1                                                                       | 6.54A                    | -30   |      | +30   |       |

|                                                                           |                           | Range -17.46A to -2                                                                       | 0.21A                    | -22   |      | +22   |       |

| CORE Negative OCP<br>Accuracy                                             |                           | Range -22.04A to -2                                                                       | 5.72A                    | -20   |      | +20   | %     |

| ricearacy                                                                 |                           | Range -27.56A to -3                                                                       | 1.24A                    | -15   |      | +15   |       |

|                                                                           |                           | Range -33.07A to -4                                                                       | 7.77A                    | -12.5 |      | +12.5 |       |

|                                                                           |                           | Range -51.44A to -2                                                                       | 31.53A                   | -10   |      | +10   |       |

| VSA Positive OCP<br>Current-Limit Range                                   | IPOCP_VSA                 | Four typical selectio                                                                     | ns: 23.5A, 28A, 35A, 40A | 23.5  |      | 40    | А     |

| VSA Negative OCP<br>Current Limit to<br>VSA Positive OCP<br>Current Limit | I <sub>NOCP_VSA</sub>     | (Note 3)                                                                                  |                          |       | -100 |       | %     |

| VSA OCP Current-Limit<br>Accuracy                                         |                           | POCP and NOCP                                                                             |                          | -20   |      | +20   | %     |

| APS THRESHOLD                                                             |                           |                                                                                           |                          |       |      |       |       |

| Fast Threshold Accuracy                                                   |                           | APS threshold range                                                                       | e: 8A to 70A             | -12.5 |      | +12.5 | %     |

| POWER GOOD (CORE ar                                                       | nd VSA)                   |                                                                                           |                          |       |      |       |       |

|                                                                           |                           | Referred to<br>VID, 9mV (typ)                                                             | 5mV mode (CORE)          | -240  | -218 | -196  | mV    |

| Power-Good Threshold,                                                     | V <sub>PWRGD_CORE</sub> , |                                                                                           | 5mV mode (VSA)           | -257  | -234 | -211  | mV    |

| Deasserting                                                               | VPWRGD_VSA                |                                                                                           | 10mV mode,<br>CORE only  | -330  | -296 | -270  | mV    |

| FAULT DETECTION                                                           |                           | 1                                                                                         |                          |       |      |       |       |

| Power-Stage<br>Fault-Detector Threshold                                   | V <sub>TS_TH</sub>        | TSENSE_ pin to GN                                                                         | ID                       |       | 300  |       | mV    |

| Power-Stage Fault-<br>Detector Propagation<br>Delay                       | <sup>t</sup> TS/FAULT     | Delay from TSENSE                                                                         | E to FAULT               |       | 2    |       | μs    |

|                                                                           | VP, FAULT, PWRG           | D_CORE, PWRGD_\                                                                           | /SA)                     |       |      |       |       |

|                                                                           |                           | Logic-high voltage, I                                                                     | $I_{OAD} = 2mA$          | 1.5   |      |       | V     |

| PWM_ Output                                                               | V <sub>PWM</sub> _        | Logic-low voltage, I <sub>LOAD</sub> = 2mA                                                |                          |       |      | 0.13  | V     |

| Output-Low Voltage                                                        | V <sub>OL</sub>           | $\overline{OVP}$ , FAULT, PWRGD_CORE, PWRGD_VSA,<br>I <sub>LOAD</sub> = 4mA               |                          |       |      | 0.4   | V     |

| Output-High Leakage<br>Current                                            | lικ                       | OVP, FAULT, PWRGD_CORE, PWRGD_VSA;         conditions = output in Hi-Z; pulled up to 3.6V |                          |       |      | 1     | μA    |

# VR13.HC and AI Cores Dual-Output Voltage Regulator Chipset

### **Electrical Characteristics (continued)**

| PARAMETER                            | SYMBOL                | CONDITIONS                                                       | MIN | TYP  | MAX  | UNITS |

|--------------------------------------|-----------------------|------------------------------------------------------------------|-----|------|------|-------|

| OUTPUT ENABLE (OEN)                  |                       |                                                                  |     |      |      |       |

| OEN Thresholds                       | V <sub>IH</sub>       | Input logic-high                                                 | 0.9 |      |      | V     |

| OEN Thresholds                       | VIL                   | Input logic-low                                                  |     |      | 0.6  | V     |

|                                      |                       | Valid enable-signal pulse width                                  |     | 0.2  |      | μs    |

| OEN Filter                           | <sup>t</sup> FILTER   | Valid shutdown-signal pulse width                                |     | 0.2  |      | μs    |

|                                      |                       | Digital OEN toggle filtering                                     |     | 200  |      | μs    |

| PMBus INTERFACE                      |                       |                                                                  |     |      |      |       |

|                                      | V <sub>IH</sub>       | Input logic-high, PMBUS_C, PMBUS_D                               | 2.1 |      |      | V     |

| PMBus Input Logic                    | VIL                   | Input logic-low, PMBUS_C, PMBUS_D                                |     |      | 0.8  | V     |

| PMBus Output Logic                   | V <sub>PMBUS_OL</sub> | Output low voltage, PMBUS_D,<br>PMBUS_A, I <sub>LOAD</sub> = 4mA |     |      | 0.4  | V     |

| Maximum PMBus<br>Operating Frequency | f <sub>PMBUS</sub>    |                                                                  |     | 400  |      | kHz   |

| VR_HOT                               |                       |                                                                  |     |      |      |       |

| VR_HOT Accuracy                      |                       | V <sub>TSENSE_</sub> = 1.145V<br>(VR_HOT threshold at 105°C)     | -3  |      | +3   | °C    |

| Temperature Zone<br>Hysteresis       |                       |                                                                  |     | 3    |      | %     |

| Output-Low Voltage                   | V <sub>OL</sub>       | VR_HOT, I <sub>LOAD</sub> = 24mA                                 |     |      | 0.3  | V     |

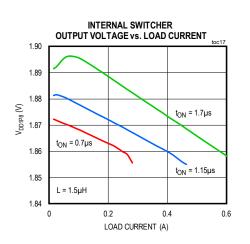

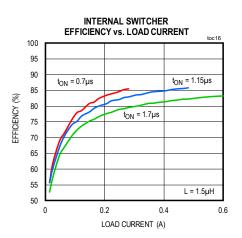

| 3.3V to 1.8V SWITCHING               | REGULATOR             |                                                                  |     |      |      |       |

| Set-Point Output Voltage             | V <sub>DD1P8</sub>    | Switcher output voltage                                          | 1.8 | 1.85 | 1.9  | V     |

| Maximum Output Current               | I <sub>VX_AVE</sub>   | L = 1.5µH, VX <sub>ON_TIME</sub> = 1.15µs                        |     | 500  |      | mA    |

| Switcher VX On-Time<br>Accuracy      | VX <sub>ON_TIME</sub> | 4 typical selections: 0.70μs, 1.15μs,<br>1.70μs, 2.26μs          | -10 |      | +10  | %     |

| TELEMETRY                            |                       |                                                                  |     |      |      |       |

| INPUT CURRENT SENSE                  |                       |                                                                  |     |      |      |       |

| ADC Resolution                       |                       |                                                                  |     | 10   |      | bit   |

| Differential Input Voltage<br>Range  |                       | External current-sense mode                                      |     |      | 200  | mV    |

|                                      | $\Delta V_{SNS_{IN}}$ | R <sub>SENSE</sub> mode                                          |     |      | 57.5 | mV    |

|                                      |                       | R <sub>SENSE</sub> mode, extended range                          |     |      | 115  | mV    |

| Update Rate                          |                       |                                                                  |     | 64   |      | μs    |

# VR13.HC and AI Cores Dual-Output Voltage Regulator Chipset

### **Electrical Characteristics (continued)**

| PARAMETER                       | SYMBOL          | CONDITIONS                                                                             |                          | MIN  | TYP | MAX  | UNITS |

|---------------------------------|-----------------|----------------------------------------------------------------------------------------|--------------------------|------|-----|------|-------|

|                                 |                 | External current-sense                                                                 | Gain                     | -0.8 |     | +0.8 | %     |

|                                 |                 | mode                                                                                   | Offset,<br>LSB = 259.4µV | -4   |     | +4   | LSB   |

|                                 |                 |                                                                                        | Gain                     | -0.6 |     | +0.6 | %     |

| Accuracy                        |                 | R <sub>SENSE</sub> mode                                                                | Offset,<br>LSB = 68.66µV | -4   |     | +4   | LSB   |

|                                 |                 | Barrian mode                                                                           | Gain                     | -0.6 |     | 0.6  | %     |

|                                 |                 | R <sub>SENSE</sub> mode,<br>extended range                                             | Offset,<br>LSB = 129.7µV | -4   |     | +4   | LSB   |

| PIN_ALERT Delay                 |                 |                                                                                        |                          |      | 32  |      | μs    |

| PIN_ALERT Output Low<br>Voltage | V <sub>OL</sub> | I <sub>LOAD</sub> = 24mA                                                               |                          |      |     | 0.3  | v     |

| SYSTEM ADC                      |                 |                                                                                        |                          |      |     |      |       |

|                                 |                 | Input voltage (Note 4)                                                                 |                          | 16   |     | ms   |       |

|                                 |                 | Input current, phase-input current<br>CORE output voltage<br>CORE phase-output current |                          |      | 16  |      | ms    |

| Update Rate                     |                 |                                                                                        |                          |      | 8   |      | ms    |

|                                 |                 |                                                                                        |                          |      | 16  |      | ms    |

|                                 |                 | Temperature                                                                            |                          |      | 16  |      | ms    |

| Resolution                      |                 |                                                                                        |                          |      | 10  |      | bits  |

|                                 |                 | Temperature,                                                                           | Gain                     | -0.8 |     | +0.8 | %     |

|                                 |                 | $T_A = 0^{\circ}C$ to +85°C                                                            | Offset                   | -4   |     | +4   | LSB   |

|                                 |                 | Input voltage,<br>T <sub>A</sub> = 0°C to +85°C                                        | Gain                     | -0.9 |     | +0.9 | %     |

|                                 |                 | V <sub>IN</sub> = 7V to 13V<br>0xD9[4] = 0                                             | Offset                   | -5   |     | +5   | LSB   |

|                                 |                 | CORE output voltage,                                                                   | Gain                     | -0.9 |     | +0.9 | %     |

| Accuracy                        |                 | $T_A = 0^{\circ}C$ to +85°C                                                            | Offset                   | -6   |     | +6   | LSB   |

|                                 |                 | CORE phase-output                                                                      | Gain                     | -1.5 |     | +1.5 | %     |

|                                 |                 | current, $T_A = 0^{\circ}C$ to +85°C                                                   | Offset                   | -4   |     | +4   | LSB   |

|                                 |                 | PWM duty-cycle<br>measurement                                                          | Gain                     | -1   |     | +1   | %     |

|                                 |                 | $T_A = 0^{\circ}C$ to +85°C<br>PWM duty cycle =<br>0% to 50%                           | Offset                   | -4   |     | +4   | LSB   |

# VR13.HC and AI Cores Dual-Output Voltage Regulator Chipset

### **Electrical Characteristics (continued)**

| PARAMETER                 | SYMBOL | CON                                                                                                                       | MIN                                                                                                             | TYP              | MAX    | UNITS |             |

|---------------------------|--------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------|--------|-------|-------------|

| VIN_ADC                   |        |                                                                                                                           |                                                                                                                 |                  |        |       |             |

| Resolution                |        |                                                                                                                           |                                                                                                                 |                  | 10     |       | bits        |

|                           |        |                                                                                                                           | Gain,<br>SNS_VIN tied to V <sub>IN</sub>                                                                        | -0.9             |        | +0.9  | %           |

| Accuracy                  |        | Input voltage,<br>$T_A = 0^{\circ}C \text{ to } +85^{\circ}C$<br>$V_{IN} = 7V \text{ to } 13V$<br>0xD9[4] = 1<br>(Note 4) | Gain,<br>SNS_VIN tied to<br>external divider<br>R <sub>VIN_TOP</sub> = 4.75kΩ,<br>R <sub>VIN_BOT</sub> = 19.6kΩ | -0.9             |        | +0.9  | %           |

|                           |        |                                                                                                                           | Offset<br>LSB = 15.625mV<br>Referred to V <sub>IN</sub>                                                         | -5               |        | +5    | LSB         |

| I <sub>OUT</sub> ADC CORE | -      |                                                                                                                           |                                                                                                                 |                  |        |       |             |

| Intel 0x15 Update Rate    |        |                                                                                                                           |                                                                                                                 |                  | 64     |       | μs          |

| Resolution                |        |                                                                                                                           |                                                                                                                 |                  | 9      |       | bits        |

|                           |        | 0xE7[2:0] = 000                                                                                                           | LSB                                                                                                             |                  | 1.27   |       | A           |

|                           |        | Range 0 to 603A                                                                                                           | Gain                                                                                                            | -1.0             |        | +1.0  | %           |

|                           |        | $T_A = 0^{\circ}C$ to +85°C                                                                                               | Offset                                                                                                          | -5.7             |        | +5.7  | A           |

|                           |        | 0xE7[2:0] = 001                                                                                                           | LSB                                                                                                             |                  | 637    |       | mA          |

|                           |        | Range 0 to 301A<br>$T_A = 0^{\circ}C$ to +85°C<br>0xE7[2:0] = 010<br>Range 0 to 201A<br>$T_A = 0^{\circ}C$ to +85°C       | Gain                                                                                                            | -1.35            |        | +1.35 | %           |

|                           |        |                                                                                                                           | Offset                                                                                                          | -4               |        | +4    | A           |

|                           |        |                                                                                                                           | LSB                                                                                                             |                  | 425    |       | mA          |

| Accuracy                  |        |                                                                                                                           | Gain                                                                                                            | -1.35            |        | +1.35 | %           |

| ,                         |        |                                                                                                                           | Offset                                                                                                          | -3.6             |        | +3.6  | A           |

|                           |        | 0                                                                                                                         | LSB                                                                                                             |                  | 318    |       | mA          |

|                           |        | 0xE7[2:0] = 011<br>Range 0 to 150A                                                                                        | Gain                                                                                                            | -1.35            |        | +1.35 | %           |

|                           |        | $T_A = 0^{\circ}C$ to +85°C                                                                                               | Offset                                                                                                          | -3.5             |        | +3.5  | A           |

|                           |        |                                                                                                                           | LSB                                                                                                             |                  | 255    | 0.0   | mA          |

|                           |        | 0xE7[2:0] = 100<br>Range 0 to 120A                                                                                        | Gain                                                                                                            | -1.35            | 200    | +1.35 | %           |

|                           |        | $T_A = 0^{\circ}C$ to +85°C                                                                                               | Offset                                                                                                          | -3.4             |        | +3.4  | A           |

| I <sub>OUT</sub> ADC VSA  |        |                                                                                                                           | 01301                                                                                                           | -0. <del>1</del> |        | · 0   |             |

| Intel 0x15 Update Rate    |        |                                                                                                                           |                                                                                                                 |                  | 64     |       | μs          |

| Resolution                |        |                                                                                                                           |                                                                                                                 |                  | 9      |       | bits        |

|                           |        |                                                                                                                           | Gain                                                                                                            |                  | 78.125 |       | mA          |

| A                         |        | 0xD1[4:3] = 01                                                                                                            | Offset                                                                                                          | -1.0             | 10.120 | +1.0  | - MA<br>- % |

| Accuracy                  |        | Range 0 to 37.1A<br>$T_A = 0^{\circ}C$ to +85°C                                                                           |                                                                                                                 |                  |        |       |             |

|                           |        |                                                                                                                           | Offset                                                                                                          | -4.5             |        | +4.5  | LSB         |

# VR13.HC and AI Cores Dual-Output Voltage Regulator Chipset

### **Electrical Characteristics (continued)**

- **Note 2:** Slew rate specification is guaranteed for the internal DAC. Performance of the output voltage of the regulator depends on the compensation and might be limited from the maximum bandwidth possible for the specific application.

- Note 3: See the <u>VSA Overcurrent Protection</u> section to calculate actual threshold based on design parameters.

- **Note 4:** The input voltage can be acquired by the system ADC if the PMBus command 0xD9[4] = 0. it Is otherwise acquired from a faster and dedicated VIN\_ADC.

# VR13.HC and AI Cores Dual-Output Voltage Regulator Chipset

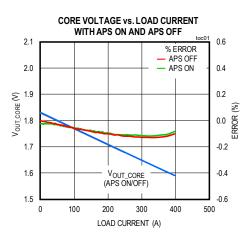

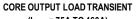

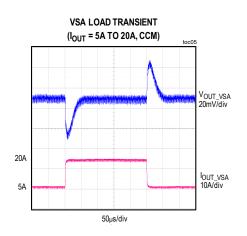

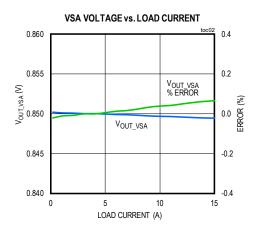

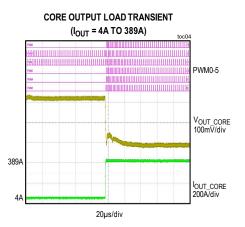

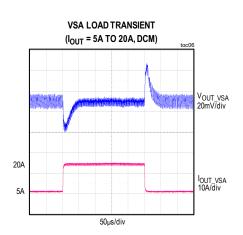

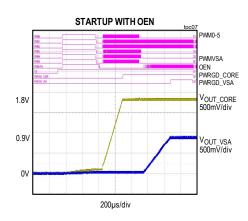

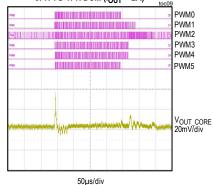

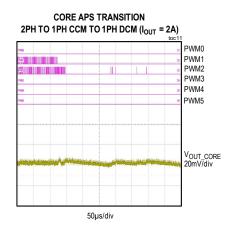

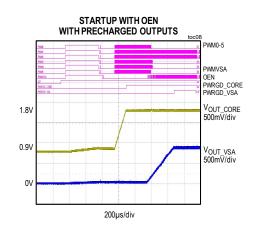

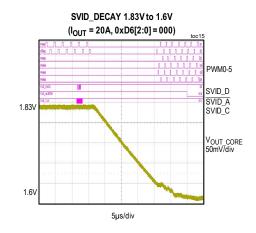

### **Typical Operating Characteristics**

$(V_{IN} = 12V, 6 + 1 \text{ phase configuration}, f_{SW} (CORE) = 500 \text{kHz}, \text{ inductor (CORE)} = 100 \text{nH} \text{ CL1208-6}, \text{ inductor (VSA)} = 180 \text{nH}, f_{SW} (VSA) = 660 \text{kHz}, V_{VID} (CORE) = 1.8V, V_{VID} (VSA) = 0.85V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

# VR13.HC and AI Cores Dual-Output Voltage Regulator Chipset

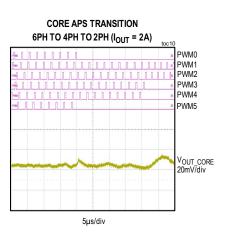

**Typical Operating Characteristics (continued)** (V<sub>IN</sub> = 12V, 6 + 1 phase configuration, f<sub>SW</sub> (CORE) = 500kHz, inductor (CORE) = 100nH CL1208-6, inductor (VSA) = 180nH,  $f_{SW}$  (VSA) = 660kHz, V<sub>VID</sub> (CORE) = 1.8V, V<sub>VID</sub> (VSA) = 0.85V, T<sub>A</sub> = +25°C, unless otherwise noted.)

CORE APS TRANSITION 6PH TO 1PH DCM (I<sub>OUT</sub> = 2A)

# VR13.HC and AI Cores Dual-Output Voltage Regulator Chipset

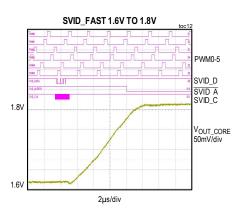

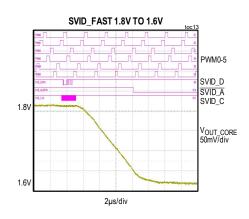

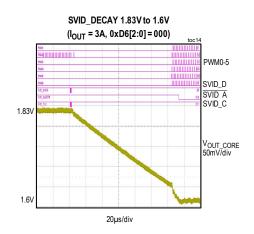

**Typical Operating Characteristics (continued)** (V<sub>IN</sub> = 12V, 6 + 1 phase configuration, f<sub>SW</sub> (CORE) = 500kHz, inductor (CORE) = 100nH CL1208-6, inductor (VSA) = 180nH,  $f_{SW}$  (VSA) = 660kHz, V<sub>VID</sub> (CORE) = 1.8V, V<sub>VID</sub> (VSA) = 0.85V, T<sub>A</sub> = +25°C, unless otherwise noted.)

# VR13.HC and AI Cores Dual-Output Voltage Regulator Chipset

### **Pin Configuration**

### **Pin Description**

| PIN | NAME                | FUNCTION                                                                                                                                                                                                                         |

|-----|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | PROG                | Configuration Programming Resistor. Connect a 1% accurate resistor to ground to program the application scenario (see <u>Table 5</u> ) and the PMBus MSB address, unless overwritten using the PMBus MSB_PMBus bit.              |

| 2   | ADDR                | Address Programming Resistor. Connect a 1% accurate resistor to ground to set the SVID address and PMBus LSB address (see <u>Table 5</u> ).                                                                                      |

| 3   | AV <sub>DD1P8</sub> | Bias Supply Pin. Connect to DVDD1P8 or external power supply through a $4.7\Omega$ resistor.<br>Decouple with a minimum of $2.2\mu$ F and $0.1\mu$ F to the exposed GND pad.                                                     |

| 4   | DGND                | Digital Ground. Connect to the ground plane using a single via placed in close proximity to the IC.                                                                                                                              |

| 5   | DVDD1P8             | Digital Bias Supply Pin. Connect to the output of the chip inductor when using the internal 1.8V switching regulator; otherwise, connect to an external 1.8V supply. Decouple with a minimum of $1\mu$ F and 0.1 $\mu$ F to GND. |

| 6   | SVID_A              | SVID Alert# Output                                                                                                                                                                                                               |

# VR13.HC and AI Cores Dual-Output Voltage Regulator Chipset

# **Pin Description (continued)**

| PIN | NAME                | FUNCTION                                                                                                                                                                                                                                                                                                                                                              |

|-----|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SVID_D              | SVID Data I/O                                                                                                                                                                                                                                                                                                                                                         |

| 8   | SVID_C              | SVID Clock Input                                                                                                                                                                                                                                                                                                                                                      |

| 9   | OEN                 | Voltage Regulator Output-Voltage Enable. When OEN is pulled high, both outputs are enabled<br>and start up to the programmed boot voltage. When OEN is pulled low, both outputs are ramped<br>down to 0.5V at the slow slew rate before the power stages are set to the IDDQ state.<br>The PMBus interface remains active when OEN is low.                            |

| 10  | OVP                 | Output Overvoltage Indicator. This active-low open-drain output indicates that one or both of the outputs have exceeded the OVP threshold.                                                                                                                                                                                                                            |

| 11  | VR_HOT/OCP_<br>FLAG | Overtemperature-Warning Indicator. This active-low open-drain output indicates that one of the power-stage temperatures has exceeded the threshold programmed in the application scenario and reported in the SVID register Temp_Max (22h). Depending on scenario programming, the controller can also indicate when the controller OCP clamp is engaged on this pin. |

| 12  | FAULT               | Voltage Regulator Fault Indicator. This active-low open-drain output indicates that a VR fault occurred (see <u>Table 2</u> and <u>Table 3</u> ).                                                                                                                                                                                                                     |

| 13  | PWRGD_CORE          | CORE Power-Good Signal. This open-drain output indicates when the V <sub>CORE</sub> output is within regulation.                                                                                                                                                                                                                                                      |

| 14  | PWRGD_VSA           | VSA Power-Good Signal. This open-drain output indicates when the VSA output is within regulation.                                                                                                                                                                                                                                                                     |

| 15  | PMBUS_A             | PMBus Alert# Output                                                                                                                                                                                                                                                                                                                                                   |

| 16  | PMBUS_C             | PMBus Clock Input                                                                                                                                                                                                                                                                                                                                                     |

| 17  | PMBUS_D             | PMBus Data I/O                                                                                                                                                                                                                                                                                                                                                        |

| 18  | V <sub>DD3P3</sub>  | 3.3V Supply Pin. V <sub>DD3P3</sub> is the input for the internal 1.8V switching regulator. Bypass this input with a 2 x 10 $\mu$ F and 0.1 $\mu$ F ceramic capacitor. V <sub>DD3P3</sub> must be connected to a 3.3V bias supply with a 0.1 $\mu$ F bypass capacitor even when the internal 1.8V switching regulator is disabled.                                    |

| 19  | VX                  | Switching Node for the Internal 1.8V Switching Regulator. Connect a chip inductor between VX and DVDD1P8, with a minimum of 2 x 22 $\mu$ F ceramic capacitors for the output of the regulator. Connect VX to V <sub>DD3P3</sub> using a 100 $\Omega$ resistor to disable the 1.8V switching regulator when using an external 1.8V bias supply.                        |

| 20  | PGND                | Power Ground. Return path for the internal 1.8V switching regulator.                                                                                                                                                                                                                                                                                                  |

| 21  | IC                  | Internally Connected Pin. Leave this pin unconnected.                                                                                                                                                                                                                                                                                                                 |

| 22  | PWM_VSA             | Phase Control Output for the VSA Regulator. Connect PWM_VSA to the input pin of the VSA power stage. Connect PWM_VSA to GND to disable the VSA regulator.                                                                                                                                                                                                             |

# VR13.HC and AI Cores Dual-Output Voltage Regulator Chipset

# **Pin Description (continued)**

| PIN   | NAME         |                                                                                                                                                                                                                            | FUN                                                                                                                                                                                              | CTION                                                                                                                                                           |  |  |  |

|-------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|       |              |                                                                                                                                                                                                                            | Phase-Control Outputs for the V <sub>CORE</sub> Regulator. Connect PWM_<7:0> to the respective inp pins of the V <sub>CORE</sub> power stages. Connect PWM_ to GND for unused power-stage pairs. |                                                                                                                                                                 |  |  |  |

|       |              | P                                                                                                                                                                                                                          | N                                                                                                                                                                                                | NAME                                                                                                                                                            |  |  |  |

|       |              | 2                                                                                                                                                                                                                          | 3                                                                                                                                                                                                | PWM_7                                                                                                                                                           |  |  |  |

|       |              | 2                                                                                                                                                                                                                          | 4                                                                                                                                                                                                | PWM_6                                                                                                                                                           |  |  |  |

| 23-30 | PWM_<7:0>    | 2                                                                                                                                                                                                                          | 5                                                                                                                                                                                                | PWM_5                                                                                                                                                           |  |  |  |

|       |              | 2                                                                                                                                                                                                                          | 6                                                                                                                                                                                                | PWM_4                                                                                                                                                           |  |  |  |

|       |              | 2                                                                                                                                                                                                                          | 7                                                                                                                                                                                                | PWM_3                                                                                                                                                           |  |  |  |

|       |              | 2                                                                                                                                                                                                                          | 8                                                                                                                                                                                                | PWM_2                                                                                                                                                           |  |  |  |

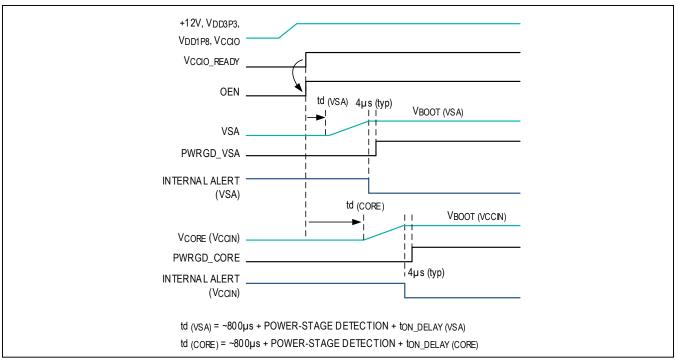

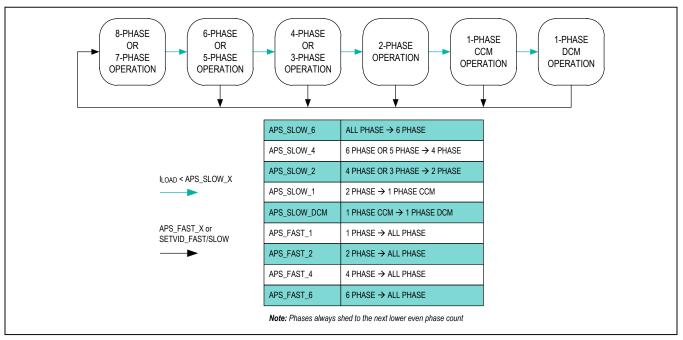

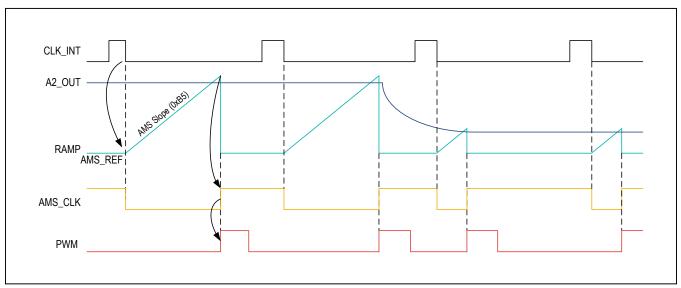

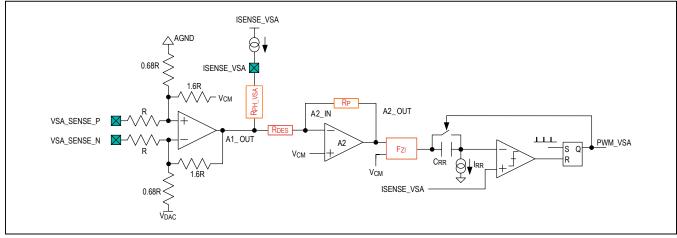

|       |              | 2                                                                                                                                                                                                                          | 9                                                                                                                                                                                                | PWM_1                                                                                                                                                           |  |  |  |