Click here to ask an associate for production status of specific part numbers.

#### MAX25520

### **Automotive 2-Channel TFT-LCD Power Supply**

#### **General Description**

The MAX25520 is a dual-output power IC that provides symmetrical or asymmetrical positive and negative voltages up to 10.5V and down to -10.5V (±12V for MAX25520ATEC) with an input voltage between 2.65V and 5.5V. It incorporates a fully integrated current-mode boost converter and a current-mode inverter with external rectifier. The device operates at one of two switching frequencies, 420kHz or 2.1MHz. Operation at 2.1MHz permits very compact dual-output power supplies.

The two output voltages can be programmed independently or can be made to track each other. Independent enable pins allow complete flexibility in powering the outputs up and down.

The outputs are protected against overcurrent and undervoltage.

The MAX25520 is available in a compact, 3mm x 3mm TQFN package and operates over the -40°C to +125°C automotive temperature range.

### **Applications**

- Infotainment Displays

- Central Information Displays

- Instrument Clusters

#### **Benefits and Features**

- High Integration

- Synchronous Boost Provides Positive Output at up to 10.5V/200mA (+12V for MAX25520ATEC)

- Inverter Output Provides up to -10.5V/-200mA (-12V for MAX25520ATEC)

- Low EMI

- 420kHz/2.1MHz Switching Frequency

- · Spread Spectrum

- UV Diagnostics on All Outputs

- Versatile

- · Complete Sequencing Flexibility

- Compact TQFN Package

- -40°C to +125°C Operating Temperature Range

- AEC-Q100 Grade 1

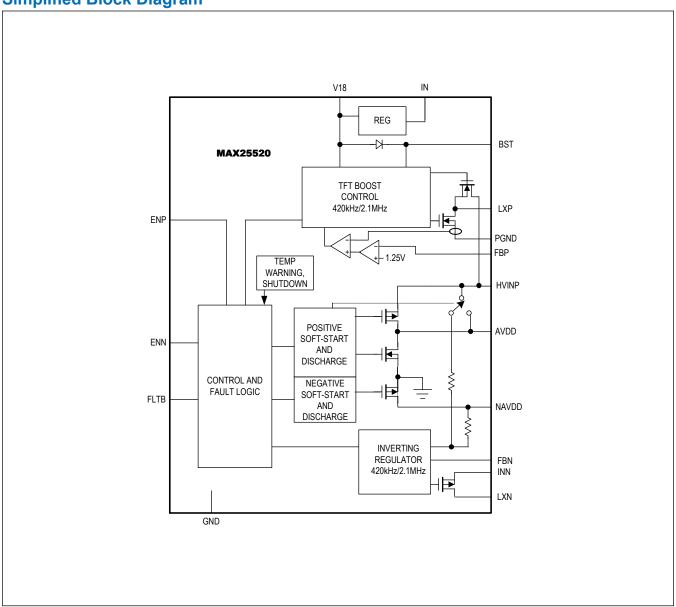

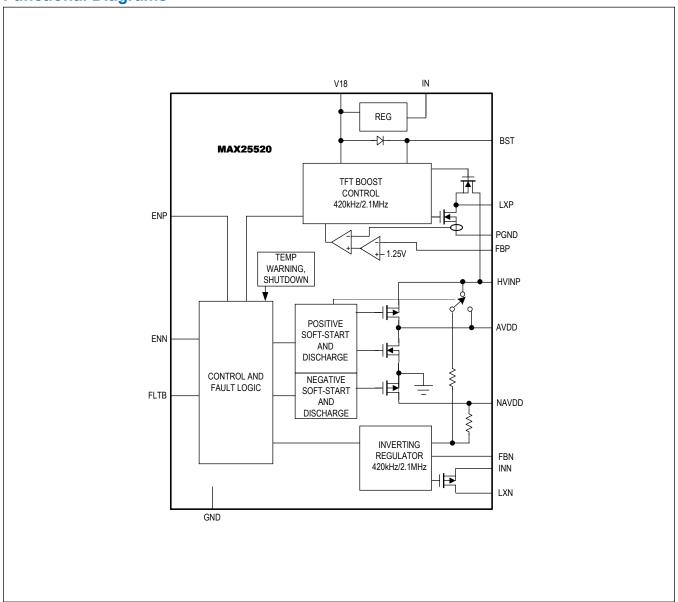

### **Simplified Block Diagram**

### **Absolute Maximum Ratings**

| IN, INN to GND     | 0.3V to +6V          | NAVDD to GND                           | V18-16V to V18+0.3V          |

|--------------------|----------------------|----------------------------------------|------------------------------|

| FBP to GND         | 0.3V to +2.2V        | ENP, ENN to GND                        | 0.3V to 6V                   |

| HVINP to GND       | 0.3V to +14V         | FLTB, FBN to GND                       | 0.3V to +6V                  |

| BST to GND         | 0.3V to +16V         | Continuous Power Dissipation (Multilay | ver Board) ( $T_A = +70$ °C, |

| BST to LXP         | 0.3V to +2.2V        | derate 21.3mW/°C above +70°C.)         | mW to 2222mW                 |

| LXP, AVDD to GND   | 0.3V to HVINP + 0.3V | Operating Temperature Range            | 40°C to 125°C                |

| LXN to INN         | 22V to +0.3V         | Junction Temperature                   | +150°C                       |

| V18 to GND         | 0.3V to +2.2V        | Soldering Temperature (reflow)         | +260°C                       |

| PGND. CPGND to GND | 0.3V to +0.3V        | ,                                      |                              |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### **TQFN**

| Package Code                            | T1633+7C |

|-----------------------------------------|----------|

| Outline Number                          | 21-0136  |

| Land Pattern Number                     | 90-0032  |

| Thermal Resistance, Single-Layer Board: |          |

| Junction to Ambient (θ <sub>JA</sub> )  | 68°C/W   |

| Junction to Case (θ <sub>JC</sub> )     | 10°C/W   |

| Thermal Resistance, Four-Layer Board:   |          |

| Junction to Ambient (θ <sub>JA</sub> )  | 43.3°C/W |

| Junction to Case $(\theta_{JC})$        | 4°C/W    |

For the latest package outline information and land patterns (footprints), go to www.maximintegrated.com/packages. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **Electrical Characteristics**

$(V_{IN} = 3.3V, V_{INN} = 3.3V, ENP = ENN = 3.3V, C_{V18} = 1\mu F, (Note 1))$

| PARAMETER            | SYMBOL               | CONDITIONS                                                     | MIN   | TYP | MAX   | UNITS                                 |

|----------------------|----------------------|----------------------------------------------------------------|-------|-----|-------|---------------------------------------|

| INPUT SUPPLY         |                      |                                                                |       |     |       |                                       |

| IN Voltage Range     |                      | MAX25520ATEA/B                                                 | 2.65  |     | 5.5   | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

|                      | V <sub>IN_RNG</sub>  | MAX25520ATEC                                                   | 4.5   |     | 5.5   | V                                     |

| IN UVLO Threshold    | V <sub>IN_UVLO</sub> | IN Voltage Rising                                              | 2.4   | 2.5 | 2.57  | V                                     |

| IN UVLO Hysteresis   | VIN_UVLO_HY          |                                                                |       | 100 |       | mV                                    |

| Start-Up Delay       | T <sub>SU_DEL</sub>  | ENP or ENN high                                                |       | 50  | 100   | μs                                    |

| IN Shutdown Current  | I <sub>IN_SHDN</sub> | ENN = ENP = GND, V <sub>IN</sub> = 3.3V, T <sub>A</sub> = 25°C |       | 4   | 6     | μA                                    |

| IN Quiescent Current | I <sub>IN_Q</sub>    | V <sub>ENN</sub> = V <sub>ENP</sub> = 3.3V, no switching.      |       | 1   | 1.8   | mA                                    |

| V18 REGULATOR        | •                    |                                                                |       |     |       |                                       |

| V18 Output Voltage   | V <sub>V18_ACC</sub> | No load on V18                                                 | 1.764 | 1.8 | 1.836 | V                                     |

| V18 Current Limit    | I <sub>LIM V18</sub> |                                                                | 50    |     |       | mA                                    |

Analog Devices | 3 www.analog.com

### **Electrical Characteristics (continued)**

$(V_{IN} = 3.3V, V_{INN} = 3.3V, ENP = ENN = 3.3V, C_{V18} = 1\mu F, (Note 1))$

| PARAMETER                                           | SYMBOL                        | CONDITIONS                                                                         | MIN                 | TYP  | MAX  | UNITS                                 |  |

|-----------------------------------------------------|-------------------------------|------------------------------------------------------------------------------------|---------------------|------|------|---------------------------------------|--|

| V18 Undervoltage<br>Lockout                         | V <sub>V18_UVLO</sub>         | V18 Voltage Rising                                                                 | 1.6                 | 1.65 | 1.7  | V                                     |  |

| V18 Undervoltage<br>Hysteresis                      | V <sub>V18_UVLO_H</sub><br>YS |                                                                                    |                     | 150  |      | mV                                    |  |

| OSCILLATOR                                          |                               |                                                                                    |                     |      |      |                                       |  |

| Operating Frequency                                 | f <sub>BOOSTH</sub>           | MAX25520ATEB/C, dither disabled.<br>Switching frequency for boost and<br>inverter. | 1950                | 2100 | 2250 | - kHz                                 |  |

| Operating Frequency                                 | fBOOSTL                       | MAX25520ATEA, dither disabled.<br>Switching frequency for boost and<br>inverter.   | 390                 | 420  | 450  | KHZ                                   |  |

| Frequency Dither                                    | fBOOSTD                       |                                                                                    |                     | ±6   |      | %                                     |  |

| <b>BOOST REGULATOR</b>                              |                               |                                                                                    |                     |      |      |                                       |  |

| HVINP Output Voltage                                | V. n. a                       | MAX25520ATEA/B                                                                     | V <sub>IN</sub> + 1 |      | 10.5 | V                                     |  |

| Range                                               | V <sub>HVINP</sub>            | MAX25520ATEC                                                                       | V <sub>IN</sub> + 1 |      | 12   | v                                     |  |

| AVDD Output Voltage                                 | V., (22                       | MAX25520ATEA/B                                                                     | 4.2                 |      | 10.5 | V                                     |  |

| Range                                               | V <sub>AVDD</sub>             | MAX25520ATEC                                                                       | 6                   |      | 12   | v                                     |  |

| AVDD Default Output<br>Voltage                      | Vavdd_acc                     | FBP connected to V18                                                               | 6.66                | 6.8  | 6.94 | V                                     |  |

| FBP Regulation Voltage                              | V <sub>FBP</sub>              | Full input voltage and output current range                                        | 0.89                | 0.9  | 0.91 | V                                     |  |

| LXP Maximum Duty                                    | D                             | 420kHz switching frequency                                                         | 86                  | 88   | 90   | %                                     |  |

| Cycle                                               | D <sub>LXP_MAX</sub>          | 2.1MHz switching frequency                                                         | 85                  | 88   | 91   |                                       |  |

| Low-Side Switch On-<br>Resistance                   | R <sub>ON_LS_LXP</sub>        | I <sub>LXP</sub> = 0.1A                                                            |                     | 0.1  | 0.2  | Ω                                     |  |

| Synchronous Rectifier On-Resistance                 | R <sub>ON_HS_LXP</sub>        | I <sub>LXP</sub> = -0.1A                                                           |                     | 0.1  | 0.2  | Ω                                     |  |

| Synchronous Rectifier<br>Zero-Crossing<br>Threshold | <sup>I</sup> ZX_TH            | I <sub>ZX</sub> decreasing                                                         |                     | 70   |      | mA                                    |  |

| LXP Leakage Current                                 | I <sub>LEAK_LXP</sub>         | $V_{ENP} = 0V, V_{LXP} = 10.5V$                                                    |                     |      | 5    | μA                                    |  |

| LXP Current Limit                                   | I <sub>LIMPH</sub>            | Duty cycle = 50%                                                                   | 1.64                | 2.1  | 2.3  | А                                     |  |

| Soft-Start Period                                   | t <sub>BOOST_SS</sub>         | Current-limit ramp                                                                 |                     | 5    |      | ms                                    |  |

| AVDD Discharge<br>Resistance                        | R <sub>AVDD_DIS</sub>         | ENP = 0V, V <sub>V18</sub> > V <sub>V18</sub> _UVLO                                |                     | 1.2  |      | kΩ                                    |  |

| INVERTING REGULATO                                  | R                             |                                                                                    | ·                   |      |      |                                       |  |

| INN Voltage Range                                   | \/                            | MAX25520ATEA/B                                                                     | 2.65                |      | 5.5  | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |  |

|                                                     | V <sub>INN_RNG</sub>          | MAX25520ATEC                                                                       | 4.5                 |      | 5.5  | V                                     |  |

| INN Shutdown Current                                | INN_SHDN                      | V <sub>ENN</sub> = 0V, T <sub>A</sub> = 25°C                                       |                     |      | 1    | μA                                    |  |

| INN Quiescent Current                               | I <sub>INN_Q</sub>            |                                                                                    |                     | 0.2  |      | mA                                    |  |

| LXN Maximum Duty<br>Cycle                           | D <sub>LXN_MAX</sub>          | F <sub>SW</sub> = 420kHz or 2.1MHz                                                 | 85                  | 88   |      | %                                     |  |

| FBN Regulation Voltage                              | V <sub>FBN</sub>              |                                                                                    | -20                 | 0    | +20  | mV                                    |  |

### **Electrical Characteristics (continued)**

$(V_{IN} = 3.3V, V_{INN} = 3.3V, ENP = ENN = 3.3V, C_{V18} = 1\mu F, (Note 1))$

| PARAMETER                                                    | SYMBOL                          | CONDITIONS                                                                                                                          | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>AVDD</sub> + V <sub>NAVDD</sub><br>Regulation Voltage | V <sub>NAVDD_AVD</sub><br>D_REG | $V_{INN}$ = 2.65V to 5.5V, $V_{AVDD}$ = 6.8V,<br>1mA < $I_{NAVDD}$ < 200mA, $I_{AVDD}$ = same<br>load as NAVDD, FBN connected to IN | -34  | 0    | 34   | mV    |

| Low-Side LXN On-<br>Resistance                               | R <sub>ON_LXN</sub>             | I <sub>LXN</sub> = 0.1A                                                                                                             |      | 0.25 | 0.5  | Ω     |

| LXN Leakage Current                                          | I <sub>LXN_LEAK</sub>           | V <sub>LXN</sub> = V <sub>NAVDD</sub> = -6.8V, T <sub>A</sub> = +25°C                                                               |      |      | 20   | μA    |

| LXN Current Limit                                            | I <sub>LIMNH</sub>              | Duty cycle = 80%                                                                                                                    | 1.55 | 1.9  | 2.25 | Α     |

| Soft-Start Period                                            | t <sub>INV_SS</sub>             | Current-limit ramp                                                                                                                  |      | 5    |      | ms    |

| NAVDD Discharge<br>Resistance                                | R <sub>NAVDD_DIS</sub>          |                                                                                                                                     |      | 2    |      | kΩ    |

| AVDD SWITCH                                                  |                                 |                                                                                                                                     |      |      |      |       |

| AVDD ON Resistance                                           | R <sub>ONAVDD</sub>             | Between HVINP and AVDD, I <sub>AVDD</sub> = 200mA                                                                                   |      | 0.5  | 0.9  | Ω     |

| AVDD Current Limit                                           | I <sub>LIM_AVDD</sub>           |                                                                                                                                     | 320  | 460  | 580  | mA    |

| FAULT PROTECTION                                             |                                 |                                                                                                                                     |      |      |      |       |

| Fault Timeout                                                | T <sub>FAULT</sub>              | Applies to both outputs                                                                                                             |      | 30   |      | ms    |

| Fault Retry Time                                             | T <sub>AUTO</sub>               |                                                                                                                                     |      | 1.9  |      | S     |

| AVDD Undervoltage Fault Threshold                            | V <sub>AVDD_UV</sub>            | Relative measurement between HVINP and AVDD, AVDD falling                                                                           | 80   | 85   | 90   | %     |

| FBP Undervoltage Fault Threshold                             | V <sub>FBP_UV</sub>             | External feedback, FBP falling                                                                                                      | 720  | 765  | 810  | mV    |

| NAVDD Undervoltage Fault Threshold                           | NAVDD <sub>UV</sub>             | FBN = IN, NAVDD rising                                                                                                              | 80   | 85   | 90   | %     |

| FBN Undervoltage Fault<br>Threshold                          | V <sub>FBN_UV</sub>             | External resistor-divider connected to FBN, NAVDD = -6.8V, FBN rising                                                               | 200  | 210  | 220  | mV    |

| AVDD Short-Circuit Fault Threshold                           | AVDD <sub>SHRT_T</sub><br>H     | As a percentage of set voltage, AVDD falling                                                                                        | 35   | 40   | 45   | %     |

| FBP Short-Circuit<br>Threshold                               | V <sub>FBP_SHRT</sub>           | External feedback, FBP falling                                                                                                      | 315  | 360  | 405  | mV    |

| NAVDD Short-Circuit Fault Threshold                          | NAVDD <sub>SHRT</sub> _<br>TH   | FBN = IN, NAVDD rising                                                                                                              | 35   | 40   | 45   | %     |

| FBN Short-Circuit Fault Threshold                            | V <sub>FBN_SHRT</sub>           | External resistor-divider connected to FBN, NAVDD = -6.8V, FBN rising                                                               | 835  | 850  | 865  | mV    |

| Short-Circuit and<br>Overload Fault Delay                    |                                 | After completion of soft-start                                                                                                      |      | 10   |      | μs    |

| LOGIC INPUTS and OUT                                         | PUTS                            |                                                                                                                                     |      |      |      |       |

| ENP, ENN Glitch Filter                                       | T <sub>EN_FLT</sub>             |                                                                                                                                     |      | 10   |      | μs    |

| ENN, ENP Minimum<br>Low Time For Reset                       | T <sub>EN_MIN</sub>             |                                                                                                                                     | 1    |      |      | ms    |

| ENP, ENN Input Logic-<br>High                                | V <sub>IH_EN</sub>              |                                                                                                                                     | 1.22 |      |      | V     |

| ENP, ENN Input Logic-<br>Low                                 | V <sub>IL_EN</sub>              |                                                                                                                                     |      |      | 0.6  | V     |

### **Electrical Characteristics (continued)**

$(V_{IN} = 3.3V, V_{INN} = 3.3V, ENP = ENN = 3.3V, C_{V18} = 1\mu F, (Note 1))$

| PARAMETER                           | SYMBOL                | CONDITIONS               | MIN | TYP | MAX | UNITS |

|-------------------------------------|-----------------------|--------------------------|-----|-----|-----|-------|

| ENP, ENN Input<br>Pulldown Resistor | R <sub>PD_EN</sub>    |                          |     | 200 |     | kΩ    |

| FLTB Output Low<br>Voltage          | V <sub>OL</sub>       | Sinking 5mA              |     |     | 0.4 | V     |

| FLTB Output Leakage<br>Current      | ILEAK_FLTB            | V <sub>FLTB</sub> = 5.5V |     |     | +1  | μA    |

| THERMAL SHUTDOWN                    |                       |                          |     |     |     |       |

| Thermal-Shutdown<br>Threshold       | T <sub>SHDN</sub>     |                          |     | 160 |     | °C    |

| Thermal-Shutdown<br>Hysteresis      | T <sub>SHDN_HYS</sub> |                          |     | 15  |     | °C    |

Note 1: Limits are 100% tested at T<sub>A</sub> = +25°C and +125°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.

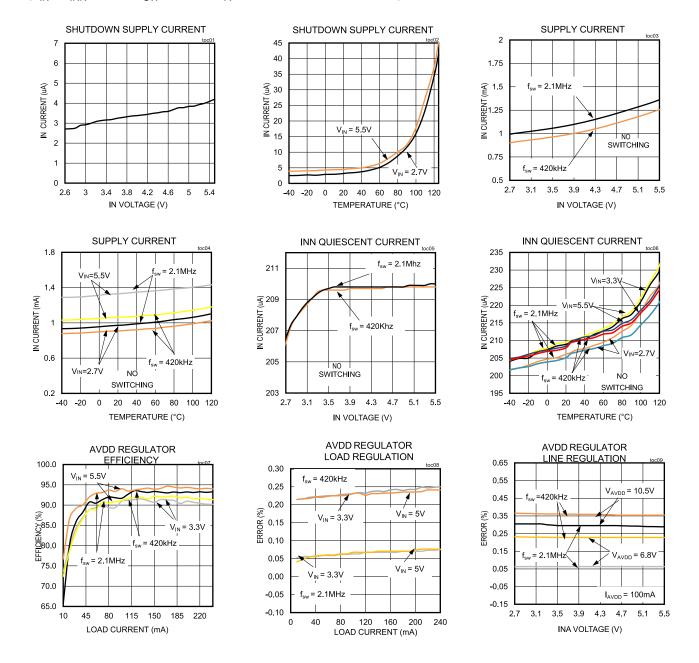

### **Typical Operating Characteristics**

$(V_{IN} = V_{INN} = +3.3V, F_{SW} = 2.1MHz, T_A = +25^{\circ}C$  unless otherwise noted.)

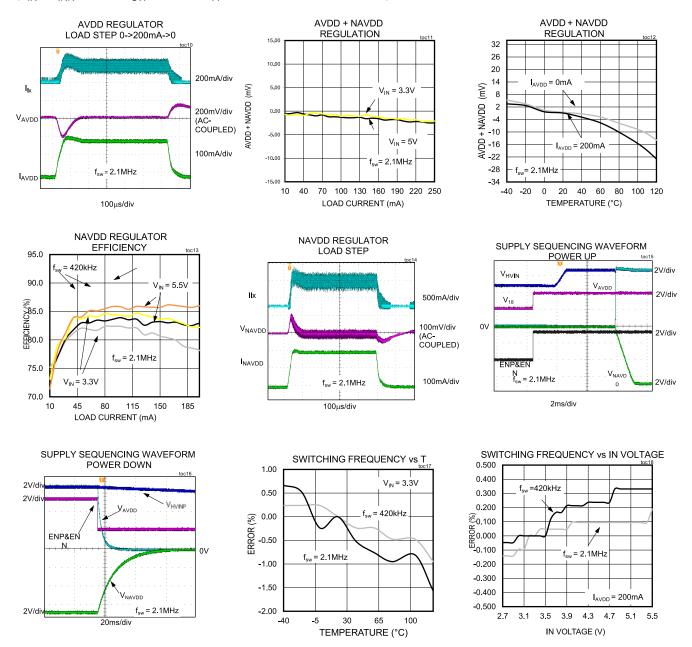

### **Typical Operating Characteristics (continued)**

$(V_{IN} = V_{INN} = +3.3V, F_{SW} = 2.1MHz, T_A = +25^{\circ}C \text{ unless otherwise noted.})$

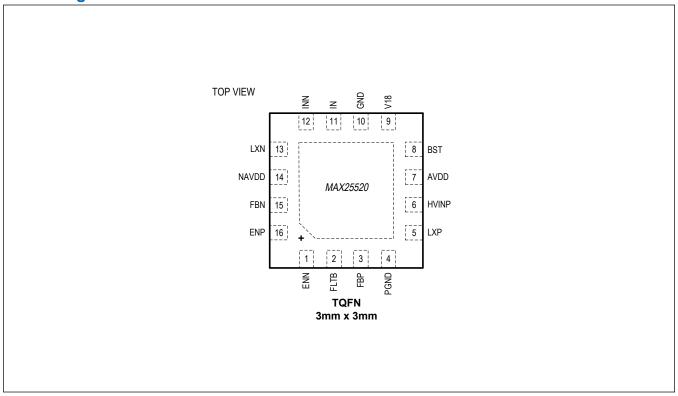

# **Pin Configuration**

# **Pin Description**

| PIN | NAME  | FUNCTION                                                                                                                                                                                                              |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | ENN   | Enable pin for inverting regulator.                                                                                                                                                                                   |

| 2   | FLTB  | Open-Drain, Active-Low Fault Output. Connect a pullup resistor from FLTB to a logic supply ≤5V.                                                                                                                       |

| 3   | FBP   | Boost feedback pin. Connect a resistor-divider between AVDD and GND with its midpoint connected to FBP to set the AVDD output voltage. Connect FBP to V18 to set AVDD to its default value of 6.8V.                   |

| 4   | PGND  | Ground Connection for Boost Switching Device. Connect to GND using a low-impedance trace.                                                                                                                             |

| 5   | LXP   | Switching Node of Boost Converter. Connect the boost inductor between LXP and IN.                                                                                                                                     |

| 6   | HVINP | Boost Output and input to AVDD switch. Bypass HVINP with a 22µF output capacitor placed close to the pin when using 420kHz switching frequency. When the switching frequency is 2.1MHz use a 10µF capacitor on HVINP. |

| 7   | AVDD  | Switched Output of Boost Converter. Connect a bypass capacitor of value 2.2µF from AVDD to PGND.                                                                                                                      |

| 8   | BST   | Bootstrap Capacitor Connection for Synchronous Rectifier Driver. Connect a 0.1µF ceramic capacitor between BST and LXP.                                                                                               |

| 9   | V18   | Output of internal 1.8V regulator. Connect a 1µF capacitor from V18 to GND.                                                                                                                                           |

| 10  | GND   | Ground connection.                                                                                                                                                                                                    |

| 11  | IN    | Supply connection for device. Bypass IN with local 10µF and 0.1µF capacitors at the minimum.                                                                                                                          |

| 12  | INN   | Inverting Converter Input. Connect directly to IN.                                                                                                                                                                    |

| 13  | LXN   | DC-DC Inverting Converter Inductor/Diode Connection.                                                                                                                                                                  |

# **Pin Description (continued)**

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                  |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14  | NAVDD | Negative Source-Driver Output Voltage. Connect a 10µF ceramic capacitor from this pin to GND.                                                                                                                                             |

| 15  | FBN   | Inverter feedback pin. Connect FBN to INN when NAVDD should track AVDD. When the inverting regulator is used independently connect a resistor divider between V18 and NAVDD with its midpoint connected to FBN to set the output voltage. |

| 16  | ENP   | Enable pin for boost converter.                                                                                                                                                                                                           |

### **Functional Diagrams**

#### **Detailed Description**

The MAX25520 is a dual-output power IC that provides symmetrical or asymmetrical positive and negative voltages up to 10.5V and down to -10.5V (±12V for MAX25520ATEC) with an input voltage between 2.65V and 5.5V. It incorporates a fully integrated current-mode boost converter and a current-mode inverter with external rectifier. The device operates at one of two switching frequencies, 420kHz or 2.1MHz. Operation at 2.1MHz permits very compact dual-output power supplies.

The two output voltages can be programmed independently or can be made to track each other. Independent enable pins allow complete flexibility in powering up and down the outputs.

The outputs are protected against overcurrent and undervoltage.

#### Input Voltage Restrictions When Using MAX25520ATEC

When using the MAX25520ATEC with output voltages greater than ±10.5V, a nominal input voltage of 5V should be used.

#### **Power-Up State**

When either of the ENP and ENN pins is taken high, the V18 regulator is turned on and the appropriate output(s) is/are turned on. While both ENN and ENP are low, the device is in low-quiescent-current mode.

If at any time the internal 1.8V regulator is out of range, the device stops operation.

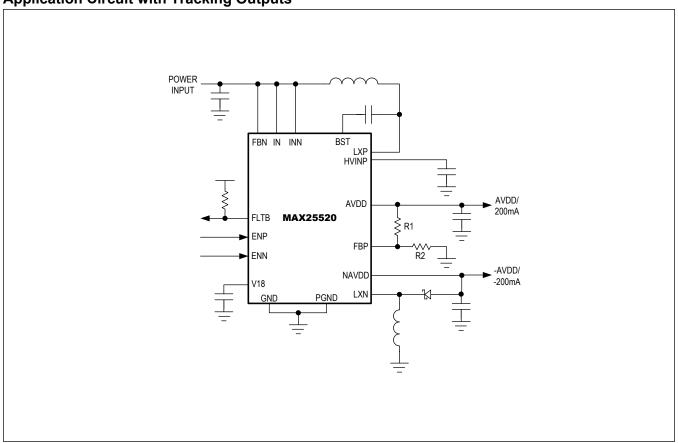

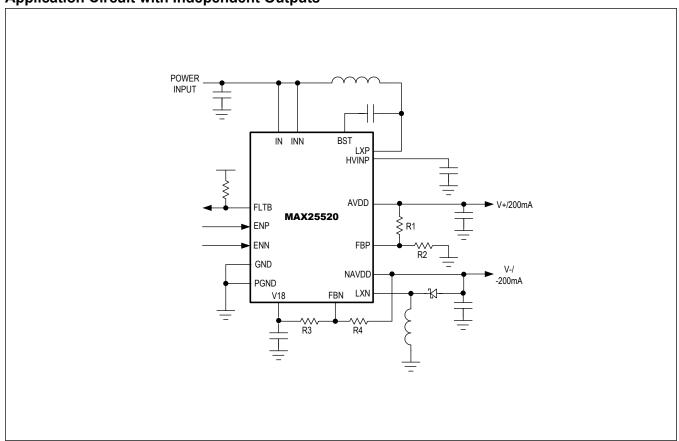

When FBN is connected to IN, the device is in tracking mode and NAVDD is regulated to -AVDD. Otherwise, the AVDD and NAVDD outputs are set independently using the FBP and FBN feedback inputs.

Device operation is shown in Table 1.

**Table 1. Device Operation**

| OPERATION MODE                 | ENP | ENN | HVINP | AVDD | NAVDD | NOTES                                                           |

|--------------------------------|-----|-----|-------|------|-------|-----------------------------------------------------------------|

|                                | 0   | Х   | Off   | Off  | Off   |                                                                 |

| Tracking (FBN connected to IN) | 1   | 0   | On    | On   | Off   |                                                                 |

|                                | 1   | 1   | On    | On   | On    |                                                                 |

|                                | 0   | 0   | Off   | Off  | Off   | Applies also with FBP connected to V18 (default output voltage) |

| Indonondant Outputs            | 0   | 1   | Off   | Off  | On    | , voluge)                                                       |

| Independent Outputs            | 1   | 0   | On    | On   | Off   |                                                                 |

|                                | 1   | 1   | On    | On   | On    |                                                                 |

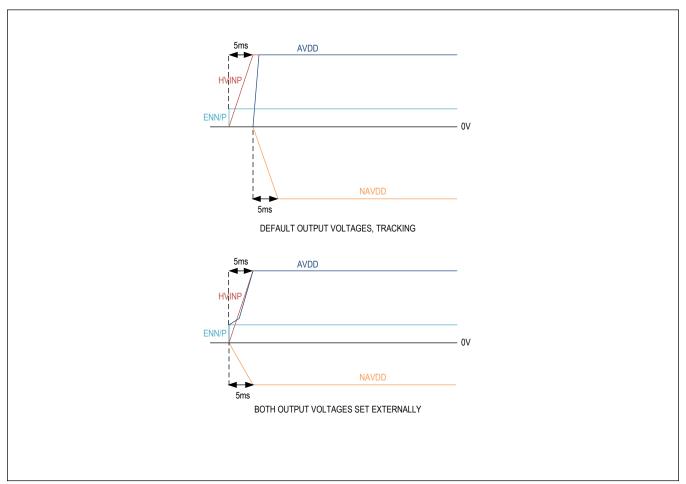

#### **Start-Up Waveforms**

Figure 1. Start-Up Waveforms

#### **Switching Frequency**

The two versions of the device provide switching frequencies of 2.1MHz and 420kHz, respectively. The switching frequency has spread-spectrum applied to improve EMI performance.

#### **AVDD Boost Converter**

The MAX25520 includes a current-mode boost converter with output switch that generates up to +10.5V (+12V for MAX25520ATEC) at up to 200mA. The boost converter's regulation voltage (AVDD) is set by the resistor-divider connected to the FBP pin. FBP is regulated to a nominal voltage of 0.9V.

Alternatively, the default AVDD output voltage (6.8V) can be chosen by connecting FBP to V18. The converter has an internal soft-start which ramps the HVINP voltage up to its final value in 5ms. The boost converter is internally compensated.

#### **NAVDD Inverting Converter**

The inverting buck-boost converter is of the current-mode type and can generate down to -10.5V output voltage (-12V for MAX25520ATEC), delivering up to -200mA. It is internally compensated.

The converter has an internal soft-start that ramps the voltage up to its final value in 5ms. The negative source-driver

## Automotive 2-Channel TFT-LCD Power Supply

supply voltage (NAVDD) is either tightly regulated to -AVDD within ±34mV (when FBN is connected to IN), or its output voltage is set by the resistors connected between V18, FBN, and NAVDD.

#### **Fault Handling**

When a fault is detected, the FLTB pin asserts low. Possible faults are undervoltage on AVDD or NAVDD (when they fall below 85% of their set value), short-circuits on AVDD or NAVDD (when they fall below 40% of their set value), and thermal shutdown.

#### **Undervoltage Faults**

The reaction to undervoltage faults depends on whether the device is in tracking mode or the outputs are set independently.

In tracking mode if an undervoltage is detected for 30ms on either of the outputs, both outputs are switched off and FLTB is asserted low. After 1.9s, a retry is performed in which an attempt is made to re-start both outputs if the enable pins are still high. If the fault is still present, the outputs will be disabled again. If the problem persists, the device will continue to retry every 1.9s unless the enable pins are taken low.

When the outputs are set independently, an undervoltage for 30ms causes the affected output to be turned off and the FLTB pin to assert low. After 1.9s, a retry is performed in which an attempt is made to re-start the affected output if its enable pin is still high. If the fault is still present, the output will be disabled again. If the problem persists, the device will continue to retry every 1.9s unless the corresponding enable pin is taken low.

During retry, the FLTB pin remains asserted low until normal operation is resumed.

#### **Thermal Shutdown**

When the junction temperature reaches 165°C, the device enters thermal shutdown. A thermal shutdown causes both outputs to turn off immediately. When the junction temperature drops by 15°C, the outputs are re-enabled according to the state of the EN\_ pins.

### **Applications Information**

#### **Boost Converter**

#### **Boost Converter Inductor Selection**

Three key inductor parameters must be specified for operation with the device: Inductance value (L), inductor saturation current (I<sub>SAT</sub>), and DC resistance (R<sub>DC</sub>). Select the inductor value using <u>Table 2</u>.

**Table 2. Boost Inductor Selection**

| SWITCHING FREQUENCY | OUTPUT CURRENT < 100mA | OUTPUT CURRENT > 100mA |  |  |

|---------------------|------------------------|------------------------|--|--|

| 420kHz              | 15μH                   | 10μH                   |  |  |

| 2.1MHz              | 3.3µH                  | 2.2µH                  |  |  |

The inductor's saturation rating must exceed the maximum current limit of 2.3A.

#### **Boost Output Filter Capacitor Selection**

The primary criterion for selecting the output filter capacitor is low effective series resistance (ESR). The product of the peak inductor current and the output filter capacitor's ESR determine the amplitude of the high-frequency ripple seen on the output voltage. For stability, the boost output-filter capacitor should have a value of 22µF or greater at 420kHz and 10µF at 2.1MHz.

To avoid a large drop on HVINP when AVDD is enabled, the capacitance on the HVINP node should be at least 3 times larger than that on AVDD.

#### **Setting the AVDD Voltage**

The AVDD output voltage can be set to its default value by connecting FBP to V18. Alternatively, the voltage is set by connecting a resistive divider from AVDD to GND with is midpoint connected to FBP. Choose the value of the resistor connected from AVDD to FBP (R1) using the following equation:

$$R1 = \frac{R2 \times (V_{\text{AVDD}} - 0.9)}{0.9}$$

where R2 is the resistor connected from FBP to ground and VAVDD is the desired output voltage.

#### **NAVDD Inverting Regulator**

#### **NAVDD Regulator Inductor Selection**

The inductor value for the NAVDD regulator can be selected using Table 3.

#### **Table 3. NAVDD Inductor Selection**

| SWITCHING FREQUENCY | OUTPUT CURRENT < 100mA | OUTPUT CURRENT > 100mA |  |  |

|---------------------|------------------------|------------------------|--|--|

| 420kHz              | 15μH                   | 10μH                   |  |  |

| 2.1MHz              | 3.3µH                  | 2.2µH                  |  |  |

The inductor's saturation current rating must exceed the maximum current limit of 2.25A.

#### **NAVDD External Diode Selection**

Select a diode with a peak current rating of at least the LXN current limit (2.25A) for use with the NEG output. The diode breakdown-voltage rating should exceed the sum of the maximum INN voltage and the absolute value of the NAVDD voltage. A Schottky diode improves the overall efficiency of the converter.

#### **NAVDD Output Capacitor Selection**

The primary criteria for selecting the output filter capacitor are low ESR and capacitance value, as the NAVDD capacitor provides the load current when the internal switch is on. The voltage ripple on the NAVDD output has two components:

#### MAX25520

# Automotive 2-Channel TFT-LCD Power Supply

- Ripple due to ESR which is the product of the peak inductor current and the output filter capacitor's ESR

- Ripple due to bulk capacitance.

For stability, the NEG output capacitor should have a value of 10µF or greater.

#### **Setting the NAVDD Voltage**

When FBN is connected to IN/INN, the NAVDD voltage mirrors the regulated voltage on AVDD.

If a voltage other than -V<sub>AVDD</sub> is required, connect a resistor-divider from V18 to NAVDD with its midpoint connected to FBN. Select the resistor values using the following equation:

$$R4 = -\frac{V_{\text{NAVDD}} \times R3}{1.8}$$

where R4 is the resistor connected between FBN and NAVDD, R3 is the resistor from V18 to FBN, and  $V_{NAVDD}$  is the desired output voltage. Use a value greater than  $4.7k\Omega$  for R3.

#### **Layout Considerations**

When designing a printed circuit board for the MAX25520, minimize the area of the LXP and LXN nodes and the area of the switching current loop. Follow these guidelines for the rest of the layout:

- 1. Separate power and analog grounds on the board and connect them together at a single point.

- 2. Connect any feedback resistor-dividers to the analog or "quiet" ground, along with the V18 and IN/INN capacitors. Feedback resistors should be placed close to their associated pins to avoid noise pickup.

- 3. Place decoupling capacitors as close as possible to their respective pins.

- 4. Keep high-current paths as short and wide as possible.

- 5. Route high-speed switching nodes (i.e., LXP, LXN) away from sensitive analog nodes (i.e., FBP, FBN, etc.).

# **Typical Application Circuits**

### **Application Circuit with Tracking Outputs**

### **Typical Application Circuits (continued)**

### **Application Circuit with Independent Outputs**

### **Ordering Information**

| PART              | TEMPERATURE RANGE | PIN-PACKAGE  | SWITCHING FREQUENCY |

|-------------------|-------------------|--------------|---------------------|

| MAX25520ATEA/V+*  | -40 to +125°C     | 16 TQFN-EP   | 420kHz              |

| MAX25520ATEB/V+   | -40 to +125°C     | 16 TQFN-EP   | 2.1MHz              |

| MAX25520ATEA/VY+* | -40 to +125°C     | 16 SWTQFN-EP | 420kHz              |

| MAX25520ATEB/VY+  | -40 to +125°C     | 16 SWTQFN-EP | 2.1MHz              |

| MAX25520ATEC/V+   | -40 to +125°C     | 16 TQFN-EP   | 2.1MHz              |

<sup>\*</sup> Future product—contact factory for availability.

N denotes an automotive qualified part.

<sup>+</sup> Denotes a lead(Pb)-free/RoHS-compliant package.

T Denotes tape-and-reel.

# Automotive 2-Channel TFT-LCD Power Supply

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                | PAGES<br>CHANGED |

|--------------------|------------------|------------------------------------------------------------|------------------|

| 0                  | 1/21             | Initial release                                            | _                |

| 1                  | 3/21             | Added "C" version, updated Absolute Maximum Ratings        | 1, 3, 12, 13, 18 |

| 2                  | 9/21             | Updated Absolute Maximum Ratings, Applications Information | 3, 14            |

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for LCD Drivers category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below:

PCF8576CU/2/F2,026 LC75821WHS-E LC75827WS-E LC75829PE-H LC75836WH-E LC75874WHS-SH-E LC75890W-NH

LC75897PW-E CD4056BE LC75829PW-H LC79430KNE-E LC79431KNE-E FAN7317BMX LC75839PW-H LC75884W-E LC75814VSTLM-E S1D15721D01B000 BU97501KV-E2 BU9795AFV-E2 BU9799KV-E2 BU9728AKV-E2 TPS65132B2YFFR R1293K241A-E2

BU9795AFV-LBE2 PCA8546BTT/AJ TPS65132A0YFFR BU9795AKV-E2 GN1622B 34801000 BU97510CKV-ME2 BU97520AKV-ME2

BU97931FV-E2 BU9796AFS-E2 HG1621BM/TR HT1623 HT1621BRQZ44 AIP1721 AIP1723 ICL7106CM44Z JSM1621B BL55070

AY0438T-I/L HT1621BQ HT1621BRQZ ICL7129ACPL+ MAX1606EUA+ AY0438-I/P AY0438-I/P AY0438/P