# 25V<sub>IN</sub>, 3A<sub>OUT</sub> to 6A<sub>OUT</sub>, USB-C Buck-Boost Charger with Integrated FETs for 2S/3S Li-Ion Batteries

### **General Description**

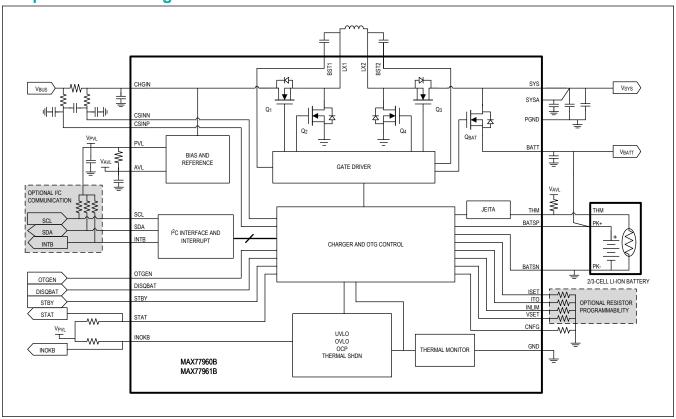

The MAX77960B/MAX77961B are high-performance wide-input 3A (MAX77960B)/6A (MAX77961B) buckboost chargers with Smart Power Selector™ and operate as a reverse buck converter without an additional inductor, allowing the ICs to power USB on-the-go (OTG) accessories. The devices integrate low-loss power switches and provide high efficiency, low heat, and fast battery charging in a small solution size. The reverse buck has true load disconnect and is protected by an adjustable output current limit. The devices are highly flexible and programmable through I²C configuration or autonomously through resistor configuration.

The battery charger includes the Smart Power Selector to accommodate a wide range of battery sizes and system loads. The Smart Power Selector allows the system to start up smoothly when an input source is available even when the battery is deeply discharged (dead battery) or missing. For battery safety/authentication reasons, the ICs can be configured to keep charging disabled, and allow the DC-DC to switch and regulate the SYS voltage. The system processor can later enable charging using I<sup>2</sup>C commands as appropriate. Alternatively, the ICs can be configured to automatically start charging.

### **Applications**

- USB Type-C Powered Wide-Input Charging Applications

- 2- and 3-Cell Battery-Powered Devices

- Smartphones, Tablets, and 2-in-1 Laptops

- Medical Devices, Health and Fitness Monitors

- Digital Still, Video, and Action Cameras

- Handheld Computers and Terminals

- Handheld Radios

- Power Tools

- Drones

- Battery Backup

- Wireless Speakers

#### **Benefits and Features**

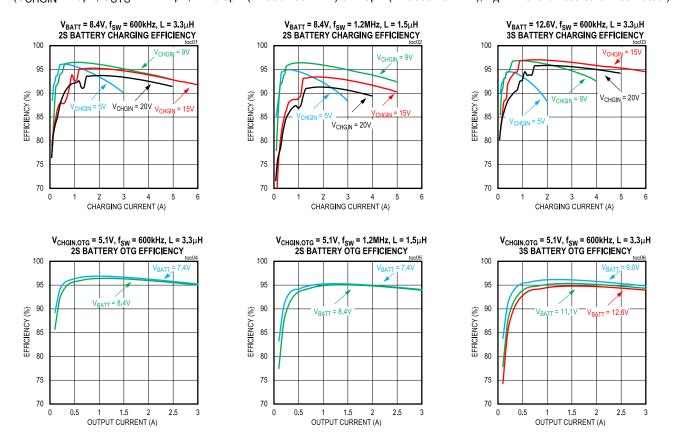

- 3.5V to 25.4V Input Operating Range, 30V<sub>DC</sub> Withstand

- 97% Peak Efficiency for 2S Battery at 9V<sub>IN</sub>/7.4V<sub>OUT</sub>/1.5A<sub>OUT</sub>

- 97% Peak Efficiency for 3S Battery at 15V<sub>IN</sub>/12.6V<sub>OUT</sub>/2A<sub>OUT</sub>

- MAX77960B

- 100mA to 3.15A Programmable Input Current Limit

- 100mA to 3A Programmable Constant Current Charge

- MAX77961B

- 100mA to 6.3A Programmable Input Current Limit

- 100mA to 6A Programmable Constant Current Charge

- Remote Differential Voltage Sensing

- 600kHz or 1.2MHz Switching Frequency Options

- System Instant On with Smart Power Selector Power Path

- Charge Safety Timer

- Die Temperature Regulation with Thermal Foldback

- Input Power Management with Adaptive Input Current Limit (AICL) and Input Voltage Regulation

- 10mΩ BATT to SYS Switch, Up to 10A Overcurrent Threshold

- Reverse Buck Mode 5.1V/3A to Support USB OTG

- JEITA Compliant with NTC Thermistor Monitor

- I<sup>2</sup>C or Resistor Programmable

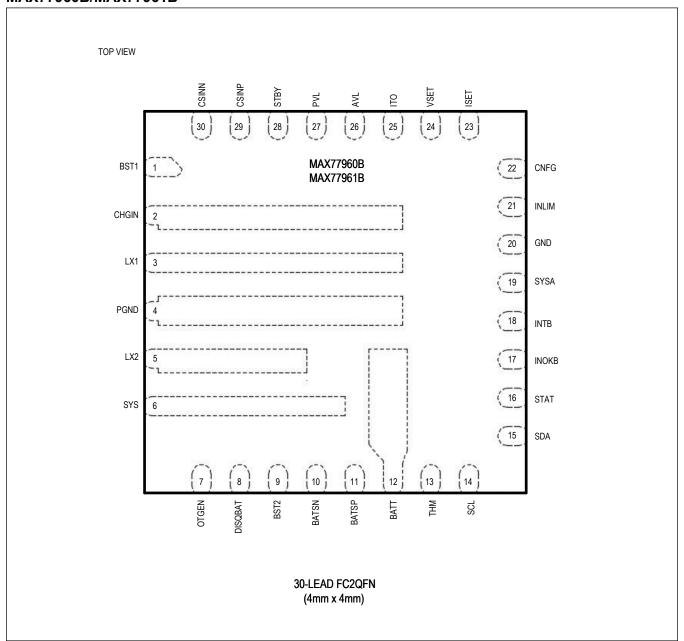

- 4mm x 4mm, 30-Lead FC2QFN

Ordering Information appears at end of data sheet.

# **Simplified Block Diagram**

# 25V<sub>IN</sub>, 3A<sub>OUT</sub> to 6A<sub>OUT</sub>, USB-C Buck-Boost Charger with Integrated FETs for 2S/3S Li-Ion Batteries

#### **TABLE OF CONTENTS**

| General Description                                              | 1  |

|------------------------------------------------------------------|----|

| Applications                                                     | 1  |

| Benefits and Features                                            | 1  |

| Simplified Block Diagram                                         | 2  |

| Absolute Maximum Ratings                                         | 8  |

| Package Information                                              | 8  |

| 30-Lead FC2QFN                                                   | 8  |

| Electrical Characteristics                                       | 10 |

| Typical Operating Characteristics                                | 19 |

| Pin Configuration                                                | 20 |

| MAX77960B/MAX77961B                                              | 20 |

| Pin Description                                                  | 20 |

| Detailed Description                                             | 23 |

| Charger Configuration                                            | 23 |

| Device Configuration Input (CNFG)                                |    |

| CHGIN Standby Input (STBY)                                       |    |

| Battery to SYS Q <sub>BAT</sub> Disable Input (DISQBAT)          | 23 |

| Q <sub>BAT</sub> and DC-DC Control—Configuration Table           | 23 |

| Thermistor Input (THM)                                           | 24 |

| Autonomous Charging                                              | 25 |

| Charger Input Current Limit Setting Input (INLIM)                | 26 |

| Fast-Charge Current Setting Input (ISET)                         | 26 |

| Top-Off Current Setting Input (ITO)                              | 27 |

| Charge Termination Voltage Setting Input (VSET)                  | 27 |

| Switch Mode Charger                                              | 28 |

| Smart Power Selector (SPS)                                       |    |

| CHGIN Regulation Voltage                                         | 29 |

| SYS Regulation Voltage                                           | 29 |

| Power States                                                     | 30 |

| Powering Up with the Charger Disabled by Default                 |    |

| Input Validation                                                 | 31 |

| Adaptive Input Current Limit (AICL) and Input Voltage Regulation | 31 |

| Input Self-Discharge                                             |    |

| System Self-Discharge with No Power                              | 31 |

| Charger States                                                   |    |

| No Input Power or Charger Disabled Idle State                    |    |

| Precharge State                                                  | 34 |

| Trickle Charge State                                             |    |

| Fast-Charge Constant Current State                               | 34 |

# TABLE OF CONTENTS (CONTINUED)

| Fast-Charge Constant Voltage State                | 35 |

|---------------------------------------------------|----|

| Top-Off State                                     | 35 |

| Done State                                        | 36 |

| Timer Fault State                                 | 36 |

| Watchdog Timer Suspend State                      | 36 |

| Thermal Shutdown State                            | 36 |

| Thermal Management                                | 37 |

| Thermal Foldback                                  | 37 |

| JEITA Compliance                                  | 38 |

| Thermal Shutdown                                  | 39 |

| Factory Ship Mode                                 | 39 |

| Minimum System Voltage                            | 39 |

| Battery Differential Voltage Sense (BATSP, BATSN) | 39 |

| Battery Overcurrent Alert                         | 39 |

| Charger Interrupt Debounce Time                   | 40 |

| Input Power-OK/OTG Power-OK Output (INOKB)        | 40 |

| Charge Status Output (STAT)                       | 40 |

| Reverse Buck Mode (OTG)                           | 41 |

| OTG Enable (OTGEN)                                | 41 |

| Analog Low-Noise Power Input (AVL)                | 42 |

| Low-Side Gate Driver Power Supply (PVL)           | 42 |

| System Faults                                     | 42 |

| Interrupt Output (INTB)                           | 42 |

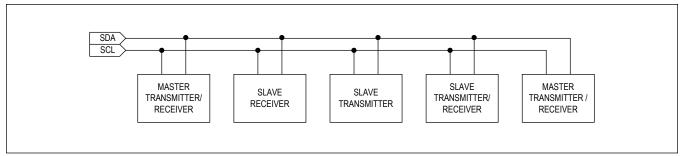

| I <sup>2</sup> C Serial Interface                 | 42 |

| System Configuration                              | 42 |

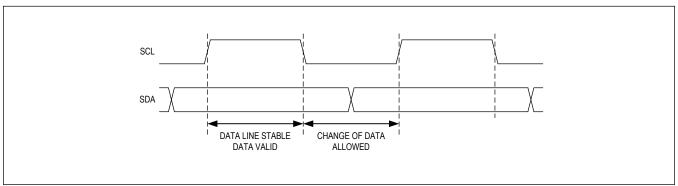

| Bit Transfer                                      | 43 |

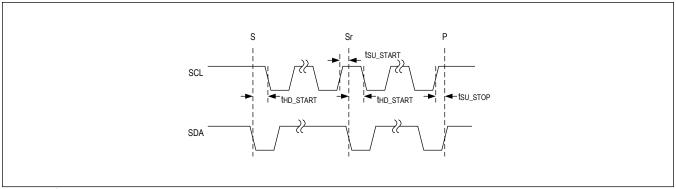

| START and STOP Conditions                         | 43 |

| Acknowledge                                       | 44 |

| Slave Address                                     | 44 |

| Clock Stretching                                  | 44 |

| General Call Address                              | 44 |

| Communication Speed                               | 44 |

| Communication Protocols                           | 45 |

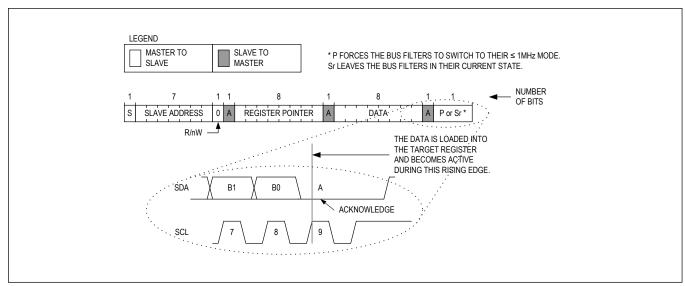

| Writing to a Single Register                      | 45 |

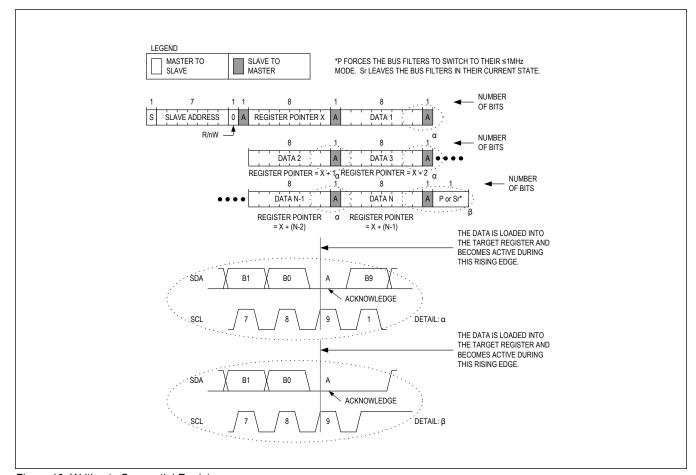

| Writing to Sequential Registers                   | 46 |

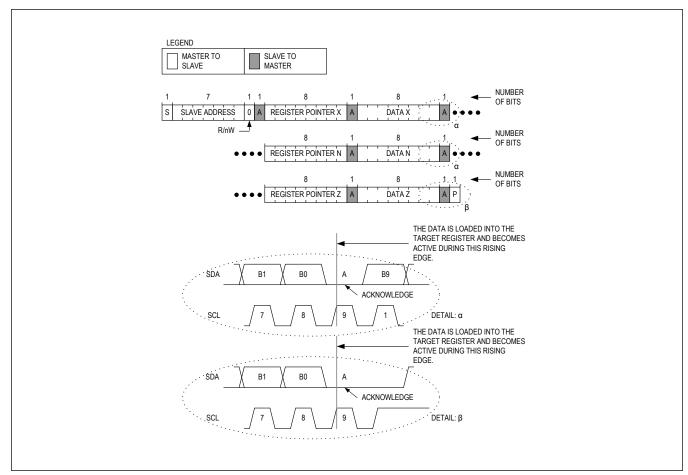

| Writing Multiple Bytes using Register-Data Pairs  | 47 |

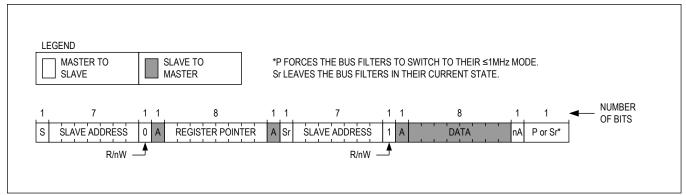

| Reading from a Single Register                    | 48 |

| Reading from Sequential Registers                 | 49 |

| Register Man                                      | 50 |

# 25V<sub>IN</sub>, 3A<sub>OUT</sub> to 6A<sub>OUT</sub>, USB-C Buck-Boost Charger with Integrated FETs for 2S/3S Li-Ion Batteries

### TABLE OF CONTENTS (CONTINUED)

| FUNC                                                               | <br> | 50 |

|--------------------------------------------------------------------|------|----|

| Register Details                                                   | <br> | 51 |

| Applications Information                                           | <br> | 73 |

| Inductor Selection                                                 | <br> | 73 |

| CHGIN Capacitor Selection                                          | <br> | 73 |

| SYS Capacitor Selection                                            | <br> | 74 |

| Battery Insertion Protection                                       | <br> | 74 |

| PCB Layout Guidelines                                              | <br> | 76 |

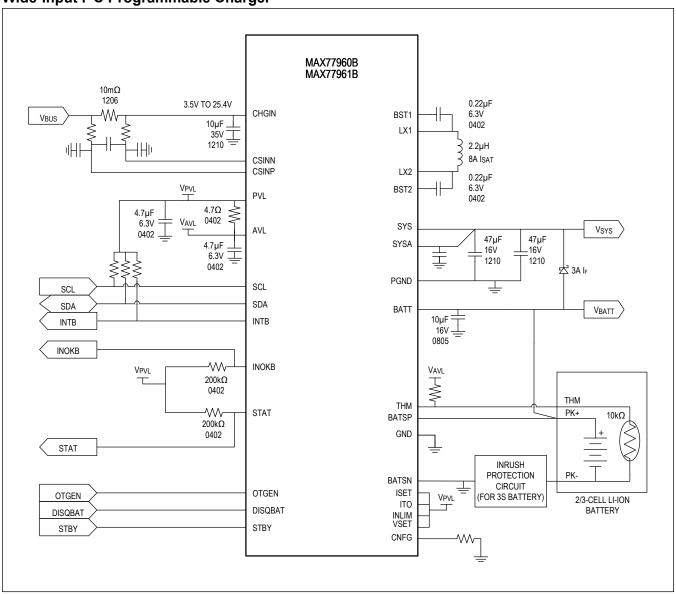

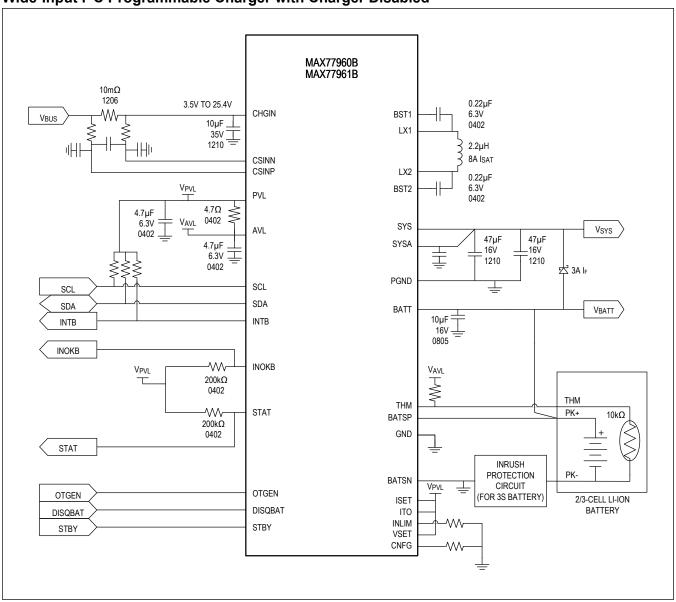

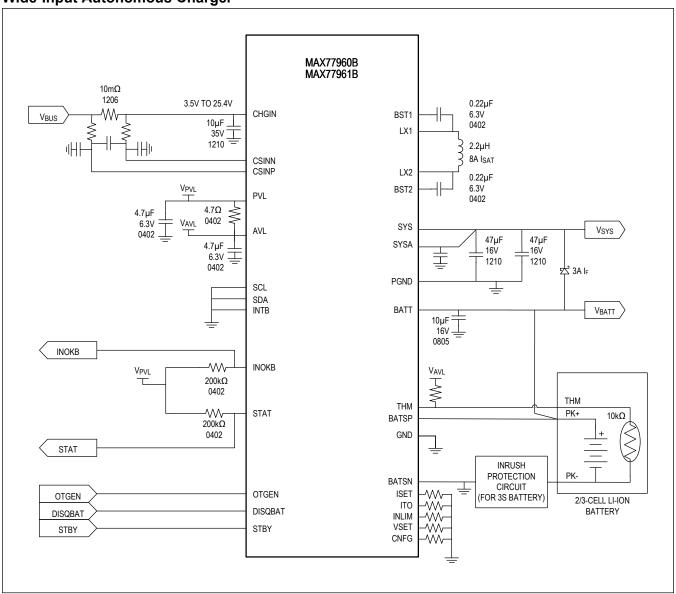

| Typical Application Circuits                                       | <br> | 78 |

| Wide-Input I <sup>2</sup> C Programmable Charger                   | <br> | 78 |

| Wide-Input I <sup>2</sup> C Programmable Charger with Charger Disa |      |    |

| Wide-Input Autonomous Charger                                      | <br> | 80 |

| Ordering Information                                               | <br> | 81 |

| Revision History                                                   |      |    |

# 25V<sub>IN</sub>, 3A<sub>OUT</sub> to 6A<sub>OUT</sub>, USB-C Buck-Boost Charger with Integrated FETs for 2S/3S Li-Ion Batteries

#### LIST OF FIGURES

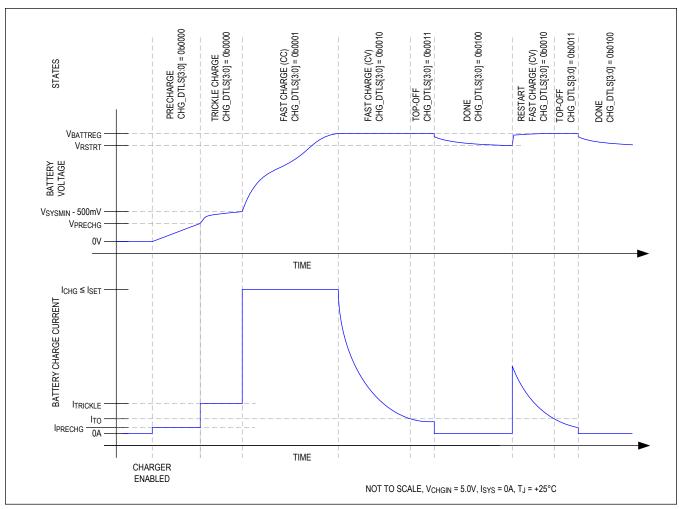

| Figure 1. Li Battery Charge Profile                                                        | 32 |

|--------------------------------------------------------------------------------------------|----|

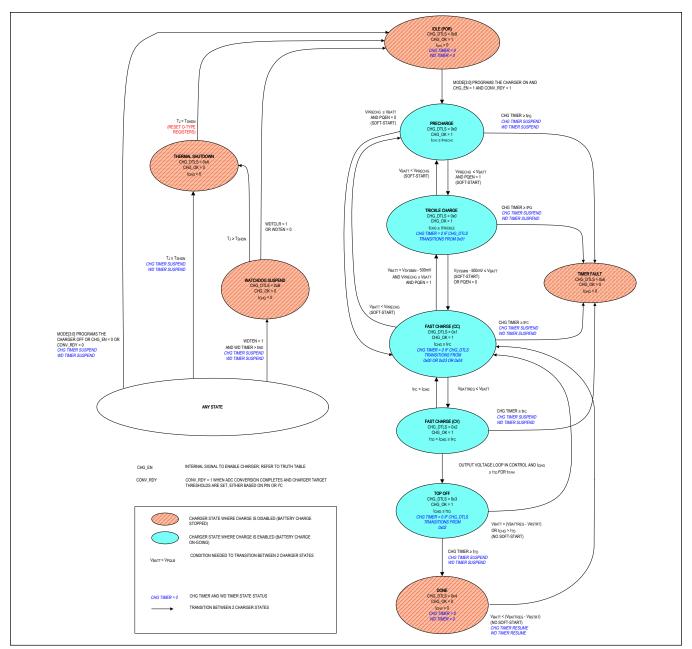

| Figure 2. Charger State Diagram                                                            | 33 |

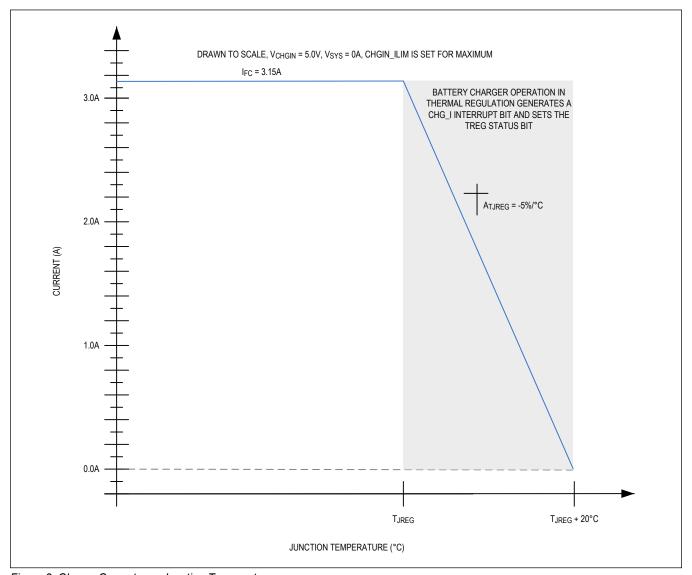

| Figure 3. Charge Currents vs. Junction Temperature                                         | 37 |

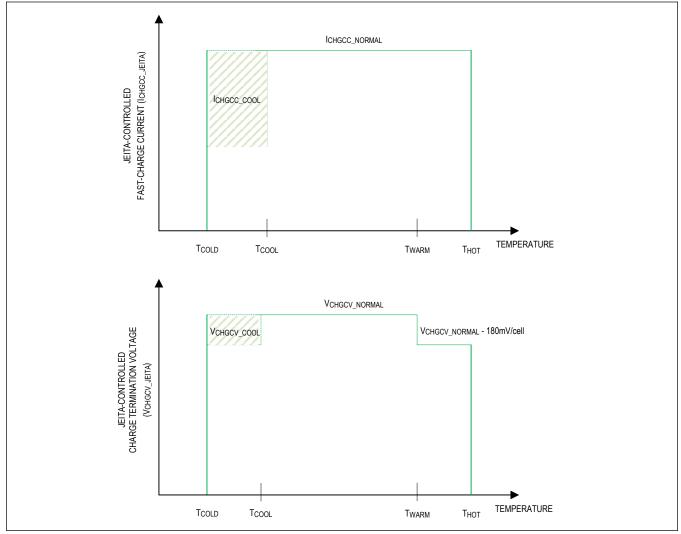

| Figure 4. JEITA Compliance                                                                 | 38 |

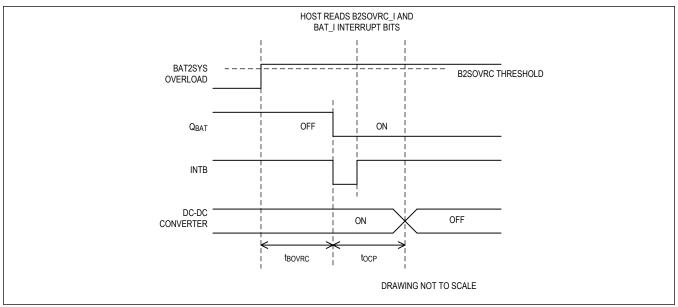

| Figure 5. B2SOVRC                                                                          | 40 |

| Figure 6. Functional Logic Diagram for Communications Controller                           | 43 |

| Figure 7. I <sup>2</sup> C Bit Transfer                                                    | 43 |

| Figure 8. I <sup>2</sup> C Start Stop                                                      | 44 |

| Figure 9. Writing to a Single Register                                                     | 45 |

| Figure 10. Writing to Sequential Registers                                                 | 46 |

| Figure 11. Writing to Multiple Registers with "Multiple Byte Register-Data Pairs" Protocol | 47 |

| Figure 12. Reading from a Single Register                                                  | 48 |

| Figure 13. Reading from Sequential Registers                                               | 49 |

| Figure 14. Battery Insertion Protection with 2S Battery                                    | 75 |

| Figure 15. Battery Insertion Protection with 3S Battery                                    | 76 |

| Figure 16. PCB Layout Example                                                              | 77 |

# 25V<sub>IN</sub>, 3A<sub>OUT</sub> to 6A<sub>OUT</sub>, USB-C Buck-Boost Charger with Integrated FETs for 2S/3S Li-Ion Batteries

### LIST OF TABLES

| Table 1. CNFG Program Options Lookup Table                                                         | . 23 |

|----------------------------------------------------------------------------------------------------|------|

| Table 2. Q <sub>BAT</sub> and DC-DC Control Configuration Table                                    | . 23 |

| Table 3. Trip Temperatures for Different Thermistors                                               | . 25 |

| Table 4. INLIM, ITO, ISET, and VSET Pin Connections for Autonomous Charging                        | . 26 |

| Table 5. INLIM Program Options Lookup Table                                                        | . 26 |

| Table 6. ISET Program Options Lookup Table                                                         | . 26 |

| Table 7. ITO Program Options Lookup Table                                                          | . 27 |

| Table 8. VSET Program Options Lookup Table                                                         | . 28 |

| Table 9. List of Charger Interrupt Debounce Time                                                   | . 40 |

| Table 10. Charge Status Indicator by STAT                                                          | . 41 |

| Table 11. Recommended Inductance for Combinations of Switching Frequency and Maximum Nominal CHGIN | 70   |

| Voltage                                                                                            |      |

| Table 12. Suggested Inductors                                                                      | . 73 |

| Table 13. Suggested CHGIN Capacitors                                                               | . 73 |

| Table 14. Suggested SYS Capacitors                                                                 | . 74 |

# 25V<sub>IN</sub>, 3A<sub>OUT</sub> to 6A<sub>OUT</sub>, USB-C Buck-Boost Charger with Integrated FETs for 2S/3S Li-Ion Batteries

### **Absolute Maximum Ratings**

| CHGIN to GND0.3V to +30.0V CSINP, CSINN to CHGIN0.3V to +0.3V | PVL, AVL, ISET, VSET, INLIM, ITO, CNFG, THM to GND0.3V to +2.2V          |

|---------------------------------------------------------------|--------------------------------------------------------------------------|

| LX1 to PGND0.3V to +30.0V                                     | AVL to PVL0.3V to +0.3V                                                  |

| LX2 to PGND0.3V to +16.0V                                     | DISQBAT, OTGEN, STBY, STAT, INOKB, INTB, SDA, SCL to                     |

| BST1 to PVL0.3V to +30.0V                                     | GND0.3V to +6.0V                                                         |

| BST2 to PVL0.3V to +16.0V                                     | CHGIN Continuous Current 6.5A <sub>RMS</sub>                             |

| BST_ to LX0.3V to +2.2V                                       | LX_, PGND Continuous Current 6.5A <sub>RMS</sub>                         |

| SYS, SYSA to GND0.3V to +16.0V                                | SYS, BATT Continuous Current 10.0A <sub>RMS</sub>                        |

| BATT to GND0.3V to +16.0V                                     | Continuous Power Dissipation (Multilayer Board) ( $T_A = +70^{\circ}C$ , |

| SYS to BATT0.3V to +16.0V                                     | derate 40.37mW/°C above +70°C.)3229.71mW                                 |

| BATSP to GND0.3V to V <sub>BATT</sub> + 0.3V                  | Operating Temperature Range40°C to +85°C                                 |

| BATSN, PGND to GND0.3V to +0.3V                               | Storage Temperature Range65°C to +150°C                                  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

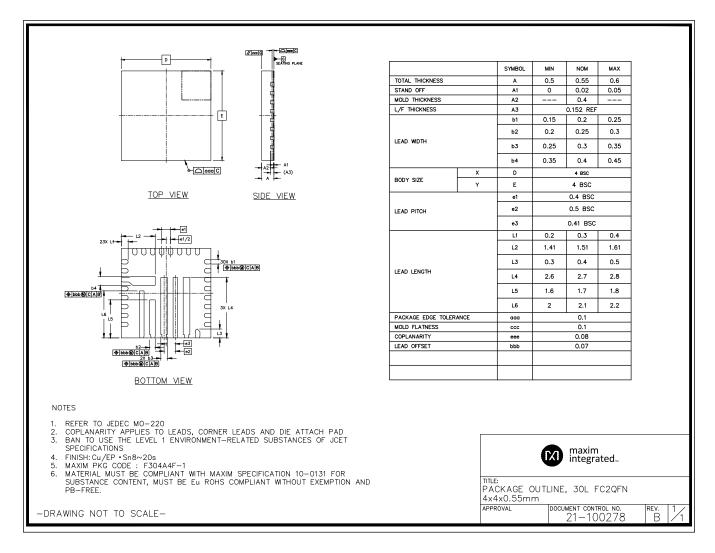

### **Package Information**

#### 30-Lead FC2QFN

| Package Code                                          | F304A4F+1        |  |  |

|-------------------------------------------------------|------------------|--|--|

| Outline Number                                        | <u>21-100278</u> |  |  |

| Land Pattern Number                                   | 90-100100        |  |  |

| Thermal Resistance, Four-Layer Board:                 |                  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                | 24.77°C/W        |  |  |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | 1.67°C/W         |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{SYS} = 7.6V, V_{BATT} = 7.6V, V_{CHGIN} = 9V, T_A = -40^{\circ}C$  to +85°C.  $T_A = +25^{\circ}C$  (typ). Limits are production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                          | SYMBOL                   | CONDITIONS                                                                                                                                                                           | MIN                | TYP   | MAX                | UNITS |

|----------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------|--------------------|-------|

| GENERAL ELECTRICAL                                 | CHARACTERIS              | TICS                                                                                                                                                                                 |                    |       |                    |       |

| CHGIN Voltage Range                                | V <sub>CHGIN</sub>       | Operating voltage                                                                                                                                                                    | 3.5                |       | 25.4               | V     |

| CHGIN Overvoltage<br>Threshold                     | V <sub>CHGIN_OVLO</sub>  | V <sub>CHGIN</sub> rising, 365mV hysteresis                                                                                                                                          | 25.4               | 26.05 | 26.7               | V     |

| CHGIN Overvoltage                                  | t <sub>D_CHGIN_OVL</sub> | V <sub>CHGIN</sub> rising, 100mV overdrive                                                                                                                                           |                    | 10    |                    | μs    |

| Delay                                              | 0                        | V <sub>CHGIN</sub> falling, 100mV overdrive                                                                                                                                          |                    | 7     |                    | ms    |

| CHGIN Undervoltage<br>Threshold                    | V <sub>CHGIN_UVLO</sub>  | V <sub>CHGIN</sub> rising, 20% hysteresis                                                                                                                                            | 3.43               | 3.5   | 3.57               | V     |

|                                                    |                          | V <sub>CHGIN</sub> = 2.4V, the input is undervoltage and R <sub>INSD</sub> is the only loading                                                                                       |                    | 0.075 |                    |       |

|                                                    | I <sub>CHGIN</sub>       | V <sub>CHGIN</sub> = 9.0V, charger disabled                                                                                                                                          |                    | 0.17  | 0.5                |       |

| CHGIN Quiescent<br>Current (I <sub>SYS</sub> = 0A) | CHGIN                    | V <sub>CHGIN</sub> = 9.0V, charger enabled, V <sub>SYS</sub> = V <sub>BATT</sub> = 8.7V (2S configuration), no switching                                                             |                    | 2.7   | 4                  | mA    |

|                                                    | ICHGIN_STBY              | MODE[3:0] = 0x0 (DC-DC off), STBY = H<br>or STBY_EN = 1, V <sub>CHGIN</sub> = 5V                                                                                                     |                    |       | 1                  |       |

| BATT Quiescent Current (I <sub>SYS</sub> = 0A)     | I <sub>SHDN</sub>        | FSHIP_MODE = 1 or DISQBAT = high,<br>V <sub>CHGIN</sub> = 0V, I <sub>SYS</sub> = 0A, V <sub>BATT</sub> = 13.5V                                                                       |                    | 2.3   | 5.0                |       |

|                                                    |                          | DISQBAT = low, I <sup>2</sup> C enabled, V <sub>CHGIN</sub> = 0V, I <sub>SYS</sub> = 0A, V <sub>BATT</sub> = 13.5V                                                                   |                    | 100   | 200                |       |

|                                                    | Іватт                    | V <sub>SYS</sub> = 7.6V, V <sub>BATT</sub> = 0V, charger disabled, T <sub>A</sub> = +25°C                                                                                            |                    | 0.01  | 10                 | μA    |

|                                                    |                          | V <sub>SYS</sub> = 7.6V, V <sub>BATT</sub> = 0V, charger disabled, T <sub>A</sub> = +85°C                                                                                            |                    | 10    |                    |       |

|                                                    |                          | V <sub>CHGIN</sub> = 9V, V <sub>BATT</sub> = 8.4V, Q <sub>BAT</sub> is off, battery overcurrent protection disabled, charger is enabled but in its done mode, T <sub>A</sub> = +25°C |                    | 57    | 65                 | μ     |

|                                                    | <sup>I</sup> BATTDN      | V <sub>CHGIN</sub> = 9V, V <sub>BATT</sub> = 8.4V, Q <sub>BAT</sub> is off, battery overcurrent protection disabled, charger is enabled but in its done mode, T <sub>A</sub> = +85°C |                    | 57    |                    |       |

| SYS Operating Voltage                              | V <sub>SYS</sub>         | Guaranteed by V <sub>SYSUVLO</sub> and V <sub>SYSOVLO</sub>                                                                                                                          | SYSUVL<br>O rising |       | SYSOVL<br>O rising | V     |

| SYS Undervoltage<br>Lockout Threshold              | V <sub>SYSUVLO</sub>     | V <sub>SYS</sub> falling, 530mV hysteresis                                                                                                                                           | 3.95               | 4.1   | 4.25               | V     |

| SYS Overvoltage                                    | V                        | V <sub>SYS</sub> rising, 430mV hysteresis, 2S battery                                                                                                                                | 10.65              | 10.9  | 11.15              | V     |

| Lockout Threshold                                  | Vsysovlo                 | V <sub>SYS</sub> rising, 267mV hysteresis, 3S battery                                                                                                                                | 13.75              | 14.1  | 14.45              |       |

| PVL Output Voltage                                 | $V_{PVL}$                |                                                                                                                                                                                      | 1.7                | 1.8   | 1.9                | V     |

| Thermal Shutdown<br>Threshold                      | T <sub>SHDN</sub>        | T <sub>J</sub> rising                                                                                                                                                                |                    | 165   |                    | °C    |

| Thermal Shutdown<br>Hysteresis                     |                          |                                                                                                                                                                                      |                    | 15    |                    | °C    |

### **Electrical Characteristics (continued)**

$(V_{SYS} = 7.6V, V_{BATT} = 7.6V, V_{CHGIN} = 9V, T_A = -40^{\circ}C$  to  $+85^{\circ}C$ .  $T_A = +25^{\circ}C$  (typ). Limits are production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                              | SYMBOL                   | CONDITIONS                                                                                                                                                                                           | MIN  | TYP  | MAX   | UNITS   |

|----------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|---------|

| CHGIN Self-Discharge Resistance        | R <sub>INSD</sub>        | V <sub>CHGIN</sub> = 3V                                                                                                                                                                              |      | 44   |       | kΩ      |

| BATT Self-Discharge<br>Resistance      | R <sub>BATSD</sub>       | V <sub>CHGIN</sub> = 9V, V <sub>SYS</sub> = V <sub>BATT</sub> = 5V                                                                                                                                   |      | 600  |       | Ω       |

| SYS Self-Discharge<br>Resistance       | R <sub>SYSSD</sub>       | V <sub>CHGIN</sub> = 9V, V <sub>SYS</sub> = V <sub>BATT</sub> = 5V                                                                                                                                   |      | 600  |       | Ω       |

| Self-Discharge Latch<br>Time           |                          |                                                                                                                                                                                                      |      | 300  |       | ms      |

| SWITCH MODE CHARG                      | ER / CHARGER             |                                                                                                                                                                                                      |      |      |       |         |

| BATT Regulation<br>Voltage Range       | V <sub>BATTREG</sub>     | Programmable from 8.0V to 9.26V (2S battery) and 12.0V to 13.05V (3S battery), production tested at 8V, 8.38V, 8.8V and 9.26V only (2S battery) and 12V, 12.57V, 13.2V, and 13.89V only (3S battery) | 8.00 |      | 13.05 | V       |

| DATT Develope                          |                          | 8.8V or 13.2V settings, T <sub>A</sub> = +25°C                                                                                                                                                       | -0.9 | -0.3 | +0.3  |         |

| BATT Regulation<br>Voltage Accuracy    |                          | 8.8V or 13.2V settings, T <sub>A</sub> = 0°C to +85°C (Note 1)                                                                                                                                       | -1   | -0.3 | +0.5  | %       |

| BATT Overvoltage<br>Lockout Threshold  | V <sub>BATTOVLO</sub>    | V <sub>BATT</sub> rising above V <sub>BATTREG</sub> , 2% hysteresis                                                                                                                                  | 75   | 240  | 375   | mV/cell |

| BATT Undervoltage<br>Lockout Threshold | V <sub>BATTUVLO</sub>    | V <sub>BATT</sub> rising, 100mV hysteresis                                                                                                                                                           | 2.0  | 2.5  | 3.0   | V       |

| Fast-Charge Current                    | te<br>10<br>arge Current | MAX77960B; 100mA to 3A; production tested at 100mA, 200mA, 500mA, 1000mA, 1500mA, 2000mA, and 3000mA settings                                                                                        | 0.10 |      | 3     |         |

| Program Range                          | IFC                      | MAX77961B; 100mA to 6A; production tested at 100mA, 200mA, 500mA, 1000mA, 1500mA, 2000mA, 3000mA, 3500mA, and 3800mA settings                                                                        | 0.10 |      | 6     | A       |

|                                        |                          | T <sub>A</sub> = +25°C, V <sub>BATT</sub> > V <sub>SYSMIN</sub> , programmed for 100mA                                                                                                               | 80   | 100  | 120   |         |

|                                        |                          | T <sub>A</sub> = +25°C, V <sub>BATT</sub> > V <sub>SYSMIN</sub> , programmed for 200mA                                                                                                               | 180  | 200  | 220   |         |

|                                        |                          | T <sub>A</sub> = +25°C, V <sub>BATT</sub> > V <sub>SYSMIN</sub> , programmed for 500mA                                                                                                               | 481  | 500  | 519   |         |

| Fast-Charge Current<br>Accuracy        |                          | T <sub>A</sub> = +25°C, V <sub>BATT</sub> > V <sub>SYSMIN</sub> , programmed for 1000mA                                                                                                              | 962  | 1000 | 1038  | m ^     |

|                                        |                          | T <sub>A</sub> = +25°C, V <sub>BATT</sub> > V <sub>SYSMIN</sub> , programmed for 2000mA                                                                                                              | 1925 | 2000 | 2075  | - mA    |

|                                        |                          | T <sub>A</sub> = +25°C, V <sub>BATT</sub> > V <sub>SYSMIN</sub> , programmed for 3000mA                                                                                                              | 2887 | 3000 | 3113  |         |

|                                        |                          | MAX77961B. T <sub>A</sub> = +25°C, V <sub>BATT</sub> > V <sub>SYSMIN</sub> , programmed for 3500mA                                                                                                   | 3369 | 3500 | 3631  |         |

|                                        |                          | MAX77961B. T <sub>A</sub> = +25°C, V <sub>BATT</sub> > V <sub>SYSMIN</sub> , programmed for 3800mA                                                                                                   | 3657 | 3800 | 3943  |         |

# 25V<sub>IN</sub>, 3A<sub>OUT</sub> to 6A<sub>OUT</sub>, USB-C Buck-Boost Charger with Integrated FETs for 2S/3S Li-Ion Batteries

### **Electrical Characteristics (continued)**

$(V_{SYS} = 7.6V, V_{BATT} = 7.6V, V_{CHGIN} = 9V, T_A = -40^{\circ}C$  to  $+85^{\circ}C$ .  $T_A = +25^{\circ}C$  (typ). Limits are production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                        | SYMBOL                 | CONDITIONS                                                                                                                         | MIN   | TYP  | MAX   | UNITS   |

|--------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|---------|

| Fast-Charge Current                              |                        | -40°C < T <sub>A</sub> < +85°C, V <sub>BATT</sub> > V <sub>SYSMIN</sub> , programmed for 200mA or less (Note 1)                    | -20   |      | +20   | mA      |

| Accuracy (Over Temperature)                      |                        | -40°C < T <sub>A</sub> < +85°C, V <sub>BATT</sub> > V <sub>SYSMIN</sub> , programmed for greater than 200mA (Note 1)               | -5    |      | +5    | %       |

| CHGIN Adaptive<br>Voltage Regulation<br>Range    | V <sub>CHGIN_REG</sub> | I <sup>2</sup> C programmable                                                                                                      | 4.025 |      | 19.05 | V       |

| CHGIN Adaptive<br>Voltage Regulation<br>Accuracy |                        | 4.55V setting                                                                                                                      | 4.42  | 4.55 | 4.68  | V       |

| CHGIN Current Limit                              | CHGIN_ILIM             | MAX77960B; programmable; production tested at 100mA, 150mA, 200mA, 500mA, 1000mA, 1500mA, and 3000mA settings only                 | 0.1   |      | 3.15  | - А     |

| Range                                            | CHGIN_ILIW             | MAX77961B; programmable; production tested at 100mA, 150mA, 200mA, 500mA, 1000mA, 1500mA, 3000mA, 4000mA, and 6300mA settings only | 0.1   |      | 6.3   |         |

|                                                  |                        | Charger enabled, 100mA input current setting, T <sub>A</sub> = +25°C                                                               | 88    | 98   | 108   |         |

|                                                  |                        | Charger enabled, 200mA input current setting, T <sub>A</sub> = +25°C                                                               | 175   | 195  | 215   |         |

|                                                  |                        | Charger enabled, 500mA input current setting, T <sub>A</sub> = +25°C                                                               | 475   | 488  | 500   | mA      |

| CHGIN Current Limit<br>Accuracy                  |                        | Charger enabled, 1000mA input current setting, T <sub>A</sub> = +25°C                                                              | 950   | 975  | 1000  |         |

|                                                  |                        | Charger enabled, 3000mA input current setting, T <sub>A</sub> = +25°C                                                              | 2850  | 2925 | 3000  |         |

|                                                  |                        | MAX77961B; charger enabled, 4000mA input current setting, T <sub>A</sub> = +25°C                                                   | 3800  | 3900 | 4000  |         |

|                                                  |                        | MAX77961B; charger enabled, 6300mA input current setting, T <sub>A</sub> = +25°C                                                   | 5985  | 6143 | 6300  |         |

| CHGIN Current Limit                              |                        | Charger enabled, 200mA or less input current setting, -40°C < T <sub>A</sub> < +85°C (Note 1)                                      | -22.5 |      | +17.5 | 0/.     |

| Accuracy (Over Temperature)                      |                        | Charger enabled, greater than 200mA input current setting, -40°C < T <sub>A</sub> < +85°C (Note 1)                                 | -7.5  |      | +2.5  | %       |

| Precharge Voltage<br>Threshold                   | V <sub>PRECHG</sub>    | V <sub>BATT</sub> rising, voltage threshold per cell                                                                               | 2.4   | 2.5  | 2.6   | V/Cell  |

| Precharge Current                                | I <sub>PRECHG</sub>    |                                                                                                                                    | 35    | 50   | 65    | mA      |

| Prequalification Threshold Hysteresis            | V <sub>PQ-H</sub>      | Applies to V <sub>PRECHG</sub>                                                                                                     |       | 150  |       | mV/Cell |

### **Electrical Characteristics (continued)**

$(V_{SYS} = 7.6V, V_{BATT} = 7.6V, V_{CHGIN} = 9V, T_A = -40^{\circ}C$  to  $+85^{\circ}C$ .  $T_A = +25^{\circ}C$  (typ). Limits are production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                                              | SYMBOL               | CONDITIONS                                                                                                                                                                | MIN    | TYP  | MAX  | UNITS   |

|------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------|---------|

| Minimum SYS Voltage<br>Accuracy                                        | V <sub>SYSMIN</sub>  | Programmable from 5.535V to 6.970V (2S battery) and 8.303V to 10.455V (3S battery), V <sub>BATT</sub> = 5.6V (2S battery) or 8.4V (3S battery), tested at 3V/cell setting | -3     |      | +3   | %       |

|                                                                        |                      | Default setting = enabled; ITRICKLE[1:0] = 00                                                                                                                             | 75     | 100  | 125  |         |

| Triakla Chargo Current                                                 | <b></b>              | Default setting = enabled; ITRICKLE[1:0] = 01 (Note 1)                                                                                                                    | 150    | 200  | 250  | mA      |

| Trickle Charge Current                                                 | I <sub>TRICKLE</sub> | Default setting = enabled; ITRICKLE[1:0] = 10 (Note 1)                                                                                                                    | 225    | 300  | 375  | ] IIIA  |

|                                                                        |                      | Default setting = enabled; ITRICKLE[1:0] = 11                                                                                                                             | 300    | 400  | 500  |         |

| Top-Off Current<br>Program Range                                       | I <sub>TO</sub>      | Programmable from 100mA to 600mA                                                                                                                                          | 100    |      | 600  | mA      |

| Charge Termination<br>Deglitch Time                                    | tTERM                | 2mV overdrive, 100ns rise/fall time                                                                                                                                       |        | 160  |      | ms      |

| Charger Restart<br>Threshold Range                                     | V <sub>RSTRT</sub>   | Program options for disabled, 100mV/cell, 150mV/cell, and 200mV/cell with CHG_RSTRT[1:0]                                                                                  | 100    |      | 200  | mV/cell |

| Charger Restart<br>Deglitch Time                                       |                      | 10mV overdrive, 100ns rise time                                                                                                                                           |        | 130  |      | ms      |

| Charger State Change<br>Interrupt Deglitch Time                        | t <sub>SCIDG</sub>   | Excludes transition to timer fault state, watchdog timer state                                                                                                            |        | 30   |      | ms      |

| SWITCH MODE CHARGE                                                     | ER / CHARGE T        | IMER                                                                                                                                                                      |        |      |      |         |

| Prequalification Time                                                  | t <sub>PQ</sub>      | Applies to both low-battery prequalification and dead-battery prequalification modes                                                                                      |        | 30   |      | min     |

| Fast-Charge Constant<br>Current + Fast-Charge<br>Constant Voltage Time | t <sub>FC</sub>      | Adjustable from 3hrs, 4hrs, 5hrs, 6hrs, 7hrs, 8hrs, 10hrs including a disable setting; 3hrs default                                                                       |        | 3    |      | hrs     |

| Top-Off Time                                                           | t <sub>TO</sub>      | Adjustable from 30s to 70min in 10min steps                                                                                                                               |        | 30   |      | min     |

| SWITCH MODE CHARGE                                                     | R / WATCHDO          | G TIMER                                                                                                                                                                   |        |      |      |         |

| Watchdog Timer Period                                                  | t <sub>WD</sub>      | (Note 2)                                                                                                                                                                  | 80     |      |      | S       |

| SWITCH MODE CHARGE                                                     | R / BUCK-BOC         | PST                                                                                                                                                                       |        |      |      |         |

| CHGIN OK to Start<br>Switching Delay                                   | tstart               | Delay from INOKB H → L to LX_ start switching                                                                                                                             |        | 150  |      | ms      |

| Buck-Boost Current                                                     | HSILIM               | MAX77960B, V <sub>CHGIN</sub> = 9V, V <sub>SYS</sub> = V <sub>BATT</sub> = 7.6V                                                                                           | 4.3    | 5    | 5.7  | - A     |

| Limit                                                                  | TIGILIIVI            | MAX77961B, V <sub>CHGIN</sub> = 9V, V <sub>SYS</sub> = V <sub>BATT</sub> = 7.6V                                                                                           | 8.6    | 10   | 11.4 |         |

| SWITCH MODE CHARGE                                                     | R / BUCK-BOC         | ST / SWITCH IMPEDANCE AND LEAKAGE                                                                                                                                         | CURREN | Т    |      |         |

| LX1 High-Side<br>Resistance                                            | R <sub>LX1_HS</sub>  | V <sub>CHGIN</sub> = 9V, V <sub>SYS</sub> = V <sub>BATT</sub> = 7.6V                                                                                                      |        | 16.5 | 26   | mΩ      |

### **Electrical Characteristics (continued)**

$(V_{SYS} = 7.6V, V_{BATT} = 7.6V, V_{CHGIN} = 9V, T_A = -40^{\circ}C$  to  $+85^{\circ}C$ .  $T_A = +25^{\circ}C$  (typ). Limits are production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                                           | SYMBOL                                  | CONDITIONS                                                                                                                | MIN | TYP  | MAX | UNITS |

|---------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| LX1 Low-Side<br>Resistance                                          | R <sub>LX1_LS</sub>                     | V <sub>CHGIN</sub> = 9V, V <sub>SYS</sub> = V <sub>BATT</sub> = 7.6V                                                      |     | 17   | 30  | mΩ    |

| LX2 High-Side<br>Resistance                                         | R <sub>LX2_HS</sub>                     | V <sub>CHGIN</sub> = 9V, V <sub>SYS</sub> = V <sub>BATT</sub> = 7.6V                                                      |     | 9    | 18  | mΩ    |

| LX2 Low-Side<br>Resistance                                          | R <sub>LX2_LS</sub>                     | V <sub>CHGIN</sub> = 9V, V <sub>SYS</sub> = V <sub>BATT</sub> = 7.6V                                                      |     | 21   | 33  | mΩ    |

| LV Lackage Current                                                  |                                         | LX1 = PGND or CHGIN, LX2 = PGND or<br>SYS, T <sub>A</sub> = +25°C                                                         |     | 0.01 | 10  |       |

| LX_ Leakage Current                                                 |                                         | LX1 = PGND or CHGIN, LX2 = PGND or<br>SYS, T <sub>A</sub> = +85°C                                                         |     | 1    |     | μA    |

| DCT Lookage Current                                                 |                                         | BST_ = 1.8V, T <sub>A</sub> = +25°C                                                                                       |     | 0.01 | 10  | μА    |

| BST_ Leakage Current                                                |                                         | BST_ = 1.8V, T <sub>A</sub> = +85°C                                                                                       |     | 1    |     |       |

| SYS, SYSA Leakage                                                   |                                         | V <sub>SYS</sub> = V <sub>SYSA</sub> = 8.4V, V <sub>BATT</sub> = 0V,<br>charger disabled, T <sub>A</sub> = +25°C          |     | 0.01 | 10  | - μΑ  |

| Current                                                             |                                         | $V_{SYS} = V_{SYSA} = 8.4V$ , $V_{BATT} = 0V$ , charger disabled, $T_A = +85^{\circ}C$                                    |     | 1    |     |       |

| CSINP, CSINN Leakage<br>Current                                     | I <sub>CSINP</sub> , I <sub>CSINN</sub> | V <sub>CHGIN</sub> = 26.05V, V <sub>CSINP</sub> = V <sub>CSINN</sub> = 26.05V, T <sub>A</sub> = +25°C                     | -1  |      | +1  | μА    |

| SWITCH MODE CHARG                                                   | ER / SMART PO                           | WER SELECTOR                                                                                                              |     |      |     |       |

| BAT to SYS Dropout<br>Resistance                                    | R <sub>BAT2SYS</sub>                    |                                                                                                                           |     | 10   | 17  | mΩ    |

| BATT to SYS Reverse<br>Regulation Voltage                           | V <sub>BSREG</sub>                      |                                                                                                                           |     | 90   |     | mV    |

| SWITCH MODE CHARG                                                   | ER / BATT TO SY                         | S OVERCURRENT ALERT                                                                                                       |     |      |     |       |

| Battery Overcurrent<br>Threshold Range                              | I <sub>BOVCR</sub>                      | Programmable from 3A to 10A. Option to disable.                                                                           | 3   |      | 10  | А     |

| Battery Overcurrent<br>Debounce Time                                | t <sub>BOVRC</sub>                      | Response time for generating the overcurrent interrupt (Note 2)                                                           |     |      | 3.3 | ms    |

| SWITCH MODE CHARG                                                   | ER / THERMAL F                          | OLDBACK                                                                                                                   |     |      |     | •     |

| Junction Temperature Thermal Regulation Loop Setpoint Program Range | T <sub>REG</sub>                        | Junction temperature when charge current is reduced; programmable from 85°C to 130°C in 5°C steps; default value is 115°C | 85  |      | 130 | °C    |

### **Electrical Characteristics (continued)**

$(V_{SYS} = 7.6V, V_{BATT} = 7.6V, V_{CHGIN} = 9V, T_A = -40^{\circ}C$  to  $+85^{\circ}C$ .  $T_A = +25^{\circ}C$  (typ). Limits are production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                   | SYMBOL                        | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MIN   | TYP   | MAX   | UNITS |  |  |  |

|---------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|--|--|--|

| Thermal Regulation<br>Gain                  | A <sub>TJREG</sub>            | The charge current is decreased 5% of the fast-charge current setting for every degree that the junction temperature exceeds the thermal regulation temperature. This slope ensures that the full-scale current of 3A (MAX77960B)/6A (MAX77961B) is reduced to 0A by the time the junction temperature is 20°C above the programmed loop set point.  For lower programmed charge currents such as 480mA, this slope is valid for charge current reductions down to 80mA; below 100mA the slope becomes shallower but the charge current still reduced to 0A if the junction temperature is 20°C above the programmed loop set point. |       |       | %/°C  |       |  |  |  |

| SWITCH MODE CHARGER / THERMISTOR MONITOR    |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |       |       |       |  |  |  |

| THM Threshold, COLD                         | THM_COLD                      | V <sub>THM</sub> /V <sub>AVL</sub> rising, 1% hysteresis (thermistor temperature falling)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 73.36 | 74.56 | 75.76 | %     |  |  |  |

| THM Threshold, COOL                         | THM_COOL                      | V <sub>THM</sub> /V <sub>AVL</sub> rising, 1% hysteresis (thermistor temperature falling) 58.8 60 61.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |       |       | %     |  |  |  |

| THM Threshold, WARM                         | THM_WARM                      | V <sub>THM</sub> /V <sub>AVL</sub> falling, 1% hysteresis (thermistor temperature rising)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 33.68 | 34.68 | 35.68 | %     |  |  |  |

| THM Threshold, HOT                          | тнм_нот                       | V <sub>THM</sub> /V <sub>AVL</sub> falling, 1% hysteresis (thermistor temperature rising)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 21.59 | 22.5  | 23.41 | %     |  |  |  |

| THM Threshold,<br>Disabled                  |                               | VTHM/AVL falling, 1% hysteresis, THM function is disabled below this voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.9   | 5.9   | 6.9   | %     |  |  |  |

| THM Threshold, Battery Removal Detection    |                               | V <sub>THM</sub> /V <sub>AVL</sub> rising, 1% hysteresis, battery removal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 85.6  | 87    | 88.4  | %     |  |  |  |

| THM Input Leakage                           |                               | V <sub>THM</sub> = GND or V <sub>AVL</sub> ; T <sub>A</sub> = +25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       | 0.1   | 1     | μA    |  |  |  |

| Current                                     |                               | V <sub>THM</sub> = GND or V <sub>AVL</sub> ; T <sub>A</sub> = +85°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       | 0.1   |       | μ, ,  |  |  |  |

| REVERSE BUCK                                |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |       |       | Г     |  |  |  |

| Buck Current Limit                          | HSILIM_REV                    | f <sub>SW</sub> = 600kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4.3   | 5     | 5.7   | Α     |  |  |  |

| Reverse Buck<br>Quiescent Current           |                               | Not switching: output forced 200mV above its target regulation voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |       | μA    |       |  |  |  |

| Minimum BATT Voltage in OTG Mode            | V <sub>BATT.MIN.OT</sub><br>G | V <sub>BATT</sub> = V <sub>SYS</sub> , SYS UVLO falling threshold in OTG mode 5.96 6.14 6.32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | 6.32  | V     |       |  |  |  |

| CHGIN Voltage in OTG<br>Mode                | V <sub>CHGIN.OTG</sub>        | $V_{BATT} = V_{BATT.MIN.OTG}$ , OTGEN = high 4.94 5.1 5.26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       | V     |       |       |  |  |  |

| CHGIN Undervoltage<br>Threshold in OTG Mode | V <sub>CHGIN.OTG.U</sub>      | V <sub>CHGIN</sub> falling, OTGEN = high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       | 85    |       | %     |  |  |  |

| CHGIN Overvoltage<br>Threshold in OTG Mode  | V <sub>CHGIN.OTG</sub> .      | V <sub>CHGIN</sub> rising, OTGEN = high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | 110   |       | %     |  |  |  |

### **Electrical Characteristics (continued)**

$(V_{SYS} = 7.6V, V_{BATT} = 7.6V, V_{CHGIN} = 9V, T_A = -40^{\circ}C$  to  $+85^{\circ}C$ .  $T_A = +25^{\circ}C$  (typ). Limits are production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                                                                                             | SYMBOL                    | CONDITIONS                                                                                 | MIN                       | TYP                        | MAX                       | UNITS |  |

|-----------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------|---------------------------|----------------------------|---------------------------|-------|--|

|                                                                                                                       |                           | $V_{BATT} = V_{BATT.MIN.OTG}$ , $T_A = +25^{\circ}C$ , OTG_ILIM[2:0] = 0b000, OTGEN = high |                           | 500                        | 550                       |       |  |

| CHGIN Output Current                                                                                                  | I <sub>CHGIN.OTG.LI</sub> | $V_{BATT} = V_{BATT.MIN.OTG}$ , $T_A = +25^{\circ}C$ , OTG_ILIM[2:0] = 0b001, OTGEN = high |                           | 900                        | 990                       | mA    |  |

| Limit in OTG Mode                                                                                                     | М                         | $V_{BATT} = V_{BATT.MIN.OTG}$ , $T_A = +25$ °C, OTG_ILIM[2:0] = 0b011, OTGEN = high        |                           | 1500                       | 1650                      |       |  |

|                                                                                                                       |                           | $V_{BATT} = V_{BATT.MIN.OTG}$ , $T_A = +25^{\circ}C$ , OTG_ILIM[2:0] = 0b111, OTGEN = high |                           | 3000                       | 3300                      |       |  |

| CHGIN Output Voltage                                                                                                  |                           | Discontinuous inductor current (i.e., skip mode), OTGEN = high                             |                           | ±150                       |                           | mV    |  |

| Ripple in OTG Mode                                                                                                    |                           | Continuous inductor current, OTGEN = high                                                  |                           | ±150                       |                           | IIIV  |  |

| IO CHARACTERISTICS                                                                                                    |                           |                                                                                            |                           |                            |                           |       |  |

| R <sub>INLIM</sub> , R <sub>ISET</sub> , R <sub>VSET</sub> ,<br>R <sub>TO</sub> , R <sub>CNFG</sub> Resistor<br>Range | R <sub>PROG</sub> _       |                                                                                            | 5.49                      |                            | 226                       | kΩ    |  |

| Output Low Voltage INOKB, STAT                                                                                        |                           | I <sub>SINK</sub> = 1mA, T <sub>A</sub> = +25°C                                            |                           |                            | 0.4                       | V     |  |

| Output High Leakage                                                                                                   |                           | 5.5V, T <sub>A</sub> = +25°C                                                               | -1                        | 0                          | +1                        | μA    |  |

| INOKB, STAT                                                                                                           |                           | 5.5V, T <sub>A</sub> = +85°C                                                               |                           | 0.1                        |                           | μΑ    |  |

| DISQBAT, OTGEN,<br>STBY Logic Input Low<br>Threshold                                                                  | V <sub>IL</sub>           |                                                                                            |                           |                            | 0.4                       | V     |  |

| DISQBAT, OTGEN,<br>STBY Logic Input High<br>Threshold                                                                 | V <sub>IH</sub>           |                                                                                            | 1.4                       |                            |                           | V     |  |

| DISQBAT, OTGEN,<br>STBY Logic Input<br>Leakage Current                                                                |                           | 5.5V (including current through pulldown resistor)                                         |                           | 5.5                        | 10                        | μA    |  |

| DISQBAT, OTGEN,<br>STBY Pulldown Resistor                                                                             | R <sub>DISQBAT</sub>      |                                                                                            |                           | 1000                       | 1200                      | kΩ    |  |

| INTERFACE / I <sup>2</sup> C INTER                                                                                    | FACE AND INTE             | RRUPT                                                                                      | •                         |                            |                           |       |  |

| SCL, SDA Input Low<br>Level                                                                                           |                           |                                                                                            |                           |                            | 0.3 x<br>V <sub>AVL</sub> | V     |  |

| SCL, SDA Input High<br>Level                                                                                          |                           |                                                                                            | 0.7 x<br>V <sub>AVL</sub> |                            |                           | V     |  |

| SCL, SDA Input<br>Hysteresis                                                                                          |                           |                                                                                            |                           | 0.05 x<br>V <sub>AVL</sub> |                           | V     |  |

| SCL, SDA Logic Input<br>Current                                                                                       |                           | SDA = SCL = 5.5V                                                                           | -10                       |                            | +10                       | μA    |  |

| SCL, SDA Input<br>Capacitance                                                                                         |                           |                                                                                            |                           | 10                         |                           | pF    |  |

| SDA Output Low<br>Voltage                                                                                             |                           | Sinking 20mA                                                                               |                           |                            | 0.4                       | V     |  |

### **Electrical Characteristics (continued)**

$(V_{SYS} = 7.6V, V_{BATT} = 7.6V, V_{CHGIN} = 9V, T_A = -40^{\circ}C$  to  $+85^{\circ}C$ .  $T_A = +25^{\circ}C$  (typ). Limits are production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                                                  | SYMBOL              | CONDITIONS                                       | MIN            | TYP     | MAX  | UNITS |

|----------------------------------------------------------------------------|---------------------|--------------------------------------------------|----------------|---------|------|-------|

| Output Low Voltage<br>INTB                                                 |                     | I <sub>SINK</sub> = 1mA                          |                |         | 0.4  | V     |

| Output High Leakage                                                        |                     | V <sub>INTB</sub> = 5.5V, T <sub>A</sub> = +25°C | -1             | 0       | +1   |       |

| INTB                                                                       |                     | V <sub>INTB</sub> = 5.5V, T <sub>A</sub> = +85°C |                | 0.1     |      | μA    |

| INTERFACE / I <sup>2</sup> C COMPA                                         | ATIBLE INTER        | FACE TIMING FOR STANDARD, FAS                    | T, AND FAST-MC | DE PLUS |      |       |

| Clock Frequency                                                            | f <sub>SCL</sub>    |                                                  |                |         | 1000 | kHz   |

| Hold Time (Repeated)<br>START Condition                                    | t <sub>HD;STA</sub> |                                                  | 0.26           |         |      | μs    |

| CLK Low Period                                                             | t <sub>LOW</sub>    |                                                  | 0.5            |         |      | μs    |

| CLK High Period                                                            | tHIGH               |                                                  | 0.26           |         |      | μs    |

| Set-Up Time Repeated START Condition                                       | <sup>t</sup> SU;STA |                                                  | 0.26           |         |      | μs    |

| DATA Hold Time                                                             | t <sub>HD:DAT</sub> |                                                  | 0              |         |      | μs    |

| DATA Valid Time                                                            | t <sub>VD:DAT</sub> |                                                  |                |         | 0.45 | μs    |

| DATA Valid<br>Acknowledge Time                                             | t <sub>VD:ACK</sub> |                                                  |                |         | 0.45 | μs    |

| DATA Set-Up time                                                           | t <sub>SU;DAT</sub> |                                                  | 50             |         |      | ns    |

| Set-Up Time for STOP<br>Condition                                          | tsu;sто             |                                                  | 0.26           |         |      | μs    |

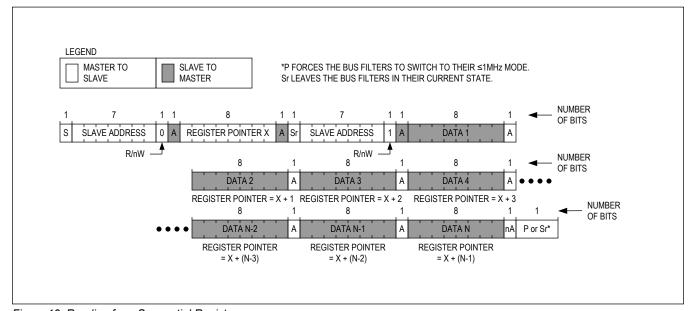

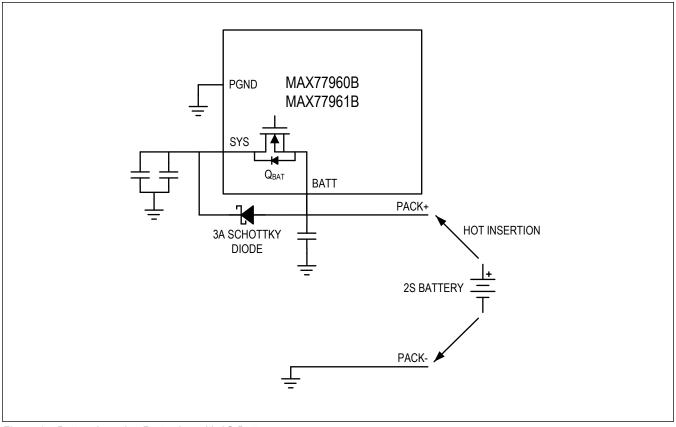

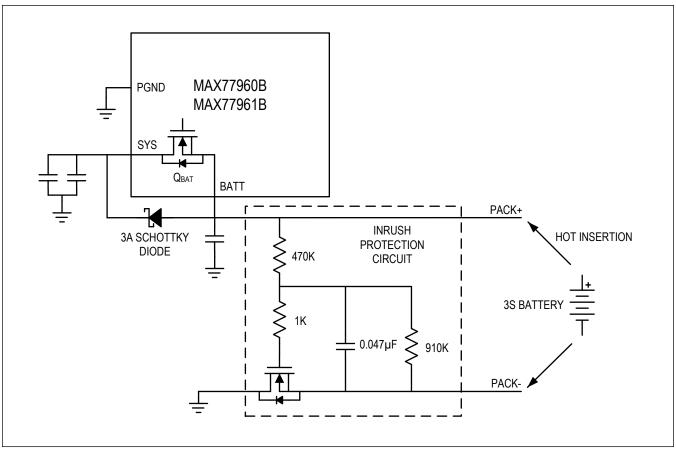

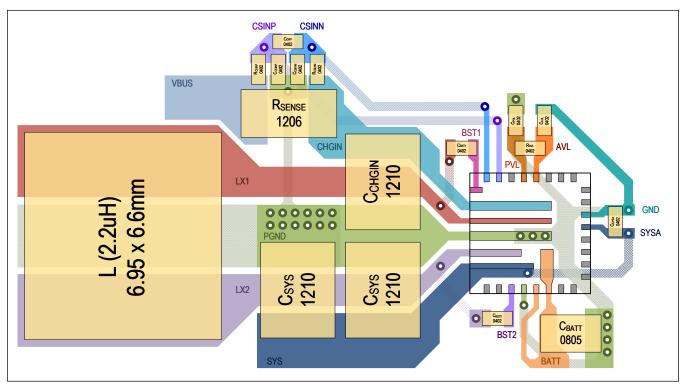

| Bus-Free Time Between STOP and START                                       | t <sub>BUF</sub>    |                                                  | 0.5            |         |      | μs    |