### DS28C22

# DeepCover Secure Memory with I<sup>2</sup>C SHA-256 and 3Kb User EEPROM

#### **General Description**

DeepCover<sup>®</sup> embedded security solutions cloak sensitive data under multiple layers of advanced physical security to provide the most secure key storage possible. The DeepCover Secure Memory (DS28C22) combines crypto-strong, bidirectional, secure challenge-andresponse authentication and small message encryption functionality with an implementation based on the FIPS 180-specified Secure Hash Algorithm (SHA-256). A 3Kb user-programmable EEPROM array provides nonvolatile storage for application data and additional protected memory holds a read-protected secret for SHA-256 operations and settings for user memory control. Each device has its own guaranteed unique and unalterable 64-bit ROM identification number (ROM ID) that is factory programmed into the chip. This unique ROM ID is used as a fundamental input parameter for cryptographic operations and also serves as an electronic serial number within the application. A bidirectional security model enables twoway authentication and encryption between a host system and slave-embedded DS28C22. Slave-to-host authentication is used by a host system to securely validate that an attached or embedded DS28C22 is authentic. Hostto-slave authentication is used to protect DS28C22 user memory from being modified by a nonauthentic host. The SHA-256 message authentication code (MAC), which the DS28C22 generates, is computed from data in the user memory, an on-chip secret, a host random challenge, and the 64-bit ROM ID. The device also facilitates encrypted read and write between host and slave using a one time pad computed by the SHA-256 engine. When not in use, the DS28C22 can be put in sleep mode where power consumption is minimal.

#### **Applications**

- Authentication of Network-Attached Appliances

- System Intellectual Property Protection

- Secure Feature Setting for Configurable Systems

- Key Generation and Secure Exchange for Cryptographic Systems

DeepCover is a registered trademark of Maxim Integrated Products, Inc.

#### **Benefits and Features**

- Symmetric Key-Based Bidirectional Secure Authentication and Encryption Model Based on SHA-256

- Dedicated Hardware-Accelerated SHA Engine for Generating SHA-256 MACs

- Strong Authentication with a 256-Bit, User-Programmable Secret, and Input Challenge

- 3072 Bits of User EEPROM Partitioned Into 12 Pages of 256 Bits

- User-Programmable and Irreversible EEPROM Protection Modes Including Authentication, Write and Read Protect, Encryption, and OTP/EPROM Emulation

- Supports 100kHz and 400kHz I<sup>2</sup>C Communication Speeds

- Supports Power-Saving Sleep Mode at 0.5µA (typ)

- Operating Range: 3.3V ±10%, -40°C to +85°C

- 8-Pin TDFN Package

#### Ordering Information appears at end of data sheet.

For related parts and recommended products to use with this part, refer to <u>www.maximintegrated.com/DS28C22.related</u>.

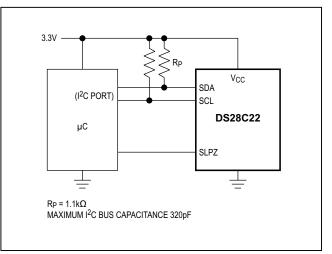

#### **Typical Application Circuit**

# DS28C22

# DeepCover Secure Memory with I<sup>2</sup>C SHA-256 and 3Kb User EEPROM

### **Absolute Maximum Ratings**

| Voltage Range on Any Pin Relative to GND0.5V to +4.0V |  |

|-------------------------------------------------------|--|

| Maximum Current into Any Pin20mA                      |  |

| Operating Temperature Range40°C to +85°C              |  |

| Junction Temperature+150°C                            |  |

| Storage Temperature Range         | 55°C to +125°C |

|-----------------------------------|----------------|

| Lead Temperature (soldering, 10s) | +300°C         |

| Soldering Temperature (reflow)    | +260°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### Package Thermal Characteristics (Note 1)

#### TDFN

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ).......60°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ).......11°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **Electrical Characteristics**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$  (Note 2)

| PARAMETER                                   | SYMBOL            | L CONDITIONS                                |                               | TYP                       | MAX                            | UNITS |

|---------------------------------------------|-------------------|---------------------------------------------|-------------------------------|---------------------------|--------------------------------|-------|

| Supply Voltage                              | V <sub>CC</sub>   |                                             | 2.97                          | 3.3                       | 3.63                           | V     |

|                                             | ICC               | (Note 3) 750                                |                               | 750                       |                                |       |

| Supply Current                              |                   | Sleep mode (SLPZ pin low), $V_{CC}$ = 3.63V |                               | 0.5                       | 2.0                            | - μΑ  |

| SHA-256 Engine                              |                   |                                             |                               |                           |                                |       |

| Computation Current                         | ICSHA             | Pofer to the full data cheet                |                               |                           |                                | mA    |

| Computation Time                            | t <sub>CSHA</sub> |                                             | Refer to the full data sheet. |                           |                                | ms    |

| EEPROM                                      |                   |                                             |                               |                           |                                |       |

| Programming Current                         | I <sub>PROG</sub> | (Notes 4, 5)                                |                               |                           | 2                              | mA    |

| Programming Time for 32-Bit<br>Segment      | t <sub>PROG</sub> | Refer to the full data sheet.               |                               |                           |                                | ms    |

| Write/Erase Cycling Endurance               | N <sub>CY</sub>   | T <sub>A</sub> = +85°C (Notes 6, 7)         | 1000                          |                           |                                | _     |

| Data Retention                              | t <sub>DR</sub>   | T <sub>A</sub> = +85°C (Notes 8, 9, 10) 10  |                               |                           | years                          |       |

| SLPZ Pin                                    |                   |                                             |                               |                           |                                |       |

| LOW Level Input Voltage                     | VIL               |                                             | -0.5                          |                           | 0.3 x V <sub>CC</sub>          | V     |

| HIGH Level Input Voltage                    | V <sub>IH</sub>   |                                             |                               | V <sub>CC</sub> +<br>0.5V | V                              |       |

| Input Leakage Current                       | II.               | Pin at 3.63V                                |                               |                           | 0.1                            | μA    |

| Wakeup Time from Sleep Mode                 | tSWUP             | (Note 11)                                   |                               |                           | 250                            | μs    |

| I <sup>2</sup> C SCL and SDA Pins (Note 12) |                   |                                             |                               |                           | <b>!</b>                       |       |

| LOW Level Input Voltage                     | VIL               |                                             | -0.5                          |                           | 0.3 x V <sub>CC</sub>          | V     |

| HIGH Level Input Voltage                    | VIH               |                                             | 0.7 x<br>V <sub>CC</sub>      |                           | V <sub>CC(MAX)</sub><br>+ 0.5V | V     |

# DS28C22

# DeepCover Secure Memory with I<sup>2</sup>C SHA-256 and 3Kb User EEPROM

## **Electrical Characteristics (continued)**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$  (Note 2)

| PARAMETER                                                                                    | SYMBOL              | CONDITIONS        | MIN TY                    | P MAX | UNITS |

|----------------------------------------------------------------------------------------------|---------------------|-------------------|---------------------------|-------|-------|

| Hysteresis of Schmitt Trigger<br>Inputs                                                      | V <sub>HYS</sub>    | (Note 4)          | 0.05 x<br>V <sub>CC</sub> |       | V     |

| LOW Level Output Voltage at<br>3mA Sink Current                                              | V <sub>OL</sub>     |                   |                           | 0.4   | V     |

| Output Fall Time from $V_{IH(MIN)}$ to $V_{IL(MAX)}$ with Bus Capacitance from 10pF to 400pF | tOF                 | (Note 4)          | 60                        | 300   | ns    |

| Pulse Width of Spikes<br>Suppressed by the Input Filter                                      | t <sub>SP</sub>     | (Note 4)          |                           | 50    | ns    |

| Input Current with Input Voltage Between $0.1V_{CC(MAX)}$ and $0.9V_{CC(MAX)}$               | ų                   | (Notes 4, 13)     | -10                       | +10   | μA    |

| Input Capacitance                                                                            | Cl                  | (Note 4)          |                           | 10    | pF    |

| SCL Clock Frequency                                                                          | f <sub>SCL</sub>    |                   | 0                         | 400   | kHz   |

| Hold Time (Repeated) START<br>Condition, After This Period, First<br>Clock Pulse Generated   | <sup>t</sup> HD:STA | (Note 4)          | 0.6                       |       | μs    |

| LOW Period of the SCL Clock                                                                  | tLOW                | (Note 4)          | 1.3                       |       | μs    |

| HIGH Period of the SCL Clock                                                                 | tHIGH               | (Note 4)          | 0.6                       |       | μs    |

| Setup Time for Repeated START<br>Condition                                                   | <sup>t</sup> SU:STA | (Note 4)          | 0.6                       |       | μs    |

| Data Hold Time                                                                               | t <sub>HD:DAT</sub> | (Notes 4, 14, 15) |                           | 0.9   | μs    |

| Data Setup Time                                                                              | t <sub>SU:DAT</sub> | (Notes 4, 16)     | 250                       |       | ns    |

| Setup Time for STOP Condition                                                                | t <sub>SU:STO</sub> | (Note 4)          | 0.6                       |       | μs    |

| Bus Free Time Between STOP<br>and START Condition                                            | t <sub>BUF</sub>    | (Note 4)          | 1.3                       |       | μs    |

| Capacitive Load for Each Bus<br>Line                                                         | Cb                  | (Notes 4, 17)     |                           | 400   | pF    |

| Oscillator Warm-Up Time                                                                      | toscwup             | (Note 11)         |                           | 250   | μs    |

**Note 2:** Limits are 100% production tested at  $T_A = +25^{\circ}C$  and  $TA = +85^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.

Note 3: Operating current continuously reading the Memory/MAC Read/Write Register at 400kHz.

Note 4: Guaranteed by design and/or characterization only. Not production tested.

Note 5: Refer to the full data sheet.

Note 6: Write-cycle endurance is tested in compliance with JESD47G.

Note 7: Not 100% production tested; guaranteed by reliability monitor sampling.

Note 8: Data retention is tested in compliance with JESD47G.

**Note 9:** Guaranteed by 100% production test at elevated temperature for a shorter time; equivalence of this production test to the data sheet limit at operating temperature range is established by reliability testing.

Note 10: EEPROM Writes can become nonfunctional after the data-retention time is exceeded. Long-term storage at elevated temperatures is not recommended.

Note 11: I<sup>2</sup>C communication should not take place for the max t<sub>OSCWUP</sub> or t<sub>SWUP</sub> time following a power-on reset or a wake-up from sleep mode.

DS28C22

# DeepCover Secure Memory with I<sup>2</sup>C SHA-256 and 3Kb User EEPROM

### **Electrical Characteristics (continued)**

(T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 2)

- Note 12: All I<sup>2</sup>C timing values are referred to  $V_{IH(MIN)}$  and  $V_{IL(MAX)}$  levels.

- Note 13: I/O pins of the DS28C22 do not obstruct the SDA and SCL lines if V<sub>CC</sub> is switched off.

- Note 14: The DS28C22 provides a hold time of at least 300ns for the SDA signal (referred to the V<sub>IH(MIN)</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- Note 15: The maximum t<sub>HD:DAT</sub> has only to be met if the device does not stretch the LOW period (t<sub>LOW</sub>) of the SCL signal. If the clock stretches the SCL, the data must be valid by the setup time before it releases the clock. (I<sup>2</sup>C-bus specification Rev. 03, 19 June 2007)

- Note 16: A fast-mode I<sup>2</sup>C-bus device can be used in a standard-mode I<sup>2</sup>C-bus system, but the requirement t<sub>SU:DAT</sub> ≥ 250ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line tr max + t<sub>SU:DAT</sub> = 1000 + 250 = 1250ns (according to the standard-mode I<sup>2</sup>C-bus specification) before the SCL line is released. Also the acknowledge timing must meet this setup time. (I<sup>2</sup>C-bus specification Rev. 03, 19 June 2007)

- Note 17: C<sub>B</sub> = total capacitance of one bus line in pF. The maximum bus capacitance allowable may vary from this value depending on the actual operating voltage and frequency of the application. (I<sup>2</sup>C-bus specification Rev. 03, 19 June 2007)

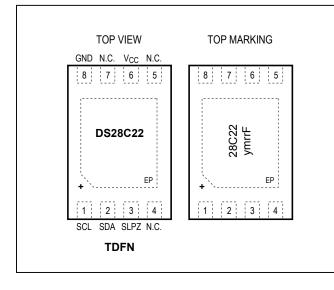

#### **Pin Configuration**

#### **Pin Description**

| PIN     | NAME            | FUNCTION                                                                                                                                                                                       |

|---------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | SCL             | $\rm I^2C$ Serial Clock Input. Must be connected to $\rm V_{CC}$ through a pullup resistor.                                                                                                    |

| 2       | SDA             | $\rm I^2C$ Serial Data Input/Output. Must be connected to $\rm V_{CC}$ through a pullup resistor.                                                                                              |

| 3       | SLPZ            | Active-low control input to activate the low-power sleep mode, and to issue a device reset.                                                                                                    |

| 4, 5, 7 | N.C.            | No Connection                                                                                                                                                                                  |

| 6       | V <sub>CC</sub> | Power-Supply Input                                                                                                                                                                             |

| 8       | GND             | Ground Reference                                                                                                                                                                               |

| _       | EP              | Exposed Pad. Solder evenly to the<br>board's ground plane for proper<br>operation. Refer to Application Note 3273:<br><i>Exposed Pads: A Brief Introduction</i> for<br>additional information. |

# DS28C22

# DeepCover Secure Memory with I<sup>2</sup>C SHA-256 and 3Kb User EEPROM

## **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| DS28C22Q+T | -40°C to +85°C | 8 TDFN-EP*  |

|            | -40 C 10 +65 C | (2.5k pcs)  |

+ Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

\*EP = Exposed pad.

### **Package Information**

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE |        |                | LAND<br>PATTERN NO. |  |

|-----------------|--------|----------------|---------------------|--|

| 8 TDFN-EP       | T823+1 | <u>21-0174</u> | <u>90-0091</u>      |  |

Note to readers: This document is an abridged version of the full data sheet. Additional device information is available only in the full version of the data sheet. To request the full data sheet, go to <a href="http://www.maximintegrated.com/DS28C22">www.maximintegrated.com/DS28C22</a> and click on Request Full Data Sheet.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Security/Authentication Development Tools category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below :

OM67201ULUL AT97SC3205P-SDK2 AT97SC3205T-SDK2 ATECC108XPLAINED MAXREFDES34# AT88CKECC-AWS-XSTK MIKROE-2761 MIKROE-2760 MIKROE-2522 cs-pastilda-01 IPL-003WR 4314 ATCRYPTOAUTH-XPRO CS-SOMU-02 BLOCKCHAINSTARTKITTOBO1 IRID9670TPM12LINUXTOBO1 IRID9670TPM20LINUXTOBO1 IRIDIUM9645TPMI2CTOBO1 IRIDIUMSLM9670TPM20TOBO1 OPTIGATRUSTEEVALKITTOBO1 OPTIGATRUSTMEVALKITTOBO1 S2GOSECURITYOPTIGAETOBO1 S2GOSECURITYOPTIGAXTOBO1 DS28C40EVKIT# AT88CK109STK3 AT88CK590 AT88CKECC-AWS-XSTK-B ATCRYPTOAUTH-XPRO-B DM320109 DM320118 DT100104 MIKROE-3746 MIKROE-3774 MIKROE-3915 MIKROE-4236 MIKROE-1819 MIKROE-2829 MIKROE-3045 MIKROE-4656 OM3710/A71CHARD OM-SE050ARD 102010288 103030395 DEV-15573 DEV-18077 KIT-18303 STEVAL-IAC001V1