# 2×, 31.76 W, Digital Input, Filterless Stereo Class-D Audio Amplifier

Data Sheet SSM3582

#### **FEATURES**

Digital input stereo, high efficiency Class-D amplifier Operates from a single 4.5 V to 16 V supply

State-of-the-art, proprietary, filterless  $\Sigma$ - $\Delta$  modulation 106.5 dB signal-to-noise ratio

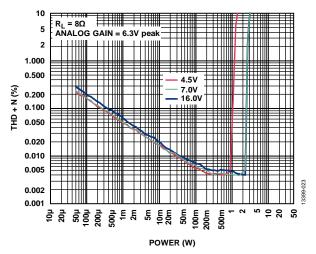

0.004% total harmonic distortion plus noise (THD + N) at 5 W into 8  $\Omega$

38.5 µV rms A weighted output noise

Pop/clickless on/off sequence

$2\times$  14.67 W output at 12 V supply to 4  $\Omega$  loads at <1% THD + N

$2\times$  14.4 W output at 16 V supply to 8  $\Omega$  loads at <1% THD + N

Mono mode for increased maximum output power

1× 49.69 W output at 16 V supply to 2  $\Omega$  loads at <1% THD + N

Support for low impedance loads

As low as 3  $\Omega/5~\mu H$  in stereo mode

As low as 2  $\Omega/5~\mu H$  in mono mode

**High power efficiency**

93.8% efficiency into an 8  $\Omega$  load

90.6% efficiency into a 4  $\Omega$  load

12.34 mA quiescent current with single 12 V PVDD supply

Single supply operation with internal LDOs or option to use an external 5 V and 1.8 V supply for lowest power consumption

I<sup>2</sup>C control and hardware modes with up to 16 pin-selectable slots/addresses

Supported sample rates from 8 kHz to 192 kHz; 24-bit resolution

Multiple PCM audio serial data formats

TDM slave with support for up to 16 devices on a single bus  $I^2S$  or left justified slave

Adjustable full-scale output tailored for many PVDD sources 2- and 3-cell Li-lon batteries

Digital volume control with selectable smooth ramp

Automatic power-down function

Supply monitoring automatic gain control (AGC) function reduces system brownout

Standalone operational mode without I<sup>2</sup>C

Temperature sensor with 1°C step readout via I2C

Short-circuit, undervoltage, and thermal protection

Thermal early warning

Power-on reset

PV<sub>DD</sub> sensing ADC

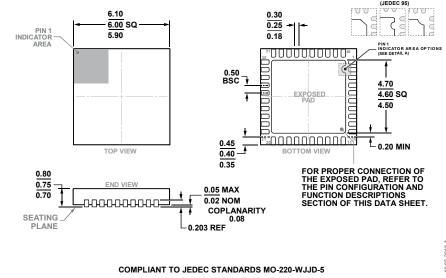

40-lead, 6 mm  $\times$  6 mm LFCSP with thermal pad

#### **APPLICATIONS**

Mobile computing

All in one computers

**Portable electronics**

Wireless speakers

**Televisions**

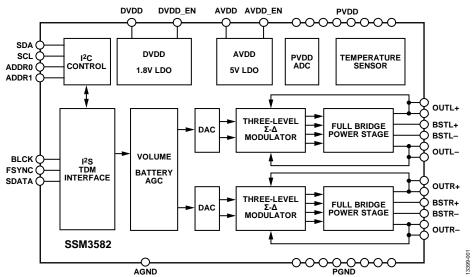

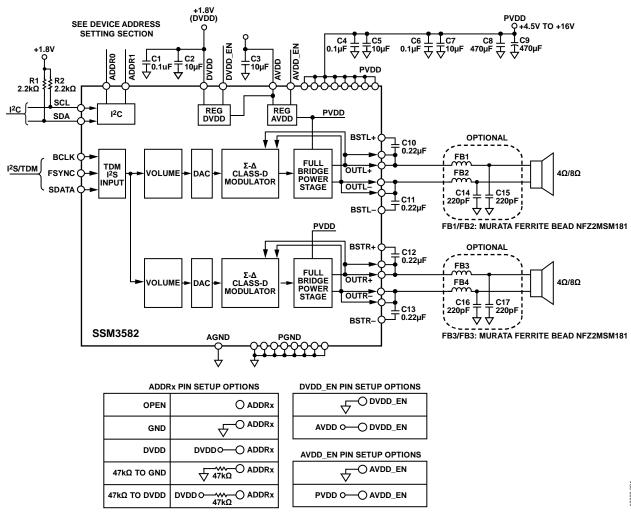

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

Rev. A Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# **TABLE OF CONTENTS**

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| Functional Block Diagram                    | 1  |

| Revision History                            | 2  |

| General Description                         | 3  |

| Specifications                              | 4  |

| Digital Input/Output Specifications         | 8  |

| Digital Timing Specifications               | 8  |

| Digital Input Timing Specifications         | 8  |

| Absolute Maximum Ratings                    | 11 |

| Thermal Resistance                          | 11 |

| ESD Caution                                 | 11 |

| Pin Configuration and Function Descriptions | 12 |

| Typical Performance Characteristics         | 14 |

| Theory of Operation                         | 25 |

| Overview                                    | 25 |

| Power Supplies                              | 25 |

| Power-Up Sequence                           | 26 |

| Power-Down Operation                        | 26 |

| Clocking                                    | 26 |

| Digital Audio Serial Interface              | 26 |

|                                             |    |

| Standalone Operation                              |

|---------------------------------------------------|

| Mono Mode31                                       |

| Analog and Digital Gain31                         |

| Pop and Click Suppression                         |

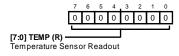

| Temperature Sensor                                |

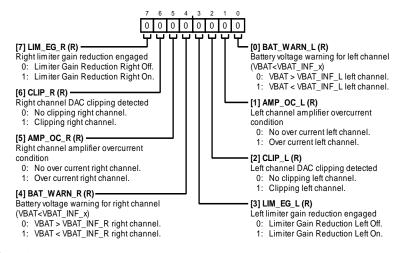

| Faults and Limiter Status Reporting               |

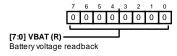

| VBAT (PV <sub>DD</sub> ) Sensing                  |

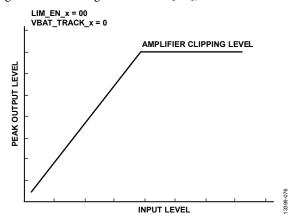

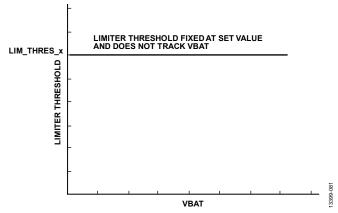

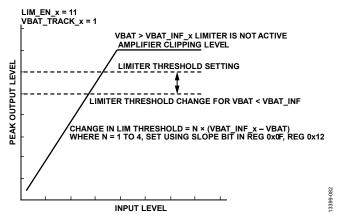

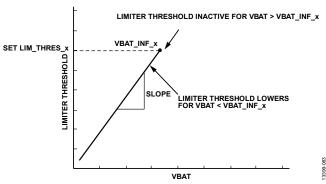

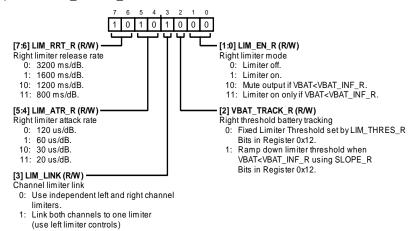

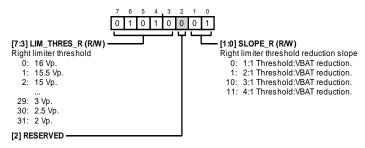

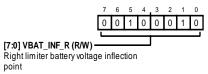

| Limiter and Battery Tracking Threshold Control 32 |

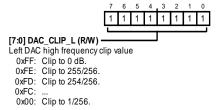

| High Frequency Clipper35                          |

| EMI Noise                                         |

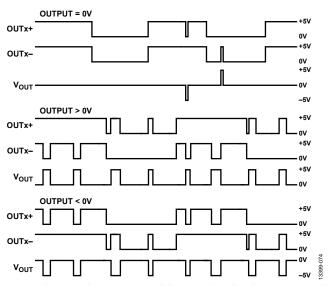

| Output Modulation Description                     |

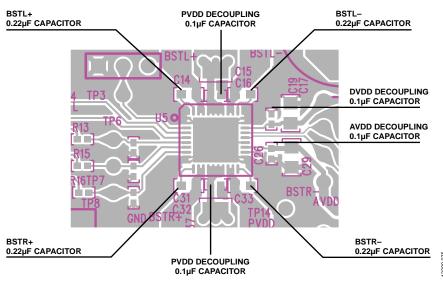

| Bootstrap Capacitors                              |

| Power Supply Decoupling                           |

| Output EMI Filtering                              |

| PCB Placement                                     |

| Layout                                            |

| Register Summary                                  |

| Register Details                                  |

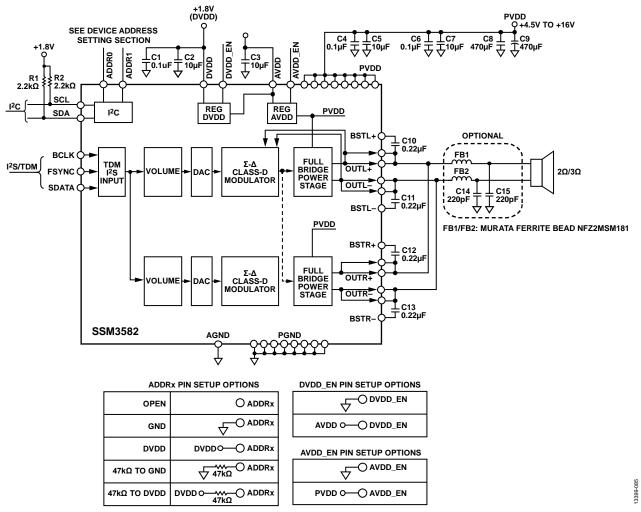

| Typical Application Circuit                       |

| Outline Dimensions                                |

| Ordering Guide59                                  |

30

#### **REVISION HISTORY**

5/2019—Rev. 0 to Rev. A

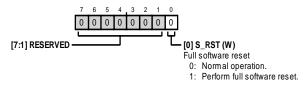

Changes to Address: 0x04, Reset: 0xA1, Name: POWER\_CTRL Section and Table 28......40

4/2016—Revision 0: Initial Version

### **GENERAL DESCRIPTION**

The SSM3582 is a fully integrated, high efficiency, digital input stereo Class-D audio amplifier. It can operate from a single supply, and requires only a few external components, significantly reducing the circuit bill of materials.

A proprietary, spread spectrum  $\Sigma$ - $\Delta$  modulation scheme enables direct connection to the speaker, and ensures state-of-the-art analog performance while lowering radiated emissions compared to other Class-D architectures. An optional ultralow electromagnetic interference (EMI) mode significantly reduces radiated emissions above 100 MHz, enabling longer speaker cable lengths. Audio is transmitted digitally to the amplifier, minimizing the possibility of signal corruption in digital environments. The amplifier provides outstanding analog performance, with an over 106 dB signal-to-noise ratio and a vanishingly low 0.004% THD + N.

The SSM3582 operates from a single 4.5 V to 16 V supply, and is capable of delivering 2  $\times$  15 W rms continuously into 8  $\Omega$  and 4  $\Omega$  loads at <1% total harmonic distortion (THD). The efficient modulation scheme maintains excellent power efficiency over a wide range of impedances: 93% into an 8  $\Omega$  load and 90% into a 4  $\Omega$  load. Optimization of the output pulse maintains performance at impedances as low as 3  $\Omega/5~\mu H$ , enabling its use with extended bandwidth tweeters.

The pulse code modulation (PCM) audio serial port supports most common protocols, such as I<sup>2</sup>S, left justified, and time division multiplexing (TDM), and can address up to 16 devices on a single interface, for up to 32 audio playback channels.

IC operation is controlled through a dedicated  $I^2C$  interface. The two ADDRx pins (2×, 5-level) define up to 16 individual addresses in  $I^2C$  and standalone modes, and automatically set the default TDM slots attribution.

A micropower shutdown mode is triggered by removing the digital audio interface clock, with a typical current of <1  $\mu$ A. A software power-down mode is also available.

An automatic power-down feature shuts down the amplifier and the digital-to-analog converter (DAC) when no signal is present at the input, minimizing power consumption during digital silence. The device restarts when nonzero data is present at the input. Mute and unmute transitions are pop/click free.

The SSM3582 is specified over the commercial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C. The device has built-in thermal shutdown and output short-circuit protection, as well as an early thermal warning with programmable gain limiting to maintain operation.

The SSM3582 is available in a 40-lead, 6 mm  $\times$  6 mm lead frame chip scale package (LFCSP), with a thermal pad to improve heat dissipation.

# **SPECIFICATIONS**

$PV_{DD}$  = 12 V,  $AV_{DD}$  = 5 V (external),  $DV_{DD}$  = 1.8 V (external),  $R_L$  = 8  $\Omega$  + 33  $\mu$ H, BCLK = 3.072 MHz, FSYNC = 48 kHz,  $T_A$  = -40°C to +85°C, unless otherwise noted. The measurements are taken with a 20 kHz AES17 low-pass filter. The other load impedances used are 4  $\Omega$  + 15  $\mu$ H and 3  $\Omega$  + 10  $\mu$ H. Measurements are taken with a 20 kHz AES17 low-pass filter, unless otherwise noted.

Table 1.

| Parameter                | Symbol | Test Conditions/Comments                                                            | Min | Тур   | Max | Unit |

|--------------------------|--------|-------------------------------------------------------------------------------------|-----|-------|-----|------|

| DEVICE CHARACTERISTICS   |        |                                                                                     |     |       |     |      |

| Output Power Per Channel | Po     |                                                                                     |     |       |     |      |

| Stereo Mode              |        | f = 1 kHz, both channels driven                                                     |     |       |     |      |

|                          |        | $R_L = 8 \Omega$ , THD + N < 1%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 16 V$             |     | 14.4  |     | W    |

|                          |        | $R_L = 8 \Omega$ , THD + N < 1%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 12 V$             |     | 8.1   |     | W    |

|                          |        | $R_L = 8 \Omega$ , THD + N < 1%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 7 V$              |     | 2.76  |     | W    |

|                          |        | $R_L = 8 \Omega$ , THD + N < 1%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 5 V$              |     | 1.41  |     | W    |

|                          |        | $R_L = 8 \Omega$ , THD + N = 10%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 16 V$            |     | 18    |     | W    |

|                          |        | $R_L = 8 \Omega$ , THD + N = 10%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 12 V$            |     | 10    |     | W    |

|                          |        | $R_L = 8 \Omega$ , THD + N = 10%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 7 V$             |     | 3.43  |     | W    |

|                          |        | $R_L = 8 \Omega$ , THD + N = 10%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 5 V$             |     | 1.75  |     | W    |

|                          |        | $R_L = 4 \Omega$ , THD + N < 1%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 16 V$             |     | 25.6  |     | W    |

|                          |        | $R_L = 4 \Omega$ , THD + N < 1%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 12 V$             |     | 14.67 |     | W    |

|                          |        | $R_L = 4 \Omega$ , THD + N < 1%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 7 V$              |     | 5.06  |     | W    |

|                          |        | $R_L = 4 \Omega$ , THD +N < 1%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 5 V$               |     | 2.6   |     | W    |

|                          |        | $R_L = 4 \Omega$ , THD + N = 10%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 16 V$            |     | 31.76 |     | W    |

|                          |        | $R_L = 4 \Omega$ , THD + N = 10%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 12 V$            |     | 18.31 |     | W    |

|                          |        | $R_L = 4 \Omega$ , THD + N = 10%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 7 V$             |     | 6.3   |     | W    |

|                          |        | $R_L = 4 \Omega$ , THD + N = 10%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 5 V$             |     | 3.21  |     | W    |

| Mono Mode                |        | f = 1  kHz                                                                          |     |       |     |      |

|                          |        | $R_L = 3 \Omega$ , THD +N < 1%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 16 V$              |     | 36.11 |     | W    |

|                          |        | $R_L = 3 \Omega$ , THD +N < 1%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 12 V$              |     | 20.46 |     | W    |

|                          |        | $R_L = 3 \Omega$ , THD +N < 1%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 7 V$               |     | 7     |     | W    |

|                          |        | $R_L = 3 \Omega$ , THD +N < 1%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 5 V$               |     | 3.58  |     | W    |

|                          |        | $R_L = 3 \Omega$ , THD + N = 10%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 16 V$            |     | 44.96 |     | W    |

|                          |        | $R_L = 3 \Omega$ , THD + N = 10%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 12 V$            |     | 25.49 |     | W    |

|                          |        | $R_L = 3 \Omega$ , THD + N = 10%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 7 V$             |     | 8.7   |     | W    |

|                          |        | $R_L = 3 \Omega$ , THD + N = 10%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 5 V$             |     | 4.43  |     | W    |

|                          |        | $R_L = 2 \Omega$ , THD + N < 1%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 16 V$             |     | 49.69 |     | W    |

|                          |        | $R_L = 2 \Omega$ , THD +N < 1%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 12 V$              |     | 28.55 |     | W    |

|                          |        | $R_L = 2 \Omega$ , THD +N < 1%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 7 V$               |     | 9.85  |     | W    |

|                          |        | $R_L = 2 \Omega$ , THD +N < 1%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 5 V$               |     | 5     |     | W    |

|                          |        | $R_L = 2 \Omega$ , THD + N = 10%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 16 V$            |     | 62.4  |     | W    |

|                          |        | $R_L = 2 \Omega$ , THD + N = 10%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 12 V$            |     | 35.5  |     | W    |

|                          |        | $R_L = 2 \Omega$ , THD + N = 10%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 7 V$             |     | 12.22 |     | W    |

|                          |        | $R_L = 2 \Omega$ , THD + N = 10%, f = 1 kHz, 20 kHz BW, $PV_{DD} = 5 V$             |     | 6.22  |     | W    |

| Minimal Load Inductance  |        | Speaker inductance                                                                  | 5   |       |     | μН   |

| Efficiency               | η      |                                                                                     |     |       |     | ľ    |

| Stereo Mode              |        | Both channels driven                                                                |     |       |     |      |

|                          |        | $P_0 = 10 \text{ W}, R_L = 8 \Omega, PV_{DD} = 12 \text{ V}$                        |     | 94    |     | %    |

|                          |        | $P_0 = 10 \text{ W}, R_L = 8 \Omega, PV_{DD} = 12 \text{ V} \text{ (low EMI mode)}$ |     | 93.8  |     | %    |

|                          |        | $P_0 = 18 \text{ W}, R_L = 4 \Omega, PV_{DD} = 12 \text{ V}$                        |     | 90.6  |     | %    |

|                          |        | $P_0 = 15 \text{ W}, R_L = 4 \Omega, PV_{DD} = 12 \text{ V} \text{ (low EMI mode)}$ |     | 89.5  |     | %    |

| Mono Mode                |        | , - , - , - , - , , , , , , , , , , , ,                                             |     | -     |     |      |

|                          |        | $P_0 = 25 \text{ W}, R_1 = 3 \Omega, PV_{DD} = 12 \text{ V}$                        |     | 92.3  |     | %    |

|                          |        | $P_0 = 25 \text{ W}, R_L = 3 \Omega, PV_{DD} = 12 \text{ V (low EMI mode)}$         |     | 92.1  |     | %    |

|                          |        | $P_0 = 35 \text{ W}, R_L = 2 \Omega, PV_{DD} = 12 \text{ V}$                        |     | 89.9  |     | %    |

|                          |        | $P_0 = 35 \text{ W}, R_L = 2 \Omega, PV_{DD} = 12 \text{ V (low EMI mode)}$         |     | 89.7  |     | %    |

Rev. A Page 4 of 59

| Parameter                                      | Symbol             | Test Conditions/Comments                                                                                                | Min   | Тур    | Max          | Unit     |

|------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------|-------|--------|--------------|----------|

| Total Harmonic Distortion +<br>Noise           | THD + N            | $P_0 = 5 \text{ W into } 8 \Omega, f = 1 \text{ kHz, } PV_{DD} = 12 \text{ V}$                                          |       | 0.004  |              | %        |

| Output Stage On Resistance                     | Ron                |                                                                                                                         |       | 100    |              | mΩ       |

| Overcurrent Protection Trip Point              | loc                |                                                                                                                         |       | 6      |              | A peak   |

| Average Switching Frequency                    | f <sub>sw</sub>    |                                                                                                                         |       | 300    |              | kHz      |

| Differential Output Offset<br>Voltage          | Voos               | $A_V = 19 \text{ dB}$                                                                                                   |       | 1      |              | mV       |

| Crosstalk between Left and<br>Right            |                    | Measured at 1 kHz with regards to full-scale output                                                                     |       | 100    |              | dB       |

| POWER SUPPLIES                                 |                    |                                                                                                                         |       |        |              |          |

| Supply Voltage Range                           | $PV_{DD}$          |                                                                                                                         | 4.5   |        | 16           | V        |

| , 3                                            | $AV_{DD}$          |                                                                                                                         | 4.5   | 5.0    | 5.5          | V        |

|                                                | $DV_DD$            |                                                                                                                         | 1.62  | 1.8    | 1.98         | V        |

| Power Supply Rejection<br>Ratio                | PSRR               |                                                                                                                         |       |        |              |          |

| AC                                             | PSRR <sub>AC</sub> | V <sub>RIPPLE</sub> =100 mV rms at 1 kHz                                                                                |       | 86     |              | dB       |

|                                                |                    | V <sub>RIPPLE</sub> =1 V rms at 1 kHz                                                                                   |       | 88     |              | dB       |

| ANALOG GAIN                                    | A <sub>V</sub>     | Measured with 0 dBFS input at 1 kHz                                                                                     |       |        |              |          |

| Gain = 00                                      |                    | PV <sub>DD</sub> ≥ 6.3 V                                                                                                |       | 6.2    |              | V peak   |

| Gain = 01                                      |                    | $PV_{DD} \ge 9V$                                                                                                        |       | 8.75   |              | V peak   |

| Gain = 10                                      |                    | PV <sub>DD</sub> ≥ 12.6 V                                                                                               |       | 12.5   |              | V peak   |

| Gain = 11                                      |                    | PV <sub>DD</sub> = 16 V                                                                                                 |       | 15.5   |              | V peak   |

| SHUTDOWN CONTROL <sup>1</sup>                  |                    | 1.100                                                                                                                   |       | 13.3   |              | v peak   |

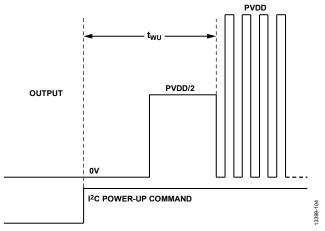

| Turn On Time, Volume<br>Ramp Disabled          | t <sub>wu</sub>    | Time from SPWDN = 0 to output switching, DAC_HV = 1 or DAC_MUTE_x = 1, two = 4 FSYNC cycles to 7 FSYNC cycles + 7.68 ms |       |        |              |          |

| $f_S = 12 \text{ kHz}$                         |                    | 7.00 113                                                                                                                | 8.01  |        | 8.27         | ms       |

| $f_S = 24 \text{ kHz}$                         |                    |                                                                                                                         | 7.84  |        | 7.98         | ms       |

| $f_S = 48 \text{ kHz}$                         |                    |                                                                                                                         | 7.76  |        | 7.83         | ms       |

| $f_S = 96 \text{ kHz}$                         |                    |                                                                                                                         | 7.72  |        | 7.76         | ms       |

| $f_S = 192 \text{ kHz}$                        |                    |                                                                                                                         | 7.72  |        | 7.70<br>7.72 | ms       |

| Turn On Time, Volume<br>Ramp Enabled           | twur               | Time from SPWDN = 0 to full volume output switching, DAC_HV = 0 and DAC_MUTE_x = 0, VOL_x = 0x40                        | 7.70  |        | 7.72         | 1115     |

| $f_S = 12 \text{ kHz}$                         |                    | twus = twu + 15.83 ms                                                                                                   | 23.84 |        | 24.10        | ms       |

| $f_S = 24 \text{ kHz}$                         |                    | twur = twu + 15.83 ms                                                                                                   | 23.67 |        | 23.81        | ms       |

| $f_S = 48 \text{ kHz}$                         |                    | twu <sub>R</sub> = twu + 15.83 ms                                                                                       | 23.59 |        | 23.66        | ms       |

| $f_S = 96 \text{ kHz}$                         |                    | twur = twu + 7.92 ms                                                                                                    | 15.64 |        | 15.68        | ms       |

| $f_S = 192 \text{ kHz}$                        |                    | twur = twu + 0.99 ms                                                                                                    | 8.69  |        | 8.71         | ms       |

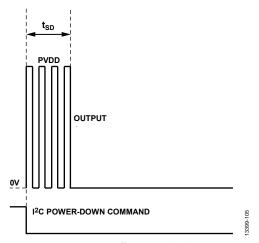

| Turn Off Time, Volume<br>Ramp Disabled         | t <sub>SD</sub>    | Time from SPWDN = 1 to full power-down, DAC_HV = 1 or DAC_MUTE_x = 1                                                    | 0.09  | 100    | 0.7 1        | μs       |

| Turn Off Time, Volume<br>Ramp Enabled          | t <sub>SDR</sub>   | Time from SPWDN = 1 to full power-down, DAC_HV = 0 and DAC_MUTE_ $x = 0$ , VOL_ $x = 0x40$                              |       |        |              |          |

| fs = 12 kHz                                    |                    | $t_{SDR} = t_{SD} + 15.83 \text{ ms}$                                                                                   |       | 15.932 |              | ms       |

| $f_S = 24 \text{ kHz}$                         |                    | $t_{SDR} = t_{SD} + 15.83 \text{ ms}$<br>$t_{SDR} = t_{SD} + 15.83 \text{ ms}$                                          |       | 15.932 |              | ms       |

| $f_S = 48 \text{ kHz}$                         |                    | $t_{SDR} = t_{SD} + 15.83 \text{ ms}$<br>$t_{SDR} = t_{SD} + 15.83 \text{ ms}$                                          |       | 15.932 |              |          |

| $f_S = 46 \text{ kHz}$                         |                    | $t_{SDR} = t_{SD} + 15.65 \text{ m/s}$<br>$t_{SDR} = t_{SD} + 7.92 \text{ m/s}$                                         |       | 8.016  |              | ms<br>ms |

| $f_S = 90 \text{ kHz}$ $f_S = 192 \text{ kHz}$ |                    | $t_{SDR} = t_{SD} + 7.92 \text{ ms}$<br>$t_{SDR} = t_{SD} + 0.99 \text{ ms}$                                            |       | 1.09   |              | ms       |

|                                                | 7                  | LSDK - LSD + 0.22 III2                                                                                                  | 100   | 1.09   |              | ms       |

| Output Impedance                               | Z <sub>out</sub>   |                                                                                                                         | 100   |        |              | kΩ       |

| Parameter                                   | Symbol | Test Conditions/Comments                                                                                 | Min | Тур   | Max  | Unit   |

|---------------------------------------------|--------|----------------------------------------------------------------------------------------------------------|-----|-------|------|--------|

| NOISE PERFORMANCE <sup>2</sup>              |        | Stereo mode                                                                                              |     |       |      |        |

| Output Voltage Noise                        | en     | $f = 20$ Hz to 20 kHz, A weighted, $PV_{DD} = 12$ V, $8 \Omega$                                          |     | 37.8  |      | μV rms |

|                                             |        | $f = 20$ Hz to 20 kHz, A weighted, $PV_{DD} = 16$ V, $8 \Omega$                                          |     | 38.5  |      | μV rms |

|                                             |        | $f = 20$ Hz to 20 kHz, A weighted, $PV_{DD} = 12$ V, $4 \Omega$                                          |     | 36.8  |      | μV rms |

|                                             |        | $f = 20$ Hz to 20 kHz, A weighted, $PV_{DD} = 16$ V, $4 \Omega$                                          |     | 36.3  |      | μV rms |

| Signal-to-Noise Ratio                       | SNR    | $P_0 = 8.1 \text{ W}, R_L = 8 \Omega, A_V = 19 \text{ dB}, PV_{DD} = 12 \text{ V}, A \text{ weighted}$   |     | 106.5 |      | dB     |

|                                             |        | $P_0 = 14.4 \text{ W}, R_L = 8 \Omega, A_V = 21 \text{ dB}, PV_{DD} = 16 \text{ V}, A \text{ weighted}$  |     | 108.9 |      | dB     |

|                                             |        | $P_0 = 14.67 \text{ W}, R_L = 4 \Omega, A_V = 19 \text{ dB}, PV_{DD} = 12 \text{ V}, A \text{ weighted}$ |     | 106.3 |      | dB     |

|                                             |        | $P_0 = 25.58 \text{ W}, R_L = 4 \Omega, A_V = 21 \text{ dB}, PV_{DD} = 16 \text{ V}, A \text{ weighted}$ |     | 108.9 |      | dB     |

| PV <sub>DD</sub> ADC PERFORMANCE            |        |                                                                                                          |     |       |      |        |

| PV <sub>DD</sub> Sense Full-Scale<br>Range  |        | PV <sub>DD</sub> with full-scale ADC output                                                              | 3.8 |       | 16.2 | V      |

| PV <sub>DD</sub> Sense Absolute<br>Accuracy |        | $PV_{DD} = 15 V$                                                                                         | -8  |       | +8   | LSB    |

|                                             |        | $PV_{DD} = 5 V$                                                                                          | -6  |       | +6   | LSB    |

| Resolution                                  |        | Unsigned 8-bit output with 3.8 V offset                                                                  |     | 8     |      | Bits   |

| Temperature Sense ADC                       |        |                                                                                                          |     |       |      |        |

| Temperature Sense Range                     |        |                                                                                                          | -60 |       | +160 | °C     |

| Temperature Sense<br>Accuracy               |        |                                                                                                          |     | ±5    |      | °C     |

| DIETEMPERATURE                              |        |                                                                                                          |     |       |      |        |

| Overtemperature Warning                     |        |                                                                                                          |     | 117   |      | °C     |

| Overtemperature Protection                  |        |                                                                                                          |     | 145   |      | °C     |

| UNDERVOLTAGE FAULT                          |        |                                                                                                          |     |       |      |        |

| $AV_DD$                                     |        |                                                                                                          |     | 3.6   |      | V      |

| $PV_{DD}$                                   |        |                                                                                                          |     | 3.6   |      | V      |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design.

Software master power-down indicates that the clocks are turned off. Automatic power-down indicates that there is no dither or zero input signal with clocks on; the device enters soft power-down after 2048 cycles of zero input values. Quiescent indicates triangular dither with zero input signal. All specifications are typical, with a 48 kHz sample rate, in stereo mode, unless otherwise noted.

Table 2. Power Supply Current Consumption, No Load<sup>1</sup>

| Edge Rate       |                       |                            |                        | $I_{PVDD}$              |                         | I <sub>DVDD</sub>        | I <sub>AVDD</sub>      |      |

|-----------------|-----------------------|----------------------------|------------------------|-------------------------|-------------------------|--------------------------|------------------------|------|

| Control<br>Mode | Internal<br>Regulator | Test Conditions            | PV <sub>DD</sub> = 5 V | PV <sub>DD</sub> = 12 V | PV <sub>DD</sub> = 16 V | PV <sub>DD</sub> = 1.8 V | PV <sub>DD</sub> = 5 V | Unit |

| Normal          | Disabled              | Software master power-down | 0.065                  | 0.065                   | 0.065                   | 2.68                     | 7.542                  | μΑ   |

|                 |                       | Automatic power-down       | 0.065                  | 0.065                   | 0.065                   | 43.72                    | 7.542                  | μΑ   |

|                 |                       | Quiescent                  | 2.54                   | 4.94                    | 6.25                    | 0.945                    | 6.335                  | mA   |

|                 | Enabled               | Software master power-down | 0.065                  | 0.065                   | 0.065                   | N/A                      | N/A                    | μΑ   |

|                 |                       | Automatic power-down       | 209                    | 286                     | 329                     | N/A                      | N/A                    | μΑ   |

|                 |                       | Quiescent                  | 9.78                   | 12.38                   | 14.05                   | N/A                      | N/A                    | mA   |

| Low EMI         | Disabled              | Software master power-down | 0.065                  | 0.065                   | 0.065                   | 2.68                     | 7.542                  | μΑ   |

|                 |                       | Automatic power-down       | 0.065                  | 0.065                   | 0.065                   | 43.72                    | 7.542                  | μΑ   |

|                 |                       | Quiescent                  | 2.56                   | 5.01                    | 6.31                    | 0.945                    | 6.171                  | mA   |

|                 | Enabled               | Software master power-down | 0.065                  | 0.065                   | 0.065                   | N/A                      | N/A                    | μΑ   |

|                 |                       | Automatic power-down       | 209                    | 286                     | 329                     | N/A                      | N/A                    | μΑ   |

|                 |                       | Quiescent                  | 9.69                   | 12.09                   | 13.74                   | N/A                      | N/A                    | mA   |

<sup>&</sup>lt;sup>1</sup> N/A means not applicable.

<sup>&</sup>lt;sup>2</sup> Noise performance is based on the bench data for  $T_A = -40$ °C to +85°C.

Table 3. Power Supply Current Consumption, 4  $\Omega$  + 15  $\mu H^1$

| Edge Rate       |                       |                            |                                      | I <sub>PVDD</sub>       |                         | I <sub>DVDD</sub>        | I <sub>AVDD</sub>                    |      |

|-----------------|-----------------------|----------------------------|--------------------------------------|-------------------------|-------------------------|--------------------------|--------------------------------------|------|

| Control<br>Mode | Internal<br>Regulator | Test Conditions            | <b>PV</b> <sub>DD</sub> = <b>5 V</b> | PV <sub>DD</sub> = 12 V | PV <sub>DD</sub> = 16 V | PV <sub>DD</sub> = 1.8 V | <b>PV</b> <sub>DD</sub> = <b>5 V</b> | Unit |

| Normal          | Disabled              | Software master power-down | 0.065                                | 0.065                   | 0.065                   | 2.68                     | 7.542                                | μΑ   |

|                 |                       | Automatic power-down       | 0.065                                | 0.065                   | 0.065                   | 43.72                    | 7.542                                | μΑ   |

|                 |                       | Quiescent                  | 2.6                                  | 4.93                    | 6.25                    | 0.945                    | 6.477                                | mA   |

|                 | Enabled               | Software master power-down | 0.065                                | 0.065                   | 0.065                   | N/A                      | N/A                                  | μΑ   |

|                 |                       | Automatic power-down       | 209                                  | 286                     | 329                     | N/A                      | N/A                                  | μΑ   |

|                 |                       | Quiescent                  | 9.83                                 | 12.34                   | 13.58                   | N/A                      | N/A                                  | mA   |

| Low EMI         | Disabled              | Software master power-down | 0.065                                | 0.065                   | 0.065                   | 2.68                     | 7.542                                | μΑ   |

|                 |                       | Automatic power-down       | 0.065                                | 0.065                   | 0.065                   | 43.72                    | 7.542                                | μΑ   |

|                 |                       | Quiescent                  | 2.51                                 | 4.62                    | 5.6                     | 0.945                    | 6.182                                | mA   |

|                 | Enabled               | Software master power-down | 0.065                                | 0.065                   | 0.065                   | N/A                      | N/A                                  | μΑ   |

|                 |                       | Automatic power-down       | 209                                  | 286                     | 329                     | N/A                      | N/A                                  | μΑ   |

|                 |                       | Quiescent                  | 9.64                                 | 11.86                   | 12.87                   | N/A                      | N/A                                  | mA   |

<sup>&</sup>lt;sup>1</sup> N/A means not applicable.

Table 4. Power Supply Current Consumption, 8  $\Omega$  + 33  $\mu H^1$

| Edge Rate       |                       |                            |                                      | I <sub>PVDD</sub>       |                         | I <sub>DVDD</sub>        | I <sub>AVDD</sub>      |      |

|-----------------|-----------------------|----------------------------|--------------------------------------|-------------------------|-------------------------|--------------------------|------------------------|------|

| Control<br>Mode | Internal<br>Regulator | Test Conditions            | <b>PV</b> <sub>DD</sub> = <b>5 V</b> | PV <sub>DD</sub> = 12 V | PV <sub>DD</sub> = 16 V | PV <sub>DD</sub> = 1.8 V | PV <sub>DD</sub> = 5 V | Unit |

| Normal          | Disabled              | Software master power-down | 0.065                                | 0.065                   | 0.065                   | 2.68                     | 7.542                  | μΑ   |

|                 |                       | Automatic power-down       | 0.065                                | 0.065                   | 0.065                   | 43.72                    | 7.542                  | μΑ   |

|                 |                       | Quiescent                  | 2.59                                 | 5.02                    | 6.31                    | 0.942                    | 6.432                  | mA   |

|                 | Enabled               | Software master power-down | 0.065                                | 0.065                   | 0.065                   | N/A                      | N/A                    | μΑ   |

|                 |                       | Automatic power-down       | 209                                  | 286                     | 329                     | N/A                      | N/A                    | μΑ   |

|                 |                       | Quiescent                  | 9.82                                 | 12.39                   | 13.73                   | N/A                      | N/A                    | mA   |

| Low EMI         | Disabled              | Software master power-down | 0.065                                | 0.065                   | 0.065                   | 2.68                     | 7.542                  | μΑ   |

|                 |                       | Automatic power-down       | 0.065                                | 0.065                   | 0.065                   | 43.72                    | 7.542                  | μΑ   |

|                 |                       | Quiescent                  | 2.57                                 | 4.86                    | 6.02                    | 0.942                    | 6.232                  | mA   |

|                 | Enabled               | Software master power-down | 0.065                                | 0.065                   | 0.065                   | N/A                      | N/A                    | μΑ   |

|                 |                       | Automatic power-down       | 209                                  | 286                     | 329                     | N/A                      | N/A                    | μΑ   |

|                 |                       | Quiescent                  | 9.65                                 | 12.02                   | 13.18                   | N/A                      | N/A                    | mA   |

<sup>&</sup>lt;sup>1</sup> N/A means not applicable.

**Table 5. Power-Down Current**

| Parameter          | Symbol            | Test Conditions/Comments                                                        | Min | Тур   | Max | Unit |

|--------------------|-------------------|---------------------------------------------------------------------------------|-----|-------|-----|------|

| POWER-DOWN CURRENT |                   | External AVDD = 5 V and DVDD = 1.8 V, software master power-down, no BCLK/FSYNC |     |       |     |      |

|                    |                   | $PV_{DD} = 5 V$                                                                 |     | 65    |     | nA   |

|                    |                   | $PV_{DD} = 12 V$                                                                |     | 65    |     | nA   |

|                    |                   | $PV_{DD} = 16 V$                                                                |     | 65    |     | nA   |

|                    | I <sub>AVDD</sub> | AVDD = 5 V external                                                             |     | 7.542 |     | μΑ   |

|                    | I <sub>DVDD</sub> | DVDD = 1.8 V external                                                           |     | 2.7   |     | μΑ   |

#### **DIGITAL INPUT/OUTPUT SPECIFICATIONS**

Table 6.

| Parameter                                    | Min                  | Тур | Max                   | Unit | Test Conditions/Comments |

|----------------------------------------------|----------------------|-----|-----------------------|------|--------------------------|

| INPUT VOLTAGE <sup>1</sup>                   |                      |     |                       |      |                          |

| BCLK, FSYNC, SDATA, SCL, and SDA Pins        |                      |     |                       |      |                          |

| High (V <sub>I</sub> H)                      | $0.7 \times DV_{DD}$ |     | 5.5                   | V    |                          |

| Low (V <sub>IL</sub> )                       | -0.3                 |     | $+0.3 \times DV_{DD}$ | V    |                          |

| INPUT LEAKAGE                                |                      |     |                       |      |                          |

| BCLK, FSYNC, SDATA, ADDRx, SCL, and SDA Pins |                      |     |                       |      |                          |

| High (I⊪)                                    |                      |     | 1                     | μΑ   |                          |

| Low (I <sub>IL</sub> )                       |                      |     | 1                     | μΑ   |                          |

| INPUT CAPACITANCE                            |                      |     | 5                     | рF   |                          |

| OUTPUT DRIVE STRENGTH <sup>1</sup>           |                      |     |                       |      |                          |

| SDA                                          | 3                    |     | 5                     | mA   |                          |

| SAMPLE RATE (FSYNC FREQUENCY)                | 8                    |     | 192                   | kHz  |                          |

<sup>1</sup> The pull-up resistor for SCL and SDA must be scaled according to the external pull-up voltage in the system. The typical value for a pull-up resistor for 1.8 V is 2.2 kΩ.

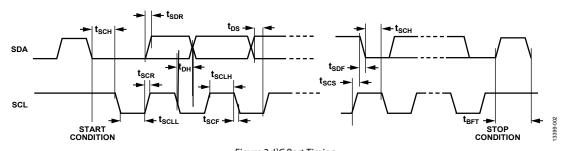

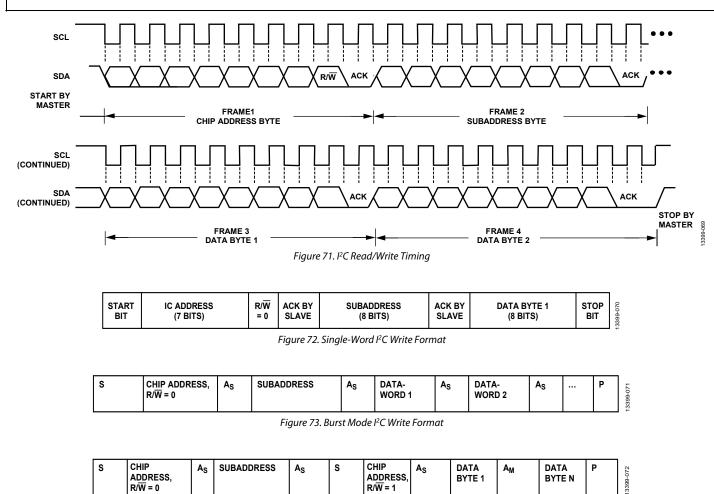

#### **DIGITAL TIMING SPECIFICATIONS**

All timing specifications are given for the default setting (I<sup>2</sup>S mode) of the serial input port.

Table 7.

|                         |      | Limit |      |                                                            |

|-------------------------|------|-------|------|------------------------------------------------------------|

| Parameter               | Min  | Max   | Unit | Description                                                |

| I <sup>2</sup> C PORT   |      |       |      |                                                            |

| $f_{SCL}$               |      | 400   | kHz  | SCL frequency                                              |

| t <sub>SCLH</sub>       | 0.26 |       | μs   | SCL high                                                   |

| t <sub>SCLL</sub>       | 0.5  |       | μs   | SCL low                                                    |

| t <sub>SCS</sub>        | 0.26 |       | μs   | Setup time; relevant for repeated start condition          |

| t <sub>SCH</sub>        | 0.26 |       | μs   | Hold time; after this period, the first clock is generated |

| $t_{DS}$                | 50   |       | ns   | Data setup time                                            |

| $t_DH$                  | 0.14 |       | μs   | Data hold time                                             |

| t <sub>SCR</sub>        |      | 120   | ns   | SCL rise time                                              |

| t <sub>SCF</sub>        |      | 120   | ns   | SCL fall time                                              |

| t <sub>SDR</sub>        |      | 120   | ns   | SDA rise time                                              |

| <b>t</b> <sub>SDF</sub> |      | 120   | ns   | SDA fall time                                              |

| <b>t</b> <sub>BFT</sub> | 0.5  |       | μs   | Bus free time (time between stop and start)                |

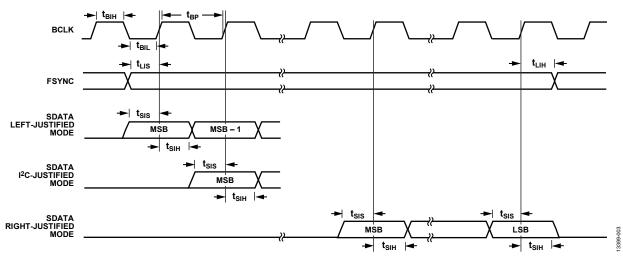

#### **DIGITAL INPUT TIMING SPECIFICATIONS**

Table 8.

|                  | Limit                             |      |                                   |

|------------------|-----------------------------------|------|-----------------------------------|

| Parameter        | T <sub>MIN</sub> T <sub>MAX</sub> | Unit | Description                       |

| SERIAL PORT      |                                   |      |                                   |

| t <sub>BIL</sub> | 10                                | ns   | BCLK low pulse width              |

| t <sub>BIH</sub> | 10                                | ns   | BCLK high pulse width             |

| t <sub>SIS</sub> | 4                                 | ns   | SDATA setup; time to BCLK rising  |

| <b>t</b> sih     | 4                                 | ns   | SDATA hold; time from BCLK rising |

| t <sub>LIS</sub> | 5                                 | ns   | FSYNC setup time to BCLK rising   |

| t <sub>LIH</sub> | 5                                 | ns   | FSYNC hold time to BCLK rising    |

| t <sub>BP</sub>  | 20                                | ns   | Minimum BCLK period               |

#### **Digital Timing Diagrams**

Figure 2. I<sup>2</sup>C Port Timing

Figure 3. Serial Input Port Timing

Figure 4. Turn On Time, Hard Volume

Figure 5. Turn Off Time, Hard Volume

## **ABSOLUTE MAXIMUM RATINGS**

Absolute maximum ratings apply at 25°C, unless otherwise noted.

Table 9.

| Parameter                            | Rating            |  |  |

|--------------------------------------|-------------------|--|--|

| PVDD Supply Voltage                  | -0.3 V to +17 V   |  |  |

| DVDD Supply Voltage                  | -0.3 V to +1.98 V |  |  |

| AVDD Supply Voltage                  | −0.3 V to +5.5 V  |  |  |

| PGND and AGND Differential           | ±0.3 V            |  |  |

| Digital Input Pins                   |                   |  |  |

| FSYNC, BCLK, SDATA, SCL, SDA         | −0.3 V to +5.5 V  |  |  |

| Analog Input Pins                    |                   |  |  |

| ADDRx                                | -0.3 V to +1.98 V |  |  |

| AVDD_EN                              | –0.3 V to +17 V   |  |  |

| DVDD_EN                              | -0.3 V to +5.5 V  |  |  |

| ESD Susceptibility                   |                   |  |  |

| Human Body Model                     | 2 kV              |  |  |

| Charged Device Model                 | 1 kV              |  |  |

| Storage Temperature Range            | −65°C to +150°C   |  |  |

| Operating Temperature Range          | −40°C to +85°C    |  |  |

| Junction Temperature Range           | −65°C to +150°C   |  |  |

| Lead Temperature (Soldering, 60 sec) | 300°C             |  |  |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  (junction to air) is specified for the worst case conditions, that is, a device soldered in a circuit board for surface-mount packages.  $\theta_{JA}$  and  $\theta_{JB}$  are determined according to JESD51-9 on a 4-layer (2s2p) printed circuit board (PCB) with natural convection cooling.

Table 10. Thermal Resistance

| Package Type               | <b>Ө</b> ЈА | θις | Unit |

|----------------------------|-------------|-----|------|

| 40-Lead, 6 mm × 6 mm LFCSP | 27          | 1.1 | °C/W |

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.**Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

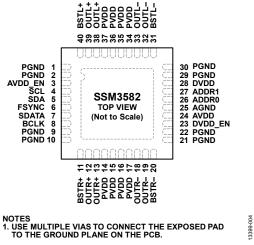

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 6. Pin Configuration

**Table 11. Pin Function Descriptions**

| Pin No. | Mnemonic | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                  |

|---------|----------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | PGND     | PWR               | Left Channel Power Stage Ground.                                                                                                                                                                                                                             |

| 2       | PGND     | PWR               | Left Channel Power Stage Ground.                                                                                                                                                                                                                             |

| 3       | AVDD_EN  | AIN               | 5 V AVDD Regulator Enable. Connect this pin to PVDD to enable the AVDD regulator or connect to AGND to disable the regulator. When this pin is connected to PVDD, the regulator is enabled. When this pin is connected to AGND, the regulator is disabled.   |

| 4       | SCL      | DIN               | I <sup>2</sup> C Clock Input.                                                                                                                                                                                                                                |

| 5       | SDA      | DIO               | I <sup>2</sup> C Data.                                                                                                                                                                                                                                       |

| 6       | FSYNC    | DIN               | I <sup>2</sup> S/TDM Frame Sync (FSYNC) Input.                                                                                                                                                                                                               |

| 7       | SDATA    | DIN               | I <sup>2</sup> S/TDM Serial Data (SDATA) Input.                                                                                                                                                                                                              |

| 8       | BCLK     | DIN               | I <sup>2</sup> S/TDM Bit Clock (BCLK) Input.                                                                                                                                                                                                                 |

| 9       | PGND     | PWR               | Right Channel Power Stage Ground.                                                                                                                                                                                                                            |

| 10      | PGND     | PWR               | Right Channel Power Stage Ground.                                                                                                                                                                                                                            |

| 11      | BSTR+    | AIN               | Bootstrap Input, Right Channel Noninverting.                                                                                                                                                                                                                 |

| 12      | OUTR+    | AOUT              | Right Channel Noninverting Output.                                                                                                                                                                                                                           |

| 13      | OUTR+    | AOUT              | Right Channel Noninverting Output.                                                                                                                                                                                                                           |

| 14      | PVDD     | PWR               | Right Channel Power Stage Supply.                                                                                                                                                                                                                            |

| 15      | PVDD     | PWR               | Right Channel Power Stage Supply.                                                                                                                                                                                                                            |

| 16      | PVDD     | PWR               | Right Channel Power Stage Supply.                                                                                                                                                                                                                            |

| 17      | PVDD     | PWR               | Right Channel Power Stage Supply.                                                                                                                                                                                                                            |

| 18      | OUTR-    | AOUT              | Right Channel Inverting Output.                                                                                                                                                                                                                              |

| 19      | OUTR-    | AOUT              | Right Channel Inverting Output.                                                                                                                                                                                                                              |

| 20      | BSTR-    | AIN               | Bootstrap Input, Right Channel Inverting.                                                                                                                                                                                                                    |

| 21      | PGND     | PWR               | Right Channel Power Stage Ground.                                                                                                                                                                                                                            |

| 22      | PGND     | PWR               | Right Channel Power Stage Ground.                                                                                                                                                                                                                            |

| 23      | DVDD_EN  | AIN               | 1.8 V DVDD Regulator Enable. Connect this pin to AVDD to enable the DVDD regulator or connect to AGND to disable the regulator. When this pin is connected to AVDD, the regulator is enabled. When this pin is connected to AGND, the regulator is disabled. |

| 24      | AVDD     | PWR               | Analog Supply 5 V Regulator Output/External 5 V Input.                                                                                                                                                                                                       |

| 25      | AGND     | PWR               | Analog Ground.                                                                                                                                                                                                                                               |

| 26      | ADDR0    | AIN               | Address Select 0 (See Table 14).                                                                                                                                                                                                                             |

| 27      | ADDR1    | AIN               | Address Select 1 (See Table 14).                                                                                                                                                                                                                             |

| 28      | DVDD     | PWR               | Digital Supply 1.8 V Regulator Output/External 1.8 V Input.                                                                                                                                                                                                  |

| 29      | PGND     | PWR               | Left Channel Power Stage Ground.                                                                                                                                                                                                                             |

| 30      | PGND     | PWR               | Left Channel Power Stage Ground.                                                                                                                                                                                                                             |

| 31      | BSTL-    | AIN               | Bootstrap Input, Left Channel Inverting.                                                                                                                                                                                                                     |

| Pin No. | Mnemonic | Type <sup>1</sup> | Description                                                                               |

|---------|----------|-------------------|-------------------------------------------------------------------------------------------|

| 32      | OUTL-    | AOUT              | Left Channel Inverting Output.                                                            |

| 33      | OUTL-    | AOUT              | Left Channel Inverting Output.                                                            |

| 34      | PVDD     | PWR               | Left Channel Power Stage Supply.                                                          |

| 35      | PVDD     | PWR               | Left Channel Power Stage Supply.                                                          |

| 36      | PVDD     | PWR               | Left Channel Power Stage Supply.                                                          |

| 37      | PVDD     | PWR               | Left Channel Power Stage Supply.                                                          |

| 38      | OUTL+    | AOUT              | Left Channel Noninverting Output.                                                         |

| 39      | OUTL+    | AOUT              | Left Channel Noninverting Output.                                                         |

| 40      | BSTL+    | AIN               | Bootstrap Input, Left Channel Noninverting.                                               |

|         | EPAD     |                   | Exposed Pad. Use multiple vias to connect the exposed pad to the ground plane on the PCB. |

<sup>&</sup>lt;sup>1</sup> PWR is power supply or ground pin, AIN is analog input, DIN is digital input, DIO is digital input/output, and AOUT is analog output.

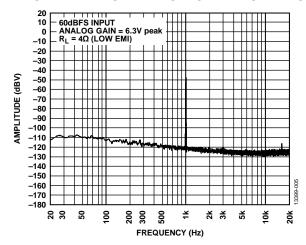

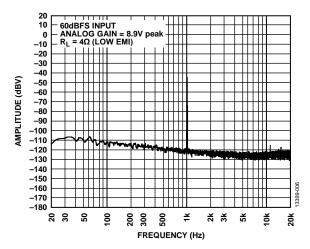

## TYPICAL PERFORMANCE CHARACTERISTICS

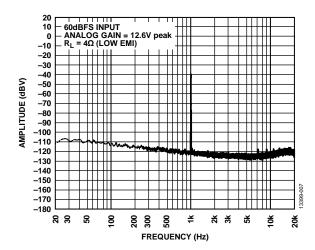

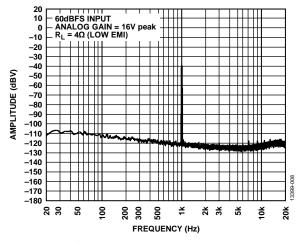

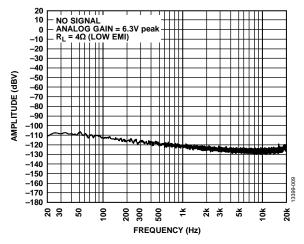

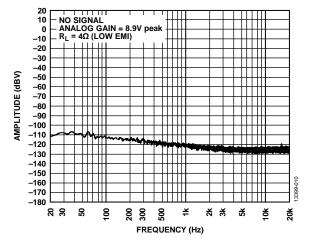

Figure 7. Amplitude vs. Frequency, 60 dBFS Input, Analog Gain = 6.3 V peak

Figure 8. Amplitude vs. Frequency, 60 dBFS Input, Analog Gain = 8.9 V peak

Figure 9. Amplitude vs. Frequency, 60 dBFS Input, Analog Gain = 12.6 V peak

Figure 10. Amplitude vs. Frequency, 60 dBFS Input, Analog Gain = 16 V peak

Figure 11. Amplitude vs. Frequency, No Signal, Analog Gain = 6.3 V peak

Figure 12. Amplitude vs. Frequency, No Signal, Analog Gain = 8.9 V peak

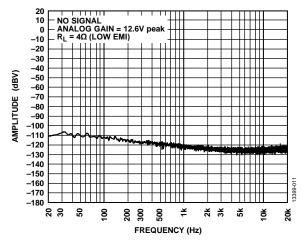

Figure 13. Amplitude vs. Frequency, No Signal, Analog Gain = 12.6 V peak

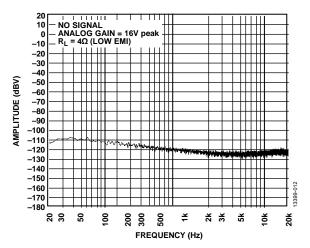

Figure 14. Amplitude vs. Frequency, No Signal, Analog Gain = 16 V peak

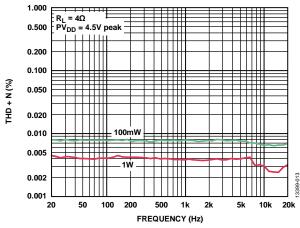

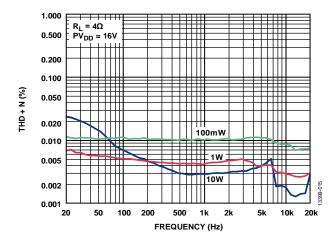

Figure 15. THD + N vs. Frequency,  $R_L = 4 \Omega$ ,  $PV_{DD} = 4.5 V$  peak

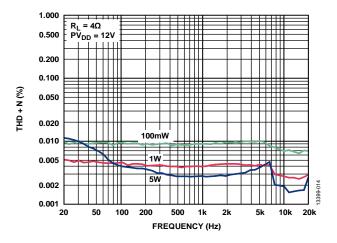

Figure 16. THD + N vs. Frequency,  $R_L = 4 \Omega$ ,  $PV_{DD} = 12 V$

Figure 17. THD + N vs. Frequency,  $R_L = 4 \Omega$ ,  $PV_{DD} = 16 V$

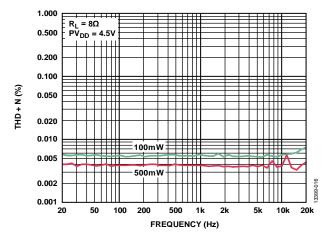

Figure 18. THD + N vs. Frequency,  $R_L = 8 \Omega$ ,  $PV_{DD} = 4.5 V$

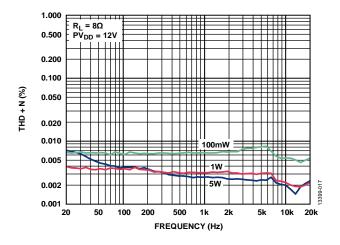

Figure 19. THD + N vs. Frequency,  $R_L = 8 \Omega$ ,  $PV_{DD} = 12 V$

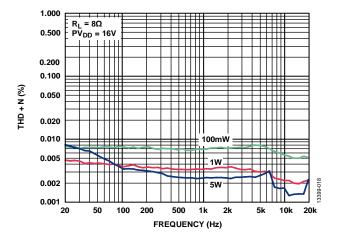

Figure 20. THD + N vs. Frequency,  $R_L = 8 \Omega$ ,  $PV_{DD} = 16 V$

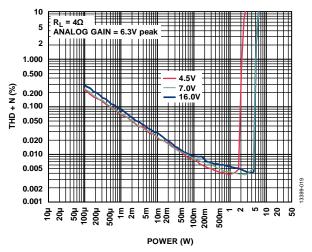

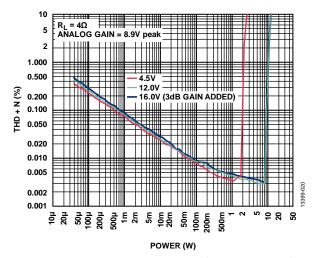

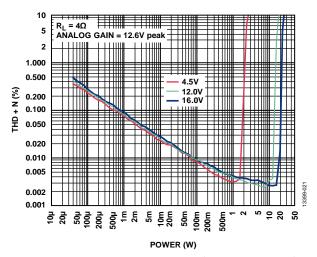

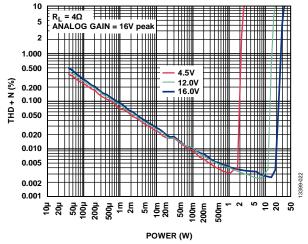

Figure 21. THD + N vs. Power,  $R_L = 4 \Omega$ , Analog Gain = 6.3 V peak

Figure 22. THD + N vs. Power,  $R_L = 4 \Omega$ , Analog Gain = 8.9 V peak

Figure 23. THD + N vs. Power,  $R_L = 4 \Omega$ , Analog Gain = 12.6 V peak

Figure 24. THD + N vs. Power,  $R_L = 4 \Omega$ , Analog Gain = 16 V peak

Figure 25. THD + N vs. Power,  $R_L = 8 \Omega$ , Analog Gain = 6.3 V peak

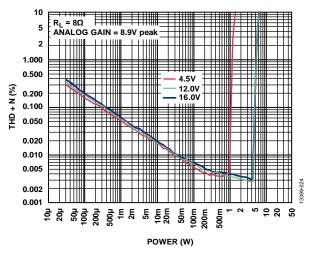

Figure 26. THD + N vs. Power,  $R_L = 8 \Omega$ , Analog Gain = 8.9 V peak

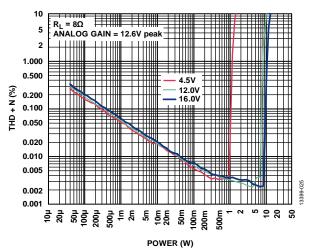

Figure 27. THD + N vs. Power,  $R_L = 8 \Omega$ , Analog Gain = 12. 6 V peak

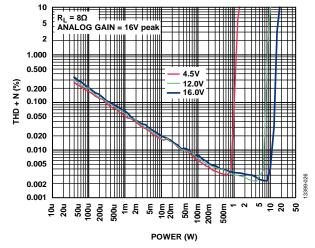

Figure 28. THD + N vs. Power,  $R_L = 8 \Omega$ , Analog Gain = 16 V peak

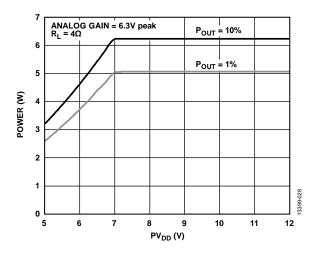

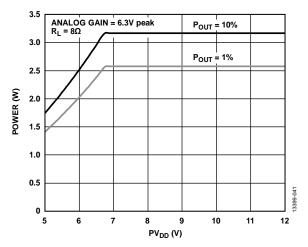

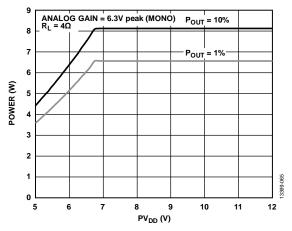

Figure 29. Power vs.  $PV_{DD}$ ,  $R_L = 4 \Omega$ , Analog Gain = 6.3 V peak

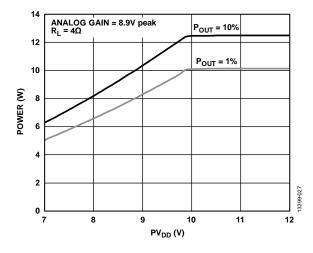

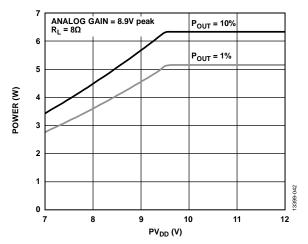

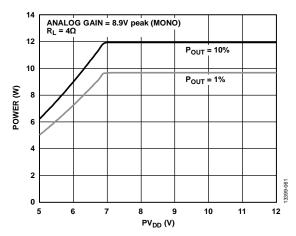

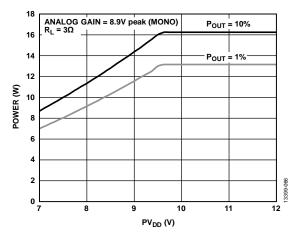

Figure 30. Power vs.  $PV_{DD}$ ,  $R_L = 4 \Omega$ , Analog Gain = 8.9 V peak

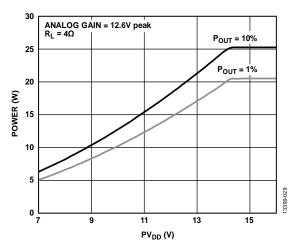

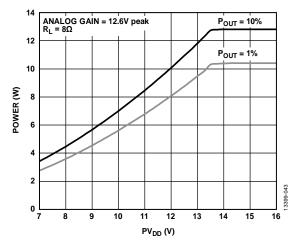

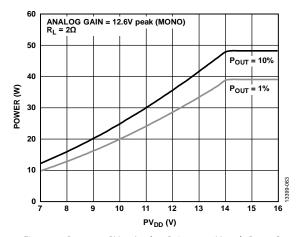

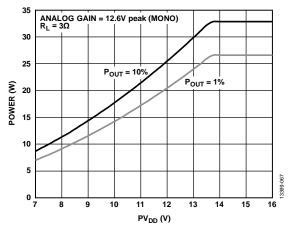

Figure 31. Power vs.  $PV_{DD}$ ,  $R_L = 4 \Omega$ , Analog Gain = 12.6 V peak

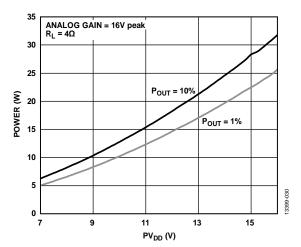

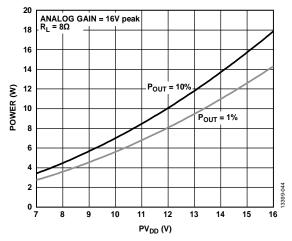

Figure 32. Power vs.  $PV_{DD}$ ,  $R_L = 4 \Omega$ , Analog Gain = 16 V peak

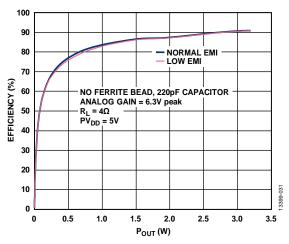

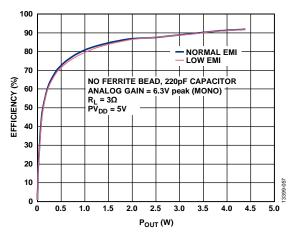

Figure 33. Efficiency vs.  $P_{OUT}$ , No Ferrite Bead, Analog Gain = 6.3 V peak,  $R_L = 4 \Omega$ ,  $PV_{DD} = 5 V$

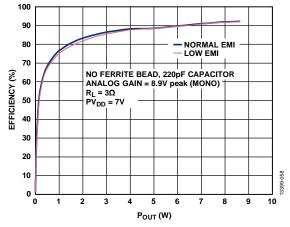

Figure 34. Efficiency vs.  $P_{OUT}$ , No Ferrite Bead, Analog Gain = 8.9 V peak,  $R_L = 4 \Omega$ ,  $PV_{DD} = 7 V$

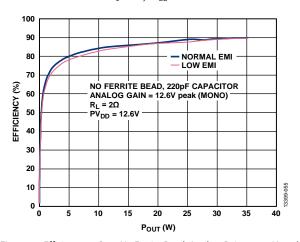

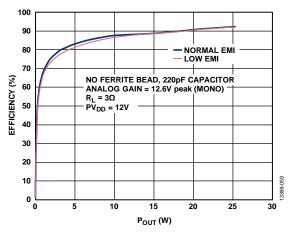

Figure 35. Efficiency vs. Pout, No Ferrite Bead, Analog Gain = 12.6 V peak,  $R_L=4\,\Omega$ ,  $PV_{DD}=12$  V

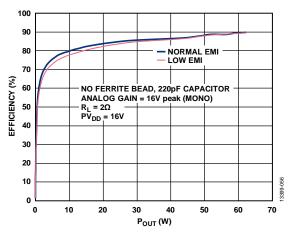

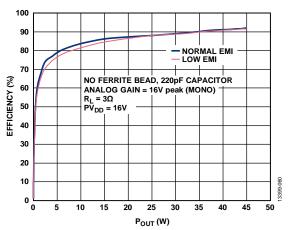

Figure 36. Efficiency vs.  $P_{OUT}$ , No Ferrite Bead, Analog Gain = 16 V peak,  $R_L = 4 \, \Omega$ ,  $PV_{DD} = 16 \, V$

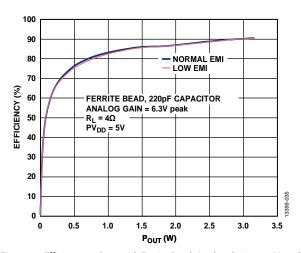

Figure 37. Efficiency vs.  $P_{OUT}$ , with Ferrite Bead, Analog Gain = 6.3 V peak,  $R_L = 4 \Omega$ ,  $PV_{DD} = 5 V$

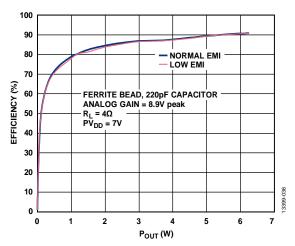

Figure 38. Efficiency vs.  $P_{OUT}$ , with Ferrite Bead, Analog Gain = 8.9 V peak,  $R_L = 4 \Omega$ ,  $PV_{DD} = 7 V$

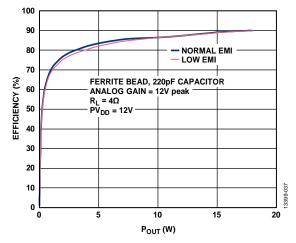

Figure 39. Efficiency vs.  $P_{OUT}$ , with Ferrite Bead, Analog Gain = 12 V peak,  $R_L = 4 \Omega$ ,  $PV_{DD} = 12 V$

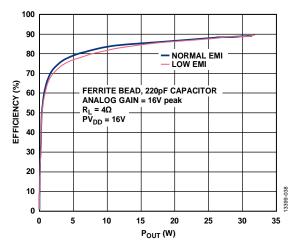

Figure 40. Efficiency vs.  $P_{OUT}$ , with Ferrite Bead, Analog Gain = 16 V peak,  $R_L = 4 \Omega$ ,  $PV_{DD} = 16 V$

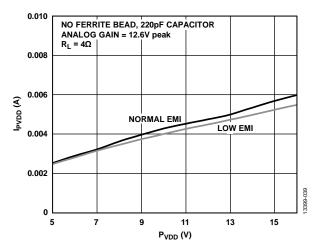

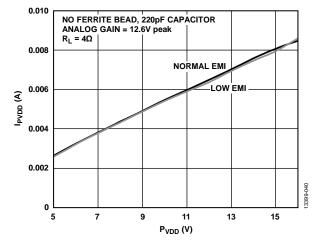

Figure 41.  $I_{PVDD}$  vs.  $PV_{DD}$ , No Ferrite Bead, Analog Gain = 12.6 V peak,  $R_L = 4 \Omega$

Figure 42.  $I_{PVDD}$  vs.  $PV_{DD}$ , No Ferrite Bead, Analog Gain = 12.6 V peak,  $R_L = 4 \Omega$

Figure 43. Power vs. PV<sub>DD</sub>, Analog Gain = 6.3 V peak,  $R_L = 8 \Omega$

Figure 44. Power vs. PV<sub>DD</sub>, Analog Gain = 8.9 V peak,  $R_L$  = 8  $\Omega$

Figure 45. Power vs. PV<sub>DD</sub>, Analog Gain = 12.6 V peak,  $R_L = 8 \Omega$

Figure 46. Power vs.  $PV_{DD}$ , Analog Gain = 16 V peak,  $R_L = 8 \Omega$

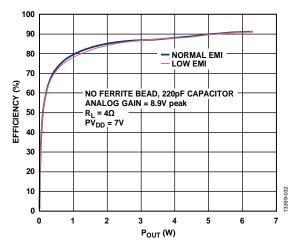

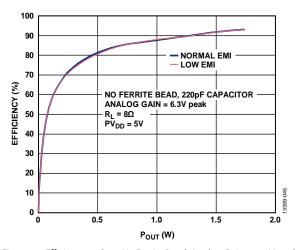

Figure 47. Efficiency vs.  $P_{OUT}$ , No Ferrite Bead, Analog Gain = 6.3 V peak,  $R_L = 8~\Omega$ ,  $PV_{DD} = 5~V$

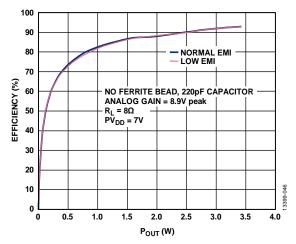

Figure 48. Efficiency vs.  $P_{OUT}$ , No Ferrite Bead, Analog Gain = 8.9 V peak,  $R_L = 8~\Omega$ ,  $PV_{DD} = 7~V$

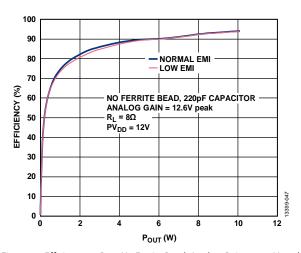

Figure 49. Efficiency vs.  $P_{OUT}$ , No Ferrite Bead, Analog Gain = 12.6 V peak,  $R_L = 8 \Omega$ ,  $PV_{DD} = 12 V$

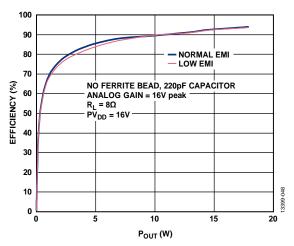

Figure 50. Efficiency vs.  $P_{OUT}$ , No Ferrite Bead, Analog Gain = 16 V peak,  $R_L = 8 \Omega$ ,  $PV_{DD} = 16 \text{ V}$

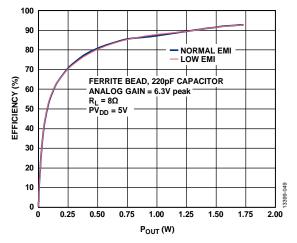

Figure 51. Efficiency vs.  $P_{OUT}$ , with Ferrite Bead, Analog Gain = 6.3 V peak,  $R_L = 8 \Omega$ ,  $PV_{DD} = 5 V$

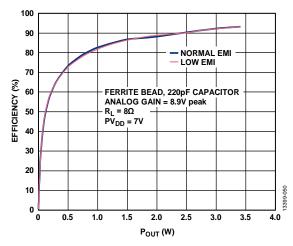

Figure 52. Efficiency vs.  $P_{OUT}$ , with Ferrite Bead, Analog Gain = 8.9 V peak,  $R_L = 8 \Omega$ ,  $PV_{DD} = 7 V$

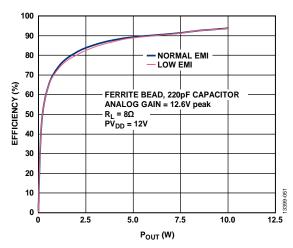

Figure 53. Efficiency vs.  $P_{OUT}$ , with Ferrite Bead, Analog Gain = 12.6 V peak,  $R_L = 8 \Omega$ ,  $PV_{DD} = 12 V$

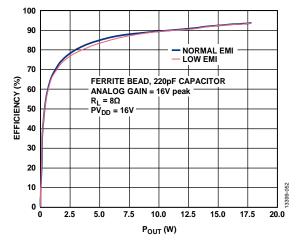

Figure 54. Efficiency vs.  $P_{OUT}$ , with Ferrite Bead, Analog Gain = 16 V peak,  $R_L = 8 \Omega$ ,  $PV_{DD} = 16 V$

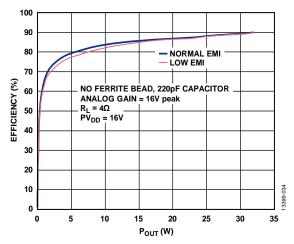

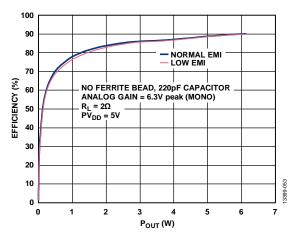

Figure 55. Efficiency vs.  $P_{OUT}$ , No Ferrite Bead, Analog Gain = 6.3 V peak,  $R_L = 2 \Omega$ ,  $PV_{DD} = 5 V$

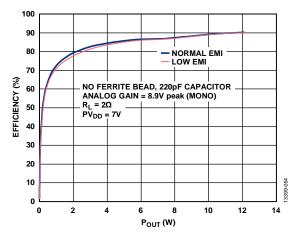

Figure 56. Efficiency vs.  $P_{OUT}$ , No Ferrite Bead, Analog Gain = 8.9 V peak,  $R_L = 2 \Omega$ ,  $PV_{DD} = 7 V$

Figure 57. Efficiency vs.  $P_{OUT}$ , No Ferrite Bead, Analog Gain = 12.6 V peak,  $R_L = 2 \Omega$ ,  $PV_{DD} = 12.6 \text{ V}$

Figure 58. Efficiency vs.  $P_{OUT}$ , No Ferrite Bead, Analog Gain = 16 V peak,  $R_L = 2 \Omega$ ,  $PV_{DD} = 16 V$

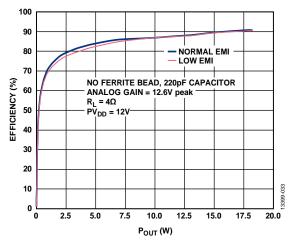

Figure 59. Efficiency vs.  $P_{OUT}$ , No Ferrite Bead, Analog Gain = 6.3 V peak,  $R_L = 3~\Omega$ ,  $PV_{DD} = 5~V$

Figure 60. Efficiency vs.  $P_{OUT}$ , No Ferrite Bead, Analog Gain = 8.9 V peak,  $R_L = 3~\Omega$ ,  $PV_{DD} = 7~V$

Figure 61. Efficiency vs.  $P_{OUT}$ , No Ferrite Bead, Analog Gain = 12.6 V peak,  $R_L = 3 \Omega$ ,  $PV_{DD} = 12 \text{ V}$

Figure 62. Efficiency vs.  $P_{OUT}$ , No Ferrite Bead, Analog Gain = 16 V peak,  $R_L = 3~\Omega$ ,  $PV_{DD} = 16~V$

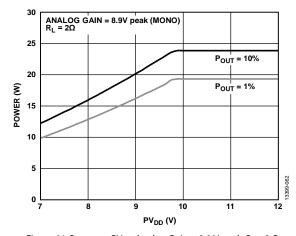

Figure 63. Power vs.  $PV_{DD}$ , Analog Gain = 8.9 V p-p,  $R_L$  = 4  $\Omega$

Figure 64. Power vs. PV<sub>DD</sub>, Analog Gain = 8.9 V peak,  $R_L$  = 2  $\Omega$

Figure 65. Power vs. PV<sub>DD</sub>, Analog Gain = 12.6 V peak,  $R_L$  = 2  $\Omega$

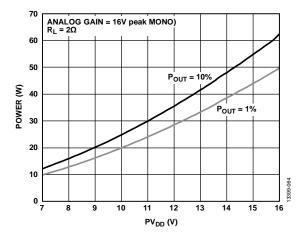

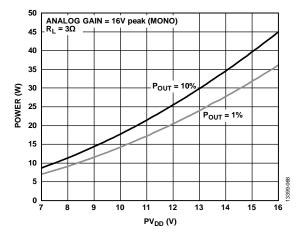

Figure 66. Power vs. PV<sub>DD</sub>, Analog Gain = 16 V peak,  $R_L = 2 \Omega$

Figure 67. Power vs. PV<sub>DD</sub>, Analog Gain = 6.3 V peak,  $R_L$  = 4  $\Omega$

Figure 68. Power vs. PV<sub>DD</sub>, Analog Gain = 8.9 V peak  $R_L$  = 3  $\Omega$

Figure 69. Power vs. PV<sub>DD</sub>, Analog Gain = 12.6 V peak,  $R_L = 3 \Omega$

Figure 70. Power vs. PV<sub>DD</sub>, Analog Gain = 16 V peak,  $R_L = 3 \Omega$

# THEORY OF OPERATION OVERVIEW

The SSM3582 is a stereo, Class-D audio amplifier with a filterless modulation scheme that greatly reduces external component count, conserving board space and reducing system cost. The SSM3582 does not require an output filter; it relies on the inherent inductance of the speaker coil and the natural filtering of the speaker and human ear to recover the audio component of the square wave output. Most Class-D amplifiers use some variation of pulsewidth modulation (PWM) to generate the output switching pattern, whereas the SSM3582 uses  $\Sigma$ - $\Delta$  modulation, resulting in important benefits.  $\Sigma$ - $\Delta$  modulators do not produce a sharp peak with many harmonics in the AM broadcast band, as pulsewidth modulators often do.  $\Sigma$ - $\Delta$  modulation reduces the amplitude of spectral components at high frequencies, reducing EMI emission that may otherwise radiate from speakers and long cable traces. Due to the inherent spread spectrum nature of  $\Sigma$ - $\Delta$  modulation, the need for oscillator synchronization is eliminated for designs incorporating multiple SSM3582 amplifiers. The SSM3582 uses less power in quiescent conditions, which helps conserve the power drawn from the battery or power supply.

The SSM3582 integrates overcurrent and temperature protection and a thermal warning with optional programmable automatic gain reduction.

#### **POWER SUPPLIES**

#### **PVDD**

PVDD supplies the output power stages, as well as the low dropout (LDO) regulator for AVDD and DVDD.

#### AVDD

AVDD is the analog supply used for the modulator, power stage driver, and other analog blocks.

When the AVDD\_EN pin = PVDD, the internal regulator generates 5 V and the AVDD pin is used for decoupling only.

When the AVDD\_EN pin = AGND, 5 V must be provided to the AVDD pin from an external system source, minimizing power losses.

#### **DVDD**

DVDD supplies the digital circuitry. The current in this node is very low, below 1 mA.

When the DVDD\_EN pin = AVDD, the internal regulator generates 1.8 V and the DVDD pin is used for decoupling only.

When the DVDD\_EN pin = AGND, 1.8 V must be provided to the DVDD pin from an external system source, minimizing power losses.

Table 12 summarizes the power dissipation in various supply configurations, operating modes, and load characteristics.

Table 12. Typical Power Supply Current Consumption for  $f_S = 48 \text{ kHz}^1$

|                 |          |                      |             |                           |                           | PVDD (V)               |                     |                        |                        |                        |                        |

|-----------------|----------|----------------------|-------------|---------------------------|---------------------------|------------------------|---------------------|------------------------|------------------------|------------------------|------------------------|

|                 |          |                      |             |                           |                           |                        | 5                   | 1                      | 2                      | 10                     | 6                      |

| AVDD_<br>EN Pin | Load     | Test<br>Conditions   | AVDD<br>Pin | I <sub>AVDD</sub><br>(mA) | I <sub>DVDD</sub><br>(mA) | I <sub>PVDD</sub> (mA) | Total Power<br>(mW) | I <sub>PVDD</sub> (mA) | Total<br>Power<br>(mW) | I <sub>PVDD</sub> (mA) | Total<br>Power<br>(mW) |

| Low             | No load  | SPWDN = 1            | External    | 0.007542                  | 0.00268                   | 0.000065               | 0.042859            | 0.000065               | 0.043314               | 0.000065               | 0.043574               |

|                 |          | Automatic power-down | External    | 0.007542                  | 0.04372                   | 0.000065               | 0.116731            | 0.000065               | 0.117186               | 0.000065               | 0.117446               |

|                 |          | Dither input         | External    | 6.335                     | 0.945                     | 2.54                   | 46.076              | 4.94                   | 92.656                 | 6.25                   | 133.376                |

| PVDD            | No load  | SPWDN = 1            | Internal    | N/A                       | N/A                       | 0.000065               | 0.000325            | 0.000065               | 0.00078                | 0.000065               | 0.00104                |

|                 |          | Automatic power-down | Internal    | N/A                       | N/A                       | 0.209                  | 1.045               | 0.286                  | 3.432                  | 0.329                  | 5.264                  |

|                 |          | Dither input         | Internal    | N/A                       | N/A                       | 9.78                   | 48.9                | 12.38                  | 148.56                 | 14.05                  | 224.8                  |

| Low             | 8Ω+33 μH | SPWDN = 1            | External    | 0.007542                  | 0.00268                   | 0.000065               | 0.042859            | 0.000065               | 0.043314               | 0.000065               | 0.043574               |

|                 |          | Automatic power-down | External    | 0.007542                  | 0.04372                   | 0.000065               | 0.116731            | 0.000065               | 0.117186               | 0.000065               | 0.117446               |

|                 |          | Dither input         | External    | 6.432                     | 0.942                     | 2.59                   | 46.8056             | 5.02                   | 94.0956                | 6.31                   | 134.8156               |

| PVDD            | 8Ω+33 μH | SPWDN = 1            | Internal    | N/A                       | N/A                       | 0.000065               | 0.000325            | 0.000065               | 0.00078                | 0.000065               | 0.00104                |

|                 |          | Automatic power-down | Internal    | N/A                       | N/A                       | 0.209                  | 1.045               | 0.286                  | 3.432                  | 0.329                  | 5.264                  |

|                 |          | Dither input         | Internal    | N/A                       | N/A                       | 9.82                   | 49.1                | 12.39                  | 148.68                 | 13.73                  | 219.68                 |

<sup>&</sup>lt;sup>1</sup> N/A means not applicable.

#### **POWER-UP SEQUENCE**

#### Using Only PVDD as a Source

When SSM3582 is used in single-supply mode, all internal rails are generated from PVDD. The internal AVDD (5 V) and DVDD (1.8 V) regulators can be enabled by pulling the AVDD\_EN and DVDD\_EN pins high. AVDD\_EN is pulled to PVDD, and DVDD\_EN is pulled to AVDD. The amplifier is operational and responds to  $\rm I^2C$  writes 10 ms after applying PVDD  $\geq$  5 V.

#### **Using PVDD and External AVDD**

Take care when an external 5 V is supplied to AVDD. The internal 5 V LDO must be disabled by pulling the AVDD\_EN pin low. In this case, DVDD (1.8 V) is generated from PVDD. It is important to maintain PVDD > AVDD to prevent the back powering of PVDD.

#### Using PVDD and External AVDD and DVDD

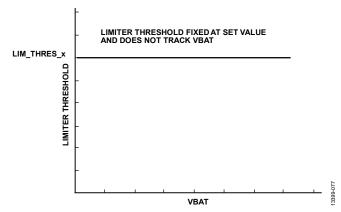

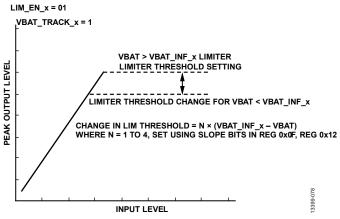

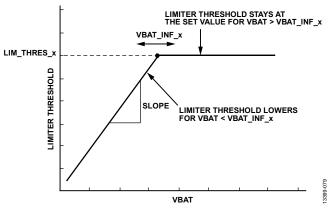

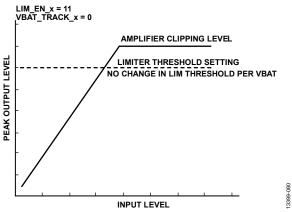

If using an external AVDD and DVDD source, both the AVDD\_EN and DVDD\_EN pins must be pulled low. It is important to maintain PVDD > AVDD/DVDD to prevent back powering PVDD.