# TMC4671 Datasheet

IC Version V1.3 | Document Revision V2.00 • 2020-Apr-17

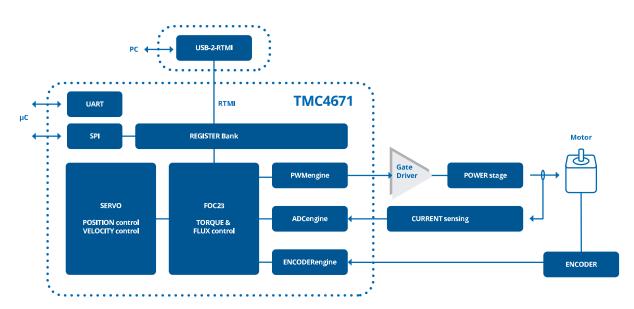

The TMC4671 is a fully integrated servo controller, providing Field Oriented Control for BLDC/PMSM and 2-phase Stepper Motors as well as DC motors and voice coils. All control functions are implemented in hardware. Integrated ADCs, position sensor interfaces, position interpolators, enable a fully functional servo controller for a wide range of servo applications.

#### **Features**

- Servo Controller w/ Field Oriented Control (FOC)

- Torque Control (FOC), Velocity Control, Position Control

- Integrated ADCs,  $\Delta\Sigma$ -ADC Frontend

- Encoder Engine: Hall analog/digital, Encoder analog/digital

- Supports 3-Phase PMSM/BLDC, 2-Phase Stepper Motors, and 1-Phase DC Motors

- Fast PWM Engine (25kHz...100kHz)

- Application SPI + Debug (UART, SPI)

- Step-Direction Interface (S/D)

- Applications

- Robotics

- Pick and Place Machines

- Factory Automation

- E-Mobility

- · Laboratory Automation

- Blowers

Pumps

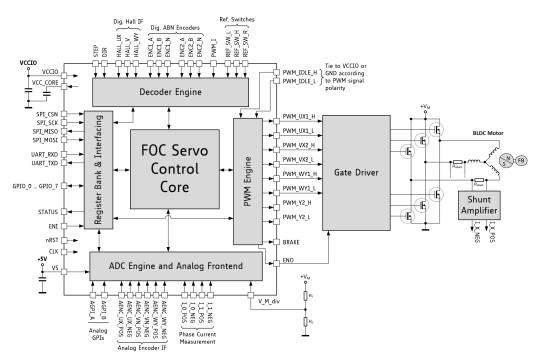

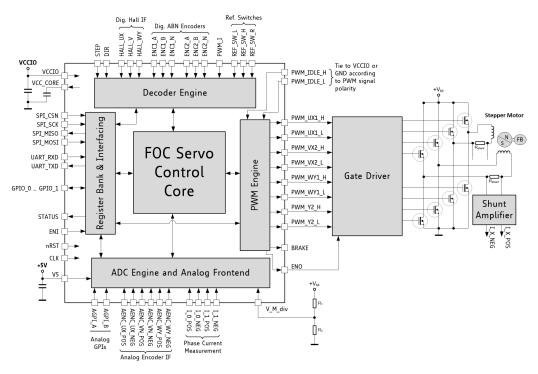

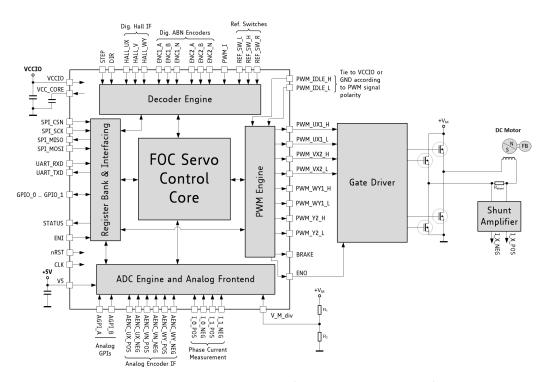

# Simplified Block Diagram

©2020 TRINAMIC Motion Control GmbH & Co. KG, Hamburg, Germany Terms of delivery and rights to technical change reserved. Download newest version at: www.trinamic.com

# **Contents**

| 1 | Order Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5                                                                                       |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 2 | Functional Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6                                                                                       |

| 3 | <ul> <li>FOC Basics</li> <li>3.1 Why FOC?</li> <li>3.2 What is FOC?</li> <li>3.3 Why FOC as pure Hardware Solution?</li> <li>3.4 How does FOC work?</li> <li>3.5 What is Required for FOC?</li> <li>3.5.1 Coordinate Transformations - Clarke, Park, iClarke, iPark</li> <li>3.5.2 Measurement of Stator Coil Currents</li> <li>3.5.3 Stator Coil Currents I_U, I_V, I_W and Association to Terminal Voltages U_U, U_V, U_W</li> <li>3.5.4 IgainADC[A/LSB] - ADC Integer Current Value to Real World Unit</li> <li>3.5.5 UgainADC[V/LSB] - ADC Integer Voltage Value to Real World Unit</li> <li>3.5.6 Measurement of Rotor Angle</li> <li>3.5.7 Measured Rotor Angle vs. Magnetic Axis of Rotor vs. Magnetic Axis of Stator</li> <li>3.5.8 Knowledge of Relevant Motor Parameters and Position Sensor (Encoder) Parameters</li> <li>3.5.9 Proportional Integral (PI) Controllers for Closed Loop Current Control</li> <li>3.5.10 Pulse Width Modulation (PWM) and Space Vector Pulse Width Modulation (SVPWM)</li> <li>3.5.11 Orientations, Models of Motors, and Coordinate Transformations</li> </ul> | 88<br>99<br>100<br>100<br>111<br>111<br>111<br>113<br>133                               |

| 4 | Functional Description 4.1 Functional Blocks 4.2 Communication Interfaces 4.2.1 SPI Slave User Interface 4.2.2 TRINAMIC Real-Time Monitoring Interface (SPI Master) 4.2.3 UART Interface 4.2.4 Step/Direction Interface 4.2.5 Single Pin Interface 4.3 Numerical Representation, Electrical Angle, Mechanical Angle, and Pole Pairs 4.3.1 Numerical Representation 4.3.2 N_POLE_PAIRS, PHI_E, PHI_M 4.3.3 Numerical Representation of Angles PHI 4.4 ADC Engine 4.4.1 ADC current sensing channels ADC_I1 and ADC_I0 4.4.2 ADC for analog Hall signals or analog sin-cos-encoders AENC_UX, AENC_VN, AENC_WY 4.4.3 ADC supply voltage measurement ADC_VM 4.4.4 ADC_VM for Brake Choppper 4.4.5 ADC EXT register option 4.4.6 ADC general purpose analog inputs AGPI_A and AGPI_B                                                                                                                                                                                                                                                                                                                          | 166<br>169<br>200<br>211<br>221<br>222<br>232<br>244<br>255<br>266<br>266<br>266<br>266 |

|   | 4.4.7 ADC RAW values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27<br>27<br>27<br>28<br>29<br>29<br>30<br>34                                            |

| 4.5 |         | g Signal Conditioning                                                           |    |

|-----|---------|---------------------------------------------------------------------------------|----|

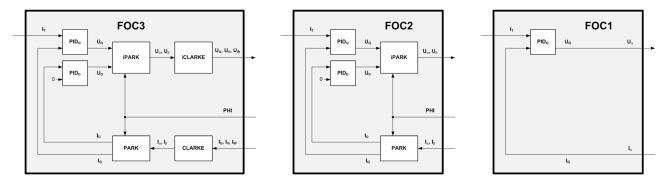

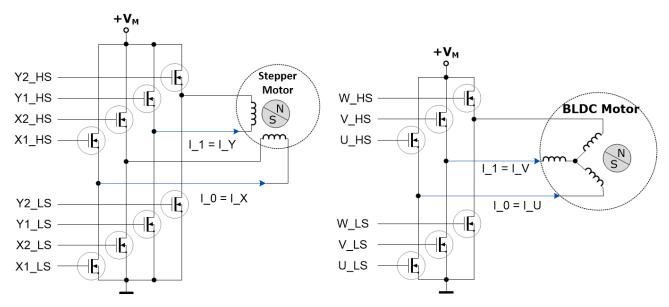

|     |         | FOC3 - Stator Coil Currents I_U, I_V, I_W and associated Voltages U_U, U_V, U_W |    |

|     |         | FOC2 - Stepper Coil Currents I_X, I_Y and associated Voltages U_X, U_Y          |    |

|     |         | FOC1 - DC Motor Coil Current I_X1, I_X2, and associated Voltage U_X1, U_X2      |    |

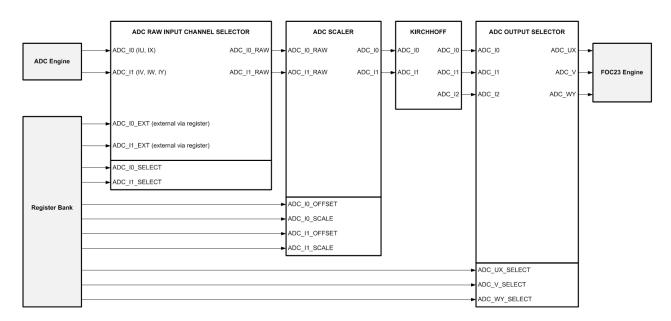

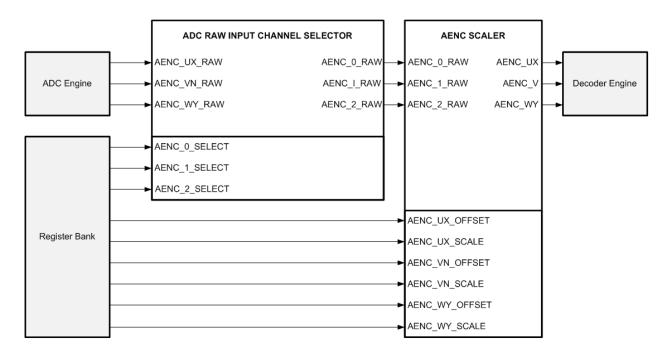

|     |         | ADC Selector & ADC Scaler w/ Offset Correction                                  |    |

| 4.6 |         | er Engine                                                                       |    |

|     |         | Open-Loop Encoder    .  .  .   .   .   .                                        |    |

|     |         | Incremental ABN Encoder                                                         |    |

|     |         | Secondary Incremental ABN Encoder                                               |    |

|     | 4.6.4   | Digital Hall Sensor Interface with optional Interim Position Interpolation      | 43 |

|     | 4.6.5   | Digital Hall Sensor - Interim Position Interpolation                            | 44 |

|     | 4.6.6   | Digital Hall Sensors - Masking, Filtering, and PWM center sampling              | 44 |

|     |         | Digital Hall Sensors together with Incremental Encoder                          |    |

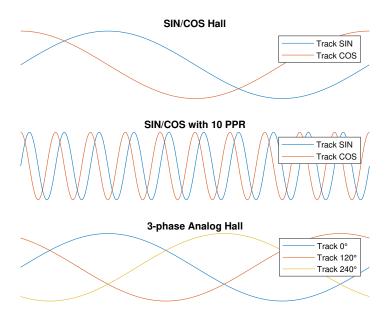

|     | 4.6.8   | Analog Hall and Analog Encoder Interface (SinCos of 0° 90° or 0° 120° 240°)     | 46 |

|     | 4.6.9   | Analog Position Decoder (SinCos of 0°90° or 0°120°240°)                         | 47 |

|     |         | Encoder Initialization Support                                                  |    |

|     |         | Velocity Measurement                                                            |    |

|     |         | Reference Switches                                                              |    |

| 4.7 |         | B Engine                                                                        |    |

|     |         | ENI and ENO pins                                                                |    |

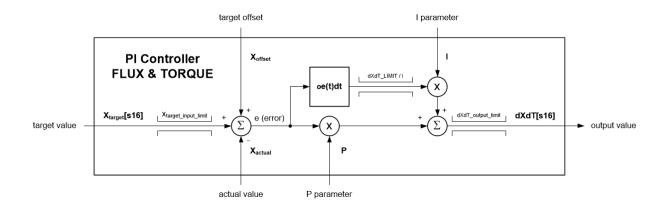

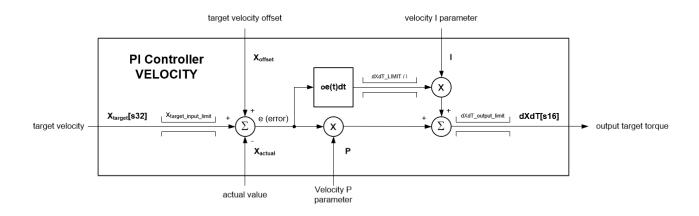

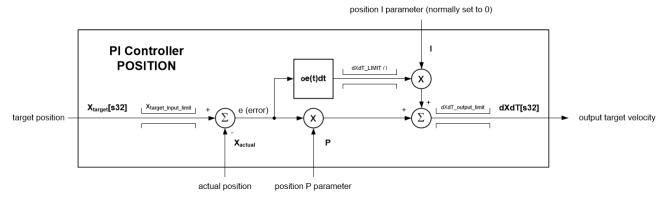

|     |         | PI Controllers                                                                  |    |

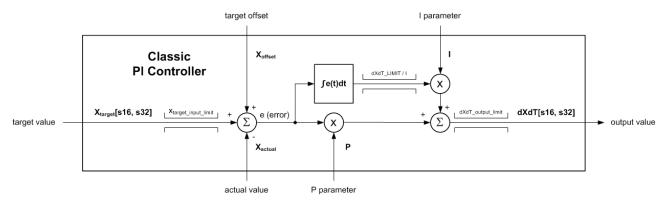

|     |         | PI Controller Calculations - Classic Structure                                  |    |

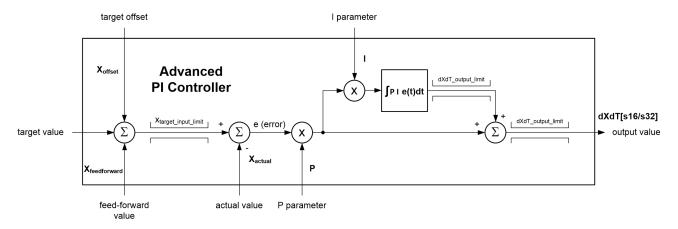

|     |         | PI Controller Calculations - Advanced Structure                                 |    |

|     |         | PI Controller - Clipping                                                        |    |

|     |         | PI Flux & PI Torque Controller                                                  |    |

|     |         | PI Velocity Controller                                                          |    |

|     |         | P Position Controller                                                           |    |

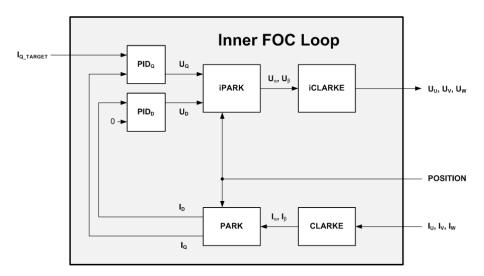

|     |         | Inner FOC Control Loop - Flux & Torque                                          |    |

|     |         | FOC Transformations and PI(D) for control of Flux & Torque                      |    |

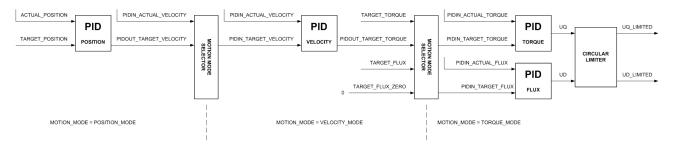

|     |         | Motion Modes                                                                    |    |

|     |         | Brake Chopper                                                                   |    |

| 4.8 |         |                                                                                 |    |

| 4.0 |         | ng and Feed-Forward Control                                                     |    |

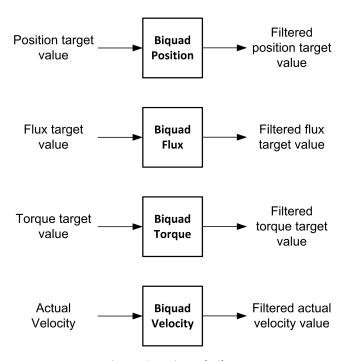

|     |         | Biquad Filters                                                                  |    |

|     |         | Standard Velocity Filter                                                        |    |

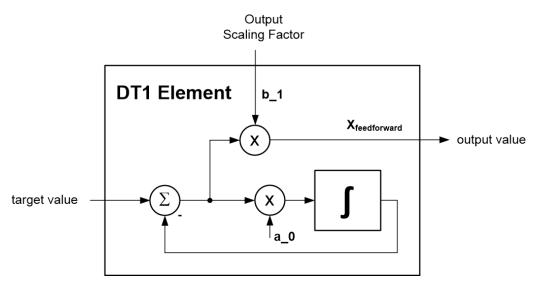

| 4.0 |         | Feed-Forward Control Structure                                                  |    |

| 4.9 |         | Engine                                                                          |    |

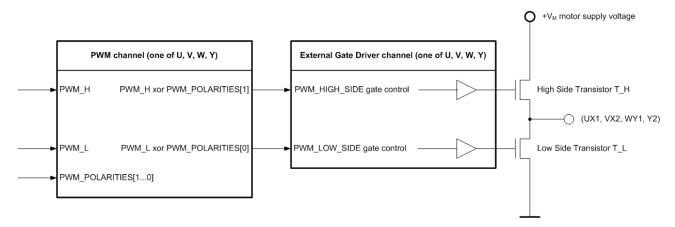

|     |         |                                                                                 |    |

|     |         | PWM Engine and associated Motor Connectors                                      |    |

|     |         | PWM Frequency                                                                   |    |

|     |         | PWM Resolution                                                                  |    |

|     |         | PWM Modes                                                                       |    |

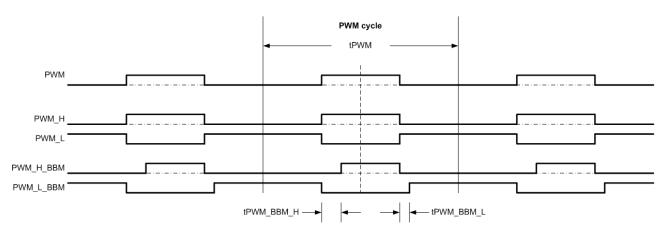

|     |         | Break-Before-Make (BBM)                                                         |    |

|     | 4.9.7   | Space Vector PWM (SVPWM)                                                        | 64 |

| Saf | ety Fun | ctions                                                                          | 64 |

| -   |         |                                                                                 | •  |

| FO  |         |                                                                                 | 66 |

| 6.1 |         | Motor Type                                                                      |    |

|     |         | FOC1 Setup - How to Turn a Single Phase DC Motor                                |    |

|     |         | FOC2 Setup - How to Turn a Two Phase Motor (Stepper)                            |    |

|     | 6.1.3   | FOC3 Setup - How to Turn a Three Phase Motor (PMSM or BLDC)                     | 66 |

| 6.2 | Set Nu  | ımber of Pole Pairs (NPP)                                                       | 66 |

| 6.3 |         | lotor Open Loop                                                                 |    |

|     | 6.3.1   | Determination of Association between Phase Voltage and Phase Currents           | 67 |

5

6

|    | 6.3.2 Determination of Direction of Rotation and Phase Shift of Angles  6.4 Selection of Position Sensors  6.4.1 Selection of FOC sensor for PHI_E  6.4.2 Selection of sensor for VELOCITY  6.4.3 Selection of sensor for POSITION  6.5 Modes of Operation - (Open Loop), Torque, Velocity, Positioning  6.6 Controller Tuning | . 67<br>. 67<br>. 67<br>. 67              |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 7  | Register Map7.1Register Map - Overview                                                                                                                                                                                                                                                                                         | . 73                                      |

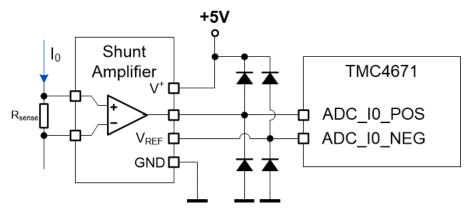

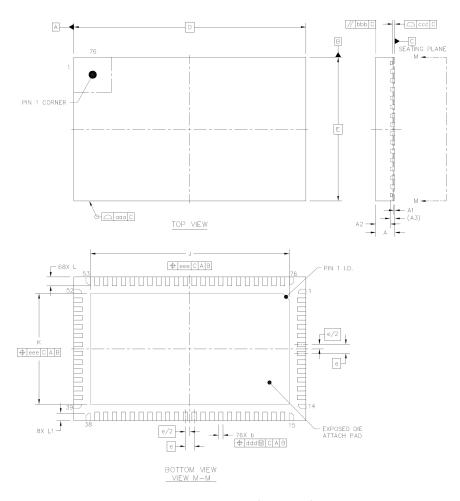

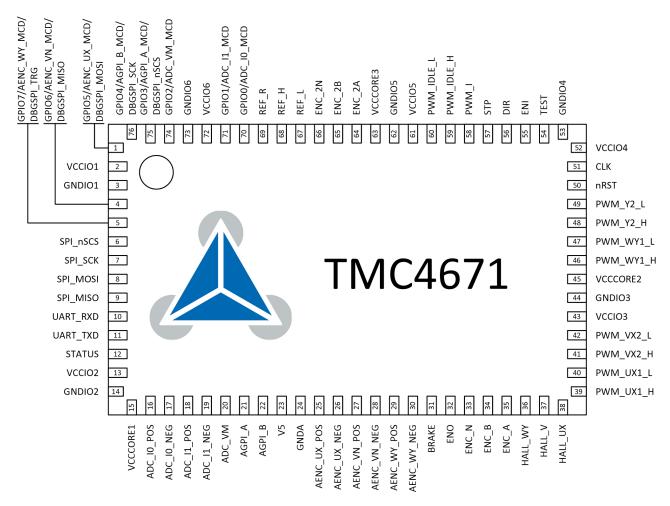

| 8  | Pinning                                                                                                                                                                                                                                                                                                                        | 120                                       |

| 9  | TMC4671 Pin Table                                                                                                                                                                                                                                                                                                              | 122                                       |

| 10 | Electrical Characteristics  10.1 Absolute Maximum Ratings  10.2 Electrical Characteristics  10.2.1 Operational Range  10.2.2 DC Characteristics                                                                                                                                                                                | . 126<br>. 126                            |

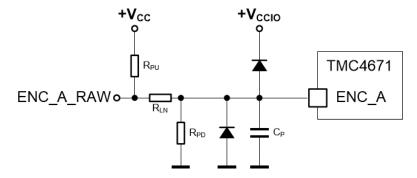

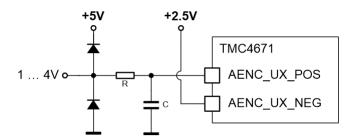

| 11 | Sample Circuits  11.1 Supply Pins  11.2 Clock and Reset Circuitry  11.3 Digital Encoder, Hall Sensor Interface and Reference Switches  11.4 Analog Frontend  11.5 Phase Current Measurement  11.6 Power Stage Interface                                                                                                        | . 128<br>. 128<br>. 129<br>. 129          |

| 12 | Setup Guidelines                                                                                                                                                                                                                                                                                                               | 132                                       |

| 13 | Package Dimensions                                                                                                                                                                                                                                                                                                             | 133                                       |

| 14 | Supplemental Directives  14.1 Producer Information  14.2 Copyright  14.3 Trademark Designations and Symbols  14.4 Target User  14.5 Disclaimer: Life Support Systems  14.6 Disclaimer: Intended Use  14.7 Collateral Documents & Tools                                                                                         | . 135<br>. 135<br>. 135<br>. 135<br>. 135 |

| 15 | Fixes of TMC4671-LA/-ES2 vs. Errata of TMC4671-ES  15.1 Errata of TMC4671-ES Engineering Samples as Reference                                                                                                                                                                                                                  | . 138                                     |

| 16 | Figures Index                                                                                                                                                                                                                                                                                                                  | 139                                       |

| 17 | Tables Index                                                                                                                                                                                                                                                                                                                   | 140                                       |

| 18 | Revision History  18.1 IC Revision                                                                                                                                                                                                                                                                                             | <b>141</b><br>. 141                       |

# 1 Order Codes

| Order Code                      | Description                     | Size           |  |

|---------------------------------|---------------------------------|----------------|--|

| TMC4671-LA                      | TMC4671 FOC Servo Controller IC | 10.5mm x 6.5mm |  |

| TMC4671-ES2                     | TMC4671-LA 1936 35735           | 10.5mm x 6.5mm |  |

|                                 | (Engineering Sample)            |                |  |

| TMC4671-EVAL                    | TMC4671 Evaluation Board        | 55mm x 85mm    |  |

| TMC4671-BOB                     | TMC4671 Breakout Board          | 38mm x 40mm    |  |

| Landungsbruecke                 | MCU Board                       | 85mm x 55mm    |  |

| TMC-UPS-2A24V-A-EVAL            | Power Stage Board               | 85mm x 55mm    |  |

| TMC-UPS-10A70V-A-EVAL           | Power Stage Board               | 85mm x 55mm    |  |

| TMC4671+TMC-UPS-2A24V-EVAL-KIT  | Evaluation Kit                  | _              |  |

| TMC4671+TMC-UPS-10A70V-EVAL-KIT | Evaluation Kit                  | _              |  |

| USB-2-RTMI                      | Interface Adapter to use RTMI   | 40mm x 20mm    |  |

Table 1: Order codes

| A  |   | ٠ | - |

|----|---|---|---|

| IV | U | L | Ľ |

TMC4671-ES2 labeled TMC4671-LA 1936 35735 are pre-series production engineering samples for evaluation of final silicone functionality of the TMC4671-LA.

# **2 Functional Summary**

# Servo Controller with Field Oriented Control (FOC)

- Torque (and flux) control mode

- Velocity control mode

- Position control mode

#### Control Functions/PI Controllers

- Programmable clipping of inputs and outputs of interim results

- Integrator windup protection for all controllers

- Status output with programmable mask for internal status signal selection

#### Supported Motor Types

- FOC3: 3-phase permanent magnet synchronous motors (PMSM) / brushless DC motor (BLDC)

- FOC2: 2-phase stepper motors

- FOC1: 1-phase brushed DC motors, or linear voice coil motors

#### ADC Engine with Offset Correction and Scaling

- Integrated Delta Sigma ADCs for current sense voltage, supply voltage, analog encoder, AGPIs

- Interface for isolated external current sensing Delta Sigma modulators

#### · Position Feedback

- Open loop position generator (programmable [rpm], [rpm/s]) for initial setup

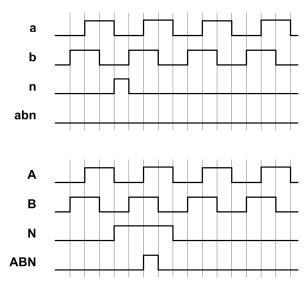

- Digital incremental encoder (ABN resp. ABZ, up to 2 MHz)

- Secondary digital incremental encoder

- Digital Hall sensor interface (H1, H2, H3 resp. H\_U, H\_V, H\_W) with interim position interpolation

- Analog encoder/analog Hall sensor interface (SinCos (0°, 90°) or 0°, 120°, 240°)

- Position target, velocity and target torque filters (Biquad)

- multi-turn position counter (32-bit)

### PWM Engine Including SVPWM

- Programmable PWM frequency within the range of 25 kHz ... 100 kHz

- PWM auto scaling for transparent change of PWM frequency during motion

- Programmable Brake-Before-Make (BBM) times (0 ns  $\dots$  2.5  $\mu$ s) for digital gate control signals

- Single bit SVPWM control (on/off) for Space Vector Modulation (switchable during operation)

#### SPI Application Communication Interface

- 40 bit datagram length (1 ReadWrite bit + 7 address bits + 32 data bits)

- Immediate SPI read response (register read access by single datagram)

- SPI clock frequency fSCK up to 2 MHz (8 MHz write, 8 MHz read w/ 500 ns pause after address)

## • TRINAMIC Real Time Monitoring Interface

- High frequency sampling of real-time data via TRINAMIC's real-time monitoring system

- Only single 10 pin high density connector on PCB needed

- Enables frequency response identification and auto tuning options with TRINAMIC's IDE

#### UART Debug Interface

- Three pin (GND, RxD, TxD) 3.3 V UART interface (1N8; 9600 (default), 115200, 921600, 3M bps)

- Available as port for external position sensors (e.g. absolute encoder together with processor)

- Transparent register access parallel to embedded user application interface (SPI)

## Supply Voltages

- 5V and 3.3V; VCC\_CORE is internally generated

### · IO Voltage

- 3.3V for all digital IOs (choosable by VCCIO Supply)

- 5V common mode analog input voltage range (1.25V ... 2.5V differential operating range)

## Clock Frequency

- 25 MHz (from external oscillator)

#### Packages

- QFN76

### 3 FOC Basics

This section gives a short introduction into some basics of Field Oriented Control (FOC) of electric motors.

# 3.1 Why FOC?

The Field Oriented Control (FOC), alternatively named Vector Control (VC), is a method for the most energy-efficient way of turning an electric motor.

#### 3.2 What is FOC?

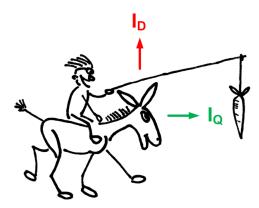

The Field Oriented Control was independently developed by K. Hasse, TU Darmstadt, 1968, and by Felix Blaschke, TU Braunschweig, 1973. The FOC is a current regulation scheme for electro motors that takes the orientation of the magnetic field and the position of the rotor of the motor into account, regulating the strength in such way that the motor gives that amount of torque that is requested as target torque. The FOC maximizes active power and minimizes idle power - that finally results in power dissipation - by intelligent closed-loop control illustrated by figure 1.

Figure 1: Illustration of the FOC basic principle by cartoon: Maximize active power and minimize idle power and power dissipation by intelligent closed-loop control.

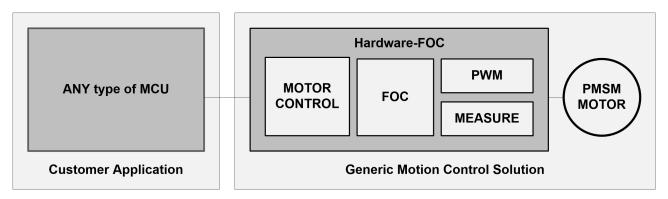

# 3.3 Why FOC as pure Hardware Solution?

The initial setup of the FOC is usually very time consuming and complex, although source code is freely available for various processors. This is because the FOC has many degrees of freedom that all need to fit together in a chain in order to work.

The hardware FOC as an existing standard building block drastically reduces the effort in system setup. With that off the shelf building block, the starting point of FOC is the setup of the parameters for the FOC. Setting up and implement the FOC itself and building and programming required interface blocks is no longer necessary. The real parallel processing of hardware blocks de-couples the higher lever application software from high speed real-time tasks and simplifies the development of application software. With the TMC4671, the user is free to use its qualified CPU together with its qualified tool chain, freeing the user from fighting with processer-specific challenges concerning interrupt handling and direct memory access. There is no need for a dedicated tool chain to access the TMC4671 registers and to operate it - just SPI (or UART) communication needs to be enabled for any given CPU.

The integration of the FOC as a SoC (System-on-Chip) drastically reduces the number of required components and reduces the required PCB space. This is in contrast to classical FOC servos formed by motor

block and separate controller box wired with motor cable and encoder cable. The high integration of FOC, together with velocity controller and position controller as a SoC, enables the FOC as a standard peripheral component that transforms digital information into physical motion. Compact size together with high performance and energy efficiency especially for battery powered mobile systems are enabling factors when embedded goes autonomous.

#### 3.4 How does FOC work?

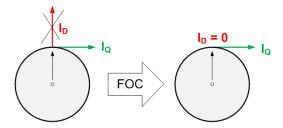

Two force components act on the rotor of an electric motor. One component is just pulling in radial direction (ID) where the other component is applying torque by pulling tangentially (IQ). The ideal FOC performs a closed loop current control that results in a pure torque generating current IQ – without direct current ID.

Figure 2: FOC optimizes torque by closed loop control while maximizing IQ and minimizing ID to 0

From top point of view, the FOC for 3-phase motors uses three phase currents of the stator interpreted as a current vector (lu; lv; lw) and calculates three voltages interpreted as a voltage vector (Uu; Uv; Uw) taking the orientation of the rotor into account in a way that only a torque generating current IQ results.

From top point of view, the FOC for 2-phase motors uses two phase currents of the stator interpreted as a current vector (Ix; Iy) and calculates two voltages interpreted as a voltage vector (Ux; Uy) taking the orientation of the rotor into account in a way that only a torque generating current IQ results.

To do so, the knowledge of some static parameters (number of pole pairs of the motor, number of pulses per revolution of an used encoder, orientation of encoder relative to magnetic axis of the rotor, count direction of the encoder) is required together with some dynamic parameters (phase currents, orientation of the rotor).

The adjustment of P parameter P and I parameters of two PI controllers for closed loop control of the phase currents depends on electrical parameters of the motor (resistance, inductance, back EMF constant of the motor that is also the torque constant of the motor, supply voltage).

# 3.5 What is Required for FOC?

The FOC needs to know the direction of the magnetic axis of the rotor of the motor in reference to the magnetic axis of the stator of the motor. The magnetic flux of the stator is calculated from the currents through the phases of the motor. The magnetic flux of the rotor is fixed to the rotor and thereby determined by an encoder device.

For the FOC, the user needs to measure the currents through the coils of the stator and the angle of the rotor. The measured angle of the rotor needs to be adjusted to the magnetic axes.

The challenge of the FOC is the high number of degrees of freedom in all parameters.

#### 3.5.1 Coordinate Transformations - Clarke, Park, iClarke, iPark

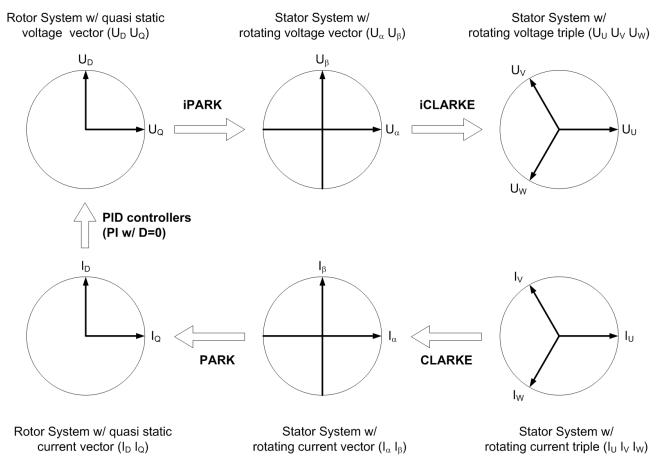

The FOC requires different coordinate transformations formulated as a set of matrix multiplications. These are the Clarke Transformation (Clarke), the Park Transformation (Park), the inverse Park Transformation (iPark) and the inverse Clarke Transformation (iClarke). Some put Park and Clarke together as DQ transformation and Park and Clarke as inverse DQ transformation.

The TMC4671 takes care of the required transformations so the user no longer has to fight with implementation details of these transformations.

### 3.5.2 Measurement of Stator Coil Currents

The measurement of the stator coil currents is required for the FOC to calculate a magnetic axis out of the stator field caused by the currents flowing through the stator coils.

Coil current stands for motor torque in context of FOC. This is because motor torque is proportional to motor current, defined by the torque constant of a motor. In addition, the torque depends on the orientation of the rotor of the motor relative to the magnetic field produced by the current through the coils of the stator of the motor.

#### 3.5.3 Stator Coil Currents I\_U, I\_V, I\_W and Association to Terminal Voltages U\_U, U\_V, U\_W

The correct association between stator terminal voltages U\_U, U\_V, U\_W and stator coil currents I\_U, I\_V, I\_W is essential for the FOC. In addition to the association, the signs of each current channel need to fit. Signs of the current can be adapted numerically by the ADC scaler. The mapping of ADC channels is programmable via configuration registers for the ADC selector. Initial setup is supported by the integrated open loop encoder block, that can support the user to turn a motor open loop.

#### 3.5.3.1 Chain of Gains for ADC Raw Values

An ADC raw value is a result of a chain of gains that determine it. A coil current I\_SENSE flowing through a sense resistor causes a voltage difference according to Ohm's law. The resulting ADC raw value is a result of the analog signal path according to

ADC

$$RAW = (I SENSE * ADC GAIN) + ADC OFFSET.$$

(1)

The ADC\_GAIN is a result of a chain of gains with individual signs. The sign of the ADC\_GAIN is positive or negative, depending on the association of connections between sense amplifier inputs and the sense resistor terminals. The ADC\_OFFSET is the result of electrical offsets of the phase current measurement signal path. For the TMC4671, the maximum ADC\_RAW value ADC\_RAW\_MAX =  $(2^{16}-1)$  and the minimum ADC raw value is ADC\_RAW\_MIN = 0.

For the FOC, the ADC\_RAW is scaled by the ADC scaler of the TMC4671 together with subtraction of offset to compensate it. Internally, the TMC4671 FOC engine calculates with s16 values. Thus, the ADC scaling needs to be chosen so that the measured currents fit into the s16 range. With the ADC scaler, the user can choose a scaling with physical units like [mA].

#### 3.5.4 IgainADC[A/LSB] - ADC Integer Current Value to Real World Unit

Together with ADC\_I0\_SCALE and ADC\_I0\_OFFSET and ADC\_I1\_SCALE and ADC\_I1\_OFFSET, measured ADC currents represented as 16 bit signed interger numbers (s16) represent real world currents. Multiplication of integer current value with gain scaling factor in unit Ampere per LSB (Low Significant Bit) gives the real world value of current in unit Ampere.

Different scalings between two associated current ADC channels can be trimmed by programing ADC\_I0\_SCALE and ADC\_I1\_SCALE. The IgainADC[A/LSB] needs to be determined from ADC gain factors, ADC reference voltage selection, and actual ADC scaling factor settings.

#### 3.5.5 UgainADC[V/LSB] - ADC Integer Voltage Value to Real World Unit

Measured ADC voltages represented as 16 bit signed interger numbers (s16) represent real world voltages. Multiplication of integer voltage value with gain scaling factor in unit Volt per LSB (Low Significant Bit) gives the real world value of voltage in unit Volt.

$$U[V] = \mathsf{UgainADC}[V/LSB] * \mathsf{ADC\_U}$$

(4)

The UgainADC[V/LSB] needs to be determined from ADC gain factors, actual ADC gains, and ADC reference voltage settings.

#### 3.5.6 Measurement of Rotor Angle

Determination of the rotor angle is either done by sensors (digital encoder, analog encoder, digital Hall sensors, analog Hall sensors) or sensorless by a reconstruction of the rotor angle. Currently, there are no sensorless methods available for FOC that work in a general purpose way as a sensor down to velocity zero.

The TMC4671 does not support sensorless FOC.

#### 3.5.7 Measured Rotor Angle vs. Magnetic Axis of Rotor vs. Magnetic Axis of Stator

The rotor angle, measured by an encoder, needs to be adjusted to the magnetic axis of the rotor. This is because an incremental encoder has an arbitrary orientation relative to the magnetic axis of the rotor, and the rotor has an arbitrary orientation to magnetic axis of the stator.

The direction of counting depends on the encoder, its mounting, and wiring and polarities of encoder signals and motor type. So, the direction of encoder counting is programmable for comfortable definition for a given combination of motor and encoder.

#### 3.5.7.1 Direction of Motion - Magnetic Field vs. Position Sensor

For FOC it is essential, that the direction of revolution of the magnetic field is compatible with the direction of motion of the rotor position reconstructed from encoder signals: For revolution of magnetic field with positive direction, the decoder position needs to turn into the same positive direction. For revolution of magnetic field with negative direction, the decoder position needs to turn into the same negative direction.

With an absolute encoder, once adjusted to the relative orientation of the rotor and to the relative orientation of the stator, one could start the FOC without initialization of the relative orientations.

#### 3.5.7.2 Bang-Bang Initialization of the Encoder

A Bang-Bang initialization is an initialization where the motor is forced with high current into a specific position. For Bang-Bang initialization, the user sets a current into direction D that is strong enough to move the rotor into the desired direction. Other initialization methods ramp up the current smoothly and adjust the current vector to rotor movement detected by the encoder.

#### 3.5.7.3 Encoder Initialization using Hall Sensors

The encoder can be initialized using digital Hall sensor signals. Digital Hall sensor signals give absolute positions within each electrical period with a resolution of sixty degrees. If the Hall sensor signals are used to initialize the encoder position on the first change of a Hall sensor signal, an absolute reference within the electrical period for commutation is given.

#### 3.5.7.4 Minimum Movement Initialization of the Encoder

For minimal movement initialization of the encoder, the user slowly increases a current into direction D and adjusts an offset of the measured angle in a way that the rotor of the motor does not move during initialization while the offset of the measured angle is determined.

# 3.5.8 Knowledge of Relevant Motor Parameters and Position Sensor (Encoder) Parameters

#### 3.5.8.1 Number of Pole Pairs of a Motor

The number of pole pairs is an essential motor parameter. It defines the ratio between electrical revolutions and mechanical revolutions. For a motor with one pole pair, one mechanical revolution is equivalent to one electrical revolution. For a motor with npp pole pairs, one mechanical revolution is equivalent to npp electrical revolutions, with  $n = 1, 2, 3, 4, \ldots$

Some define the number of poles NP instead of number of pole pairs NPP for a motor, which results in a factor of two that might cause confusion. For the TMC4671, we use NPP number of pole pairs.

### 3.5.8.2 Number of Encoder Positions per Revolution

For the encoder, the number of positions per revolution (PPR) is an essential parameter. The number of positions per revolution is essential for the FOC.

Some encoder vendors give the number of lines per revolution (LPR) or just named line count (LC) as encoder parameter. Line count and positions per revolution might differ by a factor of four. This is because of the quadrature encoding - A signal and B signal with phase shift - that give four positions per line,

enabling the determination of the direction of revolution. Some encoder vendors associate counts per revolution (CPR) or pulses per revolution associated to PPR acronym.

The TMC4671 uses Positions Per Revolution (PPR) as encoder parameter.

#### 3.5.9 Proportional Integral (PI) Controllers for Closed Loop Current Control

Last but not least, two PI controllers are required for the FOC. The TMC4671 is equipped with two PI controllers - one for control of torque generating current I\_Q and one to control current I\_D to zero.

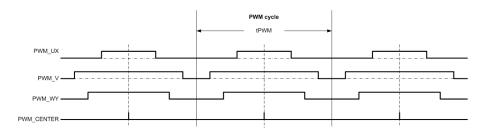

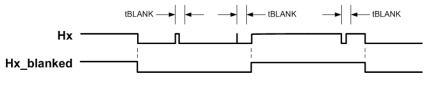

## 3.5.10 Pulse Width Modulation (PWM) and Space Vector Pulse Width Modulation (SVPWM)

The PWM power stage is a must-have for energy efficient motor control. The PWM engine of the TMC4671 just needs a couple of parameters to set PWM frequency fPWM and switching pauses for both high side switches tBBM\_H and low side switches tBBM\_L. Some control bits are for the programming of power switch polarities for maximum flexibility in the selection in gate drivers for the power MOS-FETs. An additional control bit selects SVPWM on or off. The TMC4671 allows for change of PWM frequency by a single parameter during operation.

With this, the TMC4671 is advanced compared to software solutions where PWM and SVPM configuration of CPU internal peripherals normally needs settings of many parameters.

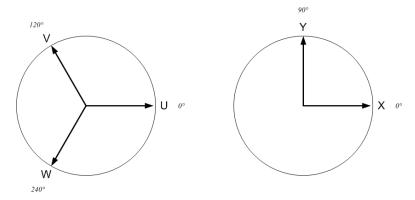

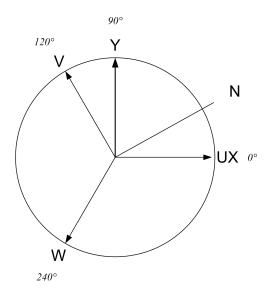

#### 3.5.11 Orientations, Models of Motors, and Coordinate Transformations

The orientation of magnetic axes (U, V, W for FOC3 resp. X, Y for FOC2) is essential for the FOC together with the relative orientation of the rotor. Here, the rotor is modeled by a bar magnet with one pole pair (n\_pole\_pairs = 1) with magnetic axis in north-south direction.

The actual magnetic axis of the stator - formed by the motor coils - is determined by measurement of the coil currents.

The actual magnetic axis of the rotor is determined by incremental encoder or by Hall sensors. Incremental encoders need an initialization of orientation, where Hall sensors give an absolute orientation, but with low resolution. A combination of Hall sensor and incremental encoder is useful for start-up initialization.

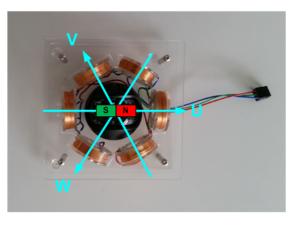

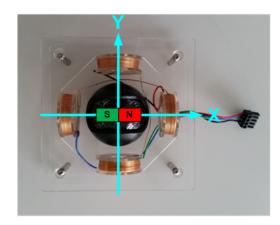

Figure 3: Orientations UVW (FOC3) and XY (FOC2)

Figure 4: Compass Motor Model w/ 3 Phases UVW (FOC3) and Compass Motor Model w/ 2 Phases (FOC2)

# 4 Functional Description

The TMC4671 is a fully integrated controller for field-oriented control (FOC) of either one 3-phase brushless motor (FOC3) or one 2-phase stepper motor (FOC2) or, as well as 1-phase DC motor or voice coil actuator (FOC1). Containing the complete control loop core architecture (position, velocity, torque), the TMC4671 also has the required peripheral interfaces for communication with an application controller, for feedback (digital encoder, analog interpolator encoder, digital Hall with interpolator, analog inputs for current and voltage measurement), and helpful additional IOs. The TMC4671 supports highest control loop speed and PWM frequencies.

The TMC4671 is the building block which takes care of all real-time critical tasks of field-oriented motor control. It decouples the real-time field-oriented motor control and its real-time sub-tasks such as current measurement, real-time sensor signal processing, and real-time PWM signal generation from the user application layer as outlined by figure 5.

Figure 5: Hardware FOC Application Diagram

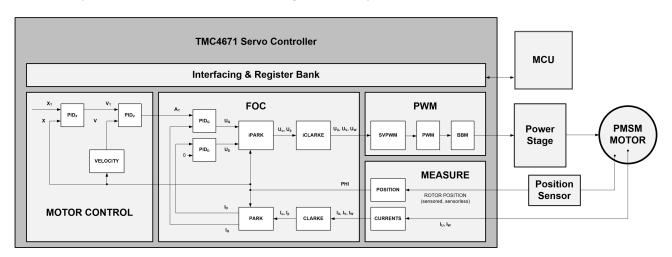

#### 4.1 Functional Blocks

The Application interface, register bank, ADC engine, encoder engine, FOC torque PI controller, velocity PI controller, position P controller, and PWM engine make up the TMC4671.

Figure 6: Hardware FOC Block Diagram

The ADC engine interfaces the integrated ADC channels and maps raw ADC values to signed 16 bit (s16) values for the inner FOC current control loop based on programmable offset and scaling factors. The FOC torque PI controller forms the inner base component including required transformations (Clark, Park, inverse Park, inverse Clark). All functional blocks are pure hardware.

### 4.2 Communication Interfaces

The TMC4671 is equipped with an SPI slave user interface for access to all registers of the TMC4671. The SPI slave user interface is the main application interface.

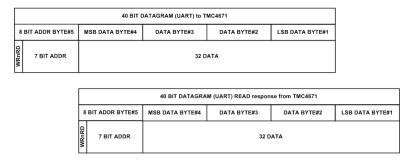

An additional UART interface is intended for system setup. With that interface, the user can access all registers of the TMC4671 in parallel to the application accessing them via the SPI communication interface - via the user's firmware or via evaluation boards and the TMCL-IDE. The data format of the UART interface is similar to the SPI communication interface - SPI 40 bit datagrams sent to the TMC4671 and SPI 40 bit datagrams received by the MCU vs. five bytes sent via UART and five bytes received via UART. Sending a burst of different real-time data for visualization and analysis via the TMCL-IDE can be triggered using special datagrams. With that, the user can set up an embedded application together with the TMCL-IDE, without having to write a complex set of visualization and analysis functions. The user can focus on its application.

The TMC4671 is also equipped with an additional SPI master interface (TRINAMIC Real-time Monitoring Interface, DBGSPI) for high-speed visualization of real-time data together with the TMCL-IDE.

#### 4.2.1 SPI Slave User Interface

The SPI of the TMC4671 for the user application has an easy command and control structure. The TMC4671 user SPI acts as a slave. The SPI datagram length is 40 bit with a clock rate up to 1 MHz (8 MHz in future chip version).

- The MSB (bit#39) is sent first. The LSB (bit#0) is sent last.

- The MSB (bit#39) is the WRITE\_notREAD (WRnRD) bit.

- The bits (bit#39 to bit#32) are the address bits (ADDR).

- Bits (bit#31) to (bit#0) are 32 data bits.

The SPI of the TMC4671 immediately responses within the actual SPI datagram on read and write for ease-of-use communication and uses SPI mode 3 with CPOL = 1 and CPHA = 1.

|       | 40 BIT DATAGRAM |         |  |  |  |  |

|-------|-----------------|---------|--|--|--|--|

|       | 8 BIT ADDR      | 32 DATA |  |  |  |  |

| WRnRD | 7 BIT ADDR      | 32 DATA |  |  |  |  |

Figure 7: SPI Datagram Structure

#### A simple SPI datagram example:

```

0x8100000000 // 1st write 0x00000000 into address 0x01 (CHIPINFO_ADDR)

0x0000000000 // 2nd read register 0x00 (CHIPINFO_DATA), returns 0x34363731 <=> ACSII "4671"

```

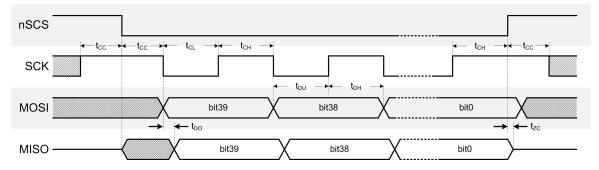

Figure 8: SPI Timing

| SPI Interface Timing Characteristics             |                  |      |     | = 25MH | lz   |

|--------------------------------------------------|------------------|------|-----|--------|------|

| Parameter                                        | Symbol           | Min  | Тур | Max    | Unit |

| SCK valid before or after change of nSCS         | $t_{CC}$         | 62.5 |     |        | ns   |

| nSCS high time                                   | $t_{CSH}$        | 62.5 |     |        | ns   |

| nSCS low time                                    | $t_{CSL}$        | 62.5 |     |        | ns   |

| SCK high time                                    | $t_{CH}$         | 62.5 |     |        | ns   |

| SCK low time                                     | $t_{CL}$         | 62.5 |     |        | ns   |

| SCK low time                                     | $t_{CL}$         | 62.5 |     |        | ns   |

| tSCKpause time after read address byte           | $t_{SCKpause}$   | 500  |     |        | ns   |

| SCK frequency with tSCKpause after write address | $f_{SCKpauseWR}$ |      |     | 8      | MHz  |

| SCK frequency for write access without pause     | $f_{SCKwr}$      |      |     | 8      | MHz  |

| SCK frequency with tSCKpause after read address  | $f_{SCKpauseRD}$ |      |     | 8      | MHz  |

| SCK frequency for read access without tSCKpause  | $f_{SCKrd}$      |      |     | 2      | MHz  |

| MOSI setup time before rising edge of SCK        | $t_{DU}$         | 62.5 |     |        | ns   |

| MOSI hold time after falling edge of SCK         | $t_{DH}$         | 62.5 |     |        | ns   |

| MISO data valid time after falling edge of SCK   | $t_{DO}$         |      |     | 10     | ns   |

Table 2: SPI Timing Parameter

1 Info

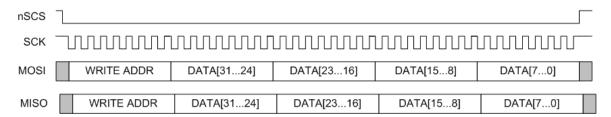

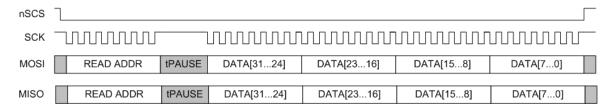

SPI write access can be performed up to 8 MHz SPI clock frequency. SPI read access can be performed up to 8 MHz SPI clock frequency if a pause of at least 500 ns is inserted after transfer of the address byte of the SPI datagram. Without a pause of 500 ns after address byte, SPI read access can be performed up to 2 MHz SPI clock frequency.

Figure 9: SPI Timing of Write Access without pause with fSCK up to 8MHz

Figure 10: SPI Timing of Read Access with pause (tPAUSE) of 500 ns with fSCK up to 8MHz.

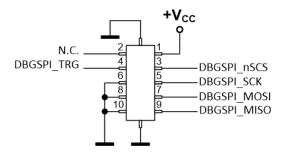

### 4.2.2 TRINAMIC Real-Time Monitoring Interface (SPI Master)

The TRINAMIC Real-Time Monitoring Interface (RTMI, SPI Master) is an additional fast interface enabling real-time identification of motor and system parameters. The user can check configuration and access registers in the TMC4671 via the TMCL-IDE with its build-in configuration wizards for FOC setup in parallel to the user firmware. TRINAMIC provides a Monitoring Adapter to access the interface, which connects easily to a single 10 pin high density connector (Type: Hirose DF20F-10DP-1V) on the user's PCB or on the evaluation board. If the interface is not needed, pins can be left open or can be used as GPIOs according to the specification. The connector needs to be placed near the TMC4671. Its assignment is pictured in figure 11.

Figure 11: Connector for Real-Time Monitoring Interface (Connector Type: Hirose DF20F-10DP-1V)

#### 4.2.3 UART Interface

The UART interface is a simple three pin (GND, RxD, TxD) 3.3V UART interface with up to 3 Mbit/s transfer speed with one start bit, eight data bits, one stop bit, and no parity bits (1N8). The default speed is 9600 bps. Other supported speeds are 115200 bps, 921600 bps, and 3000000 bps.

With an 3.3V-UART-to-USB adapter cable (e.g. FTDI TTL-232R-RPi), the user can use the full maximum data rate. The UART port enables In-System-Setup-Support by multiple-ported register access.

An UART datagram consists of five bytes - similar to the datagrams of the SPI. In contrast to SPI, the UART interface has a time out feature. So, the five bytes of a UART datagram need to be send within one second. A pause of sending more than one second causes a time out and sets the UART protocol handler back into IDLE state. In other words, waiting for more than one second in sending via UART ensures that the UART protocol handler is in IDLE state.

A simple UART example (similar to the simple SPI example):

```

0x81 0x00 0x00 0x00 0x00 // 1st write 0x00000000 into address 0x01 (CHIPINFO_ADDR) 0x00 0x00 0x00 0x00 0x00 // 2nd read register 0x00 (CHIPINFO_DATA), returns 0x34363731

```

Why UART Interface? It might become necessary during the system setup phase to simply access some internal registers without disturbing the application, without changing the actual user application software, and without adding additional debugging code that might disturb the application software itself. The UART enables this supporting function. In addition, it also enables easy access for monitoring purposes with its very simple and direct five byte protocol. The UART interface is available to write periodically positions into the TMC4671 via an external CPU used as a protocol translator to enable absolute encoders for the TMC4671.

Figure 12: UART Read Datagram (TMC4671 register read via UART)

| 40 BIT DATAGRAM (UART) to TMC4671 |  |                                   |  |             |                 |

|-----------------------------------|--|-----------------------------------|--|-------------|-----------------|

| 8 BIT ADDR BYTE#5                 |  | 8 BIT ADDR BYTE#5 MSB DATA BYTE#4 |  | DATA BYTE#2 | LSB DATA BYTE#1 |

| 7 BIT ADDR 32 DATA                |  |                                   |  | ATA         |                 |

| 40 BIT DATAGRAM (UART) WRITE response from TMC4671 |                   |                                             |      |                 |  |  |

|----------------------------------------------------|-------------------|---------------------------------------------|------|-----------------|--|--|

| -                                                  | B BIT ADDR BYTE#5 | E#5 MSB DATA BYTE#4 DATA BYTE#3 DATA BYTE#2 |      | LSB DATA BYTE#1 |  |  |

| WRnRD                                              | 7 BIT ADDR        |                                             | 32 D | ATA             |  |  |

Figure 13: UART Write Datagram (TMC4671 register write via UART)

### 4.2.4 Step/Direction Interface

The user can manipulate the target position via the step direction interface. It can be enabled by setting the STEP\_WIDTH (s32) register to a proper step width. The power-on default value of STEP\_WIDTH is 0 that causes position target update with 0 step width that is no stepping. With STEP\_WIDTH  $\neq$  0 each step pule on STEP input causes incrementing or decrementing of target position depending on polarity of DIR input. For positive STEP\_WIDTH, DIR = 0 causes incrementing and the DIR = 1 causes decrementing of the target position. For negative STEP\_WIDTH, DIR = 0 causes decrementing and DIR = 1 causes incrementing of the target position. This is because the STEP\_WIDTH is represented as a signed number.

## 4.2.5 Single Pin Interface

The TMC4671 can be operated in Motion Modes in which the main target value is calculated from either a PWM input signal on PIN PWM\_I or by analog input to AGPI\_A.

| Number               | Motion Mode          | Using PWM_I or AGPI_A |

|----------------------|----------------------|-----------------------|

| 0                    | Stopped Mode         | no                    |

| 1                    | Torque Mode          | no                    |

| 2                    | Velocity Mode        | no                    |

| 3                    | Position Mode        | no                    |

| 4                    | PRBS Flux Mode       | no                    |

| 5                    | PRBS Torque Mode     | no                    |

| 6 PRBS Velocity Mode |                      | no                    |

| 7 PRBS Position Mode |                      | no                    |

| 8 UQ UD Ext Mode     |                      | no                    |

| 9                    | (reserved)           | no                    |

| 10                   | AGPI_A Torque Mode   | AGPI_A                |

| 11                   | AGPI_A Velocity Mode | AGPI_A                |

| 12                   | AGPI_A Position Mode | AGPI_A                |

| 13 PWM_I Torque Mode |                      | PWM_I                 |

| 14                   | PWM_I Velocity Mode  | PWM_I                 |

| 15                   | PWM_I Position Mode  | PWM_I                 |

Table 3: Single Pin Interface Motion Modes

Registers SINGLE\_PIN\_IF\_OFFSET and SINGLE\_PIN\_IF\_SCALE can be used to scale the value to desired range. In case of the PWM input, a permanent low input signal or permanent high signal is treated as input error and chosen target value is set to zero.

Register SINGLE\_PIN\_IF\_CFG configures the length of a digital filter for the PWM\_I signal. Spikes on the signal can be thereby suppressed. Bit 0 in register SINGLE\_PIN\_IF\_STATUS is set high when PWM\_I is constant low, Bit 1 is set high when the PWM\_I is constant high. Writing to this register resets these flags. Maximum PWM period of the PWM signal must be 65536 x 40 ns. The calculation of the normalized duty cycle is started on the rising edge of PWM\_I. The PWM frequency needs to be constant as big variations (tolerance of 4 us in PWM period) in the PWM frequency are treated as error.

A duty cycle of 50% equals an input value of 32768. With the offset and scaling factors it can be mapped to desired range.

# 4.3 Numerical Representation, Electrical Angle, Mechanical Angle, and Pole Pairs

The TMC4671 uses different numerical representations for different parameters, measured values, and interim results. The terms electrical angle PHI\_E, mechanical angle PHI\_M, and number of pole pairs (N\_POLE\_PAIRS) of the motor are important for setup of FOC. This section describes the different numerical representations of parameters and terms.

# 4.3.1 Numerical Representation

The TMC4671 uses signed and unsigned values of different lengths and fixed point representations for parameters that require a non-integer granularity.

| Symbol                                                                        | Description                                                               | Min         | Max                              |

|-------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------|----------------------------------|

| u16                                                                           | unsigned 16 bit value                                                     | 0           | 65535                            |

| s16                                                                           | signed 16 bit values, 2'th complement                                     | -32767      | 32767                            |

| u32 unsigned 32 bit value                                                     |                                                                           | 0           | 2 <sup>32</sup> = 4294967296     |

| s32                                                                           | s32 signed 32 bit values, 2'th complement                                 |             | 2 <sup>31</sup> - 1 = 2147483647 |

| q8.8 signed fix point value with 8 bit integer part and 8 bit fractional part |                                                                           | -32767/256  | 32767/256                        |

| q4.12                                                                         | signed fix point value with 4 bit integer part and 12 bit fractional part | -32767/4096 | 32767/4096                       |

Table 4: Numerical Representations

1 Info

Two's complement of n bit is  $-2^{(n-1)}\dots-2^{(n-1)}-1$ . To avoid unwanted overflow, the range is clipped to  $-2^{(n-1)}+1\dots-2^{(n-1)}-1$ .

Because the zero is interpreted as a positive number for 2'th complement representation of integer n bit number, the smallest negative number is  $-2^{(n-1)}$  where the largest positive number is  $2^{(n-1)}-1$ . Using the smallest negative number  $-2^{(n-1)}$  might cause critical underflow or overflow. Internal clipping takes this into account by mapping  $-2^{(n-1)}$  to  $-2^{(n-1)}+1$ .

| Hexadecimal Value   | u16   | s16   | q8.8        | q4.12        |

|---------------------|-------|-------|-------------|--------------|

| 0x0000 <sub>h</sub> | 0     | 0     | 0.0         | 0.0          |

| 0x0001 <sub>h</sub> | 1     | 1     | 1 / 256     | 1 / 4096     |

| 0x0002 <sub>h</sub> | 2     | 2     | 2 / 256     | 2 / 4096     |

| 0x0080 <sub>h</sub> | 128   | 128   | 0.5         | 0.03125      |

| 0x0100 <sub>h</sub> | 256   | 256   | 1.0         | 0.0625       |

| 0x0200 <sub>h</sub> | 512   | 512   | 2.0         | 0.125        |

| 0x3FFF <sub>h</sub> | 16383 | 16383 | 16383 / 256 | 16383 / 4096 |

| Hexadecimal Value   | u16   | s16    | q8.8         | q4.12         |

|---------------------|-------|--------|--------------|---------------|

| 0x5A81 <sub>h</sub> | 23169 | 23169  | 23169 / 256  | 23169 / 4096  |

| 0x7FFF <sub>h</sub> | 32767 | 32767  | 32767 / 256  | 32767 / 4096  |

| 0x8000 <sub>h</sub> | 32768 | -32768 | -32768 / 256 | -32768 / 4096 |

| 0x8001 <sub>h</sub> | 32769 | -32767 | -32767 / 256 | -32767 / 4096 |

| 0x8002 <sub>h</sub> | 32770 | -32766 | -32766 / 256 | -32766 / 4096 |

| 0xC001 <sub>h</sub> | 49153 | -16383 | -16383 / 256 | -16383 / 4096 |

| 0xFFFE <sub>h</sub> | 65534 | -2     | -2 / 256     | -2 / 4096     |

| 0xFFFF <sub>h</sub> | 65535 | -1     | -1 / 256     | -1 / 4096     |

Table 5: Examples of u16, s16, q8.8, q4.12

The q8.8 and q4.12 are used for P and I parameters which are positive numbers. Note that q8.8 and q4.12 are used as signed numbers. This is because theses values are multiplied with signed error values resp. error integral values.

#### 4.3.2 N POLE PAIRS, PHI E, PHI M

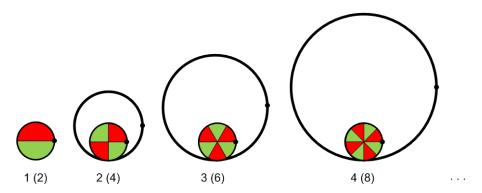

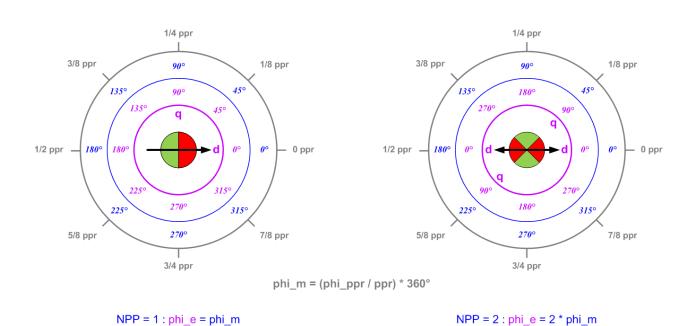

The parameter N\_POLE\_PAIRS defines the factor between electrical angle PHI\_E and mechanical angle PHI\_M of a motor (pls. refer figure 14).

A motor with one (1) pole pair turns once for each electrical period. A motor with two (2) pole pairs turns once for every two electrical periods. A motor with three (3) pole pairs turns once for every three electrical periods. A motor with four pole (4) pairs turns once for every four electrical periods.

The electrical angle PHI\_E is relevant for the commutation of the motor. It is relevant for the torque control of the inner FOC loop.

$$PHI_E = PHI_M \cdot N_POLE_PAIRS$$

(5)

The mechanical angle PHI\_M is primarily relevant for velocity control and for positioning. This is because one wants to control the motor speed in terms of mechanical turns and not in terms of electrical turns.

$$PHI_M = PHI_E/N_POLE_PAIRS$$

(6)

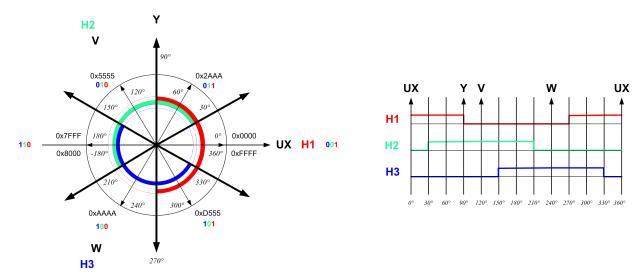

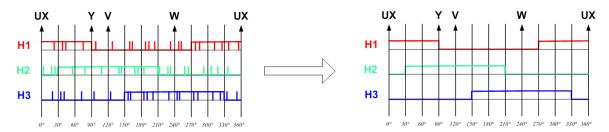

Different encoders give different kinds of position angles. Digital Hall sensors normally give the electrical position PHI\_E that can be used for commutation. Analog encoders give - depending on their resolution - angles that have to be scaled first to mechanical angles PHI\_M and to electrical angles PHI\_E for commutation.

Figure 14: N\_POLE\_PAIRS - Number of Pole Pairs (Number of Poles)

# 4.3.3 Numerical Representation of Angles PHI

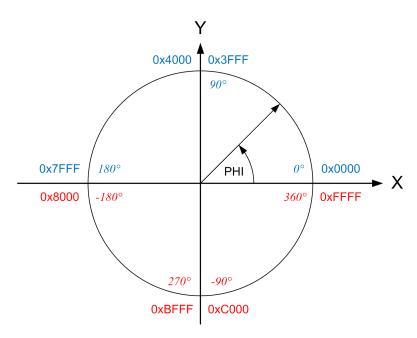

Electrical angles and mechanical angles are represented as 16 bit integer values. One full revolution of  $360\deg$  is equivalent to  $2^{16}=65536$  steps. Any position coming from a sensor is mapped to this integer range. Adding an offset of PHI\_OFFSET causes a rotation of an angle PHI\_OFFSET/ $2^{16}$ . Subtraction of an offset causes a rotation of an angle PHI\_OFFSET in opposite direction.

Figure 15: Integer Representation of Angles as 16 Bit signed (s16) resp. 16 Bit unsigned (u16)

| Hexadecimal Value   | u16   | s16   | PHI[°] | ±PHI[°] |

|---------------------|-------|-------|--------|---------|

| 0x0000 <sub>h</sub> | 0     | 0     | 0.0    | 0.0     |

| 0x1555 <sub>h</sub> | 5461  | 5461  | 30.0   | -330.0  |

| 0x2AAA <sub>h</sub> | 10922 | 10922 | 60.0   | -300.0  |

| 0x4000 <sub>h</sub> | 16384 | 16384 | 90.0   | -270.0  |

| Hexadecimal Value   | u16   | s16    | PHI[°] | ±PHI[°] |

|---------------------|-------|--------|--------|---------|

| 0x5555 <sub>h</sub> | 21845 | 21845  | 120.0  | -240.0  |

| 0x6AAA <sub>h</sub> | 27306 | 27768  | 150.0  | -210.0  |

| 0x8000 <sub>h</sub> | 32768 | -32768 | 180.0  | -180.0  |

| 0x9555 <sub>h</sub> | 38229 | -27307 | 210.0  | -150.0  |

| 0xAAAA <sub>h</sub> | 43690 | -21846 | 240.0  | -120.0  |

| 0xC000 <sub>h</sub> | 49152 | -16384 | 270.0  | -90.0   |

| 0xD555 <sub>h</sub> | 54613 | -10923 | 300.0  | -60.0   |

| 0xEAAA <sub>h</sub> | 60074 | -5462  | 330.0  | -30.0   |

Table 6: Examples of u16, s16, q8.8

The option of adding an offset is for adjustment of angle shift between the motor and stator and the rotor and encoder. Finally, the relative orientations between the motor and stator and the rotor and encoder can be adjusted by just one offset. Alternatively, one can set the counter position of an incremental encoder to zero on initial position. For absolute encoders, one needs to use the offset to set an initial position.

# 4.4 ADC Engine

The ADC engine controls the sampling, selection, scaling and offset correction of different available ADC channels. Two ADC channels are for phase current measurement, three ADC channels are for analog Hall signals or for analog sin-cos-encoder, one ADC channel is for optional measurement of the motor spupply voltage, two additional ADC channels are general purpose where one general purpose analog input can be used as analog target value by the single pin interface.

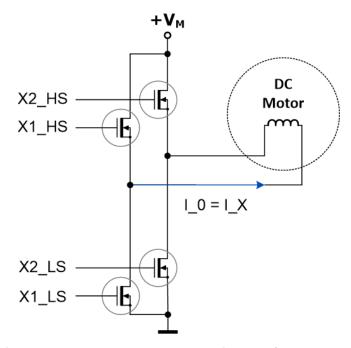

#### 4.4.1 ADC current sensing channels ADC I1 and ADC I0

The ADC channels (ADC\_I0\_POS, ADC\_I0\_NEG, ADC\_I1\_POS, ADC\_I1\_NEG) are for current sensing in differential input configuration. In differential configuration, the ADC\_I0\_POS and ADC\_I0\_POS are the inputs for the sense amplifier output signals where ADC\_I1\_NEG and ADC\_I0\_NEG) are for the zero current sensing reference of the sense amplifiers. In single ended configuration, the ADC\_I0\_POS and ADC\_I0\_POS are the inputs for the sense amplifier output signals where ADC\_I1\_NEG and ADC\_I0\_NEG) are internally connected to ground. The third current channel ADC\_I2 as required for three phase FOC is calculated using Kirchhoff's law ADC\_I2 = - (ADC\_I1 + ADC\_I0).

ADC\_I0\_POS, ADC\_I0\_NEG, ADC\_I1\_POS, ADC\_I1\_NEG are low voltage analog inputs and must not directly connected to in-line sense resistors. The TMC4671 requires external dfferential motor supply common mode range current sensing amplifiers for in-line current sensing.

### 4.4.2 ADC for analog Hall signals or analog sin-cos-encoders AENC\_UX, AENC\_VN, AENC\_WY

For analog Hall and for analog encoder, the ADC engine has three disserential input channles (AENC\_UX\_POS, AENC\_UX\_NEG), (AENC\_VN\_POS, AENC\_VN\_NEG), and AENC\_WY\_POS, AENC\_WY\_NEG). The analog encoder ADC inputs can be configured single ended (AENC\_UX\_POS, AENC\_VN\_POS, AENC\_WY\_POS) with negative inputs (AENC\_UX\_NEG, AENC\_VN\_NEG, AENC\_WY\_NEG) internally connected to ground.

The three channels AENC\_UX, AENC\_VN, AENC\_WY are for three phase analog sine (with +/-120° phase shift) wave Hall signals. The Signals AENC\_UX and AENC\_WY are for two phase analog sine wave and cosin wave Hall signals. The Signals AENC\_UX and AENC\_WY are for analog sin-cos-encoder. The AENC\_VN is for an optional zero pulse channel of sin-cos-encoders. The AENC\_VN is available for read out by the application software but it is not hardware handled by the TMC4671 for position zerroing.

For long analog signal lines, it might be necessary to use external differential receivers with twisted pair line termination resistors to drive the single ended analog encoder inputs of the TMC4671.

#### 4.4.3 ADC supply voltage measurement ADC\_VM

The ADC channel for measurement of supply voltage (ADC\_VM) and is associated with the brake chopper. The ADC\_VM is available as raw value only without digital scaling. This is because it is not directly processed by the FOC engine.

1 Info

ADC\_VM must be scaled down electrically by voltage divider to the allowed voltage range, and might require additional supply voltage spike protection.

#### 4.4.4 ADC\_VM for Brake Choppper

The ADC\_VM is available as input for optional brake chopper as raw value u16. The brake chopper thresholds have to be set as absolute u16 values to activate and deactivate the brake chopper output depending on the ADC\_VM value.

#### 4.4.5 ADC EXT register option

The user can write ADC values into the ADC\_EXT registers of the register bank from external sources or for evaluation purposes. These values can be selected as raw current ADC values by selection. ADC\_EXT registers are primarily intended for test purposes as optional inputs for external current measurement sources.

# 4.4.6 ADC general purpose analog inputs AGPI\_A and AGPI\_B

Two general purpose ADC channels are single-ended analog inputs (AGPI\_A, AGPI\_B). The general purpose analog ADC inputs AGPI\_A and AGPI\_B are available as raw values only without digital scaling. This is because these values are not directly processed by the FOC engine. These general purpose analog inputs (AGPI) are intended to monitor analog voltage signals representing MOSFET temperature or motor temperature. They are two additional ADC channels for the user. Optional, the AGPI\_A is availabe as analog target value signal.

#### 4.4.7 ADC RAW values

The sampled raw ADC values are available for read out by the user. This is important during the system setup phase to determine offset and scaling factors.

### 4.4.8 ADC\_SCALE and ADC\_OFFSET

The FOC engine expects offset corrected ADC current values, scaled into the FOC engine's 16 bit (s16) fixed point representation. The integrated scaler and offset compensator maps raw ADC samples of current measurement channels to 16 bit two's complement values (s16). While the offset is compensated by subtraction, the offset is represented as an unsigned value. The scaling value is signed to compensate wrong measurement direction. The s16 scaled ADC values are available for read out from the register (ADC\_I1, ADC\_I0) resp. (AENC\_UX, AENC\_VN, AENC\_WY) by the user.

1 Info

Wrong scaling factors (ADC\_SCALE) or wrong offsets (ADC\_OFFSET) might cause damages when the FOC is active. Integrated hardware limiters allow protection - especially in the setup phase when using careful limits.

#### 4.4.9 ADC Gain Factors for Real World Values

Each ADC channel of the TMC4671 has an individual gain factor determined by its associated chain of gain factors and by digital scaling factors if available for an ADC channel. ADC register values are either 16 bit unsigned vaulues (u16) or 16 bit signed vaules (s16). With gain factors one can calculate ADC values as real world values if required.

Gain factors IgainADC for ADC current values are typical in units [A/LSB] or [mA/LSB]. Gain factors UgainADC for ADC voltage values are typical in units [V/LSB] or [mV/LSB].

$$ADCmeasuredVoltage[V] = UgainADC[V/LSB] * ADC_VOLTAGE_S16$$

(8)

$$ADC measured Voltage [V] = Ugain ADC [V/LSB] * ADC_VOLTAGE_U16$$

(9)

# 4.4.10 Internal Delta Sigma ADCs

The TMC4671 is equipped with internal delta sigma ADCs for current measurement, supply voltage measurement, analog GPIs and analog encoder signal measurement. Delta sigma ADCs, as integrated within the TMC4671, together with programmable digital filters are flexible in parameterizing concerning resolution vs. speed. The advantage of delta sigma ADCs is that the user can adjust measurement from lower speed with higher resolution to higher speed with lower resolution. This fits with motor control application. Higher resolution is required for low speed signals, while lower resolution satisfies the needs for high speed signals.

Due to high oversampling, the analog input front-end is easier to implement than for successive approximation register ADCs as anti aliasing filters can be chosen to a much higher cutoff frequency. The ADC Engine processes all ADC channels in parallel hardware - avoiding phase shifts between the channels compared to ADC channels integrated in MCUs.

### 4.4.11 Internal Delta Sigma ADC Input Stage Configuration

ADC channels can be configured either as differential ended analog inputs (ADC\_I0, ADC\_I1, AENC\_UX, AENC\_VN, AENC\_WY) or as single ended analog inputs (ADC\_VM, AGPI\_A, AGPI\_B). Additionally, the ADC all channels can be set to fixed voltages (0V, VREF/4, VREF/2, 3\*VREF/4) for calibrations purposes.

| STAGE_CFG(n+2:n) | CONFIGURATION | DESCRIPTION                       | COMMENT                      |

|------------------|---------------|-----------------------------------|------------------------------|

| 0                | INP vs. INN   | differential mode                 | default configuration        |

| 1                | GND vs. INN   | single ended negative INN vs. GND | (for test purposes only)     |

| 2                | VDD/4         | 25% ADC reference voltage         | calibration aid              |

| 3                | 3*VDD/4       | 75% ADC reference voltage         | calibration aid              |

| 4                | INP vs. GND   | single ended mode INP vs. GND     | (half voltage range, offset) |

| 5                | VDD/2         | 50% ADC reference voltage         | calibration aid              |

| 6                | VDD/4         | 25% ADC reference voltage         | (redundant configuration)    |

| 7                | 3*VDD/4       | 75% ADC reference voltage         | (redundant configuration)    |

Table 7: Delta Sigma ( $\Delta\Sigma$ ) ADC Input Stage Configurations

The three bit vector ADC\_STAGES\_CFG(n+2:n) is part of the DS\_ANALOG\_INPUT\_STAGE\_CFG(31:0) with n = 0, 4, 8, 12, 16, 20, 24, 28 for the eight delta sigma ADC channels. DS\_ANALOG\_INPUT\_STAGE\_CFG configures the associated delta sigma ADC input stages according to table 15. For association of the bit position (bit n+2 to bit n) refere register bank section 7.2.

| STAGE_CFG(n+2:n) | ADC channel | function                                 |

|------------------|-------------|------------------------------------------|

| STAGE_CFG(2:0)   | ADC_I0      | sense voltage of current I0              |

| STAGE_CFG(6:4)   | ADC_I1      | sense voltage of current I1              |

| STAGE_CFG(9:8)   | ADC_VM      | down divided supply voltage              |

| STAGE_CFG(10)    | ′1′         | fixed for ADC_VM (STAGE_CFG=4,5,6,7)     |

| STAGE_CFG(13:12) | ADC_AGPI_A  | general purpose analog input A           |

| STAGE_CFG(14)    | ′1′         | fixed for ADC_AGPI_A (STAGE_CFG=4,5,6,7) |

| STAGE_CFG(17:16) | ADC_AGPI_B  | general purpose analog input B           |

| STAGE_CFG(18)    | ′1′         | fixed for ADC_AGPI_B (STAGE_CFG=4,5,6,7) |

| STAGE_CFG(22:20) | ADC_AENC_UX | analog Hall UX / analog encoder COS      |

| STAGE_CFG(26:24) | ADC_AENC_VN | analog Hall V / analog encoder N         |

| STAGE_CFG(30:28) | ADC_AENC_WY | analog Hall WY / analog encoder SIN      |

Table 8: Delta Sigma ( $\Delta\Sigma$ ) ADC Input Stage Configurations

ADC (differential)  $U_{ADC} = U_{INP} - U_{INN}$  ADC (single-ended)  $U_{ADC} = U_{INP} + VDD/2$

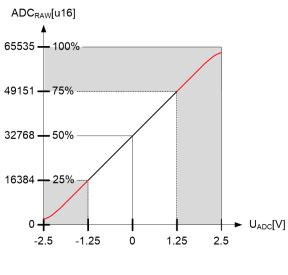

Figure 16: Input Voltage Ranges of internal Delta Sigma ADC Channels)

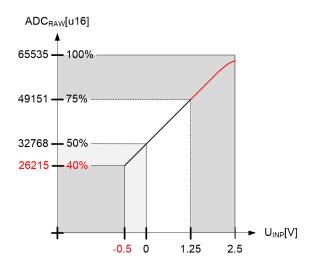

Figure 16 illustrates typical relation between input voltage and corresponding raw ADC output. For differential operation the input range between 25% and 75% corresponds to voltage values between 1.25V to 3.75V. This is the recommended operation area of the ADC. Below 25% and above 75% the ADC shows significant non-linearity due to the Delta Sigma measurement principle.

In single ended operation the recommended input range starts at 0V and ends at 1.25V. Measurement below GND might be distorted and is not recommended.

Due to manufacturing tolerances calibration of offset and amplitude is always recommended. Please also consider stability of the reference voltage.

### 4.4.12 External Delta Sigma ADCs

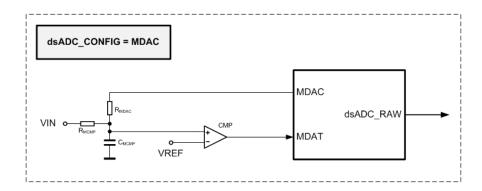

The delta sigma front-end of the ADC engine supports external delta sigma modulators to enable isolated delta sigma modulators for the TMC4671. Additionally, the delta sigma front-end supports low-cost comparators together with two resistors and one capacitor (R-C-R-CMP) forming first order delta sigma modulators, as generic analog front-end for pure digital variants of the TMC4671 core.

#### 4.4.13 ADC Group A and ADC Group B

ADC channels of the TMC4671 are grouped into two groups, to enable different sample rates for two groups of analog signals if needed. Running both ADC groups with same sampling frequency is recommended for almost all applications. It might be necessary to run its ADC channels of analog encoder with a much higher frequency than the ADC channels for current measurement in case of using a high resolution analog encoder.

## 4.4.14 Delta Sigma Configuration and Timing Configuration

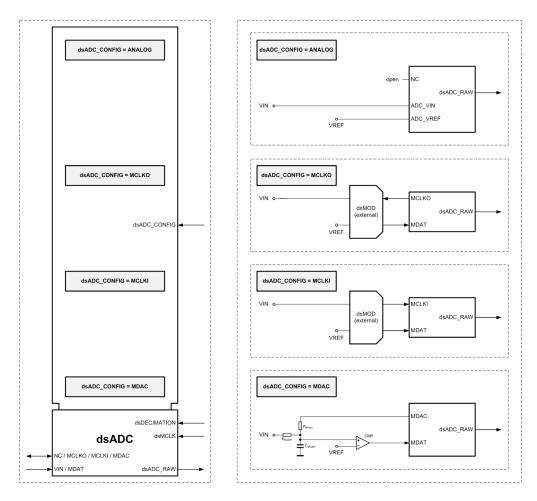

The delta sigma configuration is programmed via MCFG register that selects the mode (internal/external delta sigma modulator with programmable MCLK; delta sigma modulator clock mode (MCLK output, MCLK input, MCLK used as MDAC output with external R-C-R-CMP configuration); delta sigma modulator clock and its polarity; and the polarity of the delta sigma modulator data signal MDAT).

### 1 Info

The power-on delta sigma configuration should fit with most applications when using the intergated delta sigma ADCs of the TMC4671. Primarily, the default delta sigma configuration needs to be adapted when using external delta sigma modulators or to select differential ADC input configurations, or in case of enhanced sampling requirenment for high resolution analog encoders.

Figure 17: Delta Sigma ADC Configurations dsADC\_CONFIG (internal: ANALOG vs. external: MCLKO, MCLKI, MDAC)

| dsADC_CONGIG | Description                                                                                | NC_MCLKO_MCLKI_MDAC      | VIN_MDAT           |

|--------------|--------------------------------------------------------------------------------------------|--------------------------|--------------------|

| ANALOG       | integrated internal ADC mode, VIN_MDAT is analog input VIN                                 | MCLK not connected (NC)  | VIN (analog)       |

| MCLKO        | external dsModulator (e.g. AD7403) with MCLK input driven by MCLKO                         | MCLK output              | MDAT input         |

| MCLKI        | external dsModulator (e.g. AD7400) with MCLK output that drives MCLKI                      | MCLK input               | MDAT input         |

| MDAC         | external dsModulator (e.g. LM339) realized by external comparator CMP with two R and one C | MDAC output (= MCLK out) | MDAT input for CMP |

Table 9: Delta Sigma ADC Configurations (figure 17), selected with dsADC\_MCFG\_A and dsADC\_MCFG\_B.

| register     | function                                                                       |

|--------------|--------------------------------------------------------------------------------|

| dsADC_MCFG_B | delta sigma modulator configuration MCFG (ANALOG, MCLKI, MCLKO, MDAC), group B |

| dsADC_MCFG_A | delta sigma modulator configuration MCFG (ANALOG, MCLKI, MCLKO, MDAC), group A |

| dsADC_MCLK_B | delta sigma modulator clock MCLK, group B                                      |

| dsADC_MCLK_A | delta sigma modulator clock MCLK, group A                                      |

| dsADC_MDEC_B | delta sigma decimation parameter MDEC, group B                                 |

| dsADC_MDEC_A | delta sigma decimation parameter MDEC, group A                                 |

Table 10: Registers for Delta Sigma Configuration

#### 4.4.14.1 Timing Configuration MCLK

When the programmable MCLK is selected, the MCLK\_A and MCLK\_B parameter registers define the programmable clock frequency fMCLK of the delta sigma modulator clock signal MCLK for delta sigma modulator group A and group B. For a given target delta sigma modulator frequency fMCLK, together with the internal clock frequency fCLK = 100MHz, the MCLK frequency parameter is calculated by

$$\mathsf{MCLK} = 2^{31} \cdot \mathsf{fMCLK}[Hz]/\mathsf{fCLK}[Hz] \tag{10}$$

Due to the 32 bit's length of the MCLK frequency parameter, the resulting frequency fMCLK might differ from the desired frequency fMCLK. The back calculation of the resulting frequency fMCLK for a calculated MCLK parameter with 32 bit length is defined by

$$\mathsf{fMCLK}[Hz] = \mathsf{fCLK}[Hz] \cdot \mathsf{MCLK}/2^{31} \tag{11}$$

The precise programming of the MCLK frequency is primarily intended for external delta sigma modulators to meet given EMI requirements. With that, the user can programm frequencies fMCLK with a resolution better than 0.1 Hz. This advantage concerning EMI might cause trouble when using external delta signal modulators if they are sensitive to slight frequency alternating. This is not an issue when using external first-order delta sigma modulators based on R-C-R-CMP (e.g. LM339). But for external second-order delta signal modulators, it is recommended to configure the MCLK parameter for frequencies fMCLK with kHz quantization (e.g. 10,001,000 Hz instead of 10,000,001 Hz).

| fMCLK_target | MCLK       | fMCLK_resulting    | comment                                             |

|--------------|------------|--------------------|-----------------------------------------------------|

| 25 MHz       | 0x20000000 | 25 MHz             | w/o fMCLK frequency jitter, recommended             |