Ultra-Small, Low-Power, I<sup>2</sup>C-Compatible, 860-SPS, 16-Bit ADCs With Internal Reference, Oscillator, and Programmable Comparator

ANALOGYSEMI

## **1. FEATURES**

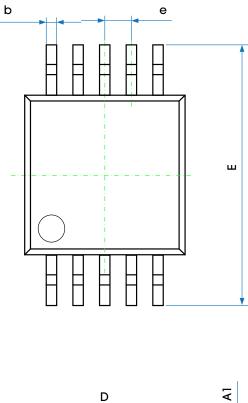

- Small 3mm × 3mm MSOP package

- Ultra-small QFN package:

2mm × 1.5mm × 0.4mm

- Wide supply range: 2.0V to 5.5V

- Low current consumption: 145µA (continuous-conversion mode)

- Programmable output data rate: 8SPS to 860SPS

- 50Hz and 60Hz rejection filter

- Single-cycle settling

- Internal low-drift voltage reference

- Internal oscillator

- I<sup>2</sup>C interface: four pin-selectable addresses

- Four single-ended or two differential inputs

- Programmable comparator

- Operating temperature range: -40°C to 125°C

## **2. APPLICATIONS**

- Portable instrumentation

- Battery voltage and current monitoring

- Temperature measurement systems

- Consumer electronics

- Factory automation and process control

## **3. DESCRIPTION**

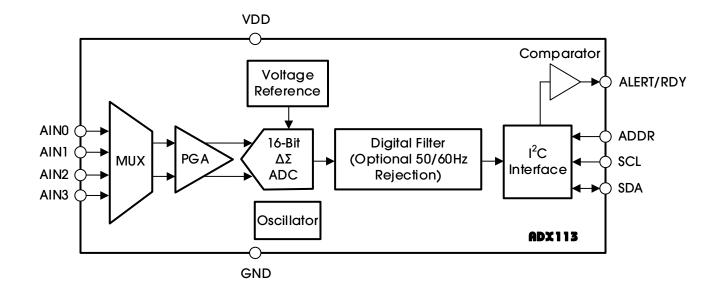

The ADX113 device is precision, low-power, 16-bit, I<sup>2</sup>C-compatible, analog-to-digital converter (ADC) offered with MSOP-10 and QFN-10 packages. The ADX113 device incorporates a low-drift voltage reference and an oscillator. It also incorporates a programmable gain amplifier (PGA) and a digital comparator. These features, along with a wide operating supply range, make the ADX113 well suited for power- and space-constrained, sensor measurement applications.

The ADX113 performs conversions at data rates up to 860 samples per second (SPS). Internal digital filter provides flexible output data rate, from 8SPS to 860SPS. Additionally, it is optional to select 50Hz and 60Hz normal mode rejection filter. The PGA offers input ranges from  $\pm 256 \text{mV}$  to  $\pm 6.144 \text{V}$ , allowina precise laraeand small-sianal measurements. The ADX113 features an input multiplexer (MUX) that allows two differential or four single-ended input measurements. Use the digital comparator in the ADX113 for under- and overvoltage detection.

The ADX113 operates in either continuousconversion mode or single-shot mode. The internal filter is single-cycle settling in both modes. The devices are automatically powered down after one conversion in single-shot mode; therefore, power consumption is significantly reduced during idle periods. See Table 1 for the order information.

#### Table 1 lists the order information.

#### Table 1. Order Information

| ORDER NUMBER <sup>(1)</sup> | CH<br>(#) | BITS | PACKAGE | BODY<br>SIZE<br>(mm) | MARKING | ODR<br>(SPS) | INTERFACE        | COMPARATOR | TEMP<br>SENSOR | 50/60<br>REJECTION | OP.<br>TEMP<br>(°C) | PKG.<br>OPTION |

|-----------------------------|-----------|------|---------|----------------------|---------|--------------|------------------|------------|----------------|--------------------|---------------------|----------------|

| ADX113AMSOP10               | 2(4)      | 16   | MSOP10  | 3 × 3                | ADX113  | 860          | I <sup>2</sup> C | Yes        | No             | Yes                | -40-125             | T/R-3000       |

#### Table 2. Family Selection Guide

| ORDER NUMBER <sup>(1)</sup>  | CH<br>(#) | BITS | PACKAGE | BODY<br>SIZE<br>(mm) | MARKING | ODR<br>(SPS) | INTERFACE        | COMPARATOR | TEMP<br>SENSOR | 50/60<br>REJECTION | OP.<br>TEMP<br>(°C) | PKG.<br>Option |

|------------------------------|-----------|------|---------|----------------------|---------|--------------|------------------|------------|----------------|--------------------|---------------------|----------------|

| ADX111AMSOP10                | 2(4)      | 16   | MSOP10  | 3 × 3                | ADX111  | 860          | I <sup>2</sup> C | Yes        | No             | No                 | -40-125             | T/R-3000       |

| ADX111AQFN10                 | 2(4)      | 16   | QFN10   | 2 × 1.5              | 111     | 860          | l <sup>2</sup> C | Yes        | No             | No                 | -40-125             | T/R-4000       |

| ADX112AMSOP10                | 2(4)      | 16   | MSOP10  | 3 × 3                | ADX112  | 860          | SPI              | No         | Yes            | No                 | -40-125             | T/R-3000       |

| ADX112AQFN10                 | 2(4)      | 16   | QFN10   | 2 × 1.5              | 112     | 860          | SPI              | No         | Yes            | No                 | -40-125             | T/R-4000       |

| ADX114AMSOP10                | 2(4)      | 16   | MSOP10  | 3 × 3                | ADX114  | 3571         | SPI              | No         | Yes            | Yes                | -40-125             | T/R-3000       |

| ADX121AMSOP10                | 2(4)      | 20   | MSOP10  | 3 × 3                | ADX121  | 3571         | l <sup>2</sup> C | Yes        | No             | Yes                | -40-125             | T/R-3000       |

| ADX121AQFN10 <sup>(2)</sup>  | 2(4)      | 20   | QFN10   | 2 × 1.5              | 121     | 3571         | I <sup>2</sup> C | Yes        | No             | Yes                | -40-125             | T/R-4000       |

| ADX122AMSOP10                | 2(4)      | 20   | MSOP10  | 3 × 3                | ADX122  | 3571         | SPI              | No         | No             | Yes                | -40-125             | T/R-3000       |

| ADX122AQFN10 <sup>(2)</sup>  | 2(4)      | 20   | QFN10   | 2 × 1.5              | 122     | 3571         | SPI              | No         | No             | Yes                | -40-125             | T/R-4000       |

| ADX128AMSOP10 <sup>(2)</sup> | 2(4)      | 20   | MSOP10  | 3 × 3                | ADX128  | 7143         | SPI              | No         | No             | Yes                | -40-125             | T/R-3000       |

| ADX128AQFN10 <sup>(2)</sup>  | 2(4)      | 20   | QFN10   | 2 × 1.5              | 128     | 7143         | SPI              | No         | No             | Yes                | -40-125             | T/R-4000       |

| ADX125AMSOP10                | 2(4)      | 20   | MSOP10  | 3 × 3                | ADX125  | 3571         | l <sup>2</sup> C | Yes        | Yes            | Yes                | -40-125             | T/R-3000       |

| ADX126AMSOP10                | 2(4)      | 20   | MSOP10  | 3 × 3                | ADX126  | 3571         | SPI              | No         | Yes            | Yes                | -40-125             | T/R-3000       |

| ADX125AQFN10 <sup>(2)</sup>  | 2(4)      | 20   | QFN10   | 2 × 1.5              | 125     | 3571         | l <sup>2</sup> C | Yes        | Yes            | Yes                | -40-125             | T/R-4000       |

| ADX126AQFN10 <sup>(2)</sup>  | 2(4)      | 20   | QFN10   | 2 × 1.5              | 126     | 3571         | SPI              | No         | Yes            | Yes                | -40-125             | T/R-4000       |

| ADX131AQFN10(2)              | 2(4)      | 20   | QFN10   | 2 × 1.5              | 131     | 440          | l <sup>2</sup> C | Yes        | No             | Yes                | -40-125             | T/R-4000       |

| ADX132AQFN10 <sup>(2)</sup>  | 2(4)      | 20   | QFN10   | 2 × 1.5              | 132     | 440          | SPI              | No         | No             | Yes                | -40-125             | T/R-4000       |

| ADX123AMSOP10 <sup>(2)</sup> | 2(4)      | 20   | MSOP10  | 3 × 3                | ADX123  | 3571         | Daisy Chain      | No         | No             | Yes                | -40-125             | T/R-3000       |

Devices can be ordered via the following two ways:

1. Place orders directly on our website (www.analogysemi.com), or;

2. Contact our sales team by mailing to sales@analogysemi.com.

Note 1:

Note 2: Available in the future.

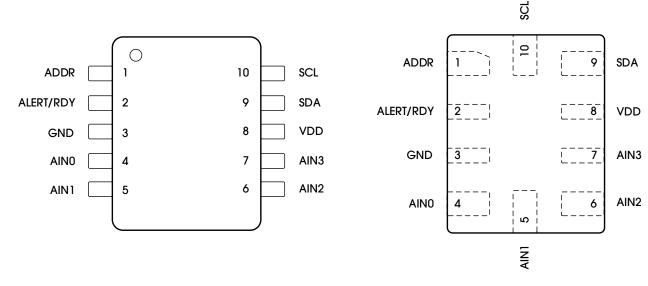

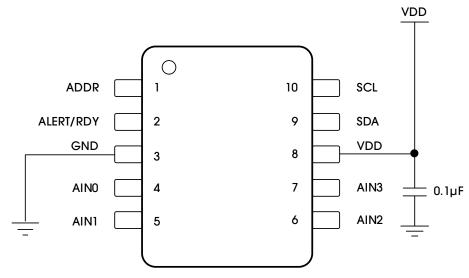

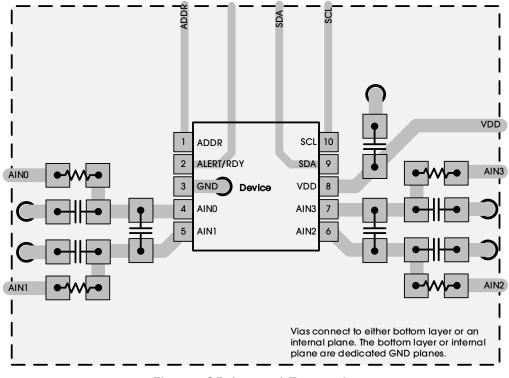

## 4. PIN CONFIGURATION AND FUNCTIONS

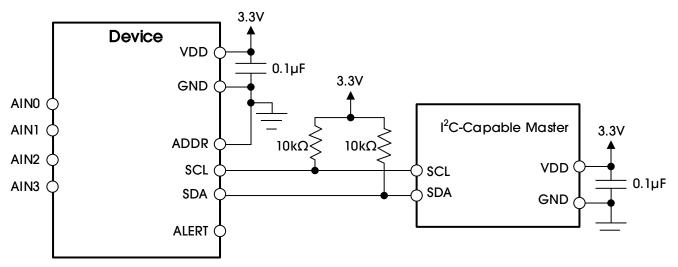

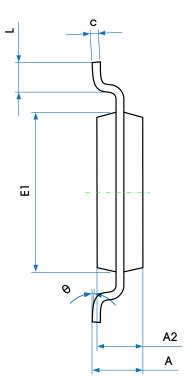

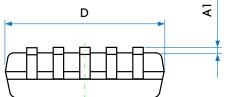

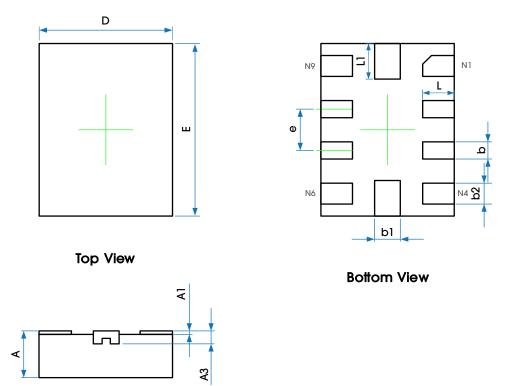

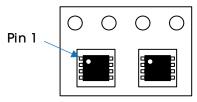

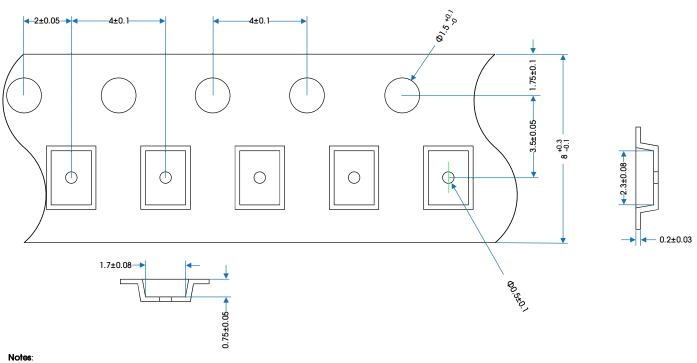

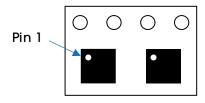

Figure 1 illustrates the pin configuration.

MSOP-10 Package

QFN-10 Package

### Figure 1. Pin Configuration

Table 3 lists the pin functions.

Table 3. Pin Functions

| POSITION | NAME      | TYPE           | DESCRIPTION                                                                        |

|----------|-----------|----------------|------------------------------------------------------------------------------------|

| 1        | ADDR      | Digital input  | I <sup>2</sup> C slave address select                                              |

| 2        | ALERT/RDY | Digital output | Comparator output or conversion ready, open drain, connected to a pull-up resistor |

| 3        | GND       | Power          | Ground                                                                             |

| 4        | AINO      | Analog input   | Analog input 0                                                                     |

| 5        | AIN1      | Analog input   | Analog input 1                                                                     |

| 6        | AIN2      | Analog input   | Analog input 2                                                                     |

| 7        | AIN3      | Analog input   | Analog input 3                                                                     |

| 8        | VDD       | Power          | Power supply. Connects a 0.1µF, power-supply decoupling capacitor to GND.          |

| 9        | SDA       | Digital I/O    | Serial data. Transmits and receives data.                                          |

| 10       | SCL       | Digital input  | Serial clock input. Locks data on SDA.                                             |

## **5. SPECIFICATIONS**

## **5.1 ABSOLUTE MAXIMUM RATINGS**

Table 4 lists the absolute maximum ratings of the ADX113.

#### Table 4. Absolute Maximum Ratings

| PARAMETER                 | DESCRIPTION                       | MIN       |           |       |

|---------------------------|-----------------------------------|-----------|-----------|-------|

| PARAIVIETER               | DESCRIPTION                       | IVIIIN    | MAX       | UNITS |

| Power-Supply Voltage      | VDD to GND                        | -0.3      | 7         | V     |

| Analog Input Voltage      | AINO, AIN1, AIN2, AIN3            | GND - 0.3 | VDD + 0.3 | V     |

| Digital Input Voltage     | SDA, SCL, ADDR, ALERT/RDY         | GND - 0.3 | 5.5       | V     |

| Input Current, Continuous | Any pin except power supply pins  | -10       | 10        | mA    |

|                           | Operating ambient, T <sub>A</sub> | -40       | 125       |       |

| Temperature               | Junction, T <sub>J</sub>          | -40       | 150       | °C    |

|                           | Storage, T <sub>stg</sub>         | -60       | 150       |       |

Note: Stresses beyond those listed under Table 4 may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Table 6. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## **5.2 ESD RATINGS**

Table 5 lists the ESD ratings of the ADX113.

Table 5. ESD Ratings

| PARAMETER     | SYMBOL             | DESCRIPTION                                                                    | VALUE | UNITS |

|---------------|--------------------|--------------------------------------------------------------------------------|-------|-------|

| Electrostatic | V <sub>(ESD)</sub> | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±6000 | V     |

| Discharge     | • (ESD)            | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1500 | •     |

Note 1: The JEDEC document JEP155 indicates that 500V HBM allows safe manufacturing with a standard ESD control process.

Note 2: The JEDEC document JEP157 indicates that 250V CDM allows safe manufacturing with a standard ESD control process.

## **5.3 RECOMMENDED OPERATING CONDITIONS**

Table 6 lists the recommended operating conditions for the ADX113.

#### Table 6. Recommended Operating Conditions

| PARAMETER                                        | DESCRIPTION                                    | SYMBOL              | MIN    | NOM | MAX    | UNITS |

|--------------------------------------------------|------------------------------------------------|---------------------|--------|-----|--------|-------|

| POWER SUPPLY                                     |                                                |                     |        |     |        |       |

| Power Supply                                     | VDD to GND                                     |                     | 2      |     | 5.5    | V     |

| ANALOG INPUTS <sup>(1)</sup>                     | · · ·                                          |                     |        |     |        |       |

| Full-Scale Input Voltage<br>Range <sup>(2)</sup> | $V_{\rm IN} = V_{\rm (AINP)} - V_{\rm (AINN)}$ | FSR                 | ±0.256 |     | ±6.144 | V     |

| Absolute Input Voltage                           |                                                | V <sub>(AINx)</sub> | GND    |     | VDD    | V     |

| DIGITAL INPUTS                                   |                                                |                     |        |     |        |       |

| Digital Input Voltage                            |                                                | V <sub>DIG</sub>    | GND    |     | 5.5    | V     |

| TEMPERATURE RANGE                                |                                                |                     |        |     |        |       |

| Operating Ambient<br>Temperature                 |                                                | T <sub>A</sub>      | -40    |     | 125    | °C    |

Note 1: AIN<sub>P</sub> and AIN<sub>N</sub> denote the selected positive and negative inputs. AINx denotes one of the four available analog inputs.

Note 2: This parameter expresses the full-scale range of the ADC scaling. No more than VDD + 0.3V must be applied to the analog inputs of the device. See Table 12 for more information.

## **5.4 THERMAL INFORMATION**

Table 7 lists the thermal information for the ADX113.

#### Table 7. Thermal Information

| PARAMETER                                    | SYMBOL                | MSOP-10 | QFN-10 | UNITS |

|----------------------------------------------|-----------------------|---------|--------|-------|

| Junction-to-Ambient Thermal Resistance       | R <sub>eja</sub>      | 150     | 119    | °C/W  |

| Junction-to-Case (Top) Thermal Resistance    | R <sub>0JC(top)</sub> | 54      | 60     | °C/W  |

| Junction-to-Board Thermal Resistance         | R <sub>ejb</sub>      | 90      | 39     | °C/W  |

| Junction-to-Top Characterization Parameter   | τĻΨ                   | 3       | 4      | °C/W  |

| Junction-to-Board Characterization Parameter | Ψ <sub>ЈВ</sub>       | 86      | 39     | °C/W  |

| Junction-to-Case (Bottom) Thermal Resistance | R <sub>0JC(bot)</sub> | 90      | 45     | °C/W  |

## **5.5 ELECTRICAL CHARACTERISTICS**

Table 8 lists the electrical characteristics of ADX113. At VDD = 3.3V, data rate = 8SPS, and full-scale input voltage range (FSR) =  $\pm 2.048V$  (unless otherwise noted). Maximum and minimum specifications apply from  $T_A = -40^{\circ}C$  to  $125^{\circ}C$ . Typical specifications are at  $T_A = 25^{\circ}C$ .

#### Table 8. Electrical Characteristics

| PARAMETER                                  | SYMBOL | CONDITIONS                                         | MIN         | TYP                        | MAX          | UNITS  |

|--------------------------------------------|--------|----------------------------------------------------|-------------|----------------------------|--------------|--------|

| ANALOG INPUT                               |        |                                                    |             |                            |              |        |

|                                            |        | $FSR = \pm 6.144V^{(1)}$                           |             | 9                          |              |        |

| Common-Mode Input                          |        | $FSR = \pm 4.096V^{(1)}$                           |             | 7                          |              |        |

| Impedance                                  |        | $FSR = \pm 2.048V$                                 |             | 6                          |              | MΩ     |

| impedance                                  |        | $FSR = \pm 1.024V$                                 |             | 5                          |              |        |

|                                            |        | $FSR = \pm 0.512V, FSR = \pm 0.256V$               |             | 6                          |              |        |

|                                            |        | $FSR = \pm 6.144V^{(1)}$                           |             | 26                         |              |        |

|                                            |        | $FSR = \pm 4.096V^{(1)}$                           |             | 17                         |              | MΩ     |

| Differential Input Impedance               |        | $FSR = \pm 2.048V$                                 |             | 3                          |              | 1012.2 |

|                                            |        | $FSR = \pm 1.024V$                                 |             | 1.5                        |              |        |

|                                            |        | $FSR = \pm 0.512V, \pm 0.256V$                     |             | 0.9                        |              | MΩ     |

| SYSTEM PERFORMANCE                         |        |                                                    |             |                            |              |        |

| Resolution (No Missing Codes)              |        |                                                    | 16          |                            |              | Bits   |

| Data Rate                                  | DR     |                                                    | 8, 16 (20), | , 32, 64, 128,<br>475, 860 | , 250 (316), | SPS    |

| Data Rate Variation                        |        | All data rates                                     | -7%         |                            | 6%           |        |

| Output Noise                               |        |                                                    | See NC      | DISE PERFOR<br>section     | MANCE        |        |

| Integral Nonlinearity                      | INL    | DR = 8SPS, FSR = $\pm 2.048V^{(2)}$                |             | 0.5                        | 1            | LSB    |

| Offset Error                               |        | FSR = ±2.048V, differential inputs                 | -2          | 0                          | 2            | 100    |

|                                            |        | FSR = ±2.048V, single-ended inputs                 |             | ±2                         |              | LSB    |

| Offset Drift Over Temperature              |        | FSR = ±2.048V                                      |             | 0.005                      |              | LSB/°C |

| Long-Term Offset Drift                     |        | FSR = ±2.048V, T <sub>A</sub> = 125°C,<br>1000 hrs |             | 0.5                        |              | LSB    |

| Offset Power-Supply Rejection              |        | $FSR = \pm 2.048V$ , DC supply variation           |             | 0.5                        |              | LSB/V  |

| Offset Channel Match                       |        | Match between any two inputs                       |             | 2                          |              | LSB    |

| Gain Error <sup>(3)</sup>                  |        | $FSR = \pm 2.048V, T_A = 25^{\circ}C$              |             | 0.01%                      | 0.10%        |        |

|                                            |        | $FSR = \pm 0.256V$                                 |             | 8                          |              |        |

| Gain Drift Over Temperature <sup>(3)</sup> |        | $FSR = \pm 2.048V$                                 |             | 8                          | 30           | ppm/°C |

|                                            |        | $FSR = \pm 6.144V^{(1)}$                           |             | 8                          |              |        |

| Long-Term Gain Drift <sup>(3)</sup>        |        | FSR = ±2.048V, T <sub>A</sub> = 125°C,<br>1000 hrs |             | ±0.05                      |              | %      |

| Gain Power-Supply Rejection                |        |                                                    |             | 70                         |              | ppm/V  |

| Gain Match <sup>(3)</sup>                  |        | Match between any two gains                        |             | 0.01%                      | 0.05%        |        |

| Gain Channel Match                         |        | Match between any two inputs                       |             | 0.03%                      | 0.05%        |        |

|                                            |        | At DC, FSR = ±0.256V                               |             | >110                       |              |        |

| Common Mode Delection                      |        | At DC, FSR = ±2.048V                               |             | >105                       |              |        |

| Common-Mode Rejection<br>Ratio             | CMRR   | At DC, FSR = ±6.144V <sup>(1)</sup>                |             |                            |              | dB     |

| Kaio                                       |        | $f_{CM} = 60Hz, DR = 8SPS$                         |             | 103                        |              |        |

|                                            |        | $f_{CM} = 50Hz$ , DR = 8SPS                        |             | 104                        |              |        |

|                             |                  | ODR = 20SPS, Fi<br>60 = 0, 50Hz ± 1  |                              | 72      | 120  |         | dB |  |

|-----------------------------|------------------|--------------------------------------|------------------------------|---------|------|---------|----|--|

| Normal-Mode Rejection Ratio | NMRR             | ODR = 20SPS, Fi<br>60 = 1, 60Hz ± 1  |                              | 73      | 128  |         | dB |  |

|                             |                  | ODR = 20SPS, Fi<br>60 = 1, 50Hz or 6 | 57                           | 100     |      | dB      |    |  |

| DIGITAL INPUT/OUTPUT        |                  |                                      |                              |         |      |         |    |  |

| High-Level Input Voltage    | VIH              |                                      |                              | 0.7 VDD |      | 5.5     | V  |  |

| Low-Level Input Voltage     | V <sub>IL</sub>  |                                      |                              | GND     |      | 0.3 VDD | V  |  |

| Low-Level Output Voltage    | V <sub>OL</sub>  | I <sub>OL</sub> = 3mA                | I <sub>OL</sub> = 3mA        |         | 0.15 | 0.4     | V  |  |

| Input Leakage Current       |                  | GND < V <sub>DIG</sub> < V           | GND < V <sub>DIG</sub> < VDD |         |      | 10      | μA |  |

| POWER SUPPLY                |                  |                                      |                              |         |      |         |    |  |

|                             |                  | Power-down                           | $T_A = 25^{\circ}C$          |         | 0.65 | 1       |    |  |

| Supply Current              |                  | Power-down                           |                              |         |      | 3.5     |    |  |

| Supply Current              | I <sub>VDD</sub> | Ore exerting                         | T <sub>A</sub> = 25°C        |         | 145  | 170     | μA |  |

|                             |                  | Operating                            |                              |         |      | 300     |    |  |

|                             |                  | VDD = 5.0V                           | -                            |         | 0.9  |         |    |  |

| Power Dissipation           | PD               | VDD = 3.3V                           |                              |         | 0.5  |         | mW |  |

|                             |                  | VDD = 2.0V                           |                              |         | 0.3  |         |    |  |

Note 1: This parameter expresses the full-scale range of the ADC scaling. No more than VDD + 0.3V must be applied to the analog inputs of the device. See Table 11 for more information.

Note 2: Best-fit INL; covers 98% of full-scale.

Note 3: Includes all errors from onboard PGA and voltage reference.

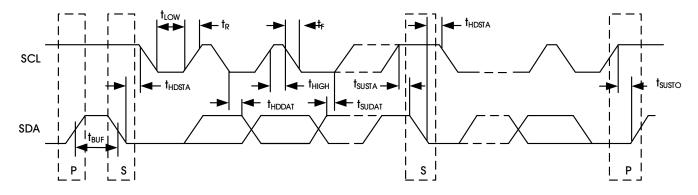

## 5.6 TIMING REQUIREMENTS: I<sup>2</sup>C INTERFACE

Table 9 lists the timing requirements for the  $l^2C$  interface. VDD = 2.0V to 5.5V, unless otherwise noted.

#### Table 9. Timing Requirements: I<sup>2</sup>C Interface

|                                                                                                    | SVMD OI                 | FAST | MODE | HIGH-SPE | ED MODE | UNITS |

|----------------------------------------------------------------------------------------------------|-------------------------|------|------|----------|---------|-------|

| PARAMETER                                                                                          | SYMBOL                  | MIN  | MAX  | MIN      | MAX     | UNIIS |

| SCL Clock Frequency                                                                                | <b>f</b> <sub>SCL</sub> | 0.01 | 0.4  | 0.01     | 3.4     | MHz   |

| Bus Free Time Between START and STOP<br>Condition                                                  | t <sub>BUF</sub>        | 600  |      | 160      |         | ns    |

| Hold Time After Repeated START<br>Condition. (After this period, the first<br>clock is generated.) | t <sub>hdsta</sub>      | 600  |      | 160      |         | ns    |

| Setup Time for A Repeated START<br>Condition                                                       | t <sub>susta</sub>      | 600  |      | 160      |         | ns    |

| Setup Time for STOP Condition                                                                      | t <sub>susto</sub>      | 600  |      | 160      |         | ns    |

| Data Hold Time                                                                                     | t <sub>HDDAT</sub>      | 0    |      | 0        |         | ns    |

| Data Setup Time                                                                                    | t <sub>sudat</sub>      | 100  |      | 10       |         | ns    |

| Low Period of the SCL Clock Pin                                                                    | t <sub>LOW</sub>        | 1300 |      | 160      |         | ns    |

| High Period for the SCL Clock Pin                                                                  | t <sub>HIGH</sub>       | 600  |      | 60       |         | ns    |

| Rise Time for Both SDA and SCL Signals <sup>(1)</sup>                                              | t <sub>F</sub>          |      | 300  |          | 160     | ns    |

| Fall Time for Both SDA and SCL Signals <sup>(1)</sup>                                              | t <sub>R</sub>          |      | 300  |          | 160     | ns    |

Note: For high-speed mode maximum values, the capacitive load on the bus line must not exceed 400pF. Figure 2 shows the I<sup>2</sup>C interface timing.

Figure 2. I<sup>2</sup>C Interface Timing

## **5.7 TYPICAL CHARACTERISTICS**

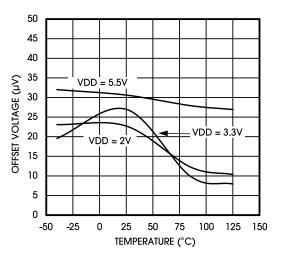

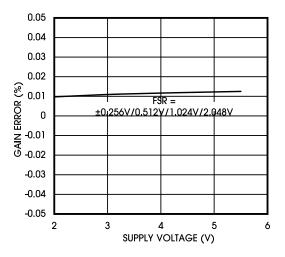

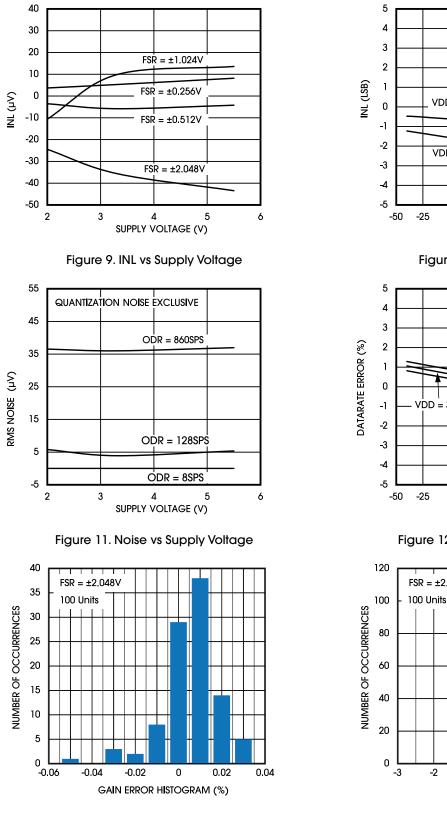

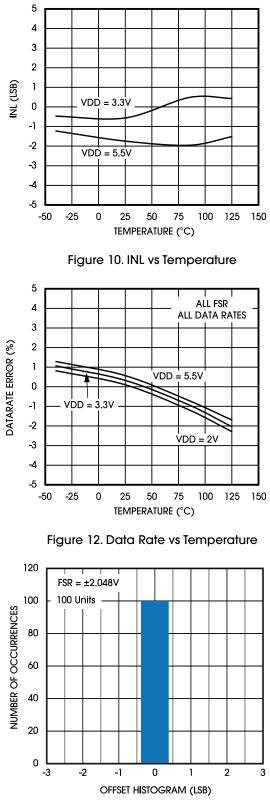

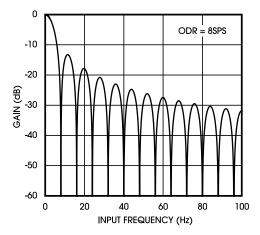

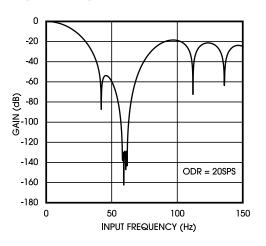

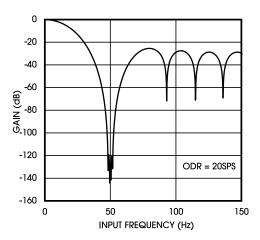

T<sub>A</sub> = 25°C, VDD = 3.3V, FSR = ±2.048V, DR = 8SPS, unless otherwise noted.

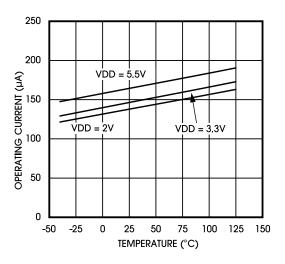

Figure 3. Operating Current vs Temperature

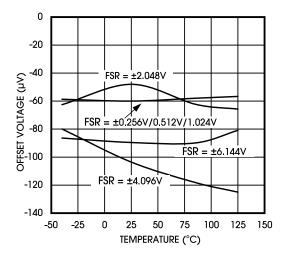

Figure 5. Single-Ended Offset Error vs Temperature

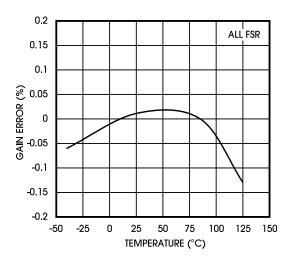

Figure 7. Gain Error vs Temperature

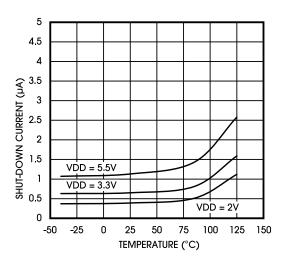

Figure 4. Power-Down Current vs Temperature

Figure 6. Differential Offset vs Temperature

Figure 8. Gain Error vs Supply Voltage

## **5.8 TYPICAL CHARACTERISTICS (CONTINUED)**

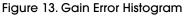

T<sub>A</sub> = 25°C, VDD = 3.3V, FSR = ±2.048V, DR = 8SPS, unless otherwise noted.

Figure 14. Offset Histogram

## **5.9 TYPICAL CHARACTERISTICS (CONTINUED)**

T<sub>A</sub> = 25°C, VDD = 3.3V, FSR = ±2.048V, DR = 8SPS, unless otherwise noted.

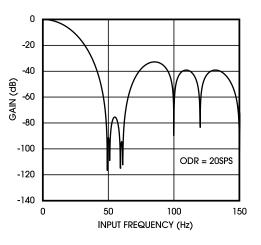

Figure 15. Digital Filter Frequency Response

Figure 17. Digital Filter 60Hz Rejection Frequency Response

Figure 16. Digital Filter 50Hz Rejection Frequency Response

Figure 18. Digital Filter 50 & 60Hz Rejection Frequency Response

## 6. PARAMETER MEASUREMENT INFORMATION

## 6.1 NOISE PERFORMANCE

Table 10 and Table 11 summarize the ADX113 noise performance, showing the RMS noise, peak-to-peak noise, effective resolution, and noise-free (peak-to-peak) resolution for various output data rates and gain settings. Data are representative of typical noise performance at  $T_A = 25^{\circ}$ C with the differential inputs shorted together externally, when the ADC is continuously converting on a single channel. Table 10 shows the input-referred noise in units of  $\mu V_{RMS}$  for the conditions shown. Note that  $\mu V_{PP}$  values are shown in parenthesis. Table 11 shows the effective resolution calculated from  $\mu V_{RMS}$  values using Equation 1. The noise-free resolution calculated from peak-to-peak noise values using Equation 2 are shown in parenthesis.

Effective Resolution = In (FSR /

$$V_{\text{RMS-Noise}}$$

) / In(2) (1)

Noise-Free Resolution = ln (FSR /

$$V_{PP-Noise}$$

) / ln (2) (2)

Table 10. Noise in  $\mu V_{RMS}$  ( $\mu V_{PP}$ ) at VDD = 3.3V

| DATA RATE |               |             | FSR (Full-Sc | ale Range)    |                 |                  |

|-----------|---------------|-------------|--------------|---------------|-----------------|------------------|

| (SPS)     | ±6.144V       | ±4.096V     | ±2.048V      | ±1.024V       | ±0.512V         | ±0.256V          |

| 8         | 187.5 (187.5) | 125 (125)   | 62.5 (62.5)  | 31.25 (31.25) | 15.625 (15.625) | 7.8125 (7.8125)  |

| 16        | 187.5 (187.6) | 125 (125)   | 62.5 (62.5)  | 31.25 (31.25) | 15.625 (15.625) | 7.8125 (7.8125)  |

| 32        | 187.5 (187.7) | 125 (125)   | 62.5 (62.5)  | 31.25 (31.25) | 15.625 (15.625) | 7.8125 (7.8125)  |

| 64        | 187.5 (187.8) | 125 (125)   | 62.5 (62.5)  | 31.25 (31.25) | 15.625 (15.625) | 7.8125 (13.889)  |

| 128       | 187.5 (187.9) | 125 (125)   | 62.5 (62.5)  | 31.25 (31.25) | 15.625 (17.333) | 7.8125 (15.625)  |

| 250       | 187.5 (375)   | 125 (250)   | 62.5 (125)   | 31.25 (62.5)  | 15.625 (31.25)  | 7.8125 (23.4375) |

| 475       | 187.5 (375)   | 125 (250)   | 62.5 (125)   | 31.25 (62.5)  | 15.625 (31.25)  | 7.8125 (32.986)  |

| 860       | 187.5 (520.8) | 125 (319.4) | 62.5 (152.7) | 31.25 (90.2)  | 15.625 (38.19)  | 8.6799 (45.138)  |

# Table 11. Effective Resolution from RMS Noise (Noise-Free Resolution from Peak-to-Peak Noise) at VDD = 3.3V

| DATA RATE |            |            | FSR (Full-Sc | ale Range) |            |              |

|-----------|------------|------------|--------------|------------|------------|--------------|

| (SPS)     | ±6.144V    | ±4.096V    | ±2.048V      | ±1.024V    | ±0.512V    | ±0.256V      |

| 8         | 16 (16)    | 16 (16)    | 16 (16)      | 16 (16)    | 16 (16)    | 16 (16)      |

| 16        | 16 (16)    | 16 (16)    | 16 (16)      | 16 (16)    | 16 (16)    | 16 (16)      |

| 32        | 16 (16)    | 16 (16)    | 16 (16)      | 16 (16)    | 16 (16)    | 16 (16)      |

| 64        | 16 (16)    | 16 (16)    | 16 (16)      | 16 (16)    | 16 (16)    | 16 (15.17)   |

| 128       | 16 (16)    | 16 (16)    | 16 (16)      | 16 (16)    | 16 (15.85) | 16 (15)      |

| 250       | 16 (15)    | 16 (15)    | 16 (15)      | 16 (15)    | 16 (15)    | 16 (14.41)   |

| 475       | 16 (15)    | 16 (15)    | 16 (15)      | 16 (15)    | 16 (15)    | 16 (13.92)   |

| 860       | 16 (14.52) | 16 (14.64) | 16 (14.7)    | 16 (14.47) | 16 (14.71) | 15.9 (13.47) |

## 7. DETAILED DESCRIPTION

## 7.1 OVERVIEW

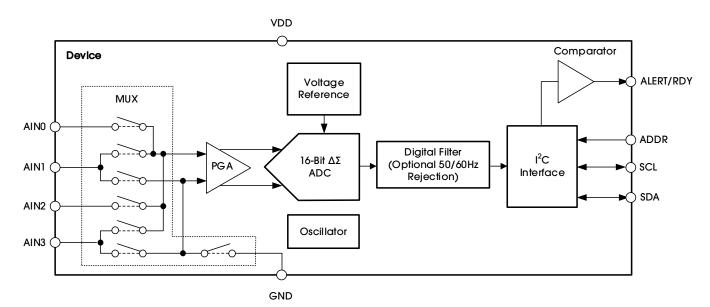

The ADX113 is very small, low-power, 16-bit, delta-sigma ( $\Delta\Sigma$ ) analog-to-digital converter (ADC). The ADX113 consists of a  $\Delta\Sigma$  ADC core with an internal voltage reference, a clock oscillator and an I<sup>2</sup>C interface. It also integrates a programmable gain amplifier (PGA) and a programmable digital comparator. Figure 19 shows the functional block diagram of ADX113.

The ADX113 ADC core measures a differential signal,  $V_{IN}$ , that is the difference of  $V_{(AINP)}$  and  $V_{(AINN)}$ . The converter core consists of a differential, switched-capacitor  $\Delta\Sigma$  modulator followed by a digital filter. This architecture results in a very strong attenuation of any common-mode signals. Input signals are compared to the internal voltage reference. The digital filter receives a high-speed bitstream from the modulator and outputs a code proportional to the input voltage.

The ADX113 has two available conversion modes: single-shot and continuous-conversion. In single-shot mode, the ADC performs one conversion of the input signal upon request, stores the conversion value to an internal conversion register, and then enters a power-down state. This mode is intended to provide significant power savings in systems that only require periodic conversions or when there are long idle periods between conversions. In continuous-conversion mode, the ADC automatically begins a conversion of the input signal as soon as the previous conversion is completed. The rate of continuous conversion is equal to the programmed data rate. Data can be read at any time and always reflect the most recent completed conversion.

## **7.2 FUNCTIONAL BLOCK DIAGRAM**

Figure 19. Functional Block Diagram

## 7.3 FEATURE DESCRIPTION

### 7.3.1 MULTIPLEXER

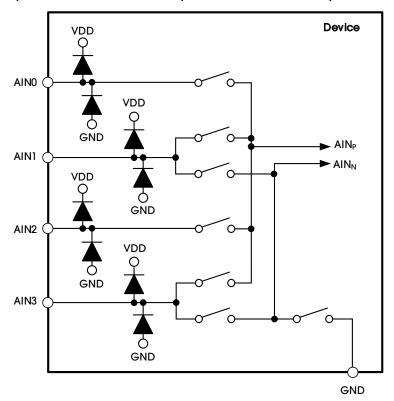

The ADX113 contains an input multiplexer (MUX), as shown in Figure 20. Either four single-ended or two differential signals can be measured. Additionally, AINO and AIN1 may be measured differentially to AIN3. The multiplexer is configured by bits MUX(2:0) in the CONFIG REGISTER. When single-ended signals are measured, the negative input of the ADC is internally connected to GND by a switch within the multiplexer.

#### Figure 20. Input Multiplexer

Electrostatic discharge (ESD) diodes connected to VDD and GND protect the ADX113 analog inputs. Keep the absolute voltage of any input within the range shown in Equation 3 to prevent the ESD diodes from turning on.

$$GND - 0.3V < V_{(AINx)} < VDD + 0.3V$$

(3)

If the voltages on the input pins can potentially violate these conditions, use external Schottky diodes and series resistors to limit the input current to safe values (see Table 4).

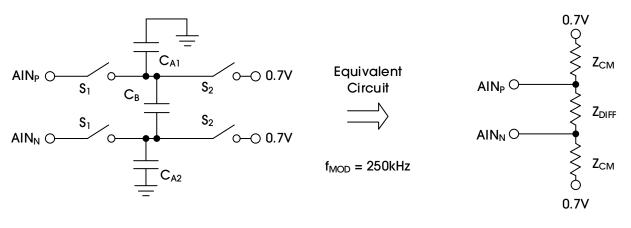

## 7.3.2 ANALOG INPUTS

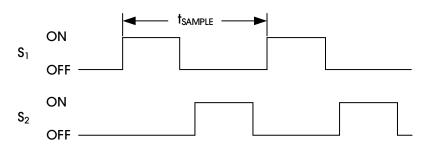

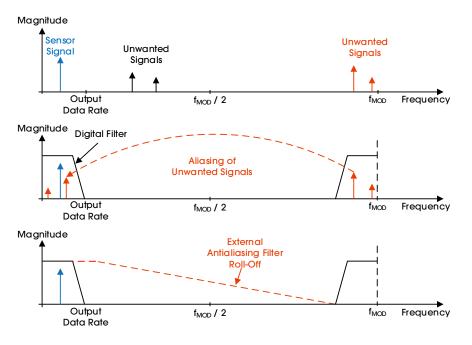

The ADX113 uses a switched-capacitor input stage where capacitors are continuously charged and then discharged to measure the voltage between AIN<sub>P</sub> and AIN<sub>N</sub>. The frequency at which the input signal is sampled is called the sampling frequency or the modulator frequency ( $f_{MOD}$ ). The ADX113 has a 1MHz internal oscillator that is further divided by a factor of 4 to generate  $f_{MOD}$  at 250kHz. The capacitors used in this input stage are small, and to external circuitry, the average loading appears resistive. Figure 21 shows this structure. The capacitor values set the resistance and switching rate. Figure 22 shows the timing for the switches in Figure 21. During the sampling phase, switches S<sub>1</sub> are closed. This event charges C<sub>A1</sub> to V<sub>(AINP)</sub>, C<sub>A2</sub> to V<sub>(AINN)</sub>, and C<sub>B</sub> to (V<sub>(AINP)</sub> – V<sub>(AINN)</sub>). During the discharge phase, S<sub>1</sub> is first opened and then S<sub>2</sub> is closed. Both C<sub>A1</sub> and C<sub>A2</sub> then discharge to approximately 0.7V and C<sub>B</sub> discharges to 0V. This charging draws a very small transient current from the source driving the ADX113 analog inputs. The average value of this current can be used to calculate the effective impedance (Z<sub>eff</sub>), where Z<sub>eff</sub> = V<sub>IN</sub> / I<sub>AVERAGE</sub>.

Figure 21. Simplified Analog Input Circuit

The common-mode input impedance is measured by applying a common-mode signal to the shorted AIN<sub>P</sub> and AIN<sub>N</sub> inputs and measuring the average current consumed by each pin. The common-mode input impedance changes depending on the full-scale range, but is approximately  $\delta M\Omega$  for the default full-scale range. In Figure 21, the common-mode input impedance is Z<sub>CM</sub>.

The differential input impedance is measured by applying a differential signal to  $AIN_P$  and  $AIN_N$  inputs where one input is held at 0.7V. The current that flows through the pin connected to 0.7V is the differential current and scales with the full-scale range. In Figure 21, the differential input impedance is  $Z_{DIFF}$ .

Make sure to consider the typical value of the input impedance. Unless the input source has a low impedance, the ADX113 input impedance may affect the measurement accuracy. For sources with high-output impedance, buffering may be necessary. Active buffers introduce noise, and also introduce offset and gain errors. Consider all of these factors in high-accuracy applications.

The clock oscillator frequency drifts slightly with temperature; therefore, the input impedances also drift. For most applications, this input impedance drift is negligible, and can be ignored.

### 7.3.3 FULL-SCALE RANGE (FSR) AND LSB SIZE

A programmable gain amplifier (PGA) is implemented before the  $\Delta\Sigma$  ADC of the ADX113. The full-scale range is configured by bits PGA(2:0) in the CONFIG REGISTER and can be set to ±6.144V, ±4.096V, ±2.048V, ±1.024V, ±0.512V, ±0.256V. Table 12 shows the FSR together with the corresponding LSB size. Equation 4 shows how to calculate the LSB size from the selected full-scale range.

#### $LSB = FSR / 2^{16}$

(4)

#### Table 12. Full-Scale Range and Corresponding LSB Size

| •                      |          |

|------------------------|----------|

| FSR                    | LSB SIZE |

| ±6.144V <sup>(1)</sup> | 187.5µV  |

| ±4.096V <sup>(1)</sup> | 125µV    |

| ±2.048V                | 62.5µV   |

| ±1.024V                | 31.25µV  |

| ±0.512V                | 15.625µV |

| ±0.256V                | 7.8125µV |

|                        |          |

Note: This parameter expresses the full-scale range of the ADC scaling. Do not apply more than VDD + 0.3V to the analog inputs of the device.

Analog input voltages must never exceed the analog input voltage limits given in the ABSOLUTE MAXIMUM RATINGS. If a VDD supply voltage is lower than the selected full-scale range, a full-scale ADC output code cannot be obtained. For example, with VDD = 3.3V and FSR =  $\pm 4.096$ V, only signals up to V<sub>IN</sub> =  $\pm 3.3$ V can be measured. The code range that represents voltages of  $|V_{IN}| > 3.3$ V is not used in this case.

It is highly recommended to use full-scale range one step higher than VDD supply voltage as the maximum full-scale range. For example, VDD = 2V, and  $\pm 2.048V$  are the best settings for a maximum full-scale range. Full-scale range larger than  $\pm 2.048V$  has no benefit.

#### 7.3.4 VOLTAGE REFERENCE

The ADX113 has an integrated voltage reference. An external reference cannot be used with the device. Errors associated with the initial voltage reference accuracy and the reference drift with temperature are included in the gain error and gain drift specifications in the ELECTRICAL CHARACTERISTICS.

#### 7.3.5 OSCILLATOR

The ADX113 has an integrated oscillator running at 1MHz. No external clock can be applied to operate the device. The internal oscillator drifts over temperature and time. The output data rate scales proportionally with the oscillator frequency.

### 7.3.6 OUTPUT DATA RATE AND CONVERSION TIME

The ADX113 offers programmable output data rates. Use the DR(2:0) bits in the CONFIG REGISTER to select output data rates of 8SPS, 16 (20) SPS, 32SPS, 64SPS, 128SPS, 250 (316) SPS, 475SPS, or 860SPS.

Furthermore, the ADX113 provides digital filter to reject 50Hz normal frequency and 60Hz normal frequency. Select one of the rejection filters or enable both 50Hz and 60Hz. If normal frequency rejection filter is enabled, the output data rate should be set to 20SPS, and any other output data rate is invalid.

Conversions in the ADX113 settle within a single cycle; thus, the conversion time is equal to 1 / DR.

## 7.3.7 DIGITAL COMPARATOR

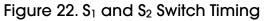

The ADX113 features a programmable digital comparator that can issue an alert on the ALERT/RDY pin. The COMP\_MODE bit in the CONFIG REGISTER configures the comparator as either a traditional comparator or a window comparator. In traditional comparator mode, the ALERT/RDY pin asserts (active low by default) when conversion data exceeds the limit set in the high-threshold register (Hi\_thresh). The comparator then deasserts only when the conversion data falls below the limit set in the low-threshold register (Lo\_thresh). In window comparator mode, the ALERT/RDY pin asserts when the conversion data exceed the Hi\_thresh register or fall below the Lo\_thresh register value.

In either window or traditional comparator mode, the comparator can be configured to latch after being asserted by the COMP\_LAT bit in the CONFIG REGISTER. This setting causes the assertion to remain even if the input signal is not beyond the bounds of the threshold registers. This latched assertion can only be cleared by issuing an SMBus alert response or by reading the CONVERSION REGISTER. The ALERT/RDY pin can be configured as active high or active low by the COMP\_POL bit in the CONFIG REGISTER. Operational diagrams for both the comparator modes are shown in Figure 23.

The comparator can also be configured to activate the ALERT/RDY pin only after a set number of successive readings exceed the threshold values set in the threshold registers (Hi\_thresh and Lo\_thresh). The COMP\_QUE(1:0) bits in the CONFIG REGISTER configure the comparator to wait for one, two, or four readings beyond the threshold before activating the ALERT/RDY pin. The COMP\_QUE(1:0) bits can also disable the comparator function, and put the ALERT/RDY pin into a high state.

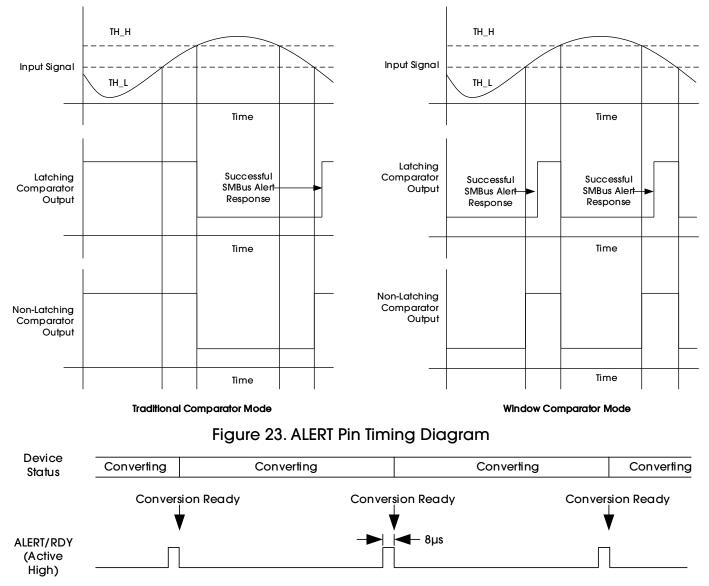

### 7.3.8 CONVERSION READY PIN

The ALERT/RDY pin can also be configured as a conversion ready pin. Set the most-significant bit of the Hi\_thresh register to 1 and the most-significant bit of Lo\_thresh register to 0 to enable the pin as a conversion ready pin. The COMP\_POL bit continues to function as expected. Set the COMP\_QUE(1:0) bits to any 2-bit value other than 11 to keep the ALERT/RDY pin enabled, and allow the conversion ready signal to appear at the ALERT/RDY pin output. The COMP\_MODE and COMP\_LAT bits no longer control any function. When configured as a conversion ready pin, ALERT/RDY continues to require a pullup resistor. The ADX113 provides an approximately 8µs conversion ready pulse on the ALERT/RDY pin at the end of each conversion in continuous-conversion mode, as shown in Figure 24. In single-shot mode, the ALERT/RDY pin asserts low at the end of a conversion if the COMP\_POL bit is set to 0.

Figure 24. Conversion Ready Pulse in Continuous-Conversion Mode

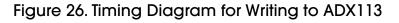

## 7.3.9 SMBUS ALERT RESPONSE

In latching comparator mode (COMP\_LAT = 1), the ALERT/RDY pin asserts when the comparator detects a conversion that exceeds the upper or lower threshold value. This assertion is latched and can be cleared only by reading conversion data, or by issuing a successful SMBus alert response and reading the asserting device I<sup>2</sup>C address. If conversion data exceed the upper or lower threshold values after being cleared, the pin reasserts. This assertion does not affect conversions that are already in progress. The ALERT/RDY pin is an open-drain output. This architecture allows several devices to share the same interface bus. When disabled, the pin holds a high state so that the pin does not interfere with other devices on the same bus line.

When the master senses that the ALERT/RDY pin has latched, the master issues an SMBus alert command (00011001) to the I<sup>2</sup>C bus. Any ADX113 data converters on the I<sup>2</sup>C bus with the ALERT/RDY pins asserted respond to the command with the slave address. If more than one ADX113 on the I<sup>2</sup>C bus assert the latched ALERT/RDY pin, arbitration during the address response portion of the SMBus alert determines which device clears assertion. The device with the lowest I<sup>2</sup>C address always wins arbitration. If a device loses arbitration, the device does not clear the comparator output pin assertion. The master then repeats the SMBus alert response until all devices have the respective assertions cleared. In window comparator mode, the SMBus alert status bit indicates a 1 if signals exceed the high threshold, and a 0 if signals exceed the low threshold.

## 7.4 DEVICE FUNCTIONAL MODES

## 7.4.1 RESET AND POWER-UP

The ADX113 resets on power-up and sets all the bits in the CONFIG REGISTER to the respective default settings. The ADX113 enters a power-down state after completion of the reset process. The device interface and digital blocks are active, but no data conversions are performed. The initial power-down state of the ADX113 relieves systems with tight power-supply requirements from encountering a surge during power-up.

The ADX113 responds to the I<sup>2</sup>C general-call reset commands. When the ADX113 receives a general call reset command (06h), an internal reset is performed as if the device is powered-up.

## 7.4.2 OPERATING MODES

The ADX113 operates in one of two modes: continuous-conversion or single-shot. The MODE bit in the CONFIG REGISTER selects the respective operating mode.

#### 7.4.2.1 SINGLE-SHOT MODE

When the MODE bit in the CONFIG REGISTER is set to 1, the ADX113 enters a power-down state, and operate in single-shot mode. This power-down state is the default state for the ADX113 when power is first applied. Although powered down, the devices still respond to commands. The ADX113 remains in this power-down state until a 1 is written to the operational status (OS) bit in the CONFIG REGISTER. When the OS bit is asserted, the device powers up in approximately 25µs, resets the OS bit to 0, and starts a single conversion. When conversion data are ready for retrieval, the device powers down again. Writing a 1 to the OS bit while a conversion is ongoing has no effect. To switch to continuous-conversion mode, write a 0 to the MODE bit in the CONFIG REGISTER.

#### 7.4.2.2 CONTINUOUS-CONVERSION MODE

In continuous-conversion mode (MODE bit set to 0), the ADX113 performs conversions continuously. When a conversion is complete, the ADX113 places the result in the CONVERSION REGISTER and immediately begin another conversion. When writing new configuration settings, the currently ongoing conversion completes with the previous configuration settings. Thereafter, continuous conversions with the new configuration settings start. To switch to single-shot conversion mode, write a 1 to the MODE bit in the CONFIG REGISTER or reset the device.

### 7.4.3 DUTY CYCLING FOR LOW POWER

The noise performance of a  $\Delta\Sigma$  ADC generally improves when lowering the output data rate because more samples of the internal modulator are averaged to yield one conversion result. In applications where power consumption is critical, the improved noise performance at low data rates may not be required. For these applications, the ADX113 supports duty cycling that yields significant power savings by periodically requesting high data rate readings at an effectively lower data rate. For example, an ADX113 in power-down state with a data rate set to 860SPS can be operated by a microcontroller that instructs a single-shot conversion every 125ms (8SPS). A conversion at 860SPS only requires approximately 1.2ms, so the ADX113 enters power-down state for the remaining 123.8ms. In this configuration, the ADX113 consumes approximately 1/100th the power that is otherwise consumed in continuous-conversion mode. The duty cycling rate is completely arbitrary and is defined by the master controller. The ADX113 offers lower data rates that do not implement duty cycling and also offer improved noise performance if required.

## 7.5 PROGRAMMING

### 7.5.1 I<sup>2</sup>C INTERFACE

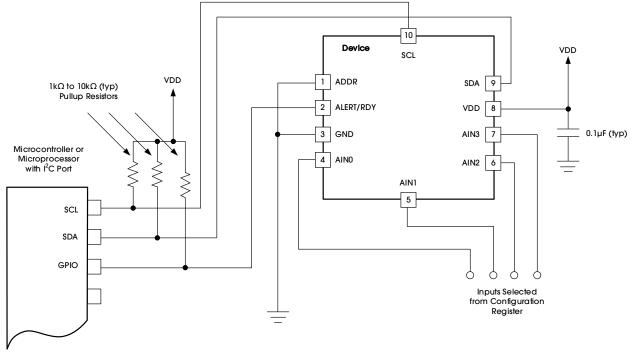

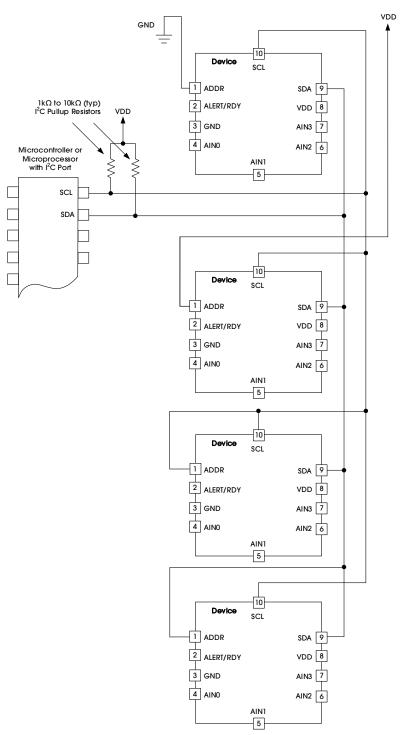

The ADX113 communicates through an I2C interface. I2C is a two-wire open-drain interface that supports multiple devices and masters on a single bus. Devices on the I2C bus only drive the bus lines low by connecting them to ground; the devices never drive the bus lines high. Instead, the bus wires are pulled high by pullup resistors, so the bus wires are always high when no device is driving them low. As a result of this configuration, two devices cannot conflict. If two devices drive the bus simultaneously, there is no driver contention.

Communication on the I2C bus always takes place between two devices, one acting as the master and the other as the slave. Both the master and slave can read and write, but the slave can only do so under the direction of the master. Some I2C devices can act as a master or slave, but the ADX113 can only act as a slave device.

An I2C bus consists of two lines: SDA and SCL. SDA carries data; SCL provides the clock. All data are transmitted across the I2C bus in groups of eight bits. To send a bit on the I2C bus, drive the SDA line to the appropriate level while SCL is low (a low on SDA indicates the bit is zero; a high indicates the bit is one). After the SDA line settles, the SCL line is brought high, then low. This pulse on SCL clocks the SDA bit into the receiver shift register. If the I2C bus is held idle for more than 25ms, the bus times out.

The I2C bus is bidirectional; that is, the SDA line is used for both transmitting and receiving data. When the master reads from a slave, the slave drives the data line; when the master sends to a slave, the master drives the data line. The master always drives the clock line. The ADX113 cannot act as a master, and therefore can never drive SCL.

Most of the time the bus is idle; no communication occurs, and both lines are high. When communication takes place, the bus is active. Only a master device can start a communication and initiate a START condition on the bus. Normally, the data line is only allowed to change state while the clock line is low. If the data line changes state while the clock line is high, it is either a START condition or a STOP condition. A START condition occurs when the clock line is high, and the data line goes from high to low. A STOP condition occurs when the clock line is high, and the data line goes from low to high.

After the master issues a START condition, the master sends a byte that indicates with which slave device to communicate. This byte is called the address byte. Each device on an I<sup>2</sup>C bus has a unique 7-bit address to which it responds. The master sends an address in the address byte, together with a bit that indicates whether the master wishes to read from or write to the slave device.

Every byte (address and data) transmitted on the l<sup>2</sup>C bus is acknowledged with an acknowledge bit. When the master finishes sending a byte (eight data bits) to a slave, the master stops driving SDA and waits for the slave to acknowledge the byte. The slave acknowledges the byte by pulling SDA low. The master then sends a clock pulse to clock the acknowledge bit. Similarly, when the master completes reading a byte, the master pulls SDA low to acknowledge this completion to the slave. The master then sends a clock pulse to clock the details completion to the slave. The master then sends a clock pulse to clock the bit. The master always drives the clock line.

If a device is not present on the bus, and the master attempts to address it, it receives a not-acknowledge because no device is present at that address to pull the line low. A not-acknowledge is performed by simply leaving SDA high during an acknowledge cycle.

When the master has finished communicating with a slave, it may issue a STOP condition. When a STOP condition is issued, the bus becomes idle again. The master may also issue another START condition. When a START condition is issued while the bus is active, it is called a repeated start condition.

The TIMING REQUIREMENTS section shows a timing diagram for the ADX113 I<sup>2</sup>C communication.

#### 7.5.1.1 I<sup>2</sup>C ADDRESS SELECTION

The ADX113 has one address pin, ADDR, that configures the I<sup>2</sup>C address of the device. This pin can be connected to GND, VDD, SDA, or SCL, allowing for four different addresses to be selected with one pin, as shown in Table 13. The state of address pin ADDR is sampled continuously. Use the GND, VDD, and SCL addresses first. If SDA is used as the device address, hold the SDA line low for at least 100ns after the SCL line goes low to make sure the device decodes the address correctly during I<sup>2</sup>C communication.

| ADDR PIN CONNECTION | SLAVE ADDRESS |

|---------------------|---------------|

| GND                 | 1001000       |

| VDD                 | 1001001       |

| SDA                 | 1001010       |

| SCL                 | 1001011       |

Table 13. ADDR Pin Connection and Corresponding Slave Address

#### 7.5.1.2 I<sup>2</sup>C GENERAL CALL

The ADX113 responds to the I<sup>2</sup>C general call address (0000000) if the eighth bit is 0. The devices acknowledge the general call address and respond to commands in the second byte. If the second byte is 00000110 (06h), the ADX113 resets the internal registers and enter a power-down state.

#### 7.5.1.3 I<sup>2</sup>C SPEED MODES

The I<sup>2</sup>C bus operates at one of three speeds. Standard mode allows a clock frequency of up to 100kHz; fast mode permits a clock frequency of up to 400kHz; and high-speed mode (also called Hs mode) allows a clock frequency of up to 3.4MHz. The ADX113 is fully compatible with all three modes.

No special action is required to use the ADX113 in standard or fast mode, but high-speed mode must be activated. To activate high-speed mode, send a special address byte of 00001xxx following the START condition, where xxx are bits unique to the Hs-capable master. This byte is called the Hs master code, and is different from normal address bytes; the eighth bit does not indicate read/write status. The ADX113 does not acknowledge this byte; the I<sup>2</sup>C specification prohibits acknowledgment of the Hs master code. Upon receiving a master code, the ADX113 switches on Hs mode filters, and communicate at up to 3.4MHz. The ADX113 switches out of Hs mode with the next STOP condition.

For more information on high-speed mode, consult the  $I^2C$  specification.

#### 7.5.2 SLAVE MODE OPERATIONS

The ADX113 acts as slave receivers or slave transmitters. The ADX113 cannot drive the SCL line as slave devices.

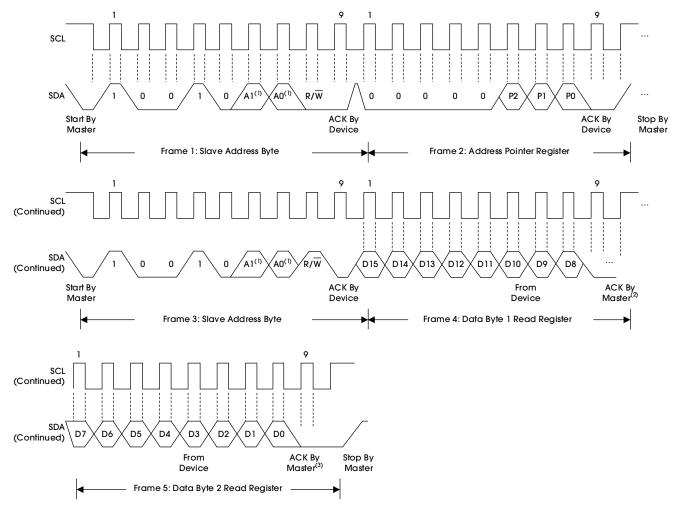

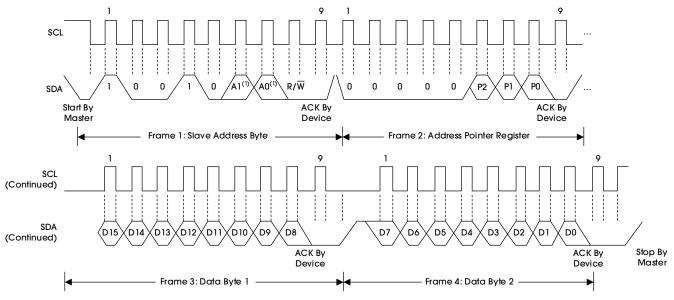

#### 7.5.2.1 RECEIVE MODE

In slave receive mode, the first byte transmitted from the master to the slave consists of the 7-bit device address followed by a low R/W bit. The next byte transmitted by the master is the ADDRESS POINTER REGISTER. The ADX113 then acknowledge receipt of the Address Pointer register byte. The next two bytes are written to the address given by the register address pointer bits, P(2:0). The ADX113 acknowledges each byte sent. Register bytes are sent with the most significant byte first, followed by the least significant byte.

#### 7.5.2.2 TRANSMIT MODE

In slave transmit mode, the first byte transmitted by the master is the 7-bit slave address followed by the high  $R/\overline{W}$  bit. This byte places the slave into transmit mode and indicates that the ADX113 is being read from. The next byte transmitted by the slave is the most significant byte of the register that is indicated by the register address pointer bits, P(2:0). This byte is followed by an acknowledgment from the master. The remaining least significant byte is then sent by the slave and is followed by an acknowledgment from the master. The master may terminate transmission after any byte by not acknowledging or issuing a START or STOP condition.

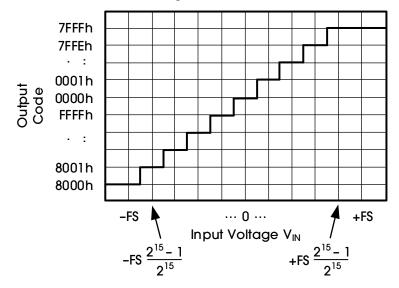

### 7.5.3 WRITING TO AND READING FROM THE REGISTERS

To access a specific register from the ADX113, the master must first write an appropriate value to register address pointer bits P(2:0) in the ADDRESS POINTER REGISTER. The Address Pointer register is written to directly after the slave address byte, low R/W bit, and a successful slave acknowledgment. After the Address Pointer register is written, the slave acknowledges, and the master issues a STOP or a repeated START condition.

When reading from the ADX113, the previous value written to bits P(2:0) determines the register that is read. To change which register is read, a new value must be written to P(2:0). To write a new value to P(2:0), the master issues a slave address byte with the  $R/\overline{W}$  bit low, followed by the Address Pointer register byte. No additional data has to be transmitted, and a STOP condition can be issued by the master. The master can now issue a START condition and send the slave address byte with the  $R/\overline{W}$  bit high to begin the read. Figure 25 details this sequence. If repeated reads from the same register are desired, there is no need to continually send the Address Pointer register, because the ADX113 stores the value of P(2:0) until it is modified by a write operation. However, for every write operation, the Address Pointer register must be written with the appropriate values.

(1) The values of A0 and A1 are determined by the ADDR pin.

(2) Master can leave SDA high to terminate a single-byte read operation.

(3) Master can leave SDA high to terminate a two-byte read operation.

#### Figure 25. Timing Diagram for Reading from ADX113

(1) The values of A0 and A1 are determined by the ADDR pin.

(1) The values of A0 and A1 are determined by the ADDR pin.

#### Figure 27. Timing Diagram for SMBus Alert Response

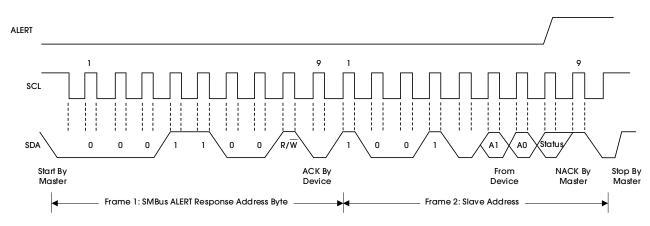

## 7.5.4 DATA FORMAT

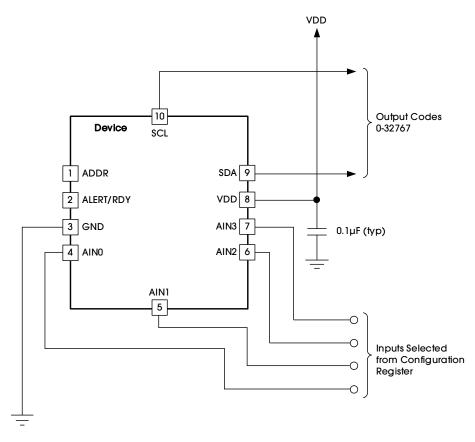

The ADX113 provides 16 bits of data in binary two's complement format. A positive full-scale (+FS) input produces an output code of 7FFFh and a negative full-scale (-FS) input produces an output code of 8000h. The output clips at these codes for signals that exceed full-scale. Table 14 summarizes the ideal output codes for different input signals.

#### Table 14. Input Signal versus Ideal Output Code

| INPUT SIGNAL                                  | IDEAL OUTPUT CODE                                             |

|-----------------------------------------------|---------------------------------------------------------------|

| $V_{IN} = (V_{AINP} - V_{AINN})$              | (EXCLUDES THE EFFECTS OF NOISE, INL, OFFSET, AND GAIN ERRORS) |

| ≥ +FS (2 <sup>15</sup> - 1) / 2 <sup>15</sup> | 7FFFh                                                         |

| +FS / 2 <sup>15</sup>                         | 0001h                                                         |

| 0                                             | 0000h                                                         |

| -FS / 2 <sup>15</sup>                         | FFFFh                                                         |

| ≤ -FS                                         | 8000h                                                         |

Figure 28 shows code transitions versus input voltage.

#### Figure 28. Code Transition Diagram

Note: Single-ended signal measurements, where  $V_{AINN} = 0V$  and  $V_{AINP} = 0V$  to +FS, only use the positive code range from 0000h to 7FFFh. However, because of device offset, the ADX113 can still output negative codes in case  $V_{AINP}$  is close to 0V.

## 8. REGISTER MAPS

The ADX113 has 6 registers that are accessible through the I<sup>2</sup>C interface using the ADDRESS POINTERREGISTER. The CONVERSION REGISTER contains the result of the last conversion. The CONFIG REGISTER and CONFIG\_EXTRA are used to change the ADX113 operating modes and query the status of the device. Device ID shows the ID. The other two registers, Lo\_thresh and Hi\_thresh, set the threshold values used for the comparator function.

#### Table 15. Register Map

| ADDRESS        | REGISTER    | DEFAULT   | READ/WRIT   | BIT15  | BIT14  | BIT13 | BIT12         | BIT11        | BIT10        | BIT9          | BIT8          |

|----------------|-------------|-----------|-------------|--------|--------|-------|---------------|--------------|--------------|---------------|---------------|

| ADDRE33        | REGISTER    | VALUE     | E           | BIT7   | BIT6   | BIT5  | BIT4          | BIT3         | BIT2         | BIT1          | BITO          |

| 0x00           | CONVERSION  | 0000h     | Read only   | D15    | D14    | D13   | D12           | D11          | D10          | D9            | D8            |

| 0,00           | CONVERSION  | 000011    | Redu Only   | D7     | D6     | D5    | D4            | D3           | D2           | Dl            | D0            |

|                |             |           |             | OS     | MUX2   | MUX1  | MUX0          | PGA2         | PGA1         | PGA0          | MODE          |

| 0x01           | CONFIG      | 8583h     | Read/Write  | CR2    | CR1    | CR0   | COMP_<br>MODE | COMP_<br>POL | COMP_<br>LAT | COMP_<br>QUE1 | COMP_<br>QUE0 |

| 0x02           | CMP_TL      | 00001-    | Doad /Write | TL15   | TL14   | TL13  | TL12          | TL11         | TL10         | TL9           | TL8           |

| UXUZ           |             | 8000h     | Read/Write  | TL7    | TL6    | TL5   | TL4           | TL3          | TL2          | TL1           | TLO           |

| 0x03           | CMP_TH      | 7FFFh     | Read/Write  | TH15   | TH14   | TH13  | TH12          | TH11         | TH10         | TH9           | TH8           |

| 0,005          |             | 76661     | Kedu/ Wille | TH7    | TH6    | TH5   | TH4           | TH3          | TH2          | TH1           | THO           |

| 0x06           | CONFIG_EXTR | 0800h     | Doad /Write | FILT50 | FILT60 | RSV   | RSV           | RSV          | RSV          | RSV           | RSV           |

| 0,00           | A           | 0800N     | Read/Write  | RSV    | RSV    | RSV   | RSV           | RSV          | RSV          | RSV           | RSV           |

| 0,07           |             | 2000h     | Doad only   | ID7    | ID6    | ID5   | ID4           | ID3          | ID2          | ID1           | ID0           |

| 0x07 DEVICE_ID | 3000h       | Read only | RSV         | RSV    | RSV    | RSV   | RSV           | RSV          | RSV          | RSV           |               |

## 8.1.1 ADDRESS POINTER REGISTER (ADDRESS = N/A) [RESET = N/A]

All four registers are accessed by writing to the Address Pointer register; see Figure 25.

| Tabla | 16  | Addross | Dointor | Dogistor |  |

|-------|-----|---------|---------|----------|--|

| laple | 10. | Address | Pointer | Reaister |  |

| 7           | 6                                                               | 5    | 4    | 3    | 2    | 1      | 0    |  |  |  |  |

|-------------|-----------------------------------------------------------------|------|------|------|------|--------|------|--|--|--|--|

| 0           | 0                                                               | 0    | 0    | 0    |      | P(2:0) |      |  |  |  |  |

| W-0h        | W-0h                                                            | W-0h | W-0h | W-0h | W-0h | W-0h   | W-0h |  |  |  |  |

| LEGEND: R/W | LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |      |      |      |      |        |      |  |  |  |  |

#### Table 17. Address Pointer Field Descriptions

| BIT | FIELD    | TYPE | RESET | DESCRIPTION                                                                                                                                                                                   |

|-----|----------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Reserved | W    | 0h    | Always write 0h                                                                                                                                                                               |

| 1:0 | P(2:0)   | w    | 0h    | Register address pointer<br>000: Conversion register<br>001: Config register<br>010: Lo_thresh register<br>011: Hi_thresh register<br>101: CONFIG_EXTRA<br>110: DEVICE_ID<br>Others: Reserved |

## 8.1.2 CONVERSION REGISTER (P[2:0] = OH) [RESET = 0000H]

The 16-bit Conversion register contains the result of the last conversion in binary two's complement format. Following power-up, the Conversion register is cleared to 0, and remains 0 until the first conversion is completed.

#### Table 18 Conversion Register

| 15                                                             | 14   | 13   | 12   | 11   | 10   | 9    | 8    |  |  |

|----------------------------------------------------------------|------|------|------|------|------|------|------|--|--|

| D15                                                            | D14  | D13  | D12  | D11  | D10  | D9   | D8   |  |  |

| R-0h                                                           | R-0h | R-0h | R-0h | R-0h | R-0h | R-0h | R-0h |  |  |

| 7                                                              | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

| D7                                                             | D6   | D5   | D4   | D3   | D2   | D1   | D0   |  |  |

| R-0h                                                           | R-0h | R-0h | R-0h | R-0h | R-0h | R-0h | R-0h |  |  |

| FGFND: R/W = Read/Write: R = Read only: -n = value after reset |      |      |      |      |      |      |      |  |  |

EGEND: R/W = Redd/Write; R = Redd only; -n = value after reset

#### Table 19. Conversion Register Field Descriptions

| BIT  | FIELD   | TYPE | RESET | DESCRIPTION              |

|------|---------|------|-------|--------------------------|

| 15:0 | D(15:0) | R    | 0000h | 16-bit conversion result |

## 8.1.3 CONFIG REGISTER (P[2:0] = 1H) [RESET = 8583H]

The 16-bit Config register is used to control the operating mode, input selection, data rate, full-scale range, and comparator modes.

#### Table 20. Config Register

| 15        | 14              | 13             | 12               | 11       | 10       | 9      | 8        |

|-----------|-----------------|----------------|------------------|----------|----------|--------|----------|

| OS        |                 | MUX(2:0)       |                  |          |          | MODE   |          |

| R/W-1h    |                 | R/W-0h         |                  |          |          | R/W-1h |          |

| 7         | 6               | 5              | 4                | 3        | 2        | 1      | 0        |

|           | DR(2:0)         |                | COMP_MODE        | COMP_POL | COMP_LAT | COMP_0 | ຊUE(1:0) |

|           | R/W-4h          |                | R/W-0h           | R/W-0h   | R/W-0h   | R/W    | V-3h     |

| GEND: R/W | = Read/Write; F | R = Read only; | -n = value after | reset    |          |        |          |

#### Table 21. Config Register Field Descriptions

| BIT   | FIELD    | TYPE | RESET | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|----------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | OS       | R/W  | lh    | Operational status or single-shot conversion start<br>This bit determines the operational status of the device. OS can only<br>be written when in power-down state and has no effect when a<br>conversion is ongoing.<br>When writing:<br>0: No effect<br>1: Start a single conversion (when in power-down state)<br>When reading:<br>0: Device is currently performing a conversion.<br>1: Device is not currently performing a conversion.                                                                 |

| 14:12 | MUX(2:0) | R/W  | 0h    | Input multiplexer configuration<br>These bits configure the input multiplexer.<br>000: $AIN_P = AIN0$ and $AIN_N = AIN1$ (default)<br>001: $AIN_P = AIN0$ and $AIN_N = AIN3$<br>010: $AIN_P = AIN1$ and $AIN_N = AIN3$<br>011: $AIN_P = AIN2$ and $AIN_N = AIN3$<br>100: $AIN_P = AIN0$ and $AIN_N = GND$<br>101: $AIN_P = AIN1$ and $AIN_N = GND$<br>110: $AIN_P = AIN2$ and $AIN_N = GND$<br>111: $AIN_P = AIN3$ and $AIN_N = GND$                                                                         |

| 11:9  | PGA(2:0) | R/W  | 2h    | Programmable gain amplifier configuration<br>These bits set the FSR of the programmable gain amplifier.<br>000: FSR = $\pm 6.144V^{(1)}$<br>001: FSR = $\pm 4.096V^{(1)}$<br>010: FSR = $\pm 2.048V$ (default)<br>011: FSR = $\pm 1.024V$<br>100: FSR = $\pm 0.512V$<br>101: FSR = $\pm 0.256V$<br>110: FSR = $\pm 0.256V$<br>111: FSR = $\pm 0.256V$<br>Note: This parameter expresses the full-scale range of the ADC<br>scaling. Do not apply more than VDD + 0.3V to the analog inputs of<br>the device. |

| 8     | MODE     | R/W  | lh    | Device operating mode<br>This bit controls the operating mode.<br>0: Continuous-conversion mode<br>1: Single-shot mode or power-down state (default)                                                                                                                                                                                                                                                                                                                                                         |

| BIT | FIELD         | TYPE | RESET | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|---------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | DR(2:0)       | R/W  | 4h    | Data rate<br>These bits control the data rate setting.<br>000: 8SPS<br>001: 16SPS (20SPS when 50/60 filter is enabled)<br>010: 32SPS<br>011: 64SPS<br>100: 128SPS (default)<br>101 : 250SPS (316SPS when 50/60 filter is enabled)<br>110: 475SPS<br>111 : 860SPS                                                                                                                                                                                                                                                                                                                                                             |

| 4   | COMP_MODE     | R/W  | 0h    | Comparator mode<br>This bit configures the comparator operating mode.<br>0: Traditional comparator (default)<br>1: Window comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3   | COMP_POL      | R/W  | 0h    | Comparator polarity<br>This bit controls the polarity of the ALERT/RDY pin.<br>0: Active low (default)<br>1: Active high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2   | COMP_LAT      | R/W  | 0h    | Latching comparator<br>This bit controls whether the ALERT/RDY pin latches after being<br>asserted or clears after conversions are within the margin of the<br>upper and lower threshold values.<br>0: Nonlatching comparator. The ALERT/RDY pin does not latch when<br>asserted (default).<br>1: Latching comparator. The asserted ALERT/RDY pin remains<br>latched until conversion data are read by the master or an<br>appropriate SMBus alert response is sent by the master. The device<br>responds with its address, and it is the lowest address currently<br>asserting the ALERT/RDY bus line.                      |

| 1:0 | COMP_QUE(1:0) | R/W  | 3h    | Comparator queue and disable<br>These bits perform two functions. When set to 11, the comparator is<br>disabled and the ALERT/RDY pin is set to a high-impedance state.<br>When set to any other value, the ALERT/RDY pin and the<br>comparator function are enabled, and the set value determines<br>the number of successive conversions exceeding the upper or<br>lower threshold required before asserting the ALERT/RDY pin.<br>00: Assert after one conversion<br>01: Assert after two conversions<br>10: Assert after four conversions<br>11: Disable comparator and set ALERT/RDY pin to high-impedance<br>(default) |

## 8.1.4 LO\_THRESH (P[2:0] = 2H) [RESET = 8000H] AND HI\_THRESH (P[2:0] = 3H) [RESET = 7FFFH] REGISTERS

The upper and lower threshold values used by the comparator are stored in two 16-bit registers in two's complement format. The comparator is implemented as a digital comparator; therefore, the values in these registers must be updated whenever the PGA settings are changed.

The conversion-ready function of the ALERT/RDY pin is enabled by setting the Hi thresh register MSB to 1 and the Lo\_thresh register MSB to 0. To use the comparator function of the ALERT/RDY pin, the Hi\_thresh register value must always be greater than the Lo\_thresh register value. The threshold register formats are shown in Table 22. When set to RDY mode, the ALERT/RDY pin outputs the OS bit when in single-shot mode, and provides a continuous-conversion ready pulse when in continuous-conversion mode.

| 15          | 14                                                             | 13          | 12          | 11          | 10          | 9          | 8          |  |

|-------------|----------------------------------------------------------------|-------------|-------------|-------------|-------------|------------|------------|--|

| Lo_thresh15 | Lo_thresh14                                                    | Lo_thresh13 | Lo_thresh12 | Lo_thresh11 | Lo_thresh10 | Lo_thresh9 | Lo_thresh8 |  |

| R/W-1h      | R/W-0h                                                         | R/W-0h      | R/W-0h      | R/W-0h      | R/W-0h      | R/W-0h     | R/W-0h     |  |

| 7           | 6                                                              | 5           | 4           | 3           | 2           | 1          | 0          |  |

| Lo_thresh7  | Lo_thresh6                                                     | Lo_thresh5  | Lo_thresh4  | Lo_thresh3  | Lo_thresh2  | Lo_thresh1 | Lo_thresh0 |  |

| R/W-0h      | R/W-0h                                                         | R/W-0h      | R/W-0h      | R/W-0h      | R/W-0h      | R/W-0h     | R/W-0h     |  |