## High-Side Power Distribution Controller

#### **Features**

- **High-Side Driver for an External N-Channel MOSFET**

- **Under-Voltage Lockout (UVLO)**

- **Wrong VIN Input Voltage Protection**

- **Output Under-Voltage Protection (UVP)**

- **Short-Circuit Protection During Power-Up (SCP)**

- **Over-Current Protection (OCP)**

- **Shutdown Function**

- Power-Ok (POK) Function

- **Lead Free and Green Devices Available** (RoHS Compliant)

## **Applications**

**Desktop PCs**

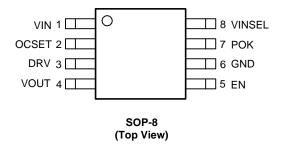

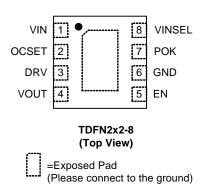

# **Pin Configuration**

## **General Description**

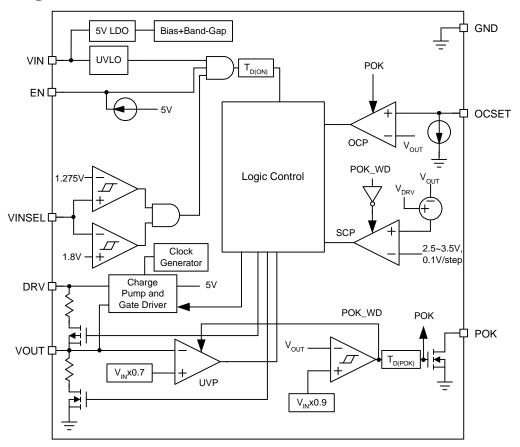

APL3540 is a high-side power distribution controller for an external N-channel MOSFET, allow for +12V and +19V power-supply rails. The wrong input voltage protection function protects a wrong input adapter insertion. When input voltage is out of the target input voltage range, the IC is off.

The built-in under-voltage protection monitors the output voltage for short-circuit conditions. When output voltage is less than 70% of VIN voltage, the IC will be shut down. The over-current protection monitors the output current by using the voltage drop across the external MOSFET's  $R_{\text{DS(ON)}}$ . When output current reaches the trip point, the IC will be shut down. The APL3540 also provides a shortcircuit protection during power-up. The device monitors DRV and VOUT voltages for a short-circuit detection. If a short-circuit condition is detected, the IC will be shut down. Other features, including a POK output which indicates that the output voltage is ready and a logic-controlled shutdown mode.

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise customers to obtain the latest version of relevant information to verify before placing orders.

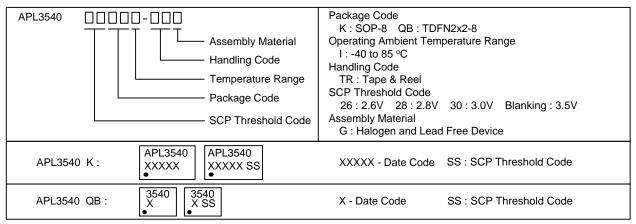

## **Ordering and Marking Information**

Note: ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which are fully compliant with RoHS. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J-STD-020D for MSL classification at lead-free peak reflow temperature. ANPEC defines "Green" to mean lead-free (RoHS compliant) and halogen free (Br or Cl does not exceed 900ppm by weight in homogeneous material and total of Br and Cl does not exceed 1500ppm by weight).

## **Absolute Maximum Ratings** (Note 1)

| Symbol                                                                                                  | Parameter                                       | Rating     | Unit |

|---------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------|------|

| V <sub>IN</sub>                                                                                         | VIN Input Voltage (VIN to GND)                  | -0.3 to 35 | V    |

| V <sub>OUT</sub> , V <sub>DRV</sub> ,<br>V <sub>OCSET</sub> , V <sub>POK</sub> ,<br>V <sub>VINSEL</sub> | VOUT, DRV, POK, OCSET and VINSEL to GND Voltage | -0.3 to 40 | V    |

| $V_{EN}$                                                                                                | EN to GND Voltage                               | -0.3 to 7  | V    |

| TJ                                                                                                      | Maximum Junction Temperature                    | 150        | °C   |

| T <sub>STG</sub>                                                                                        | Storage Temperature                             | -65 to 150 | °C   |

| $T_{SDR}$                                                                                               | Maximum Lead Soldering Temperature,10 Seconds   | 260        | °C   |

Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## Thermal Characteristics (Note 2)

| Symbol        | Parameter                                                  | Typical Value | Unit |

|---------------|------------------------------------------------------------|---------------|------|

| $\theta_{JA}$ | Junction-to-Ambient Resistance in Free Air SOP-8 TDFN2x2-8 | 150<br>80     | °C/W |

Note 2:  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air.

# **Recommended Operating Conditions (Note 3)**

| Symbol          | Parameter                      | Range      | Unit |

|-----------------|--------------------------------|------------|------|

| V <sub>IN</sub> | VIN Input Voltage (VIN to GND) | 10 to 26   | V    |

| V <sub>EN</sub> | EN to GND Voltage              | 0 to 5     | V    |

| T <sub>A</sub>  | Ambient Temperature            | -40 to 85  | °C   |

| TJ              | Junction Temperature           | -40 to 125 | °C   |

Note 3: Refer to the typical application circuit

## **Electrical Characteristics**

Unless otherwise specified, these specifications apply over  $V_{IN}$ =19V,  $V_{EN}$  =5V and  $T_A$ = -40 to 85 °C. Typical values are at  $T_A$ =25°C.

|                        | Domester.                                                                                                                         | T O                                                                                          |       |       |       |     |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------|-------|-------|-----|

| Symbol                 | Parameter                                                                                                                         | Test Conditions                                                                              | Min.  | Тур.  | Max.  | Uni |

| UNDER-VO               | DLTAGE LOCKOUT (UVLO) AND SUP                                                                                                     | PLY CURRENT                                                                                  |       |       |       |     |

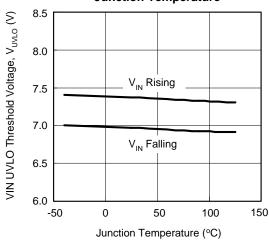

| $V_{\text{UVLO}}$      | VIN UVLO Threshold Voltage                                                                                                        | $V_{IN}$ rising, $T_A$ = -40 to 85 $^{\circ}$ C                                              | 7.0   | 7.5   | 8.0   | V   |

|                        | VIN UVLO Hysteresis                                                                                                               |                                                                                              | 0.3   | 0.4   | 0.5   | V   |

| $T_{D(ON)}$            | Power-On Delay Time  V <sub>IN</sub> >V <sub>UVLO</sub> , V <sub>EN</sub> =5V, and V <sub>VINSEL(H)</sub> >V <sub>VINSEL(L)</sub> |                                                                                              | 5     | 8.5   | 12    | ms  |

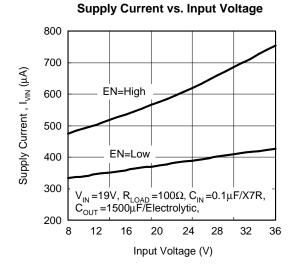

| I <sub>VIN</sub>       | VIN Supply Current                                                                                                                | No load, V <sub>EN</sub> =5V                                                                 | ı     | 750   | 1200  | μΑ  |

| IVIN                   | VIIV Supply Guirent                                                                                                               | No load, $V_{EN} = 0V$                                                                       | -     | 400   | 600   | μΑ  |

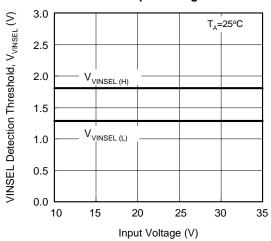

| WRONG V                | IN INPUT VOLTAGE PROTECTION                                                                                                       |                                                                                              |       |       |       |     |

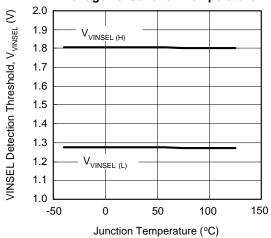

| $V_{\text{VINSEL(L)}}$ | VINSEL Low Detection Rising<br>Threshold                                                                                          | $V_{\text{IN}}$ rising, IC is on, $V_{\text{IN}}$ =10V to 21V                                | 1.223 | 1.275 | 1.305 | ٧   |

|                        | VINSEL Low Detection Falling<br>Threshold                                                                                         | $V_{\text{IN}}$ falling, IC is off, $V_{\text{IN}}$ =10V to 21V                              | 1.148 | 1.200 | 1.230 | V   |

| $V_{\text{VINSEL(H)}}$ | VINSEL High Detection Rising<br>Threshold                                                                                         | $V_{\rm IN}$ rising, IC is off, $V_{\rm IN}$ =10V to 21V                                     | 1.748 | 1.800 | 1.830 | V   |

|                        | VINSEL High Detection Falling<br>Threshold                                                                                        | V <sub>IN</sub> falling, IC is on, V <sub>IN</sub> =10V to 21V                               | 1.673 | 1.725 | 1.755 | V   |

|                        | VINSEL Input Current                                                                                                              | V <sub>VINSEL</sub> =40V                                                                     | -     | -     | 1     | μΑ  |

|                        | VINSEL Low Detection Debounce                                                                                                     | $V_{\text{VINSEL}}$ falling, $V_{\text{VINSEL}} < V_{\text{VINSEL(L)}}$                      | -     | 10    | -     | μs  |

|                        | VINSEL High Detection Debounce                                                                                                    | $V_{VINSEL}$ rising, $V_{VINSEL} > V_{VINSEL(H)}$                                            | -     | 10    | -     | μs  |

| GATE DRIV              | ER .                                                                                                                              |                                                                                              |       |       |       |     |

| $V_{DRV\text{-}OUT}$   | DRV to VOUT Voltage                                                                                                               | $V_{DRV}$ - $V_{OUT}$ , $V_{IN}$ =19                                                         | 4.3   | 4.6   | 4.9   | V   |

|                        | DRV Source Current                                                                                                                | $V_{DRV}$ =10V, $V_{DRV}$ - $V_{OUT}$ =2.5                                                   | 155   | 185   | 215   | μΑ  |

|                        | DRV Discharge Resistance                                                                                                          | Any fault condition and shutdown (connected from DRV to VOUT), $V_{DRV}$ =5V, $V_{OUT}$ =GND | 1.8   | 2.0   | 2.2   | kΩ  |

| PROTECTION             | ONS                                                                                                                               |                                                                                              |       |       |       |     |

|                        | Under-Voltage Protection Threshold                                                                                                | $V_{\text{OUT}}$ falling, $V_{\text{OUT}}/V_{\text{IN}}$                                     | 65    | 70    | 75    | %   |

|                        | Under-Voltage Protection Debounce                                                                                                 |                                                                                              | -     | 5     | -     | μs  |

| I <sub>OCSET</sub>     | OCSET Source Current                                                                                                              | No load, $V_{VINSEL}$ =1.5V, $V_{EN}$ =5V, $V_{OCSET}$ =18.9V                                | 45    | 50    | 55    | μΑ  |

|                        | OCSET Offset Voltage                                                                                                              |                                                                                              | -10   | 0     | 10    | m∖  |

|                        | Over-Current Debounce                                                                                                             |                                                                                              | -     | 10    | -     | μs  |

# **Electrical Characteristics (Cont.)**

Unless otherwise specified, these specifications apply over  $V_{IN}$ =19V,  $V_{EN}$  =5V and  $T_A$ = -40 to 85 °C. Typical values are at  $T_A$ =25°C.

| Cumbal               | Parameter                                   | Test Conditions                                                                     | APL3540 |      |      | l linit |

|----------------------|---------------------------------------------|-------------------------------------------------------------------------------------|---------|------|------|---------|

| Symbol               | Parameter Test Conditions —                 |                                                                                     | Min.    | Тур. | Max. | Unit    |

| PROTECTION           | ONS (CONT.)                                 |                                                                                     |         |      |      |         |

| $V_{DRV(SC)}$        | Short Circuit Protection Threshold Accuracy | V <sub>DRV</sub> -V <sub>OUT</sub> SCP threshold tunable range: 2.5~3.5V, 0.1V/step | -100    | -    | +100 | mV      |

|                      | VOUT Input Current                          | V <sub>OUT</sub> =19V                                                               | -       | 60   | 80   | μА      |

|                      | VOUT Discharge Resistance                   | Any fault condition and shutdown, V <sub>OUT</sub> =1V                              | 1.5     | 1.75 | 2.0  | kΩ      |

| EN INPUT             |                                             |                                                                                     |         | •    | •    |         |

|                      | EN Logic High Threshold Voltage             | V <sub>IN</sub> =10V to 21V                                                         | 0.8     | -    | 1.5  | V       |

|                      | EN Hyteresis                                |                                                                                     | -       | 0.2  | -    | V       |

|                      | EN Pull-up Current                          |                                                                                     | -       | 5    | -    | μΑ      |

| POK OUTP             | UT                                          |                                                                                     |         | •    | •    |         |

| V <sub>POK(TH)</sub> | POK Threshold                               | V <sub>OUT</sub> rising, V <sub>OUT</sub> /V <sub>IN</sub> , V <sub>POK</sub> =High | 85      | 90   | 95   | %       |

|                      | POK Hysteresis                              | V <sub>OUT</sub> falling, V <sub>POK</sub> =Low                                     | -       | 5    | -    | %       |

|                      | POK Low Voltage                             | I <sub>POK</sub> =10mA                                                              | -       | 0.2  | 0.5  | V       |

|                      | POK Leakage Current                         | V <sub>POK</sub> =40V                                                               | -       | -    | 1    | μА      |

| T <sub>D(POK)</sub>  | POK Rising Delay Time                       | V <sub>OUT</sub> rising, POK assertion                                              | 8       | 11.5 | 15   | ms      |

## **Typical Operating Characteristics**

VINSEL Detection Threshold Voltage vs. Input Voltage

VIN UVLO Threshold Voltage vs. Junction Temperature

VINSEL Detection Threshold Voltage vs. Junction Temperature

## **Operating Waveforms**

The test condition is  $V_{IN}$ =19V,  $T_A$ =25°C unless otherwise specified.

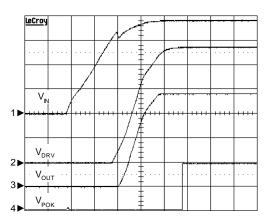

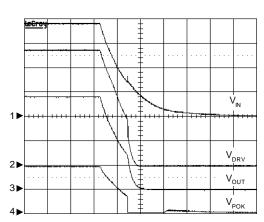

#### **Power On**

$\begin{aligned} &V_{\text{IN}}\!=\!19V, \ R_{\text{LOAD}}\!=\!100\Omega, \ R3\!=\!\!51k\Omega, \\ &C_{\text{IN}}\!=\!0.1\mu\text{F/X7R}, \ C_{\text{OUT}}\!=\!1500\mu\text{F/Electrolytic}, \\ &CH1: \ V_{\text{IN}}, \ 5V/\text{Div}, \ DC \end{aligned}$

CH2: V<sub>DRV</sub>, 5V/Div, DC CH3: V<sub>OUT</sub>, 5V/Div, DC CH4: V<sub>POK</sub>, 10V/Div, DC TIME: 10ms/Div

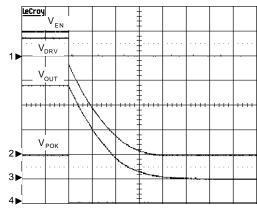

#### **Power Off**

$\begin{aligned} &V_{\text{IN}}\!=\!19\text{V}, \ &R_{\text{LOAD}}\!=\!100\Omega, \ &R3\!=\!51\text{k}\Omega, \\ &C_{\text{IN}}\!=\!0.1\mu\text{F/X7R}, \ &C_{\text{OUT}}\!=\!1500\mu\text{F/Electrolytic}, \\ &C\text{H1: } &V_{\text{IN}}\!, 5\text{V/Div}, \ DC \end{aligned}$

CH2: V<sub>DRV</sub>, 5V/Div, DC CH3:  $V_{OUT}$ , 5V/Div, DC CH4: V<sub>POK</sub>, 10V/Div, DC

TIME: 0.5s/Div

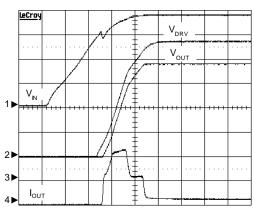

#### **Enable**

$$\begin{split} &V_{\text{IN}}\!=\!19V,\,R_{\text{LOAD}}\!=\!100\Omega,\,R3\!=\!\!51k\Omega,\\ &C_{\text{IN}}\!=\!0.1\mu\text{F}/\text{X7R},\,C_{\text{OUT}}\!=\!1500\mu\text{F}/\text{Electrolytic},\\ &C\text{H1:}\,\,V_{\text{EN}},\,5V/\text{Div},\,DC \end{split}$$

CH2: V<sub>DRV</sub>, 5V/Div, DC CH3:  $V_{OUT}$ , 5V/Div, DC

CH4: V<sub>POK</sub>, 10V/Div, DC TIME: 5ms/Div

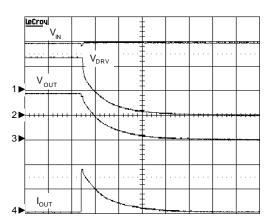

#### **Disable**

$$\begin{split} &V_{\text{IN}}\!=\!19V,\,R_{\text{LOAD}}\!=\!100\Omega,\,R3\!=\!\!51k\Omega,\\ &C_{\text{IN}}\!=\!0.1\mu\text{F/X7R},\,C_{\text{OUT}}\!=\!1500\mu\text{F/Electrolytic},\\ &C\text{H1:}\,V_{\text{EN}},\,5\text{V/Div},\,D\text{C} \end{split}$$

CH2: V<sub>DRV</sub>, 5V/Div, DC CH3:  $V_{OUT}$ , 5V/Div, DC CH4:  $V_{POK}$ , 10V/Div, DC

TIME: 50ms/Div

## **Operating Waveforms (Cont.)**

The test condition is  $V_{IN}$ =19V,  $T_A$ =25°C unless otherwise specified.

#### Soft-Start

$\begin{aligned} &V_{IN}\!=\!19V,\,R_{LOAD}\!=\!100\Omega,\,C1\!=\!100nF,\\ &C_{IN}\!=\!0.1\mu\text{F}/\text{XTR},\,C_{OUT}\!=\!1500\mu\text{F}/\text{Electrolytic}, \end{aligned}$

CH1: V<sub>IN</sub>, 5V/Div, DC CH2: V<sub>DRV</sub>, 5V/Div, DC CH3: V<sub>OUT</sub>, 5V/Div, DC CH4: I<sub>OUT</sub>, 1A/Div, DC TIME: 10ms/Div

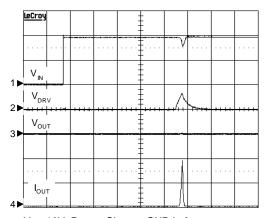

#### **Over-Current Protection**

$$\begin{split} &V_{\text{IN}}\!=\!19V,\,R_{\text{LOAD}}\!=\!1\Omega,\,R_{\text{OCSET}}\!=\!1.5k\Omega,\\ &C_{\text{IN}}\!=\!0.1\mu\text{F/X7R},\,C_{\text{OUT}}\!=\!470\mu\text{F/Electrolytic},\\ &C\text{H1:}\,\,V_{\text{IN}},\,10V/\text{Div},\,\text{DC} \end{split}$$

CH2: V<sub>DRV</sub>, 10V/Div, DC CH3: V<sub>OUT</sub>, 10V/Div, DC CH4: I<sub>OUT</sub>, 10A/Div, DC TIME: 0.5ms/Div

#### **Short-Circuit Protection**

$V_{IN}$ =19V,  $R_{LOAD}$ =Short to GND before power-up,  $C_{\text{IN}}^{\text{IN}}$  =0.1 $\mu$ F/X7R,  $C_{\text{OUT}}$  =470 $\mu$ F/Electrolytic CH1:  $V_{\text{IN}}$ , 10V/Div, DC

CH2: V<sub>DRV</sub>, 5V/Div, DC CH3: V<sub>OUT</sub>, 5V/Div, DC CH4: I<sub>OUT</sub>, 10A/Div, DC TIME: 2ms/Div

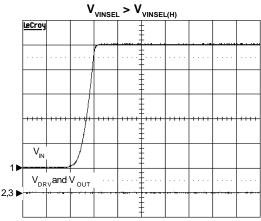

#### Wrong VIN Input Voltage Protection,

$V_{IN} = 25V$ , R1=24k $\Omega$ , R2=2k $\Omega$

CH1: V<sub>IN</sub>, 5V/Div, DC CH2: V<sub>DRV</sub>, 5V/Div, DC CH3: V<sub>OUT</sub>, 5V/Div, DC TIME: 50ms/Div

# **Operating Waveforms (Cont.)**

The test condition is  $\rm V_{IN}\!\!=\!\!19V,\,T_{A}\!\!=\!\!25^{o}C$  unless otherwise specified.

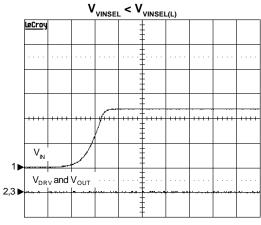

#### Wrong VIN Input Voltage Protection,

$V_{IN}$ =12V, R1=24k $\Omega$ , R2=2k $\Omega$

CH1:  $V_{IN}$ , 5V/Div, DC CH2:  $V_{DRV}$ , 5V/Div, DC CH3:  $V_{OUT}$ , 5V/Div, DC TIME: 20ms/Div

# **Pin Description**

| Р   | IN     | FUNCTION                                                                                                                                                                                                                            |  |  |  |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NO. | NAME   | FUNCTION                                                                                                                                                                                                                            |  |  |  |

| 1   | VIN    | Input Supply Pin. Provides power to the IC, $V_{IN}$ can range from 10V to 21V and should be bypassed with at least a $0.1\mu F$ capacitor.                                                                                         |  |  |  |

| 2   | OCSET  | Over-Current Trip Point Adjustment Pin. Connect a resistor (R <sub>OCSET</sub> ) from this pin to the drain of the external MOSFET to set the OCP trip point.                                                                       |  |  |  |

| 3   | DRV    | Gate Driver Output. The gate driver for the external N-channel MOSFET.                                                                                                                                                              |  |  |  |

| 4   | VOUT   | Output Voltage Sense Pin. Connect this pin to the source of external N-channel MOSFET to monitor the output voltage.                                                                                                                |  |  |  |

| 5   | EN     | Enable Input. Pulling the $V_{EN}$ above 2V will enable the IC; pulling $V_{EN}$ below 0.6V will disable the IC. This pin is pulled high by an internal current source.                                                             |  |  |  |

| 6   | GND    | Ground.                                                                                                                                                                                                                             |  |  |  |

| 7   | POK    | Power-Okay Indicator Output. The POK is an open-drain pull-down device. When VOUT voltage is below the POK threshold, the POK output is pulled low; when VOUT voltage is above the POK threshold, the POK output is high impedance. |  |  |  |

| 8   | VINSEL | Input Voltage Sense Pin. Connect a resistive divider from VIN to VINSEL to GND to monitor the input voltage. This pin cannot be left floating.                                                                                      |  |  |  |

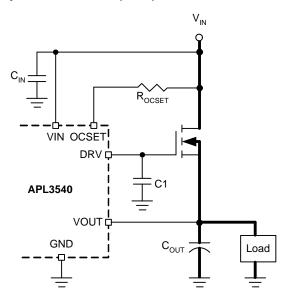

## **Block Diagram**

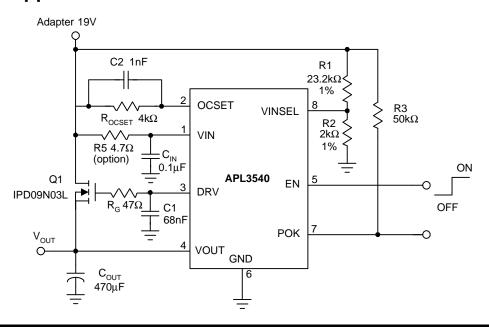

# **Typical Application Circuit**

## **Function Description**

#### **Wrong VIN Input Voltage Protection**

The APL3540 provides an input voltage detection function to protect a wrong input adapter insertion. Connect a resistive divider from VIN to VINSEL to GND to set the target input voltage. The target input voltage is set at:

$$V_{IN(target)} = 1.5V x (1+R1/R2)$$

The IC is enabled when input voltage is within the  $V_{IN(target)}$  ±15% ( $V_{IN}$  also must above  $V_{UVLO}$  and EN is high); the device shuts down when input voltage is outside the  $V_{IN}$  (target) ±20%.

#### Power-Up

The APL3540 has a built-in under-voltage lockout circuitry to keep the DRV output shutting off until internal circuitry operates properly. The UVLO circuit has a hysteresis and a de-glitch feature so that it will typically ignore undershoot transients on the input. When input voltage exceeds the UVLO threshold ( $V_{IN}$  also must within the  $V_{IN(target)}\pm10\%$  and EN is high) and after 7ms delay time, the DRV output starts to charge the C1.

The voltage at DRV rises with a slope equals to  $185\mu\text{A/C}$  and the VOUT output voltage rise time is set at:

$$T_{ss} = C1 \times V_{IN} / 185 \mu A$$

where

T<sub>ss</sub> is the rise time of VOUT output voltage

#### **Under-Voltage Protection (UVP)**

The VOUT pin monitors the output voltage. If the  $V_{\text{OUT}}$  is under 70% of VIN input voltage because of the short circuit or other influences, it will cause the under-voltage protection and turn off IC, the VOUT voltage is also discharged to the GND by an internal resistor, requiring a VIN UVLO or EN re-enable again to restart IC. Note that the UVP is active after the power-up and POK are asserted.

#### **Over-Current Protection (OCP)**

The APL3540 monitors the voltage across the external MOSFET and uses the OCSET pin to set the over-current trip point.

A resistor (R<sub>OCSET</sub>) connected between OCSET pin and the drain of the MOSFET will determine the over current trip point. An internal 50µA current source will flow through this resistor, creating a voltage drop, which will be compared with the voltage across the MOSFET.

When the voltage across the MOSFET exceeds the voltage drop across the  $\rm R_{\rm \tiny OCSET}$ , an over-current will be detected.

The threshold of the over current is therefore given by:

$$I_{OCP} = I_{OCSET} \times R_{OCSET} / R_{DS(ON)}$$

For the over-current is never occurred in the normal operating load range, the variation of all parameters in the above equation should be determined.

- The MOSFET's  $R_{\rm DS(ON)}$  is varied by temperature, the user should determine the maximum  $R_{\rm DS(ON)}$  in manufacturer's datasheet.

- The minimum  $I_{\text{OCSET}}$  (45 $\mu A)$  and minimum  $R_{\text{OCSET}}$  should be used in the above equation.

An over-current condition will shut down the device and pull the V<sub>DRV-OUT</sub> to low, the VOUT voltage is also discharged to the GND by an internal resistor, requiring a VIN UVLO or EN re-enable again to restart IC. Note that the OCP is active after the power-up and POK are asserted.

#### **POK Output**

The power okay function monitors the output voltage and drives the POK low to indicate a fault. When a fault condition such as over-current or under-voltage is occurred, the VOUT output voltage falls to 85% of VIN input voltage and the POK is pulled low. When the VOUT output voltage reaches to 90% of VIN input voltage and after 10ms delay time, the POK is pulled high. Since the POK is an open-drain device, connecting a resistor to a pull high voltage is necessary.

#### **Short-Circuit Protection**

The APL3540 monitors DRV and VOUT voltages for the short circuit detection during power-up. When the difference in voltage between DRV pin and VOUT pin is above short circuit protection threshold, a short-circuit condition is detected and the device will be shut down. Requiring a VIN UVLO or EN re-enable again to restart IC.

Caution must be taken when selecting a power MOSFET. If an unsuitable MOSFET is used, the SCP will be falsely activated during power-up. A complete power-up partly relies on the current driving capacity of the MOSFET. In the startup of  $V_{DRV}$  while gate voltage starts to rise, the MOSFET starts to conduct. If the current via the MOSFET is insufficient to supply for the needs of  $C_{OUT}$  and  $R_{LOAD}$ ,

## **Function Description (Cont.)**

#### **Short-Circuit Protection (Cont.)**

the  $V_{\text{OUT}}$  voltage will not follow the  $V_{\text{DRV}}$  to rise, eventually, when  $V_{\text{DRV}}$  -  $V_{\text{OUT}}$  > short circuit protection threshold, the SCP happens. Since the  $C_{\text{OUT}}$  demands the most current during power-up, the supplying current via the MOSFET should satisfy the following equation for a completion of power-up.

I<sub>SUPPLY(max)</sub> > I<sub>CHARGING</sub>

#### where:

$I_{CHARGING} = C_{OUT} x (185 \mu A/C1)$

- I<sub>SUPPLY(max)</sub> is the maximum supply current via the MOSFET in the conditions of  $V_{\rm GS}$  = short circuit protection threshold and  $V_{\rm DS} = V_{\rm IN}$ - $V_{\rm OUT}$ .

- $I_{\text{CHARGING}}$  is the charging current of  $C_{\text{OUT}}$  during soft-start.

- C<sub>OUT</sub> is output capacitor.

- C1, placed on the gate of MOSFET is the capacitor that controls the ramp-up rate of output voltage during softstart.

- 185μA is the soft-start current driving from the DRV pin during the power-up process.

For example, If  $C_{\text{OUT}}=1500\mu\text{F}$ , C1=100nF, short circuit protection threshold=3.0V and  $V_{\text{IN}}=19\text{V}$ , the  $I_{\text{CHARGING}}$  demanded by the output capacitor is 2.78A. The  $I_{\text{SUPPLY(max)}}$  in the conditions of  $V_{\text{GS}}=3.0\text{V}$  and  $V_{\text{DS}}=19\text{V}$  (while  $V_{\text{IN}}$ - $V_{\text{OUT}}$   $V_{\text{IN}}$ ) should be greater than the  $I_{\text{CHARGING}}$ . We set the safety margin that is 1.5 times greater than the demanded 2.78A, therefore, we can choose a MOSFET that can deliver at least 4.17A in such conditions.

#### **Shutdown Control**

The APL3540 has an active-low shutdown function. Pulling the  $V_{\text{EN}}$  above 2V will enable the IC; pulling  $V_{\text{EN}}$  below 0.6V will disable the IC and the POK is pulled low immediately (ignore the  $V_{\text{POK}(\text{TH})}$  and  $T_{\text{D(POK)}}$ ), the VOUT voltage is also discharged to the GND by an internal resistor. EN pin is pulled high by an internal current source and can be left floating.

## **Application Information**

#### **Input Capacitor**

While hot plug-in an AC adapter, the inductive peak voltage seen in the VIN pin could be very high if there is no any filtering measure taken. It is recommended to place a 0.1 to  $1\mu F$  ceramic bypass capacitor as close as possible to the VIN pin. An RC-filter, depicted in the application circuit, is preferable because better performance in filtering the peak voltage and noise. Note that the voltage rating of the input capacitor must be greater than the maximum  $V_{\text{IN}}$  voltage.

#### **Gate and Output Capacitor**

It is recommended to place a capacitor in the gate of external power MOSFET to control the soft-start rate of output voltage, especially when a high-value output capacitor is used. The gate capacitor can reduce the inrush current to the output capacitor during soft-start. If the power supply cannot support the inrush current, the  $C_{\text{OUT}}$  voltage will be clamped during soft-start and SCP will be falsely activated. The inrush current must be controlled within power supply current capability by using this gate capacitor. Note that the voltage rating of the gate capacitor must be greater than the maximum  $V_{\text{DRV}}$  voltage, where the  $V_{\text{DRV}}$  approximately equals  $V_{\text{IN}}$ +5V.

A bulk output capacitor, placed close to the load, is recommended to support load transient current. Precautions should be taken when a high-value output capacitor is used the gate capacitor C1 (shown in the application circuit) must be matched. A high-value output capacitor with a small-value C1 would probably lead to inrush current and end up SCP latched-off in the soft-start period. Please make sure that the gate capacitor C1 is matched with a high-value output capacitor. Note that the voltage rating of the output capacitor must be greater than the maximum V<sub>IN</sub> voltage.

#### **Gate Resistor**

It is recommended to place a resistor  $R_{\rm g}$ , as shown in the Typical Application Circuit, in the gate of external power MOSFET to prevent occurrence of oscillation during powering on. If the oscillation occurs, the SCP or VINSEL wrong voltage detection might be activated unexpectedly. The  $R_{\rm g}$  literally could stabilize the external MOSFET to

avoid oscillation. The R  $_{\text{G}}$  can be in the range of 10~100  $\!\Omega$  . The recommended value is 47  $\!\Omega$  .

#### **Power MOSFETs**

APL3540 requires an N-channel MOSFET that is utilized as an on/off switch. When a MOSEFT is selected, please make sure that the  ${\rm R}_{\rm \scriptscriptstyle DS(ON)}$  of this MOSFET can meet your maximum voltage droop requirement in full load conditions. And also make sure that the MOSFET you select can satisfy the current delivering requirement, described in the paragraph of Short-Circuit Protection in Function Description. Another important criterion for selection of MOSFET is the MOSFET must be operated within its safe operation area in your application. The package type of the MOSFET must be chosen for efficient heat removal. Note that the  $V_{\rm DS}$  rating of the MOSFET you selected must be greater than the  $\rm V_{IN}$  voltage and the  $\rm V_{GS}$ rating must be greater than  $V_{IN}$ +5V. The power dissipated in the MOSFET while on is shown in the following equation:

$$P_{D} = I_{O}^{2} x R_{DS(on)}$$

Select a package type and heatsink that maintains the junction temperature below the rating.

#### **Layout Consideration**

Figure 1 illustrates the layout, with bold lines indicating high current paths; and these traces must be short and wide. The layout guidelines are listed as below.

- Place the input capacitors C<sub>IN</sub> for VIN near pin as close as possible.

- 2. The trace from DRV to the gate of power MOSFETs should be wide and short.

- 3. Place output capacitor  $\mathbf{C}_{\text{OUT}}$  near the load as close as possible.

- Large current paths must have wide and thick traces, depicted as the bold lines.

- 5. The drain of the power MOSFETs should be a large plane for heatsinking.

# **Application Information (Cont.)**

### **Layout Consideration (Cont.)**

Figure 1. Layout Guidelines

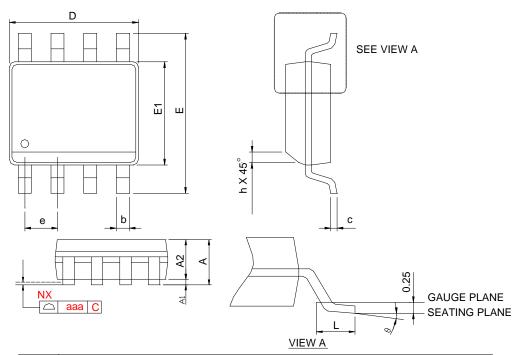

## **Package Information**

#### SOP-8

| S                          |             | so   | P-8   |       |

|----------------------------|-------------|------|-------|-------|

| S<br>Y<br>M<br>B<br>O<br>L | MILLIMETERS |      | INC   | HES   |

| P                          | MIN.        | MAX. | MIN.  | MAX.  |

| Α                          |             | 1.75 |       | 0.069 |

| A1                         | 0.10        | 0.25 | 0.004 | 0.010 |

| A2                         | 1.25        |      | 0.049 |       |

| b                          | 0.31        | 0.51 | 0.012 | 0.020 |

| С                          | 0.17        | 0.25 | 0.007 | 0.010 |

| D                          | 4.80        | 5.00 | 0.189 | 0.197 |

| Е                          | 5.80        | 6.20 | 0.228 | 0.244 |

| E1                         | 3.80        | 4.00 | 0.150 | 0.157 |

| е                          | 1.27        | BSC  | 0.05  | 0 BSC |

| h                          | 0.25        | 0.50 | 0.010 | 0.020 |

| L                          | 0.40        | 1.27 | 0.016 | 0.050 |

| θ                          | 0°          | 8°   | 0°    | 8°    |

| aaa                        | 0.          | 10   | 0.0   | 004   |

Note: 1. Follow JEDEC MS-012 AA.

- 2. Dimension "D" does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion or gate burrs shall not exceed 6 mil per side.

- Mold flash, protrusion or gate burrs shall not exceed 6 mil per side.

3. Dimension "E" does not include inter-lead flash or protrusions.

Inter-lead flash and protrusions shall not exceed 10 mil per side.

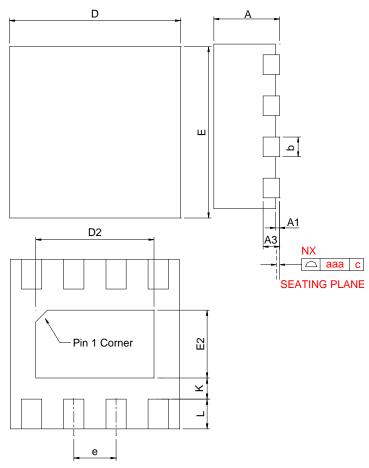

# Package Information

### TDFN2x2-8

| ş      | TDFN2x2-8 |             |       |       |  |  |

|--------|-----------|-------------|-------|-------|--|--|

| SYMBOL | MILLIM    | MILLIMETERS |       | HES   |  |  |

| 2      | MIN.      | MAX.        | MIN.  | MAX.  |  |  |

| Α      | 0.70      | 0.80        | 0.028 | 0.031 |  |  |

| A1     | 0.00      | 0.05        | 0.000 | 0.002 |  |  |

| АЗ     | 0.20      | REF         | 0.008 | REF   |  |  |

| b      | 0.18      | 0.30        | 0.007 | 0.012 |  |  |

| D      | 1.90      | 2.10        | 0.075 | 0.083 |  |  |

| D2     | 1.00      | 1.60        | 0.039 | 0.063 |  |  |

| Е      | 1.90      | 2.10        | 0.075 | 0.083 |  |  |

| E2     | 0.60      | 1.00        | 0.024 | 0.039 |  |  |

| е      | 0.50      | BSC         | 0.020 | ) BSC |  |  |

| L      | 0.30      | 0.45        | 0.012 | 0.018 |  |  |

| K      | 0.20      |             | 0.008 |       |  |  |

| aaa    | 0.0       | 08          | 0.0   | 03    |  |  |

Note: 1. Followed from JEDEC MO-229 WCCD-3.

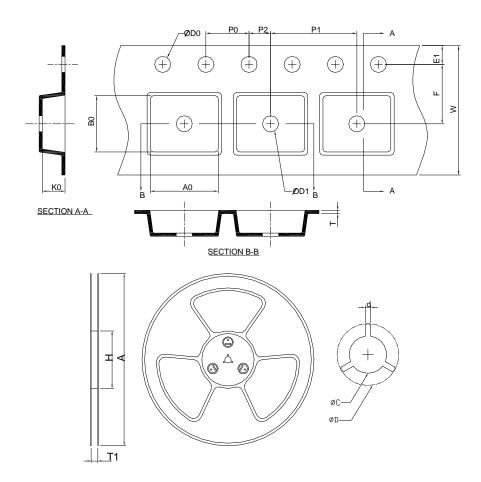

# **Carrier Tape & Reel Dimensions**

| Application | Α                      | Н                 | T1                 | С                  | d        | D                 | W                  | E1                 | F                  |

|-------------|------------------------|-------------------|--------------------|--------------------|----------|-------------------|--------------------|--------------------|--------------------|

|             | 330.0 ₤.00             | 50 MIN.           | 12.4+2.00<br>-0.00 | 13.0+0.50<br>-0.20 | 1.5 MIN. | 20.2 MIN.         | 12.0 <b>±</b> 0.30 | 1.75 ±0.10         | 5.5 ±0.05          |

| SOP-8       | P0                     | P1                | P2                 | D0                 | D1       | T                 | A0                 | В0                 | K0                 |

|             | 4.0 ±0.10              | 8.0 <b>±</b> 0.10 | 2.0 ±0.05          | 1.5+0.10<br>-0.00  | 1.5 MIN. | 0.6+0.00<br>-0.40 | 6.40 <b>±</b> 0.20 | 5.20 <b>±</b> 0.20 | 2.10 <b>±</b> 0.20 |

| Application | Α                      | Н                 | T1                 | С                  | d        | D                 | W                  | E1                 | F                  |

|             | 178.0 <del>£</del> .00 | 50 MIN.           | 8.4+2.00<br>-0.00  | 13.0+0.50<br>-0.20 | 1.5 MIN. | 20.2 MIN.         | 8.0 <b>±</b> 0.20  | 1.75 ±0.10         | 3.50 ±0.05         |

| TDFN2x2-8   | P0                     | P1                | P2                 | D0                 | D1       | T                 | A0                 | В0                 | K0                 |

|             | 4.0 ±0.10              | 4.0 <b>±</b> 0.10 | 2.0 ±0.05          | 1.5+0.10<br>-0.00  | 1.5 MIN. | 0.6+0.00<br>-0.4  | 3.35 MIN           | 3.35 MIN           | 1.30 <b>±</b> 0.20 |

(mm)

## **Devices Per Unit**

| Package Type | Unit        | Quantity |

|--------------|-------------|----------|

| SOP-8        | Tape & Reel | 2500     |

| TDFN2x2-8    | Tape & Reel | 3000     |

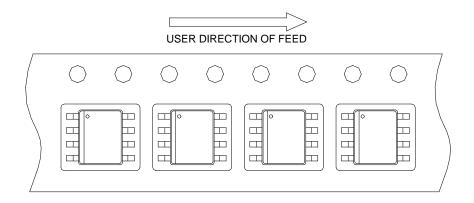

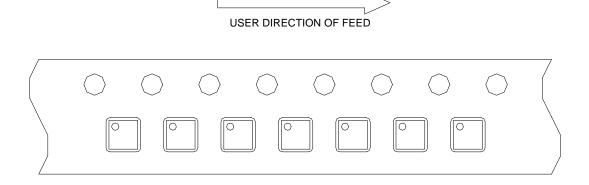

# **Taping Direction Information**

SOP-8

#### TDFN2x2-8

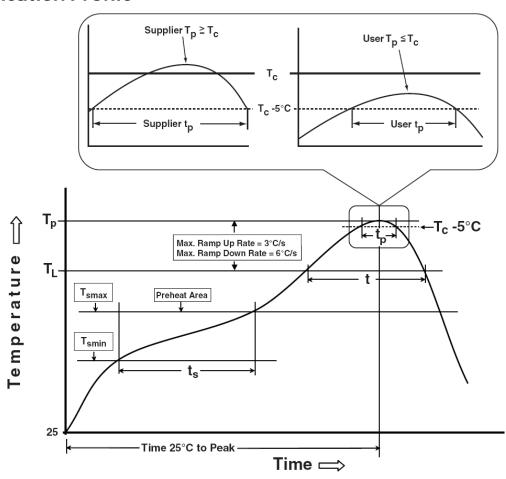

### **Classification Profile**

## **Classification Reflow Profiles**

| Profile Feature                                                                                                                                           | Sn-Pb Eutectic Assembly            | Pb-Free Assembly                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------|

| Preheat & Soak Temperature min (T <sub>smin</sub> ) Temperature max (T <sub>smax</sub> ) Time (T <sub>smin</sub> to T <sub>smax</sub> ) (t <sub>s</sub> ) | 100 °C<br>150 °C<br>60-120 seconds | 150 °C<br>200 °C<br>60-120 seconds |

| Average ramp-up rate (T <sub>smax</sub> to T <sub>P</sub> )                                                                                               | 3 °C/second max.                   | 3°C/second max.                    |

| Liquidous temperature (T <sub>L</sub> )<br>Time at liquidous (t <sub>L</sub> )                                                                            | 183 °C<br>60-150 seconds           | 217 °C<br>60-150 seconds           |

| Peak package body Temperature (T <sub>p</sub> )*                                                                                                          | See Classification Temp in table 1 | See Classification Temp in table 2 |

| Time (t <sub>P</sub> )** within 5°C of the specified classification temperature (T <sub>c</sub> )                                                         | 20** seconds                       | 30** seconds                       |

| Average ramp-down rate (T <sub>p</sub> to T <sub>smax</sub> )                                                                                             | 6 °C/second max.                   | 6 °C/second max.                   |

| Time 25°C to peak temperature                                                                                                                             | 6 minutes max.                     | 8 minutes max.                     |

<sup>\*</sup> Tolerance for peak profile Temperature (Tp) is defined as a supplier minimum and a user maximum.

<sup>\*\*</sup> Tolerance for time at peak profile temperature (tp) is defined as a supplier minimum and a user maximum.

# **Classification Reflow Profiles (Cont.)**

Table 1. SnPb Eutectic Process – Classification Temperatures (Tc)

| Package<br>Thickness | Volume mm <sup>3</sup> <350 | Volume mm <sup>3</sup><br><sup>3</sup> 350 |

|----------------------|-----------------------------|--------------------------------------------|

| <2.5 mm              | 235 °C                      | 220 °C                                     |

| ≥2.5 mm              | 220 °C                      | 220 °C                                     |

Table 2. Pb-free Process – Classification Temperatures (Tc)

| Package<br>Thickness | Volume mm <sup>3</sup><br><350 | Volume mm <sup>3</sup><br>350-2000 | Volume mm <sup>3</sup> >2000 |

|----------------------|--------------------------------|------------------------------------|------------------------------|

| <1.6 mm              | 260 °C                         | 260 °C                             | 260 °C                       |

| 1.6 mm – 2.5 mm      | 260 °C                         | 250 °C                             | 245 °C                       |

| ≥2.5 mm              | 250 °C                         | 245 °C                             | 245 °C                       |

## **Reliability Test Program**

| Test item     | Method             | Description                            |

|---------------|--------------------|----------------------------------------|

| SOLDERABILITY | JESD-22, B102      | 5 Sec, 245°C                           |

| HOLT          | JESD-22, A108      | 1000 Hrs, Bias @ T <sub>j</sub> =125°C |

| PCT           | JESD-22, A102      | 168 Hrs, 100%RH, 2atm, 121°C           |

| TCT           | JESD-22, A104      | 500 Cycles, -65°C~150°C                |

| НВМ           | MIL-STD-883-3015.7 | VHBM 2KV                               |

| MM            | JESD-22, A115      | VMM 200V                               |

| Latch-Up      | JESD 78            | 10ms, 1 <sub>tr</sub> 100mA            |

### **Customer Service**

#### **Anpec Electronics Corp.**

Head Office:

No.6, Dusing 1st Road, SBIP, Hsin-Chu, Taiwan, R.O.C. Tel: 886-3-5642000

Fax: 886-3-5642050

Taipei Branch:

2F, No. 11, Lane 218, Sec 2 Jhongsing Rd., Sindian City, Taipei County 23146, Taiwan

Tel: 886-2-2910-3838 Fax: 886-2-2917-3838

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Controllers category:

Click to view products by Anpec manufacturer:

Other Similar products are found below:

LV5065VB-TLM-H LV5066V-TLM-H LV5725JAZ-AH 633888R MP2908AGF AZ7500EP-E1 NCP1012AP133G NCP1217P133G

NCP1218AD65R2G NCP1234AD100R2G NCP1244BD065R2G NCP1336ADR2G NCP1587GDR2G NCP6153MNTWG

NCP81005MNTWG NCP81101BMNTXG NCP81205MNTXG HV9123NG-G-M934 IR35207MTRPBF ISL6367HIRZ CAT874-80ULGT3

SJ6522AG SJE6600 TLE63893GV50XUMA1 IR35215MTRPBF SG3845DM NCP1216P133G NCP1236DD65R2G NCP1247BD100R2G

NCP1250BP65G NCP4202MNR2G NCP4204MNTXG NCP6132AMNR2G NCP81141MNTXG NCP81142MNTXG NCP81172MNTXG

NCP81203MNTXG NCP81206MNTXG NX2155HCUPTR UC3845ADM UBA2051C IR35201MTRPBF MAX8778ETJ+

MAX17500AAUB+T MAX17411GTM+T MAX16933ATIR/V+ NCP1010AP130G NCP1063AD100R2G NCP1216AP133G

NCP1217AP100G