# ANV32A62ASE

64Kb Serial I<sup>2</sup>C nvSRAM

# **FEATURES**

- Two-Wire Serial Interface

- BI-directional Data Transfer Protocol

- 1MHz Clock Rate

- Low Power Consumption

- Write Protection Pin for Hardware Data Protection

- Internal 8192 x 8b Organized

- Block rollover

- WRITE at Bus Speed

- Self-Timed PowerStore Cycle (8ms)

- Hardware Write-Protect

- Unlimited READ and WRITE Cycles

- 100k PowerStore Cycles

- 20-Year Non-volatile Data Retention

- 3.0V to 3.6V Power Supply

- Extended Temperature Range

- 8-pin 150 mil SOIC Packages

- RoHS-Compliant

# DESCRIPTION

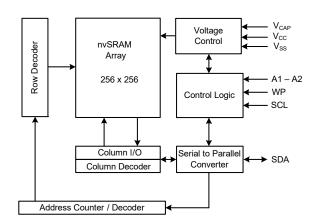

The Anvo-Systems Dresden ANV32A62ASE is a 64Kb serial SRAM with a non-volatile SONOS storage element included with each memory cell, organized as 8k words of 8 bits each. The devices are accessed by a two-wire bus. Up to 4 cascadable devices can share the common bus. The ANV32A62ASE is accessed via a two-wire interface consisting of Serial Data / Address (SDA) and Serial Clock (SCL). All STORE cycles are self-timed.

The serial nvSRAM provides the access and cycle times, easy to use and unlimited READ and WRITE endurance of a SRAM.

Data transfers automatically to the non-volatile storage cells when power loss is detected or in any brown out situation (PowerStore). As long as power will be supplied within operating conditions all data stay volatile in the SRAM cells.

WRITE Protection of data in upper quarter of address space of the memory occurs when the Write Protect pin is connected to  $V_{CC}.$

## **BLOCK DIAGRAM**

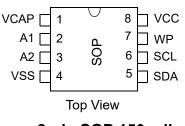

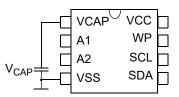

# PIN CONFIGURATION

8-pin SOP 150 mil

## PIN DESCRIPTION

| Signal Name | Signal Description        |  |  |

|-------------|---------------------------|--|--|

| A1 - A2     | Address Inputs            |  |  |

| SCL         | Serial Clock              |  |  |

| SDA         | Serial Data / Address     |  |  |

| WP          | Write Protect             |  |  |

| VCC         | Supply Voltage            |  |  |

| VCAP        | PowerStore Supply Voltage |  |  |

| VSS         | VSS Ground                |  |  |

This product conforms to Anvo-Systems Dresden specifications

# **Pin Description**

**Device Select Addresses (A2, A1)**: The 2 pins A1 - A2 are device address inputs to select 1 of up to 4 devices of the same type on the same SCL / SDA bus. To select one device the hard wired addresses on the 2 pins have to match with the related bits in the slave address.

**Serial Data / Address (SDA)**: The SDA pin is a bidirectional pin for the data transfer. As output it is open drain and as input it will as Schmitt trigger to increase

## **Memory Architecture**

The ANV32A62ASE is a 64Kb serial nvSRAM 8Kb x 8 organized. It is using a standard two-wire interface ( $l^2C$ ) and is functional similar to serial EEPROMs or FRAM. The addressing requires a 13 bit address out of the 2-byte address of the two-wire protocol.

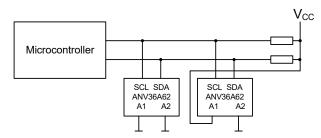

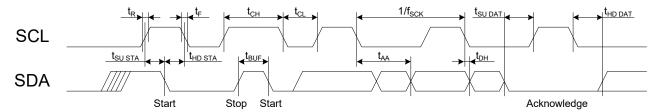

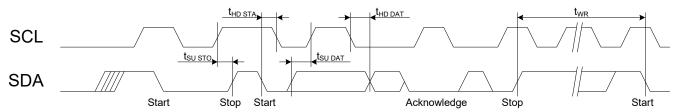

### **Two-wire Interface**

The ANV32A62ASE is designed to support a bi-directional two-wire bus protocol. Figure 1 below shows a typical system configuration.

Any device sending data onto the bus is the transmitter and the target device is the receiver. The master controls the bus and is generating the clock for all devices on the bus. All controlled devices are slaves and the ANV32A62ASE is a slave.

Fig.1: System configuration example

#### **Stop Condition**

Master must have the control over the two-wire bus, no memory READ can be in progress, to assert a stop condition. A stop condition is valid when the master drives SDA from low to high when SCL is stable high. All operations should end with such a stop condition. Any operation which is in progress will be aborted.

#### Start Condition:

A start condition is indicated when the master drives SDA from high to low while SCL is stable high. All commands should be preceded by a start condition.With a start condition any operation in progress can be aborted at any time. **Serial Clock (SCL)**: The SCL input clocks in the data into the nvSRAM with the positive edge and with the negative edge the data clocked out of the device.

**Write Protect (WP)**: The WP input pin controls the Write access to the upper 16Kb of the memory. When WP is connected to ground the whole nvSRAM can be written. If the pin is floating it will be internally pulled down to ground. When WP is connected to  $V_{CC}$  the upper 16Kb are read-only.

#### Data Transfer:

All address and data transfers take place while SCL is high. Data on SDA may change only during SCL low phase. The SDA pin should not change while SCL is high. All data transfers occur with MSB first.

#### Acknowledge:

All addresses and data words are serially transmitted to and from the ANV32A62ASE in 8-bit words. During the 9<sup>th</sup> clock cycle the ANV32A62ASE sends a zero to acknowledge receipt of the byte or expect a zero from the master to send the next byte. If there is no acknowledge signal the condition is no-acknowledge and the operation is aborted.

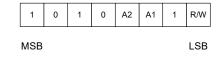

#### Slave Address:

After start condition the first byte is the slave address. The slave address contains in the bits 7 to 4 the slave ID (1010), in the bits 3 to 1 the device select address bits and in bit 0 the selection for read or write operation. See Figure 2.

Fig. 2: Device Address

#### Addressing Overview:

The ANV32A62ASE uses the 2 device addresses A2 to A1 to allow up to 4 devices on the same bus. After acknowledge the device address from the selected device the master can send the 2 byte memory address to the bus for a write operation. Internally the 13 bit address will be latched. With each access the latched address will be incremented by 1. The current address is the value in the latch which is either a new written address or the address following the last access as long as power is supported or a new address is written in the latch.

Reads always use the current address. To start a random read a "dummy write" has to occur before.

#### Memory Reset:

The part can be reset by clocking up to 9 cycles and looking for SDA high in each cycle followed by start condition.

# **Device Operation**

The ANV32A62ASE operates most similar like other two-wire interface memory products. Major differences are related to the nvSRAM technology, especially the PowerStore operation as explained below.

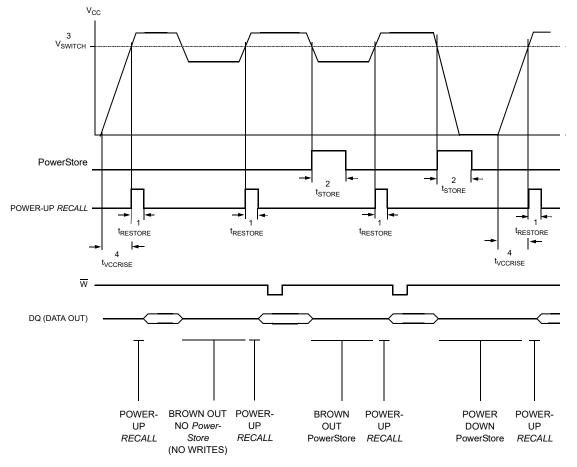

#### Power Up Recall:

During power up or after any low-power condition ( $V_{CC}$ < $V_{RESET}$ ), an internal RECALL request will be latched. When  $V_{CC}$  once again exceeds the sense voltage of  $V_{SWITCH}$ , a RECALL cycle will automatically be initiated and will take t<sub>RESTORE</sub> to complete.

During Power Up Recall operation, all input information will be ignored and SDA is high-Z.

#### Write:

A write operation requires a start condition first, the 8bit device address with the LSB = 0 to select Write function, followed by the acknowledgment from the nvSRAM. Thereafter the first 8 address bits, where the first 3 bits are don't care, will be clocked in and after acknowledgement the second 8- address bits will be clocked in. After acknowledgment first 8-bit data word can be clocked in. An unlimited number of data bytes can be clocked in and will be stored volatile as long as the master doesn't send the stop condition. Before the nvSRAM sent a 0 to the bus for acknowledgement the internal address counter will be incremented by 1. When the end of the address range is reached internally, the address counter will wrap from 1FFFh to 0000h. The complete memory can be written with one write operation. With the stop condition a new READ or WRITE operation can be executed.

If the WRITE will not be terminated by a stop condition, all written data of the last byte will be ignored.

Every, with start and stop condition, completely executed write operation will store all volatile data to non-volatile with the next power down cycle. This is also valid for all written data of the current write operation and all prior written valid volatile data out of incomplete writes without stop condition.

When Write Protect pin is pulled to  $V_{CC}$  the upper 16Kb are write protected and the internal address counter will not increment addresses in this upper block.

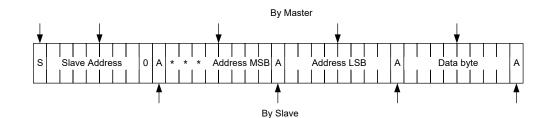

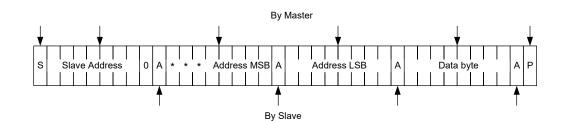

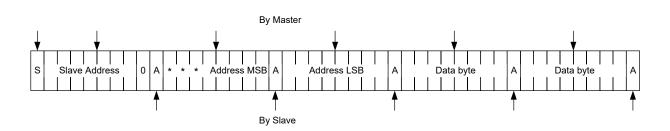

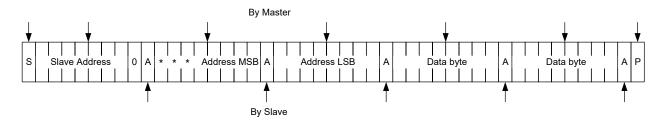

Single byte writes and multiple byte writes, volatile and non-volatile, are illustrated in Fig. 3 to Fig. 6 below.

Fig.3: volatile single byte write

Fig. 4: single byte write

Fig. 5: volatile multiple byte write

Fig. 6: non-volatile multiple byte write

#### **Read Operation**

There are 3 types of read operations:

- current address read

- sequential read

- random read

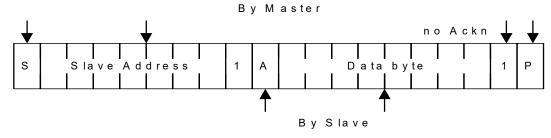

#### **Current Address Read**

The internal address counter maintains the last address of any completed write or read operation incremented by 1. This will be the address for the data byte which will be clocked out. The master has just to send the start condition followed by the slave address and LSB = 1. The Slave will acknowledge and clock out 8 data bits. To complete the current address read the master will not acknowledge in the 9th clock cycle and sent in the 10<sup>th</sup> clock cycle a stop condition.

Fig.7 illustrates the current address read operation.

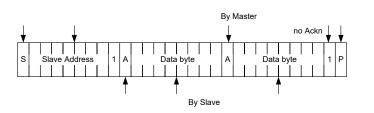

#### Sequential Read

Any Current Address Read is the first sequence of Sequential Read. After clocking out the first data byte the nvSRAM increments the internal address counter

by 1 and after an acknowledgement from the master the next byte will be clocked out. Any acknowledgement from the master is a further start for clocking out the next sequential byte so that the complete memory can be read out independent what the start address was.

Fig. 8 illustrates the sequential read.

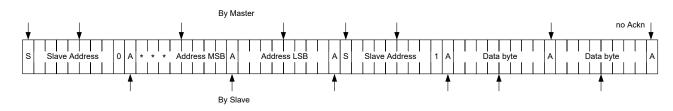

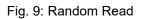

#### **Random Read**

Any random read requires a dummy byte write sequence to load the data word address. Once the device address and the data address are clocked in and acknowledged by the nvSRAM, the master has to generate a start condition again. Now the master can initiate a random read by sending the slave address the read/write select bit =1. with After acknowledgement by the slave it will clock out the first byte of data. If master doesn't acknowledge the data byte and send a stop condition the random read operation is finished. In case the master acknowledges the first data byte the slave will clock out the sequential next byte. This will continue as long as the master acknowledge each clocked out data byte.

Fig. 9 illustrates random read.

Fig. 7: Current Address Read

Fig. 8: Sequential Read

#### **PowerStore Operation:**

PowerStore operation is a unique feature of the SONOS technology that is enabled by default on the ANV32A62ASE.

During normal operation, the device will draw current from V<sub>CC</sub> for circuit operation and to charge a capacitor connected to the V<sub>CAP</sub> pin. This stored charge will be used by the chip to perform a single STORE operation in case of power down. If the voltage on the V<sub>CC</sub> pin drops below V<sub>SWITCH</sub>, the part will automatically disconnect the V<sub>CAP</sub> pin from V<sub>CC</sub>. A STORE operation will be initiated with power provided by the V<sub>CAP</sub> capacitor.

If a WRITE operation is in progress all data of complete written pages are valid. Only the last incomplete written byte will be ignored. With the following Power Store execution these data become non-volatile.

Below, is shown the proper connection of the storage capacitor ( $V_{CAP}$ ) for automatic store operation. Refer to the DC CHARACTERISTICS table for the size of  $V_{CAP}$ .

Fig. 10: PowerStore Cofiguration

To reduce needless non-volatile stores, Power Store operation will be ignored unless at least one WRITE operation has taken place since the most recent STORE cycle. The PowerStore Operation is valid for the complete memory array.

#### Power Up Recall:

During power up or after any low-power condition ( $V_{CC}$ < $V_{SWITCH}$ ), an internal RECALL request will be latched. When  $V_{CC}$  once again exceeds the sense voltage of  $V_{SWITCH}$ , a RECALL cycle will automatically be initiated and will take t<sub>RESTORE</sub> to complete.

During Power Up Recall operation, all commands will be ignored.

# ANV32A62ASE

#### **ABSOLUTE MAXIMUM RATINGS<sup>a</sup>**

| Voltage on Input Relative to Ground                     |

|---------------------------------------------------------|

| Voltage on Input Relative to VSS0.6V to (VCC + 0.5V)    |

| Temperature under Bias55°C to 125°C                     |

| Storage Temperature65°C to 150°C                        |

| Power Dissipation                                       |

| DC Output Current (1 output at a time, 1s duration)15mA |

a. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **Operating Conditions**

| Symbol          | Parameter         | ANV32 | A62ASE | Unit |

|-----------------|-------------------|-------|--------|------|

| Symbol          | Falametei         | Min.  | Max.   | Onit |

| V <sub>CC</sub> | Operating Voltage | 3.0   | 3.6    | V    |

## **DC CHARACTERISTICS**

# $(V_{CC} / V = 3.0 - 3.6)$

| SYMBOL                        | PARAMETER                                  | Extended              |                       | UNITS | NOTES                                                                     |

|-------------------------------|--------------------------------------------|-----------------------|-----------------------|-------|---------------------------------------------------------------------------|

| STNIBOL                       | PARAIVETER                                 | MIN                   | MAX                   | UNITS | NOTES                                                                     |

| I <sub>CC1</sub> <sup>a</sup> | Average V <sub>CC</sub> Current at 1MHz    |                       | 1                     | mA    | $V_{\text{IN}} \leq 0.2 V_{\text{CC}} \text{ or } \geq 0.8 V_{\text{CC}}$ |

| I <sub>CC3</sub> <sup>a</sup> | Average V <sub>CC</sub> Current at 400 kHz |                       | 700                   | μA    | $V_{IN} \leq 0.2 V_{CC} \text{ or } \geq 0.8 V_{CC}$                      |

| I <sub>SB1</sub>              | V <sub>CC</sub> Current Standby            |                       | 200                   | μA    | $V_{IN} \leq 0.2V \text{ or } \geq (V_{CC} - 0.2V)$                       |

| I <sub>ILK</sub>              | Input Leakage Current                      |                       | ±3                    | μΑ    | $V_{CC} = max$<br>$V_{IN} = V_{SS}$ to $V_{CC}$                           |

| I <sub>OLK</sub>              | Off-State Output Leakage Current           |                       | ±3                    | μΑ    | $V_{CC} = max$<br>$V_{IN} = V_{SS}$ to $V_{CC}$ ,                         |

| V <sub>IH</sub>               | Input Logic "1" Voltage                    | 0.8V <sub>CC</sub>    | V <sub>CC</sub> + 0.5 | V     | All Inputs                                                                |

| V <sub>IL</sub>               | Input Logic "0" Voltage                    | V <sub>SS</sub> – 0.5 | 0.2V <sub>CC</sub>    | V     | All Inputs                                                                |

| R <sub>IN</sub>               | Address Input Resistance                   | 50                    |                       | КОНМ  | $V_{IN} = V_{IL}$                                                         |

| V <sub>OL</sub>               | Output Logic "0" Voltage                   |                       | 0.4                   | V     | I <sub>OUT</sub> = 2 mA                                                   |

| T <sub>A</sub>                | Operating Temperature                      | -40                   | 105                   | °C    |                                                                           |

| C <sub>CAP</sub>              | Storage Capacitor                          | 48                    | 100                   | μF    | 6.3V                                                                      |

| NV <sub>C</sub>               | PowerStore operations                      | 100                   |                       | К     |                                                                           |

| DATA <sub>R</sub>             | Data Retention                             | 20                    |                       | Years | @70 °C after last STORE operation                                         |

Note a: I<sub>CC1</sub> and I<sub>CC3</sub> are dependent on output loading and cycle rate. The specified values are obtained with outputs unloaded.

### **AC Characteristics**

| Switching Characteristics      | Symbol              | Min. | Max. | Unit |

|--------------------------------|---------------------|------|------|------|

| SCK Clock Frequency            | f <sub>SCK</sub>    | 0    | 1    | MHz  |

| Clock High Period <sup>a</sup> | t <sub>CH</sub>     | 400  |      | ns   |

| Clock Low Period <sup>a</sup>  | t <sub>CL</sub>     | 600  |      | ns   |

| Input Rise Time <sup>b</sup>   | t <sub>R</sub>      |      | 300  | ns   |

| Input Fall Time <sup>c</sup>   | t <sub>F</sub>      |      | 100  | ns   |

| Clock Low to Data Out Valid    | t <sub>AA</sub>     |      | 550  | ns   |

| Bus Free before new Transition | t <sub>BUF</sub>    | 500  |      | ns   |

| Start Condition Hold Time      | t <sub>HD STA</sub> | 250  |      | ns   |

| Start Condition Set-Up Time    | t <sub>SU STA</sub> | 250  |      | ns   |

| Data in Hold Time              | t <sub>HD DAT</sub> | 0    |      | ns   |

| Data In Set-Up Time            | <sup>t</sup> SU DAT | 100  |      | ns   |

| Stop Set-UP Time               | t <sub>su sto</sub> | 250  |      | ns   |

| Data Out Hold Time             | t <sub>DH</sub>     | 0    |      | ns   |

| nv-Write Cycle Time            | t <sub>WR</sub>     |      | 8    | ms   |

a. t<sub>CH</sub> + t<sub>CL</sub>  $\geq$  1 / f<sub>SCK</sub>

b.  $0.2 V_{CC}$  to  $0.8 V_{CC}$

c.  $0.8 V_{CC}$  to  $0.2 V_{CC}$

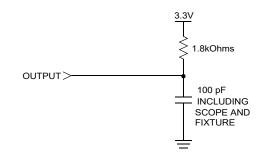

# **AC TEST CONDITIONS**

| ļ | Input Pulse Levels 0V to 3V                   |

|---|-----------------------------------------------|

| ļ | Input Rise and Fall Times                     |

| ļ | Input and Output Timing Reference Levels 1.5V |

| ļ | Output Load                                   |

#### CAPACITANCE

# (T<sub>A</sub> = 25°C, f = 1.0MHz)

| SYMBOL           | PARAMETER          | MAX | UNITS | CONDITIONS             |

|------------------|--------------------|-----|-------|------------------------|

| CIN              | Input Capacitance  | 5   | pF    | ∆V = 0 to 3.3V         |

| C <sub>OUT</sub> | Output Capacitance | 7   | pF    | $\Delta V = 0$ to 3.3V |

These parameters are guaranteed but not tested.

#### Fig. 11: AC Output Loading

#### PowerStore/POWER-UP RECALL

| NO. SYMBOLS |                                   | PARAMETER             | ANV32                     | UNITS |      |    |

|-------------|-----------------------------------|-----------------------|---------------------------|-------|------|----|

|             |                                   | FARAWETER             | MIN                       | MAX   | 0113 |    |

| 1           | t <sub>RESTORE</sub> <sup>a</sup> |                       | Power-up RECALL Duration  |       | 200  | μs |

| 2           | t <sub>STORE</sub>                | PowerStore Cycle time |                           |       | 8    | ms |

| 3           | V <sub>SWITCH</sub>               |                       | Low Voltage Trigger Level |       | 2.95 | V  |

| 4           | t <sub>VCCRISE</sub>              |                       | V <sub>CC</sub> rise time | 100   |      | μs |

a.  $t_{\mbox{\scriptsize RESTORE}}$  starts from the time  $V_{\mbox{\scriptsize CC}}$  rises above  $V_{\mbox{\scriptsize SWITCH}}$

# ANV32A62ASE

## POWER-UP RECALL and Brown Out

## **Read Bus Timing**

# Write BusTiming

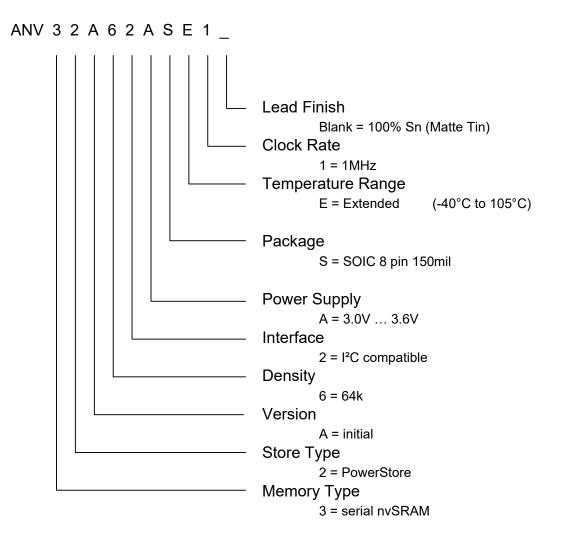

#### **Product Versions**

The ANV32A62ASE will be available with the feature sets:

- Supply voltage range 3.0 to 3.6V

# Anvo-Systems Dresden

#### Initial Delivery State

The device is delivered with non-volatile memory array "0".

#### NOISE CONSIDERATIONS

The ANV32A62ASE is a high-speed memory and so must have a high-frequency bypass capacitor of approximately  $0.1\mu$ F connected between V<sub>CC</sub> and V<sub>SS</sub>, using leads and traces that are as short as possible. As with all high-speed CMOS ICs, common careful routing of power, ground and signals will help prevent noise problems.

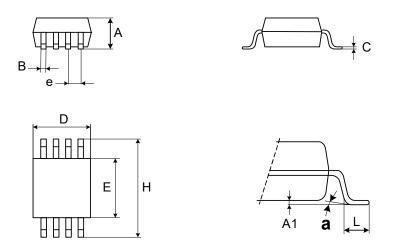

# Package

# 8-pin 150mil SOIC

| Symbol |      | mm   |      | inches |       |       |  |

|--------|------|------|------|--------|-------|-------|--|

| Symbol | typ  | min. | max  | typ.   | min.  | max.  |  |

| А      |      | 1.35 | 1.75 |        | 0.053 | 0.069 |  |

| A1     |      | 0.1  | 0.25 |        | 0.004 | 0.010 |  |

| В      |      | 0.33 | 0.51 |        | 0.013 | 0.020 |  |

| С      |      | 0.19 | 0.25 |        | 0.007 | 0.010 |  |

| D      |      | 4.80 | 5.00 |        | 0.189 | 0.197 |  |

| E      |      | 3.80 | 4.00 |        | 0.150 | 0.157 |  |

| е      | 1.27 |      |      | 0.050  |       |       |  |

| Н      |      | 5.80 | 6.20 |        | 0.228 | 0.244 |  |

| L      |      | 0.40 | 0.90 |        | 0.016 | 0.035 |  |

| а      |      | 0°   | 8°   |        | 0°    | 8°    |  |

# **Ordering Information**

#### **Document Revision History**

| Revision | Date     | Summary         |

|----------|----------|-----------------|

| 1.0      | May 2019 | initial version |

|          |          |                 |

|          |          |                 |

|          |          |                 |

|          |          |                 |

|          |          |                 |

|          |          |                 |

|          |          |                 |

Anvo-Systems Dresden ANV32A62ASE Datasheet, May 2019 Copyright 2019, Anvo-Systems Dresden GmbH. All rights reserved.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for SRAM category:

Click to view products by Anvo-Systems manufacturer:

Other Similar products are found below :

CY6116A-35DMB CY7C1049GN-10VXI GS8161Z36DD-200I GS88237CB-200I RMLV0408EGSB-4S2#AA0 IDT70V5388S166BG IS64WV3216BLL-15CTLA3 IS66WVE4M16ECLL-70BLI PCF8570P K6F2008V2E-LF70000 K6T4008C1B-GB70 CY7C1353S-100AXC AS6C8016-55BIN AS7C164A-15PCN 515712X IDT71V67603S133BG IS62WV51216EBLL-45BLI IS63WV1288DBLL-10HLI IS66WVE2M16ECLL-70BLI IS66WVE4M16EALL-70BLI IS61WV102416DBLL-10TLI CY7C1381KV33-100AXC CY7C1381KVE33-133AXI 8602501XA 5962-3829425MUA 5962-3829430MUA 5962-8866201YA 5962-8866204TA 5962-9062007MXA 5962-9161705MXA GS882Z18CD-150I 8413202RA 5962-8866203YA IS61WV102416DBLL-10BLI CY7C1380KV33-250AXC AS6C8016-55BINTR GS81284Z18B-250I AS7C34096B-10TIN GS84018CB-200I IS62WV25616EALL-55TLI IS61WV204816BLL-10TLI GS8128418B-167IV CY7C1460KV25-200BZXI CY7C1315KV18-333BZXC CY62157G30-45ZSXI 71V016SA12YG RMLV0416EGBG-4S2#AC0 CY62126EV18LL-70BVXI CY62128ELL-45SX CY62146EV30LL-45ZSXA