### J20 technical reference manual 38223 Version 1.0

# Preliminary

November 2016

Auvidea GmbH Kellerberg 3 D-86920 Denklingen

Tel: +49 8243 7714 622 info@auvidea.com www.auvidea.com

## **Copyright Notice**

#### Trademarks

NVIDIA, the NVIDIA logo, CUDA, Jetson, Maxwell, Tegra and VisionWorks are registered trademarks and/or trademarks of NVIDIA Corporation in the United States and other countries. Other company and product names may be trademarks of the respective companies with which they are associated.

#### © Auvidea GmbH 2016

#### All Rights Reserved

No part of this document or any of its contents may be reproduced, copied, modified or adapted, without the prior written consent of the author, unless otherwise indicated for stand-alone materials.

You may share this document by any of the following means: this PDF file may be distributed freely, as long as no changes or modifications to the document are made.

For any other mode of sharing, please contact the author at the email below. info@auvidea.com

Commercial use and distribution of the contents of this document is not allowed without express and prior written consent of Auvidea GmbH.

### Features

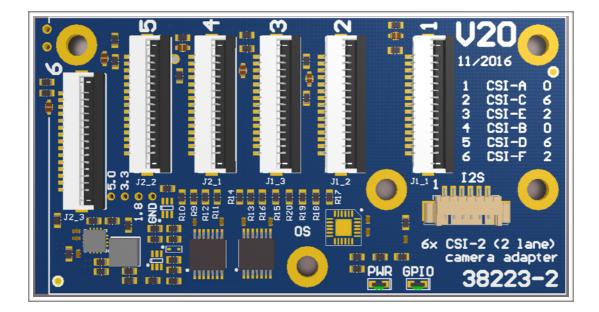

J20 six camera adapter module for the NVIDIA® Jetson™ TX1 dev kit

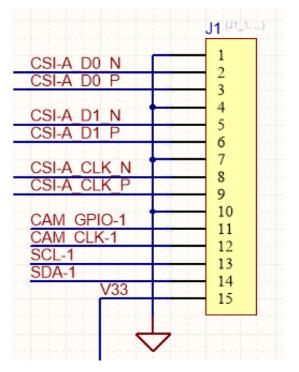

The J20 adapter module is specifically designed for the TX1 dev kit. It plugs into the 120 pin CSI-2 camera socket. Six 2 lane CSI-2 interfaces are provided. The 15 pin CSI-2 connector is compatible to the Raspberry Pi camera connector. Up to six identical camera modules may be plugged in. To access all 6 cameras individually 3 I2C busses are used. Each bus connects to 2 connectors. To separate the 2 cameras on a single I2C bus, the 2nd connector (J2\_x) is connected through an I2C address translation device. This changes the I2C address of the camera so that 2 cameras can coexist on the same I2C bus.

#### Software drivers

The J20 is intended for software developers who wish to develop a software driver for setups with multiple cameras.

- Ridgerun (<u>ridgerun.com</u>) is developing drivers for multiple Raspberry Pi camera setups. Please contact Ridgerun for details.

- Raytrix (raytrix.de) is developing a driver for their C41 4k CSI-2 camera module. Please contact Raytrix for details.

#### Status

- Rev 1: 38223 very limited supply patch for power up reset of GPIO port expander

- Rev 2: 38223-2 first samples end of November 2016

# **I2C** configuration

| # | port | I2C<br>device | CSI-2<br>bus | address<br>translation | Pi camera 1.3 | Pi camera 2.1 | B101 |

|---|------|---------------|--------------|------------------------|---------------|---------------|------|

| 1 | J1_1 | 0             | CSI-A        | -                      | 0x36          | 0x64          | 0x0F |

| 2 | J1_2 | 6             | CSI-C        | -                      | 0x36          | 0x64          | 0x0F |

| 3 | J1_3 | 2             | CSI-E        | -                      | 0x36          | 0x64          | 0x0F |

| 4 | J2_1 | 0             | CSI-B        | $\checkmark$           | 0x34          | 0x12          | 0x0D |

| 5 | J2_2 | 6             | CSI-D        | $\checkmark$           | 0x34          | 0x12          | 0x0D |

| 6 | J2_3 | 2             | CSI-F        | $\checkmark$           | 0x34          | 0x12          | 0x0D |

#### Example: Pi Camera 1.3 plugged into port J1\_1 (I2C device 0)

| \$ i        | 2cd | ete | ct | -у | -r | 0 |    |   |   |   |   |   |    |   |   |   |  |

|-------------|-----|-----|----|----|----|---|----|---|---|---|---|---|----|---|---|---|--|

|             | 0   | 1   | 2  | 3  | 4  | 5 | 6  | 7 | 8 | 9 | а | b | С  | d | е | f |  |

| 00:         |     |     |    |    |    |   |    |   |   |   |   |   |    |   |   |   |  |

| 10:         |     |     |    |    |    |   |    |   |   |   |   |   |    |   |   |   |  |

| 20:         |     |     |    |    |    |   |    |   |   |   |   |   |    |   |   |   |  |

| 30:         |     |     |    |    |    |   | 36 |   |   |   |   |   |    |   |   |   |  |

| 40:         |     |     |    |    |    |   |    |   |   |   |   |   | UU |   |   |   |  |

| 50 <b>:</b> |     |     |    |    |    |   |    |   |   |   |   |   |    |   |   |   |  |

| 60:         |     |     |    |    |    |   |    |   |   |   |   |   |    |   |   |   |  |

| 70:         |     |     |    |    |    |   |    | — |   |   |   |   |    |   |   |   |  |

The "36" is the hex address 0x36 and indicates that no driver is loaded yet. If a driver would have been loaded it would show as "UU" in location "36".

#### Connecting the cable for the cameras or B101 modules

The cameras are connected with the standard 15 pin FFC cable with 1.0mm pitch. To plug in the cable just lift the brown hatch of the connector, insert the cable the press the hatch down.

### Note: please make sure that the contacts of the FFC cable face down. They have to be on the opposite side of the brown hatch.

The cable is now safely locked in place. Some cables may have lengthy stiffeners on the opposite side of the contacts. So it may be difficult to slide the cable in, as the connectors are placed close to each other. In this case please use scissors to shorten the FFC cable. So contact length of 2mm is fine for the connectors on the J20 module.

Auvidea supplies FFC cables with contact on the same side in various lengths.

Note: The Pi cameras and the B101 require FFC cables with contacts on the same side.

### Initialization

The J20 rev1 requires a supply of 1.8V from the dev kit board. This has to be enabled first by writing to the GPIO port expander on the dev kit board. Rev 2 of the J20 features an on-board 1.8V LDO, so the enabling of the 1.8V supply is not required. Please run the following commands every time after powering up the system, so that the J20 is initialized.

| i2cset -f -y 1 0x77 3 0xfb | - enable 1.8V power to the J20 (rev 1 only)                                                                            |

|----------------------------|------------------------------------------------------------------------------------------------------------------------|

| i2cset -f -y 6 0x20 6 0x3e | <ul> <li>configure the outputs of the I2C port expander<br/>(low byte) - clock lines remain input, so there</li> </ul> |

|                            | is no data collision                                                                                                   |

| i2cset -f -y 6 0x20 7 0x33 | <ul> <li>configure the outputs of the I2C port expander<br/>(high byte)</li> </ul>                                     |

| i2cset -f -y 6 0x20 2 0xfe | - write ones to all GPIO outputs and turn on LED (low byte)                                                            |

| i2cset -f -y 6 0x20 3 0xff | - write ones to all GPIO outputs (high byte)                                                                           |

If the initialization commands above have been executed successfully the GPIO LED should be lighted up. The power (PWR) LED should be always on. A Pi camera connected should respond to I2C accesses. We have tested the port detection with i2cdetect. After init the GPIO port expander should show up on address 0x20 (device 6).

In the default configuration the J20 is configured that the GPIO port expander only supplies the CAM\_GPIO signal to the CSI-2 connectors.

With the Raspberry Pi cameras the CAM\_GPIO is the reset to the camera. It must be inactive to allow the camera to work.

The CAM\_CLK by default is connected to the CAM\_CLK signals of the 120 pin dev kit connector. So R11, R12, R15, R16, R17, and R18 are installed. OR resistors (0603 size) or solder jumpers.

Please make sure that the on-board GPIO expander is configured correctly with the i2cset commands as listed above. The clock pins must be configured as inputs. If not then the port expander will drive against the clock signals of the dev kit board. This potentially could cause a hardware damage.

| Default conf                       | figuration of the rea                | sistors:                              | U12<br><u>23</u> VccI2C P15                                                                                    | A_GPIO                                                         |

|------------------------------------|--------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| CLK provideo<br>expander.          | d by the dev kit, GP                 | IO by the GPIO board                  | $\begin{array}{c} 16 \\ 15 \\ 16 \\ 17 \\ 17 \\ 17 \\ 17 \\ 17 \\ 17 \\ 17$                                    | B_GPIO<br>A_CLK<br>B_CLK<br>C_GPIO<br>D_GPIO<br>C_CLK<br>D_CLK |

| A_GPIO<br>B_GPIO<br>A_CLK<br>B_CLK | R9 nb<br>R10 nb<br>R11 0R<br>R12 0R  | SNN_CAM1_RST_3.3<br>SNN_CAM1_MCLK_3.3 | $\begin{array}{c c} 19 \\ 20 \\ \hline \\ 20 \\ \hline \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$  | E_GPIO<br>F_GPIO<br>E_CLK<br>F_CLK                             |

| C GPIO<br>D GPIO<br>C CLK<br>D_CLK | R13nb<br>R14nb<br>R150R<br>R160R     | CAM_RST_3.3<br>CAMFQ_MCLK_3.3         | 22     /INT     P4     44       24     RESET     P2       9     GND     P1       Pad     P0       TCA6416ARTWR |                                                                |

| E_GPIO<br>F_GPIO<br>E_CLK<br>F_CLK | R20 nb<br>R19 nb<br>R18 0R<br>R17 0R | SNN_CAM2_RST_3.3<br>SNN_CAM2_MCLK_3.3 | R48 499R D8                                                                                                    | ST-S220KGKT V3.3                                               |

If you want to modify the settings of the GPIOs to the 6 connectors just change the data in the following 2 commands:

GPIOs all 1:

i2cset -f -y 6 0x20 2 0xfe i2cset -f -y 6 0x20 3 0xff

GPIOs all 0:

i2cset -f -y 6 0x20 2 0x00 i2cset -f -y 6 0x20 3 0x00

#### J20 rev 1

The "clock" resistors are equipped with solder jumpers.

The black rubber covers the power on reset patch for the GPIO port expander.

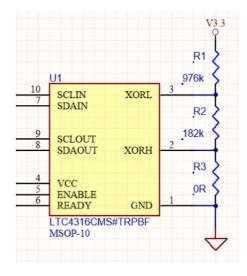

### **I2C address translation**

Configuration resistors for the address translation

The J20 employs an address translation device to change the I2C address for the 2nd connector (J2). This device is configured by 3 resistors (R1, R2 and R3).

By default the address translation is configured for cameras which have a single I2C address. Cameras with multiple I2C addresses may require a custom configuration of the three resistors (R1, R2, and R3).

120 pin SAMTEC connector to the TX1 dev kit

|                                                              |            | 73                |          |          |                                                                                                               |

|--------------------------------------------------------------|------------|-------------------|----------|----------|---------------------------------------------------------------------------------------------------------------|

| SNN_CSLA_D0_P                                                | . 1        | 1                 | 2        | 2        | SNN_CSI_B_D0_P                                                                                                |

| SNN_CSLA_D0_N                                                | 3          | 3                 | 4        | 4        | SNN_CSI_B_D0_N                                                                                                |

| SNN CSI A CLK P                                              | . 5        | 5                 | 6        | 6        | SNN CSI B CLK P                                                                                               |

| SNN CSI A CLK N                                              | 9          | 7                 | 8        | 10       | SNN CSI B CLK N                                                                                               |

|                                                              | 11         | 9<br>11           | 10       | 12       | CHIT_COLD_CERCIT                                                                                              |

| SNN_CSI_A_D1_P                                               | 13         | 13                | 12       | 14       | SNN_CSI_B_D1_P                                                                                                |

| SNN_CSI_A_D1_N                                               | 15         | 15                | 14       | 16       | SNN_CSI_B_D1_N                                                                                                |

|                                                              | 17         | 17                | 18       | 18       |                                                                                                               |

| CON CSI C D0 P                                               | 19<br>21   | 19                | 20       | 20 22    | SNN_CSI_D_D0_P<br>SNN_CSI_D_D0_N                                                                              |

| CON_CSI_C_DU_N                                               | 21         | 21                | 22       | 24       | SNN_CSI_D_DU_N                                                                                                |

| CON CSI C CLK P                                              | 25         | 23                | 24       | 26       | SNN CSI D CLK P                                                                                               |

| CON CSI C CLK N                                              | 27         | 25<br>27          | 26       | 23       | JNN CSI D CLK N                                                                                               |

|                                                              | 29         | 29                | 30       | 30       |                                                                                                               |

| CON_CSI_C_D1_P                                               | 31         | 31                | 32       | 32       | .SNN_CSI_D_D1_P                                                                                               |

| CON_CSI_C_D1_N                                               | 33         | 33                | 34       | 34       | SNN_CSI_D_D1_N                                                                                                |

| SNN CSI E D0 P                                               | 35         | 35                | 36       | 36       | SNN CSI F D0 P                                                                                                |

| SNN_CSI_E_D0_P                                               | 30         | 37                | 38       | 40       | SNN_CSI_F_D0_N                                                                                                |

| 0.00 00 E DO 11                                              | 41         | 39                | 40       | 42       | 0011_00_N                                                                                                     |

| SNN_CSI_E_CLK_P                                              | 43         | 41                | 42       | 44       | SNN_CSI_F_CLK_P                                                                                               |

| SNN CSI E CLK N                                              | 45         | 43                | 44       | 46       | SNN_CSI_F_CLK_N                                                                                               |

|                                                              | 47         | 47                | 40       | 48       |                                                                                                               |

| SNN CSI E D1 P                                               | 49         | 49                | 50       | 50       | SNN CSLF D1 P                                                                                                 |

| SNN_CSI_E_D1_N                                               | 51         | 51                | 52       | 52<br>54 | SNN_CSI_F_D1_N                                                                                                |

| DVDD CAM LV 1                                                | 55         | 53                | 54       | 56       |                                                                                                               |

| TYOD CHALLET                                                 | 57         | 55                | 56       | 58       | DVDD CAM LV 2                                                                                                 |

| SNN UART PRESENT                                             | 39         | 57<br>59          | 58       | 60       | SNN PIN60                                                                                                     |

|                                                              |            | 29                | 00       |          |                                                                                                               |

|                                                              |            |                   |          | 0        |                                                                                                               |

| SNN_UART_TX<br>SNN_UART_RX                                   | 61         | 61                | 62       | 62       | SNN SPI SCK                                                                                                   |

| SNN_UART_CTS                                                 | 65         | 63                | 64       | 66       | SNN SPLCS0                                                                                                    |

| SNN UART RTS                                                 | 67         | 65                | 66       | 63       | SNN_SPI_SCK<br>SNN_SPI_DIN<br>SNN_SPI_CS0<br>SNN_SPI_DOUT                                                     |

| -                                                            | 69         | 67<br>69          | 68<br>70 | 70       |                                                                                                               |

| SNN_DMIC_CLK                                                 | 71         | 71                | 72       | 72       | SNN_12S_CLK                                                                                                   |

| SNN_DMIC_CLK<br>SNN_DMIC_DAT<br>CAM_I2C3_SCL<br>CAM_I2C3_SDA | 73         | 73                | 74       | 74       | SNN 125 LRCLK<br>SNN 125 SDIN<br>SNN 125 SDOUT                                                                |

| CAM_I2C3_SCL                                                 | 75         | 75                | 76       | 76       | SNN 125 SDIN                                                                                                  |

| CAM_12C3_SDA                                                 | 79         | 77                | 78       | 70<br>S0 | SNN_125_50001                                                                                                 |

|                                                              | \$1        | 79                | 80       | 82       | AVDD CAM                                                                                                      |

| VDD CAM FQ HV CAM                                            | 83         | \$1               | 82       | 84       | VDD AF                                                                                                        |

| CAM AE DIAIDAL                                               | \$5        | 83<br>85          | 84<br>86 | \$6      |                                                                                                               |

| CAM_12C2_SCL<br>CAM_12C2_SDA                                 | \$7        | 87                | 30       | 83       | SNN_CAM1_MCLK                                                                                                 |

| CAM_I2C2_SDA                                                 | 39         | 39                | 90       | 90       | CAM VSYNC<br>SNN CAMT MCLK<br>SNN CAMT PWDN<br>SNN CAMT RST<br>SNN CAM2 PWDN<br>SNN CAM2 PWDN<br>SNN CAM2 RST |

| CAMFQ_MCLK<br>CAMFQ_PWDN                                     | 91         | 91                | 92       | 92<br>94 | SNN_CAM1_RST                                                                                                  |

| CAMEQ_PWDN<br>CAM_RST                                        | 93         | 93                | 94       | 94       | SNN CAM2 MOLK                                                                                                 |

| SNN FLASH EN                                                 | 97         | 95                | 96       | 98       | SNN CAM2 RST                                                                                                  |

|                                                              | 99         | 97                | 98       | 100      |                                                                                                               |

| DVDD_CAM_IO_1V2                                              | 101        | 99<br>101         | 100      | 102      | DVDD_CAM_IO_1V8                                                                                               |

| SNN_FLASH_MASK                                               | 103        | 101               | 102      | 104      | SNN_TORCH_EN<br>SNN_FLASH_STROB                                                                               |

| CAMEIZC1_SCL<br>CAMEIZC1_SDA                                 | 105        | 105               | 104      | 106      | SNN_FLASH_STROB                                                                                               |

| CAM_I2C1_SDA                                                 | 107        | 107               | 103      | 103      | VDD_3V3_SLP                                                                                                   |

| IR READY                                                     | 109        | 109               | 110      | 110      | SNN GYRO INT                                                                                                  |

| IR_TRIGGER                                                   | 113        | 111               | 112      | 112      | SNN IR EN                                                                                                     |

|                                                              | 115        | 113               | 114      | 116      |                                                                                                               |

| CAM_INTR                                                     | 117        | 115               | 116      | 118      | V5.0                                                                                                          |

| VDD_SYS_EN                                                   | 119        | 119               | 115      | 120      | VDD_SYS 9                                                                                                     |

|                                                              |            |                   |          |          |                                                                                                               |

|                                                              | 121        | 121               | 122      | 122      |                                                                                                               |

|                                                              | 123<br>125 | 123               | 124      | 124      |                                                                                                               |

|                                                              | 125        | 125               | 126      | 120      |                                                                                                               |

|                                                              |            | 127               | 128      |          |                                                                                                               |

|                                                              | -          | QTH-060-01-L-D-A- |          |          |                                                                                                               |

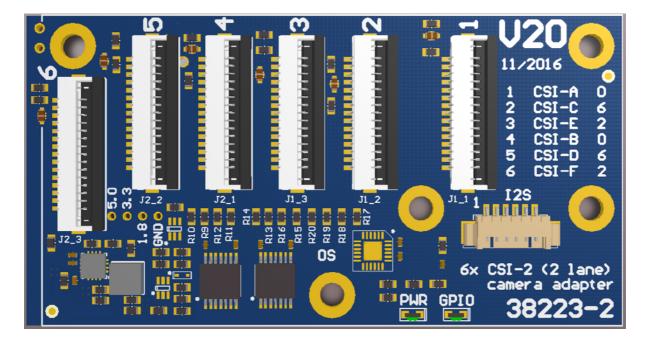

### J20 rev 2

Rev 2 adds the power on reset circuitry and the 1.8V LDO. Also the silkscreen on top on bottom has been extended.

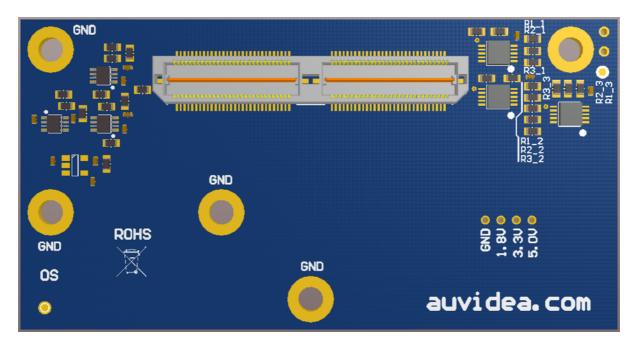

top view:

bottom view:

1. to be added

### Disclaimer

Thank you for reading this manual. If you have found any typos or errors in this document, please let us know.

This is the preliminary version of this data sheet. Please treat all specifications with caution as there may be any typos or errors.

The Auvidea Team

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Sockets & Adapters category:

Click to view products by Auvidea manufacturer:

Other Similar products are found below :

6508-0-00-01-00-00-33-0 AC164348 1262 22827 AC164353 TDGL015 SA247 SM64TQ-ACTEL-1 70-0036 8.06.03 DS91230+ SMPA-ISP-ACTEL-3-KIT 16017 LFVDBGF KIT 70601-3 SM132CQ-ACTEL R0E000010ACB20 IPC0181 IPC0175 IPC0165 AC164397 conga-Thin MITX/eDP to DP Adapter SLG46536V-SKT SLG46621V-SKT SLG46538V-SKT SLG46535V-SKT SLG46722V-SKT ML-ADP-EVN TOOLSTICK990MPP 110-83-320-41-605101 110-83-632-41-605101 110-83-640-41-605101 110-83-628-41-605101 116-83-306-41-001101 PA0003 PA0007 PA0009 PA0035 PA0085 PA0096 IPC0079 ATARD-DBGADPT 80-000286 ATSTK600-RC88 ATSTK600-SC06 ATSTK600-RC78 SPC560PADPT64S AC164345 AC164342 AC164038